# PM8357

# QuadPHY<sup>®</sup> XR

# 4 X 1.2-3.2 Gbit/s Quad, Full Duplex, XAUI Re-timer, 10 Gigabit Ethernet & Fibre Channel Device

# **Data Sheet**

Released Issue No. 5: November 2005

## Legal Information

## Copyright

Copyright 2005 PMC-Sierra, Inc. All rights reserved.

The information in this document is proprietary and confidential to PMC-Sierra, Inc., and for its customers' internal use. In any event, no part of this document may be reproduced or redistributed in any form without the express written consent of PMC-Sierra, Inc.

PMC-2021521 (R5)

## Disclaimer

None of the information contained in this document constitutes an express or implied warranty by PMC-Sierra, Inc. as to the sufficiency, fitness or suitability for a particular purpose of any such information or the fitness, or suitability for a particular purpose, merchantability, performance, compatibility with other parts or systems, of any of the products of PMC-Sierra, Inc., or any portion thereof, referred to in this document. PMC-Sierra, Inc. expressly disclaims all representations and warranties of any kind regarding the contents or use of the information, including, but not limited to, express and implied warranties of accuracy, completeness, merchantability, fitness for a particular use, or non-infringement.

In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or consequential damages, including, but not limited to, lost profits, lost business or lost data resulting from any use of or reliance upon the information, whether or not PMC-Sierra, Inc. has been advised of the possibility of such damage.

## Trademarks

For a complete list of PMC-Sierra's trademarks, see our web site at <u>http://www.pmc-sierra.com/legal/</u>.

Other product and company names mentioned herein may be the trademarks of their respective owners.

## Patents

The technology discussed in this document may be protected by one or more patent grants.

## Contacting PMC-Sierra

PMC-Sierra 100-2700 Production Way Burnaby, BC Canada V5A 4X1

Tel: +1 (604) 415-6000 Fax: +1 (604) 415-6200

Document Information: <u>document@pmc-sierra.com</u> Corporate Information: <u>info@pmc-sierra.com</u> Technical Support: <u>apps@pmc-sierra.com</u> Web Site: <u>http://www.pmc-sierra.com</u>

## **Revision History**

| lssue No. | Issue Date    | Details of Change                                                     |

|-----------|---------------|-----------------------------------------------------------------------|

| 1         | January 2003  | Advance Release                                                       |

| 2         | March 2003    | Advance Release 2                                                     |

| 3         | January 2004  | Preliminary Release                                                   |

| 4         | April 2004    | Production Release                                                    |

| 5         | November 2005 | Updated ordering information including RoHS-compliant device details. |

## **Table of Contents**

| Leo | al Info | rmation2                          |

|-----|---------|-----------------------------------|

|     |         | -ight                             |

|     |         | aimer                             |

|     |         | marks                             |

|     |         | ts2                               |

| Со  |         | g PMC-Sierra                      |

|     |         | History                           |

|     |         | Contents                          |

|     |         | ures                              |

|     | -       | bles                              |

| 1   |         | tions                             |

| 2   |         | res                               |

|     | 2.1     | General Features                  |

|     | 2.2     | High Speed Interface Features     |

|     | 2.3     | Test and Control Features         |

|     | 2.4     | Physical                          |

| 3   | Applic  | rations                           |

| 4   | Refer   | ences                             |

| 5   | Applic  | cation Examples                   |

| 6   | Block   | Diagram                           |

| 7   | Descr   | iption                            |

| 8   | Pin Di  | iagram                            |

| 9   | Pin D   | escription                        |

|     | 9.1     | Pad Summary                       |

| 10  | Funct   | ional Description                 |

|     | 10.1    | Clock Synthesizer                 |

|     | 10.2    | Transmit Data Path                |

|     | 10.3    | Receive Data Path                 |

|     | 10.4    | Crossbar                          |

|     | 10.5    | Management Interface46            |

|     | 10.6    | JTAG Test Access Port Interface47 |

| 11  | Regis   | ter Memory Map48                  |

| 12  | Norm    | al Mode Register Description1     |

| 13 | Test F   | eatures Description                      | 140 |  |  |  |  |  |  |

|----|----------|------------------------------------------|-----|--|--|--|--|--|--|

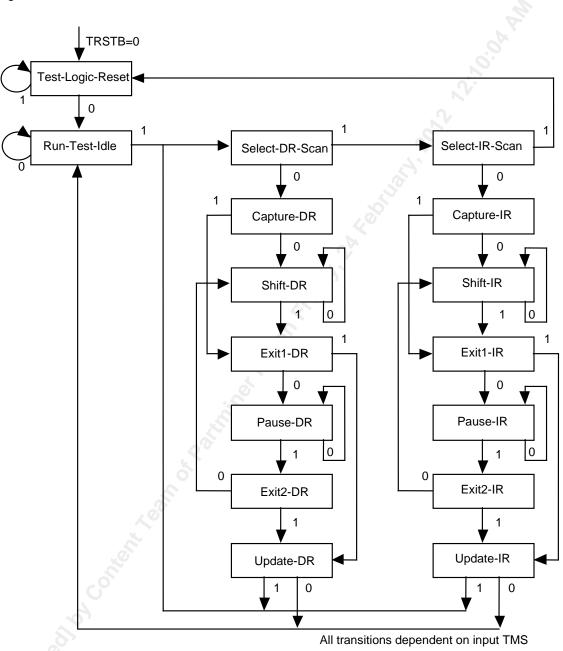

|    | 13.1     | JTAG Test Port                           |     |  |  |  |  |  |  |

|    | 13.2     | JTAG Control                             |     |  |  |  |  |  |  |

| 14 | Opera    | tion                                     |     |  |  |  |  |  |  |

|    | 14.1     | Modes of Operation                       | 146 |  |  |  |  |  |  |

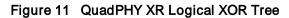

|    | 14.2     | Logical XOR Programmability              |     |  |  |  |  |  |  |

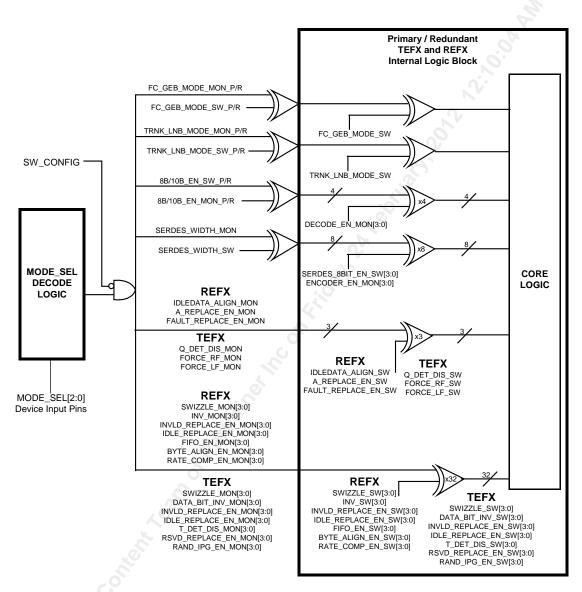

|    | 14.3     | XC16 Cross Bar Operation                 | 149 |  |  |  |  |  |  |

|    | 14.4     | REFX Operation                           | 154 |  |  |  |  |  |  |

|    | 14.5     | Latency                                  | 160 |  |  |  |  |  |  |

|    | 14.6     | Power-up                                 |     |  |  |  |  |  |  |

|    | 14.7     | Interrupt Service Routine                |     |  |  |  |  |  |  |

|    | 14.8     | Board Design Recommendations             | 161 |  |  |  |  |  |  |

|    | 14.9     | High-Speed Serial Interface              | 161 |  |  |  |  |  |  |

|    | 14.10    | PECL and CML Input and Output Levels     | 161 |  |  |  |  |  |  |

|    | 14.11    | High Speed Interface Considerations      | 162 |  |  |  |  |  |  |

| 15 | Function | onal Timing                              | 166 |  |  |  |  |  |  |

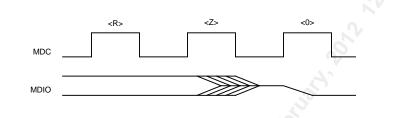

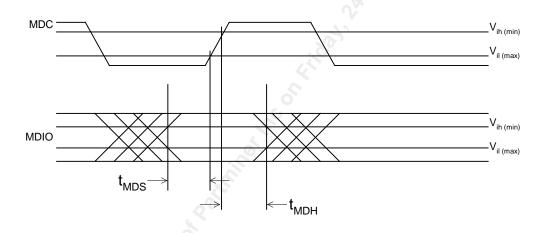

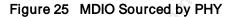

|    | 15.1     | MDIO Functional Timing                   | 166 |  |  |  |  |  |  |

| 16 | Absolu   | ute Maximum Ratings                      | 167 |  |  |  |  |  |  |

| 17 |          | Normal Operating Conditions              |     |  |  |  |  |  |  |

| 18 | Power    | r Information                            | 169 |  |  |  |  |  |  |

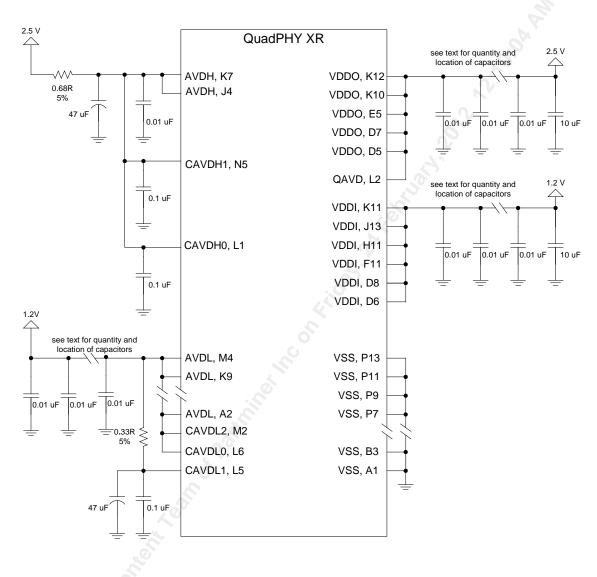

|    | 18.1     | Power Supplies                           | 169 |  |  |  |  |  |  |

|    | 18.2     | Power Supply Decoupling                  | 169 |  |  |  |  |  |  |

|    | 18.3     | Power Requirements                       | 171 |  |  |  |  |  |  |

|    | 18.4     | Power Sequencing                         | 171 |  |  |  |  |  |  |

| 19 | D.C. C   | Characteristics                          | 172 |  |  |  |  |  |  |

| 20 | A.C CI   | haracteristics                           | 174 |  |  |  |  |  |  |

|    | 20.1     | MDIO Interface Characteristics           | 174 |  |  |  |  |  |  |

|    | 20.2     | High Speed Output Characteristics        | 176 |  |  |  |  |  |  |

|    | 20.3     | High Speed Input Characteristics         | 180 |  |  |  |  |  |  |

|    | 20.4     | Reset Timing                             | 182 |  |  |  |  |  |  |

|    | 20.5     | JTAG Timing                              | 182 |  |  |  |  |  |  |

| 21 | Orderi   | ing, Thermal and Reliability Information |     |  |  |  |  |  |  |

| 22 | Mecha    | anical Information                       | 186 |  |  |  |  |  |  |

| No | tes      | 187                                      |     |  |  |  |  |  |  |

## List of Registers

| Register 0x0000: PHY XS, PMA/PMD, PCS Control 1                                                               |    |

|---------------------------------------------------------------------------------------------------------------|----|

| Register 0x0001: PHY XS, PMA/PMD, PCS Status 1                                                                |    |

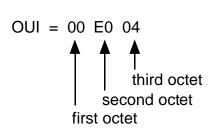

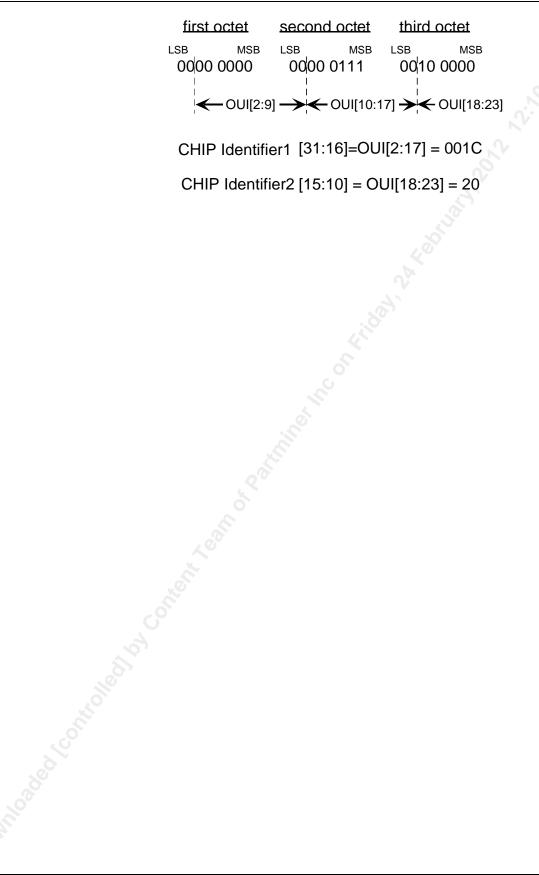

| Register 0x0002: PHY XS, PMA/PMD, PCS Device Identifier 1                                                     | 5  |

| Register 0x0003: PHY XS, PMA/PMD, PCS Device Identifier 2                                                     |    |

| Register 0x0004: PHY XS, PMA/PMD, PCS Speed Ability                                                           |    |

| Register 0x0005: PHY XS, PMA/PMD, PCS Devices in Package 2                                                    | 9  |

| Register 0x0006: PHY XS, PMA/PMD, PCS Devices in Package 1                                                    | 11 |

| Register 0x0007: PMA/PMD, PCS Control 2                                                                       |    |

| Register 0x0008: PHY XS, PMA/PMD, PCS Status 2                                                                | 13 |

| Register 0x0009: PMD Transmit Disable                                                                         | 15 |

| Register 0x000A: PMD Receive Signal Detect                                                                    | 16 |

| Register 0x000E: PHY XS, PMA/PMD, PCS Package Identifier 1                                                    | 17 |

| Register 0x000F: PHY XS, PMA/PMD, PCS Package Identifier 2                                                    | 19 |

| Register 0x0018: PHY XS, PCS Lane Status Register                                                             |    |

| Register 0x0019: PHY XS, PCS Test Control                                                                     |    |

| Register 0xD000: Master Identity and Global Performance Monitor Update                                        | 24 |

| Register 0xD001: Master Reset and Configuration 1                                                             | 27 |

| Register 0xD002: Master Configuration 2                                                                       |    |

| Register 0xD003: Master Receive Fault Configuration                                                           |    |

| Register 0xD004: Master Port A Receive Fault Configuration/Monitor                                            |    |

| Register 0xD005: Master Port B Receive Fault Configuration/Monitor                                            |    |

| Register 0xD006: Master Register Port Status                                                                  |    |

| Register 0xD007: Master Port A Receive Fault Status                                                           |    |

| Registers 0xD008: Master Port B Receive Fault Status                                                          |    |

| Register 0xD009: MDIO Device ID 1                                                                             |    |

| Register 0xD00A: MDIO Device ID 2                                                                             | 53 |

| Register 0xD00C: Master Register Port Status                                                                  | 54 |

| Registers 0xD020, 0xD028, 0xD030, 0xD038: Port A Channel Lanes 0-3<br>Analog Transmit Configuration/Monitor 1 | 55 |

| Registers 0xD021, 0xD029, 0xD031, 0xD039: Port A Channel Lanes 0-3<br>Analog Transmit Configuration 2         | 56 |

| Registers 0xD025, 0xD02D, 0xD035, 0xD03D: Port A Channel Lanes 0–3<br>Analog Receive Configuration 4          | 58 |

| Registers 0xD040, 0xD048, 0xD050, 0xD058: Port B Channel Lanes 0-3<br>Analog Transmit Configuration/Monitor 1 | 60 |

# PMC-SIERRA

| Registers 0xD041, 0xD049, 0xD051, 0xD059: Port B Channel Lanes 0-3<br>Analog Transmit Configuration 2 |     |

|-------------------------------------------------------------------------------------------------------|-----|

| Registers 0xD045, 0xD04D, 0xD055, 0xD05D: Port B Channel Lanes 0–3<br>Analog Receive Configuration 4  |     |

| Registers 0xD080: XC16 Control                                                                        | 65  |

| Registers 0xD081: XC16 Switch Enable                                                                  | 67  |

| Registers 0xD082: XC16 Busy                                                                           |     |

| Registers 0xD083: XC16 IDLE Compare 0                                                                 |     |

| Registers 0xD084: XC16 IDLE Compare 1                                                                 | 70  |

| Registers 0xD085: XC16 IDLE Compare 2                                                                 |     |

| Registers 0xD086: XC16 IDLE Compare 3                                                                 | 72  |

| Registers 0xD087: XC16 IDLE TX                                                                        |     |

| Registers 0xD088: XC16 Lane Reset                                                                     | 74  |

| Register 0xD089: XC16 Terminate Control Character 0                                                   | 75  |

| Register 0xD08A: XC16 Terminate Control Character 1                                                   | 76  |

| Registers 0xD094, 0xD095, 0xD096, 0xD097: XC16 Standby                                                | 77  |

| Registers 0xD0A4, 0xD0A5, 0xD0A6, 0xD0A7: XC16 Standby Active                                         | 79  |

| Registers 0xD0B0: CSU Configuration and Status Registers                                              |     |

| Registers 0xD0B1: CSU Monitor and Interrupt Status Registers                                          |     |

| Registers 0xD100, 0xD200: REFX Port A/Port B Global Control                                           |     |

| Registers 0xD101, 0xD201: REFX Port A/Port B Global Monitor                                           | 85  |

| Registers 0xD102, 0xD202: REFX Port A/Port B PGC Threshold                                            |     |

| Registers 0xD103, 0xD203: REFX Port A/Port B PGC Packet and Idle Length                               |     |

| Registers 0xD104, 0xD204: REFX Port A/Port B 8B/10B Code Error Threshold                              |     |

| Registers 0xD105, 0xD205: REFX Port A/Port B Packet Counter Control                                   |     |

| Registers 0xD106, 0xD206: REFX Port A/Port B Trunked Inserted Column<br>Count                         |     |

| Registers 0xD107H, 0xD207H: REFX Port A/Port B Trunked Deleted Column<br>Count                        |     |

| Registers 0xD108, 0xD208: REFX Port A/Port B Interrupt Enable 1                                       |     |

| Registers 0xD109, 0xD209: REFX Port A/Port B Interrupt Enable 2                                       |     |

| Registers 0xD10A, 0xD20A: REFX Port A/Port B Interrupt Enable 3                                       |     |

| Registers 0xD10B, 0xD20B: REFX Port A/Port B Interrupt Status 1                                       | 97  |

| Registers 0xD10C, 0xD20C: REFX Port A/Port B Interrupt Status 2                                       |     |

| Registers 0xD10D, 0xD20D: REFX Port A/Port B Interrupt Status 3                                       | 100 |

| Registers 0xD10E, 0xD20E: REFX Port A/Port B Status 1                                                 | 102 |

| Registers 0xD10F, 0xD20F: REFX Port A/Port B Status 2                                                 |     |

| Registers | 0xD110, 0xD210: REFX Port A/Port B Status 31                                                                                            | 05 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| Register  | 0xD119, 0xD219: REFX TIP Mask1                                                                                                          | 07 |

| Registers | 0xD140, 0xD150, 0xD160, 0xD170, 0xD240, 0xD250, 0xD260,<br>0xD270: REFX Port A Lanes 0-3 and Port B Lanes 0-3 Control                   | 08 |

|           | 0xD141, 0xD151H, 0xD161, 0xD171, 0xD241, 0xD251, 0xD261,<br>0xD271: REFX Port A Lanes 0-3 and Port B Lanes 0-3 Monitor                  | 11 |

|           | 0xD142, 0xD152, 0xD162, 0xD172, 0xD242, 0xD252, 0xD262,<br>0xD272: REFX Port A Lanes 0-3 and Port B Lanes 0-3 PGC Control               | 13 |

| •         | 0xD143, 0xD153, 0xD163, 0xD173, 0xD243, 0xD253, 0xD263,<br>0xD273: REFX Port A Lanes 0-3 and Port B Lanes 0-3 PGC Error<br>Count        | 15 |

| -         | 0xD144, 0xD154, 0xD164, 0xD174, 0xD244, 0xD254, 0xD264,<br>0xD274: REFX Port A Lanes 0-3 and Port B Lanes 0-3 8B/10B Error<br>Count     | 16 |

| •         | 0xD145, 0xD155, 0xD165, 0xD175, 0xD245, 0xD255, 0xD265,<br>0xD275: REFX Port A Lanes 0-3 and Port B Lanes 0-3 Packet Error<br>Count     | 17 |

| Registers | 0xD146, 0xD156, 0xD166, 0xD176, 0xD246, 0xD256, 0xD266,<br>0xD276: REFX Port A Lanes 0-3 and Port B Lanes 0-3 Total Packet<br>Count MSW |    |

| •         | 0xD147, 0xD157, 0xD167, 0xD177, 0xD247, 0xD257, 0xD267,<br>0xD277: REFX Port A Lanes 0-3 and Port B Lanes 0-3 Total Packet<br>Count LSW | 19 |

| Registers | 0xD300, 0xD400: TEFX Port A and Port B Global Control 1                                                                                 | 20 |

| Registers | 0xD301, 0xD401: TEFX Port A and Port B Global Diagnostic1                                                                               | 23 |

| Registers | 0xD302, 0xD402: TEFX Port A and Port B Packet Counter Control 1                                                                         | 25 |

| Registers | 0xD303, 0xD403: TEFX Port A and Port B Interrupt Enable 1                                                                               | 27 |

| Registers | 0xD304, 0xD404: TEFX Port A and Port B Interrupt Status 1                                                                               | 28 |

| Registers | 0xD305, 0xD405: TEFX Port A and Port B Status1                                                                                          | 29 |

|           | 0xD320, 0xD328, 0xD330, 0xD338, 0xD420, 0xD428, 0xD430,<br>0xD438: TEFX Port A Lanes 0-3 and Port B Lanes 0-3 Control                   | 30 |

| 0         | 0xD321, 0xD329, 0xD331, 0xD339, 0xD421, 0xD429, 0xD431,<br>0xD439: TEFX Port A Lanes 0-3 and Port B Lanes 0-3 Control and<br>Diagnostic | 34 |

| Ū.(O.     | 0xD322, 0xD32A, 0xD332, 0xD33A, 0xD422, 0xD42A, 0xD432,<br>0xD43A: TEFX Port A Lanes 0-3 and Port B Lanes 0-3 Total Packet<br>Count LSW | 37 |

|           | 0xD323, 0xD32B, 0xD333, 0xD33B, 0xD423, 0xD42B, 0xD433,<br>0xD43B: TEFX Port A Lanes 0-3 and Port B Lanes 0-3 Total Packet<br>Count MSW | 38 |

| 0         | 0xD324, 0xD32C, 0xD334, 0xD33C, 0xD424, 0xD42C, 0xD434,<br>0xD43C: TEFX Port A Lanes 0-3 and Port B Lanes 0-3 Error Packet<br>Count     | 39 |

|           |                                                                                                                                         |    |

## List of Figures

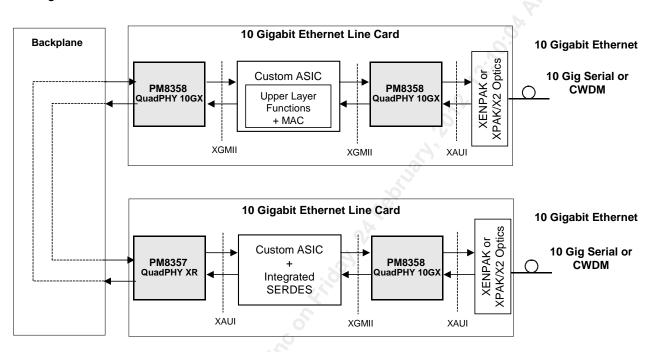

| Figure 1  | QuadPHY XR in XENPAK 10GBASE-LX4 WWDM Optical Module                         |     |

|-----------|------------------------------------------------------------------------------|-----|

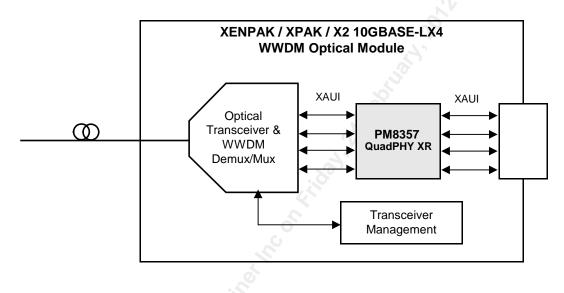

| Figure 2  | QuadPHY XR in 10 Gigabit Ethernet Line Card as a Backplane<br>Extender       |     |

| Figure 3  | QuadPHY XR in 10 Gigabit Ethernet Line Card extending short-reach            |     |

|           | ASIC signals.                                                                |     |

| Figure 4  | Block Diagram                                                                |     |

| Figure 5  | Block Diagram with Loopbacks                                                 |     |

| Figure 6  | Block Diagram: MDIO MMD View                                                 |     |

| Figure 7  | Pin Diagram (Ball View)                                                      |     |

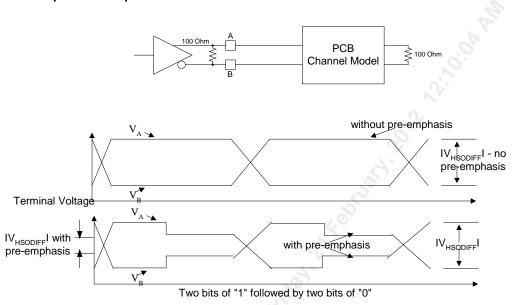

| Figure 8  | Output Pre-Emphasis                                                          |     |

|           | Boundary Scan Architecture                                                   |     |

|           | TAP Controller Finite State Machine                                          |     |

| Figure 11 | QuadPHY XR Logical XOR Tree                                                  | 148 |

| Figure 12 | MUX_PRESET XOR Diagram                                                       | 149 |

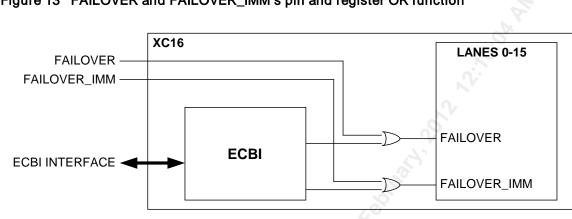

| Figure 13 | FAILOVER and FAILOVER_IMM's pin and register OR function                     | 151 |

| Figure 14 | PGC in the device                                                            | 157 |

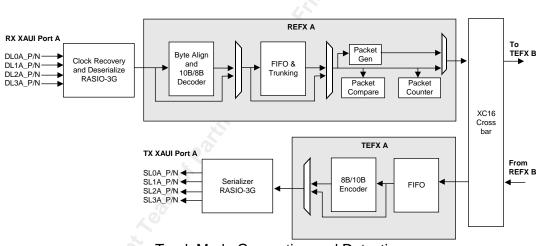

| Figure 15 | Serial Receive and Transmit Interface                                        |     |

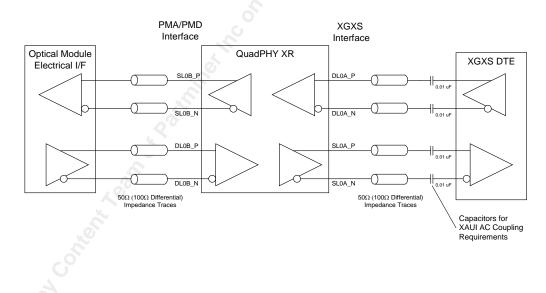

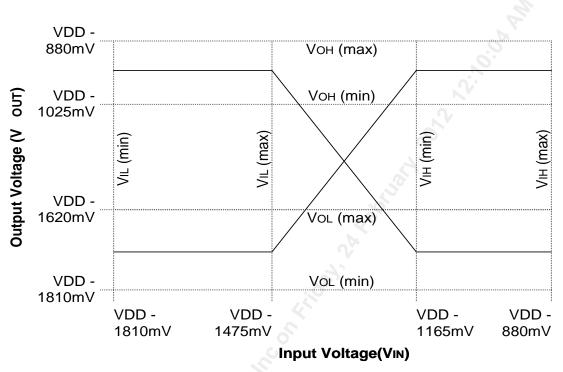

| Figure 16 | PECL Levels (100K Characteristics)                                           | 162 |

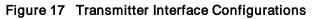

| Figure 17 | Transmitter Interface Configurations                                         | 163 |

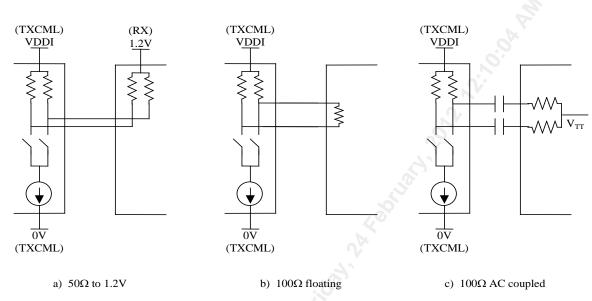

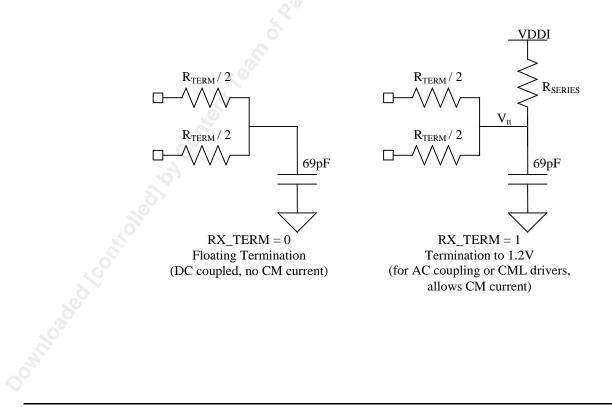

| Figure 18 | Receiver Termination Modes                                                   | 163 |

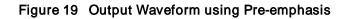

| Figure 19 | Output Waveform using Pre-emphasis                                           |     |

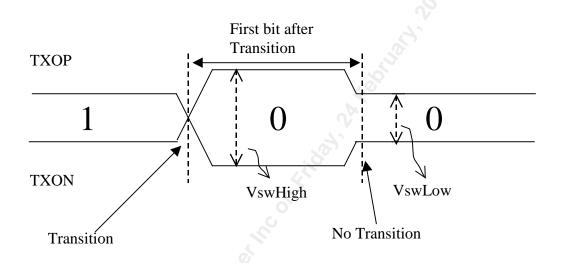

| Figure 20 | AC coupling for LVPECL Clock Signal to REFCLK inputs                         |     |

| Figure 21 | MDIO I/O Functional Timing (MDIO Mode)                                       |     |

| Figure 22 | Power Supply Decoupling                                                      | 170 |

| Figure 23 | Behavior of MDIO During Turnaround Time of a Read Transaction                | 175 |

| Figure 24 | MDIO Sourced by STA                                                          | 175 |

| Figure 25 | MDIO Sourced by PHY                                                          | 175 |

| Figure 26 | Signal Level with No Pre-emphasis                                            | 177 |

| Figure 27 | Signal Level with Pre-emphasis                                               | 178 |

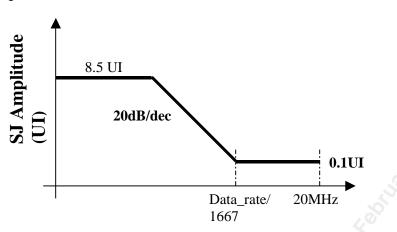

| Figure 28 | XAUI Sinusoidal Jitter Tolerance Mask                                        | 181 |

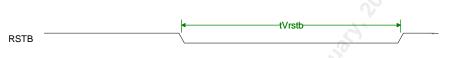

| Figure 29 | Reset Timing                                                                 |     |

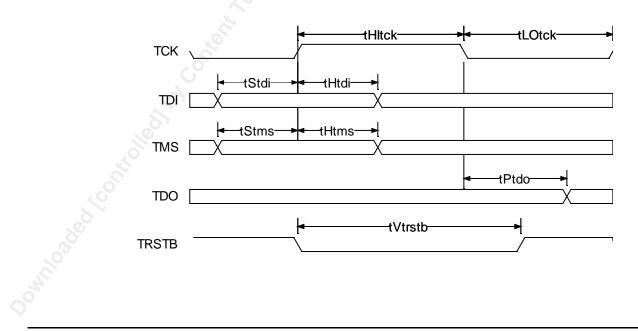

| Figure 30 | JTAG Port Interface Timing                                                   |     |

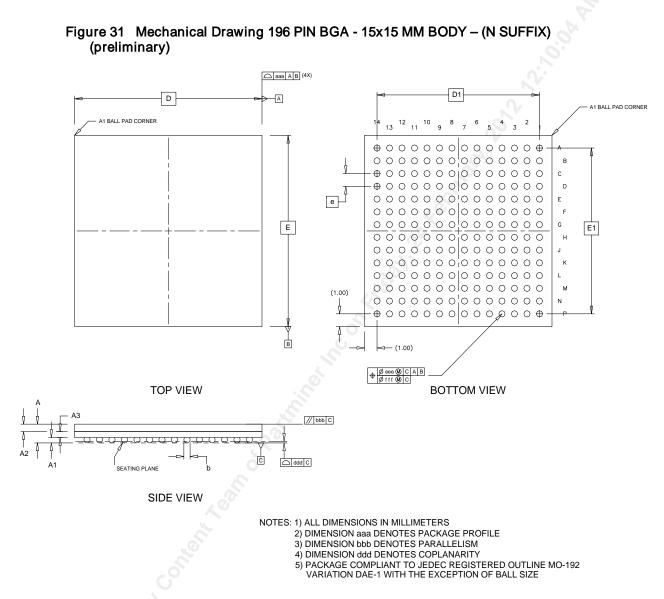

| Figure 31 | Mechanical Drawing 196 PIN BGA - 15x15 MM BODY – (N<br>SUFFIX) (preliminary) |     |

## List of Tables

| Table 1  | Definitions                                                                        |     |

|----------|------------------------------------------------------------------------------------|-----|

| Table 2  | XAUI Receive High Speed Input Pin Descriptions                                     |     |

| Table 3  | XAUI Transmit High Speed Output Pin Descriptions                                   |     |

| Table 4  | Management Interface Pin Descriptions                                              |     |

|          | Cross Bar Control                                                                  |     |

|          | Clock, Control and Status Pin Descriptions                                         |     |

|          | JTAG Test Pin Descriptions                                                         |     |

| Table 8  | Supply and Reference Pin Descriptions                                              |     |

| Table 9  | Pad Summary                                                                        |     |

| Table 10 | REFCLK+/- and PLL Clock Combinations                                               |     |

| Table 11 | Lock time of CSU in bit periods                                                    |     |

| Table 12 | Management Frame Format for Indirect Access                                        |     |

| Table 13 | Indirect Addressing Management Frame Descriptions                                  |     |

| Table 14 | Register Memory Map                                                                |     |

| Table 15 | PATT Register Bits Decode                                                          | 113 |

| Table 16 | Data Swizzle Functionality                                                         |     |

| Table 17 | Instruction Register (Length - 3 bits)                                             |     |

| Table 18 | Identification Register                                                            |     |

| Table 19 | Boundary Scan Register                                                             |     |

| Table 20 | Block Latency                                                                      |     |

| Table 21 | Absolute Maximum Ratings                                                           |     |

| Table 22 | Normal Operating Voltages                                                          |     |

| Table 23 | Power Requirements                                                                 |     |

| Table 24 | D.C. Characteristics (CMOS/TTL) <sup>1</sup>                                       |     |

| Table 25 | Electrical Characteristics of MDIO and MDC Inputs                                  |     |

| Table 26 | CPU Interface Section                                                              |     |

| Table 27 | High-speed Output Characteristics                                                  |     |

| Table 28 | Differential Peak to Peak Output Amplitude, No Pre-emphasis                        |     |

| Table 29 | Differential Peak to Peak Output Amplitude, Pre-emphasis Enabled, Register Control |     |

| Table 30 | Differential Peak to Peak Output Amplitude, Pre-emphasis Enabled, Pin Control      |     |

| Table 31 | High-speed Input Characteristics                                                   |     |

|          |                              | 81 |

|----------|------------------------------|----|

| Table 33 | System Miscellaneous Timing1 | 82 |

|          |                              | 84 |

| Table 34 | Ordering Information         | 54 |

|          |                              |    |

|          |                              |    |

|          |                              |    |

#### Definitions 1

#### Table 1 Definitions

| Definitions         |                                                                                                                               |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------|

| The following table | defines terms and abbreviations used in this document.                                                                        |

|                     |                                                                                                                               |

| Table 1 Definition  | s                                                                                                                             |

| ANSI                | American National Standards Institute                                                                                         |

| ASSP                | Application Specific Standard Product                                                                                         |

| BER                 | Bit Error Rate                                                                                                                |

| BIST                | Built In Self Test                                                                                                            |

| Channel             | A group of 4 Lanes carrying 10GE or 10GFC 8b/10b encoded data.                                                                |

| CMOS                | Complementary Metal Oxide Semiconductor                                                                                       |

| CRU                 | Clock Recovery Unit                                                                                                           |

| DCRU                | Data Clock and Recovery Unit                                                                                                  |

| DTE                 | Data Termination Equipment                                                                                                    |

| ESD                 | Electrostatic Discharge                                                                                                       |

| FC-HSPI             | Fibre Channel – High Speed Parallel Interface                                                                                 |

| FIFO                | First-In First-Out                                                                                                            |

| HSTL                | High Speed Transceiver Logic – 1.5 V                                                                                          |

| IEEE                | Institute of Electrical and Electronics Engineers                                                                             |

| IPG                 | Inter-Packet Gap                                                                                                              |

| JTAG                | Joint Test Action Group                                                                                                       |

| Lane                | single 1.2Gbit/s to 3.2 Gbit/s CML differential pair or a single 8 or 10 bit internal data path in either RX or TX direction. |

| LVDS                | Low Voltage Differential Signaling                                                                                            |

| MDIO                | Management Data Input/Output                                                                                                  |

| MMD                 | MDIO Manageable Device                                                                                                        |

| NC                  | No Connect, indicates an unused pin                                                                                           |

| NCITS               | American National Standard of Accredited Standards Committee.                                                                 |

| PCS                 | Physical Coding Sublayer                                                                                                      |

| PECL                | Pseudo Emitter Coupled Logic                                                                                                  |

| РНҮ                 | Physical Layer                                                                                                                |

| PISO                | Parallel-in-Serial-Out                                                                                                        |

| PMA                 | Physical Medium Attachment                                                                                                    |

| PMD 🚫               | Physical Medium Dependent                                                                                                     |

| Port                | A pair of Channels forming a full duplex data stream.                                                                         |

| PRBS                | Pseudo-Random Binary Sequence                                                                                                 |

| RDI                 | Remote Defect Indication                                                                                                      |

| REFX                | Receive 10G Ethernet/Fibre Channel Telecom System Block                                                                       |

| SAW                 | Surface Acoustic Wave                                                                                                         |

| SD                  | Signal Detect                                                                                                                 |

| SERDES              | Serializer/De-Serializer                                                                                                      |

| SIPO  | Serial-in-Parallel-Out                                   |

|-------|----------------------------------------------------------|

| TEFX  | Transmit 10G Ethernet/Fibre Channel Telecom System Block |

| VCSO  | Voltage Controlled SAW Oscillator                        |

| WAN   | Wide Area Network                                        |

| XAUI  | 10Gb Attachment Unit Interface                           |

| XGMII | 10Gb Media Independent Interface                         |

| XGXS  | XGMII Extender Sublayer                                  |

## 2 Features

#### 2.1 General Features

- IEEE 802.3ae compliant fully redundant, full duplex, XAUI Re-timer, 10 Gigabit Ethernet (10GbE) device

- T11 NCITS 1413-D Rev 3.2 compliant fully redundant, full duplex, XAUI to XAUI, 10 Gigabit Fibre Channel (10GFC) device.

- Integrated serializer/de-serializer, clock recovery, clock synthesis, byte alignment, trunking, and 8B/10B encode/decode logic.

- Supports completely non-blocking cross-connect to enable flexible configuration in parallel loopback, XAUI re-timer or XAUI cross connect.

- Complete 8 lane x 10bit, non-blocking Cross-Connect with any lane to any lane switching capability enabling simpler board layouts. The device implements a smart switchover mechanism allowing connections to be changed during IPG and minimize packet fragmentation.

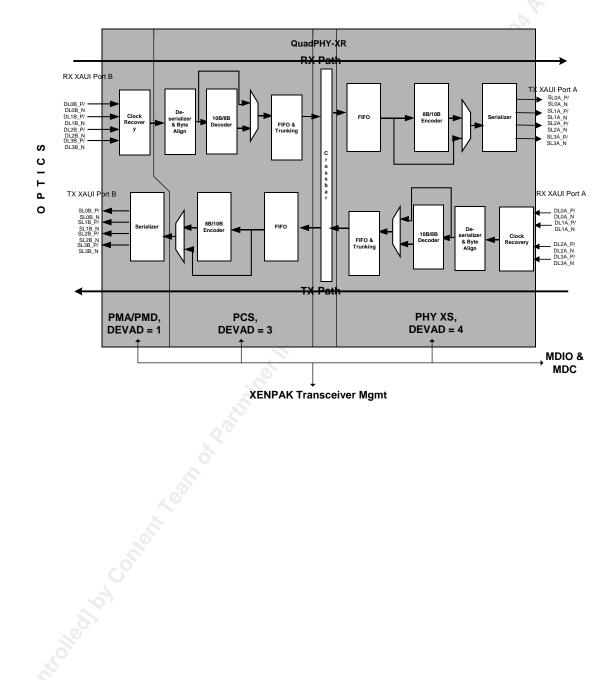

- Implements the PHY-XS constituent of the XGMII Extender Sublayer (XGXS) and the PMA/PMD and PCS MDIO Manageable Devices (MMDs) as defined in IEEE 802.3ae for 10GBASE-X family of physical layer implementations .

- Contains a per-link 16 byte receive FIFO that supports clock rate difference compensation to ± 100 ppm and performs lane-to-lane de-skew/alignment across the four lanes of a 10GbE or 10GFC data stream.

- Supports differential AC coupled PECL level *REFCLK*+/- at 60.00 MHz to 160 MHz for 1.2 Gbit/s to 3.2 Gbit/s operations respectively.

- Supports independent lane based operation each running at 1.2 Gbit/s to 3.2 Gbit/s Gbit/s with 8B/10B encoded data and 2.48832 Gbit/s for per-SERDES scrambled NRZ 8 bit data.

- Electrostatic Discharge tested to meet 2KV HBM and 500V CDM

## 2.2 High Speed Interface Features

- Allows full control and monitoring under the Management Interface of the high-speed ports.

- High-speed outputs with programmable pre-emphasis to counteract dielectric losses and allow maximum reach on printed circuit boards.

- High-speed inputs with programmable equalization to reduce Inter Symbol Interference (ISI) providing robust BER performance.

- Internal 100 ohms differential termination on transmit and receive high-speed signals for optimal signal integrity.

## 2.3 Test and Control Features

• Supports pin programmable configuration with software override. Needs no microprocessor interface for normal mode of operation.

- Supports a optional 2-pin serial management interface using IEEE 802.3ae Clause 45 MDC/MDIO management control for configuration and diagnostic access.

- Supports built in self-test (BIST) via internal packet generation and checking,

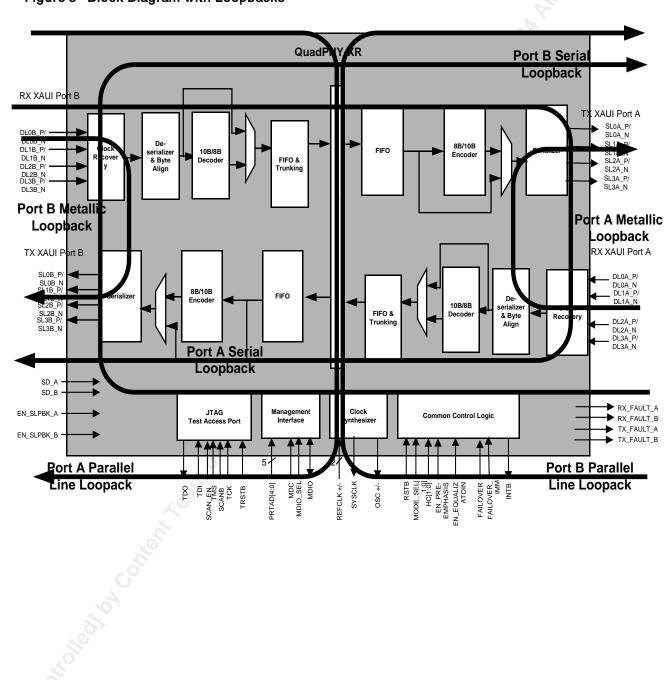

- Supports Metallic Line Loopback, Parallel Line Loopback, Serial Loopback, Parallel Diagnostic Loopback, Recovery Clock Loopback and System Loopback modes for each link/lane for rich debugging capability. Further control over data flow is also available on a per-lane basis.

- Internal CRPAT and CJPAT Packet generator as per IEEE 802.3ae for 10GbE and ANSI T11 NCITS working group for 10GFC.

- Provides automatic packet generation (PRBS 7, PRBS 23, Fixed pattern, Counting pattern) with selective self checking capabilities. All patterns can be framed or unframed, trunked or per-lane, and 8 or 10 bits.

- Supports packet monitoring by providing the total number of packets received and the number of errored packets received.

- Allows bit swizzle and invert of input/output serial data on per-lane basis across the Port A and Port B.

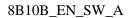

- Provides a standard 5 signal IEEE 1149.1 JTAG test port for boundary scan board purpose.

### 2.4 Physical

- Low power operation with power saving modes to disable unused channels and unused features.

- Power under maximum use configuration with 2 XAUI links is 1.6 Watts typical case.

- Power with only the single XAUI link active with loaded outputs yields only 1 Watt typical case.

- Implemented in 0.13 µm CMOS technology.

- Small footprint 15x15 mm, 196-pin BGA package with 1 mm ball pitch.

## 3 Applications

- 10 Gbits/s full duplex Ethernet or Fibre Channel XAUI retimers.

- 10 Gbits/s full duplex XAUI transponders.

- High-speed serial backplanes.

- Intra-system interconnects.

- 2.5 Gbits/s Infiniband transceivers.

- 2.125 Gbits/s Fibre Channel applications.

- 2.488 Gbit/s pure SERDES mode for NRZ data.

- 1.536 Gbit/s Open Base Station Architecture Initiative (OBSAI) standard.

- 1.2288 & 2.4576 Gbit/s Common Public Radio Interface (CPRI) standard.

- 1.485 Gbit/s SMPTE 292M HD-SDI for HDTV switch/routers.

- 1.25 Gbit/s, 2.5 Gbit/s and 3.125 Gbit/s Serial RapidIO transceivers.

P M C - SIE R R /

- IEEE P802.3ae 2002 Standard for Information Technology Local & Metropolitan Area Networks – Part 3: Carrier sense multiple access with collision detection (CSMA/CD) access method and physical layer specifications--Media Access Control (MAC) Parameters, Physical Layer, and Management Parameters for 10 Gbits/s Operation.

- 2. NCITS T11 project 1413-D Rev 3.5 Fibre Channel 10 Gigabit (10GFC).

- 3. IEEE 1149.1-1990 Standard Test Access Port and Boundary-Scan Architecture.

- 4. PMC-2010750, Signal Integrity for PMC-Sierra 3.125/2.488/1.25 Gbits/s Links Application Note.

- 5. PMC-2010793, High Frequency Simulation with HSPICE Application Note. PMC-Sierra.

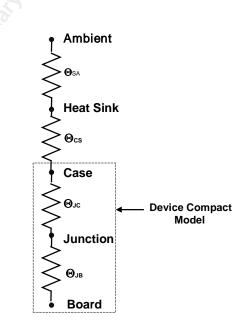

- 6. Electronic Industries Association. *Methodology for the Thermal Measurement of Component Packages (Single Semiconductor Device)*: EIA/JESD51. December 1995.

- 7. Electronic Industries Alliance 1999. Integrated Circuit Thermal Test Method Environmental Conditions -Junction-to-Board: JESD51-8. October 1999.

- 8. Telcordia Technologies. Network Equipment-Building System (NEBS) Requirements: Physical Protection: Telcordia Technologies Generic Requirements GR-63-CORE. Issue 1. October 1995.

- 9. SEMI (Semiconductor Equipment and Materials International). SEMI G30-88 Test Method for Junction-to-Case Thermal Resistance Measurements of Ceramic Packages. 1988.

- 10. ITU-T G.958 "Digital line systems based on the synchronous digital hierarchy for use on optical fibre cables", 1994.

- 11. PMC-2040363, Retimer Support for Serial RapidIO Applications, Issue 1, March 2004.

- 12. PMC-2030760, SERDES and Retimer Support for Infiniband Applications, Issue 1, February 2004.

## 5 Application Examples

The QuadPHY XR has numerous applications throughout data networking and storage applications.

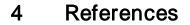

Figure 1 QuadPHY XR in XENPAK 10GBASE-LX4 WWDM Optical Module

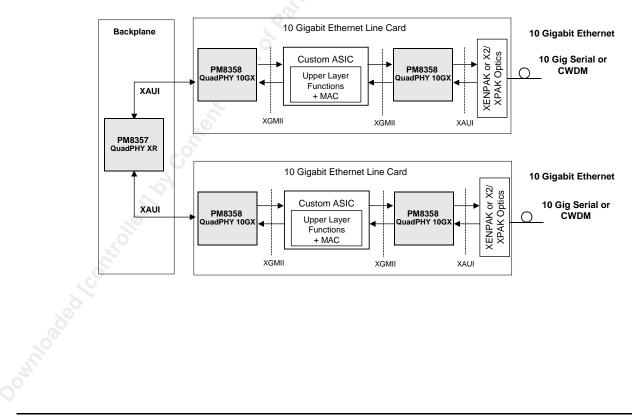

## Figure 3 QuadPHY XR in 10 Gigabit Ethernet Line Card extending short-reach ASIC signals.

## 6 Block Diagram

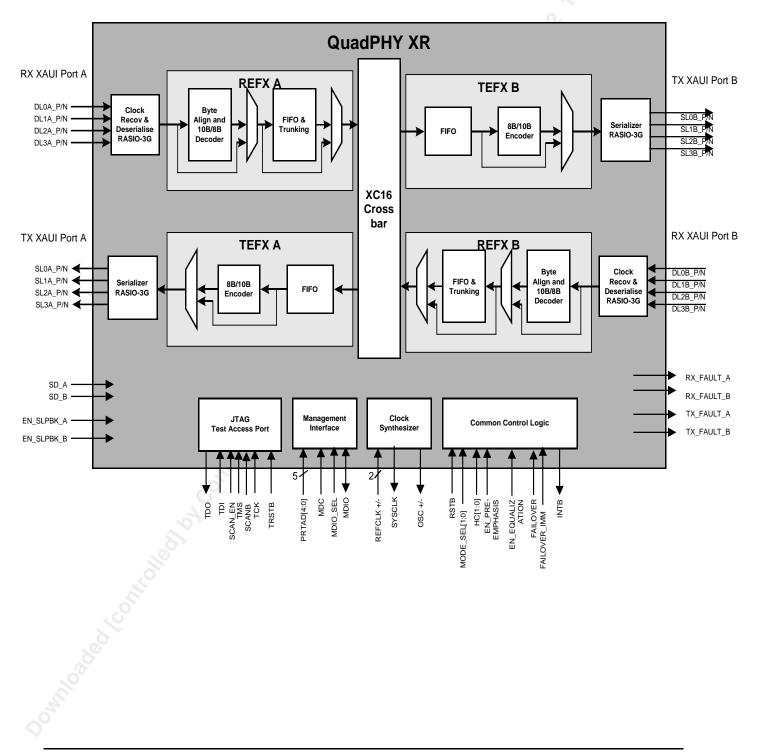

Figure 4 Block Diagram

Figure 5 Block Diagram with Loopbacks

Figure 6 Block Diagram: MDIO MMD View

## 7 Description

The PM8357, QuadPHY XR is an IEEE 802.3ae and T11 compliant, fully redundant, full duplex, XAUI to XAUI 10 Gigabit Ethernet/Fibre Channel SERDES device. It includes integrated serializer/de-serializer, clock recovery, clock synthesis, byte alignment, trunking, and 8B/10B encode/decode logic for both ports. The QuadPHY XR also supports completely non-blocking cross-connect to enable flexible configuration in parallel loopback, XAUI re-timer and XAUI cross-connect. The QuadPHY XR non-blocking cross-connect includes a smart switchover mechanism allowing connections to be changed during IPG and minimize packet fragmentation. The device implements the PHY-XS constituent of the XGMII Extender Sublayer (XGXS) and the PMA/PMD and PCS MDIO Manageable Devices (MMDs) as defined in IEEE 802.3ae for 10GBASE-X family of physical layer implementations (10GBASE-LX4). The QuadPHY XR supports independent lane based operation for all 8 lanes each running at 1.2Gbit/s to 3.2 Gbit/s with 8B/10B encoded data and 2.488 Gbit/s for scrambled NRZ 8 bit data. In addition, the QuadPHY XR supports a differential PECL REFCLK up to 159.375 MHz.

The PM8357, QuadPHY XR device provides a bi-directional high-speed interface with integrated serializer/de-serializer, clock recovery, clock synthesis, byte alignment, and 8B/10B encode/decode logic. The high-speed outputs have programmable pre-emphasis to counteract dielectric losses and allow maximum reach on printed circuit boards. The high-speed inputs with programmable equalization to reduce Inter Symbol Interference (ISI) providing robust BER performance. The QuadPHY XR incorporates internal 100  $\Omega$  differential termination on transmit and receive high-speed interfaces for optimal signal integrity.

The QuadPHY XR device supports pin programmable configuration with a software override for all major modes of operation. For most of the targeted applications, pin configuration is adequate. This device also supports 2-pin serial management interface using an MDC/MDIO interface for configuration and diagnostic access.

The QuadPHY XR supports built in self-test (BIST) via internal packet generator and checker and various serial and parallel loopback modes for testing and debugging on a per-channel basis. The device provides a standard 5 signal IEEE 1149.1 JTAG test port for boundary scan.

The QuadPHY XR has a low power operation and further power savings can be achieved by disabling unused links and unused features. Power for full mode of operation with loaded outputs is 1.6 Watts typical case with 2 XAUI links operating, and only 1 Watt typical case with a single XAUI link active.

The QuadPHY XR is packaged in small footprint 15x15 mm, 196-pin BGA package with 1 mm ball pitch.

PMC-SIERRA

The QuadPHY XR is packaged in a 196 BGA package having a body size of 15 mm by 15 mm and a pin pitch of 1.0 mm.

|   | 14                  | 13               | 12                      | 11     | 10     | 9      | 8      | 7      | 6            | 5      | 4     | 3      | 2      | 1      |   |

|---|---------------------|------------------|-------------------------|--------|--------|--------|--------|--------|--------------|--------|-------|--------|--------|--------|---|

| A | PRTAD3              | TX_FAULT<br>_B   | NC                      | VSS    | PRTAD1 | TRSTB  | TDO    | TDI    | TMS          | RSTB   | MDIO  | HC[1]  | AVDL   | VSS    | А |

| В | MODE_SEL<br>1       | .EN_SLBK_<br>A   | EN_PRE_<br>EMPHASI<br>S | PRTAD0 | PRTAD2 | PRTAD4 | NC     | NC     | тск          | MDC    | HC[0] | VSS    | SL1A_P | SL1A_N | В |

| С | VSS                 | MODE_SE<br>L0    | TX_FAULT<br>_A          | VSS    | VSS    | VSS    | NC     | VSS    | VSS          | VSS    | VSS   | SL0A_P | SL0A_N | VSS    | С |

| D | MDIO_SE<br>L        | EN_SLBK_<br>B    | VSS                     | VSS    | VSS    | VSS    | VDDI   | VDDO   | VDDI         | VDDO   | VSS   | VSS    | DL1A_P | DL1A_N | D |

| Е | SYSCLK              | SD_A             | NC                      | VSS    | VSS    | VSS    | VSS    | VSS    | VSS          | VDDO   | AVDL  | DL0A_P | DL0A_N | VSS    | E |

| F | VSS                 | FAILOVER         | VSS                     | VDDI   | VSS    | VSS    | VSS    | vss    | VSS          | AVDL   | VSS   | VSS    | SL2A_P | SL2A_N | F |

| G | SD_B                | FAILOVER<br>_IMM | NC                      | VSS    | VSS    | VSS    | VSS    | VSS    | VSS          | VSS    | AVDL  | SL3A_P | SL3A_N | VSS    | G |

| н | RX_FAUL<br>T_B      | VSS              | NC                      | VDDI   | VSS    | VSS    | VSS    | VSS    | VSS          | AVDL   | VSS   | VSS    | DL2A_P | DL2A_N | н |

| J | RX_FAUL<br>T_A      | VDDI             | VSS                     | VSS    | vss    | VSS    | VSS    | VSS    | VSS          | VSS    | AVDH  | DL3A_P | DL3A_N | VSS    | J |

| к | EN_EQUA<br>LIZATION | VSS              | VDDO                    | VDDI   | VDDO   | AVDL   | AVDL   | AVDH   | VSS          | VSS    | VSS   | VSS    | AVDL   | VSS    | к |

| L | INTB                | NC               | VSS                     | VSS    | AVDL   | VSS    | VSS    | AVDL   | CAVDL0       | CAVDL1 | VSS   | NC     | QAVD   | CAVDH0 | L |

| М | VSS                 | DL3B_N           | VSS                     | SL2B_N | VSS    | DL0B_N | VSS    | SL0B_N | VSS          | VSS    | AVDL  | VSS    | CAVDL2 | NC     | М |

| N | DL2B_N              | DL3B_P           | SL3B_N                  | SL2B_P | DL1B_N | DL0B_P | SL1B_N | SL0B_P | REFCLK_<br>P | CAVDH1 | NC    | NC     | NC     | NC     | N |

| Ρ | DL2B_P              | VSS              | SL3B_P                  | VSS    | DL1B_P | VSS    | SL1B_P | VSS    | REFCLK_<br>N | VSS    | NC    | VSS    | NC     | VSS    | Р |

|   | 14                  | 13               | 12                      | 11     | 10     | 9      | . 8    | 7      | 6            | 5      | 4     | 3      | 2      | 1      | - |

|   | 14                  | 15               | 12                      |        | 10     | э      | 0      | 1      | U            | 5      | 4     | 3      | 2      | 1      |   |

#### Figure 7 Pin Diagram (Ball View)

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2021521, Issue 5

## 9 Pin Description

#### Table 2 XAUI Receive High Speed Input Pin Descriptions

| Pin Name            | Туре                | Pin       | Function                                                                                                                                                                                                                                                                                                                                         |                                                                                                 |

|---------------------|---------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| DL0A_P              | Analog              | E3        | Port A XAUI Differential Serial Data Inpo                                                                                                                                                                                                                                                                                                        | ut – lane 0                                                                                     |

| DLOA_N CML<br>Input | CML<br>Input        | Ε2        | DL0A_P and DL0A_N are the $3.1875/3.^{\circ}$ differential inputs for lane 0 of port A XAI 10GFC/10GE mode of operation. <i>DL0A</i> _are the 1.2 Gbit/s to 3.2 Gbit/s differentia of the primary serial receive port when cosupport Lane Based and SERDES operadifferential inputs are internally terminate 100 $\Omega$ differential resistor. | JI port in<br><i>P</i> and <i>DLOA_N</i><br>I inputs for lane 0<br>onfigured to<br>ation. These |

|                     |                     |           | These differential inputs are ignored whe<br>Loopback is enabled.                                                                                                                                                                                                                                                                                | en Serial                                                                                       |

|                     |                     |           | If a channel is enabled, active data must<br>or the invalid data will be recovered. Do<br>up/pull-down resistors on the high-speec<br>inputs.                                                                                                                                                                                                    | not use pull-                                                                                   |

|                     |                     |           | These inputs may be left unconnected w is disabled.                                                                                                                                                                                                                                                                                              | hen this channel                                                                                |

| DLOB_P              | Analog              | N9        | Port B XAUI Differential Serial Data Inp                                                                                                                                                                                                                                                                                                         | ut – lane 0                                                                                     |

| DLOB_N              | DLOB_N CML<br>Input |           | DL0B_N and DL0B_N are /3.125 Gbit/s of<br>for lane 0 of port B XAUI port when confi<br>10GFC/10GE mode. DL0B_N and DL0E<br>Gbit/s to 3.2 Gbit/s differential inputs for<br>serial receive port when configured to su<br>Based and SERDES operation.                                                                                              | gured to support<br>3_N are the 1.2<br>lane 0 of port B                                         |

|                     |                     |           | These differential inputs are internally ter $100\Omega$ differential resistor.                                                                                                                                                                                                                                                                  | rminated with a                                                                                 |

|                     |                     |           | These differential inputs are ignored whe Loopback is enabled.                                                                                                                                                                                                                                                                                   | en Serial                                                                                       |

|                     | onter,              |           | If a channel is enabled, active data must<br>or the invalid data will be recovered. Do<br>up/pull-down resistors on the high-speec<br>inputs.                                                                                                                                                                                                    | not use pull-                                                                                   |

|                     | 5                   |           | These inputs may be left unconnected w is disabled.                                                                                                                                                                                                                                                                                              | hen this channel                                                                                |

| DL1A_P              | Analog              | Analog D2 | Port A XAUI Differential Serial Data Inpu                                                                                                                                                                                                                                                                                                        | t – lane 1                                                                                      |

| DL1A_N              | CML<br>Input        | D1        | Equivalent to DL0A_P and DL0A_N for >                                                                                                                                                                                                                                                                                                            | (AUI port lane 1.                                                                               |

| DL1B_P              | Analog              | P10       | Port B XAUI Differential Serial Data Inpu                                                                                                                                                                                                                                                                                                        | t – lane 1                                                                                      |

| DL1B_N              | CML<br>Input        | N10       | Equivalent to DL0B_N and DL0B_N for >                                                                                                                                                                                                                                                                                                            | KAUI port lane 1                                                                                |

| DL2A_P              |                     |           | Port A XAUI Differential Serial Data Inpu                                                                                                                                                                                                                                                                                                        | t – lane 2                                                                                      |

| DL2A_N              | CML<br>Input        | H1        | Equivalent to DL0A_P and DL0A_N for >                                                                                                                                                                                                                                                                                                            | KAUI port lane 2.                                                                               |

| DL2B_P              | Analog              | P14       | Port B XAUI Differential Serial Data Inpo                                                                                                                                                                                                                                                                                                        | ut – lane 2                                                                                     |

| DL2B_N              | CML<br>Input        | N14       | Equivalent to DL0B_N and DL0B_N for X                                                                                                                                                                                                                                                                                                            | KAUI port lane 2.                                                                               |

| Pin Name         | Туре                   | Pin        | Function                                                                                                            |

|------------------|------------------------|------------|---------------------------------------------------------------------------------------------------------------------|

| DL3A_P<br>DL3A_N | Analog<br>CML<br>Input | J3<br>J2   | <i>Port A XAUI Differential Serial Data Input – lane 3</i><br>Equivalent to DL0A_P and DL0A_N for XAUI port lane 3. |

| DL3B_P<br>DL3B_N | Analog<br>CML<br>Input | N13<br>M13 | <i>Port B XAUI Differential Serial Data Input – lane 3</i><br>Equivalent to DL0B_N and DL0B_N for XAUI port lane 3. |

#### Table 3 XAUI Transmit High Speed Output Pin Descriptions

| Pin Name | Туре                 | Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Function                                                                                                                                                                                                                                                                                                                   |

|----------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SLOA_P   | Analog               | VL <i>C2</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Port A XAUI Differential Serial Data Output – lane 0                                                                                                                                                                                                                                                                       |

| SLOA_N   | SLOA_N CML<br>Output |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SL0P_A and SL0N_A are the 3.1875/3.125 Gbit/s<br>outputs for Port A XAUI port lane 0 when configured to<br>support 10GFC/10GE mode. SL0P_A and SL0N_A are<br>the 1.2 Gbit/s to 3.2 Gbit/s differential outputs for lane 0 of<br>port A serial transmit port when configured to support<br>Lane Based and SERDES operation. |

|          |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | These differential outputs are internally terminated with a $100\Omega$ differential resistor.                                                                                                                                                                                                                             |

|          |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | When Serial, Parallel Diagnostic or System Loopback mode is selected, these outputs are optionally driven high.                                                                                                                                                                                                            |

|          |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | These outputs are tri-stated when disabled through management register control.                                                                                                                                                                                                                                            |

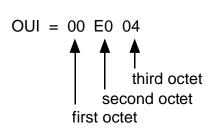

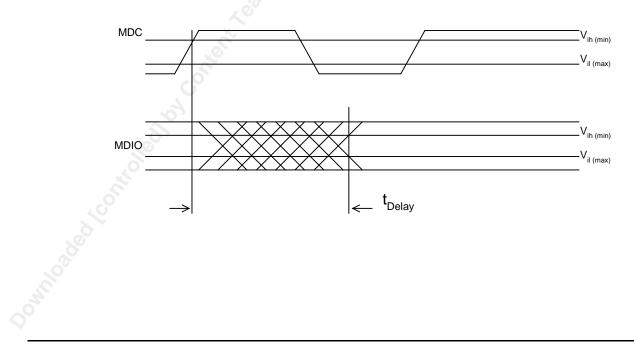

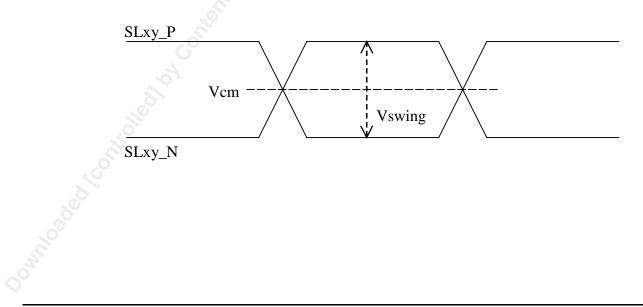

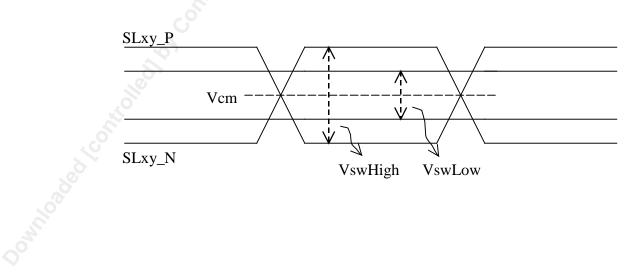

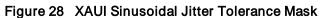

| SL0B_P   | Analog               | N7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Port B XAUI Differential Serial Data Output – lane 0                                                                                                                                                                                                                                                                       |