PM8363

# QuadPHY® 1GR

### 4 CHANNEL PHYSICAL LAYER TRANSCEIVER WITH GIGABIT ETHERNET PCS AND RGMII INTERFACE

# **Data Sheet**

Released Issue No. 4: December 2005

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2030571, Issue 4

# **Legal Information**

### Copyright

Copyright 2005 PMC-Sierra, Inc. All rights reserved.

The information in this document is proprietary and confidential to PMC-Sierra, Inc., and for its customers' internal use. In any event, no part of this document may be reproduced or redistributed in any form without the express written consent of PMC-Sierra, Inc.

PMC-2030571 (R4); Ref PMC-2021957 (P4)

### Disclaimer

None of the information contained in this document constitutes an express or implied warranty by PMC-Sierra, Inc. as to the sufficiency, fitness or suitability for a particular purpose of any such information or the fitness, or suitability for a particular purpose, merchantability, performance, compatibility with other parts or systems, of any of the products of PMC-Sierra, Inc., or any portion thereof, referred to in this document. PMC-Sierra, Inc. expressly disclaims all representations and warranties of any kind regarding the contents or use of the information, including, but not limited to, express and implied warranties of accuracy, completeness, merchantability, fitness for a particular use, or non-infringement.

In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or consequential damages, including, but not limited to, lost profits, lost business or lost data resulting from any use of or reliance upon the information, whether or not PMC-Sierra, Inc. has been advised of the possibility of such damage.

### Trademarks

For a complete list of PMC-Sierra's trademarks and registered trademarks, visit: <u>http://www.pmc-sierra.com/legal/</u>

### Patents

### Granted

The technology discussed in this document is protected by one or more of the following patent grants:

U.S. Patent No. -6,552,619

# **Revision History**

| Issue No. | Issue Date       | Details of Change                                                     |

|-----------|------------------|-----------------------------------------------------------------------|

| 4         | December<br>2005 | Updated ordering information including RoHS-compliant device details. |

| 3         | May 2004         | MDIO timing updated                                                   |

|           |                  | HSTL drive levels updated                                             |

|           |                  | VDDA current updated                                                  |

|           |                  | Power Requirements updated                                            |

|           |                  | Device latency updated                                                |

|           |                  | 933Mbit/s data rate support added                                     |

| 2         | April 2003       | Initial release to customers.                                         |

| 1         | April 2003       | Initial internal release.                                             |

### **Table of Contents**

| Leg | gal Information                                             | 2   |

|-----|-------------------------------------------------------------|-----|

|     | Copyright                                                   |     |

|     | Disclaimer                                                  | 2   |

|     | Trademarks                                                  | 2   |

|     | Patents                                                     | 2   |

| Re  | vision History                                              | 3   |

| Tab | ble of Contents                                             | 4   |

|     | t of Registers                                              |     |

|     | t of Figures                                                |     |

| Lis | t of Tables                                                 |     |

| 1   | Definitions                                                 | 11  |

| 2   | Features                                                    | 12  |

| 3   | References                                                  |     |

| 4   | Application Examples                                        | 14  |

|     | 4.1 Gigabit Ethernet Switch/Router Application              | 14  |

|     | 4.2 IEEE 802.3-2000 Gigabit Ethernet Transceiver            | 15  |

| 5   | Block Diagram                                               | 17  |

| 6   | Description                                                 | 19  |

|     | 6.1 Overview                                                | 19  |

| 7   | Pin Diagram                                                 |     |

| 8   | Pin Description                                             | 22  |

| 9   | Functional Description                                      |     |

|     | 9.1 Modes of Operation                                      |     |

|     | 9.2 Serial Channel Overview                                 |     |

|     | 9.3 JTAG Test Access Port                                   | 52  |

|     | 9.4 Management Interface                                    |     |

| 10  | Normal Mode Register Description                            | 62  |

|     | 10.1 IEEE Defined Registers (only applicable in RGMII mode) | 62  |

|     | 10.2 Non-IEEE Defined Registers                             |     |

| 11  | Test Features Description                                   | 97  |

|     | 11.1 Packet Generator and Packet Comparator                 |     |

|     | 11.2 JTAG Test Access Port                                  |     |

| 12  | Operation                                                   | 101 |

|     | 12.1   | SERDES or RTBI Configuration             | 101 |

|-----|--------|------------------------------------------|-----|

|     | 12.2   | GE PCS or RGMII Configuration            |     |

|     | 12.3   | Parallel Loopback                        |     |

|     | 12.4   | Power-up 102                             |     |

|     | 12.5   | Parallel Interface                       |     |

|     | 12.6   | High-Speed Serial Interface              | 103 |

|     | 12.7   | Clock Requirements                       |     |

|     | 12.8   | Hardware/Software Configuration Options  |     |

|     | 12.9   | Analog Considerations                    |     |

|     | 12.10  | ) JTAG Considerations                    |     |

| 13  | Func   | tional Timing                            | 105 |

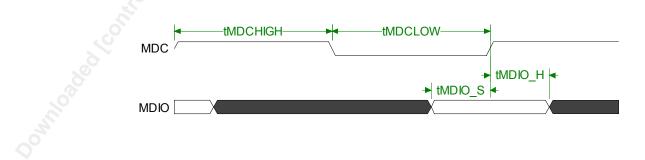

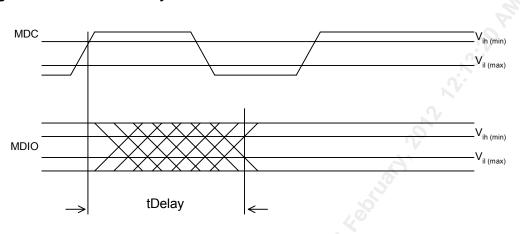

|     | 13.1   | MDC/MDIO Interface                       | 105 |

| 14  | Abso   | lute Maximum Ratings                     |     |

| 15  | Powe   | er Information                           |     |

|     | 15.1   | Power Requirements                       |     |

|     | 15.2   | Power Supply Decoupling                  |     |

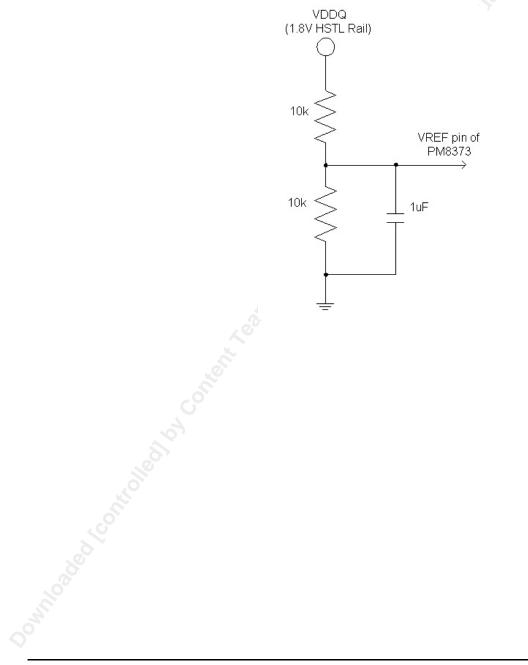

|     | 15.3   | VREF Decoupling                          | 111 |

| 16  | D.C.   | Characteristics                          | 112 |

| 17  | Interf | ace Timing Characteristics               | 116 |

|     | 17.1   | Reference Clock                          | 116 |

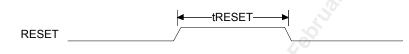

|     | 17.2   | Asynchronous Reset                       | 117 |

|     | 17.3   | MII Management Interface (MDC/MDIO)      | 117 |

|     | 17.4   | JTAG 118                                 |     |

|     | 17.5   | Transmit Timing                          | 121 |

|     | 17.6   | Receive Timing                           | 122 |

|     | 17.7   | Receive Latency                          |     |

|     | 17.8   | Transmit Latency                         | 125 |

|     | 17.9   | High-speed Serial Timing Characteristics | 125 |

| 18  | Therr  | mal Information                          | 128 |

| 19  | Mech   | nanical Information                      |     |

| 20  | Orde   | ring Information                         | 131 |

| Not | tes    |                                          | 132 |

### **List of Registers**

| Register 0x00: GMII Control                                         |                | 2 |

|---------------------------------------------------------------------|----------------|---|

| Register 0x01: GMII Status                                          |                |   |

| Register 0x02: GMII PHY Identifier 1                                | 68             | 8 |

| Register 0x03: GMII PHY Identifier 2                                | 7(             | 0 |

| Register 0x04: GMII Auto-Negotiation Advertisement                  | 7 <sup>.</sup> | 1 |

| Register 0x05: GMII Auto-Negotiation Link Partner Ability Base Page | 7:             | 3 |

| Register 0x06: GMII Auto-Negotiation Expansion                      | 7!             | 5 |

| Register 0x07: GMII Auto-Negotiation Next Page Transmit             |                | 6 |

| Register 0x08: GMII Auto-Negotiation Link Partner Next Page Ability | 78             | 8 |

| Registers 0x09 through 0x0E: Reserved                               | 80             | 0 |

| Register 0x0F: GMII Extended Status                                 | 8 <sup>.</sup> | 1 |

| Register 0x10: PMC Control 1                                        | 82             | 2 |

| Register 0x11: PMC Control 2                                        | 84             | 4 |

| Register 0x12 – 0x15: PMC Reserved                                  |                |   |

| Register 0x16: Loopback Control                                     |                | 7 |

| Register 0x17: Status                                               |                | 8 |

| Register 0x18: PMC Control 3                                        |                | 9 |

| Register 0x19: Auto-Negotiation Status 1                            | 9 <sup>.</sup> | 1 |

| Register 0x1A: Auto-Negotiation Status 2                            | 92             | 2 |

| Register 0x1B: Packet Generator/Checker Control/Status              | 9:             | 3 |

| Register 0x1C: Packet Generator Count Control                       | 9!             | 5 |

|                                                                     |                |   |

# **List of Figures**

|           | QuadPHY® 1GR in Switch/Router Applications                 |    |

|-----------|------------------------------------------------------------|----|

|           | IEEE 802.3-2000 Gigabit Ethernet Supported Functions       |    |

| Figure 3  | QuadPHY 1GR Block Diagram                                  |    |

| Figure 4  | QuadPHY 1GR Loopback Diagram                               |    |

| Figure 5  | QuadPHY 1GR Pin Diagram                                    | 21 |

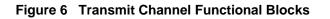

| Figure 6  | Transmit Channel Functional Blocks                         |    |

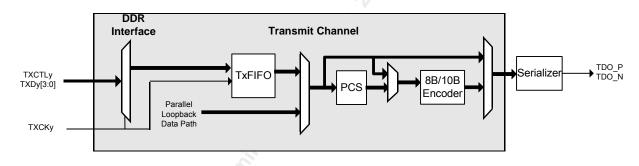

| Figure 7  | Center Aligned RGMII Transmit (Input) Functional Timing    |    |

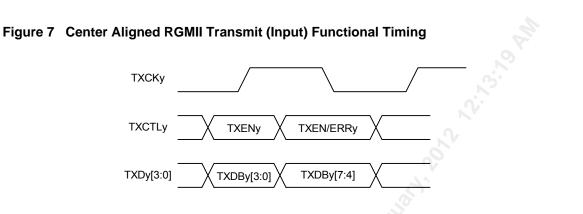

| -         | Center Aligned RTBI Transmit (Input) Functional Timing     |    |

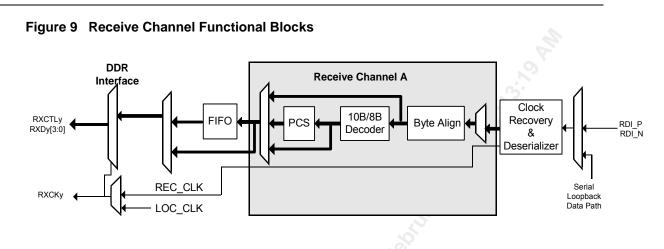

|           | Receive Channel Functional Blocks                          |    |

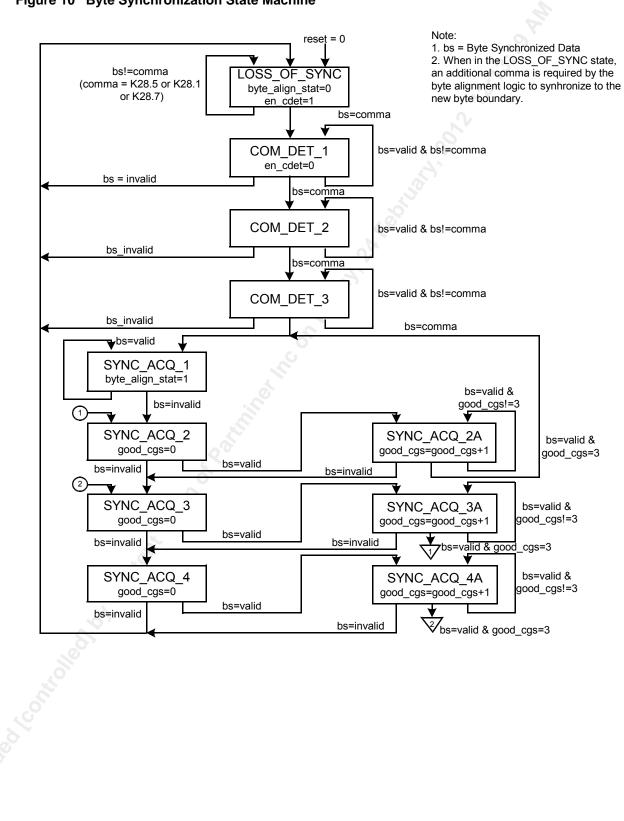

| Figure 10 | Byte Synchronization State Machine                         |    |

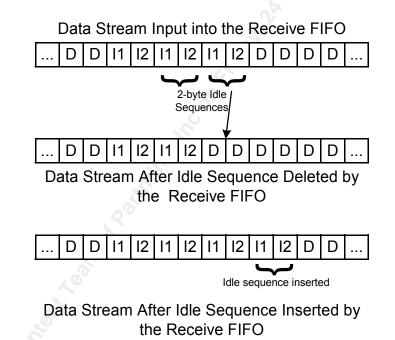

| Figure 11 | Insertion/Deletion of Idle Sequences by the Receive FIFO   |    |

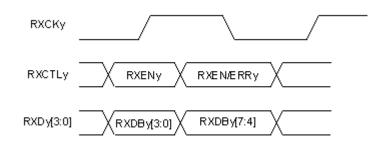

| Figure 12 | Center Aligned RGMII Receive (Output) Functional Timing    |    |

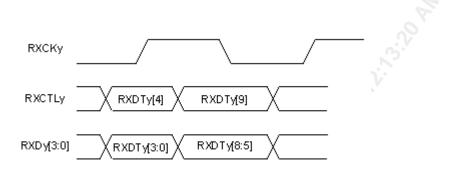

| Figure 13 | Center Aligned RTBI Receive (Output) Functional Timing     | 51 |

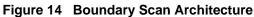

| Figure 14 | Boundary Scan Architecture                                 | 53 |

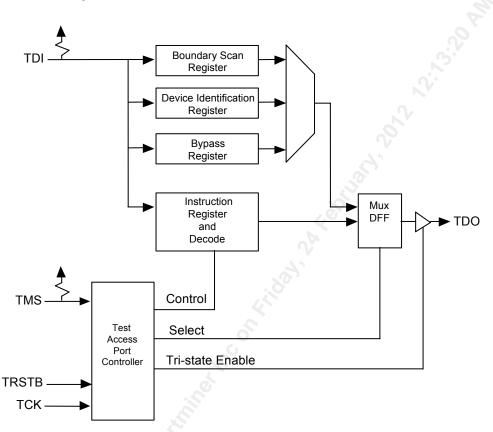

| Figure 15 | TAP Controller Finite State Machine                        |    |

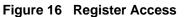

| Figure 16 | Register Access                                            |    |

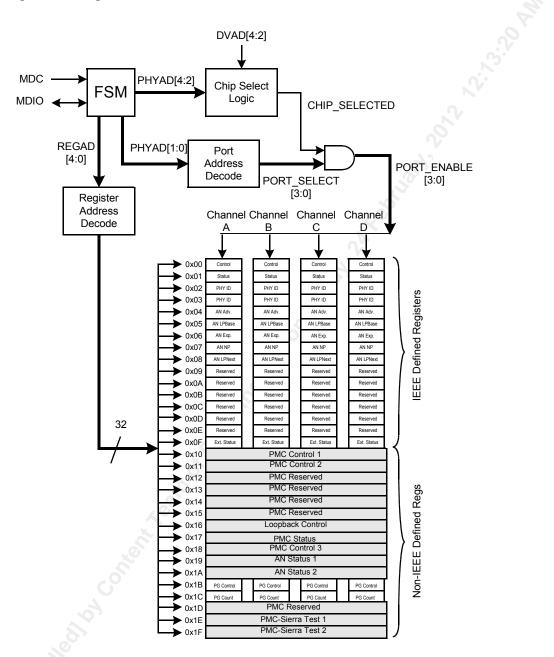

| Figure 17 | Behavior of MDIO During TA Field of a Read Transaction     | 60 |

| Figure 18 | Register Memory Map                                        | 61 |

|           | Serial Loopback Data Path with Packet Generator/Comparator | 00 |

|           | ed                                                         |    |

| U U       | Parallel Receive and Transmit Interface                    |    |

| Figure 21 |                                                            |    |

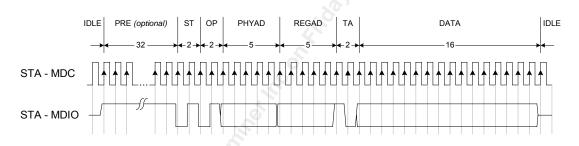

| -         | MDC/MDIO Write Cycle                                       |    |

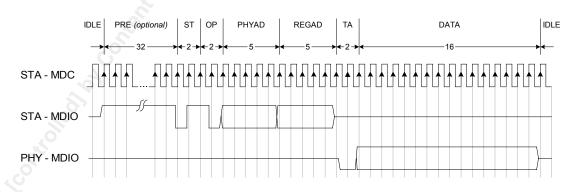

| •         | MDC/MDIO Read Cycle                                        |    |

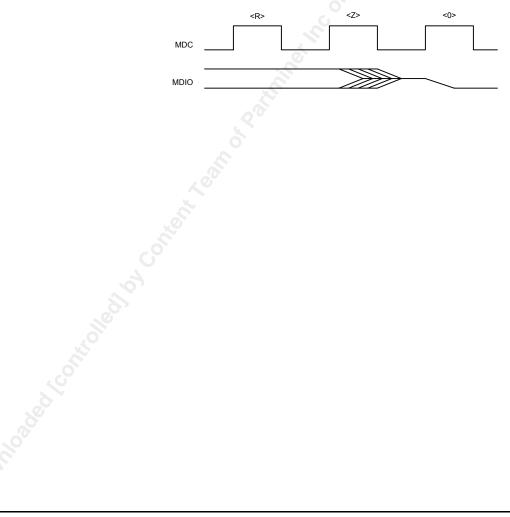

| -         | Behavior of MDIO During TA Field of a Read Transaction     |    |

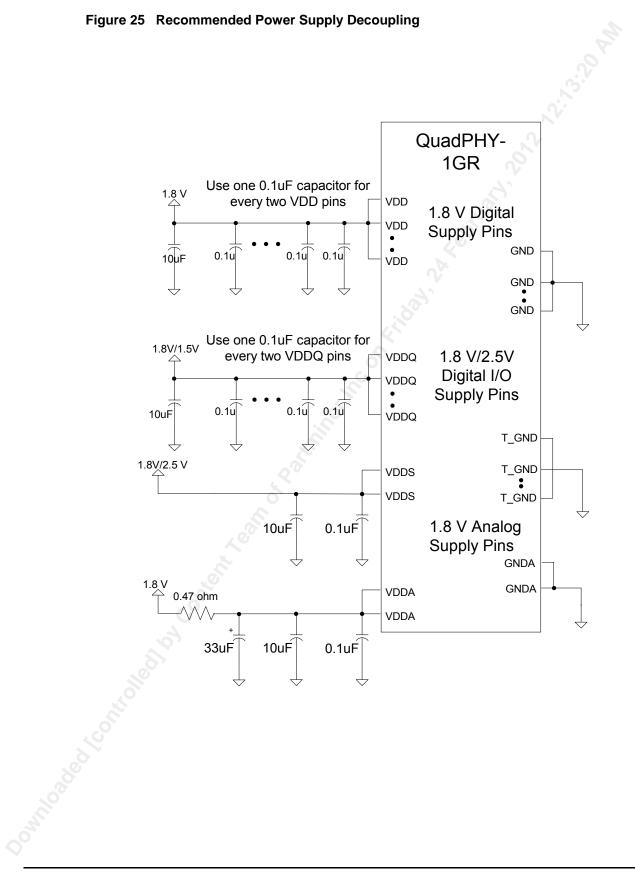

| -         | Recommended Power Supply Decoupling                        |    |

|           | VREF Filtering Circuit                                     |    |

|           | QuadPHY 1GR Reset Timing                                   |    |

| Figure 28 |                                                            |    |

| Figure 29 | -                                                          |    |

| Figure 30 | e e e e e e e e e e e e e e e e e e e                      |    |

| Figure 31 | Center Aligned DDR Transmit Timing                         |    |

| •         | Parallel Receive Timing Diagram                            |    |

| Figure 33 | Receive Latency                                            |    |

| Figure 35 933Mbit/s to 1.25 Gbit/s Serial I/O Block Diagram |     |

|-------------------------------------------------------------|-----|

|                                                             | 125 |

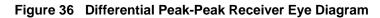

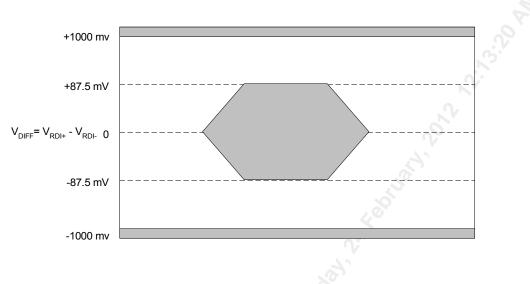

| Figure 36 Differential Peak-Peak Receiver Eye Diagram       | 126 |

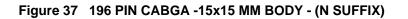

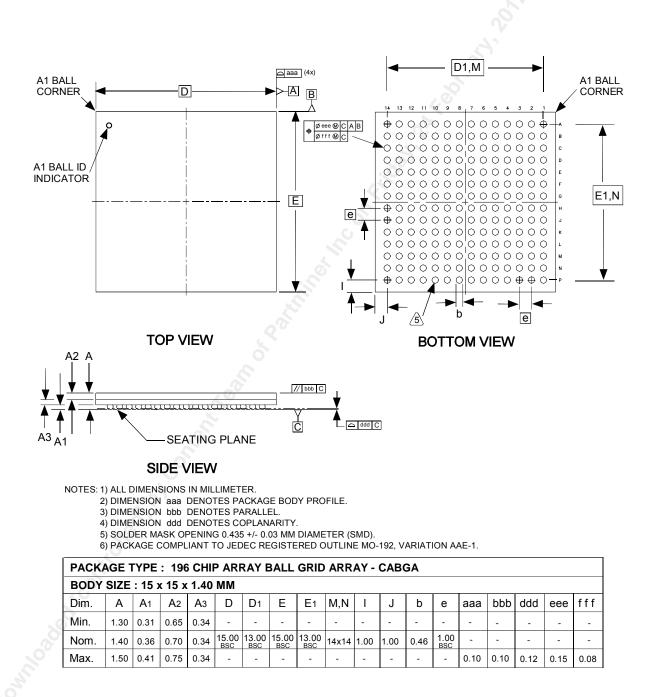

| Figure 37 196 PIN CABGA -15x15 MM BODY - (N SUFFIX)         | 130 |

|                                                             |     |

|                                                             |     |

|                                                             |     |

|                                                             |     |

|                                                             |     |

|                                                             |     |

|                                                             |     |

|                                                             |     |

|                                                             |     |

|                                                             |     |

|                                                             |     |

### **List of Tables**

| Table 1  | Definitions                                              |     |

|----------|----------------------------------------------------------|-----|

| Table 2  | Receive Path Pins                                        | 23  |

| Table 3  | Transmit Path Pins                                       | 26  |

| Table 4  | MDC/MDIO Pins                                            |     |

| Table 5  | Configuration/Status Pins                                | 31  |

| Table 6  | JTAG Pins                                                |     |

| Table 7  | Miscellaneous Pins                                       | 33  |

| Table 8  | Digital Power and Digital Ground Pins                    | 34  |

|          | Analog Power and Ground Pins                             |     |

| Table 10 | Valid K Bit Values                                       |     |

| Table 11 | Example REFCLK and PLL Clock Combinations                |     |

| Table 12 | Parallel Transmit Interface Summary for RGMII/RTBI       | 41  |

| Table 13 | Mapping of 10-bit or Byte transmit data                  | 41  |

| Table 14 | Parallel Receive Interface Summary for RGMII/RTBI        | 52  |

| Table 15 | Mapping of 10-bit or Byte receive data                   | 52  |

| Table 16 | Management Interface Frame Format                        | 59  |

| Table 17 | Instruction Register                                     | 99  |

| Table 18 | Identification Register                                  |     |

| Table 19 | Hardware/Software Configuration Options                  | 104 |

| Table 20 | Maximum Ratings                                          | 107 |

| Table 21 | Power Requirements                                       | 108 |

| Table 22 | Conditions For Power Requirements                        | 108 |

| Table 23 | D.C. Characteristics                                     | 113 |

| Table 24 | Reference Clock Timing                                   | 116 |

| Table 25 | QuadPHY 1GR Reset Timing                                 | 117 |

| Table 26 | MDIO Timing                                              | 117 |

| Table 27 | JTAG Port Interface                                      | 118 |

| Table 28 | Center Aligned DDR Transmit Timing                       |     |

| Table 29 | Receive Timing (Center Aligned) <sup>3</sup>             | 122 |

| Table 30 | Receive Latency Timing                                   |     |

| Table 31 | Transmit Latency Timing                                  | 125 |

| Table 32 | High-speed I/O Characteristics (V <sub>DD</sub> = 1.8 V) | 127 |

| Table 33 | Gigabit Ethernet Jitter Specifications <sup>2</sup>      | 127 |

|          | 2                                                |  |

|----------|--------------------------------------------------|--|

| Table 34 | Fibre Channel Jitter Specifications <sup>3</sup> |  |

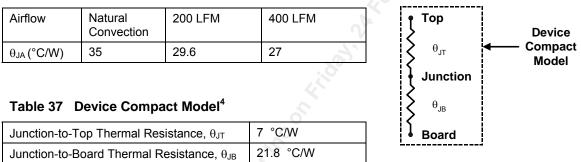

|          | Outside Plant Thermal Information                |  |

| Table 36 | Thermal Resistance vs. Air Flow <sup>3</sup>     |  |

|          | Device Compact Model <sup>4</sup>                |  |

| Table 38 | Outside Plant Thermal Information                |  |

| Table 39 | Device Compact Model <sup>3</sup>                |  |

|          | Heat Sink Requirements                           |  |

| Table 41 | Ordering Information                             |  |

|          |                                                  |  |

### 1 Definitions

The following table defines terms and abbreviations used in this document.

#### Table 1 Definitions

| Term     | Definition                                         |

|----------|----------------------------------------------------|

| ANSI     | American National Standards Institute              |

| ASIC     | Application Specific Integrated Circuit            |

| BIST     | Built-in Self Test                                 |

| CABGA    | Chip Array Ball Grid Array                         |

| CMOS     | Complementary Metal-oxide Silicon                  |

| COL      | Collision Detect.                                  |

| CRS      | Carrier Sense                                      |

| DDR      | Dual Data Rate or Double Data Rate                 |

| HSTL     | High Speed Transceiver Logic                       |

| FIFO     | First In, First Out                                |

| IEEE     | Institute of Electrical and Electronics Engineers  |

| IPG      | Interpacket Gap                                    |

| JTAG     | Joint Test Action Group                            |

| MDC/MDIO | Management Data Clock/Management Data Input/Output |

| PCS      | Physical Coding Sublayer                           |

| RGMII    | Reduced Gigabit Medium-Independent Interface       |

| RTBI     | Reduced Ten Bit Interface                          |

### 2 Features

#### General

- Four 933Mbit/s to 1.25 Gbit/s IEEE 802.3-2000 Gigabit Ethernet and Fibre Channel Physical Interfaces (RTBI serdes mode only) (FC-PI) System Compliant Transceivers.

- Integrated clock synthesis, clock recovery, serializer/deserializer, built-in self-test, 8B/10B codec and IEEE 802.3-2000 Gigabit Ethernet Physical Coding Sublayer (PCS) logic.

- Rate matching via IDLE character insertion and deletion capable of compensating up to ±200 ppm of clock difference between reference clock and incoming serial data stream.

- Pin programmable or software configurable operation using 2 pin IEEE 802.3 MDC/MDIO serial management interface.

- Ultra-low power operation using 0.18µ technology.

#### **Serial Interface**

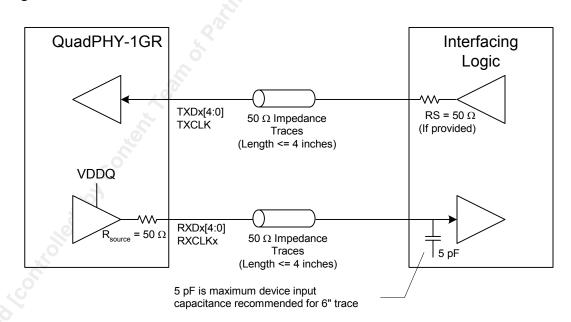

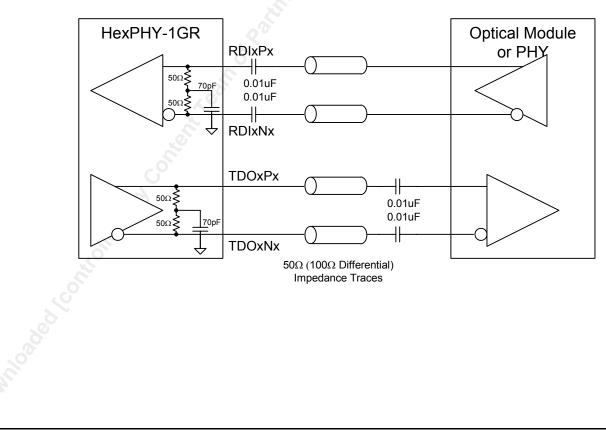

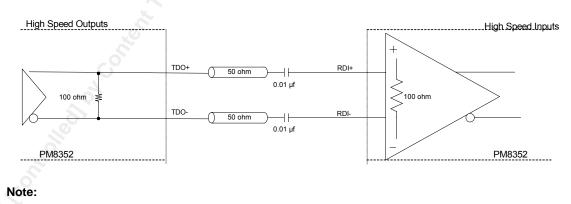

- High-speed outputs feature programmable output current to optimize drive distance and power directly drives 50  $\Omega$  (100  $\Omega$  differential) systems.

- Direct AC coupled interface to copper serial backplanes, optics and coaxial cable.

#### **Parallel Interface**

- DDR parallel interface with synchronous receive clock (clock forwarding).

- Local or Recovered Receive Clock Modes.

- Supports RGMII/RTBI (Reduced Ten-bit Interface) v2.0 standards.

- Receive channel output clocks eliminate the need for PLLs in interface ASICs.

- Supports 1.5V JEDEC HSTL class I and 1.8V Expanded HSTL class I for unterminated DDR interface.

- Supports 2.5V /1.8V LVCMOS for rest of digital interface.

#### Test Features

- IEEE 1149.1 JTAG Boundary Scan support.

- Built-in self-test (BIST) via internal packet generator/checker.

- Per-channel control of serial and parallel loopback.

- 8B/10B error counters.

#### Physical

Thermally enhanced 196-pin, 15mm x 15mm CABGA Package.

### 3 References

- 1. IEEE 802.3-2000 Gigabit Ethernet, 2000 Edition.

- 2. Methodologies for Jitter and Signal Quality Specification (MJSQ) Rev. 4.0.

- 3. Fibre Channel Physical Interfaces (FC-PI) Rev. 13.

- 4. IEEE 1149.1-2001 Standard Test Access Port and Boundary Scan Architecture, 23 July 2001.

- 5. Reduced Gigabit Media Independent Interface (RGMII), December 10, 2000, Revision 2.0.

- 6. HSTL 1.5V Output Buffer Supply Voltage Based Interface Standard for Digital Integrated Circuits, EIA/HESD8-6, August 1995.

- 7. Electronic Industries Association. *Methodology for the Thermal Measurement of Component Packages (Single Semiconductor Device)*: EIA/JESD51. December 1995.

- 8. Electronic Industries Alliance 1999. Integrated Circuit Thermal Test Method Environmental Conditions -Junction-to-Board: JESD51-8. October 1999.

- 9. Telcordia Technologies. Network Equipment-Building System (NEBS) Requirements: Physical Protection: Telcordia Technologies Generic Requirements GR-63-CORE. Issue 1. October 1995.

- 10. SEMI (Semiconductor Equipment and Materials International). SEMI G30-88 Test Method for Junction-to-Case Thermal Resistance Measurements of Ceramic Packages. 1988.

- 11. PMC-Sierra, Inc. *JTAG Test Features Description Applications Note*. PMC-2021518. Issue 1, November 2002.

### 4 Application Examples

The QuadPHY® 1GR has numerous applications in networking, storage and computing systems requiring high-speed serial I/O technology. Typical applications include backplane interconnect, Gigabit Ethernet line cards and Fiber Channel line cards.

- High-speed serial backplanes.

- IEEE 802.3-2000 Gigabit Ethernet dense line cards.

- ANSI X3T11 Fibre Channel dense line cards.

- Intra-system and inter-system interconnect.

- Chassis Extender.

### 4.1 Gigabit Ethernet Switch/Router Application

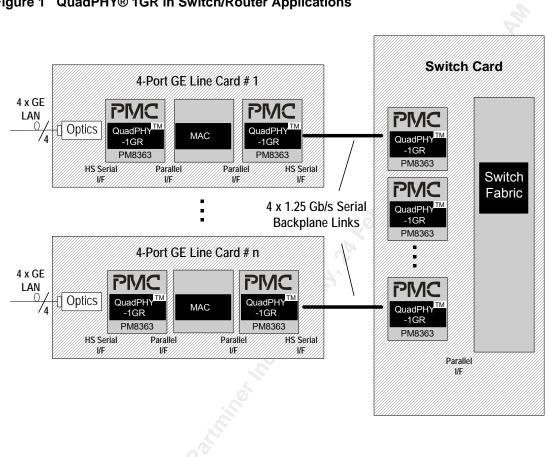

Figure 1 shows the QuadPHY 1GR in a Gigabit Ethernet Switch/Router Application. This application demonstrates the many uses of the QuadPHY 1GR. On the line cards, the QuadPHY 1GR functions as the Gigabit Ethernet Transceiver as well as the interface to the backplane. On the switch card, the QuadPHY 1GR provides a dense, high-speed interconnect to the line cards over a copper backplane.

#### Figure 1 QuadPHY® 1GR in Switch/Router Applications

#### IEEE 802.3-2000 Gigabit Ethernet Transceiver 4.2

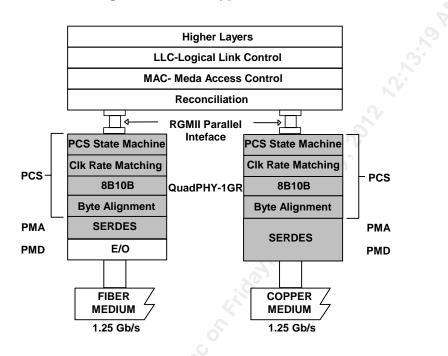

As a Gigabit Ethernet Transceiver, the QuadPHY 1GR integrates the PCS layer down to the PMA layer for fiber mediums, and from the PCS layer down to the PMD layer for copper mediums. The gray shaded cells in Figure 2 shows the supported functions of the device. The QuadPHY 1GR may be configured to enable or disable certain layers.

Figure 2 IEEE 802.3-2000 Gigabit Ethernet Supported Functions

### 5 Block Diagram

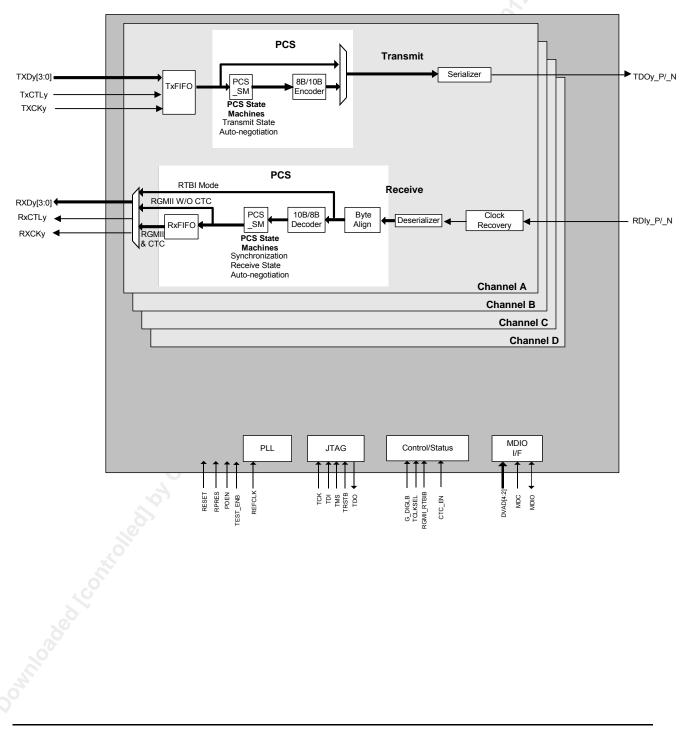

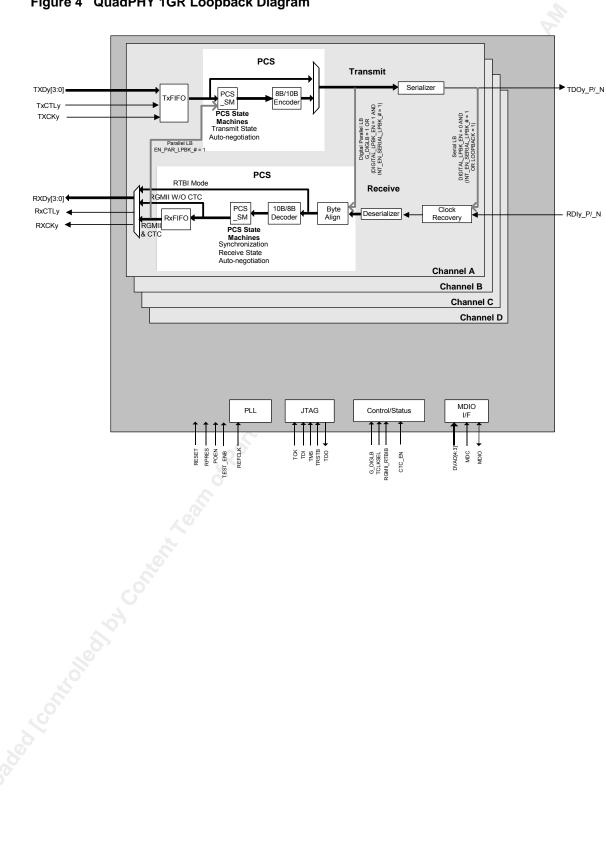

The block diagram of the QuadPHY 1GR is shown in Figure 3 and the Loopback Diagram is shown in Figure 4.

#### Figure 3 QuadPHY 1GR Block Diagram

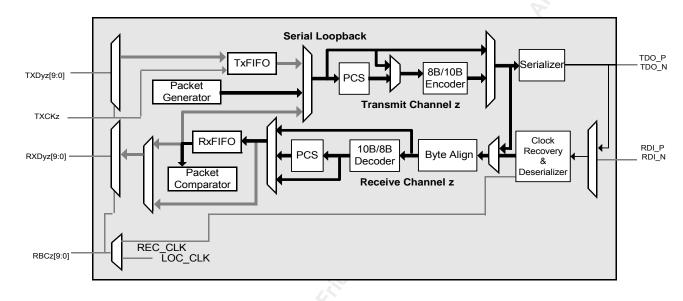

Figure 4 QuadPHY 1GR Loopback Diagram

### 6 **Description**

### 6.1 Overview

The PM8363 QuadPHY 1GR is a low power, four-channel transceiver suitable for applications such as high-speed serial backplanes and dense Gigabit Ethernet line cards.

### **RTBI Mode**

In the transmit direction, the PM8363 takes 10-bit data, serializes the data and transmits it differentially at 933Mbit/s to 1.25 Gbit/s. The PM8363 integrates an RTBI-compliant parallel interface, serializer, clock synthesis unit and differential transmitters.

In the receive direction, the PM8363 receives serial differential data, recovers the data and converts it back to 10-bit data. The PM8363 integrates differential receivers, clock recovery unit and an RTBI-compliant parallel interface. The received data can be output using the recovered clock only in RTBI mode.

The QuadPHY 1GR supports a Dual Data Rate (DDR) Parallel Interface with independent receive and transmit ports. The interface is RTBI compliant (as specified in the Reduced Gigabit Media Independent Interface Specification v2.0).

#### **RGMII Mode**

In the transmit direction, the PM8363 implements an RGMII interface which accepts RGMII formatted data, inputs it to the PCS Tx State Machine, performs 8B/10B encoding, serializes the data and transmits it differentially at 933Mbit/s to 1.25Gbit/s. The PM8363 integrates an RGMII compatible parallel interface, 8B/10B encoder, IEEE 802.3-2000 Gigabit Ethernet PCS logic, serializer, clock synthesis unit and differential transmitters.

In the receive direction, the PM8363 receives serial differential data, deserializes it, performs byte alignment, decodes the data, inputs it to the PCS Rx State Machine and outputs the data in RGMII format on the parallel interface. The PM8363 integrates differential receivers, clock recovery unit, IEEE 802.3-2000 Gigabit Ethernet PCS logic, 8B/10B decoder, receive FIFOs and an RGMII/RTBI compatible parallel interface. The received data can be output using the recovered clock or local clock in RGMII mode.

In addition to these fundamental SERDES functions, the PM8363 provides rate compensation. A system requires rate compensation if the transmitting device and receiving device are operating from different clock sources (i.e. are asynchronous). For example, if four asynchronous 1.25 Gbit/s links from four line cards are transmitting over a backplane to one receiving device, the receiving device must provide rate compensation to achieve a common local clock. The receive logic compensates for these clock differences by inserting or deleting special 8B/10B IDLE characters. Rate compensation can be enabled or disabled in RGMII mode, but cannot be enabled in RTBI mode.

The QuadPHY 1GR supports a Dual Data Rate (DDR) Parallel Interface with independent receive and transmit ports. The interface is RGMII compatible (as specified in the Reduced Gigabit Media Independent Interface Specification v2.0). The receive output RGMII interface can be synchronized to either the received data's recovered clock or the QuadPHY 1GR's local reference clock.

#### General

The PM8363 has four transmit and four receive channels (A to D). Figure 3 shows a detailed block diagram for the functionality of channel A. The block diagrams of channels B, C and D are identical to channel A.

The QuadPHY 1GR supports IEEE 802.3-2000 Gigabit Ethernet and Fibre Channel Physical Interfaces (FC-PI) Rev. 13. The high-speed outputs feature programmable output drive that enables directly driving 50  $\Omega$  (100  $\Omega$  differential) systems. This allows direct interface to optical modules, coax, or serial backplanes.

The selection of interface modes, as well as operating features such as the internal 8B/10B encoding/decoder, full duplex PCS, frequency compensation, and parallel loopback, can be done via the 2-pin serial MDC/MDIO management interface, or through external pins for systems that do not support MDC/MDIO. The QuadPHY 1GR supports parallel loopback mode for testing. Support for built-in self test (BIST) via an internal packet generator/checker is also provided on a per transceiver basis.

The part is produced in 0.18  $\mu$ M. The HSTL Class I I/O is capable of operating at 1.5V or 1.8V. The CMOS I/O compatible with 2.5V or 1.8V LVCMOS I/Os. IEEE 1149.1 JTAG is fully supported and the 196-pin CABGA package has a small 15x15 mm footprint.

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2030571, Issue 4

PMC-SIERRA

The QuadPHY 1GR is packaged in a 196-ball Chip Array Ball Grid Array (CABGA) package. Dimensions are 15 mm by 15 mm. Figure 5 shows the QuadPHY 1GR.pin diagram.

|   |         |         |         |         |         | Тор        | Viev    | /       |        |         |          |        |        |      |   |

|---|---------|---------|---------|---------|---------|------------|---------|---------|--------|---------|----------|--------|--------|------|---|

|   | 1       | 2       | 3       | 4       | 5       | 6          | 7       | 8       | 9      | 10      | -11      | 12     | 13     | 14   |   |

| А | RXDB[0] | NC      | NC      | NC      | RXCKA   | RXDA[0]    | TXCKA   | TXDA[0] | NC     | TEST[4] | VDDA     | TDOD_N | TDOD_P | VSS  | А |

| в | RXDB[1] | VSS     | VDDQ    | NC      | VSS     | VDDQ       | TXDA[1] | VSS     | VDDQ   | TEST[5] | VDDA     | NC     | NC     | VSS  | в |

| С | RXCKB   | RXDB[2] | NC      | RXCTLA  | RXDA[3] | RXDA[1]    | TXDA[2] | TXDA[3] | NC     | NC      | VDDA     | TDOC_N | TDOC_P | VSS  | с |

| D | RXDB[3] | RXCTLB  | NC      | VSS     | VDDQ    | RXDA[2]    | VSS     | VDDQ    | TXCTLA | NC      | VDDA     | TDOB_N | TDOB_P | VSS  | D |

| Е | ТХСКВ   | TXDB[0] | TXDB[1] | TXDB[2] | G_DIGLB | RGMI_RTBIB | NC      | TCLKSEL | POEN   | RESET   | VDDA     | VDDA   | VSS    | VSS  | E |

| F | MDC     | MDIO    | TXDB[3] | TXCTLB  | NC      | VSS        | VSS     | VSS     | VSS    | VDDI    | VDDA     | TDOA_N | TDOA_P | VSS  | F |

| G | VDDS    | VREF    | тск     | TDI     | TRSTB   | VSS        | VSS     | VSS     | VSS    | VDDI    | VDDI     | NC     | NC     | VSSA | G |

| н | REFCLK  | VSS     | TMS     | TDO     | CTC_EN  | VSS        | VSS     | VSS     | VSS    | VDDI    | VDDI     | NC     | NC     | VSSA | н |

| J | VSS     | VDDS    | TXDC[3] | TXCTLC  | PRES    | VSS        | VSS     | VSS     | VSS    | VDDI    | VDDA     | RDID_N | RDID_P | VSS  | L |

| к | тхскс   | TXDC[0] | TXDC[1] | TXDC[2] | DVAD0   | DVAD1      | DVAD2   | DVAD3   | DVAD4  | NC      | VDDA     | VDDA   | VSS    | VSS  | к |

| L | RXDC[3] | RXCTLC  | NC      | VSS     | VDDQ    | RXDD[2]    | VSS     | VDDQ    | TXCTLD | TEST[3] | VDDA     | RDIC_N | RDIC_P | VSS  | L |

| м | RXCKC   | RXDC[2] | NC      | RXCTLD  | RXDD[3] | RXDD[1]    | TXDD[2] | TXDD[3] | NC     | TEST[2] | VDDA     | RDIB_N | RDIB_P | VSS  | м |

| N | RXDC[1] | VSS     | VDDQ    | NC      | VSS     | VDDQ       | TXDD[1] | VSS     | VDDQ   | TEST[1] | VDDA     | NC     | NC     | VSS  | N |

| Ρ | RXDC[0] | NC      | NC      | NC      | RXCKD   | RXDD[0]    | TXCKD   | TXDD[0] | NC     | TEST[0] | TEST_ENB | RDIA_N | RDIA_P | VSS  | Р |

|   | 1       | 2       | 3       | 4       | 5       | 6          | 7       | 8       | 9      | 10      | 11       | 12     | 13     | 14   |   |

|   | 1       |         |         |         |         |            |         |         |        |         |          |        |        |      |   |

|   |         |         |         |         |         |            |         |         |        |         |          |        |        |      |   |

|   |         |         |         |         |         |            |         |         |        |         |          |        |        |      |   |

|   |         |         |         |         |         |            |         |         |        |         |          |        |        |      |   |

|   |         |         |         |         |         |            |         |         |        |         |          |        |        |      |   |

|   |         |         |         |         |         |            |         |         |        |         |          |        |        |      |   |

#### Figure 5 QuadPHY 1GR Pin Diagram

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2030571, Issue 4

# 8 Pin Description

The following tables describe all pins of the QuadPHY 1GR.

| Table 2 | Receive | Path Pins |  |

|---------|---------|-----------|--|

|---------|---------|-----------|--|

| Pin Name                   | Туре                                | Pin<br>No.           | Function                                                                                                                                                                                                                                                                        |

|----------------------------|-------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDIA_P<br>RDIA_N<br>RDIB_P | Input<br>High-speed<br>Differential | P13<br>P12<br>M13    | Differential, high-speed serial <b>Receive Data Input pins</b> . The data must be 8B/10B line coded and operate in the range from 933Mbit/s and 1.25 Gbit/s.                                                                                                                    |

| RDIB_N<br>RDIC P           |                                     | M12<br>L13           | The differential inputs are internally terminated with 100 $\Omega$ differential terminations.                                                                                                                                                                                  |

| RDIC_N<br>RDID_P<br>RDID_N |                                     | L12<br>J13<br>J12    | These Receive channels are ignored when Serial Loopback<br>is enabled using the INT_EN_SERIAL_LPBK [D:A] bits in<br>Loopback Control Register                                                                                                                                   |

| —                          |                                     |                      | These inputs are enabled by default.                                                                                                                                                                                                                                            |

|                            |                                     |                      | If a channel is enabled, active data must be provided to it. D<br>not use pull-up/pull-down resistors on the high-speed<br>differential inputs.                                                                                                                                 |

|                            |                                     |                      | These inputs may be left unconnected when this channel is not used.                                                                                                                                                                                                             |

| RXCKA                      | Output<br>HSTL                      | A5                   | The <b>Receive Reference Clock Channel A</b> is a continuous receive reference clock that operates between 93.3Mhz and 125Mhz. Depending on the mode of operation, the receive clock may be recovered from the high speed received data derived from the local reference clock. |

|                            |                                     | 2                    | The rising edge of RXCKA is used to sample the least significant nibble of data on the RXDA[3:0] and the RXCTLA pins. The falling edge of RXCKA is used to sample the mos significant nibble of data on the RXDA[3:0] and the RXCTLA pins.                                      |

|                            |                                     | 2<br>P<br>P          | The received data can be output using recovered clock or<br>local clock in RGMII mode, and recovered clock only in RTE<br>mode.                                                                                                                                                 |

| RXDA[3]<br>RXDA[2]         | Output<br>HSTL                      | C5<br>D6<br>C6<br>A6 | The <b>Receive Data Channel A</b> is generated from the RDIA_P, RDIA_N inputs.                                                                                                                                                                                                  |

| RXDA[1]<br>RXDA[0]         |                                     |                      | When RGMII mode is selected, RGMII Data bits 3:0 are updated using the rising edge of RXCKA and RGMII Data b 7:4 are updated on the falling edge of RXCKA.                                                                                                                      |

|                            |                                     |                      | When RTBI mode is selected, RTBI Data bits 3:0 are updat<br>using the rising edge of RXCKA and RTBI Data bits 8:5 are<br>updated on the falling edge of RXCKA.                                                                                                                  |

|                            |                                     |                      | Please refer to Figure 17 and Figure 18 for details on functional timing between clock and data.                                                                                                                                                                                |

|                            |                                     |                      | RXDA[0] represents the first bit of the word received on the<br>differential pairs RDIA_P, RDIA_N.                                                                                                                                                                              |

| Pin Name           | Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Pin<br>No. | Function                                                                                                                                                                                                                                                                           |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXCTLA             | RXCTLA Output C4<br>HSTL C4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | C4         | The <b>Receive Control Channel A</b> pin outputs either a control in RGMII mode or a data bit in RTBI mode.                                                                                                                                                                        |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | When RGMII mode is selected, RXCTLA outputs RXDV on the rising edge of RXCKA and a derivative (XOR) of RXDV and RXERR on the falling edge of RXCKA.                                                                                                                                |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | When RTBI mode is selected, RXCTLA outputs data bit 4 on the rising edge of RXCKA and data bit 9 on the falling edge of RXCKA.                                                                                                                                                     |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | Please refer to Figure 17 and Figure 18 for details on functional timing between clock and data.                                                                                                                                                                                   |

| RXCKB              | RXCKB Output<br>HSTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | C1         | The <b>Receive Reference Clock Channel B</b> is a continuous receive reference clock that operates between 93.3Mhz and 125Mhz. Depending on the mode of operation, the receive clock may be recovered from the high speed received data or derived from the local reference clock. |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | The rising edge of RXCKB is used to sample the least significant nibble of data on the RXDB[3:0] and the RXCTLB pins. The falling edge of RXCKB is used to sample the most significant nibble of data on the RXDB[3:0] and the RXCTLB pins.                                        |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | The received data can be output using recovered clock or local clock in RGMII mode, and recovered clock only in RTBI mode.                                                                                                                                                         |

| RXDB[3]<br>RXDB[2] | Output<br>HSTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | D1<br>C2   | The <b>Receive Data Channel B</b> is generated from the RDIB_P, RDIB_N inputs.                                                                                                                                                                                                     |

| RXDB[1]<br>RXDB[0] |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | B1<br>A1   | When RGMII mode is selected, RGMII Data bits 3:0 are<br>updated using the rising edge of RXCKB and RGMII Data bits<br>7:4 are updated on the falling edge of RXCKB.                                                                                                                |

|                    | Support of the second s | 5          | When RTBI mode is selected, RTBI Data bits 3:0 are updated using the rising edge of RXCKB and RTBI Data bits 8:5 are updated on the falling edge of RXCKB.                                                                                                                         |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | Please refer to Figure 17 and Figure 18 for details on functional timing between clock and data. RXDB[0] represents the first bit of the word received on the differential pairs RDIB_P, RDIB_N.                                                                                   |

| RXCTLB             | Output<br>HSTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | D2         | The <b>Receive Control Channel B</b> pin outputs either a control in RGMII mode or a data bit in RTBI mode.                                                                                                                                                                        |

| 1910               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | When RGMII mode is selected, RXCTLB outputs RXDV on the rising edge of RXCKB and a derivative (XOR) of RXDV and RXERR on the falling edge of RXCKB.                                                                                                                                |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | When RTBI mode is selected, RXCTLB outputs data bit 4 on the rising edge of RXCKB and data bit 9 on the falling edge of RXCKB.                                                                                                                                                     |

| 02                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | Please refer to Figure 17 and Figure 18 for details on functional timing between clock and data.                                                                                                                                                                                   |

| Pin Name           | Туре                                     | Pin<br>No.                                                                                                                                                                                                                                                                         | Function                                                                                                                                                                                                                                                                           |

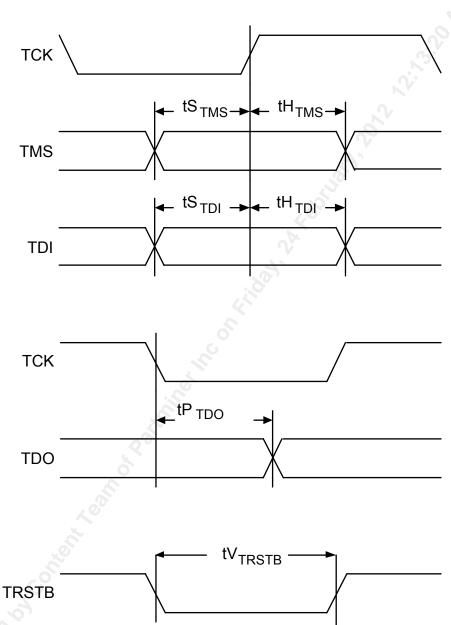

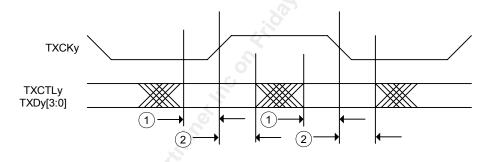

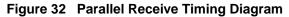

|--------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|