## **PM5332**

## SPECTRA™ 1x2488

# SONET/SDH Payload Extractor/Aligner For 2488 Mbit/s

**Data Sheet**

Released

Issue No. 4: January 2006

#### **Legal Information**

#### Copyright

Copyright 2006 PMC-Sierra, Inc. All rights reserved.

The information in this document is proprietary and confidential to PMC-Sierra, Inc., and for its customers' internal use. In any event, no part of this document may be reproduced or redistributed in any form without the express written consent of PMC-Sierra, Inc.

PMC-2012682 (R4)

#### **Disclaimer**

None of the information contained in this document constitutes an express or implied warranty by PMC-Sierra, Inc. as to the sufficiency, fitness or suitability for a particular purpose of any such information or the fitness, or suitability for a particular purpose, merchantability, performance, compatibility with other parts or systems, of any of the products of PMC-Sierra, Inc., or any portion thereof, referred to in this document. PMC-Sierra, Inc. expressly disclaims all representations and warranties of any kind regarding the contents or use of the information, including, but not limited to, express and implied warranties of accuracy, completeness, merchantability, fitness for a particular use, or non-infringement.

In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or consequential damages, including, but not limited to, lost profits, lost business or lost data resulting from any use of or reliance upon the information, whether or not PMC-Sierra, Inc. has been advised of the possibility of such damage.

#### **Trademarks**

For a complete list of PMC-Sierra's trademarks, see our web site at <a href="http://www.pmc-sierra.com/legal/">http://www.pmc-sierra.com/legal/</a>.

Other product and company names mentioned herein may be the trademarks of their respective owners.

#### **Patents**

The technology discussed in this document is protected by one or more of the following patent grants:

U.S. Patent No. 5,606,563.

Canadian Patent No. 2,159,763.

Other relevant patent grants and patent applications may also exist.

## **Contacting PMC-Sierra**

PMC-Sierra 100-2700 Production Way Burnaby, BC Canada V5A 4X1

Tel: +1 (604) 415-6000 Fax: +1 (604) 415-6200

Document Information: <a href="mailto:document@pmc-sierra.com">document@pmc-sierra.com</a>

Corporate Information: <a href="mailto:info@pmc-sierra.com">info@pmc-sierra.com</a>

Technical Support: <a href="mailto:apps@pmc-sierra.com">apps@pmc-sierra.com</a>

Web Site: <a href="http://www.pmc-sierra.com">http://www.pmc-sierra.com</a>

## **Revision History**

| Issue<br>No. | Issue Date   | Details of Change                                                                                                                                                                                                           |

|--------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4            | January 2006 | o Updated ordering information including RoHS-compliant device details.                                                                                                                                                     |

| 3            | March 2003   | o Lead Temperature incorrectly specified – Updated lead temperature from +230°C to +225°C                                                                                                                                   |

|              |              | o Updated patent information                                                                                                                                                                                                |

|              |              | o 4x622 mode using 155 MHz refclk. Added IREF_CTRL[1:0] register bit description                                                                                                                                            |

|              |              | o OC-48 CSU (Div1 vs. Div8). Added notes to TX2488 ABC Control register 1021H                                                                                                                                               |

|              |              | o TPOH Port Data Insertion. Added note to Operation: Path Overhead Bytes section 14.1.                                                                                                                                      |

|              |              | o Pin names differ between Pin Diagram and Pin Description. Updated pin descriptions for VDDI_JAT[3:0] and LC_AVDL.                                                                                                         |

|              |              | o LOS interrupt not being generated during state change of LOSV = 1 to 0. Updated LOSI (LAS4x622) register bit description.                                                                                                 |

|              |              | o SELF_NARROWBANDING MODE for CSUR PM70_00_04. Updated Quad STS-12/STM-4 Mode Operation section.                                                                                                                            |

|              |              | o Added optical jitter characterization results to section 20.2 and 20.3.                                                                                                                                                   |

|              |              | o TAPI path alarms persist when disabled causing PAIS in transmit path. Added section 14.12 Disabling Transmit Add Bus Pointer Interpreter.                                                                                 |

|              |              | o Minimum reset input pulse width (tV <sub>RSTB</sub> ) changed from 100ns to 2ms to account for analog block reset time.                                                                                                   |

|              |              | o Added configuration of REF77_P/N for 155.52MHz clock power up sequence to Quad STS-12/STM-4 Mode Operation section                                                                                                        |

|              |              | o Updated Absolute Maximum Ratings section                                                                                                                                                                                  |

|              |              | o SVCA: Unexpected indirect register behavior with concat. payloads. Updated indirect register 02H: TSVCA & RSVCA Diagnostic/Configuration registers descriptions and PJPMON[12:0]/ NJPMON[12:0] register bit descriptions. |

|              |              | o Fixed PREP#10035, 10036 - ALLPAISC generation error in last sts3c for RHPP and RHPP-R. Added section 14.13 Invalid Concatenation Pointer Processing Disable Bit.                                                          |

|              | 70           | o Updated OC-12 Line Interface Timing min REF77 Hi/Low pulse widths.                                                                                                                                                        |

|              |              | o Top level RTL bug in parallel diagnostic loopback on los_or_sd_defect.  Added notes to Loop Back Operation section.                                                                                                       |

|              |              | o 4x622 SDI_MASK prevents LOS detection. Updated SDI_MASK register description in 0036H 0436H 0836H and 0C36H.                                                                                                              |

| 79.00        |              | o 4x622 AC coupled LOS prevents RCLK from locking to reference. Updated Operations section with workarounds.                                                                                                                |

| .00          |              | o LAS4x622 DOOLI does not assert at +/-999 ppm with default CLK_CNT_MAX. Updated DOOLI and DOOLV register bit descriptions.                                                                                                 |

| 0            |              | o Changed register 001CH: SPECTRA 1X2488 Miscellaneous Configuration #1 to SPECTRA 1X2488 DOOL, LOS and SD Defect Enable                                                                                                    |

|              |              | o Changed register 001DH: SPECTRA 1X2488 Miscellaneous Configuration #1 to SPECTRA 1X2488 Miscellaneous Configuration #1                                                                                                    |

|              |              | o Modified VDDI_JAT[3:0] pin description.                                                                                                                                                                                   |

|              |              | o Updated Pin Description Note#2 – 2mA, 4mA and 10mA drive capability                                                                                                                                                       |

| Issue | Issue Date | Details of Change                                                                                                                                                          |

|-------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.   | issue Date | Details of Gridinge                                                                                                                                                        |

|       |            | o Added note to REF77 pin description.                                                                                                                                     |

|       |            | o Thermal Information Tj specified as 105C for both Central Office and Outside Plant                                                                                       |

|       |            | o Updated document to new template.                                                                                                                                        |

|       |            | o ILLPTR may be asserted on legal justification requests                                                                                                                   |

|       |            | o Register 0022H: Rx2488 Analog CRU Control – bit 15 and 13 reserved bits have default value of 1 instead of 0.                                                            |

|       |            | o Disagreement between H1H2 value and J1-byte location at SVCA output – Ensure payload pointer is recalculated when payload is configured.                                 |

|       |            | o Updated ILLPTR and JUST3DIS register descriptions.                                                                                                                       |

|       |            | o Updated Power Requirements section                                                                                                                                       |

|       |            | o Updated Thermal Information section                                                                                                                                      |

|       |            | o Clarification on FOOF bit description.                                                                                                                                   |

|       |            | o Analog power pin names require function suffix. Added power supply filtering tables.                                                                                     |

|       |            | <ul> <li>Analog power pin names require function suffix. Updated analog power<br/>filtering figure and added power pin description table.</li> </ul>                       |

|       |            | <ul> <li>Incorrect bit description for CSUR_LDBV in Register 0033H. Corrected bit<br/>inversion for CSUR_LBDV.</li> </ul>                                                  |

|       |            | o Incorrect bit description for ROOL-I bit in register 1020H. Updated reference to CSU_RESET in register 1021H.                                                            |

|       |            | o Rx2488 Analog PRBS Control register 0024H has no bit description. Label register as Rx2488 Reserved.                                                                     |

|       |            | <ul> <li>Incorrect bit description Indirect Register 02H: RSVCA<br/>Diagnostic/Configuration. Corrected PTRDD[1:0] bits for both RSVCA and<br/>TSVCA registers.</li> </ul> |

|       |            | o Set TDCLKOEN to high for 1x2488 mode to work. Updated SERDES1x2488 Mode Operation section.                                                                               |

|       |            | o DOOL_HSTR_SEL[1:0] description needs correction. Updated register bit description.                                                                                       |

|       | 2          | o Treatment of JTAG TRSTB pin is misleading. Modified pin description to be less restrictive.                                                                              |

|       | 700        | o OC-48 CRU Reset Time Documentation. Added note minimum 100us cru reset period.                                                                                           |

|       |            | o Corrected Register 0039H title. Removed PRBS from title.                                                                                                                 |

|       | 70.        | o AU-4 to 3x AU-3 Translation configuration errors. Corrected wording.                                                                                                     |

|       | S          | o TOFP[4:1] pin description. Corrected wording.                                                                                                                            |

|       | 3          | o ROHFP[4:1] pin description. Corrected wording.                                                                                                                           |

| 3     |            | o Updated Reliability Section                                                                                                                                              |

| 2     | July 2002  | o Updated the top-level registers: 0000H-0006H, 000FH, 001AH-001EH.                                                                                                        |

| 0     |            | o Added RCS2488 registers.                                                                                                                                                 |

| 5     |            | o Added TCP2488 registers.                                                                                                                                                 |

|       |            | o Added LAS4x622 registers.                                                                                                                                                |

|       |            | o Added JAT622 registers.                                                                                                                                                  |

|       |            | o Deleted pins OOF1-4, PRGMRCLK, TXD_P/TXD_N, RXD_P/RXD_N, SD.                                                                                                             |

|       |            | o Changed channel 1 of quad STM-4 to dual mode. Channel 1 is either STM-                                                                                                   |

| Issue<br>No. | Issue Date   | Details of Change                                                                                             |

|--------------|--------------|---------------------------------------------------------------------------------------------------------------|

|              |              | 16 or STM-4.                                                                                                  |

|              |              | o Pins RCLK1-4 could be gated if configured and RCLK1-2 could be selected from 4 internal RCLK if configured. |

|              |              | o Added SD/LOS/DOOLEN to SALM, AIS_L, and RDI_L generation enable register description.                       |

|              |              | o Updated Test registers.                                                                                     |

|              |              | o Updated Block Diagram, Loop Back Diagram.                                                                   |

|              |              | o Updated Operation Loop Back, SERDES sections.                                                               |

|              |              | o Deleted functional timing for digital line interface.                                                       |

| 1            | January 2002 | Data Sheet created.                                                                                           |

## **Table of Contents**

| Le  | gal Info | ormation                                                                    | 2     |

|-----|----------|-----------------------------------------------------------------------------|-------|

|     | Сору     | right                                                                       | 2     |

|     | Discl    | aimer                                                                       | 2     |

|     |          | emarks                                                                      |       |

|     | Pate     | nts                                                                         | 2     |

| Со  | ntactir  | ng PMC-Sierra                                                               | 3     |

| Re  | vision   | History                                                                     | 4     |

|     |          | Contents                                                                    |       |

| Lis | t of Re  | egisters                                                                    | 11    |

|     |          | gures                                                                       |       |

|     |          | bles                                                                        |       |

| 1   | Defin    | itions                                                                      | 33    |

| 2   | Feat     | ures                                                                        | 34    |

|     | 2.1      | General                                                                     | 34    |

|     | 2.2      | SONET Section and Line / SDH Regenerator and Multiplexer Section            | 35    |

|     | 2.3      | SONET Path / SDH High Order Path                                            | 36    |

|     | 2.4      | System Side Interfaces                                                      | 36    |

| 3   | Appli    | cations                                                                     | 38    |

| 4   | Refe     | rences                                                                      | 39    |

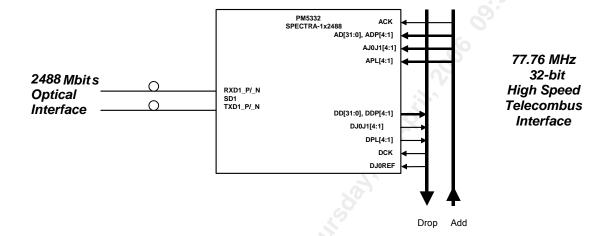

| 5   | Appli    | cation Examples                                                             | 41    |

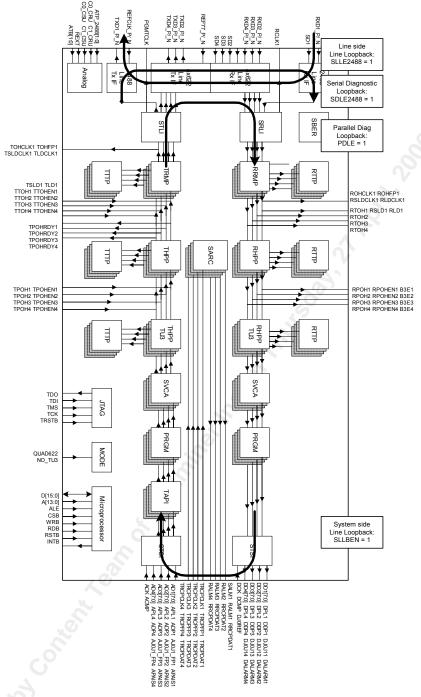

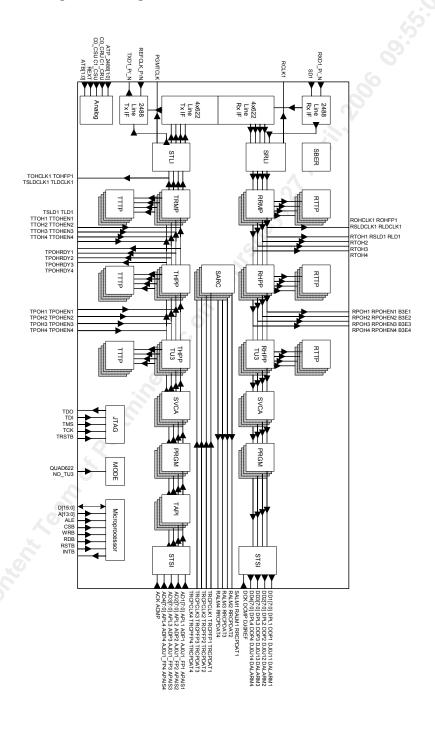

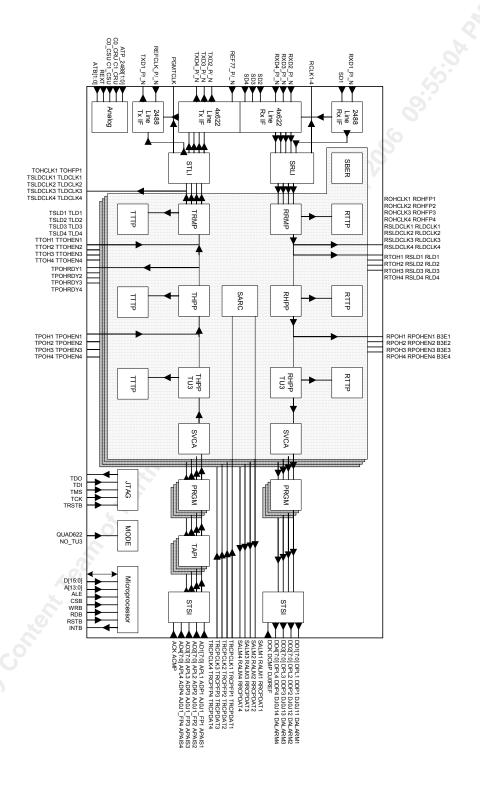

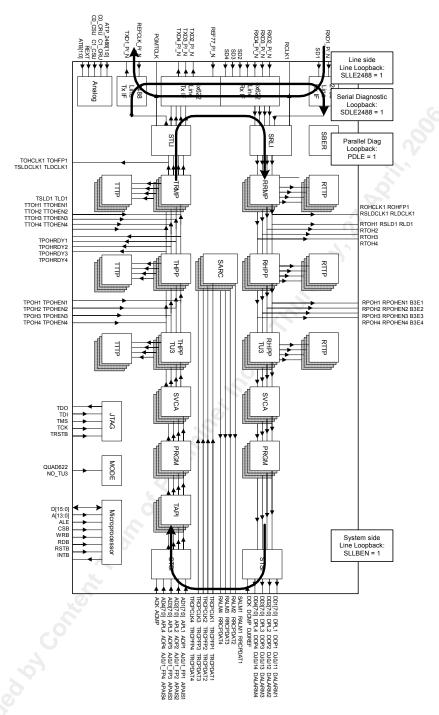

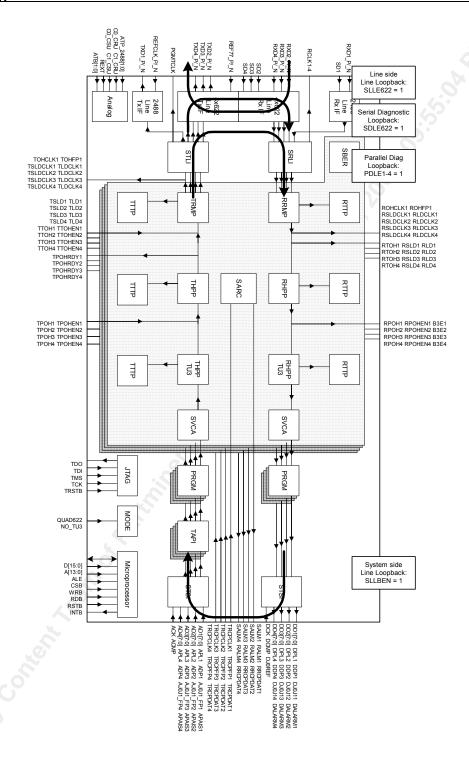

| 6   | Block    | CDiagrams                                                                   | 43    |

| 7   | Desc     | ription                                                                     | 47    |

| 8   | Pin D    | Diagram                                                                     | 49    |

| 9   | Pin D    | Description (500-pin UBGA)                                                  | 51    |

|     | 9.1      | Configuration Pin Signals                                                   | 51    |

|     | 9.2      | STS-48/STM-16 and Quad STS-12/STM-4 Line Side Interface Signals             | 51    |

|     | 9.3      | Receive and Transmit Reference (Single and Quad Mode)                       | 53    |

|     | 9.4      | Section/Line/Path Status and Alarms Signals (Single and Quad Mode)          | 54    |

|     | 9.5      | Receive Section/Line/Path Overhead Extraction Signals (Single and Quad Mode | e) 56 |

|     | 9.6      | Transmit Section/Line/Path Overhead Insertion Signals (Single and Quad Mode | )57   |

|     | 9.7      | Receive Section/Line DCC Extraction Signals (Single and Quad Mode)          | 59    |

|     | 9.8      | Transmit Section/Line DCC Insertion Signals (Single and Quad Mode)          | 60    |

|     | 9.9      | Receive Path BIP-8 Error Signals                                            | 61    |

|     | 9.10     | Drop Bus Telecom Interface Signals (Single and Quad Mode)                   | 61    |

|    | 9.11   | Add Bus Telecom Interface Signals (Single and Quad Mode)                             | 64  |

|----|--------|--------------------------------------------------------------------------------------|-----|

|    | 9.12   | Microprocessor Interface Signals                                                     | 66  |

|    | 9.13   | Analog Miscellaneous Signals                                                         | 68  |

|    | 9.14   | JTAG Test Access Port (TAP) Signals                                                  | 68  |

|    | 9.15   | Power and Ground                                                                     | 69  |

| 10 | Func   | tional Description                                                                   | 72  |

|    | 10.1   | Receive Line Interface                                                               | 72  |

|    | 10.2   | SONET/SDH Receive Line Interface (SRLI)                                              | 72  |

|    | 10.3   | Receive Regenerator and Multiplexer Processor (RRMP)                                 | 73  |

|    | 10.4   | Receive Trail Trace Processor (RTTP)                                                 | 76  |

|    | 10.5   | Receive High Order Path Processor (RHPP)                                             | 77  |

|    | 10.6   | Transmit Line Interface                                                              | 85  |

|    | 10.7   | SONET/SDH Transmit Line Interface (STLI)                                             | 85  |

|    | 10.8   | Transmit Regenerator Multiplexer Processor (TRMP)                                    | 85  |

|    | 10.9   | Transmit Trail Trace Processor (TTTP)                                                | 90  |

|    | 10.10  | Transmit High Order Path Processor (THPP)                                            | 90  |

|    | 10.11  | Transmit Add TelecomBus Pointer Interpreter (TAPI)                                   | 92  |

|    | 10.12  | SONET/SDH Virtual Container Aligner (SVCA)                                           | 92  |

|    | 10.13  | SONET/SDH PRBS Generator and Monitor (PRGM)                                          | 95  |

|    | 10.14  | SONET/SDH Time-Slot Interchange (STSI)                                               | 96  |

|    | 10.15  | System Side Interfaces                                                               | 97  |

|    | 10.16  | SJTAG Test Access Port Interface                                                     | 98  |

|    | 10.17  | Microprocessor Interface                                                             | 98  |

| 11 | Addre  | essing Soft-Errors                                                                   | 99  |

| 12 | Norm   | al Mode Register Description                                                         | 100 |

|    | 12.1   | Register Memory Map                                                                  | 100 |

|    | 12.2   | Registers 112                                                                        |     |

| 13 | Test I | Features Description                                                                 | 597 |

|    | 13.1   | Master Test and Test Configuration Registers                                         | 597 |

|    | 13.2   | JTAG Test Port                                                                       | 602 |

| 14 | Oper   | ation                                                                                | 615 |

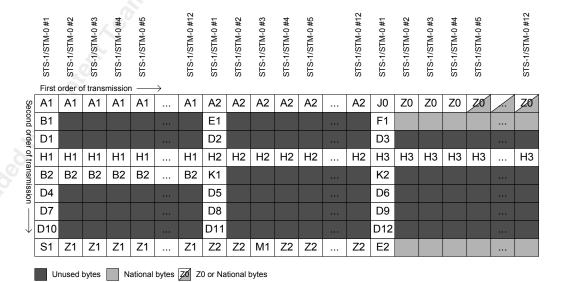

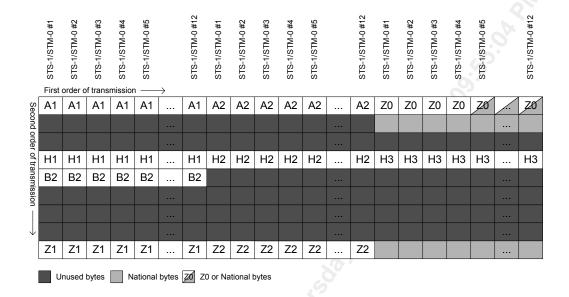

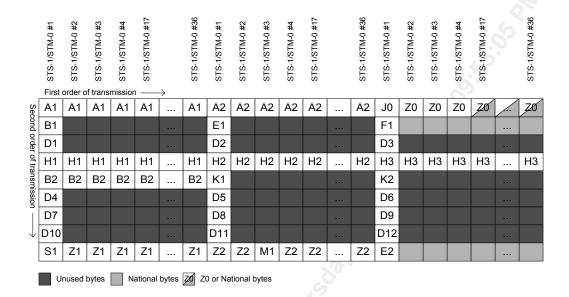

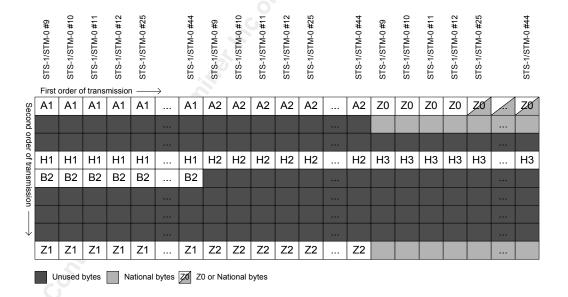

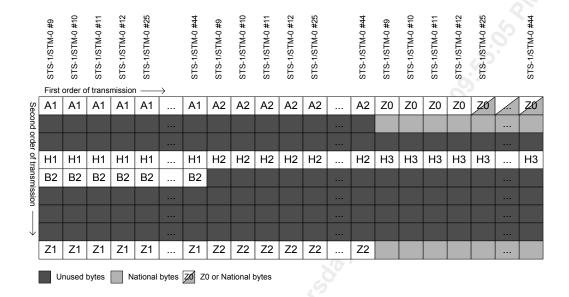

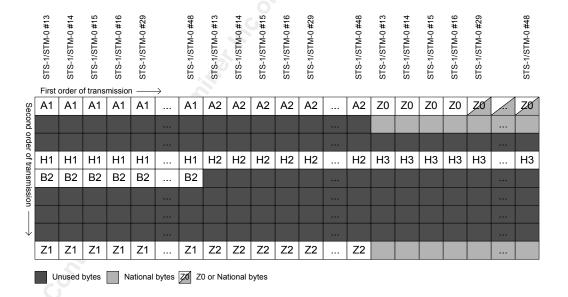

|    | 14.1   | Transport and Path Overhead Bytes                                                    | 615 |

|    | 14.2   | Accessing Indirect Registers                                                         | 620 |

|    | 14.3   | Interrupt Service Routine                                                            | 621 |

|    | 14.4   | Using the Performance Monitoring Features                                            | 621 |

|    | 14.5   | Configuring SONET/SDH Payload from a Concatenated Stream to a Channelized Stream 622 | t   |

|    | 14.6 Translation from AU4/3x(TUG3/TU3/VC3) into 3x(AU3/VC3)                 | 622 |

|----|-----------------------------------------------------------------------------|-----|

|    | 14.7 Translation from 3x(AU3/VC3) into AU4/3x(TUG3/TU3/VC3)                 | 623 |

|    | 14.8 Bit Error Rate Monitor                                                 |     |

|    | 14.9 Setting Up Timeslot Assignments in the STSI                            | 625 |

|    | 14.10 PRBS Generator and Monitor (PRGM)                                     | 627 |

|    | 14.11 Path Unequipped Configuration                                         | 629 |

|    | 14.12 Disabling Transmit Add Bus Pointer Interpreter                        | 630 |

|    | 14.13 Invalid Concatenation Pointer Processing Disable Bit                  | 630 |

|    | 14.14 4x622 Analog Block does not detect an All '0' or All '1' Data Pattern | 632 |

|    | 14.15 Loop Back Operation                                                   |     |

|    | 14.16 JTAG Support                                                          | 634 |

|    | 14.17 Board Design Recommendations                                          | 638 |

|    | 14.18 Power Up Sequence                                                     | 639 |

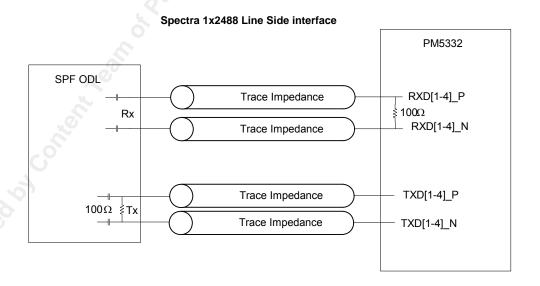

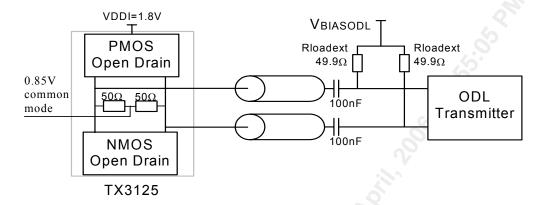

|    | 14.19 Interfacing to SFP ODL Devices                                        | 640 |

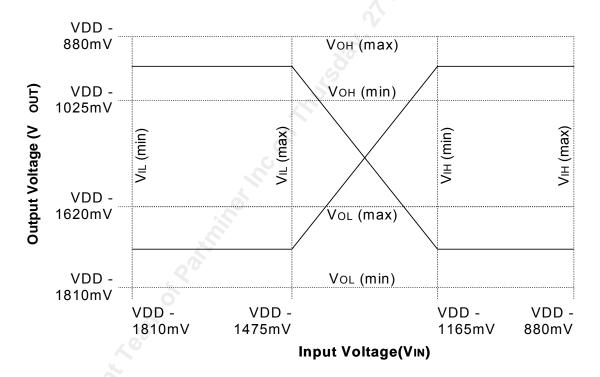

|    | 14.20 Interfacing to ECL or PECL Devices                                    | 641 |

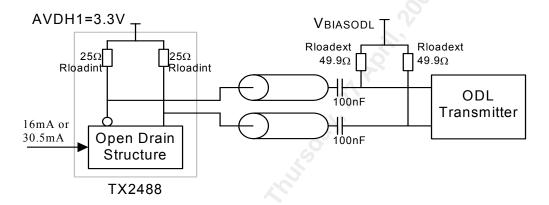

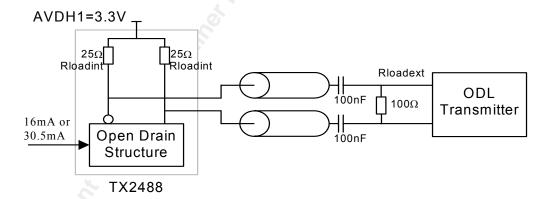

|    | 14.21 Termination Scheme                                                    | 643 |

| 15 | Functional Timing                                                           | 645 |

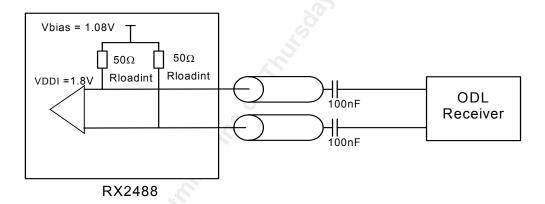

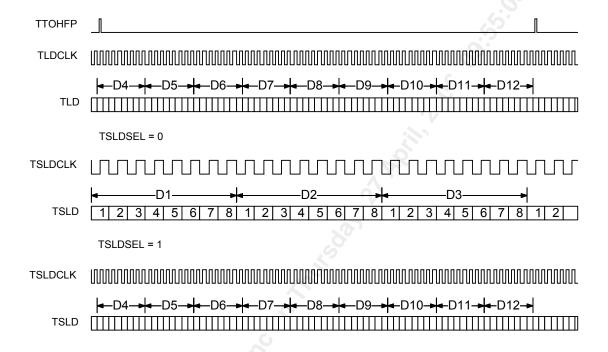

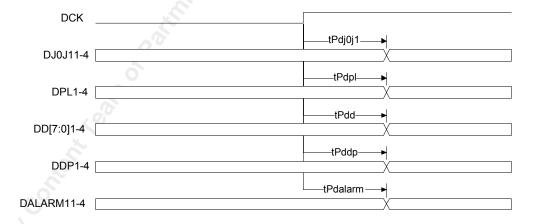

|    | 15.1 ADD Parallel TelecomBus                                                | 645 |

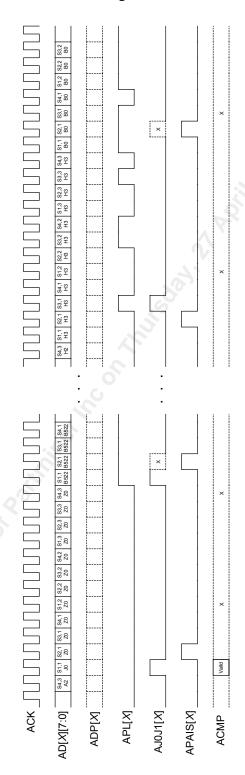

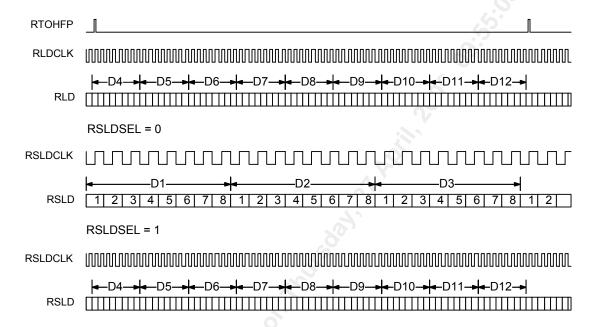

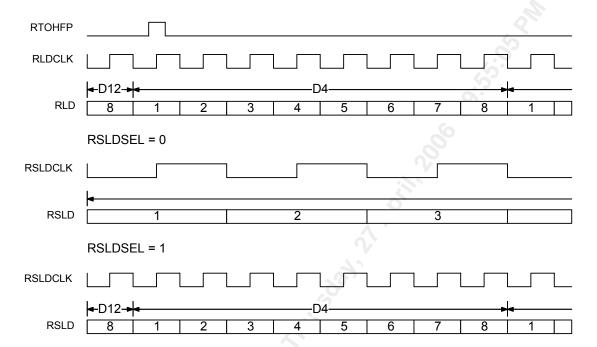

|    | 15.2 DROP Parallel TelecomBus                                               | 647 |

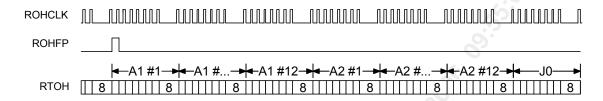

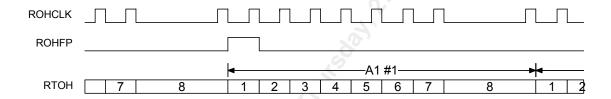

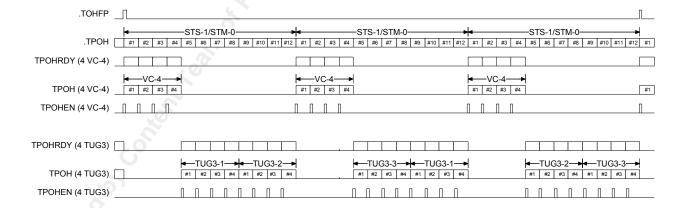

|    | 15.3 Receive Transport Overhead                                             | 649 |

|    | 15.4 Receive Section and Line DCC                                           | 650 |

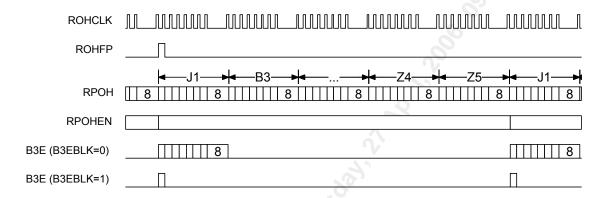

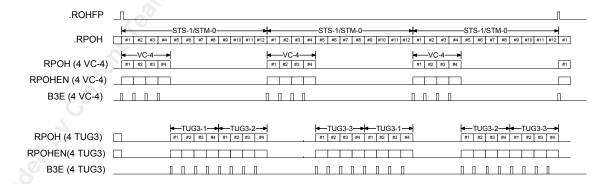

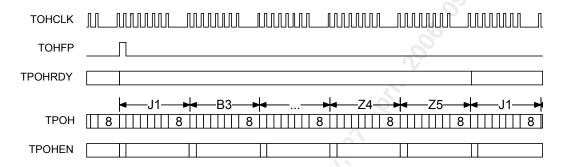

|    | 15.5 Receive Path Overhead Port                                             | 651 |

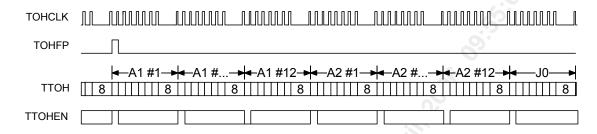

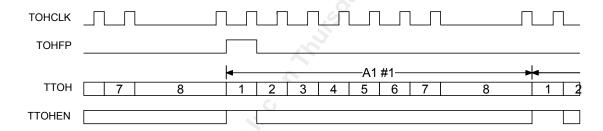

|    | 15.6 Transmit Transport Overhead                                            | 653 |

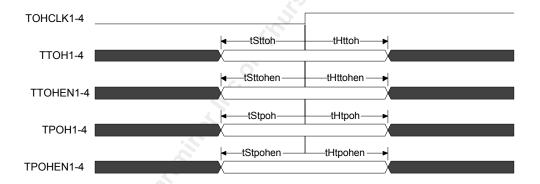

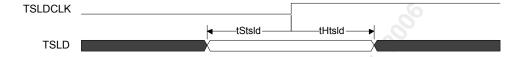

|    | 15.7 Transmit Section and Line DCC                                          | 654 |

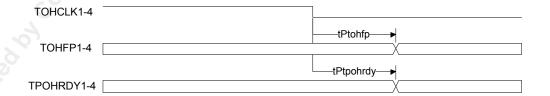

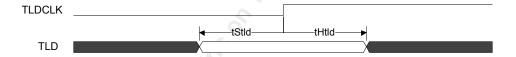

|    | 15.8 Transmit Path Overhead                                                 | 655 |

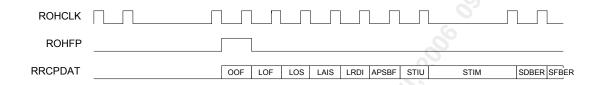

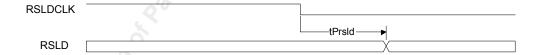

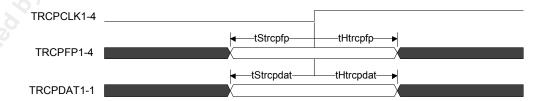

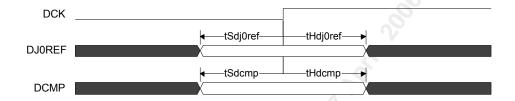

|    | 15.9 Receive Ring Control Port                                              | 656 |

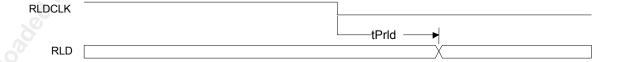

|    | 15.10 Transmit Ring Control Port                                            | 658 |

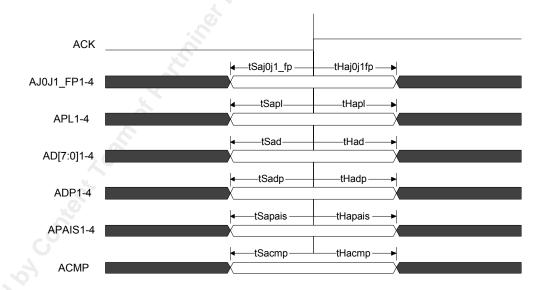

|    | 15.11 Receive Path Alarm                                                    | 659 |

| 16 | Absolute Maximum Ratings                                                    | 660 |

| 17 | Normal Operating Conditions                                                 | 661 |

| 18 | Power Information                                                           | 662 |

|    | 18.1 Power Requirements                                                     | 662 |

|    | 18.2 Power Sequencing                                                       | 662 |

|    | 18.3 Power Supply Filtering                                                 | 663 |

| 19 | D.C. Characteristics                                                        | 667 |

| 20 | A.C. Timing Characteristics                                                 | 669 |

|     | 20.1  | System Miscellaneous Timing                     | .669  |

|-----|-------|-------------------------------------------------|-------|

|     | 20.2  | Single OC-48 Line Interface Timing              | 669   |

|     | 20.3  | Quad OC-12 Line Interface Timing                | . 670 |

|     | 20.4  | Receive Overhead Port Timing                    | 670   |

|     | 20.5  | Transmit Overhead Port Timing                   | . 672 |

|     | 20.6  | Transmit Ring Control Port Timing               | 673   |

|     | 20.7  | System Interface Timing                         | 674   |

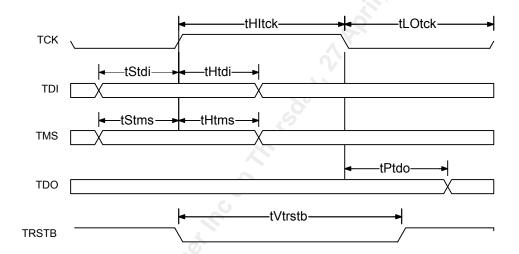

|     | 20.8  | JTAG Test Port Timing                           | 675   |

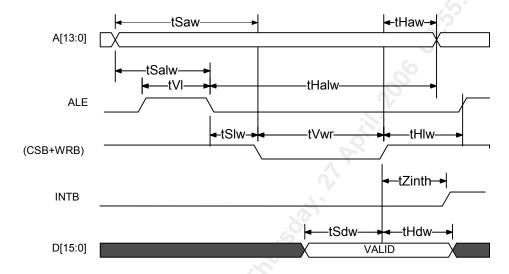

|     | 20.9  | Microprocessor Interface Timing Characteristics | 676   |

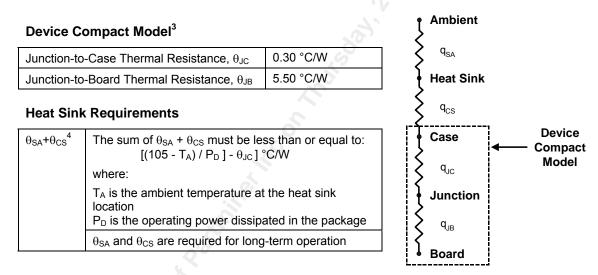

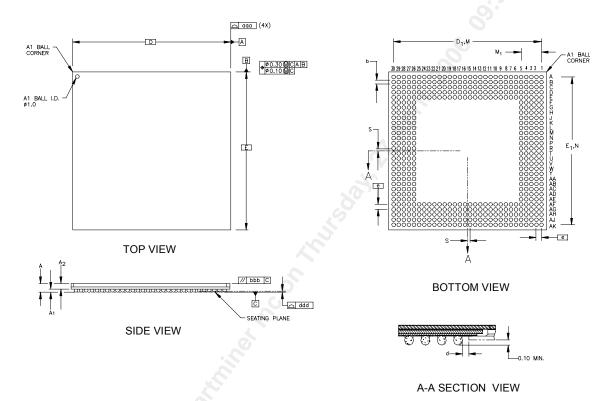

| 21  | Therr | mal Information                                 | 679   |

| 22  | Mech  | anical Information                              | . 680 |

| 23  | Orde  | ring Information                                | . 681 |

| Not | es    | 3.5                                             | . 682 |

## **List of Registers**

| Register 0000H: SPECTRA 1X2488 Master Configuration                                               |     |

|---------------------------------------------------------------------------------------------------|-----|

| Register 0001H: SPECTRA 1X2488 Receive Configuration                                              | 115 |

| Register 0002H: SPECTRA 1X2488 Transmit Configuration                                             | 117 |

| Register 0003H: SPECTRA 1X2488 Loop Timing Configuration                                          | 119 |

| Register 0004H: SPECTRA 1X2488 RCLK Gating Control #1                                             |     |

| Register 0005H: SPECTRA 1X2488 RCLK Gating Control #2                                             |     |

| Register 0006H: SPECTRA 1X2488 RCLK Gating Control #3                                             | 123 |

| Register 0008H: SPECTRA 1X2488 System Side Line Loop Back #1                                      | 124 |

| Register 0009H: SPECTRA 1X2488 System Side Line Loop Back #2                                      | 125 |

| Register 000AH: SPECTRA 1X2488 System Side Line Loop Back #3                                      | 126 |

| Register 000BH: SPECTRA 1X2488 System Side Line Loop Back #4                                      | 127 |

| Register 000EH: SPECTRA 1X2488 Line Activity Monitor                                              | 128 |

| Register 000FH: SPECTRA 1X2488 Interrupt Status #0                                                | 129 |

| Register 0010H: SPECTRA 1X2488 Interrupt Status #1                                                | 130 |

| Register 0011H: SPECTRA 1X2488 Interrupt Status #2                                                | 131 |

| Register 0012H: SPECTRA 1X2488 Interrupt Status #3                                                | 132 |

| Register 0013H: SPECTRA 1X2488 Interrupt Status #4                                                | 133 |

| Register 0014H: SPECTRA 1X2488 Drop System Configuration                                          | 134 |

| Register 0016H: SPECTRA 1X2488 Add System Configuration                                           | 136 |

| Register 0017H: SPECTRA 1X2488 Add Parity Interrupt Status                                        | 138 |

| Register 0018H: SPECTRA 1X2488 System Activity Monitor                                            | 139 |

| Register 0019H: SPECTRA 1X2488 TAPI Path AIS Configuration                                        | 141 |

| Register 001AH: SPECTRA 1X2488 Version ID                                                         | 143 |

| SPECTRA 1x2488Register 001BH: SPECTRA 1X2488 Chip ID                                              | 144 |

| Register 001CH: SPECTRA 1X2488 DOOL, LOS and SD Defect Enable                                     | 145 |

| Register 001DH: SPECTRA 1X2488 Miscellaneous Configuration #1                                     | 147 |

| Register 001FH: SPECTRA 1X2488 Free Registers                                                     | 148 |

| Register 0020H: Rx2488 Analog Interrupt Status                                                    | 149 |

| Register 0021H: Rx2488 Analog Interrupt Control (Single 2488 Mode Only)                           | 151 |

| Register 0022H: Rx2488 Analog CRU Control                                                         | 153 |

| Register 0023H: Rx2488 Analog CRU Clock Training Configuration and Status (Single 2488 Mode Only) | 155 |

| Register 0030H: Quad 622 MABC General Control Register (Quad 622 Mode Only)                       | 158 |

| Register 0031H: Quad 622 Rx MABC Control Register (Quad 622 Mode Only)                            | 160 |

| Register 0033H: Quad 622 Rx MABC Interrupt Enable Register (Quad 6 Mode Only)                                |           |

|--------------------------------------------------------------------------------------------------------------|-----------|

| Register 0034H: Quad 622 Rx MABC Interrupt Status Register (Quad 6: Mode Only)                               | 22<br>163 |

| Register 0035H 0435H 0835H 0C35H: Quad 622 Rx MABC Channel Co<br>Register (Quad 622 Mode Only)               | ontrol    |

| Register 0036H 0436H 0836H 0C36H: Quad 622 Rx Channel Data Path Control Register (Quad 622 Mode Only)        | n167      |

| Register 0038H 0438H 0838H 0C38H: Quad 622 Rx Channel Data Intersection Status Register (Quad 622 Mode Only) |           |

| Register 0039H, 0439H, 0839H, and 0C39H: Quad 622 Rx Channel Data Status Register (Quad 622 Mode Only)       |           |

| Register 0040H: SRLI Clock Configuration                                                                     | 173       |

| Register 0060H, 0460H, 0860H, and 0C60H: SBER Configuration                                                  | 175       |

| Register 0061H, 0461H, 0861H, and 0C61H: SBER Status                                                         | 177       |

| Register 0062H, 0462H, 0862H, and 0C62H: SBER Interrupt Enable                                               | 178       |

| Register 0063H, 0463H, 0863H, and 0C63H: SBER Interrupt Status                                               | 179       |

| Register 0064H, 0464H, 0864H, and 0C64H: SBER SF BERM Accumul Period (LSB)                                   |           |

| Register 0065H, 0465H, 0865H, and 0C65H: SBER SF BERM Accumul Period (MSB)                                   |           |

| Register 0066H, 0466H, 0866H, and 0C66H: SBER SF BERM Saturation                                             |           |

| Register 0067H, 0467H, 0867H, and 0C67H: SBER SF BERM Saturation Threshold (MSB)                             |           |

| Register 0068H, 0468H, 0868H, and 0C68H: SBER SF BERM Declarate Threshold (LSB)                              |           |

| Register 0069H, 0469H, 0869H, and 0C69H: SBER SF BERM Declarate Threshold (MSB)                              |           |

| Register 006AH, 046AH, 086AH, and 0C6AH: SBER SF BERM Clearing Threshold (LSB)                               |           |

| Register 006BH, 046BH, 086BH, and 0C6BH: SBER SF BERM Clearing Threshold (MSB)                               |           |

| Register 006CH, 046CH, 086CH, and 0C6CH: SBER SD BERM Accum Period (LSB)                                     |           |

| Register 006DH, 046DH, 086DH, and 0C6DH: SBER SD BERM Accum<br>Period (MSB)                                  |           |

| Register 006EH, 046EH, 086EH, and 0C6EH: SBER SD BERM Saturat Threshold (LSB)                                |           |

| Register 006FH, 046FH, 086FH, and 0C6FH: SBER SD BERM Saturation Threshold (MSB)                             |           |

| Register 0070H, 0470H, 0870H, and 0C70H: SBER SD BERM Declarate Threshold (LSB)                              |           |

| Register 0072H, 0472H, 0872H, and 0C72H: SBER SD BERM Clearing Threshold (LSB)         | )4 |

|----------------------------------------------------------------------------------------|----|

| Pegister 0073H 0473H 0873H and 0C73H SREP SD REPM Clearing                             |    |

| Threshold (MSB)                                                                        | 95 |

| Register 0080H, 0480H, 0880H, and 0C80H: RRMP Configuration19                          | 96 |

| Register 0081H, 0481H, 0881H, and 0C81H: RRMP Status19                                 | 9  |

| Register 0082H, 0482H, 0882H, and 0C82H: RRMP Interrupt Enable20                       | )1 |

| Register 0083H, 0483H, 0883H, and 0C83H: RRMP Interrupt Status20                       | )4 |

| Register 0084H, 0484H, 0884H, and 0C84H: RRMP Receive APS20                            | )7 |

| Register 0085H, 0485H, 0885H, and 0C85H: RRMP Receive SSM                              | 8( |

| Register 0086H, 0486H, 0886H, and 0C86H: RRMP AIS Enable                               | )9 |

| Register 0087H, 0487H, 0887H, and 0C87H: RRMP Section BIP Error Counter21              | 11 |

| Register 0088H, 0488H, 0888H, and 0C88H: RRMP Line BIP Error Counter (LSB)21           | 12 |

| Register 0089H, 0489H, 0889H, and 0C89H: RRMP Line BIP Error Counter (MSB)21           | 13 |

| Register 008AH, 048AH, 088AH, and 0C8AH: RRMP Line REI Error Counter (LSB)             | 14 |

| Register 008BH, 048BH, 088BH, and 0C8BH: RRMP Line REI Error Counter (MSB)21           | 15 |

| Register 00A0H, 04A0H, 08A0H, and 0CA0H: RTTP SECTION Indirect Address                 | 16 |

| Register 00A1H, 04A1H, 08A1H, and 0CA1H: RTTP SECTION Indirect Data21                  | 18 |

| Register 00A2H, 04A2H, 08A2H, and 0CA2H: RTTP SECTION Trace Unstable Status            | 19 |

| Register 00A3H, 04A3H, 08A3H, and 0CA3H: RTTP SECTION Trace Unstable Interrupt Enable  |    |

| Register 00A4H, 04A4H, 08A4H, and 0CA4H: RTTP SECTION Trace Unstable Interrupt Status  |    |

| Register 00A5H, 04A5H, 08A5H, and 0CA5H: RTTP SECTION Trace Mismatch Status            |    |

| Register 00A6H, 04A6H, 08A6H, and 0CA6H: RTTP SECTION Trace Mismatch Interrupt Enable  |    |

| Register 00A7H, 04A7H, 08A7H, and 0CA7H: RTTP SECTION Trace  Mismatch Interrupt Status |    |

| Indirect Register 00H: RTTP SECTION Trace Configuration                                |    |

| Indirect Register 40H to 7FH: RTTP SECTION Captured Trace                              |    |

| Indirect Register 80H to BFH: RTTP SECTION Accepted Trace                              |    |

| Indirect Register C0H to FFH: RTTP SECTION Expected Trace                              |    |

| Register 00C0H, 04C0H, 08C0H, and 0CC0H: RTTP PATH Indirect Address                     | 230 |

|-----------------------------------------------------------------------------------------|-----|

| Register 00C1H, 04C1H, 08C1H, and 0CC1H: RTTP PATH Indirect Data                        | 232 |

| Register 00C2H, 04C2H, 08C2H, and 0CC2H: RTTP PATH Trace Unstable Status                | 233 |

| Register 00C3H, 04C3H, 08C3H, and 0CC3H: RTTP PATH Trace Unstable Interrupt Enable      | 234 |

| Register 00C4H, 04C4H, 08C4H, and 0CC4H: RTTP PATH Trace Unstable Interrupt Status      | 235 |

| Register 00C5H, 04C5H, 08C5H, and 0CC5H: RTTP PATH Trace Mismatch Status                | 236 |

| Register 00C6H, 04C6H, 08C6H, and 0CC6H: RTTP PATH Trace Mismatch Interrupt Enable      | 237 |

| Register 00C7H, 04C7H, 08C7H, and 0CC7H: RTTP PATH Trace Mismatch Interrupt Status      | 238 |

| Indirect Register 00H: RTTP PATH Trace Configuration                                    | 239 |

| Indirect Register 40H to 7FH: RTTP PATH Captured Trace                                  | 241 |

| Indirect Register 80H to BFH: RTTP PATH Accepted Trace                                  | 242 |

| Indirect Register C0H to FFH: RTTP PATH Expected Trace                                  | 243 |

| Register 00E0H, 04E0H, 08E0H and 0CE0H: RTTP PATH TU3 Indirect Address                  | 244 |

| Register 00E1H, 04E1H, 08E1H, and 0CE1H: RTTP PATH TU3 Indirect Data                    | 246 |

| Register 00E2H, 04E2H, 08E2H, and 0CE2H: RTTP PATH TU3 Trace Unstable Status            | 247 |

| Register 00E3H, 04E3H, 08E3H, and 0CE3H: RTTP PATH TU3 Trace Unstable Interrupt Enable  | 248 |

| Register 00E4H, 04E4H, 08E4H, and 0CE4H: RTTP PATH TU3 Trace Unstable Interrupt Status  | 249 |

| Register 00E5H, 04E5H, 08E5H, and 0CE5H: RTTP PATH TU3 Trace Mismatch Status            | 250 |

| Register 00E6H, 04E6H, 08E6H, and 0CE6H: RTTP PATH TU3 Trace  Mismatch Interrupt Enable | 251 |

| Register 00E7H, 04E7H, 08E7H, and 0CE7H: RTTP PATH TU3 Trace  Mismatch Interrupt Status | 252 |

| Indirect Register 00H: RTTP PATH TU3 Trace Configuration                                | 253 |

| Indirect Register 40H to 7FH: RTTP PATH TU3 Captured Trace                              | 255 |

| Indirect Register 80H to BFH: RTTP PATH TU3 Accepted Trace                              | 256 |

| Indirect Register C0H to FFH: RTTP PATH TU3 Expected Trace                              | 257 |

| Register 0100H, 0500H, 0900H, and 0D00H: RHPP Indirect Address                          |     |

| Register 0101H, 0501H, 0901H, and 0D01H: RHPP Indirect Data                             | 260 |

| Register 0102H, 0502H, 0902H, and 0D02H: RHPP Payload Configuration                     |     |

| Register 0103H, 0503H, 0903H, and 0D03H: RHPP Counter Update                            |     |

|                                                                                         |     |

| Register 0104H, 0504H, 0904H, and 0D04H: RHPP Path Interrupt Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 264 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Register 0105H, 0505H, 0905H and 0D05H: RHPP Pointer Concatenation Processing Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 265   |

| Register 0108H, 0508H, 0908H and 0D08H: RHPP Pointer Interpreter Status (STS1/STM0 #1) Register 0110H, 0510H, 0910H and 0D10H: (STS1/STM0 #2) Register 0118H, 0518H, 0918H and 0D18H: (STS1/STM0 #3) Register 0120H, 0520H, 0920H and 0D20H: (STS1/STM0 #4) Register 0128H, 0528H, 0928H and 0D28H: (STS1/STM0 #5) Register 0130H, 0530H, 0930H and 0D30H: (STS1/STM0 #6) Register 0138H, 0538H, 0938H and 0D38H: (STS1/STM0 #7) Register 0140H, 0540H, 0940H and 0D40H: (STS1/STM0 #8) Register 0148H, 0548H, 0948H and 0D48H: (STS1/STM0 #9) Register 0150H, 0550H, 0950H and 0D50H: (STS1/STM0 #10) Register 0158H, 0558H, 0958H and 0D58H: (STS1/STM0 #11) Register 0160H, 0560H, 0960H and 0D60H: (STS1/STM0 #12)           | 266   |

| Register 0109H, 0509H, 0909H and 0D09H: RHPP Pointer Interpreter Interrupt Enable (STS1/STM0 #1) Register 0111H, 0511H, 0911H and 0D11H: (STS1/STM0 #2) Register 0119H, 0519H, 0919H and 0D19H: (STS1/STM0 #3) Register 0121H, 0521H, 0921H and 0D21H: (STS1/STM0 #4) Register 0129H, 0529H, 0929H and 0D29H: (STS1/STM0 #5) Register 0131H, 0531H, 0931H and 0D31H: (STS1/STM0 #6) Register 0139H, 0539H, 0939H and 0D39H: (STS1/STM0 #7) Register 0141H, 0541H, 0941H and 0D41H: (STS1/STM0 #8) Register 0149H, 0549H, 0949H and 0D49H: (STS1/STM0 #9) Register 0151H, 0551H, 0951H and 0D51H: (STS1/STM0 #10) Register 0159H, 0559H, 0959H and 0D59H: (STS1/STM0 #11) Register 0161H, 0561H, 0961H and 0D61H: (STS1/STM0 #12) | 268   |

| Register 010AH, 050AH, 090AH and 0D0AH: RHPP Pointer Interpreter Interrupt Status (STS1/STM0 #1) Register 0112H, 0512H, 0912H and 0D12H: (STS1/STM0 #2) Register 011AH, 051AH, 091AH and 0D1AH: (STS1/STM0 #3) Register 0122H, 0522H, 0922H and 0D22H: (STS1/STM0 #4) Register 012AH, 052AH, 092AH and 0D2AH: (STS1/STM0 #5) Register 0132H, 0532H, 0932H and 0D32H: (STS1/STM0 #6) Register 013AH, 053AH, 093AH and 0D3AH: (STS1/STM0 #7) Register 0142H, 0542H, 0942H and 0D42H: (STS1/STM0 #8) Register 014AH, 054AH, 094AH and 0D4AH: (STS1/STM0 #9) Register 0152H, 0552H, 0952H and 0D52H: (STS1/STM0 #10) Register 015AH, 055AH, 095AH and 0D5AH: (STS1/STM0 #11) Register 0162H, 0562H, 0962H and 0D62H: (STS1/STM0 #12) | 270   |

| Register 010BH, 050BH, 090BH and 0D0BH: RHPP Error Monitor Status (STS1/STM0 #1) Register 0113H, 0513H, 0913H and 0D13H: (STS1/STM0 #2) Register 011BH, 051BH, 091BH and 0D1BH: (STS1/STM0 #3) Register 0123H, 0523H, 0923H and 0D23H: (STS1/STM0 #4) Register 012BH, 052BH, 092BH and 0D2BH: (STS1/STM0 #5) Register 0133H, 0533H, 0933H and 0D33H: (STS1/STM0 #6) Register 013BH, 053BH, 093BH and 0D3BH: (STS1/STM0 #7) Register 0143H, 0543H, 0943H and 0D43H: (STS1/STM0 #8) Register 014BH, 054BH, 094BH and 0D4BH: (STS1/STM0 #9) Register 0153H, 0553H, 0953H and 0D53H: (STS1/STM0 #10) Register 015BH, 055BH, 095BH and 0D5BH: (STS1/STM0 #11) Register 0163H, 0563H, 0963H and 0D63H: (STS1/STM0 #12)           | 272 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Register 010CH, 050CH, 090CH and 0D0CH: RHPP Error Monitor Interrupt Enable (STS1/STM0 #1) Register 0114H, 0514H, 0914H and 0D14H: (STS1/STM0 #2) Register 011CH, 051CH, 091CH and 0D1CH: (STS1/STM0 #3) Register 0124H, 0524H, 0924H and 0D24H: (STS1/STM0 #4) Register 012CH, 052CH, 092CH and 0D2CH: (STS1/STM0 #5) Register 0134H, 0534H, 0934H and 0D34H: (STS1/STM0 #6) Register 013CH, 053CH, 093CH and 0D3CH: (STS1/STM0 #7) Register 0144H, 0544H, 0944H and 0D44H: (STS1/STM0 #8) Register 014CH, 054CH, 094CH and 0D4CH: (STS1/STM0 #9) Register 015CH, 055CH, 095CH and 0D5CH: (STS1/STM0 #10) Register 015CH, 055CH, 095CH and 0D5CH: (STS1/STM0 #11) Register 0164H, 0564H, 0964H and 0D64H: (STS1/STM0 #12) | 275 |

| Register 010DH, 050DH, 090DH and 0D0DH: RHPP Error Monitor Interrupt Status (STS1/STM0 #1) Register 0115H, 0515H, 0915H and 0D15H: (STS1/STM0 #2) Register 011DH, 051DH, 091DH and 0D1DH: (STS1/STM0 #3) Register 0125H, 0525H, 0925H and 0D25H: (STS1/STM0 #4) Register 012DH, 052DH, 092DH and 0D2DH: (STS1/STM0 #5) Register 013DH, 0535H, 0935H and 0D35H: (STS1/STM0 #6) Register 013DH, 053DH, 093DH and 0D3DH: (STS1/STM0 #7) Register 0145H, 0545H, 0945H and 0D45H: (STS1/STM0 #8) Register 014DH, 054DH, 094DH and 0D4DH: (STS1/STM0 #9) Register 0155H, 0555H, 0955H and 0D55H: (STS1/STM0 #10) Register 015DH, 055DH, 095DH and 0D5DH: (STS1/STM0 #11) Register 0165H, 0565H, 0965H and 0D65H: (STS1/STM0 #12) |     |

| Indirect Register 00H: RHPP Pointer Interpreter Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| Indirect Register 01H: RHPP Error Monitor Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 283 |

| The B3EONRPOH bit controls the data presented on RPOH ports. When set to logic 0, the received B3 byte is placed on the RPOH port. When set to logic 1, the B3 error count is placed on the RPOH port as it is placed on the B3E port. Indirect Register 02H: RHPP Pointer Value and ERDI                                                                                                                                                                                                                                                                                                                                                                                                                                  | 286 |

| Indirect Register 03H: RHPP Captured and Accepted PSL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 287 |

| Indirect Register 04H: RHPP Expected PSL and PDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 288 |

| Indirect Register 05H: RHPP Pointer Interpreter Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 289 |

| Indirect Register 06H: RHPP Path BIP Error Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 291 |

| Indirect Register 07H: RHPP Path REI Error Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 292 |

| Indirect Register 08H: RHPP Path Negative Justification Event Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .93 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Indirect Register 09H: RHPP Path Positive Justification Event Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 94  |

| Register 0180H, 0580H, 0980H, and 0D80H: RHPP TU3 Indirect Address2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 95  |

| Register 0181H, 0581H, 0981H, and 0D81H: RHPP TU3 Indirect Data2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 97  |

| Register 0182H, 0582H, 0982H, and 0D82H: RHPP TU3 Payload Configuration2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| Register 0183H, 0583H, 0983H, and 0D83H: RHPP TU3 Counters Update3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 00  |

| Register 0184H, 0584H, 0984H, and 0D84H: RHPP TU3 Path Interrupt Status3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 01  |

| Register 0188H, 0588H, 0988H and 0D88H: RHPP TU3 Pointer Interpreter Status(STS1/STM0 #1) Register 0190H, 0590H, 0990H and 0D90H: (STS1/STM0 #2) Register 0198H, 0598H, 0998H and 0D98H: (STS1/STM0 #3) Register 01A0H, 05A0H, 09A0H and 0DA0H: (STS1/STM0 #4) Register 01A8H, 05A8H, 09A8H and 0DA8H: (STS1/STM0 #5) Register 01B0H, 05B0H, 09B0H and 0DB0H: (STS1/STM0 #6) Register 01B8H, 05B8H, 09B8H and 0DB8H: (STS1/STM0 #7) Register 01C0H, 05C0H, 09C0H and 0DC0H: (STS1/STM0 #8) Register 01C8H, 05C8H, 09C8H and 0DC8H: (STS1/STM0 #9) Register 01D0H, 05D0H, 09D0H and 0DD0H: (STS1/STM0 #10) Register 01D8H, 05D8H, 09D8H and 0DD8H: (STS1/STM0 #11) Register 01E0H, 05E0H, 09E0H and 0DE0H: (STS1/STM0 #12) | 302 |

| Register 0189H, 0589H, 0989H and 0D89H: RHPP TU3 Pointer Interpreter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 02  |

| Interrupt Enable (STS1/STM0 #1) Register 0191H, 0591H, 0991H and 0D91H: (STS1/STM0 #2) Register 0199H, 0599H, 0999H and 0D99H: (STS1/STM0 #3) Register 01A1H, 05A1H, 09A1H and 0DA1H: (STS1/STM0 #4) Register 01A9H, 05A9H, 09A9H and 0DA9H: (STS1/STM0 #5) Register 01B1H, 05B1H, 09B1H and 0DB1H: (STS1/STM0 #6) Register 01B9H, 05B9H, 09B9H and 0DB9H: (STS1/STM0 #7) Register 01C1H, 05C1H, 09C1H and 0DC1H: (STS1/STM0 #8) Register 01C9H, 05C9H, 09C9H and 0DC9H: (STS1/STM0 #9) Register 01D1H, 05D1H, 09D1H and 0DD1H: (STS1/STM0 #10) Register 01D9H, 05D9H, 09D9H and 0DD9H: (STS1/STM0 #11) Register 01E1H, 05E1H, 09E1H and 0DE1H: (STS1/STM0 #12)                                                           | 304 |

| Register 018AH, 058AH, 098AH and 0D8AH: RHPP TU3 Pointer Interpreter Interrupt Status (STS1/STM0 #1) Register 0192H, 0592H, 0992H and 0D92H: (STS1/STM0 #2) Register 019AH, 059AH, 099AH and 0D9AH: (STS1/STM0 #3) Register 01A2H, 05A2H, 09A2H and 0DA2H: (STS1/STM0 #4) Register 01AAH, 05AAH, 09AAH and 0DAAH: (STS1/STM0 #5) Register 01B2H, 05B2H, 09B2H and 0DB2H: (STS1/STM0 #6) Register 01BAH, 05BAH, 09BAH and 0DBAH: (STS1/STM0 #7) Register 01C2H, 05C2H, 09C2H and 0DC2H: (STS1/STM0 #8) Register 01CAH, 05CAH, 09CAH and 0DCAH: (STS1/STM0 #9) Register 01D2H, 05D2H, 09D2H and 0DD2H: (STS1/STM0 #10) Register 01DAH, 05DAH, 09DAH and 0DDAH: (STS1/STM0 #11) Register 01E2H, 05E2H, 09E2H and 0DE2H:      | 100 |

| (STS1/STM0 #12)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | UD  |

| Register 018BH, 058BH, 098BH and 0D8BH: RHPP TU3 Error Monitor Status (STS1/STM0 #1) Register 0193H, 0593H, 0993H and 0D93H: (STS1/STM0 #2) Register 019BH, 059BH, 099BH and 0D9BH: (STS1/STM0 #3) Register 01A3H, 05A3H, 09A3H and 0DA3H: (STS1/STM0 #4) Register 01ABH, 05ABH, 09ABH and 0DABH: (STS1/STM0 #5) Register 01B3H, 05B3H, 09B3H and 0DB3H: (STS1/STM0 #6) Register 01BBH, 05BBH, 09BBH and 0DBBH: (STS1/STM0 #7) Register 01C3H, 05C3H, 09C3H and 0DC3H: (STS1/STM0 #8) Register 01CBH, 05CBH, 09CBH and 0DCBH: (STS1/STM0 #9) Register 01D3H, 05D3H, 09D3H and 0DD3H: (STS1/STM0 #10) Register 01DBH, 05DBH, 09DBH and 0DDBH: (STS1/STM0 #11) Register 01E3H, 05E3H, 09E3H and 0DE3H: (STS1/STM0 #12)           | 308 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| (STS1/STM0 #5) Register 01B4H, 05B4H, 09B4H and 0DB4H: (STS1/STM0 #6) Register 01BCH, 05BCH, 09BCH and 0DBCH: (STS1/STM0 #7) Register 01C4H, 05C4H, 09C4H and 0DC4H: (STS1/STM0 #8) Register 01CCH, 05CCH, 09CCH and 0DCCH: (STS1/STM0 #9) Register 01D4H, 05D4H, 09D4H and 0DD4H: (STS1/STM0 #10) Register 01DCH, 05DCH, 09DCH and 0DDCH: (STS1/STM0 #11) Register 01E4H, 05E4H, 09E4H and 0DE4H: (STS1/STM0 #12)                                                                                                                                                                                                                                                                                                             | 311 |

| Register 018DH, 058DH, 098DH and 0D8DH: RHPP TU3 Error Monitor Interrupt Status (STS1/STM0 #1) Register 0195H, 0595H, 0995H and 0D95H: (STS1/STM0 #2) Register 019DH, 059DH, 099DH and 0D9DH: (STS1/STM0 #3) Register 01A5H, 05A5H, 09A5H and 0DA5H: (STS1/STM0 #4) Register 01ADH, 05ADH, 09ADH and 0DADH: (STS1/STM0 #5) Register 01B5H, 05B5H, 09B5H and 0DB5H: (STS1/STM0 #6) Register 01BDH, 05BDH, 09BDH and 0DBDH: (STS1/STM0 #7) Register 01C5H, 05C5H, 09C5H and 0DC5H: (STS1/STM0 #8) Register 01CDH, 05CDH, 09CDH and 0DCDH: (STS1/STM0 #9) Register 01D5H, 05D5H, 09D5H and 0DD5H: (STS1/STM0 #10) Register 01DDH, 0D5DH, 09DDH and 0DDDH: (STS1/STM0 #11) Register 01E5H, 05E5H, 09E5H and 0DE5H: (STS1/STM0 #12) | 314 |

| Indirect Register 00H: RHPP TU3 Pointer Interpreter Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| Indirect Register 01H: RHPP TU3 Error Monitor Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| Indirect Register 02H: RHPP TU3 Pointer Value and ERDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| Indirect Register 03H: RHPP TU3 captured and accepted PSL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 323 |

| Indirect Register 04H: RHPP TU3 Expected PSL and PDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 324 |

| Indirect Register 05H: RHPP TU3 Pointer Interpreter status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 325 |

| Indirect Register 06H: RHPP TU3 Path BIP Error Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 327 |

| Indirect Register 07H: RHPP TU3 Path REI Error Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 328 |

| Indirect Register 08H: RHPP TU3 Path Negative Justification Event Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 329 |

| Indirect Register 09H: RHPP TU3 Path Positive Justification Event Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 330 |

| Register 0200H, 0600H, 0A00H, and 0E00H: RSVCA Indirect Address                                | 331 |

|------------------------------------------------------------------------------------------------|-----|

| Register 0201H, 0601H, 0A01H, and 0E01H: RSVCA Indirect Data                                   | 333 |

| Register 0202H, 0602H, 0A02H, and 0E02H: RSVCA Payload Configuration                           | 334 |

| Register 0203H, 0603H, 0A03H, and 0E03H: RSVCA Positive Pointer Justification Interrupt Status | 337 |

| Register 0204H, 0604H, 0A04H, and 0E04H: RSVCA Negative Pointer Justification Interrupt Status | 338 |

| Register 0205H, 0605H, 0A05H, and 0E05H: RSVCA FIFO Overflow Interrupt Status                  | 339 |

| Register 0206H, 0606H, 0A06H, and 0E06H: RSVCA FIFO Underflow Interrupt Status                 | 340 |

| Register 0207H, 0607H, 0A07H, and 0E07H: RSVCA Pointer Justification Interrupt Enable          | 341 |

| Register 0208H, 0608H, 0A08H, and 0E08H: RSVCA FIFO Interrupt Enable                           | 342 |

| Register 020AH, 060AH, 0A0AH, and 0E0AH: RSVCA Clear Fixed Stuff                               | 343 |

| Register 020BH, 060BH, 0A0BH, and 0E0BH: RSVCA Counter Update                                  | 344 |

| Indirect Register 00H: RSVCA Positive Justifications Performance Monitor                       | 345 |

| Indirect Register 01H: RSVCA Negative Justifications Performance Monitor                       | 346 |

| Indirect Register 02H: RSVCA Diagnostic/Configuration                                          | 347 |

| Register 0220H: DSTSI Indirect Address                                                         | 349 |

| Register 0221H: DSTSI Indirect Data                                                            | 351 |

| Register 0222H: DSTSI Configuration                                                            | 353 |

| Register 0223H: DSTSI Interrupt Status                                                         | 355 |

| Register 0240H, 0640H, 0A40H, and 0E40H: DPRGM Indirect Address                                | 356 |

| Register 0241H, 0641H, 0A41H, and 0E41H: DPRGM Indirect Data                                   | 358 |

| Register 0242H, 0642H, 0A42H, and 0E42H: DPRGM Generator Payload Configuration                 | 359 |

| Register 0243H, 0643H, 0A43H, and 0E43H: DPRGM Monitor Payload Configuration                   | 361 |

| Register 0244H, 0644H, 0A44H, and 0E44H: DPRGM Monitor Byte Error Interrupt Status             | 363 |

| Register 0245H, 0645H, 0A45H, and 0E45H: DPRGM Monitor Byte Error Interrupt Enable             | 364 |

| Register 0246H, 0646H, 0A46H, and 0E46H: DPRGM Monitor B1/E1 Bytes Interrupt Status            | 365 |

| Register 0247H, 0647H, 0A47H, and 0E47H: DPRGM Monitor B1/E1 Bytes Interrupt Enable            | 366 |

| Register 0249H, 0649H, 0A49H, and 0E49H: DPRGM Monitor Synchronization Interrupt Status        | 367 |

| Register 024AH, 064AH, 0A4AH, and 0E4AH: DPRGM Monitor Synchronization Interrupt Enable        | 368 |

| Register 024BH, 064BH, 0A4BH, and 0E4BH: DPRGM Monitor Synchronization Status | 369 |

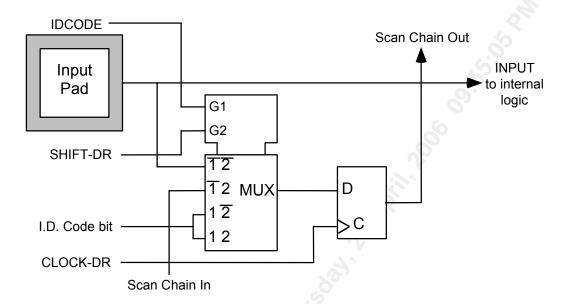

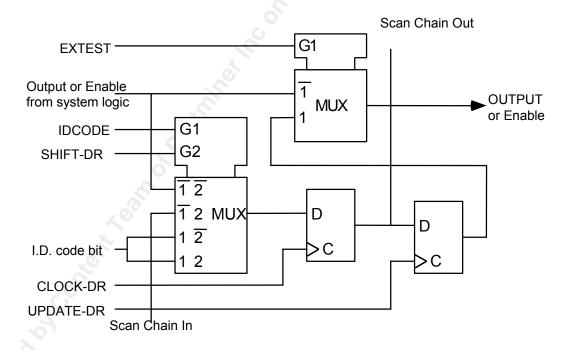

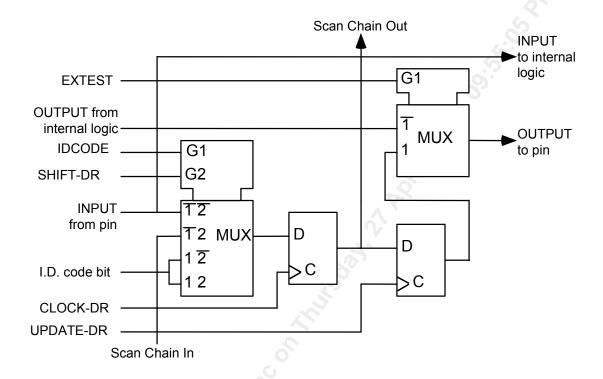

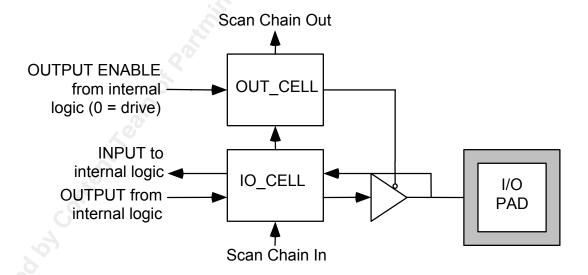

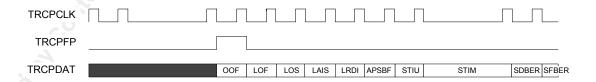

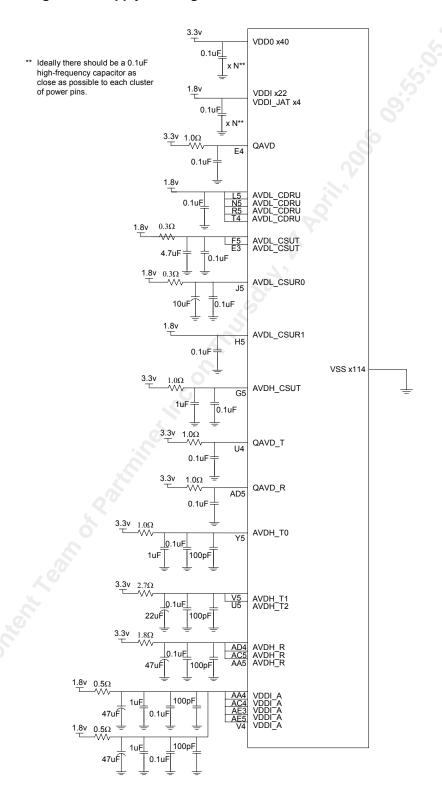

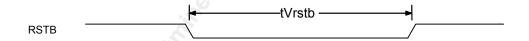

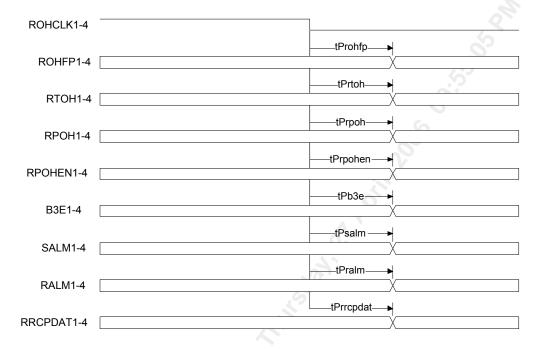

|-------------------------------------------------------------------------------|-----|