# VSC8256-01 Datasheet Quad Channel 1G/10GBASE-KR to SFI Multi-Rate Multiprotocol Bi-Directional Repeater/Re-Timer/Conditioner

Microsemi Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

Email: sales.support@microsemi.com www.microsemi.com

©2017–2018 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at www.microsemi.com.

# **Contents**

| 1 | Revisi<br>1.1<br>1.2<br>1.3       | Revision<br>Revision                                           | tory<br>n 4.0<br>n 2.1<br>n 2.0                                                                                                                                                             | 1<br>1               |  |

|---|-----------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|

| 2 | Overv<br>2.1<br>2.2<br>2.3<br>2.4 | Highligh<br>Interface<br>Feature                               | nts                                                                                                                                                                                         |                      |  |

| 3 | 3.1<br>3.2                        | Data Pa<br>3.1.1                                               | escriptions  th Overview  Ingress and Egress Operation                                                                                                                                      | 5<br>5               |  |

|   | 3.2                               | 3.2.1<br>3.2.2<br>3.2.3                                        | l Media Attachment (PMA) Reference Clock VScope™ Input Signal Monitoring Integrated Circuit 10GBASE-KR                                                                                      | 6<br>6               |  |

|   | 3.3<br>3.4                        | •                                                              | ck                                                                                                                                                                                          |                      |  |

|   | 3.5                               | Host-Sid<br>3.5.1                                              | de Interface Output Clocks                                                                                                                                                                  |                      |  |

|   | 3.6                               | Table 2,<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5<br>3.6.6 | page 6 Table 2, page 6Table 2, page 6Management Interfaces MDIO Interface SPI Slave Interface Two-Wire Serial (Slave) Interface Two-Wire Serial (Master) Interface JTAG General Purpose I/O | 10<br>11<br>14<br>16 |  |

| 4 | Electrical Specifications         |                                                                |                                                                                                                                                                                             |                      |  |

| т | 4.1                               |                                                                | racteristics Low-Speed Inputs and Outputs Reference Clock                                                                                                                                   | 22<br>22             |  |

|   | 4.2                               | 4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6             | racteristics Receiver Specifications Transmitter Specifications Timing and Reference Clock Two-Wire Serial (Slave) Interface MDIO Interface SPI Slave Interface ng Conditions               |                      |  |

|   | 4.4                               | -                                                              | Ratings                                                                                                                                                                                     |                      |  |

| 5 | Pin De 5.1 5.2                    | Pin Diag                                                       | ONS                                                                                                                                                                                         | 34                   |  |

| 6 |                                   | •                                                              | ormation                                                                                                                                                                                    | 43                   |  |

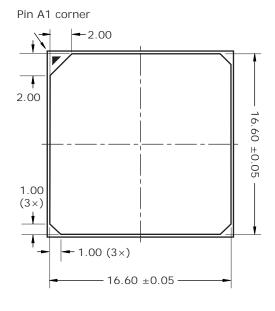

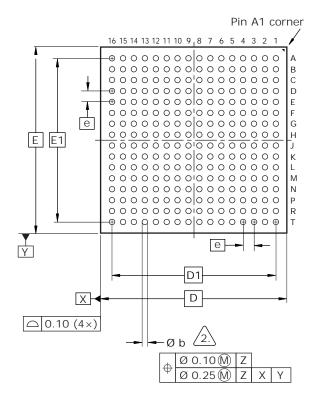

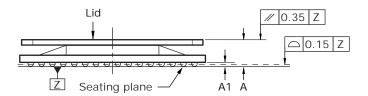

|   | 6.1   | Package Drawing                       | 43   |

|---|-------|---------------------------------------|------|

|   | 6.2   | Thermal Specifications                | . 44 |

|   | 6.3   | Moisture Sensitivity                  | . 45 |

| 7 | Desig | n Considerations                      | . 46 |

|   | 7.1   | SPI bus speeds                        | 46   |

|   | 7.2   | Device clocking                       | 46   |

|   | 7.3   | Low-power mode and SerDes calibration | 46   |

|   | 7.4   | PHY ID error with VDDLR               | 46   |

|   | 7.5   | KR autonegotiation/training           | 46   |

|   | 7.6   | 1G mode operation                     | . 46 |

| 8 | Order | ing Information                       | . 47 |

# **Figures**

| Figure 1  | Block Diagram                                    | . 3 |

|-----------|--------------------------------------------------|-----|

| Figure 2  | SFP+ Transceiver                                 |     |

| Figure 3  | Backplane Equalization Application               |     |

| Figure 4  | 10GBASE-KR Output Driver                         | . 7 |

| Figure 5  | 10GBASE-KR Test Pattern                          | . 8 |

| Figure 6  | Host-Side and Line-Side Loopbacks                | . ( |

| Figure 7  | Per-Port Clock Outputs                           | . ( |

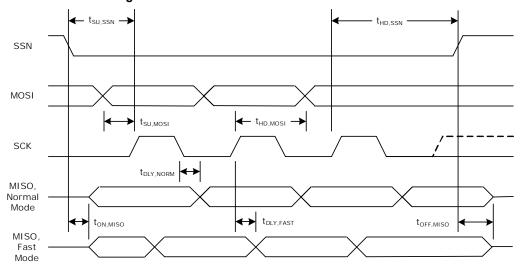

| Figure 8  | SPI Single Register Read                         | 12  |

| Figure 9  | SPI Multiple Register Reads                      | 12  |

| Figure 10 | SPI Multiple Register Writes                     | 13  |

| Figure 11 | SPI Read Following Write                         | 13  |

| Figure 12 | SPI Write Following Read                         | 13  |

| Figure 13 | SPI Slave Default Mode                           | 14  |

| Figure 14 | SPI Slave Fast Mode                              | 14  |

| Figure 15 | Two-Wire Serial Bus Reset Sequence               | 15  |

| Figure 16 | Two-Wire Serial Slave Register Address Format    | 15  |

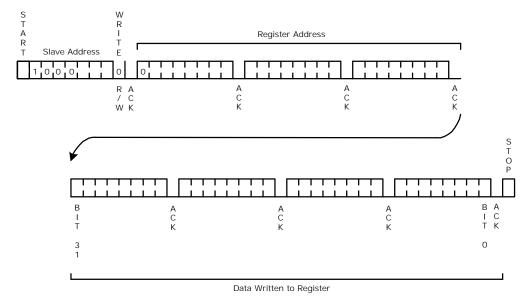

| Figure 17 | Two-Wire Serial Write Instruction                | 16  |

| Figure 18 | Two-Wire Serial Read Instruction                 | 16  |

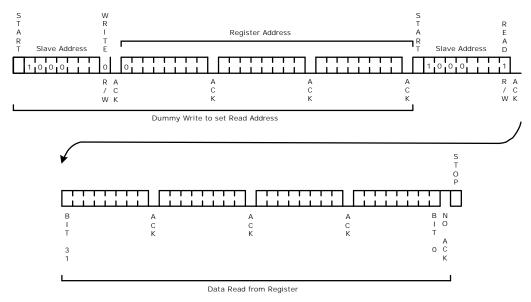

| Figure 19 | GPIO Block Diagram                               | 19  |

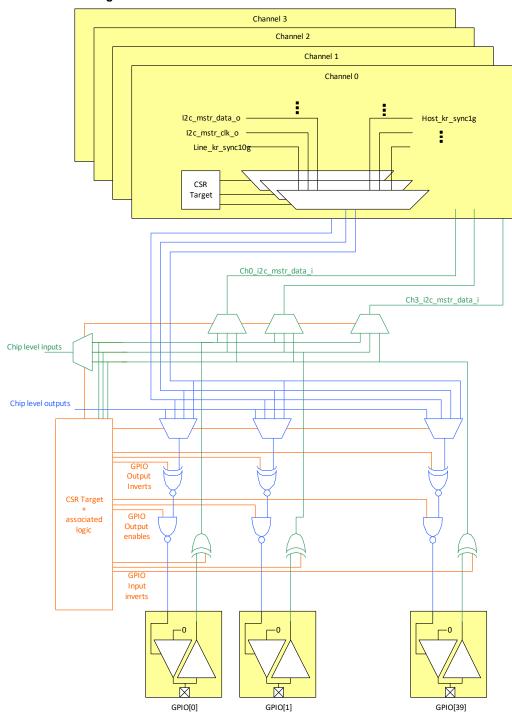

| Figure 20 | Interrupt Scheme                                 | 21  |

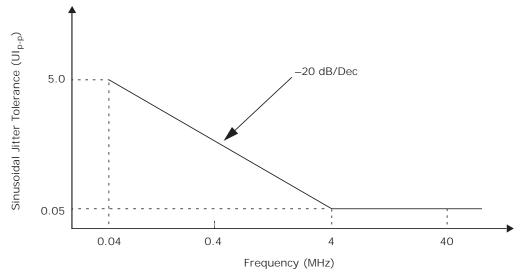

| Figure 21 | SFI Datacom Sinusoidal Jitter Tolerance          | 25  |

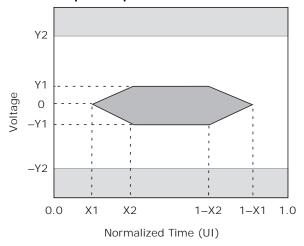

| Figure 22 | SFI Transmit Differential Output Compliance Mask | 27  |

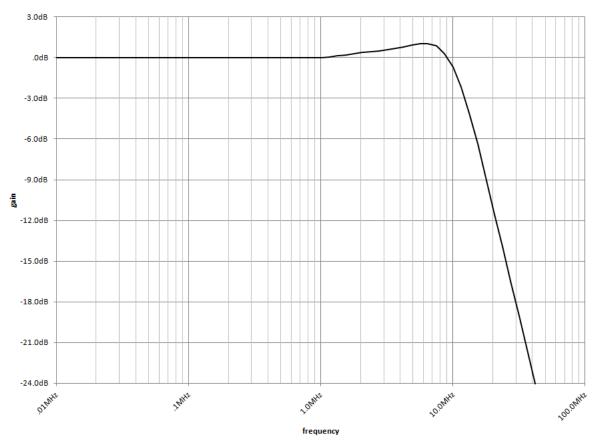

| Figure 23 | LREFCK/HREFCLK to Data Output Jitter Transfer    | 29  |

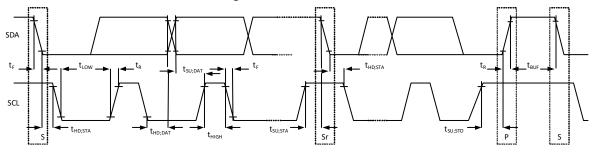

| Figure 24 | Two-Wire Serial Interface Timing                 | 30  |

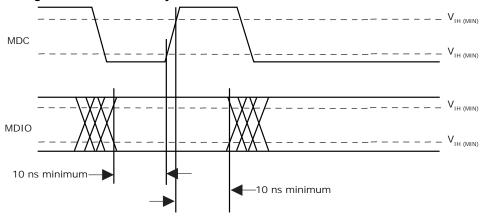

| Figure 25 | Timing with MDIO Sourced by STA                  | 31  |

| Figure 26 | Timing with MDIO Sourced by MMD                  | 31  |

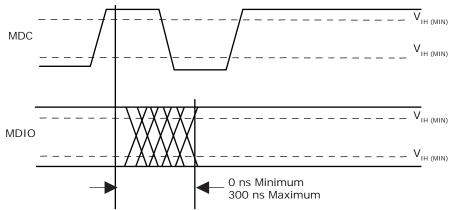

| Figure 27 | SPI Interface Timing                             | 32  |

| Figure 28 | Pin Diagram                                      | 34  |

| Figure 29 | VSC8256-01 Package                               | 44  |

# **Tables**

| Table 1  | Repeater Interface Data Rates                                   | . 5 |

|----------|-----------------------------------------------------------------|-----|

| Table 2  | Selecting LREFCK Frequency                                      | . 6 |

| Table 3  | Line-Side Loopback                                              | . 8 |

| Table 4  | Host-Side Loopback                                              | . 8 |

| Table 5  | MDIO Port Addresses Per Channel                                 |     |

| Table 6  | SPI Slave Instruction Bit Sequence                              |     |

| Table 7  | JTAG Instructions and Register Codes                            | 17  |

| Table 8  | LVTTL Input and Push/Pull Output DC Characteristics             | 22  |

| Table 9  | LVTTLOD Input and Open-Drain Output DC Characteristics          | 22  |

| Table 10 | Reference Clock DC Characteristics                              | 23  |

| Table 11 | Host- and Line-Side 10G Receiver Input (SFI Point D)            | 23  |

| Table 12 | Host- and Line-Side 10G Receiver Input (SFI Point C")           | 24  |

| Table 13 | Host- and Line-Side SONET 10G Input Jitter                      | 25  |

| Table 14 | Host- and Line-Side 1.25 Gbps SFI Input                         | 25  |

| Table 15 | Host- and Line-Side 10G Transmitter Output (SFI Point A)        | 26  |

| Table 16 | Host- and Line-Side 10G Transmitter Output (SFI Point B)        | 26  |

| Table 17 | Transmitter SFP+ Direct Attach Copper Output AC Characteristics | 27  |

| Table 18 | 10 Gbps Transmitter 10GBASE-KR AC Characteristics               |     |

| Table 19 | Host- and Line-Side Optical 10G Output Jitter                   | 28  |

| Table 20 | Host- and Line-Side 1.25 Gbps SFI Output                        | 28  |

| Table 21 | Reference Clock AC Characteristics                              | 28  |

| Table 22 | Two-Wire Serial Interface AC Characteristics                    | 29  |

| Table 23 | MDIO Interface AC Characteristics                               | 30  |

| Table 24 | Clock Output AC Characteristics                                 | 31  |

| Table 25 | SPI Slave Interface AC Characteristics                          | 31  |

| Table 26 | Recommended Operating Conditions                                | 33  |

| Table 27 | Stress Ratings                                                  | 33  |

| Table 28 | Thermal Resistances                                             | 45  |

| Table 29 | Ordering Information                                            | 47  |

### 1 Revision History

This section describes the changes that were implemented in this document. The changes are listed by revision, starting with the most current publication.

### 1.1 **Revision 4.0**

Revision 4.0 was published in February 2018. The following is a summary of the changes in revision 4.0 of this document.

- Host- and line-side 10G receiver input characteristics were updated. For more information, see Table 11, page 23 and Table 12, page 24.

- Host- and line-side 10G transmitter output characteristics were updated. For more information, see Table 15, page 26 and Table 16, page 26.

- 10 Gbps transmitter 10GBASE-KR AC characteristics were updated. For more information, see Table 18, page 27.

- Host- and line-side optical 10G output jitter specifications were updated. For more information, see Table 19, page 28.

- · Recommended operating conditions were updated. For more information, see Table 26, page 33.

### 1.2 **Revision 2.1**

Revision 2.1 was published in January 2018. The following is a summary of the changes in revision 2.1 of this document.

- The two-wire serial slave interface register address illustrations and 24-bit addressing scheme details were updated.

- DC characteristics for low-speed inputs and outputs were updated.

- Receiver and transmitter AC characteristics were updated.

- Reference clock AC characteristics were updated.

- The SPI interface timing diagram was updated.

- · Pin descriptions were updated to correctly reflect device functionality.

### **1.3** Revision 2.0

Revision 2.0 was published in September 2017. It was the first publication of the document.

### 2 Overview

The VSC8256-01 device is part of Microsemi's SynchroPHY™ product family. It is a four channel 1G/10G serial-to-serial, protocol-agnostic repeater/retimer that integrates hardware-based host-side only 10GBASE-KR auto-negotiation and training in a small form factor, low-power FCBGA ideal for a wide array of board-level signal integrity applications.

The VSC8256-01 device provides a complete suite of on-chip instrumentation including built-in self-test (BIST) functions, line-side and client-side circuit loopbacks, pattern generation, and error detection. Its highly flexible clocking options support LAN and WAN operation using a single 156.25 MHz reference clock rate.

The VSC8256-01 device delivers excellent jitter attenuation with low power. It is well-suited for SFP+ based optical modules and direct-attach copper cabling as well as challenging backplane interface applications. As a signal conditioner, it supports protocol-agnostic data rates. It also supports 10 GbE LAN, 10 Gb WAN, 40 GbE (4 x 10G), as well as 1 Gb Ethernet.

### 2.1 Highlights

The following standards are supported by the device, which is programmed to operate as a protocol-agnostic signal conditioner/repeater:

- IEEE Standard 802.3ae-2002, Telecommunications and Information Exchange between Local and Metropolitan Area Networks, 10 Gbps Ethernet over fiber for LAN (10GBASE-SR, -LR, -ER, -LX4) and WAN (10GBASE-SW, -LW, and -EW)

- IEEE Standard 802.3ap-2007, Backplane Ethernet (1 and 10 Gbps over printed circuit boards)

- SFF-INF-8074i MSA for 1GbE SFP, Revision 1.0, 2001

- SFF-INF-8077i MSA for XFP, 2005, Specification for 10 Gbps Small Form Factor 10G Pluggable (XFP) Module supporting SONET OC-192 and G.709 (OTU-2), and 10 Gbps Ethernet

- SFF-8431 MSA Specification for SFP+, 2009, High- and Low-speed electrical and management interface specifications for enhanced Small Form Factor Pluggable modules and hosts

Data rates supported include:

- Ethernet 10.3125 Gbps, Ethernet 9.95328 Gbps, and Ethernet 1.25 Gbps

- OTN OTU2 (10.709 Gbps), OTU1e (11.049 Gbps), and OTU2e (11.095 Gbps)

- Support for SFP+ I/O and auto-negotiation and training for 10GBASE-KR (IEEE 802.3-2012) backplanes

### 2.2 Interfaces

The VSC8256-01 device provides multiple types of interfaces supporting IEEE 802.3ae and IEEE 802.3ap Ethernet connections with hardware-based 10GBASE-KR auto-negotiation and training.

The device meets the 1 GbE SFP and SFP+ SR/LR/ER/ZR host requirements in accordance with the SFF MSA specifications and compensates for optical impairments in SFP+ applications and degradations of the PCB.

The high-speed serial input receiver compensates for loss of optical and copper media performance or margin due to inter-symbol interference (ISI). The high-speed serial transmit output features a 3-tap FIR filter output buffer fully compliant with the 10GBASE-KR standard to provide full 10GBASE-KR support, including 10GBASE-KR state machine, for auto-negotiation and link optimization. The transmit path incorporates a multitap output driver to provide flexibility to meet the demanding 10GBASE-KR (IEEE 802.3ap) Tx output launch requirements.

The serial ports support 1.25 Gbps and 10 Gbps modes. Each channel consists of a receiver (Rx) and a transmitter (Tx) subsection. Programmable reference clock inputs (HREFCK and LREFCK) support the modes along with clock and data recovery (CDR) in the Rx and Tx subsections of all channels. Each channel of the device can be in a different mode within the limitations of the available reference clocks, while ensuring the Rx and Tx subsections within a channel are in the same mode.

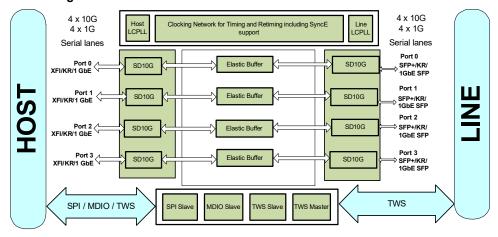

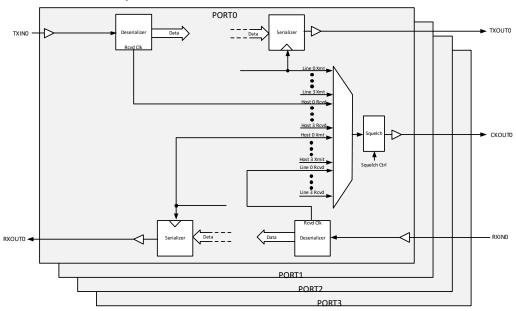

The following illustration shows a high-level block diagram.

Figure 1 • Block Diagram

### 2.3 Features

The main features of the VSC8256-01 device include:

- Support for protocol-agnostic repeater operation (jitter clean-up) at very low latency and power consumption

- Compliant with IEEE 802.3ae and SFF-8431 electrical (SFI) specifications

- Support for 9.95 Gbps WAN, 10.3125 Gbps LAN, and 1.25 Gbps Ethernet

- Support for standard SFP+ applications

- Support for 10GBASE-KR (IEEE 802.3ap) for 10G backplanes

- Support for ITU-T recommendation G.709 (OTN) OTU2, OTU1e, and OTU2e line rates

- Adaptive equalization receiver and programmable multitap transmitter pre-emphasis

- SPI (preferred), MDIO, and two-wire serial slave management interfaces

- VScope™ input signal monitoring integrated circuitry

- Host-side and line-side loopbacks with BIST functions

- Programmable analog signal, invert, amplitude, slew, pre-emphasis, and equalization

- Flexible clocking options

- Passive copper cable support for lowest connectivity cost

### 2.4 Applications

Target applications for the VSC8256-01 device include switching, IP edge router connectivity, rack mount connectivity through backplane, fiber and copper cable connectivity, and standalone server access (in LAN on motherboard designs or separate network adapters).

- · Multi-port serial-to-serial signal conditioning

- 10GBASE-KR-compliant backplane transceivers

- Multi-port XFI/10GBASE-KR to SFI/SFP+ 10 GbE switch cards, router cards, and network adapters

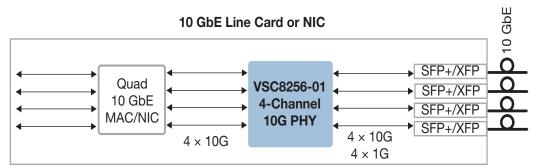

The following figures illustrate various device applications.

Figure 2 • SFP+ Transceiver

Figure 3 • Backplane Equalization Application

# 3 Functional Descriptions

This section includes a functional block diagram, information on the operating modes, and descriptions of the major functional blocks of the VSC8256-01 device.

### 3.1 Data Path Overview

VSC8256-01 supports a protocol agnostic Ethernet-bypass mode.

Ingress and egress data flow is relative to the line-side interface.

Both the host-side and the line-side interfaces are 10G SFI, 10GBASE-KR, or SGMII. Each lane has the following main sections.

- Line and host PMA: The PMA section contains the high speed serial I/O interfaces, an input

equalization circuit, a 10GBASE-KR compliant output buffer and a SerDes. Additionally, the PMAs

also generate all the clocks.

- 10GBASE-KR: Supports 10GBASE-KR training and auto-negotiation. The 10GBASE-KR driver includes programmable equalization accomplished by a three-tap finite impulse response (FIR) structure (IEEE 802.3ap compliant). Three-tap delays are achieved by three flip-flops clocked by the high speed serial clock (10G in 10G mode, 1 GHz in 1G mode). 10GBASE-KR auto-negotiation is supported on either the line side or the host side, but not both sides simultaneously.

- Loopbacks: Includes both system and network loopbacks to enhance engineering debugging and manufacturing testing capability.

- Management: Contains status and configuration registers, and the serial management interface logic to access them.

### 3.1.1 Ingress and Egress Operation

The VSC8256-01 can be defined as a protocol-agnostic repeater. Data is received by the line-side interface (SFP+/1 GbE), deserialized, and passed to the host-side serializer through an elastic buffer that absorbs phase jitter/wander. In this mode, the transmit (serializer) clock is required to be synchronous to the incoming recovered clock. A digital synchronization block with filtering capabilities down to the khz range is used to align the receive and transmit clocks. As a result, the input jitter is filtered completely. Each direction (ingress and egress) is identical.

The following table lists the interface data rates for the device's Ethernet mode.

Table 1 • Repeater Interface Data Rates

| Operating Mode | Line-side Data Rate (Gbps) | Host-Side Interface | Host-Side Data Rate (Gbps) |

|----------------|----------------------------|---------------------|----------------------------|

| 10G LAN        | 1 x 10.3125                | 10G LAN             | 1 x 10.3125                |

| 1 GbE          | 1 x 1.25                   | 1 GbE               | 1 x 1.25                   |

| 10G OTU2       | 1 x 10.709                 | OTU2                | 1 x 10.709                 |

| 10G OTU1e      | 1 x 11.049                 | OTU1e               | 1 x 11.049                 |

| 10G OTU2e      | 1 x 11.095                 | OTU2e               | 1 x 11.095                 |

### 3.2 Physical Media Attachment (PMA)

The PMA section consists of receiver (Rx) and transmitter (Tx) subsections. The receiver accepts data from the serial data input RXIN and sends the parallel data to the elastic buffer. A data rate clock also accompanies the parallel data. The transmitter accepts parallel data from the elastic buffer and transmits at serial data output TXOUT. A loopback at the data path is also provided to connect the Rx and the Tx subsections.

To support different data rates, each PMA contains a flexible frequency synthesizer that generates the necessary clocks. The PMA also has four fully programmable clock outputs, CKOUT[0:3], that may be used to output various clock domains from the PMA.

### 3.2.1 Reference Clock

The VSC8256-01 device uses differential input CML level reference clocks. LREFCK and HREFCK are required at all times and have to be synchronous. They may be 125 MHz or 156.25 MHz. This rate must be selected at power-up using the MODE[1:0] pins. LREFCK and HREFCK are multiplied to generate the reference clocks for all the SerDes blocks in the line and host-side interfaces respectively.

The following table shows the MODE pin settings for the various LREFCK frequencies.

Table 2 • Selecting LREFCK Frequency

| MODE1 Pin | MODE0 Pin | Frequency            |

|-----------|-----------|----------------------|

| 0         | 0         | 156.25 MHz (default) |

| 1         | 0         | 125 MHz              |

### 3.2.2 VScope™ Input Signal Monitoring Integrated Circuit

The VScope™ input signal monitoring integrated circuit displays the input signal before it is digitized by the CDR. The two primary configurations are as follows:

- Unity Gain Amplifier monitors the 10 Gbps input signals before signal processing and equalization.

VScope input signal monitoring integrated circuit acts as a virtual scope to effectively observe the received data signal before it has been processed. The autonomous adaptive filter taps must first be disabled and the front-end receiver must be set for operation as a linear, unity gain amplifier. In this mode, all DFE taps are set to zero. This mode does not require an adaptive algorithm.

- Link Monitor provides the link margin. VScope input signal monitoring integrated circuit enables

design engineers and system developers to monitor signals remotely without disrupting the data

integrity of a live data path. By monitoring the health of a given link, optical or electrical, various

types of signal degradation can be identified and corrected.

**Note:** The VScope input signal monitoring integrated circuit feature is only available in the 10G operation mode.

### 3.2.3 10GBASE-KR

The VSC8256-01 device implements the 10GBASE-KR standard in hardware with no additional firmware requirement for 10GBASE-KR backplane rate auto-negotiation and link training per IEEE 802.3 clause 72 and 73. The 10GBASE-KR output driver itself may be used outside the 10GBASE-KR backplane application and is set by programming the registers.

### 3.2.3.1 Rate Auto-Negotiation

The VSC8256-01 device supports auto-detection between 1.25 Gbps and 10.3125 Gbps data rates, according to the IEEE 802.3ap Clause 73. The auto-negotiation/auto-detection feature switches the CRU rate selection to different rates.

Rate auto-negotiation enables devices at both ends of a link segment to advertise abilities, acknowledge receipt, and discover the common modes of operation that both devices share, and to reject the use of operational modes that are not shared by both devices. Where more than one common mode exists between the two devices, a mechanism is provided to allow the devices to resolve to a single mode of operation using a predetermined priority resolution function. The auto-negotiation function allows the devices to switch between the various operational modes in an orderly fashion, permits management to disable or enable the auto-negotiation function, and allows management to select a specific operational mode. The auto-negotiation function also provides a parallel detection function to allow backplane Ethernet devices to connect to other backplane Ethernet devices that have auto-negotiation disabled and interoperate with legacy devices that do not support Clause 73 Auto-Negotiation.

### **3.2.3.2** Training

The purpose of training is to establish optimal settings for the VSC8256-01 device and the link partner. For more information about the training function, see IEEE 802.3ap Clause 72.

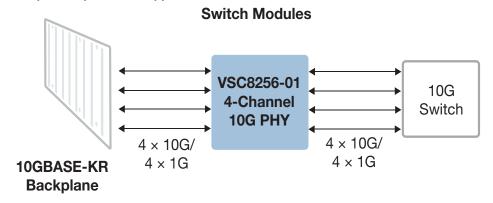

### 3.2.3.3 Output Driver

The high-speed output driver includes programmable equalization accomplished by a three-tap finite impulse response (FIR) structure. The three-tap delays are achieved by three flip-flops clocked by a high-speed serial clock, as shown in the following illustration. Coefficients C(–1), C(0), and C(+1) adjust the pre-cursor, main-cursor, and post-cursor of the output waveform. The three delayed data streams, after being properly strength adjusted by their coefficients, are summed by a summing amplifier. The output driver meets the requirements defined in IEEE 802.3ap Clause 72.

Figure 4 • 10GBASE-KR Output Driver

The final output stage has 50  $\Omega$  back-termination with inductor peaking. The output slew rate is controlled by adjusting the effectiveness of the inductors.

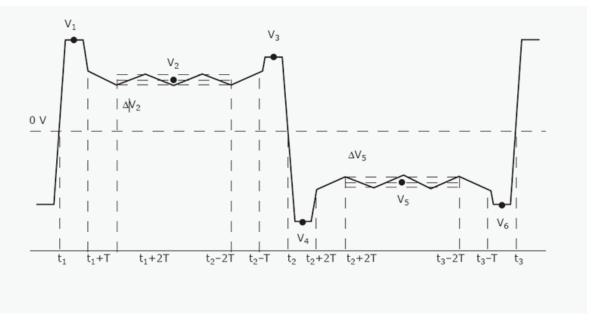

The test pattern for the transmitter output waveform is the square wave test pattern with at least eight consecutive 1s. The following illustration shows the transmitter output waveform test, based on voltages V1 through V6,  $\Delta$ V2, and  $\Delta$ V5.

Figure 5 • 10GBASE-KR Test Pattern

The output waveform is manipulated through the state of the coefficient C(-1), C(0), and C(+1).

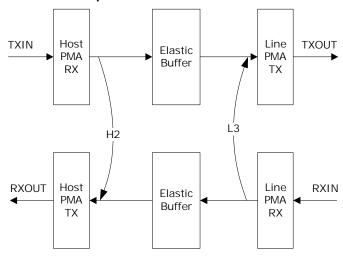

### 3.3 Loopback

The following table shows the name and location of the loopback modes. These modes may be extremely useful for both test and debug purposes.

Table 3 • Line-Side Loopback

| Name | Location                        |

|------|---------------------------------|

| L3   | Line PMA interface (1G and 10G) |

Table 4 • Host-Side Loopback

| Name | Location                        |

|------|---------------------------------|

| H2   | Host PMA interface (1G and 10G) |

The following illustration shows the host and line-side loopbacks.

Figure 6 • Host-Side and Line-Side Loopbacks

### 3.4 Elastic Buffer

The transmit clock on each side is synchronized to the recovered clock on the opposite side through a low-pass filter. A small, elastic buffer in each direction in each channel is added to compensate for the inherent phase variation between these two clocks.

### 3.5 Host-Side Interface

The host interface of VSC8256-01 consists of the same PMA block utilized on the line side. This interface has the same capabilities and feature set as the line side PMA discussed earlier.

### 3.5.1 Output Clocks

Four output clocks (CKOUT[0:3]) are available to drive legacy optics or any other purpose. Each output clock can be independently configured to source any of the recovered clocks or transmit clocks.

The following illustration shows the per-port clock outputs.

Figure 7 • Per-Port Clock Outputs

The rate of these clocks is the line rate divided by 32 or 64 (322.27 MHz or 161.13 MHz in 10G LAN mode, for example).

# 3.6 Table 2, page 6 Table 2, page 6 Management Interfaces

This section contains information about the low-speed serial interfaces of the VSC8256-01 device. The primary control and monitor interfaces in the design are as follows:

- MDIO

- SPI slave

- Two-wire serial (slave)

- Two-wire serial (master)

- GPIO

- JTAG

The VSC8256-01 device supports three different interfaces for accessing status and configuration registers: MDIO, SPI slave, and two-wire serial slave. Only one of the interfaces can be active at a time. The VSC8256-01 device doesn't arbitrate between these interfaces. Users must exercise caution and ensure that multiple interfaces are not active at the same time.

The SPI slave interface is the recommended interface for accessing the status and configuration registers

The VSC8256-01 device registers are arranged according to the MDIO devices as defined in IEEE 802.3 clause 45, as shown in the following list:

- · Device 1: Line PMA and line interface registers

- Device 4: Rate compensating registers

- Device 7: Line 10GBASE-KR registers

- Device 9: Host PMA and host interface registers

- Device F: Host 10GBASE-KR registers

- Device 1E: Global, SFP+, PLLs, GPIOs

### 3.6.1 MDIO Interface

The MDIO interface in the VSC8256-01 device complies with IEEE 802.3ae Clause 45. For more information, see the IEEE standard. The MDIO management interface consists of a bi-directional data path (MDIO) and a clock reference (MDC).

MDIO instructions can be used to read registers, write registers, and perform post-read-increment-address instructions. Due to its slow bandwidth and high latency, the MDIO interface is not recommended as the only interface to access the VSC8256-01 device.

**Note:** The maximum data rate of the MDIO interface is 2.5 Mbps.

The PADDR[4:2] pins select the MDIO port addresses to which the VSC8256-01 device will respond. A single VSC8256-01 device requires the use of four MDIO port addresses, one for each channel. The port address transmitted in MDIO read/write commands to access registers in a particular VSC8256-01 channel is shown in the following table. The port address is a function of the PADDR pins and a pre-programmed number indicating the channel number. Up to eight VSC8256-01 devices can be controlled by a single MDIO host.

Table 5 • MDIO Port Addresses Per Channel

| Channel Number | Channel's Port Address |  |

|----------------|------------------------|--|

| 3              | {PADDR[4:2], 11}       |  |

| 2              | {PADDR[4:2], 10}       |  |

| 1              | {PADDR[4:2], 01}       |  |

| 0              | {PADDR[4:2], 00}       |  |

### 3.6.1.1 Accessing 32-Bit Data Registers

Even though the MDIO interface is defined to access 16-bit data registers, 32-bit configuration and status registers are present in the line and host MACs in 1G mode and line-side SerDes. Use the following steps when accessing registers in 32-bit blocks.

### 3.6.1.1.1 Write to 32-Bit Register

- 1. Issue address instruction specifying the MDIO address for bits [31:16].

- 2. Issue write instruction to write data to register bits [31:16].

- 3. Issue address instruction specifying the MDIO address for bits [15:0].

- 4. Issue write instruction to write data to register bits [15:0].

**Note:** Writing to the two halves of the 32-bit register in the opposite order is not permitted. Nor is it possible to write to only one-half of the register. All four MDIO instructions must be issued to write to a 32-bit register.

### 3.6.1.1.2 Read 32-Bit Register

- 1. Issue address instruction specifying the MDIO address for bits [15:0].

- 2. Issue read-increment instruction. The data read is the contents of register bits [15:0].

- 3. Issue read instruction. The data read is the contents of register bits [31:16].

**Note:** Perform all three steps to read a 32-bit register even when reading consecutive addresses. Issuing back-to-back read-increment instructions to read consecutive 32-bit register addresses is not supported.

Register addresses listed for the line and host MACs and SerDes apply to the SPI slave and two-wire serial slave interfaces, which support direct access to 32-bit data registers. There are two MDIO addresses for each of these 32-bit data registers: one address to access data bits [31:16] and one address to access data bits [15:0]. Contact Microsemi for support using the MDIO interface to access line and host MACs and SerDes registers.

### 3.6.2 SPI Slave Interface

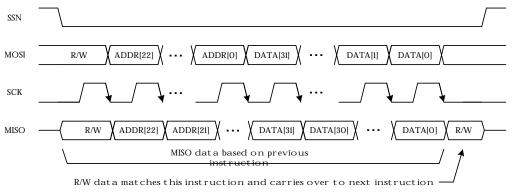

The VSC8256-01 device supports the serial peripheral interface (SPI) for reading and writing registers for high bandwidth tasks. The SPI interface is also capable of accessing all status and configuration registers. The SPI slave port consists of a clock input (SCK), data input (MOSI), data output (MISO), and slave select input (SSN).

**Note:** The SPI slave interface is the recommended interface to access status and configuration registers for the rest of the device.

Drive the SSN pin low to enable the interface. The interface is disabled when SSN is high and MISO is placed into a high impedance state. The VSC8256-01 device captures the state of the MOSI pin on the rising edge of SCK. 56 data bits are captured on the MOSI pin and transmitted on the MISO pin for each SPI instruction. The serial data bits consist of 1 read/write command bit, 23 address bits, and 32 register data bits.

The 23-bit addressing scheme consists of a 2-bit channel number, a 5-bit MDIO device number, and a 16-bit register number. For example, the 23-bit register address for accessing the GPIO\_0\_Config\_Status register in channel 1 (device number is 0x1E and register number is 0x0100) is 0x3E0100. The notion of device number conforms to MDIO register groupings. For example, device 1 is assigned to WIS registers.

The following table shows the order in which the bits are transferred on the interface. Bit 55 is transferred first, and bit 0 is transferred last. This sequence applies to both the MOSI and MISO pins.

Table 6 • SPI Slave Instruction Bit Sequence

| Bit | Name       | Description         |

|-----|------------|---------------------|

| 55  | Read/Write | 0: Read<br>1: Write |

Table 6 • SPI Slave Instruction Bit Sequence (continued)

| Bit   | Name                | Description                                                                                                     |

|-------|---------------------|-----------------------------------------------------------------------------------------------------------------|

| 54:53 | Port/Channel Number | 00: Port/Channel 0<br>01: Port/Channel 1<br>10: Port/Channel 2<br>11: Port/Channel 3                            |

| 52:48 | Device Number       | 5-bit device number Bit 4 corresponds to SPI instruction bit 52 Bit 0 corresponds to SPI instruction bit 48     |

| 47:32 | Register Number     | 16-bit register number Bit 15 corresponds to SPI instruction bit 47 Bit 0 corresponds to SPI instruction bit 32 |

| 31:0  | Data                | 32-bit data Bit 31 corresponds to SPI instruction bit 31 Bit 0 corresponds to SPI instruction bit 0             |

The register data received on the MOSI pin during a write operation is the data value to be written to a VSC8256-01 register. Register data received on the MOSI pin during a read operation is not used, but must still be delivered to the device.

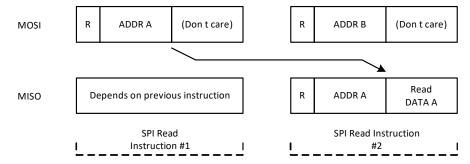

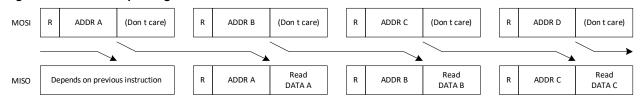

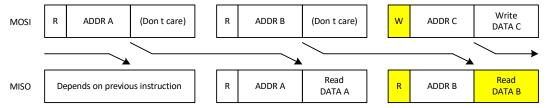

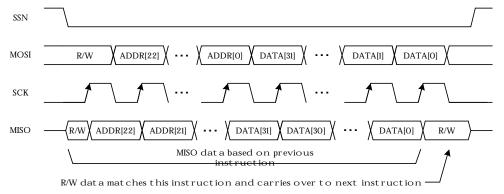

The VSC8256-01 device SPI slave has a pipelined read process. Two read instructions must be sent to read a single register. The first read instruction identifies the register address to be read. The MISO data transmitted on the second read instruction contains the register contents from the address specified in the first instruction. While a pipelined read implementation is not the most efficient use of bandwidth to read a single register, it is very efficient when performing multiple back-to-back reads. The second read instruction contains the address for the second register to be read plus the data read from the first register. The third read instruction contains the address for the third register to be read plus the data read from the second register. Register reads can continue in this fashion indefinitely. The following illustrations show the situations where back-to-back read instructions are issued.

Figure 8 • SPI Single Register Read

Figure 9 • SPI Multiple Register Reads

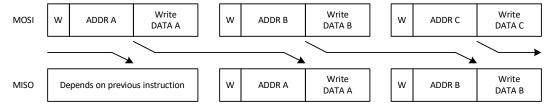

The SPI read instruction figures also point out the read/write state and address bits on the MISO output match the information received in the previous instruction. The SPI master could use this data to verify the device captured the previous instruction properly, or simply ignore the data. The following illustration shows the MISO output during write instructions reporting the previous instruction's read/write state, address, and register write data.

Figure 10 • SPI Multiple Register Writes

The following illustration shows that when a read instruction follows a write instruction, the MISO data during the read instruction is the data field from the previous write.

Figure 11 • SPI Read Following Write

The following illustration shows that when a write instruction followings a read instruction, the MISO data during the write instruction is not pipelined read data. MISO contains all 0's in the data field.

Figure 12 • SPI Write Following Read

Some VSC8256-01 registers are made up of less than 32 data bits. Any bits not defined for a register will return a 0 when the register is read. Reading an invalid register address will return 0x0.

There is one hazard condition to be aware of when issuing two read instructions to read a single clear-on-read register. Issuing two read instructions internally fetches data twice even though valid read data is present only in the second instruction. Fetching data also resets a clear-on-read register. The address specified in the second read instruction should be something other than the clear-on-read register address. This prevents an event causing register re-assertion occurring between the two read instructions from being cleared and never detected. The address in the second instruction can be any register not having a clear-on-read function. Device\_ID is one example. The same address can be used in each read instruction when continuously polling a clear-on-read register. This works because subsequently fetched data is transmitted from the interface allowing assertion between reads to be detected. Only the last read instruction where fetched data is not transmitted should some other address in the instruction be used.

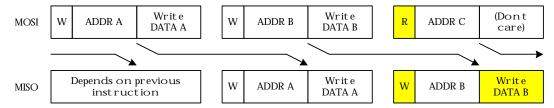

### 3.6.2.1 MISO Output Timing Modes

MISO changes state when SCK transitions from high to low in the default SPI operating mode. This aids in meeting hold time at the SPI master assuming the master captures the data on the rising SCK edge. The SPI port can run up to a maximum of 30 Mbps depending upon the VSC8256-01 device SCK-to-MISO timing, MISO loading SCK duty cycle, the board layout, and the external SPI master's interface timing requirements. For more information about SPI timing, see Table 25, page 31.

The SPI slave port has an alternate operating mode that allows the interface to run faster. Setting register bit SPI\_CTRL.FAST\_MODE=1 configures the SPI slave such that MISO changes state when SCK transitions from low to high. Thus, data is both transmitted from the SPI slave and captured by the SPI master on a rising SCK edge. The interface can run faster in this mode by using the entire SCK clock period instead of half the period to transfer data from the slave to the master. Care must be taken to

ensure the SPI master's hold time requirement is met. The following illustrations show MISO timing in the default and slave modes.

Figure 13 • SPI Slave Default Mode

Figure 14 • SPI Slave Fast Mode

MISO output timing is the only difference between the two SPI modes. Sampling of MOSI on the rising SCK clock edge remains the same so writing to the VSC8256-01 device registers is identical in both modes. Thus the SPI\_CTRL.FAST\_MODE register setting may be modified using the SPI slave port to change the port's MISO output timing.

### 3.6.3 Two-Wire Serial (Slave) Interface

The VSC8256-01 device registers may be read and written using a two-wire serial slave interface. The two-wire serial slave SCL and SDA pins are multifunction general purpose I/O (GPIO) pins, GPIO\_33 and GPIO\_32, respectively. The GPIO pins are configured to serve SCL and SDA functions following device reset.

The slave address assigned to the VSC8256-01 device. is a function of four fixed values and the MDIO port address pins. The 7-bit slave address is {1000, PADDR4, PADDR3, PADDR2}. The use of the port address pins allows multiple VSC8256-01 devices to be serviced by a single two-wire serial (master). The maximum data transfer rate for the interface is 400 kbps.

**Note:** The two-wire serial slave interface does not work with two-wire serial masters using 10-bit slave addresses.

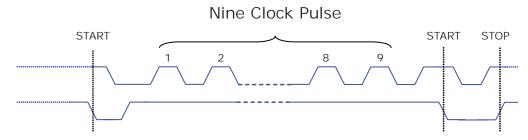

A valid START condition is generated by a two-wire serial master device by transitioning the SDA line from high to low while the SCL line is high. Data is then transferred on the SDA line, most significant bit (MSB) first, with the SCL line clocking data. Data transitions during SCL low periods are valid (read) or latched (write) when SCL pulses high then low. Data transfers are acknowledged (ACK) by the receiving device for data writes and by the master for data reads. An acknowledge is signaled by holding the SDA signal low while pulsing SCL high then low. The master terminates data transfer by generating a STOP condition by transitioning SDA low to high while SCL is high.

**Note:** If the external two-wire serial master device gets out of sync with the two-wire serial slave interface, the master device must issue a bus reset sequence. This puts the two-wire serial slave interface back into a state that allows it to receive future two-wire serial instructions. The external two-wire serial master device and the two-wire serial slave interface can become out-of-sync and freeze the bus if either device is reset during an instruction.

The following illustration shows a two-wire serial bus reset sequence. The reset sequence consists of a START symbol, nine SCK clock pulses while SDA is high, another START symbol, and a STOP symbol.

Figure 15 • Two-Wire Serial Bus Reset Sequence

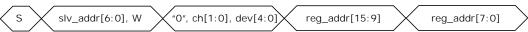

Registers in the VSC8256-01 device are accessed using the 24-bit addressing scheme. The first 8 bits consist of one logic LOW, the channel number (00, 01, 10, 11), and the 5-bit MDIO device number of the register to be accessed. The next 16 bits are the register number. For example, the 24-bit register address for accessing the GPIO\_0\_Config\_Status register in channel 1 (device number 0x1E and register number 0x0100) is 0x3E0100. The notion of device number conforms to MDIO register groupings. For example, device 2 is assigned to WIS registers. The following illustration shows the 24-bit addressing scheme used to access registers.

Figure 16 • Two-Wire Serial Slave Register Address Format

An illegal two-wire serial slave read instruction to an invalid channel number, device number, or register address will return a read value of 0x0000 when the slave address matches this device.

Four bytes of data are transferred on the two-wire serial bus after the address when a register is read or written. Data register bits [31:24] are transferred first, followed by bits [23:16], bits [15:8], and finally bits [7:0]. An ACK symbol is sent between each byte of data. Any bits not defined in a register will return a 0 when the register is read.

The following illustration shows the data transferred on the SDA pin during a register write operation. The R/W bit following the slave address is set to logic low to specify a write operation.

Figure 17 • Two-Wire Serial Write Instruction

The register address to be accessed is specified by initiating a write operation. After the slave address and three register address bytes are sent to the VSC8256-01 device, a START condition must be resent, followed by the slave address with the read/write bit set to logic high. The four-byte data register contents are then transmitted from the VSC8256-01 device. The two-wire serial (master) sends NO ACK after the fourth data byte to indicate it has finished reading data. The following illustration shows data transferred on the SDA pin during a register read operation.

Figure 18 • Two-Wire Serial Read Instruction

The two-wire serial slave interface supports sequential read and sequential write instructions.

### 3.6.4 Two-Wire Serial (Master) Interface

A two-wire serial master interface in the VSC8256-01 channel is available for SFP+/XFP module management. A two-wire serial master interface per channel is required because the slave address in the optics modules are identical. Two-wire serial interface instructions used to access optics module registers are initiated by writing to VSC8256-01 registers. The two-wire serial interface busses are brought out through GPIO pins by configuring the desired GPIO pins to function as SDA and SCL.

The two-wire serial master interface must be configured before initiating any instructions. The slave ID to be transmitted in the first byte of every instruction is selectable in the SLAVE\_ID register. The default setting is 0x50. The interface's data rate is determined by the PRESCALE register. The default data rate is 400 kbps.

The two-wire serial master transmits instructions for slave devices with 8-bit data registers and 256 register addresses per slave ID. Always read register I2C\_BUS\_STATUS.I2C\_BUS\_BUSY or I2C\_READ\_STATUS\_DATA.I2C\_BUS\_BUSY to verify the previous instruction has finished prior to initiating a new instruction. Instructions initiated when the interface is busy will be ignored. Both registers report the same interface busy status. The same busy status is reported in two registers for user convenience.

The two-wire serial master initiates a write instruction when the I2C\_WRITE\_CTRL register is written. The value written to I2C\_WRITE\_CTRL.WRITE\_ADDR is the register address to be modified in the slave device. The value written to I2C\_WRITE\_CTRL.WRITE\_DATA is the data to be written to the slave device's register. The I2C\_BUS\_STATUS register reports the status of the write instruction. I2C\_BUS\_STATUS.I2C\_BUS\_BUSY indicates when the instruction has finished. I2C\_BUS\_STATUS.I2C\_WRITE\_ACK=1 means the two-wire serial master received ACKs from the slave at appropriate times. I2C\_BUS\_STATUS.I2C\_WRITE\_ACK is cleared each time a new instruction is issued. If the two-wire serial master did not receive ACKs from the slave at appropriate times (I2C\_BUS\_STATUS.I2C\_WRITE\_ACK=0), the interface is likely stuck in a state waiting for the ACK. Writing a 1 to the BLOCK\_LEVEL\_RESET1.I2CM\_RESET register will reset the two-wire serial master and release it from its stuck state. The slave device should then be put into a known state by writing any value to the I2C\_RESET\_SEQ register. The two-wire serial master issues a bus reset sequence when this register is written. For more information, see Two-Wire Serial (Slave) Interface, page 14.

The two-wire serial master initiates a read instruction when the I2C\_READ\_ADDR register is written. The value written to I2C\_READ\_ADDR.READ\_ADDR is the register address to be accessed in the slave device. I2C\_READ\_STATUS\_DATA.READ\_DATA contains the data read from the slave device. READ\_DATA is not valid until I2C\_READ\_STATUS\_DATA.I2C\_BUS\_BUSY=0 to indicate the instruction completed. The two-wire serial master does not support read-increment instructions.

### 3.6.5 JTAG

The VSC8256-01 device has an IEEE 1149.1–2001 compliant JTAG interface. The following table shows the supported instructions and corresponding instruction register codes. The code's least significant bit is shifted into TDI first when loading an instruction (the 0 is shifted in first when loading the IDCODE instruction).

| Table 7 • | JIAG | Instructions | and Regi | ster Codes |

|-----------|------|--------------|----------|------------|

| Instruction  | Register Code                           | Notes                                                                                                                                                                                                                                                         |

|--------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IDCODE       | 111111111111111111111111111111111111111 |                                                                                                                                                                                                                                                               |

| BYPASS       | 111111111111111111111111111111111111111 |                                                                                                                                                                                                                                                               |

| EXTEST       | 1111111111111111111101000               |                                                                                                                                                                                                                                                               |

| EXTEST_PULSE | 11111111011111111111101000              |                                                                                                                                                                                                                                                               |

| EXTEST_TRAIN | 11111110111111111111101000              |                                                                                                                                                                                                                                                               |

| SAMPLE       | 1111111111111111111111000               |                                                                                                                                                                                                                                                               |

| PRELOAD      | 1111111111111111111111000               |                                                                                                                                                                                                                                                               |

| LV_HIGHZ     | 11111111111111111111001111              | Provides the ability to place outputs in a high impedance state to facilitate manufacturing test and PC board diagnostics. The SFP+ serial data outputs are not put into the high impedance state when this instruction is loaded in the JTAG TAP controller. |

Table 7 • JTAG Instructions and Register Codes (continued)

| Instruction | Register Code                           | Notes                                                                                                                                    |

|-------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| CLAMP       | 111111111111111111111111111111111111111 | Provides the ability to place all outputs in a predefined state when the scan process is being used to test other devices on a PC board. |

### 3.6.6 General Purpose I/O

The general purpose I/O (GPIO) functions are organized into 2 groups: per-channel functions and global functions. Per-channel functions include an I2C master (often used for communicating with a module), host and line link status indications. Global functions include interrupt generation logic, an I2C slave interface, and other miscellaneous I/O configuration and control.

The 40 pins associated with the GPIO functionality are configurable; any function can be mapped to any GPIO pin. The only restriction is that for each channel, only 8 of the per-channel GPIO output functions may be used at a time.

All GPIOs are configured for open-drain operation, so if used as an output, they must have pull-up resistors connected.

The following block diagram shows the GPIO scheme.

Figure 19 • GPIO Block Diagram

### 3.6.6.1 Inputs

The input state of the GPIO pins can be routed to any of GPIO input functions in each channel, or to any of the global functions. The multiplexors for each of these functions may select any of the GPIOs, or a "0" or "1" to force the function input to a known state.

By default, GPIO32 and GPIO33 are routed to the I2C slave input data and input clock, respectively.

The current state of each GPIO input can be read, and a sticky bit corresponding to each GPIO input indicates if it has changed state. These may be useful for monitoring module status signals such as MOD ABS, TWS INTERRUPT, and so on.

### 3.6.6.2 **Outputs**

A set of eight multiplexors in each channel select the per-channel output functions that are routed out to each of the eight per-channel virtual GPIO outputs. These multiplexors are configured using the configuration/status module in the channel. A second level of multiplexing occurs at the GPIO pin itself, where the individual per-channel virtual outputs, as well as chip level output functions, are associated with a particular GPIO output.

There are additional chip-level functions (such as interrupts) that may also be assigned to a GPIO pin. Each output may also be configured to drive a static low or static high.

All outputs are initially disabled except for GPIO32, which is by default assigned as the I2C slave output data.

### 3.6.6.3 Interrupts and Interrupt Masking

The VSC8256-01 has configurable interrupt generators that can be used to flag error or alarm conditions which can, in turn, be used to prompt external controllers to take action upon certain events. Multiple blocks in a given channel contain these maskable interrupts (including line and host PMAs and rate-adaptation FIFOs). Each of the channel interrupt sources is routed to 2 interrupt generators per channel. For each per-channel interrupt generator, the sources that contribute to that interrupt are independently maskable using channel interrupt enables. Also, the status of each masked interrupt source is always readable in the channel so that the source of the interrupt can be determined quickly. Any GPIO input can be configured to produce an interrupt upon state change.

All the chip-level interrupts, as well as the 8 channel interrupts, are routed to each of 4 aggregate interrupt generators. The source of the interrupts for each aggregator is independently maskable (see note) using global interrupt enables, and the masked status of each interrupt is readable in the global target for quick determination of the source of the interrupt.

**Note:** While there are four interrupt generators, in the case of GPIO input state change detection, there is only one mask shared among all four interrupt aggregators.

Any GPIO may be configured to output the state of any of the 4 interrupts.

The following figure shows an overview of the interrupt blocks.

Figure 20 • Interrupt Scheme

# 4 Electrical Specifications

This section provides the DC characteristics, AC characteristics, recommended operating conditions, and stress ratings for the VSC8256-01 device.

### 4.1 DC Characteristics

This section contains the DC specifications for the VSC8256-01 device.

### 4.1.1 Low-Speed Inputs and Outputs

The following tables list the DC specifications for the LVTTL inputs and outputs for the VSC8256-01 device. LVTTL inputs are  $3.3\ V$  tolerant when VDDTTL is  $2.5\ V$ .

Table 8 • LVTTL Input and Push/Pull Output DC Characteristics

| Parameter                    | Symbol              | Minimum | Maximum            | Unit | Condition                                                     |

|------------------------------|---------------------|---------|--------------------|------|---------------------------------------------------------------|

| Output high voltage, LVTTL   | V <sub>OH_TTL</sub> | 1.8     | $V_{DDTTL}$        | V    | V <sub>DDTTL</sub> = 2.5 V and<br>I <sub>OH</sub> = –4 mA     |

| Output low voltage,<br>LVTTL | V <sub>OL</sub>     |         | 0.5                | V    | $V_{DDTTL}/V_{DDMDIO} = 2.5 V$<br>and $I_{OL} = 4 \text{ mA}$ |

| Input high voltage           | V <sub>IH</sub>     | 1.7     | V <sub>DDTTL</sub> | V    | V <sub>DDTTL</sub> /V <sub>DDMDIO</sub> = 2.5 V               |

| Input low voltage            | $V_{IL}$            |         | 0.8                | V    | V <sub>DDTTL</sub> /V <sub>DDMDIO</sub> = 2.5 V               |

| Input high current           | I <sub>IH</sub>     |         | 500                | μΑ   | $V_{IH} = V_{DDTTL}/V_{DDMDIO}$                               |

| Input low current            | I <sub>IL</sub>     | -100    |                    | μΑ   | V <sub>IL</sub> = 0 V                                         |

Table 9 • LVTTLOD Input and Open-Drain Output DC Characteristics

| Parameter                              | Symbol             | Minimum               | Maximum     | Unit | Condition                                                      |

|----------------------------------------|--------------------|-----------------------|-------------|------|----------------------------------------------------------------|

| Output high voltage, open drain        | V <sub>OH_OD</sub> | See note <sup>1</sup> | $V_{DDTTL}$ | V    | $V_{DDTTL}/V_{DDMDIO} = 2.5 V$<br>and $I_{OH} = -4 \text{ mA}$ |

| Input high leakage current, open drain | I <sub>OZH</sub>   |                       | 100         | μА   |                                                                |

| Output low voltage (open drain)        | V <sub>OL</sub>    |                       | 0.5         | V    | $V_{DDTTL}/V_{DDMDIO} = 2.5 V$<br>and $I_{OL} = 4 \text{ mA}$  |

| Input high voltage                     | V <sub>IH</sub>    | 1.7                   | $V_{DDTTL}$ | V    | V <sub>DDTTL</sub> /V <sub>DDMDIO</sub> = 2.5 V                |

| Input low voltage                      | $V_{IL}$           |                       | 0.8         | V    | $V_{DDTTL}/V_{DDMDIO} = 2.5 V$                                 |

| Input high current                     | I <sub>IH</sub>    |                       | 500         | μΑ   | $V_{IH} = V_{DDTTL}/V_{DDMDIO}$                                |

| Input low current                      | I <sub>IL</sub>    | -100                  |             | μΑ   | V <sub>IL</sub> = 0 V                                          |

Determined by the loading current of the other devices connecting to this pin, the I<sub>OZH</sub> current of this pin, and the value of the pull-up resistor used.

### 4.1.2 Reference Clock

The following table lists the DC specifications for the reference clock for the VSC8256-01 device.

Table 10 • Reference Clock DC Characteristics

| Parameter                                                 | Symbol                     | Minimum | Maximum | Unit              | Condition                          |

|-----------------------------------------------------------|----------------------------|---------|---------|-------------------|------------------------------------|

| HREFCK/LREFCK differential input swing, high <sup>1</sup> | $\Delta V_{I\_DIFF\_HIGH}$ | 1100    | 2400    | mV <sub>P-P</sub> | LVPECL<br>reference clock<br>input |

| HREFCK/LREFCK differential input swing, low <sup>1</sup>  | $\Delta V_{I\_DIFF\_LOW}$  | 200     | 1200    | mV <sub>P-P</sub> | CML reference clock input          |

| SREFCK differential input swing                           | $\Delta V_{I\_DIFF}$       | 200     | 2400    | mV <sub>P-P</sub> |                                    |

<sup>1.</sup> An API call is used to set the input swing to be high or low.

### 4.2 AC Characteristics

This section contains the AC specifications for the VSC8256-01 device. The specifications apply to all channels. All SFI inputs and outputs should be AC-coupled, and should work in differential.

### 4.2.1 Receiver Specifications

The specifications in the following table correspond to line-side 10G receiver input, SFI point D. Point D assumes that the input is from a compliant point C output and a compliant SFI or XFI channel according to the SFP+ standard (SFF-8431) or the XFP multisource agreement (INF-8077i). The measurement is done with a 9 dB channel loss unless stated otherwise.

The SFI and XFI input of the 10G receiver are tested and characterized to support the ITU-T recommendation G.709 (OTN) OTU2, OTU1e, and OTU2e line rates (10.709 Gbps, 11.049 Gbps, and 11.095 Gbps) with a channel loss of 6.5 dB or less.

**Note:** For additional details regarding OTN line rates and the corresponding electrical characteristics, contact your Microsemi representative.

The CDR lock time at the 10G input to the PMA is 5  $\mu$ s, maximum.

Table 11 • Host- and Line-Side 10G Receiver Input (SFI Point D)

| Parameter                                         | Symbol                     | Minimum              | Typical | Maximum                                                | Unit                 | Condition                          |

|---------------------------------------------------|----------------------------|----------------------|---------|--------------------------------------------------------|----------------------|------------------------------------|

| Input data rate                                   |                            | 9.95328 –<br>100 ppm | 10.3125 | 10.3125 +<br>100 ppm                                   | Gbps                 | 10 Gbps LAN/WAN                    |

| Input linear mode differential input data swing   | ΔVRXIN <sub>LINEAR</sub>   | 180                  |         | 600                                                    | mV                   | Voltage modulation amplitude (VMA) |

| Input limiting mode differential input data swing | ΔVRXIN <sub>LIMITING</sub> | 300                  |         | 850                                                    | mV                   | Measured peak-to-peak              |

| Input AC common-mode voltage                      | V <sub>CM</sub>            |                      |         | 15                                                     | ${\sf mV}_{\sf RMS}$ |                                    |

| Differential return loss                          | RL <sub>SDD11</sub>        |                      |         | -12                                                    | dB                   | 0.01 GHz to 2.8 GHz                |

| Differential return loss                          | RL <sub>SDD11</sub>        |                      |         | -8.15 +<br>13.33 x<br>log <sub>10</sub> (f/5.5<br>GHz) | dB                   | 2.8 GHz to 11.1 GHz                |

Table 11 • Host- and Line-Side 10G Receiver Input (SFI Point D) (continued)

| Parameter                                        | Symbol              | Minimum | Typical | Maximum    | Unit | Condition            |

|--------------------------------------------------|---------------------|---------|---------|------------|------|----------------------|

| Reflected differential to common-mode conversion | RL <sub>SCD11</sub> |         |         | <b>–15</b> | dB   | 0.01 GHz to 11.1 GHz |

Table 12 • Host- and Line-Side 10G Receiver Input (SFI Point C")

| Parameter                                              | Symbol                   | Minimum | Typical | Maximum | Unit | Condition                                                                                       |

|--------------------------------------------------------|--------------------------|---------|---------|---------|------|-------------------------------------------------------------------------------------------------|

| 99% jitter                                             | 99% <sub>JIT_p-p</sub>   |         |         | 0.42    | UI   |                                                                                                 |

| Pulse width shrinkage jitter                           | DDPWS <sub>JIT_p-p</sub> |         |         | 0.3     | UI   |                                                                                                 |

| Total jitter tolerance                                 | TOL <sub>JIT_P-P</sub>   |         |         | 0.70    | UI   |                                                                                                 |

| Eye mask X1                                            | X1                       |         |         | 0.35    | UI   |                                                                                                 |

| Eye mask Y1                                            | Y1                       | 150     |         |         | mV   |                                                                                                 |

| Eye mask Y2                                            | Y2                       |         |         | 425     | mV   |                                                                                                 |

| Waveform distortion penalty                            | WDPc                     |         |         | 9.3     | dBe  | BER 1E–12. This parameter of DAC is measured with 7dB SFI channel loss.                         |

| Voltage modulation amplitude                           | VMA                      | 180     |         |         | mV   | BER 1E–12. This parameter of DAC is measured with 7dB SFI channel loss.                         |

| Optical sensitivity (ROP), back-to-back, 10.3 Gbps     | S <sub>B2B</sub>         |         |         | -24     | dBm  | BER 1E–12, PRBS31<br>and 10 GbE frame.<br>5.76 dB SFI channel loss.                             |

| Optical sensitivity (ROP), with fiber plant, 10.3 Gbps | S <sub>FIBER</sub>       |         |         | -21     | dBm  | 95 km single-mode fiber,<br>BER 1E–12, PRBS31<br>and 10 GbE frame.<br>5.76 dB SFI channel loss. |

| Chromatic dispersion penalty                           | F <sub>CDP</sub>         |         |         | 3       | dB   | 1600 ps/nm. 5.76 dB SFI channel loss.                                                           |

| OSNR vs BER with fiber plant, 10.7 Gbps                | OSNR <sub>FEC</sub>      | 16      |         |         | dB   | 95 km single-mode fiber,<br>BER 7E–4, 5.76 dB SFI<br>channel loss.                              |

The following illustration shows the sinusoidal jitter tolerance for the SFI datacom.

Figure 21 • SFI Datacom Sinusoidal Jitter Tolerance

The following table lists the 10G input jitter specifications for the VSC8256-01 device.

Table 13 • Host- and Line-Side SONET 10G Input Jitter

| Parameter                                 | Symbol          | Minimum              | Typical | Maximum              | Unit | Condition                                 |

|-------------------------------------------|-----------------|----------------------|---------|----------------------|------|-------------------------------------------|

| Input data rate, 10 Gbps<br>WAN           |                 | 9.95328 –<br>100 ppm | 9.95328 | 9.95328 +<br>100 ppm | Gbps |                                           |

| Sinusoidal jitter tolerance,<br>9.95 Gbps | SJ <sub>T</sub> | 2x jitter mask       |         |                      |      | GR-253 according to SONET OC-192 standard |

The following table lists the line-side 1.25 Gbps SFI input specifications for the VSC8256-01 device.

Table 14 • Host- and Line-Side 1.25 Gbps SFI Input

| Parameter                      | Symbol               | Minimum           | Typical | Maximum                       | Unit              | Condition                                        |

|--------------------------------|----------------------|-------------------|---------|-------------------------------|-------------------|--------------------------------------------------|

| Input data rate, 1.25 Gbps     |                      | 1.25 –<br>100 ppm | 1.25    | 1.25 +<br>100 ppm             | Gbps              | 1.25 Gbps mode                                   |

| Differential input return loss | RLI <sub>SDD11</sub> |                   |         | -10                           | dB                | 50 MHz to 625 MHz                                |

| Differential input return loss | RLI <sub>SDD11</sub> |                   |         | -10 + 10 x log<br>(f/625 MHz) | dB                | 625 MHz to 1250 MHz                              |

| Total jitter tolerance         | TJ <sub>T</sub>      |                   |         | 0.749                         | UI                | Jitter above 637 kHz<br>(IEEE 802.3 clause 38.5) |

| Deterministic jitter           | DJ                   |                   |         | 0.462                         | UI <sub>P-P</sub> | Jitter above 637 kHz<br>(IEEE 802.3 clause 38.5) |

| Eye mask Y1                    | Y1                   | 125               |         |                               | mV                |                                                  |

| Eye mask Y2                    | Y2                   |                   |         | 600                           | mV                |                                                  |

### 4.2.2 Transmitter Specifications

This section includes the transmitter specifications.

The specifications in the following table correspond to line-side 10G transmitter output, SFI point B. Point B is after a standard-compliant SFI or XFI channel, as defined in the SFP+ standard (SFF-8431) or the XFP multisource agreement (INF-8077i). The measurement is done with a 9 dB channel loss unless stated otherwise.

The SFI and XFI output of the 10G transmitter are tested and characterized to support ITU-T recommendation G.709 (OTN) OTU2, OTU1e, and OTU2e line rates (10.709 Gbps, 11.049 Gbps, and 11.095 Gbps) with a channel loss of 6.5 dB or less.

**Note:** For additional details regarding OTN line rates and the corresponding electrical characteristics, contact your Microsemi representative.

Table 15 • Host- and Line-Side 10G Transmitter Output (SFI Point A)

| Parameter                | Symbol         | Minimum | Maximum                                                | Unit | Condition            |

|--------------------------|----------------|---------|--------------------------------------------------------|------|----------------------|

| Termination mismatch     | $\Delta Z_{M}$ |         | 5                                                      | %    |                      |

| Differential return loss | SDD22          |         | -12                                                    | dB   | 0.01 GHz to 2.8 GHz  |

| Differential return loss | SDD22          |         | -8.15 +<br>13.33 x<br>log <sub>10</sub> (f/5.5<br>GHz) | dB   | 2.8 GHz to 11.1 GHz  |

| Common-mode return loss  | SCC22          |         | <b>-9</b>                                              | dB   | 0.01 GHz to 4.74 GHz |

| Common-mode return loss  | SCC22          |         | -8.15 +<br>13.33 x<br>log <sub>10</sub> (f/5.5<br>GHz) | dB   | 4.74 GHz to 11.1 GHz |

Table 16 • Host- and Line-Side 10G Transmitter Output (SFI Point B)

| Parameter              | Symbol              | Minimum | Maximum | Unit                 | Condition                        |

|------------------------|---------------------|---------|---------|----------------------|----------------------------------|

| AC common-mode voltage | V <sub>OCM_AC</sub> |         | 15      | ${\sf mV}_{\sf RMS}$ |                                  |

| Total jitter           | TJ                  |         | 0.28    | UI                   |                                  |

| Data-dependant jitter  | DDJ                 |         | 0.1     | UI                   |                                  |

| Pulse shrinkage jitter | DDPWS               |         | 0.055   | UI                   |                                  |

| Uncorrelated jitter    | UJ                  |         | 0.023   | UI <sub>RMS</sub>    |                                  |

| Eye mask X1            | X1                  |         | 0.12    | UI                   |                                  |

| Eye mask X2            | X2                  |         | 0.33    | UI                   |                                  |

| Eye mask Y1            | Y1                  | 95      |         | mV                   | Tested at 7 dB SFI channel loss. |

| Eye mask Y2            | Y2                  |         | 350     | mV                   |                                  |

The following illustration shows the compliance mask associated with the Tx SFI transmit differential output.

Figure 22 • SFI Transmit Differential Output Compliance Mask

The following table shows the transmit path output specifications for SFI point B. These DAC parameters are measured with 7 dB SFI channel loss.

Table 17 • Transmitter SFP+ Direct Attach Copper Output AC Characteristics

| Parameter                                                                         | Symbol          | Minimum | Maximum | Unit        | Condition                                                                                      |

|-----------------------------------------------------------------------------------|-----------------|---------|---------|-------------|------------------------------------------------------------------------------------------------|

| SFP+ direct attach<br>copper voltage<br>modulation<br>amplitude, peak-to-<br>peak | V <sub>MA</sub> | 300     |         | mV          | See SFF-8431 section D.7.                                                                      |

| SFP+ direct attach copper transmitter Q <sub>SQ</sub>                             | Q <sub>SQ</sub> | 63.1    |         |             | See SFF-8431 section D.8.                                                                      |

| SFP+ direct attach<br>copper output AC<br>common-mode<br>voltage                  |                 |         | 12      | mV<br>(RMS) | See SFF-8431 section D.15.                                                                     |

| SFP+ direct attach<br>copper output<br>TWDPc                                      | TWDPc           |         | 10.7    | dB          | Electrical output measured using SFF-8431 Appendix G, including copper direct attach stressor. |

The following table shows that the 10 Gbps transmitter operating in 10GBASE-KR mode complies with IEEE 802.3 clause 72.7.

Table 18 • 10 Gbps Transmitter 10GBASE-KR AC Characteristics