## **PANCoordinator-EK Kit User Manual**

# **USER GUIDE**

## Introduction

This PANCoordinator Evaluation Kit (EK) comprises all necessary resources to develop a complete G3-PLC PANCoordinator. It implements an Atmel<sup>®</sup> Cortex<sup>™</sup>-M7 device acting as MCU host, combined with ATPL250A modem for PLC (Power Line Communication). ATPL250A is a power line communications base band transceiver, compliant with the PHY layer of G3-PLC specification.

G3-PLC is a mature, consolidated and worldwide accepted standard for OFDM-based power line communications, with focus on providing Smart Grid services over electricity distribution networks.

This guide describes how to use the kit and get start with it.

## **Contents**

- Welcome letter introducing the evaluation kit and its contents.

- Boards:

- One ATPL250ABNv2 board.

- One ATPLCOUP007v2.5 coupling board (CEN-A frequency band).

- One ATPLCOUP002v2 coupling board (ARIB frequency band).

- One ATPLCOUP006v2 coupling board (FCC frequency band).

- Cables:

- One micro A/B-type USB cable.

- One power cord cable IEC320-C8.

- Jumpers:

- One voltage jumper with pitch 5.08 mm.

- One erase jumper with pitch 2.54mm.

## **Features**

- ATPL250A is a compact and high-efficient device for a wide range of Smart Grid applications such as Smart Metering (Smart Meters and Data Concentrators), Lighting, Industrial/Home Automation, Home and Building Energy Management Systems, Solar Energy and Plug-in Hybrid Electric Vehicle (PHEV) Charging Stations.

- ATPL250A G3-PLC device includes enhanced features such as additional robust modes and frequency band extension.

- ATPL250A has been conceived to be bundled with an external Atmel MCU. ATPL250ABN PAN

Coordinator board mounts the ATPL250A transceiver and a SAME70 ARM Cortex M7

microcontroller. This development board provides a full featured platform to develop a complete

communications system based on Power Line Communication technology, providing support for:

- PLC band characterization.

- Noise level measurement.

- Sensitivity level measurement.

- Maximum reachable distance.

- Power consumption.

- Check PLC performance in different bands (CENELEC, FCC, ARIB) setting different PLC coupling boards (provided with this evaluation kit).

- The EK board can be supplied with universal 115-230 V<sub>AC</sub> 50-60 Hz power input.

- The EK boards include a JTAG interface for MCU debugging and programming purposes, a UART for debugging purposes, as well as Ethernet connectivity.

- Software application examples available based on G3-PLC Stack:

- Atmel provides an Atmel G3-PLC PHY layer library which is used by the external MCU to take control of ATPL250A PHY layer device. Three G3-PLC PHY layer example projects are provided with the kit.

- Atmel G3 Stack (ADP + MAC + PHY) for PAN Coordinator with some user applications is provided with the EK.

# **Table of Contents**

| 1. | Evaluation Kit Specifications |                                                                 |    |

|----|-------------------------------|-----------------------------------------------------------------|----|

|    | 1.1                           | Safety recommendations                                          | 7  |

|    | 1.2                           | Electrical characteristics                                      |    |

| 2. | Eva                           | aluation Kit Overview                                           | 9  |

|    | 2.1                           | Design support                                                  | 9  |

|    | 2.2                           | PANCoordinator-EK contents                                      |    |

| 2  |                               |                                                                 |    |

| 3. |                               | PL250ABN Hardware                                               |    |

|    | 3.1                           | Overview                                                        |    |

|    | 3.2                           | Features Block diagram                                          |    |

| 4. | 3.3                           | Mechanical and user considerations                              |    |

|    | 3.4<br>3.5                    | Hardware description                                            |    |

|    | 3.5                           | 3.5.1 Power supply                                              |    |

|    |                               | 3.5.2 Zero crossing detector                                    |    |

|    |                               | 3.5.3 SAME70Q21 Flash microcontroller                           |    |

|    |                               | 3.5.4 ATPL250A PLC Transceiver                                  |    |

|    |                               | 3.5.5 PLC Coupling                                              |    |

|    |                               | 3.5.6 Peripherals                                               |    |

|    |                               | 3.5.7 Interface Ports                                           |    |

|    |                               |                                                                 |    |

| 4. |                               | PLCOUP007 Hardware                                              |    |

| 4. | 4.1                           | Overview                                                        |    |

|    | 4.2                           | Features                                                        |    |

|    | 4.3                           | Mechanical and user considerations                              |    |

|    | 4.4                           | Hardware description                                            |    |

| 5. | ATI                           | PLCOUP002 Hardware                                              |    |

|    | 5.1                           | Overview                                                        |    |

|    | 5.2                           | Features                                                        |    |

|    | 5.3                           | Mechanical and user considerations                              |    |

|    | 5.4                           | Hardware description                                            | 29 |

| 6. | ATI                           | PLCOUP006 Hardware                                              | 30 |

|    | 6.1                           | Overview                                                        | 30 |

|    | 6.2                           | Features                                                        | 30 |

|    | 6.3                           | Mechanical and user considerations                              | 31 |

|    | 6.4                           | Hardware description                                            | 31 |

| 7. | PA                            | N Coordinator Evaluation Kit: Getting started                   | 32 |

|    | 7.1                           | Introduction to the embedded system                             | 32 |

|    |                               | 7.1.1 IAR Embedded Workbench                                    | 32 |

|    |                               | 7.1.2 Keil µVision                                              | 32 |

|    |                               | 7.1.3 Atmel Studio 6                                            | 32 |

|    |                               | 7.1.4 Atmel SAM-ICE JTAG Probe                                  | 33 |

|    |                               | 7.1.5 J-Link / SAM-ICE JTAG Probe Software & Documentation Pack | 33 |

|    |                               | 7.1.6 Atmel Software Framework (ASF)                            | 35 |

|    | 7.2                           | PLC application example 1 – PHY Tester                          | 36 |

|            |       | 7.2.1   | Atmel PLC PHY Tester tool Installation       | 37 |

|------------|-------|---------|----------------------------------------------|----|

|            |       | 7.2.2   | Supplying the boards                         | 39 |

|            |       | 7.2.3   | USB connection                               | 40 |

|            |       | 7.2.4   | Programming the embedded file                | 41 |

|            |       | 7.2.5   | Running the PLC application example 1        | 43 |

|            | 7.3   | PLC a   | application example 2 – PHY TX Test Console  | 55 |

|            |       | 7.3.1   | Supplying the boards                         | 56 |

|            |       | 7.3.2   | USB connection                               | 56 |

|            |       | 7.3.3   | Programming the embedded file                | 56 |

|            |       | 7.3.4   | Running the PLC application example 2        | 57 |

|            | 7.4   | PLC a   | pplication example 3 – PHY Sniffer           | 61 |

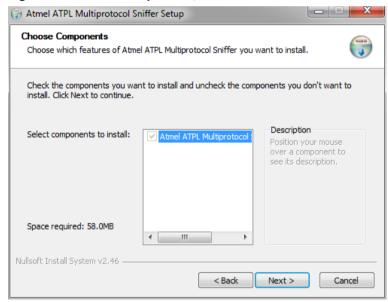

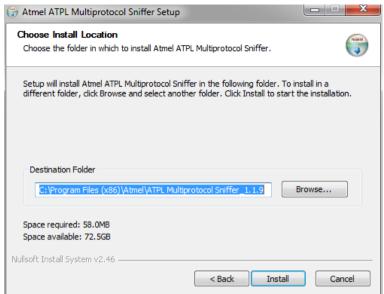

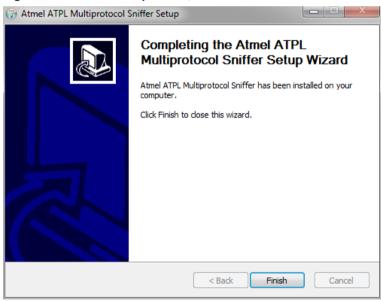

|            |       | 7.4.1   | ATPL Multiprotocol Sniffer tool Installation | 62 |

|            |       | 7.4.2   | Supplying the boards                         | 64 |

|            |       | 7.4.3   | USB connection                               | 64 |

|            |       | 7.4.4   | Programming the embedded files               | 65 |

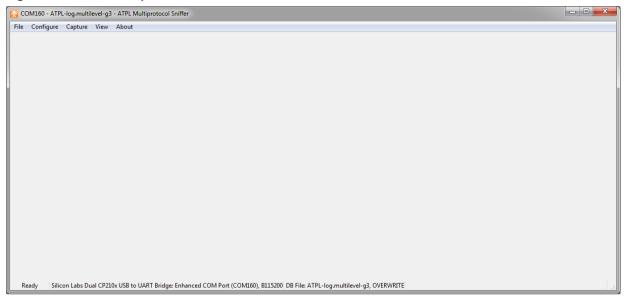

|            |       | 7.4.5   | Running the PLC application example 3        | 65 |

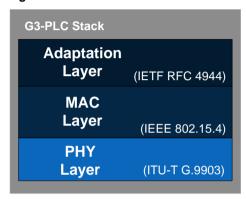

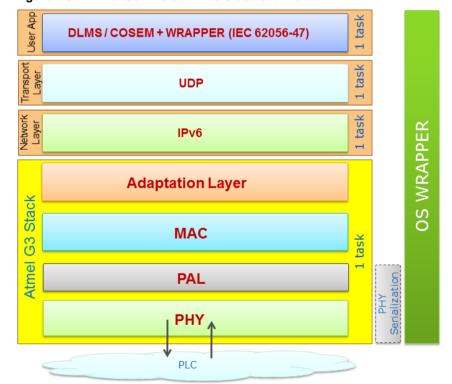

|            | 7.5   | Introdu | uction to G3 Stack                           | 68 |

|            |       | 7.5.1   | FreeRTOS                                     | 68 |

|            |       | 7.5.2   | ASF Integration                              | 69 |

|            |       | 7.5.3   | Atmel G3-PLC Stack Structure                 | 70 |

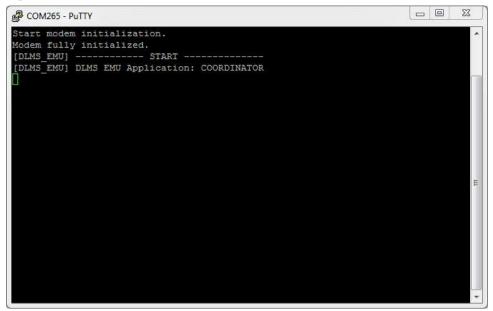

|            | 7.6   | PLC a   | pplication 4 – PLC Network                   | 72 |

|            |       | 7.6.1   | Supplying the boards                         | 72 |

|            |       | 7.6.2   | USB connection                               | 72 |

|            |       | 7.6.3   | Programming the embedded files               | 72 |

|            |       | 7.6.4   | Running the PLC application example 4        | 74 |

| 8.         | Ref   | erenc   | es                                           | 77 |

| Appendix A |       |         | Board schemes                                | 78 |

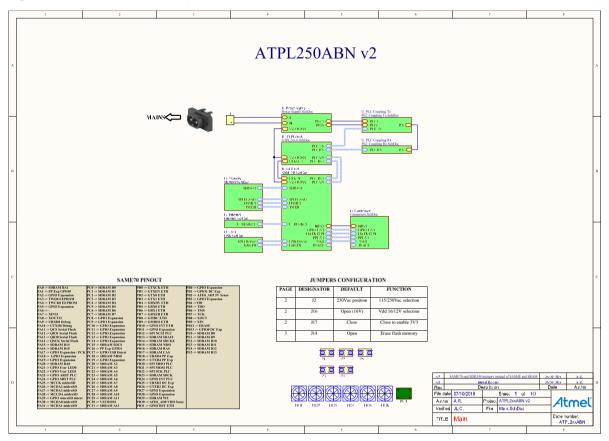

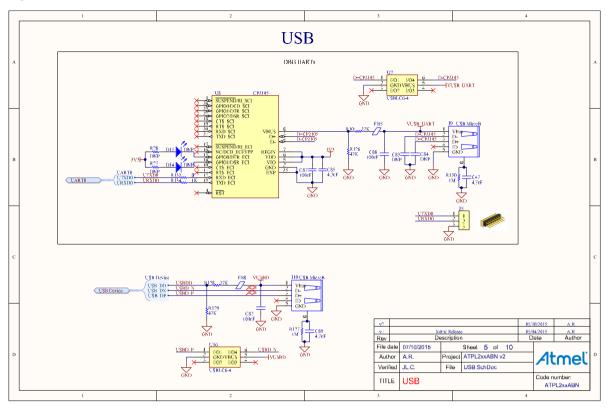

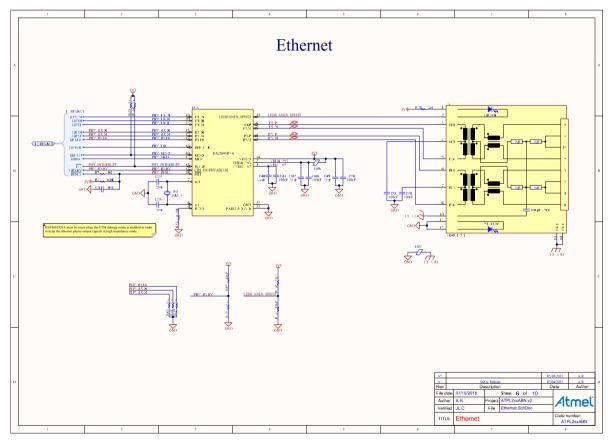

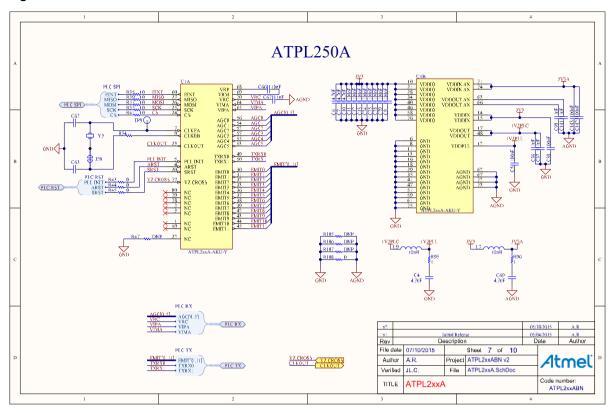

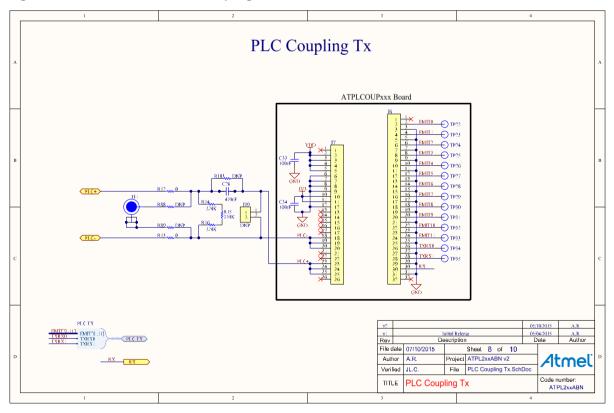

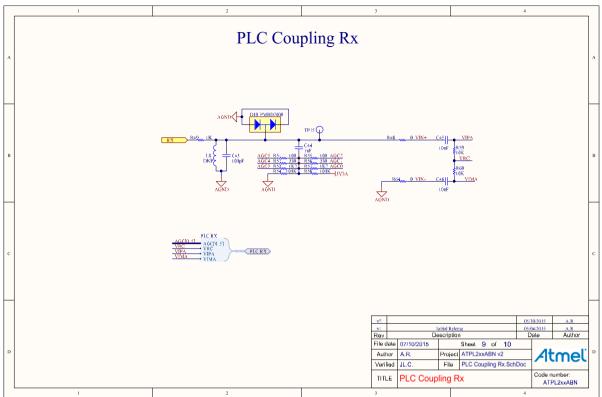

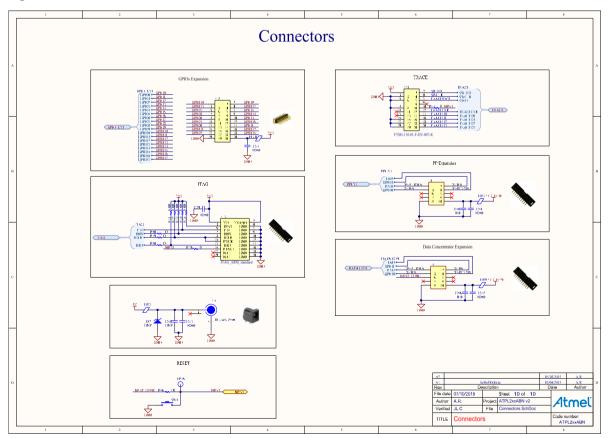

|            | A.1   | ATPL2   | 250ABNv2 Schemes                             | 78 |

|            | A.2   | ATPLO   | COUP007v2.5 schemes                          | 85 |

| D۸         | vicio | n Hist  | orv.                                         | 99 |

# **Icon Key Identifiers**

TIP Useful Tips and Techniques

INFO Delivers Contextual Information About a Specific Topic

IMPORTANT Note to Quality and Performance

TO DO Objectives to be Completed

EXECUTE Actions to be Executed Out of the Target

RESULT The Expected Result of an Assignment Step

CAUTION Procedure Which Can Result in Minor Equipment Damage

WARNING Procedure With Potential Equipment Damage

DANGER Procedure With Imminent Equipment Destruction

# 1. Evaluation Kit Specifications

## 1.1 Safety recommendations

These development boards must be only used by expert technicians. ATPL250ABN is directly powered from mains grid, so hazardous voltage (100/230V<sub>AC</sub>) is present on the board. To avoid user access to dangerous parts, ATPL250ABN must always be used within its enclosure. All required connectors and configuration jumpers are easily accessible without electrical shock risk.

A normal use of ATPL250ABN does not require removing the enclosure cover. If this action is necessary, it must be performed by qualified staff after being sure that mains connection has been previously removed. Be careful it is only for indoor use.

This development board does not have any switch on mains connection to switch on or off it. It must always be connected to an easy accessible mains socket.

Do not connect any probe to high voltage sections if the board is not isolated from the mains supply to avoid damaging of measurement instruments.

Coupling boards' kits are shipped in a protective anti-static package. The boards system must not be subjected to high electrostatic discharge.

We strongly recommend using a grounding strap or similar ESD protective device when handling the board in hostile ESD environments (offices with synthetic carpet, for example) without enclosure. Avoid touching the component pins or any other metallic element on the board.

ATPL250ABN is a CE mark product which passes EN60950-1 safety standard, EN50065-1, EN50065-2-3, EN50065-7 EMC and FCC (as current carrier system) standards. It also satisfies Pb-Free and ROHS directive.

ATMEL does not assume responsibility for the consequences arising from any improper use of this board.

Boards' kits are intended for further engineering, development, demonstration, or evaluation purposes only. It is not a finished product except as may be otherwise noted on the board/kit.

## 1.2 Electrical characteristics

This section shows the electrical characteristics of the kit's boards. See the following tables:

Table 1-1. Power Supply Requirements.

| Parameter              | Condition                                      | Min. | Тур.    | Max.   | Unit            |

|------------------------|------------------------------------------------|------|---------|--------|-----------------|

| AC mains Voltage Range |                                                | 100  | 115/230 | 250    | Vac             |

| Mains Frequency        |                                                |      | 50/60   |        | Hz              |

| Maximum Input Current  |                                                |      |         | 200(1) | mA              |

| Isolation Voltage      | ACDC power supply and PLC coupling transformer |      |         | 3000   | V <sub>AC</sub> |

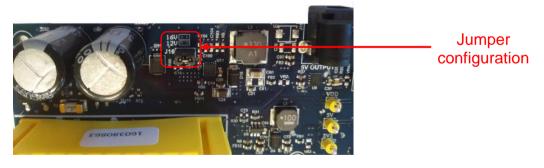

Note that the ATPL250ABN can be supplied either with  $100V_{AC}$  or  $230V_{AC}$  by setting the proper jumpers (pitch = 5.08mm) in the voltage selector, J2, as depicted in the Figure 7-10. By default, voltage jumper is set for  $230V_{AC}$ . For more information about power supply, see section 3.5.1.

Note:

1. This maximum input current is measured in the worst case situation, so that, when board is supplied with a minimum input voltage,100V<sub>AC</sub>, and the worst consumption conditions. That is when it emits against very low impedance in higher frequency band and it is supplying an extra board through the DC jack J15.

Table 1-2. Power Supply Requirements.

| Parameter            | Condition                                                                                                                  | Min. | Тур.                | Max. | Unit |

|----------------------|----------------------------------------------------------------------------------------------------------------------------|------|---------------------|------|------|

| TV Dower Consumption | FW: PHY TX Test Console Application<br>Low Impedance Load (PRIME LISN).<br>Measured on V <sub>DD</sub> (16V) DCDC output.  |      | 3523 <sup>(1)</sup> |      | mW   |

| TX Power Consumption | FW: PHY TX Test Console Application<br>High Impedance Load (CISPR LISN).<br>Measured on V <sub>DD</sub> (16V) DCDC output. |      | 2280 <sup>(1)</sup> |      | mW   |

| RX Power Consumption | Measured on 3.3V LDO output                                                                                                |      | 664 <sup>(1)</sup>  |      | mW   |

Note:

1. These measurements were taken with a non-optimized FW (the PHY TX Test Console project included in the kit with a default configuration in TX mode and RX mode) from a power consumption point of view and they highly depend on the architecture and efficiency of the power supplies. These measurements correspond to the whole PCBA design and not only to ATPL250A and ATSAME70 devices. All PCB peripherals are supplied, i.e. ATPLCOUP007 coupling board emitting in CENELEC-A band. Refer to Atmel ATPL250A and ATSAME70 datasheets for an optimized power consumption measurement result.

## 2. Evaluation Kit Overview

ATPL250ABN is the name of the development board included in this PAN Coordinator EK. It implements an ATPL250A analog front end for PLC, supporting G3-PLC, which has been designed to be controlled by an external Atmel MCU. In this case, Atmel | Smart SAME70 is the device driving ATPL250A PLC analog front end.

This document describes how to start working with the Atmel PANCoordinator-EK. A complete description of PC tools, software examples and hardware are provided in this EK.

## 2.1 Design support

To make it faster and easier for you to evaluate, prototype, develop and program with Atmel products, we offer a variety of design resources, including development tools, software, boards, kits and documentation.

For any technical support request, please refer to our Design Support webpage <a href="http://www.atmel.com/design-support/">http://www.atmel.com/design-support/</a>.

There any user can search the Atmel knowledge base to find tips, help topics, and answers to common questions. In case that the obtained information is not helpful any user can *Open a Support Case* indicating a description of the case, product information, etc.

## 2.2 PANCoordinator-EK contents

PANCoordinator-EK contents –documentation, software and tools- are available online in <a href="https://secure.atmel.com/">https://secure.atmel.com/</a>. To download this information you need a *myAtmel* account, please access to <a href="https://secure.atmel.com/myAtmel">www.atmel.com/myAtmel</a> and create your own account After that, please contact with <a href="plc@atmel.com">plc@atmel.com</a>, specifying your myAtmel user name, your company name and email, and request access to the specific evaluation kit you have acquired. <a href="Please do not hesitate to visit our web site to get the last kit updates">please do not hesitate to visit our web site to get the last kit updates</a>.

myAtmel EK contents are:

- 1. A welcome letter, PANCoordinator-EK\_WL, introducing the EK and its contents.

- 2. PANCoordinator-EK Kit User Manual, doc43106.

- 3. Hardware folder:

- a. ATPL250A datasheet. doc43079.

- b. Hardware application notes: PLC coupling reference designs, crystal selection guidelines, layout recommendations, critical design guidelines, etc.

- c. EK schemes, PCB layouts, gerbers and BOM files of ATPL250ABN, ATPLCOUP002, ATPLCOUP006 and ATPLCOUP007 boards.

## 4. Software folder:

- a. G3\_va.b.c folder, contains five projects for several IDE tools, IAR, Atmel Studio and Keil μVision to work in both frequency bands, CENELEC-A, ARIB and FCC bands, see g3.workspace.same70q21\_atpl250abn\_v2.zip file:

- Apps\_Phy\_Tester\_Tool. This application configures G3-PLC PHY layer and its serial

interface to communicate with Atmel PLC PHY Tester Tool to send and receive PLC

messages from/to the PLC line and check the PLC transmission/reception processes

between ATPL250ABN boards. Atmel PLC PHY Tester tool for PC is available in the

PCTools folder.

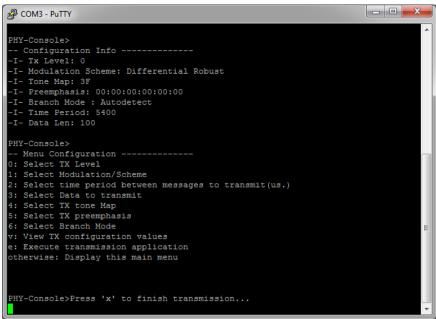

- Apps\_Phy\_Tx\_Test\_Console. This application lets the user to configure a proper set up

to perform both EMC emissions and immunity tests on ATPL250ABN board. These tests

are based on the use of G3 PHY layer with a terminal console firmware that eases the

configuration of several transmission parameters such as modulation, frame data length

and time interval between frames.

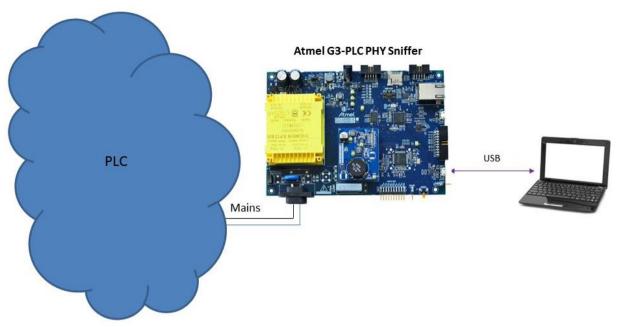

- Apps\_Phy\_Sniffer\_Tool. This application configures G3 PHY layer to monitor the PLC data traffic on ATPL250ABN board and sends via serial communication this traffic to the ATPL Multiprotocol Sniffer tool. This tool can be downloaded from the PCTools folder. Every coupling board is intended to be used in their corresponding frequency bands only. By default, sniffer project is compiled for ATPLCOUP007 board. This means that only G3 CENELEC band-A is supported.

- APPS\_DLMS\_EMU\_COORD\_APP. The DLMS Emulator application is an example using the Atmel G3-PLC stack and show how the G3 API should be used. This application is provided for Coordinator. Application configure the ATPL250ABN board as G3 Coordinator. A Device node is required, it is configured with DLMS Emulation capabilities and simulate the data exchange between the G3 Coordinator and the Device(s). The Device responds dummy DLMS messages after receiving data requests from the Coordinator.

- APPS\_ADP\_MAC\_SERIALIZED\_APP. The ADP and MAC serialization is an application

example that bring you access to the ADP, MAC and Bootstrap API through a serial

connection. This application could be useful for users that want to make intensive test for

the stack or want to run the upper layers in other CPU.

- b. Common software documentation folder. It contains some user guides as the description of the Atmel G3 firmware stack, doc43081. Document describes in detail all layers from the Atmel G3 implementation as well as configuration options provided, target platforms, default architecture and the provided solutions by Atmel.

- c. Evaluation License Agreement document.

#### 5. PCTools folder:

- a. Atmel PLC PHY Tester, PC tool used to monitor point to point PLC transmissions between Atmel boards.

- b. ATPL Multiprotocol Sniffer, PC tool to monitor data traffic in G3-PLC networks using an Atmel board as sniffer.

- c. SAM-ICE™ Drivers. Users may need to install this driver the first time the SAM-ICE is connected to the PC.

- d. USB Drivers (Silicon USB drivers). Users may need to install these drivers the first time the ATPL250ABN board is connected to the host PC by means of a serial USB connection.

We recommend installing the evaluation kit contents in the root C:\ to avoid problems with very long paths.

Unpack and inspect the kit carefully. Contact your local Atmel distributor, should you have any issues concerning the contents of the kit.

The ATPL250ABN board with the ATPLCOUP007 are encapsulated with methacrylate enclosures and shipped in protective anti-static foam. The two coupling boards, ATPLCOUP002 and ATPLCOUP006, are shipped in shielded bags.

The boards must not be subject to high electrostatic discharge. We recommend using a grounding strap or similar ESD protective device when handling the board in hostile ESD environments. Avoid touching the components pins or any other metallic elements on the board.

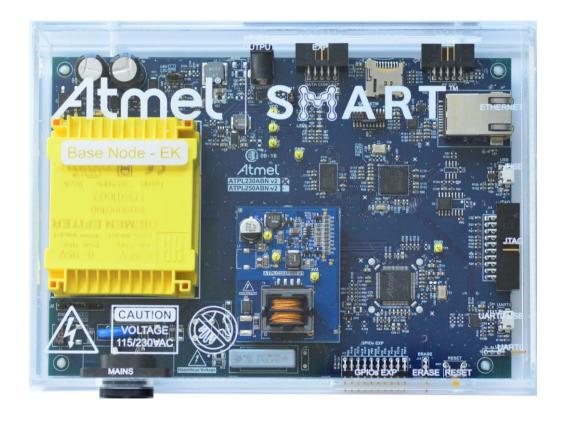

Figure 2-1. Packed Atmel PANCoordinator-EK.

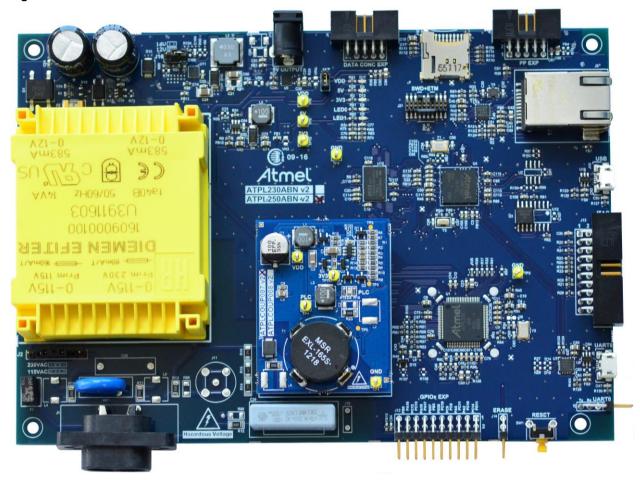

Figure 2-2. ATPL250ABN PAN Coordinator board and with ATPLCOUP007.

ATPL250ABN board is provided with an example application preprogrammed, the G3-PLC PHY Tester project for SAM4E70Q21. After installing the Atmel PLC PHY Tester PC Tool in your PC, users can interface with the device and start exploring its capabilities, for example, checking the point to point PLC transmissions between the two Atmel boards. Please refer to chapter 7.2 for further information.

Take into account that the PANCoordinator-EK provides one coupling board for CENELEC-A band, Figure 2-3, set over the ATPL250ABN board. In addition to the ATPLCOUP007 board, evaluation kit adds one coupling boards for FCC bands, Figure 2-4. And another coupling board for ARIB bands, Figure 2-5.

Depending on the coupling board set in ATPL250ABN board and the PHY configuration parameters selected in the software project you will send and receive PLC messages in the proper PLC band. So that, with ATPLCOUP007 board only lets you send and receive PLC messages in CENELEC-A band. And with ATPLCOUP002 and ATPLCOUP006 board in ARIB or FCC bands respectively.

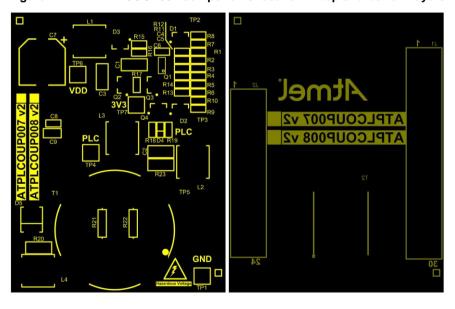

Figure 2-3. ATPLCOUP007 Coupling board.

Figure 2-4. ATPLCOUP002 Coupling board.

Figure 2-5. ATPLCOUP006 Coupling board.

## 3. ATPL250ABN Hardware

## 3.1 Overview

This section summarizes the Atmel ATPL250ABN board design. It introduces system-level concepts, such as power supply, MCU, PLC coupling, memories, peripherals and interface board.

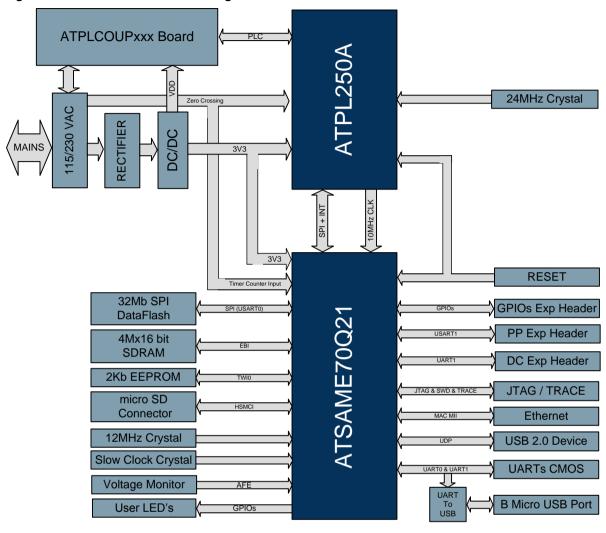

ATPL250ABN is a PAN Coordinator development board based on the ATPL250A, G3-PLC transceiver, and on the SAME70 ARM Cortex M7 microcontroller. ATPL250ABN PAN Coordinator board provides a platform to develop a complete communications system over G3-PLC technology.

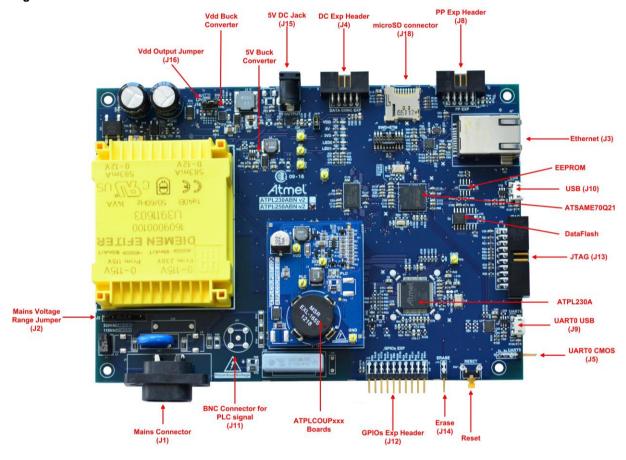

Figure 3-1. ATPL250ABNv2 PAN Coordinator board.

## 3.2 Features

The ATPL250ABNv2 board includes the following features:

- Power supply:

- Non switched ACDC isolated power supply: 100-230V<sub>AC</sub>, 50-60Hz.

- 5 volts rail is accessible by means of a DC Jack connector (J15).

- Selectable 12/16 V<sub>DD</sub> power supply.

- ATPL250A G3-PLC Transceiver:

- Implements G3 CENELEC-A, FCC and ARIB profiles (ITU-T G.9903, June 2014).

- Power Line Carrier modem for 50 and 60 Hz mains.

- G3-PLC coherent and continuous amplitude tracking in signal reception.

- Automatic Gain Control (AGC).

- Zero cross detection.

- Embedded PLC Analog Front End (AFE), requires only external discrete high efficient Class D Line Driver for signal injection.

- Support to G3-PLC coupling boards ATPLCOUPxxx.

- Mains zero-crossing detector circuit.

- SAME70Q21 MCU ARM Cortex-M7:

- Core

- ARM Cortex-M7 at up to 300 MHz.

- 16 Kbytes of ICache and 16 Kbytes of DCache with Error Code Correction (ECC).

- Memory Protection Unit (MPU) with 16 zones.

- Simple- and double-precision HW Floating Point Unit (FPU).

- DSP Instructions, Thumb<sup>®</sup>-2 Instruction Set.

- Embedded Trace Module (ETM) with instruction trace stream, including Trace Port Interface Unit (TPIU).

### Memories

- 2048 Kbytes Embedded Flash.

- 384 Kbytes Embedded SRAM.

- Tightly Coupled Memory (TCM) interface with four configurations (disabled, 2 x 32 Kbytes, 2 x 64 Kbytes, and 2 x 128 Kbytes).

- 16 Kbytes ROM with embedded Boot Loader routines (UART0, USB) and IAP routines.

- 16-bit Static Memory Controller (SMC) with support for SRAM, PSRAM, NOR and NAND Flash.

- 16-bit SDRAM Controller.

- Cryptography

- True Random Number Generator (TRNG).

- AES: 256-, 192-, 128-bit Key Algorithm, Compliant with FIPS PUB-197 Specifications.

- Integrity Check Monitor (ICM). Supports Secure Hash Algorithm SHA1, SHA224 and SHA256.

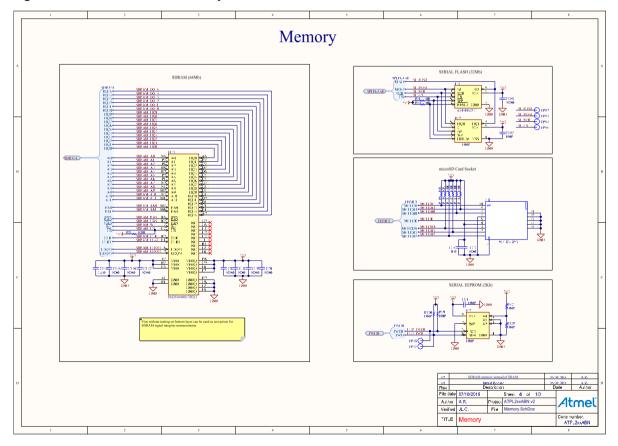

- External Memories:

- 4Mx16-bit SDRAM.

- 32-Mbit SPI Data Flash.

- TWI EEPROM (do not populate).

- microSD card connector.

- Peripherals:

- MCU 24 MHz crystal oscillator.

- MCU 32.768 kHz crystal oscillator.

- V<sub>DD</sub> and 5V Voltage monitor.

- Reset button.

- User's LEDs.

- Chip erase.

- Interface:

- JTAG debugging port.

- Embedded Trace Module (ETM).

- High Speed USB 2.0 Device.

- Xplained PRO Master/Slave Interface.

- UARTs over USB and CMOS levels.

- Ethernet 10/100 Mbps.

- Poly-phase Base Node extension header.

- Data Concentrator extension header.

- GPIOs extension header.

Figure 3-2. ATPL250ABNv2 PAN Coordinator board overview.

## 3.3 Block diagram

Figure 3-3. ATPL250ABNv2 Block diagram.

## 3.4 Mechanical and user considerations

This development board is directly powered from mains grid, so hazardous voltage is present on the board. To avoid user access to dangerous parts, ATPL250ABN must always be used in its enclosure. All required connectors and configuration jumpers are easily accessible without removing the enclosure cover.

A normal use of the ATPL250ABN does not require removing the enclosure cover. If this action is necessary, it must be performed by qualified staff being sure that mains connection has been previously removed.

ATPL250ABN is a CE mark product which passes EN60950-1 safety standard and EN50065-1, EN50065-2-3, EN50065-7 EMC and FCC (as current carrier system) standards. It also satisfies Pb-Free and ROHS directive.

ATPL250ABN supply voltage is taken from mains grid (100/230V<sub>AC</sub>, 50-60Hz), J1 connector.

ATPL250ABN dimensions are 178mm x 124mm x 30mm (LxWxH) and the enclosure dimensions are 191mm x 140mm x 48mm (LxWxH).

The operating temperature range is about -10 to 85°C.

## 3.5 Hardware description

In this section the modules of the ATPL250ABNv2 board are described. Take into account that the board's BOM; is not a final design, so they include devices that could be no necessary in the customer designs once the design has been optimized.

Hardware files are contained in the Hardware folder: ".\Hardware\HW SCH&PCB\ATPL250ABNv2".

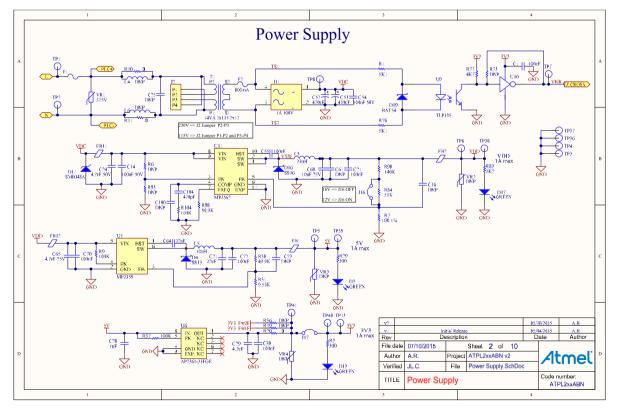

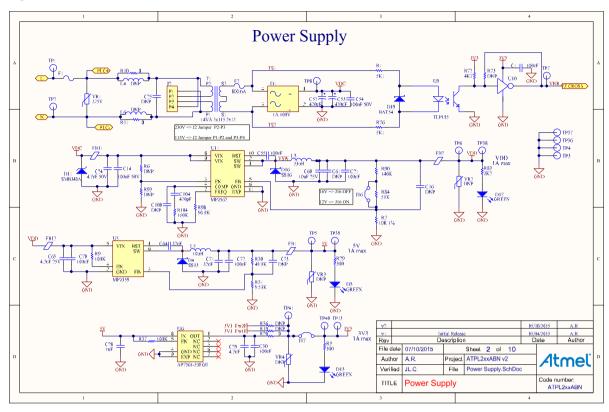

### 3.5.1 Power supply

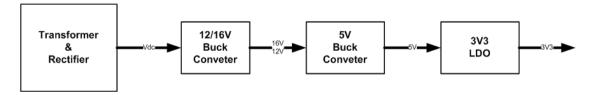

ATPL250ABN board can be powered either with 100V<sub>AC</sub> or 230V<sub>AC</sub> by setting the proper jumpers in the voltage selector (J2, Figure A-2). J1 IEC-320-C8 connector allows cable connection to mains grid. This design uses an encapsulated transformer (T1, Figure A-2) plus a full bridge rectifier (D1, Figure A-2) to obtain a DC voltage without increasing noise in PLC frequency bands (42 to 472 kHz), as may occur with switched ACDC power supplies. F1 and VR1 are used as protective devices in the equipment input and F2 protects the transformer output against over current situations.

By default, the voltage jumpers' configuration is for 230V<sub>AC</sub>. See Figure 7-10.

The maximum transformer output power of 14VA is oversized compared to the maximum current consumption of ATPL250ABN when it is used as a G3-PLC PAN Coordinator. However, this design is intended to power up other development kits which may have considerable power consumption if they include components such TFT displays.

The "V<sub>DC</sub>" voltage rail is used as input power of a high switching frequency buck converter (U11, Figure A-2) to generate the regulated DC voltage "V<sub>DD</sub>", which is used to power the class D amplifier of the PLC coupling circuit. The output level of the buck converter is selectable between 12V and 16V by means of jumper J16. Refer to the application note "PLC Coupling Reference Designs" doc43052 to know how the jumper J16 must be configured depending on the PLC coupling board which is being used.

A second buck converter (U12, Figure A-2) also with switching frequency above the highest PLC frequency band is used to generate a regulated 5V voltage rail. Despite 5V is not used by any device on ATPL250ABN board, it may be useful to power other Atmel evaluation kits to form more complex PLC reference designs, such as data concentrators. The DC Jack connector J15 (J15, Figure A-10) can be used to connect other board to 5V.

Finally on the power supply chain scheme, a low dropout (LDO) regulator (U13, Figure A-2) is used to generate the 3V3 voltage rail required by ATPL250A and the MCU. The current consumption from 3V3 voltage rail can be measured connecting an ammeter in the placeholder of jumper J17.

Other 1.2V voltage levels are generated by the embedded LDOs on ATPL250A and ATSAME70Q21 respectively. For a more detailed information about these LDOs, refer to ATPL250A and ATSAME70Q21 datasheets.

Figure 3-4. Power supply diagram.

Switching frequency of DCDC buck converters used in this evaluation kit has been chosen to be higher than maximum PLC frequency band supported by ATPL250A device.

We recommend characterizing the potential impact of the selected SMPS for customer designs on the G3-PLC frequency band transmission.

$V_{DD}$  could be two different voltages, 16 volts or 12 volts, depending on the jumper position. If the jumper is not placed, the voltage  $V_{DD}$  is 16 volts. If the jumper is placed in J16,  $V_{DD}$  is 12 volts. By default, the board has a jumper, so board provides 12 volts. These different voltages are used to supply the PLC coupling driver board.

Be careful with the  $V_{DD}$  voltage selected, because the PLC coupling driver board ATPLCOUP*XXX* could be damaged. Please check the features of these boards to select the operation voltage.

Figure 3-5. V<sub>DD</sub> selection in ATPL250ABN board.

The following test points and LEDs allow to check that these power supplies are operating properly (see Figure A-2):

- V<sub>DD</sub>: TP6 and green LED D17.

- 5V: TP5 and green LED D3.

- 3V3: TP13 and green LED D13.

- GND: TP3 & TP4.

### 3.5.2 Zero crossing detector

Phase identification is an important feature of devices that are connected to a smart grid network, such as smart meters. A typical implementation is based on measuring the time difference between a specific PLC frame reception and the last zero crossing event of the mains single-phase to which the device is connected.

Figure A-2 shows the zero crossing detection circuit, U10, used in ATPL250ABN board, which allows discerning between rising and falling edges of the mains voltage. The output signal of the detection circuit "VNR" is connected to a specific input of the ATPL250A and a synchronization algorithm is applied in order to obtain an accurate measurement of the time between PLC frame reception and zero crossing events.

The "VNR" signal is also connected to a timer counter input pin of the ATSAME70Q21 in order to have also information about zero crossing events on the microcontroller side.

It is important to note that in products that do not require galvanic isolation between primary and secondary circuits and the digital reference ground is connected to either line or neutral, a simple zenner diode with proper current limiting resistors, which considerably reduce the BOM cost, can be used instead of the circuit mounted in ATPL250ABN.

#### 3.5.3 SAME70Q21 Flash microcontroller

### 3.5.3.1 SAME70Q21 Overview

The Atmel SAME70Q21 Flash microcontroller is based on the high-performance 32-bit ARM Cortex-M7 RISC processor and includes a floating point unit (FPU). It operates at a maximum speed of 300 MHz and

features 2048 Kbytes of Flash and 384 Kbytes of multiport SRAM, which guarantees a minimum access latency. The on-chip SRAM can be configured as Tightly Coupled Memory (TCM) or system memory.

The SAME70 offers a rich set of advanced connectivity peripherals including a 10/100 Mbps Ethernet MAC supporting IEEE 1588, 802.1Qbb, 802.3az, 802.1AS and 802.1Qav. With a simple- and double-precision HW FPU, advanced analog features, as well as a full set of timing and control functions, the SAME70 is the ideal solution for industrial automation, home and building control, machine-to-machine communications, automotive aftermarket and energy management applications.

Furthermore, the peripheral set of SAME70 includes a high-speed USB device port with embedded transceiver, a high-speed MCI for SDIO/SD/MMC, 16-bit SDRAM interface, 16-bit external bus interface featuring a static memory controller providing connection to SRAM, PSRAM, NOR Flash, LCD Module and NAND Flash, 12-bit ITU-R BT.601/656 Image Sensor Interface (ISI), hardware acceleration for AES256, three USARTs, five UARTs, three TWIs, three SPIs, as well as two 4-channel PWM, four three-channel 16-bit Timers with quadrature decoder logic support, one RTC, Analog Front End interfaces (12-bit ADC, DAC, MUX and PGA), one 12-bit DAC (2-ch) and an analog comparator.

### 3.5.3.2 SAME70Q21 Clocking

Besides the embedded RC oscillators of ATSAME70Q21, two crystal oscillators are assembled on ATPL250ABN board to obtain a more precise and stable system clock reference, Y1 of 12 MHz and Y2, (Figure A-3). Furthermore, a 24MHz clock signal generated by the PLC transceiver ATPL250A is used by default as clock input by configuring the high frequency oscillator of ATSAME70Q21 in bypass mode. This configuration allows reducing the overall BOM cost (12MHz crystal oscillator is not required) while keeping a stable clock input signal.

A slow clock crystal oscillator of 32.768 kHz (Y2, Figure A-3) is used as SAME70 can be used as calendar and time base counter.

### 3.5.4 ATPL250A PLC Transceiver

#### 3.5.4.1 ATPL250A Overview

Atmel ATPL250A (U1, Figure A-7) is a power line communications modem, compliant with the PHY layer of G3-PLC specification. G3-PLC is an open standard technology used for Smart Grid applications like Smart Metering, Industrial Lighting and Automation, Home Automation, Street Lighting, Solar Energy and PHEV Charging Stations.

ATPL250A G3-PLC device includes enhanced features such as additional robust modes and frequency band extension. ATPL250A is able to operate in independently selectable transmission bands up to 472 kHz.

ATPL250A has been conceived to be bundled with an ATMEL MCU running the Physical Layer API and being controlled by means of a serial synchronous communication interface (SPI).

Please refer to ATPL250A datasheet on the Atmel website or in doc43079 for a detailed description.

## 3.5.4.2 ATPL250A Clocking

ATPL250A requires a 24MHz crystal oscillator (Y3, Figure A-7). And SAME70Q21 requires a 12 MHz crystal oscillator (Y1, Figure A-7).

The 24MHz clock signal could be used as internal reference time of the PLC modem, ATPL250A, and also to generate a 12MHz. So, it could be connected the output clock signal (CLKOUT) of ATPL250A like an input clock (CLKIN) of SAME70Q21 when ATPL250A is configured in bypass mode. In this way, only one high frequency crystal oscillator is required. For this option that is mounted by default in the board, R85 is soldered but R67 and R68 are not populated, and remember that ATPL250A must be configured properly.

Clocking item is widely detailed in the datasheet, doc43079.

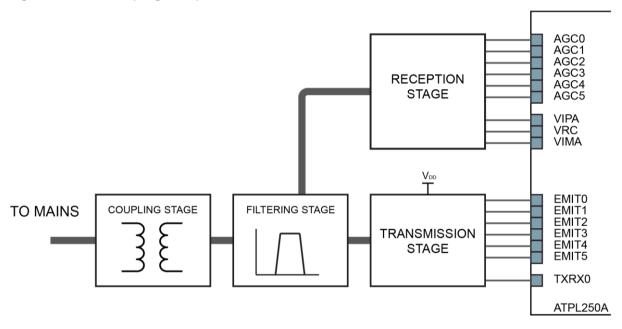

## 3.5.5 PLC Coupling

Atmel PLC technology is purely digital and does not require external DAC/ADC, thus simplifying the external required circuitry. Generally Atmel PLC coupling reference designs make use of few passive components plus a Class D amplification stage for transmission.

Figure A-8 and Figure A-9 show external components required by ATPL250A for PLC reception and transmission respectively.

PLC coupling reference design is composed by the same sub-circuits:

- Coupling Stage.

- Reception Stage.

- Transmission Stage.

- Filtering Stage.

Figure 3-6. PLC Coupling example.

### 3.5.5.1 Coupling stage

The coupling stage blocks the DC component of the line to/from which the signal is injected / received (i.e.: 50/60 Hz of the mains). This is carried out by a high voltage capacitor (C26, Figure A-8). Coupling stage could also voltage isolate the coupling circuitry from the external world by means of a 1:1 PLC transformer. Capacitor is laying out in ATPL250ABN. The optional PLC transformer is included in ATPLCOUP007 board (voltage isolated), see section 4.

Footprint of BNC connector (J11, Figure A-8) is included in the board, but is not mounted by default. Removing the R12 and R13 and soldering R88 and R89 resistors, the PLC coupling signal can be isolated from the mains grid and that connector allows performing measurements of transmitted and received PLC signal without side effects (noise) coming from the grid.

### 3.5.5.2 Reception stage

The reception stage adapts the received analog signal to be properly captured by the internal reception chain. Reception circuit is independent of the PLC frequency band which is being used. It basically consists on:

Single-pole low pass filter (RC Filter), R49 & C43, Figure A-9.

- Automatic Gain Control (AGC) circuit. The AGC circuit avoids distortion (set of resistors used to attenuate the incoming PLC signal) on the received signal that may arise when the input signal is high enough to polarize the protective diodes in direct region (D10, Figure A-9).

- Driver of the internal ADC. The driver to the internal ADC comprises a couple of resistors (DC biasing resistors, R59 and R60) and a couple of capacitors (DC decoupling capacitors, C45 and C46). This driver provides a DC component and adapts the received signal to be properly converted by the internal reception chain.

### 3.5.5.3 Transmission stage

The transmission stage adapts the EMIT signals and amplifies them if required (Figure A-8). It can be composed by:

- Driver: A group of resistors which adapt the EMIT signals to either control the Class-D amplifier or to be filtered by the next stage.

- Amplifier: If required, a Class-D amplifier which generates a square waveform from 0 to VDD is included.

- Bias and protection: A couple of resistors and a couple of Schottky barrier diodes provide a DC component and provide protection from received disturbances.

Transmission stage shall be always followed by a filtering stage.

## 3.5.5.4 Filtering stage

The filtering stage is composed by band-pass filters which have been designed to achieve high performance in field deployments complying at the same time with the proper normative and standards.

The in-band flat response filtering stage does not distort the injected signal, reduces spurious emission to the limits set by the corresponding regulation and blocks potential interferences from other transmission frequency bands.

The filtering stage has three aims:

- Band-pass filtering of high frequency components of the square waveform generated by the transmission stage.

- Adapt Input/Output impedances for optimal reception/transmissions. This is controlled by TXRX signals.

- And, in some cases, Band-pass filtering for received signals.

When the system is intended to be connected to a physical frequency band with high voltage or which is not electrically referenced to the same point then the filtering stage must be always followed by a coupling stage.

These components are not implemented on ATPL250ABN board because are dependent on the application parameters such frequency band transmission. A set of boards known as ATPLCOUPxxx have been design by to support multiple transmission options supported by ATPL250A. PANCoordinator-EK includes ATPLCOUP007, ATPLCOUP002 and ATPLCOUP006 boards which are described in chapters 4, 5 and 6 respectively. Other coupling boards have been designed. The Application Note, doc43052, provides a complete description of Atmel PLC Coupling Reference Designs available.

## 3.5.5.5 ATPLCOUP boards

Table 3-1 summarizes the main characteristics of currently available PLC coupling reference designs. Please refer to Atmel doc43052 for a complete description of ATPLCOUP boards.

This technology only allows one frequency band active at a time.

Table 3-1. ATPLCOUP boards.

| Board Name  | Frequency Band | Branch | Electrical<br>Isolation | CENELEC<br>Band | ARIB | FCC |

|-------------|----------------|--------|-------------------------|-----------------|------|-----|

| ATPLCOUP002 | 152-405 kHz    | Double | Yes                     | -               | Х    | -   |

| ATPLCOUP006 | 152-489 kHz    | Double | Yes                     | -               | -    | Х   |

| ATPLCOUP007 | 35-91 kHz      | Single | Yes                     | А               | -    | -   |

| ATPLCOUP008 | 35-91 kHz      | Single | No                      | А               | -    | -   |

Figure 3-7. FCC & ARIB bands.

## 3.5.6 Peripherals

These peripherals are not necessary to implement a G3-PLC design, they are included to show some features of the ATPL250A for a customer designs.

#### 3.5.6.1 SDRAM

The amount of data to be managed by a PAN Coordinator device typically exceeds the embedded SRAM density of ATSAME70Q21 (384kB). To overcome this limitation, an external SDRAM with 4Mx16-bit density is used in ATPL250ABN to support a big quantity of connected devices.

## 3.5.6.2 Data Flash

A 4MB SPI serial DataFlash is used to extend the non-volatile memory capability of ATSAME70Q21 (1MB).

Two different packages (U3 and U12, Figure A-4) are used in ATPL250ABN board to support the pinout of both the Adesto (former Atmel) family of DataFlash memories and standard serial flash products. Since both packages use the same chip select signal, only one device can be assembled simultaneously.

#### 3.5.6.3 **EEPROM**

ATPL250ABN board includes the possibility to mount a serial EEPROM memory connected by Two Wires Interface, TWI, (U2, Figure A-4) with the SAME70. This device is not assembled by default. Please refer to AT24Cxx datasheet for a further description on Atmel's website.

## 3.5.6.4 microSD card connector

The high speed multimedia card interface (HSMCI) peripheral of ATSAME70Q21 supports the SD memory card specification V2.0. A microSD card connector with card detection switch is used in ATPL250ABN board. The card detection feature can be implemented by means of a GPIO with interrupt capability.

### 3.5.6.5 Voltage Monitor

Two ports (PB2 and PD30) of the ATSAME70Q21 analog front end module are used to monitor the V<sub>DD</sub> and 5V voltage rails through external voltage divisors, as shown in Figure A-3.

The voltage monitor circuit allows the implementation of multiple applications such as:

- Detection of fault conditions.

- Detection of low power mode entering conditions.

- Detection of wake-up situations.

- Measuring of PLC power amplifier voltage value.

The selected ports for the voltage monitor circuit can also be used as input of the analog comparator in ATSAME70Q21.

#### 3.5.6.6 Reset

Besides the reset conditions managed by the reset controller peripheral of the ATSAME70Q21, such as power-on-reset and brown-out monitor, two other reset sources are added at PCB level in ATPL250ABN:

- User controller reset switch button (SW1).

- The "NRST\_CONC" signal on the data concentrator expansion connector, which allows resetting the base node reference design when it is used in data concentrator topologies.

The input/output "NRST" pin of ATSAME70Q21 is connected to the "PLL\_INIT" input reset pin of the ATPL250A. Therefore, all reset conditions commented above, generate also a complete reset of the PLC transceiver. It is important to note that a reset event on "PLL\_INIT" disables the "CLKOUT" output pin and, in case the ATSAME70Q21 is using this clock signal as the external clock input in bypass mode, a reset condition may lead to a loss of master clock on the microcontroller if a proper configuration is not applied by firmware. The firmware releases provided by Atmel for the base node reference design take this condition into account.

In addition to the complete reset of the PLC transceiver generated by an assertion of the "PLL\_INIT" input, the "ARST" and "SRST" input reset signals allow also resetting the ATPL250A but in each of these cases without disabling the external clock on "CLKOUT" pin. Therefore, no special configurations have to be considered on the microcontroller side related to the clock system configuration. "ARST" and "SRST" are managed by the GPIOs PE1 and PE2 respectively in ATPL250ABN board.

#### **3.5.6.7 Chip Erase**

The 1x2 right angle pin-header J14 marked as "ERASE" (see Figure A-3) is connected to the SAME70 chip erase pin (PB12) and 3V3. This header can be used to erase the ATSAME70Q21 flash memory by placing a jumper on the header and pressing the reset switch button. After a while, the erase jumper should be removed and the PCBA must be turn off and turn on by disconnecting and connecting it again to the mains grid (flash erasing takes only 200ms).

## 3.5.6.8 User LEDs

The board incorporates two user LEDs (LED0 & LED1), green and red (D5 & D6, Figure A-3), connected to GPIOs PA21 and PA22 respectively of the SAME70Q21.

#### 3.5.7 Interface Ports

### 3.5.7.1 ATSAME70Q21 JTAG/SWD Debug Port

The ATSAME70Q21 JTAG/SWD interface is available in a standard 20 pins male right angle header for debugging and programming purposes.

Please, refer to ATSAME70Q21 datasheet for a more detailed description of the debug port. It is important to note that JTAG is only available for boundary scan manufacturing test purposes.

#### 3.5.7.2 Embedded Trace Module (ETM)

The Embedded Trace Macrocell (ETM) is a real-time trace module which delivers unrivalled instruction trace capture in an area far smaller than traditional trace units, enabling the SAME70 MCU to implement full instruction trace.

The ETM depends on the Trace Port Interface Unit (TPIU) to export data out of the system. The TPIU features the following pins:

- TRACECLK is the data stream synchronization signal

- TRACED0-TRACED3

ATPL250ABN implements a CoreSight™ 20, 20-pin, 50-mil keyed connector (pin seven is removed). Besides the TPIU signals, the CoreSight connector features also a Serial Wire Debug (SWD) interface.

Considering that the TPIU signals of the ATSAME70Q21 are multiplexed with the GMAC Ethernet RMII interface, it is not possible to use the ETM if the Ethernet port is enabled. Furthermore, if ETM is used, it is important to keep the Ethernet PHY IC in reset mode (GPIO PD31 must be asserted low) to avoid signal collisions.

### 3.5.7.3 High-speed USB Device 2.0

The ATPL250ABN has a micro-USB receptacle connected to the high-speed USB device 2.0 module of ATSAME70Q21. To be able to detect when a USB host is attached to ATPL250ABN board, a GPIO (PC17) is used to detect the VBUS voltage on the connector. The 5V voltage rail provided by the USB host is not used in ATPL250ABN rather than for detection purpose.

## **3.5.7.4 Debug UART**

The UART0 of ATSAME70Q21 is connected to a CP2105 UART to USB 2.0 bridge to ease PC connectivity for debugging purposes. The firmware projects provided by Atmel to ease the evaluation of the G3 PHY-layer performance are based on serial interface through UART0.

As shown in Figure A-5, the UART to USB bridge CP2105 is powered from the 3.3V LDO on ATPL250ABN rather than from the 5V voltage rail of the USB connection. Therefore, ATPL250ABN board has to be connected to mains if the debugging UART is going to be used.

UARTO signals in CMOS levels are also available in the 3-pins right angle header J5.

#### 3.5.7.5 Ethernet

The ATSAME70Q21 has a built in 10/100 Mbps Ethernet IEEE® 802.3 MAC with a RMII interface that connects to a Micrel KSZ8081RNA PHY-layer transceiver. The Ethernet input and output differential pairs of the PHY-layer transceiver are directly connected to a RJ45 Ethernet connector with embedded isolating signal transformers.

Refer to Figure A-6 for a complete view of the Ethernet PHY-layer transceiver design.

## 3.5.7.6 Poly-Phase Expansion Header

The 10-pin dual row male header J8 contains the USART transmission and reception signals of ATSAME70Q21 USART1 and two extra GPIOs. This expansion header is intended to cover poly-phase PLC base node reference designs in combination with other Atmel evaluation boards.

## 3.5.7.7 Data Concentrator Expansion Header

The 10-pin dual row male header J4 contains the UART transmission and reception signals of ATSAME70Q21 UART1 and two extra GPIOs. Furthermore, as commented in section 3.5.6.6, a reset input of ATPL250ABN board is available as well. This expansion header is intended to cover data concentrator reference designs in combination with other Atmel evaluation boards.

## 3.5.7.8 GPIOs Expansion Header

The 2.54mm pitch right-angle header J12 offers access to the I/O ports of the microcontroller that are not used within the ATPL250ABN board. Refer to ATSAME70Q21 datasheet for a description of the peripheral functionality available of each GPIO.

## 4. ATPLCOUP007 Hardware

## 4.1 Overview

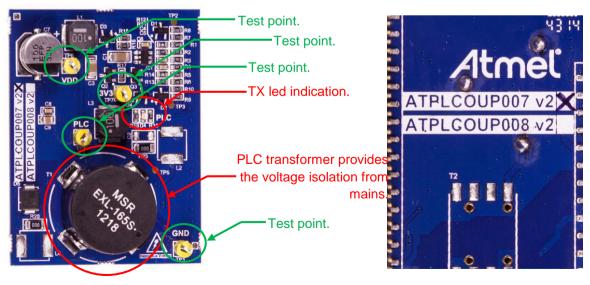

ATPLCOUP007 is a PLC coupling board designed to communicate in CENELEC-A band, especially in G3-PLC band, from 35 to 91 kHz. ATPLCOUP007 mounts a single branch with voltage isolation from mains to the PLC coupling driver board. The goal of this design is provided to the customers with a cost optimized performance transmission board in CENELEC-A band for G3-PLC. This board is set by default in the ATPL250ABN board of the PANCoordinator-EK.

S<sub>max</sub>(f) dB(μV) 134 116 89 66 A-Band B C D

Figure 4-1. CENELEC bands.

## 4.2 Features

The ATPLCOUP007v2.5 board includes the following features:

• Specially designed to communicate in CENELEC-A frequency band (35 – 91 kHz).

95

• Voltage Isolation from mains with a transformer, MSR EXL-165S-LT, soldered in top layer board.

125

140 148.5 f (kHz)

Single branch:

9

Low impedance optimized.

Figure 4-2. ATPLCOUP007v2.5 PLC Coupling board (top view).

## 4.3 Mechanical and user considerations

ATPLCOUP007 is delivered with the PANCoordinator-EK. Board-to-board SMD connectors, J1 and J2, are used to connect the ATPLCOUP007 into connectors J6 and J7 of ATPL250ABN board (Figure A-8). These J1 and J2 connectors are in bottom layer of ATPLCOUP007 and they have the following part numbers:

- J1: SAMTEC FTR-130-54-L-S.

- J2: SAMTEC FTR-124-54-L-S.

The ATPLCOUP007 board is directly powered from mains grid, so hazardous voltage is present on the board. To avoid user access to dangerous parts, ATPLCOUP007 must always be used in its enclosure.

ATPLCOUP007 is a CE mark product that passes EN 50065-1, EN 50065-2-3 and EN 50065-7 EMC standards. It also satisfies Pb-Free and ROHS directive.

ATPLCOUP007 dimensions are 51.5mm x 39.5mm x 18mm (LxWxH).

The operating temperature range is about -40 to 85°C.

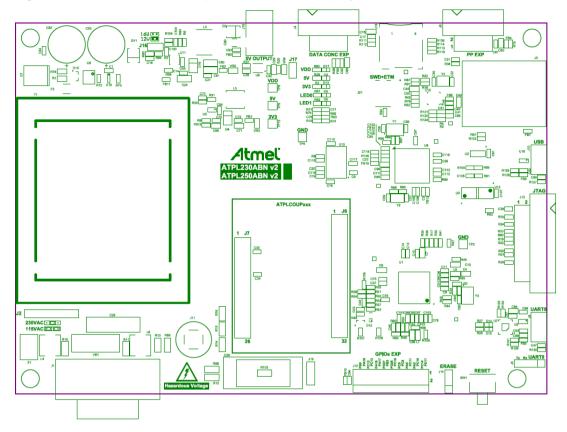

## 4.4 Hardware description

Hardware files are contained in the Hardware folder: ".\Hardware\HW SCH&PCB\ATPLCOUP007v2.5".

ATPLCOUP007 is an isolated reference design which provides a full performance PLC coupling reference design in terms of output signal level over a wide range of load impedance values while complying with EN50065-1, EN50065-2-3 and EN50065-7 normative. It supports the frequency band between 35 and 91 kHz of CENELEC-A band.

ATPLCOUP007 is composed of only one transmission branch (single branch) which filtering stage has a flat band pass response with typical field impedances. It involves a cost optimization in the BOM. For more information, see PLC coupling reference designs document, doc43052.

Take into account that, when ATPLCOUP007 is connected to ATPL250ABN, V<sub>DD</sub> voltage must be **12 volts** to avoid damaging the coupling board, so jumper in J16 must be **set** (see section 3.5.1 and Figure A-2). By default, the jumper is placed in J16.

Figure 4-3. V<sub>DD</sub> selection in ATPL250ABN board.

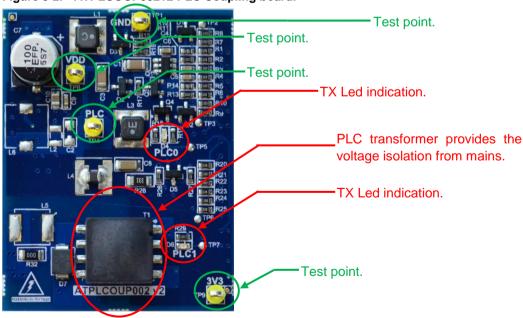

## 5. ATPLCOUP002 Hardware

## 5.1 Overview

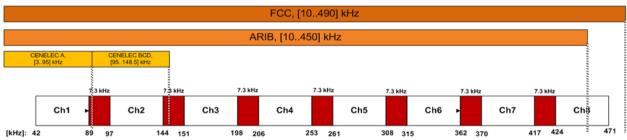

ATPLCOUP002 is a PLC coupling board designed to communicate in ARIB and FCC bands, especially in bands from 152 to 405 kHz. ATPLCOUP002 mounts a double branch with voltage isolation from mains to the PLC coupling driver board. The goal of this design is provided to the customers with a full performance transmission board in ARIB bands. This board is not set by default in the ATPL250ABN board of the PANCoordinator-EK.

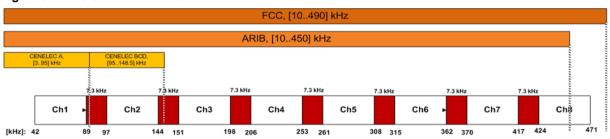

FCC, [10..490] kHz

ARIB, [10..450] kHz

CENELEC A. [3.95] kHz [95.148.5] kHz

7.3 kHz 7.3 kHz 7.3 kHz 7.3 kHz 7.3 kHz 7.3 kHz 7.3 kHz

Ch1 Ch2 Ch3 Ch4 Ch5 Ch6 Ch6 Ch7 Ch8

253 261

308 315

362 370

Figure 5-1. FCC and ARIB bands.

## 5.2 Features

[kHz]: 42

The ATPLCOUP002v2 board includes the following features (see Figure 5-2):

198 206

G3 FCC/ARIB bands (152 – 405 kHz).

144 151

- Double-branch design:

- Low impedance optimized.

- High impedance optimized.

- Voltage Isolation from mains with a transformer, VAC T60403K5024X044, soldered in top layer board.

Figure 5-2. ATPLCOUP002v2 PLC Coupling board.

417 424

## 5.3 Mechanical and user considerations

ATPLCOUP002 is delivered with the PANCoordinator-EK. Board-to-board SMD connectors, J1 and J2, are used to connect the ATPLCOUP002 into connectors J6 and J7 of ATPL250ABN board (Figure A-8). These J1 and J2 connectors are in bottom layer of ATPLCOUP002 and they have the following part numbers:

- J1: SAMTEC FTR-130-54-L-S.

- J2: SAMTEC FTR-124-54-L-S.

The ATPLCOUP002 board is directly powered from mains grid, so hazardous voltage is present on the board. To avoid user access to dangerous parts, ATPLCOUP002 must always be used in its enclosure.

ATPLCOUP002 is a CE mark product that passes EN 50065-1, EN 50065-2-3, EN 50065-7 EMC and STD-T84v1.0 (ARIB) standards. It also satisfies Pb-Free and ROHS directive.

ATPLCOUP002 dimensions are 51.5mm x 39.5mm x 18mm (LxWxH).

The operating temperature range is about -40 to 85°C.

## 5.4 Hardware description

Hardware files are contained in the Hardware folder: ".\Hardware\HW SCH&PCB\ATPLCOUP002v2".

ATPLCOUP002v2 board is a PLC coupling driver board with double branch design and galvanic voltage isolation. ATPLCOUP002 has been designed to transmit in ARIB and FCC bands, especially in bands from 260 to 417 kHz.

It has a good performance in terms of transmitted frequency band power over a range of load impedance values complying with ARIB standard (sections 3.2 and 3.3 of the standard), see ARIB normative. ATPLCOUP002 is composed of two transmission branches which only differ on the filtering stage. A 12V power supply voltage for the class-D amplifier is recommended to be used with ATPLCOUP002.

For more information, see PLC coupling reference designs document, doc43052.

Take into account that, when ATPLCOUP002 is connected to ATPL250ABN, V<sub>DD</sub> voltage must be **12 volts** to avoid damaging the coupling board, so jumper in J20 must be **set** (see section 3.5.1 and Figure A-2). By default, the jumper is placed in J16.

Figure 5-3. V<sub>DD</sub> selection in ATPL250ABN board.

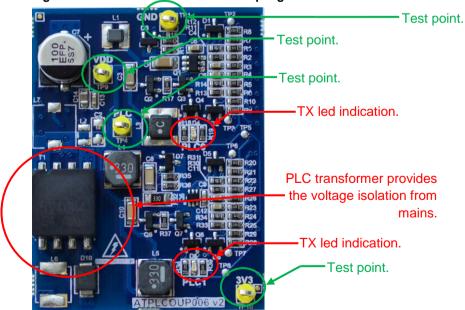

## 6. ATPLCOUP006 Hardware

## 6.1 Overview

ATPLCOUP006 is a PLC coupling board designed to communicate in ARIB and FCC bands, especially in G3 bands from 152 to 489 kHz. ATPLCOUP006 mounts a double branch with voltage isolation from mains to the PLC coupling driver board. The goal of this design is provided to the customers with a full performance transmission board in FCC band. This board is not set by default in the ATPL250ABN board of the PANCoordinator-EK.

Figure 6-1. FCC and ARIB bands.

## 6.2 Features

The ATPLCOUP006v2 board includes the following features:

- Specially designed to communicate in ARIB and FCC frequency bands (152 489 kHz).

- Voltage Isolation from mains with a transformer, VAC T60403K5024X044, soldered in top layer board.

- Double branch, each one for a range of impedances:

- Low impedance optimized.

- High impedance optimized.

Figure 6-2. ATPLCOUP006v2 PLC coupling board.

## 6.3 Mechanical and user considerations

ATPLCOUP006 is delivered with the PANCoordinator-EK. Board-to-board SMD connectors, J1 and J2, are used to connect the ATPLCOUP006 into connectors J6 and J7 of ATPL250ABN board (Figure A-8). These J1 and J2 connectors are in bottom layer of ATPLCOUP006 and they have the following part numbers:

- J1: SAMTEC FTR-130-54-L-S.

- J2: SAMTEC FTR-124-54-L-S.

The ATPLCOUP006 board is directly powered from mains grid, so hazardous voltage is present on the board. To avoid user access to dangerous parts, ATPLCOUP006 must always be used in its enclosure.

ATPLCOUP006 is a CE mark product that passes EN 50065-1, EN 50065-2-3, EN 50065-7 EMC and FCC (as current carrier system) standards. It also satisfies Pb-Free and ROHS directive.

ATPLCOUP006 dimensions are 51.5mm x 39.5mm x 18mm (LxWxH).

The operating temperature range is about -40 to 85°C.

# 6.4 Hardware description

Hardware files are contained in the Hardware folder: ".\Hardware\HW SCH&PCB\ATPLCOUP006v2".

ATPLCOUP006v2 board is a PLC coupling driver board with double branch design and galvanic voltage isolation. ATPLCOUP006 has been designed to transmit in ARIB and FCC band, especially in bands from 151 to 472 kHz.

It has a good performance in terms of transmitted frequency band power over a range of load impedance values complying with FCC standard as current carrier system, see FCC normative. ATPLCOUP006 is composed of two transmission branches which only differ on the filtering stage. A 12V power supply voltage for the class-D amplifier is recommended to be used with ATPLCOUP006.

For more information, see PLC coupling reference designs document, doc43052.

Take into account that, when ATPLCOUP006 is connected to ATPL250ABN, V<sub>DD</sub> voltage must be **12 volts** to avoid damaging the coupling board, so jumper in J20 must be **set** (see section 3.5.1 and Figure A-2). By default, the jumper is placed in J16.

Figure 6-3. V<sub>DD</sub> selection in ATPL250ABN board.

# 7. PAN Coordinator Evaluation Kit: Getting started

The purpose of this chapter is to provide an introduction to the Atmel PANCoordinator-EK and its functionalities.

First of all, the software is presented to create, build, program and debug your application using the appropriate IDE tools (section 7.1).

Chapter 7.2 describes a simple PLC application to check PLC performance in a point-to-point connection (PHY layer example).

Chapter 7.3 describes the PHY TX Test Console application, which lets you configure a proper setup to perform both EMC emissions and immunity tests on ATPL250ABN board.

Chapter 7.4 describes the G3 PHY Sniffer project, which, is able to monitor data traffic on the G3-PLC network.

Chapter 7.5 describes the Atmel G3-PLC Stack and we present you the structure of a G3-PLC project.

Chapter 7.6 explains the setup and operations required to create a smart PLC network using the included G3 PAN Coordinator example. This network communicates by means of G3-PLC.

Note: The software described in this manual is under the Atmel's *Evaluation License Agreement.pdf* document, available in the Software folder.

## 7.1 Introduction to the embedded system

The purpose of this section is to guide new users through the initial settings of IAR Embedded Workbench, Atmel Studio (AS) or Keil µVision, and compile a G3 project. The section shows setup of a G3 project to generate a debug target that can be loaded into the microcontroller.

Kit projects are supported by IAR 7.70, μVision 5.14 or AS 6.2 versions or above. From this point on, it is assumed that a working copy of this IDE is installed in your computer. The IAR's homepage, http://www.iar.com, is a suitable source to download (i.e.: 30-day time-limited evaluation license). In the Atmel's homepage, http://www.atmel.com, is suitable for downloading the Atmel Studio (free download). Visit http://www.keil.com/ to get a MDK-Lite version.

#### 7.1.1 IAR Embedded Workbench

IAR Embedded Workbench is a high-performance C/C++ compiler assembler, linker, librarian, text editor, project manager, and C-SPY® Debugger in an integrated development environment for applications based on 8-, 16-, and 32-bit microcontrollers. IAR Embedded Workbench is compatible with other ARM EABI compliant compilers and supports the SAM4C core family (example projects are developed only for 7.70 versions or above).

## 7.1.2 Keil µVision

μVision is a window-based software development platform that combines a robust and modern editor with a project manager and makes facility tool. It integrates all the tools needed to develop embedded applications including a C/C++ compiler, macro assembler, linker/locator, and a HEX file generator.

$\mu$ Vision offers a Build Mode for creating applications and a Debug Mode for debugging applications. Applications can be debugged with the integrated  $\mu$ Vision Simulator or directly on hardware.

PLC example projects are developed only for µVision 5.14 versions or above.

## 7.1.3 Atmel Studio 6

Atmel Studio is the integrated development platform (IDP) for developing and debugging Atmel ARM Cortex-M and Atmel AVR® microcontroller (MCU) based applications. The Atmel Studio IDP gives you a

seamless and easy-to-use environment to write, build and debug your applications written in C/C++ or assembly code.

Atmel Studio 6 is free of charge and is integrated with the Atmel Software Framework (ASF) — a large library of free source code with 1,600 ARM and AVR project examples. ASF strengthens the IDP by providing, in the same environment, access to ready-to-use code that minimizes much of the low-level design required for projects. Use the IDP for our wide variety of AVR and ARM Cortex-M processor-based MCUs, including our broadened portfolio of Atmel SAM3 ARM Cortex-M3 and M4 Flash devices.

We recommend download and installing the last version of Atmel Studio. You can download all versions from the following link:

http://www.atmel.com/tools/STUDIOARCHIVE.aspx.

### 7.1.4 Atmel SAM-ICE JTAG Probe

Atmel SAM-ICE (a dedicated Atmel J-Link version) is a USB-powered JTAG emulator supporting Atmel ARM-based microcontrollers.

Atmel SAM-ICE is a JTAG emulator designed for Atmel SAMA5, SAM3, SAM4, SAM7 and SAM9 ARM core-based microcontrollers, including the Thumb® mode. It supports download speeds up to 720 Kbytes per second and maximum JTAG speeds up to 12 MHz. It also supports Serial Wire Debug (SWD) and Serial Wire Viewer (SWV) from SAM-ICE hardware V6.

SAM-ICE support is integrated in most professional integrated development environments (IDEs) such as IAR, Keil and many others.

More details are available here: http://www.atmel.com/tools/ATMELSAM-ICE.aspx.

Figure 7-1. Atmel SAM-ICE JTAG.

This evaluation kit does not provide an Atmel SAM-ICE.

To use Segger tools with Atmel Studio, download Atmel's latest USB driver driver-atmel-bundle-7.0.712.exe from the following link: https://gallery.atmel.com/Products/Details/07bf16c1-444f-4ac8-8f40-9d4005575dca or take it from the PCTools folder: ".\PCTools\SAM-ICE\_Drivers". And install the file.

#### 7.1.5 J-Link / SAM-ICE JTAG Probe Software & Documentation Pack

The J-Link / SAM-ICE JTAG software and documentation pack includes:

GDB Server - Support for GDB and other debuggers using the same protocol. GUI & command line version.

- J-Link Configurator Free utility to manage a various number of J-Links connected to the PC via USB or Ethernet.

- J-Link Commander Simple command line utility, primarily for diagnostics and trouble shooting.

- J-Link Remote Server Free utility which provides the possibility to use J-Link / J-Trace remotely via TCP/IP.

- SWO Viewer Free tool which shows terminal output of the target performed via SWO pin.

- J-Mem Memory viewer.

- J-Link DLL Updater Allows updating 3rd party applications which use the J-Link DLL.

- Free flash programming utilities Simple command line utilities which allow programming a bin file into the internal/external flash memory of popular evaluation boards.

- USB driver (Includes driver for J-Links with CDC functionality).

- Manuals: UM08001 (J-Link User Guide), UM08003 (J-Flash User Guide), UM08004 (RDI User Guide), UM08005 (GDB Server User Guide) and UM08007 (Flasher ARM User Guide).

- Release notes for J-Link DLL, J-Flash and J-Link RDI DLL.

- J-Flash, including sample projects for most popular evaluation boards.

- J-Link RDI Support for ARM RDI standard. Makes J-Link compatible with RDI compliant debuggers.

Installing the software will automatically install the J-Link USB drivers. It also allows the update of applications that use the J-Link DLL.

The last version of the driver for the SAM-ICE JTAG Probe can be downloaded from the http://www.segger.com/website using the following link: http://www.segger.com/jlink-software.html. The package for Windows, Setup\_JLinkARM\_V496b.zip, is located in the following folder: ".\PCTools\SAM-ICE Driver".

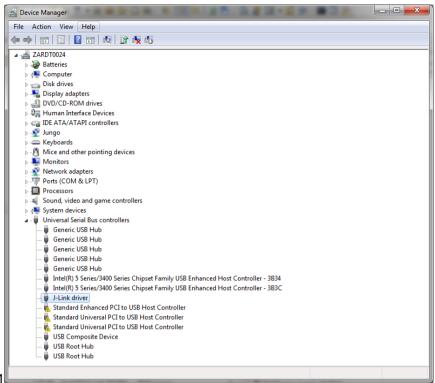

Once drivers have been installed you may verify the driver installation by consulting the Windows® device manager. If the driver is installed and your SAM-ICE is connected to your computer, the device manager should list the J-Link driver as a node below "Universal Serial Bus controllers" as shown in the following screenshot.

Figure 7-2. Device manager.

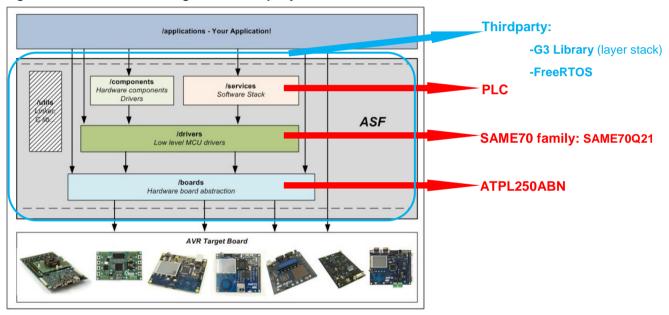

### 7.1.6 Atmel Software Framework (ASF)

The Atmel Software Framework (ASF) is a collection of embedded software for the Atmel Flash MCUs: megaAVR, AVR XMEGA, AVR UC3 and SAM devices.

It simplifies the use of our microcontrollers by providing an abstraction to the hardware and high-value middleware. ASF is designed to be used for evaluation, prototyping, design and production phases. The intention of ASF is to provide a rich set of proven drivers and code modules developed by Atmel experts to reduce customer design-time. It simplifies the usage of microcontrollers, providing an abstraction to the hardware and high-value middleware.

ASF is integrated in the Atmel Studio IDE with a graphical user interface or available as standalone for GCC, IAR compilers. ASF can be downloaded for free. ASF is an open-source code library designed to be used for evaluation, prototyping, design and production phases.

The Atmel Software Framework is split in six main parts, the *avr32*/ directory, the *xmega*/ directory, the *mega*/ directory, the *common*/ directory, the *sam*/ *directory* and the *thirdparty*/ directory. These six directories represent the Atmel AVR UC3 architecture, the Atmel megaAVR, the Atmel AVR XMEGA architecture and the Atmel SAM architecture, what are common between all architectures and finally third party libraries.

Each architecture (and the common directory) is split into several subdirectories, these directories contain the various modules; boards, drivers, components, services and utilities.

See the list below and Figure 7-3 for an overview of how the various modules are wired together:

- Boards contain mapping of all digital and analog peripheral to each I/O pin of Atmel's development kits

- Drivers is composed of a driver.c and driver.h file that provides low level register interface functions to access a peripheral or device specific feature. The services and components will interface the drivers.

- Components is a module type which provides software drivers to access external hardware components such as memory (e.g. Atmel DataFlash®, SDRAM, SRAM, and NAND flash), displays, sensors, wireless, etc.

- Services is a module type which provides more application oriented software such as a USB classes, FAT file system, architecture optimized DSP library, graphical library, etc.

- *Utilities* provide several linker script files, common files for the build system and C/C++ files with general usage define, macros and functions.

- Applications provide application examples that are based on services, components and drivers modules. These applications are more high level and might have multiple dependencies into several modules.

Figure 7-3. ASF modules structures.

Download link for more information: http://www.atmel.com/tools/AVRSOFTWAREFRAMEWORK.aspx. Please do not hesitate to visit our web site to get the last library updates.

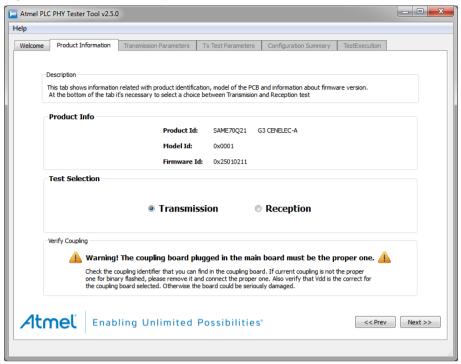

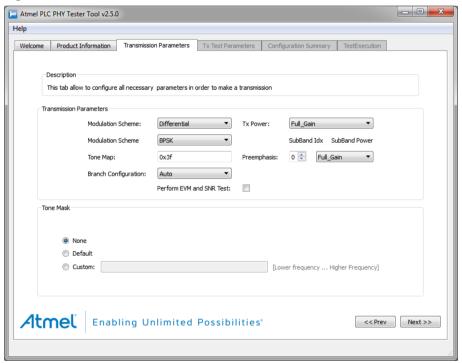

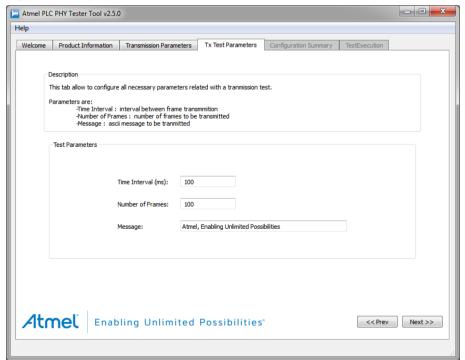

# 7.2 PLC application example 1 – PHY Tester

Board of the kit, by default, are programmed with the embedded PLC PHY Tester tool firmware for SAME70Q21 device, *apps\_phy\_tester\_tool.bin*. It is an application example that shows the capabilities of the ATPL250A in a point-to-point connection (physical layer). This application requires a pair of boards and a PC tool, Atmel PLC PHY Tester tool, which has to be installed in the user's host PC to interface with the board.

In any case, if you want to load this file again, you have to build the project <a href="mailto:apps\_phy\_tester\_tool">apps\_phy\_tester\_tool</a> to generate the output file to program. See section 7.2.4 to know more about programming the ATPL250ABN board.

Atmel recommends to load the binary generated with the last PHY Tester Tool project released in the kit to evaluate the board with last improvements.

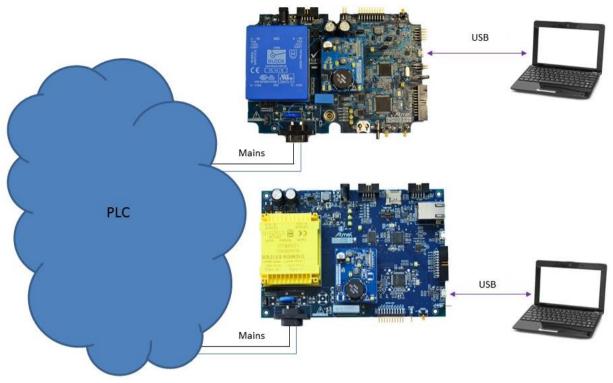

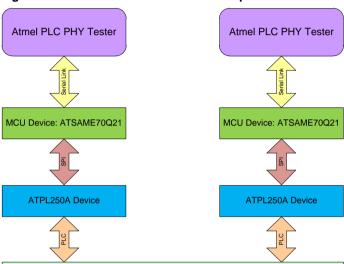

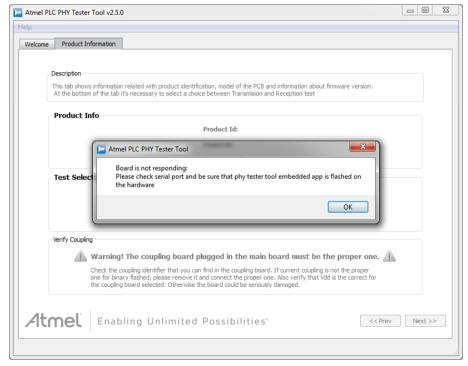

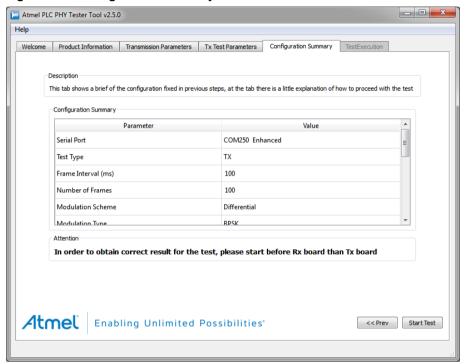

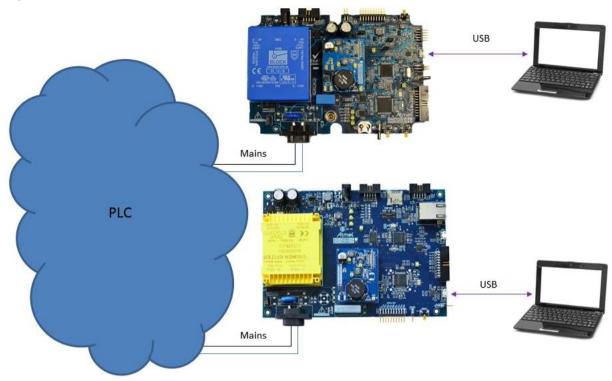

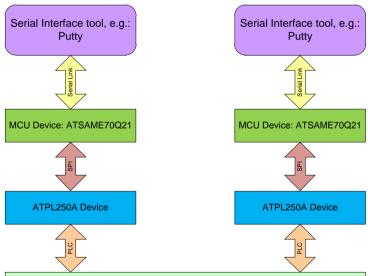

After installing the Atmel PLC PHY Tester tool in your PC(s), connect the two boards to the grid and to the host(s) PC(s) as shown in the following figure.

To run this example, two boards are used. So another Atmel board besides of ATPL250ABN is necessary to run this test, e. g, ATPL250AMB.

Figure 7-4. Atmel Boards connection scheme.

Following chapters explain to you how to install the PC tool, supply the boards, and select the UART0 to communicate with the SAME70Q21. Load the firmware and run the application.

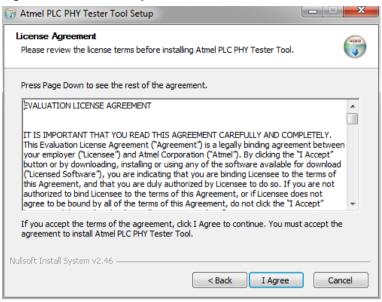

## 7.2.1 Atmel PLC PHY Tester tool Installation

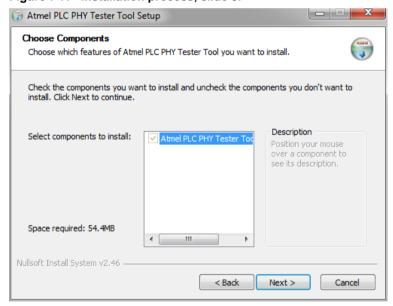

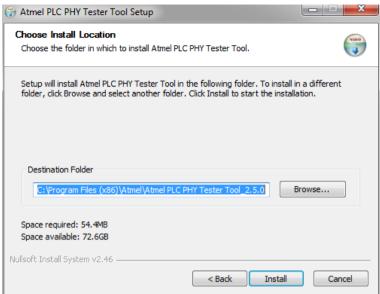

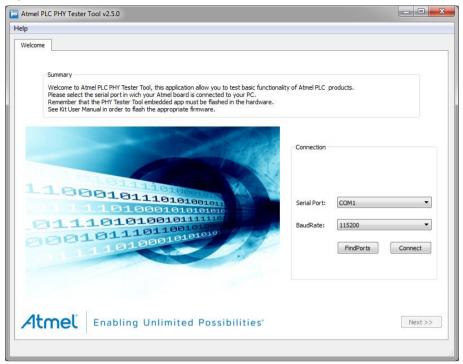

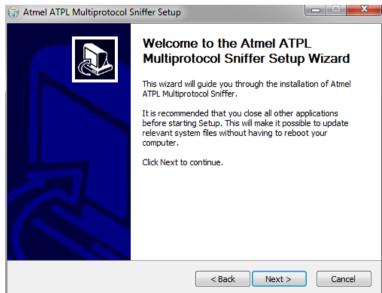

To install Atmel PLC PHY Tester tool in a Windows Operating System, execute the provided installer in the Tools folder: ".\PCTools\ATMEL\_PLC\_PHY\_Tester\ATMEL\_PLC\_PHY\_Tester\_Tool\_vX.Y.Z.exe", and follow the installation wizard. The installer wizard should open. To follow with the installation, click Next.

Figure 7-5. Installation process, slide 1.

Select the users' permissions and click Next.

Figure 7-6. Installation process, slide 2.

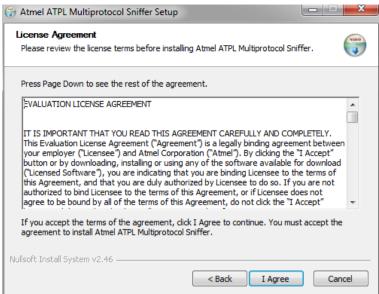

Click I Agree to continue.

Figure 7-7. Installation process, slide 3.

Click Next.

Figure 7-8. Installation process, slide 4.

Setup will install the program in the *Destination Folder*. To install in a different folder, click Browse and select your destination folder. Click Install.

Figure 7-9. Installation process, slide 5.

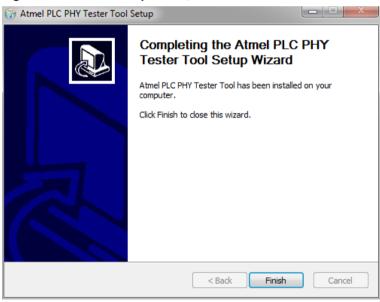

Click Finish.

Now the program is installed in your computer and a shortcut should have been created in your desktop.

Note that Atmel releases of G3-PLC versions lower than 1.2.2 run with PHY Tester PC Tool version 2.4.6. Atmel G3-PLC version 1.2.2 or above run with PHY Tester PC Tool version 2.5.0 or above.

# 7.2.2 Supplying the boards

Kit is provided with power cord cable in order to connect the board to the mains. Mains connector is shown below in Figure 7-10. Please connect the provided power cord cable with the kit to the *Power Cord Connector*, *J1*, in order to supply the board.

Figure 7-10. ATPL250ABN mains and voltage jumper selector.

Note that the ATPL250ABN board can be supplied either with 100V<sub>AC</sub> or 230V<sub>AC</sub> by setting the proper jumpers in the voltage selector, J2, as depicted in the Figure 7-11. By default, voltage jumper is set for 230V<sub>AC</sub>. For more information about power supply section, see section 3.5.1.

Figure 7-11. Jumper configuration for 115V<sub>AC</sub> or 230V<sub>AC</sub>.

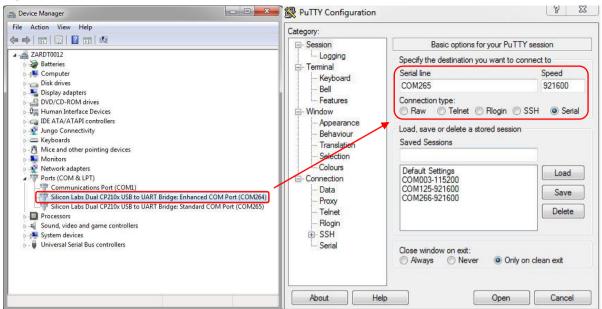

#### 7.2.3 USB connection

By default, the programmed firmware for Atmel PHY Tester tool establishes serial communication with **UARTO**. Boards have such UARTO available either by micro-B USB connector, J9, or the triple pin row CMOS connector, J16. See the Figure 3-2 and section 3.5.7.4 for more information about the USB device. PAN Coordinator Evaluation Kit is provided with one micro USB cable in order to connect the user's host(s) PC(s) with the PAN Coordinator board.

Previous to connect the USB cable to the micro-B USB connector and the host PC, supply the ATPL250ABN board. If the PC does not recognize the USB, download the USB driver from the manufacturer webpage or take it from the *PCTools* folder: ".\PCTools\USB\_Drivers". Once the driver is downloaded, unpack the driver archive to a folder on the host PC's hard-disk. Connect the USB cable to the board. The new hardware installation will recognize the new board and will guide you through the USB driver installation. When the wizard asks for the driver to install, navigate to the directory where the driver archive has been unpacked to.

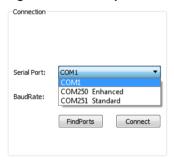

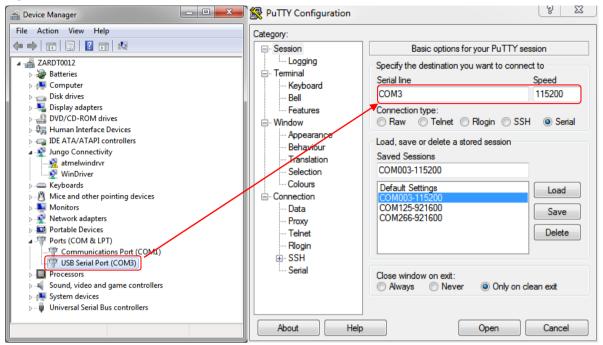

Identify the new hardware in the *Windows Device Manager*. The assigned COM port number is needed when configuring the PHY Tester tool application later. See the following figure for an example of a COM port assignment.

Figure 7-12. Windows device manager.

As you can see in the figure above, the CP210x USB to UART Bridge Virtual COM Port (VCP) appears as two COM ports (Enhanced and Standard COM ports) in the Device Manager. They are assigned the lowest available COM ports for operation. In the ATPL250ABN design, the Enhanced COM port corresponds to UARTO, so select the Enhanced COM Port when you use the Atmel PLC PHY Tester PC tool.

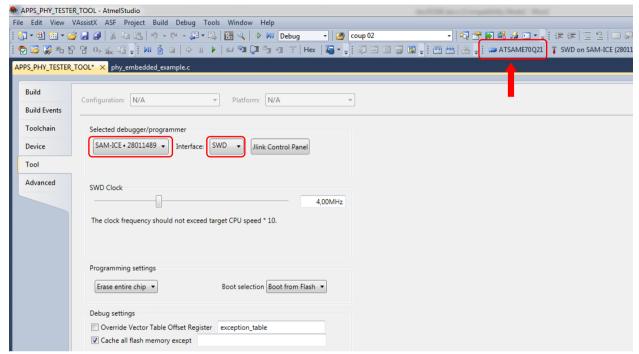

### 7.2.4 Programming the embedded file

To be able to develop applications, build binaries and program the firmware on the SAME70Q21 device, you can use the IAR Workbench, Keil  $\mu$ Vision or Atmel Studio. For that, open the IDE tool used, select the PHY Tester tool project and now build it to generate the output file.

Remember that the J-Link USB drivers must have been downloaded previously from the Segger webpage (see section 7.1.5) and they depend on your operating system. In order to program the firmware on the board, set the JTAG probe, SAM-ICE, on the JTAG connector, J13 (see section about JTAG programming mode, 3.5.7.1).

Note that kits do not provide a J-Link ARM or SAM-ICE JTAG probe in order to connect to the user's host PC and the boards to download and debug the projects.

The process to load the file should be as is explained below; in that process we use a programming tool, J-Link Tool. Remember that the J-Link USB drivers must have been downloaded previously from the Segger webpage (see section 7.1.5) and they depend on your operating system:

- 1. Place the JTAG connector of the J-Link or SAM-ICE in the J13, JTAG connector of the board. Check pin number 1 of J13 connector to place the cable in the right position.

- 2. Switch on the power supply of the board.

- Launch the IAR, Keil or Atmel Studio and select the PHY Tester tool project. Now you can download

the file to the board. Build the project apps\_phy\_tester\_tool.atsIn or apps\_phy\_tester\_tool.eww or

apps\_phy\_tester\_tool\_flash.uvprojx to generate the output file to program. Now you can download

the file to the board. In case of programming with Atmel Studio IDE, select the interface to SWD to download the output file. By default, JTAG option is selected. That option is found in Tool tab of Device (ATSAME70Q21) button toolbar. See the following figure.

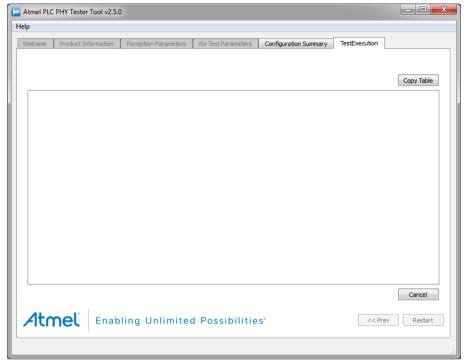

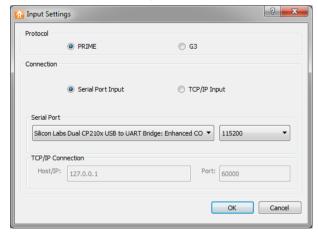

Figure 7-13. Atmel Studio debugger/programmer settings.