Le79124

# Next Generation VoiceEdge<sup>™</sup> Control Processor **Next Generation Carrier Chipset (NGCC)**

**Data Sheet**

# **Applications**

- Cost effective voice solution for long or short loops providing POTS and integrated test capabilities

- Applications include: IVD, DLC, CO, Voiceenabled DSLAM, PBX/KTS, MDU, MSAP, MSAN

#### **Features**

- Aggregated call control lowers demand on host micro-processor

- 72 channels of call control

- Provides expanded line and circuit testing in conjunction with Microsemi's NGCC chipset

- · Provides 4 channels of simultaneous line testina

- Software interface using VoicePath™ API-II

- Software downloadable, field upgradeable, expandable

- Serial and parallel host controller interface options

- Complete control of up to 9 Octal NGSLAC devices

- Two master SPI ports

- 32 General Purpose I/Os

- 9 configured as chip selects

- 9 configured for interrupts

- Two slave PCM highway ports

- Single or dual PCM highways capable of operating up to 16.384 MHz

- Separate test highway option

- Internal PLL and hardware network timing recovery for creating analog sampling clocks

- 3.3 V compliant I/O; Internal 3.3 V to 1.8 V linear regulator for the core logic

## Description

The Le79124 Next Generation VoiceEdge Control Processor (VCP) is a second generation platform that delivers enhanced call control, self-test and line test capabilities. This latest processor works Microsemi NGCC devices using its SPI interface(s),

Document ID#:081567 Version 11 November 2011

|    | Ordering Information |                                   |                |  |  |  |  |  |  |  |

|----|----------------------|-----------------------------------|----------------|--|--|--|--|--|--|--|

|    | Device               | Package                           | Packing        |  |  |  |  |  |  |  |

|    | Le79124KVC           | 128 Pin TQFP (Green) <sup>1</sup> | Tray           |  |  |  |  |  |  |  |

|    | Le79124KVCT          | 128 Pin TQFP (Green) <sup>1</sup> | Tape&Reel      |  |  |  |  |  |  |  |

|    | ZL79124GDG           | 144 Pin LBGA <sup>2</sup>         | Tray           |  |  |  |  |  |  |  |

|    | ZL79124GDG2          | 144 Pin LBGA <sup>3</sup>         | Tray           |  |  |  |  |  |  |  |

| 1. | The green packag     | ge meets RoHS Directive 2002      | 2/95/EC of the |  |  |  |  |  |  |  |

|    | F                    |                                   | -1:            |  |  |  |  |  |  |  |

- European Council to minimize the environmental impact of electrical equipment.

- The ZL79124GDG package is RoHS-5 compliant.

- The ZL79124GDG2 package is RoHS-6 compliant.

PCM port(s) and GPIO. The Le79124 device provides the same integrated line-testing and feature-set as the Le79112 device, plus additional capabilities such as 4 channels of simultaneous line testing and 72 channels of improved POTS control.

This product enables the design of a low-cost, highperformance, fully software programmable line interface with worldwide applicability, All AC, DC, and signaling parameters are programmable.

The Le79124 device is provided with extensive software and support, through the LineCare™ software suite, enabling the designer to develop a fully programmable solution in the least amount of time.

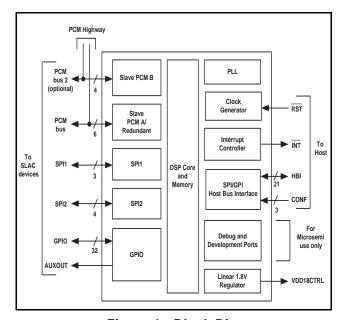

Figure 1 - Block Diagram

# **Related Literature**

- 126583 NGCC Hardware Design Guide

- 081555 Le79271 NGSLIC Device Data Sheet

- 138884 Le79272 Dual NGSLIC Device Data Sheet

- 081193 Le79238 Octal NGSLAC Device Data Sheet

- 136868 ZL79258 Octal External Ringing NGSLAC Device Data Sheet

- 127671 Le79124-SW NGVCP Software Data Sheet

- 139365 Le79128 NGVCP Data Sheet

- 133514 Le79234 NGVCP Data Sheet

- 129907 VoicePath<sup>TM</sup> API-II Reference Guide VCP/VCP2-BT/AT/ATP/TH

- 129908 VoicePath<sup>TM</sup> API-II Reference Guide VCP/VCP2-NT

# **Table of Contents**

| 1.0 Connection Diagrams                                   | 7          |

|-----------------------------------------------------------|------------|

| 2.0 Pin Descriptions                                      | 10         |

| 3.0 Electrical Characteristics                            | 16         |

| 3.1 Absolute Maximum Ratings                              |            |

| 3.1.1 Package Assembly                                    |            |

| 3.2 Operating Ranges                                      |            |

| 3.2.1 Environmental Ranges                                |            |

| 3.2.2 Electrical Ranges                                   | . , . , 16 |

| 3.3 DC Specifications                                     |            |

| 4.0 Host Bus Interface (HBI) Overview                     |            |

| 4.0.0.1 Transport Layer                                   |            |

| 4.0.0.2 Application Layer                                 |            |

| 4.0.0.3 Physical Layer                                    |            |

| 5.0 Transport Layer                                       |            |

| 5.1 Interface Addressing                                  |            |

| 5.2 Command Structure                                     |            |

| 5.2.1 Paged Offset Access                                 |            |

| 5.2.2 Direct Offset Access.                               |            |

| 5.2.3 Start Paged Access                                  |            |

| 5.2.4 Continue Paged Access                               | 21         |

| 5.2.5 Select Page                                         | 21         |

| 5.2.6 Configure Interface                                 | 21         |

| 5.2.7 NOP                                                 |            |

| 5.3 VCP Direct Page Hardware Register Summary             | 22         |

| 5.4 Direct Page (Hardware) Registers                      | 23         |

| 5.5 Code Loading                                          | 32         |

| 5.6 Host Boot Procedure                                   | 33         |

| 6.0 Application Layer                                     | 33         |

| 6.1 Software (Application Derived) Registers              | 33         |

| 6.1.1 Mailboxes Buffers                                   |            |

| 6.1.2 Command/Response Mailboxes                          |            |

| 6.1.3 Event Queue                                         |            |

| 7.0 Physical Layer                                        |            |

| 7.1 General Purpose Parallel Interface (GPI)              |            |

| 7.1.1 GPI External Pin List                               |            |

| 7.1.2 GPI Features                                        |            |

| 7.1.3 GPI Connections to an External Host                 |            |

| 7.1.4 GPI Timing Requirements                             |            |

| 7.2 Serial Peripheral Interface (SPI)                     |            |

| 7.2.1 SPI External Pins Connection                        |            |

| 7.2.2 SPI Features                                        | 43         |

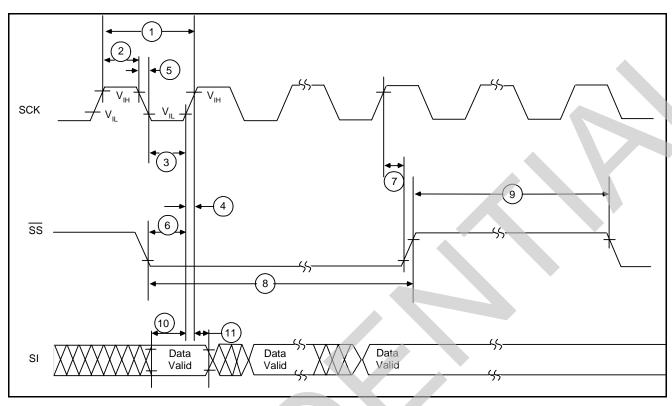

| 7.2.3 SPI Timing Requirements                             | 45         |

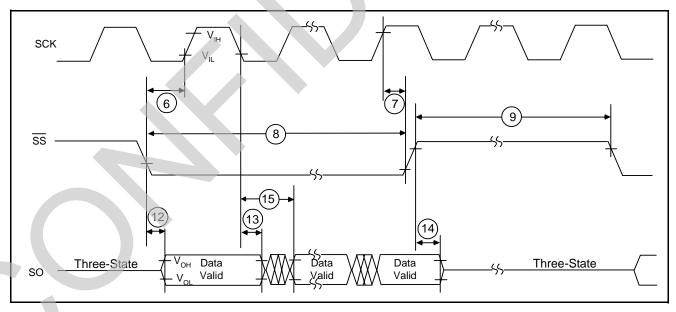

| 7.3 SPI1 and SPI2 Timing                                  | 48         |

| 7.3.1 Timing Requirements                                 | 49         |

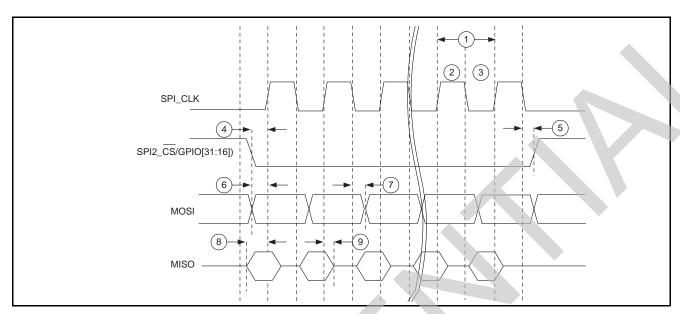

| 8.0 PCM Interface                                         |            |

| 9.0 The VCP Device Interrupt Report and Service Mechanism |            |

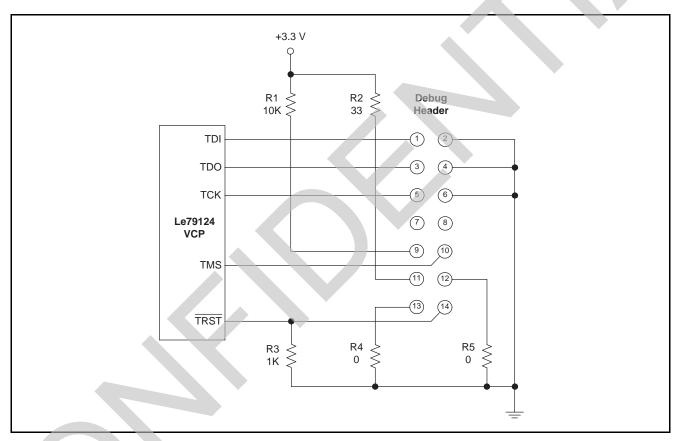

| 10.0 Debug Interface                                      |            |

|                                                           |            |

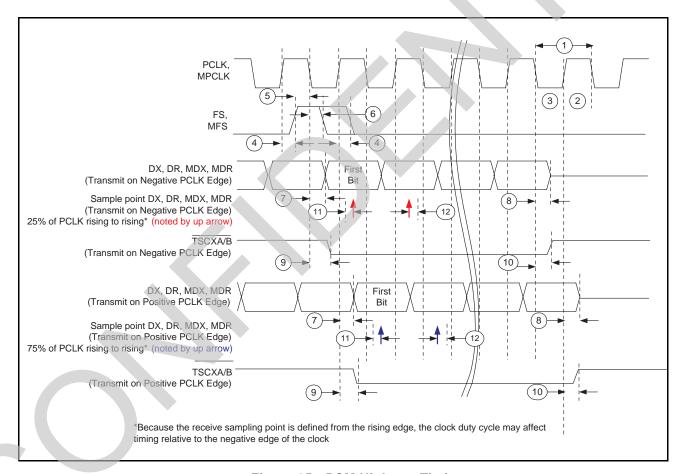

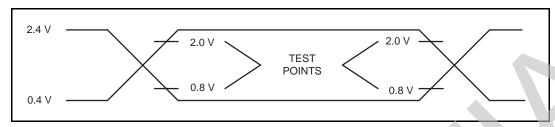

| 11.0 Timing Diagram Test Points                           |            |

| 12.0 Troubleshooting at Initial Start-up                  |            |

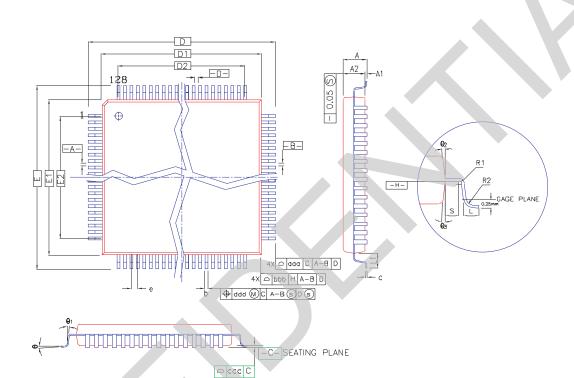

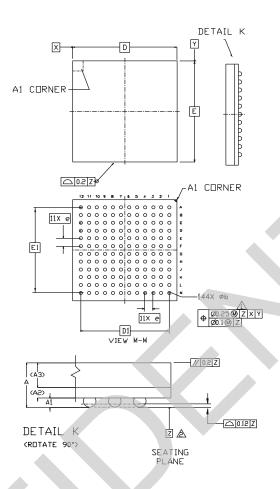

| 13.0 Physical Dimensions                                  | 55         |

|                                                           |            |

# **Table of Contents**

| 13.1 128-Pin TQFP                  | 55   |

|------------------------------------|------|

| 13.2 144-Pin LBGA                  |      |

| 14.0 Revision History              | . 57 |

| 14.1 Revision D1 to E1             |      |

| 14.2 Revision E1 to F1             |      |

| 14.3 Revision F1 to G1             |      |

| 14.4 Revision G1 to H1             |      |

| 14.5 Revision H1 to I1 (Version 8) | 57   |

| 14.6 Version 8 to Version 9        |      |

| 14.7 Version 9 to Version 10       |      |

| 14.8 Version 10 to Version 11      | 58   |

# **List of Figures**

| Figure 1 - Block Diagram                                                      | 1    |

|-------------------------------------------------------------------------------|------|

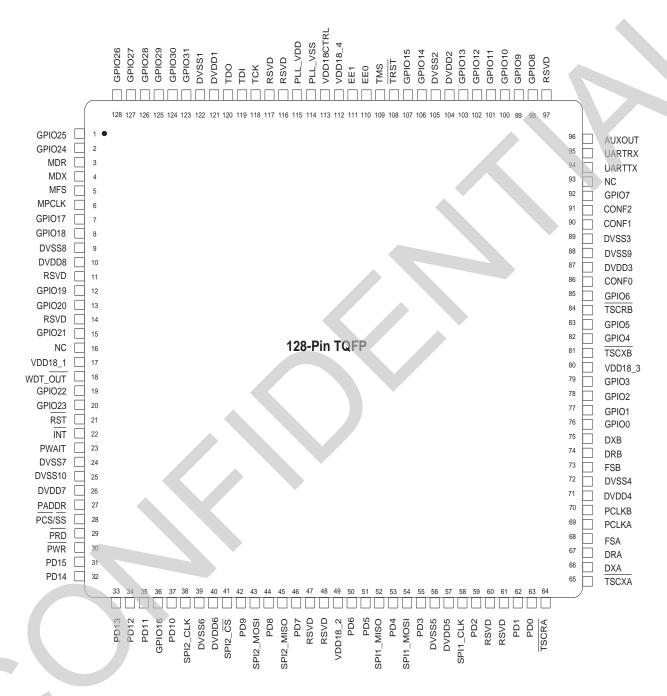

| Figure 2 - Le79124KVC 128-Pin TQFP Package                                    |      |

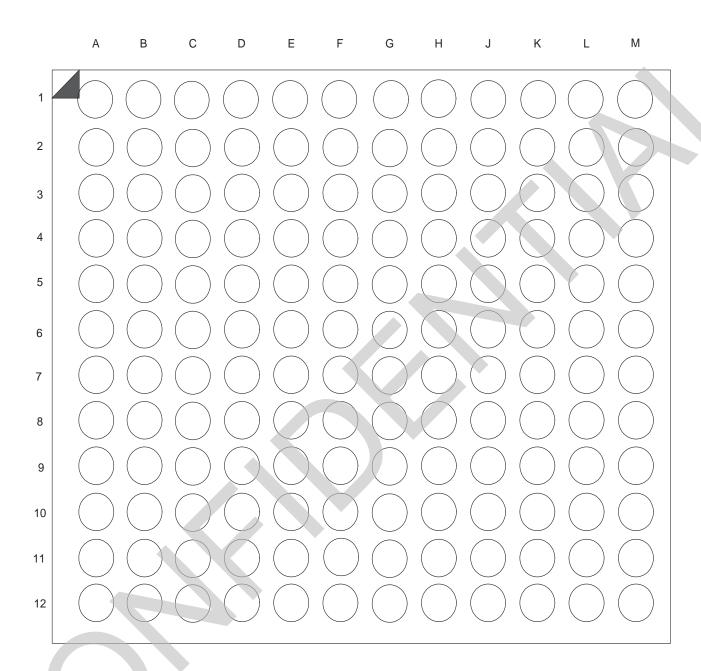

| Figure 3 - ZL79124GDG 144-Pin LBGA Diagram                                    |      |

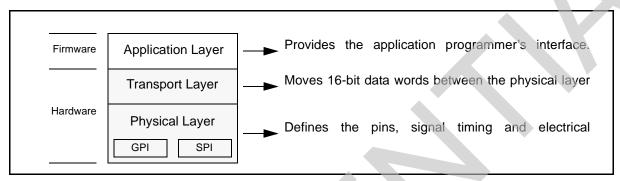

| Figure 4 - Host Bus Interface Layers                                          |      |

| Figure 5 - Host Bus Interface Address Mode                                    | . 19 |

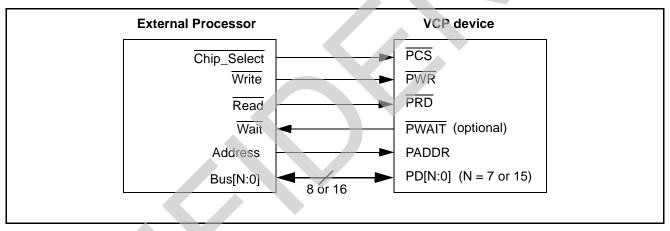

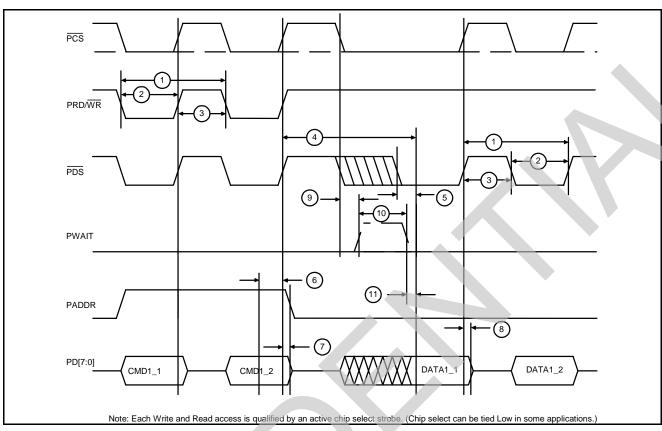

| Figure 6 - GPI Connections Using Separate Read and Write Strobes              | . 36 |

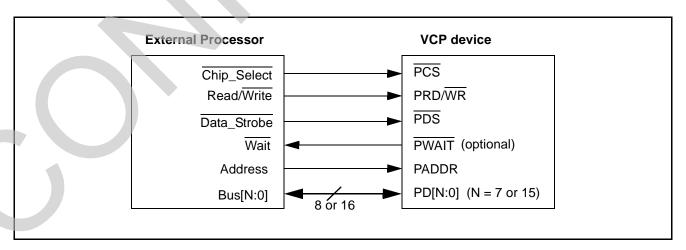

| Figure 7 - GPI Connections Using Combined Read/Write and Data Strobes         | . 36 |

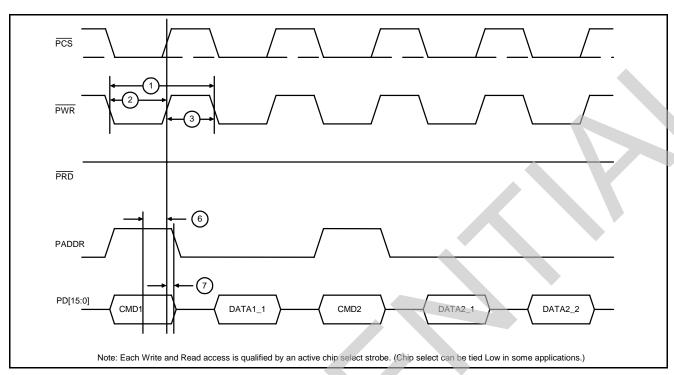

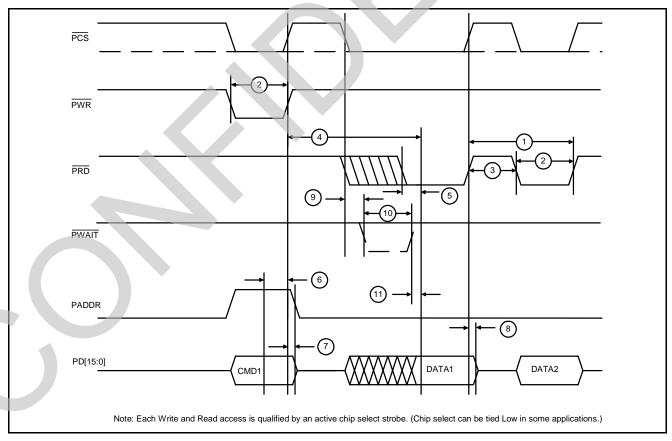

| Figure 8 - GPI 16-Bit Write Access Using Separate Read and Write Strobes      | . 38 |

| Figure 9 - GPI 16-Bit Read Access Using Separate Read and Write Strobes       | . 38 |

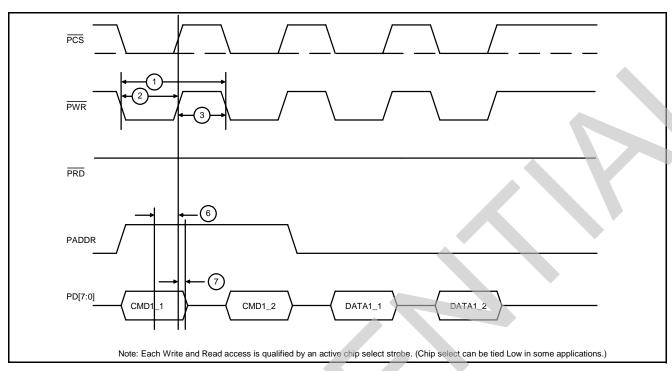

| Figure 10 - GPI 8-Bit Write Access Using Separate Read and Write Strobes      | . 39 |

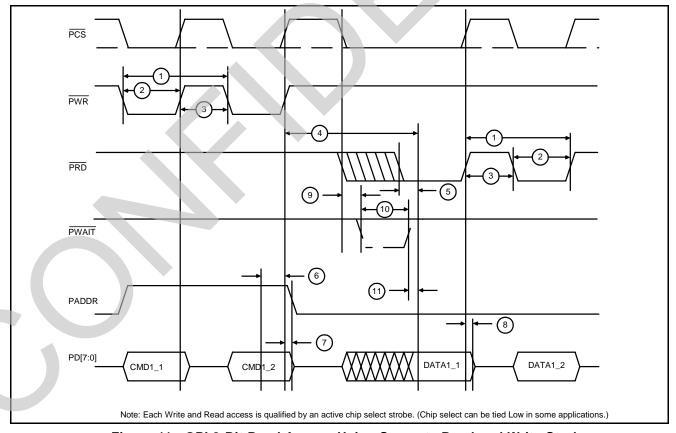

| Figure 11 - GPI 8-Bit Read Access Using Separate Read and Write Strobes       | . 39 |

| Figure 12 - GPI 8-Bit Write Access Using Combined Read/Write and Data Strobes | . 40 |

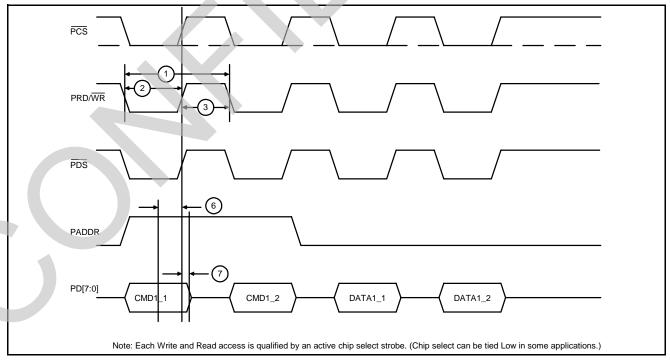

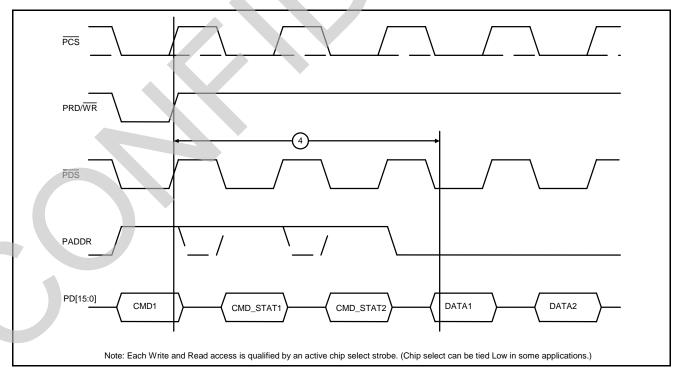

| Figure 13 - GPI 8-Bit Read Access Using Combined Read/Write and Data Strobes  | . 41 |

| Figure 14 - GPI Read Status Register Access                                   | . 41 |

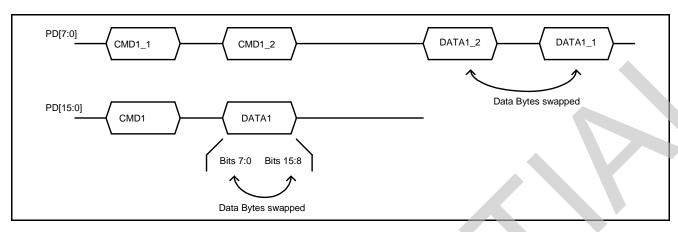

| Figure 15 - GPI Data Byte Swap Access                                         | . 42 |

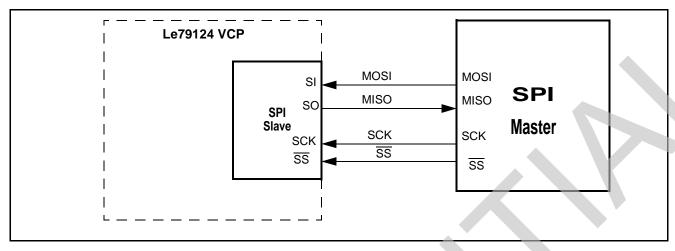

| Figure 16 - 4-Wire Master-Slave Connections                                   | . 43 |

| Figure 17 - 3-Wire Master-Slave Connections                                   | . 43 |

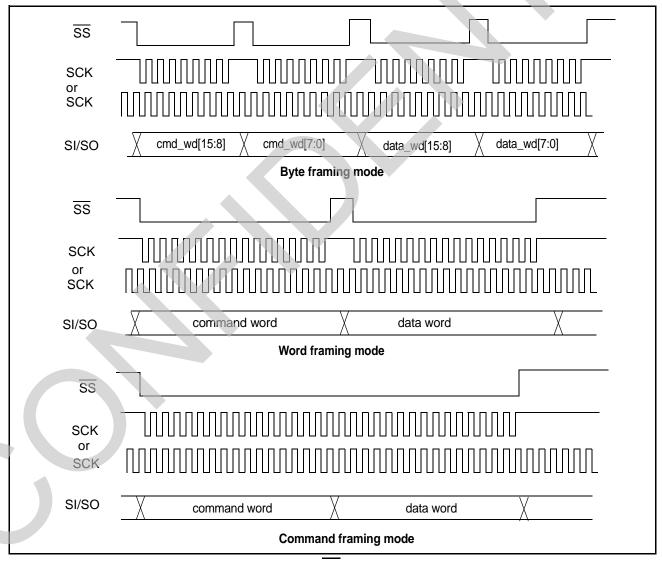

| Figure 18 - SS Framing Modes                                                  | . 44 |

| Figure 19 - One Data Word Write in Byte Framing Mode                          | . 45 |

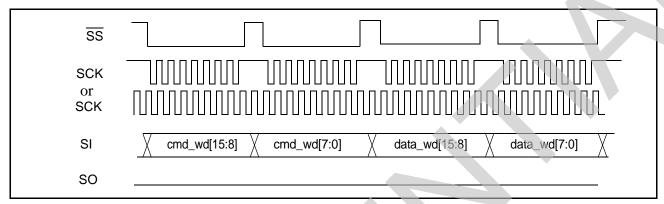

| Figure 20 - One Data Word Read in Word Framing Mode                           | . 45 |

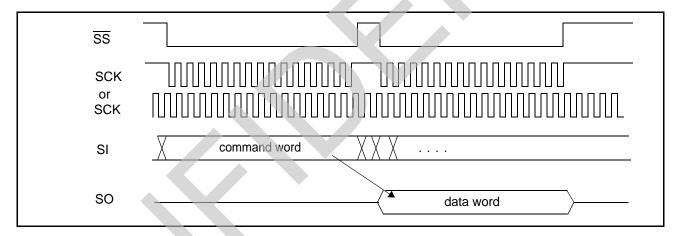

| Figure 21 - One Data Word Write in Byte Framing Mode with Byte Swap           | . 45 |

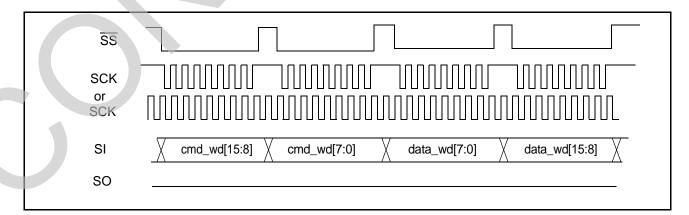

| Figure 22 - SPI Interface (Input Timing)                                      | . 47 |

| Figure 23 - SPI Interface (Output Timing)                                     | . 47 |

| Figure 24 - SPI Timing Waveforms                                              | . 49 |

| Figure 25 - PCM Highway Timing                                                | . 51 |

| Figure 26 - VCP Debug Port - Optional Header Interface                        | . 53 |

| Figure 27 - Timing Diagram Test Points                                        | . 54 |

# **List of Tables**

| Table 1 - ZL79124GDG 144-Pin LBGA Pin Numbers and Pin Names                    | 9  |

|--------------------------------------------------------------------------------|----|

| Table 2 - Le79124 VCP Device Pin Description (Host Interface Pins)             | 10 |

| Table 3 - Le79124 VCP Device Pin Description (PCM Interface Pins)              | 11 |

| Table 4 - Le79124 VCP Device Pin Description (Debug and Development Ports)     | 12 |

| Table 5 - Le79124 VCP Device Pin Description (Peripheral Logic Pins)           | 12 |

| Table 6 - Le79124 VCP Device Pin Description (Power Supply Pins)               | 14 |

| Table 7 - Le79124 VCP Device Pin Description (Control Pins)                    |    |

| Table 8 - Configuration Assignments (CONF2 - CONF0)                            |    |

| Table 9 - Host Bus Interface Transport Commands                                |    |

| Table 10 - VoiceEdge VCP Hardware Derived Register Space                       | 22 |

| Table 11 - CLKGEN Status Hardware Reset Controls                               |    |

| Table 12 - Boot Sense Pin Definitions                                          |    |

| Table 13 - GPI Pins                                                            |    |

| Table 14 - GPI Interface Access Types                                          | 36 |

| Table 15 - GPI Bus Timing Parameters for Separate Read and Write Strobes1      | 37 |

| Table 16 - GPI Bus Timing Parameters for Combined Read/Write and Data Strobes1 | 40 |

| Table 17 - SPI Signals                                                         | 42 |

| Table 18 - SPI Timing Parameters                                               |    |

| Table 19 - SPI1 and SPI2 Timing Parameters                                     |    |

| Table 20 - PCM Interface Timing Parameters                                     |    |

# 1.0 Connection Diagrams

Figure 2 - Le79124KVC 128-Pin TQFP Package

# **BOTTOM VIEW**

Figure 3 - ZL79124GDG 144-Pin LBGA Diagram

| LBGA<br>Pin# | Pin Name  | LBGA<br>Pin# | Pin Name | LBGA<br>Pin# | Pin Name | LBGA<br>Pin# | Pin Name             |

|--------------|-----------|--------------|----------|--------------|----------|--------------|----------------------|

| A1           | MDR       | D1           | MPCLK    | G1           | DVSS1    | K1           | PRD (PRD/WR or SI)   |

| A2           | GPIO24    | D2           | GPIO18   | G2           | GPIO21   | K2           | PWR (PDS or SCK)     |

| А3           | GPIO26    | D3           | GPIO28   | G3           | DVDD1    | K3           | PCS/SS               |

| A4           | RSVD      | D4           | DVDD2    | G4           | VDD18_1  | K4           | PD <sub>9</sub>      |

| A5           | TDO       | D5           | DVSS4    | G5           | NC       | K5           | PD <sub>6</sub>      |

| A6           | PLL_VDD   | D6           | VDD18_2  | G6           | VDD18_3  | K6           | PD <sub>3</sub>      |

| A7           | VDD18CTRL | D7           | DVSS7    | G7           | NC       | K7           | PD <sub>0</sub>      |

| A8           | GPIO15    | D8           | DVSS9    | G8           | NC       | K8           | SPI2_CLK             |

| A9           | GPIO14    | D9           | VDD18_5  | G9           | DVSS12   | K9           | SPI2_CS              |

| A10          | GPIO11    | D10          | GPIO6    | G10          | VDD18_6  | K10          | SPI1_CLK             |

| A11          | GPIO9     | D11          | GPIO7    | G11          | GPIO1    | K11          | TSCRA                |

| A12          | RSVD      | D12          | CONF1    | G12          | GPIO2    | K12          | FSA                  |

| B1           | MDX       | E1           | RSVD     | H1           | RST      | L1           | PD <sub>15</sub>     |

| B2           | GPIO25    | E2           | GPIO19   | H2           | ĪNT      | L2           | PD <sub>13</sub>     |

| В3           | GPIO27    | E3           | GPIO22   | НЗ           | GPIO16   | L3           | PD <sub>11</sub>     |

| B4           | RSVD      | E4           | DVDD3    | H4           | DVSS3    | L4           | PD <sub>8</sub>      |

| B5           | TDI       | E5           | NC       | H5           | NC       | L5           | PD <sub>5</sub>      |

| B6           | TCK       | E6           | NC       | H6           | NC       | L6           | PD <sub>2</sub>      |

| B7           | PLL_VSS   | E7           | NC       | H7           | NC       | L7           | AUXOUT               |

| B8           | EE0       | E8           | NC       | H8           | NC       | L8           | RSVD                 |

| B9           | GPIO13    | <b>E</b> 9   | DVDD6    | H9           | DVDD7    | L9           | SPI2_MISO            |

| B10          | GPIO10    | E10          | TSCRB    | H10          | GPIO0    | L10          | SPI1_MISO            |

| B11          | GPIO8     | E11          | GPIO5    | H11          | DRB      | L11          | TSCXA                |

| B12          | RSVD      | E12          | CONF0    | H12          | FSB      | L12          | DRA                  |

| C1           | MFS       | F1           | RSVD     | J1           | WDT_OUT  | M1           | PD <sub>14</sub>     |

| C2           | GPIO17    | F2           | GPIO20   | J2           | PADDR    | M2           | PD <sub>12</sub>     |

| C3           | GPIO29    | F3           | GPIO23   | J3           | PWAIT    | M3           | PD <sub>10</sub>     |

| C4           | GPIO30    | F4           | DVSS2    | J4           | DVDD4    | M4           | PD <sub>7</sub> (SO) |

| C5           | GPIO31    | F5           | NC       | J5           | DVSS5    | M5           | PD <sub>4</sub>      |

| C6           | TMS       | F6           | DVDD5    | J6           | DVSS6    | M6           | PD <sub>1</sub>      |

| C7           | TRST      | F7           | DVSS8    | J7           | VDD18_4  | M7           | RSVD                 |

| C8           | EE1       | F8           | NC       | J8           | DVSS10   | M8           | RSVD                 |

| C9           | GPIO12    | F9           | DVSS11   | J9           | DVDD8    | M9           | SPI2_MOSI            |

| C10          | UARTRX    | F10          | TSCXB    | J10          | NC       | M10          | SPI1_MOSI            |

| C11          | UARTTX    | F11          | GPIO3    | J11          | DXB      | M11          | PCLKB                |

| C12          | CONF2     | F12          | GPIO4    | J12          | PCLKA    | M12          | DXA                  |

Table 1 - ZL79124GDG 144-Pin LBGA Pin Numbers and Pin Names

# 2.0 Pin Descriptions

Refer to the Next Generation Carrier Chipset Hardware Design Guide (Document ID 126583) for an Application Circuit and Parts List of external components.

All signals are CMOS levels unless otherwise stated.

| Pin Name<br>(Alternate) | TQFP<br>Pin # | LBGA<br>Pin # | Туре             | Reset <sup>1</sup>                      | Description                                                                                                                                                                                                                        |  |  |

|-------------------------|---------------|---------------|------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CONF <sub>2</sub>       | 91            | C12           | Input            | Z                                       | VCP configuration pins that determine serial or parallel modes (8-bit, 16-bit,                                                                                                                                                     |  |  |

| CONF <sub>1</sub>       | 90            | D12           | Input            | Z                                       | separate read and write strobes, data strobe and combined read/write                                                                                                                                                               |  |  |

| CONF <sub>0</sub>       | 86            | E12           | Input            | Z                                       | strobe). See Table 8 for configuration summary.                                                                                                                                                                                    |  |  |

| PCS/SS                  | 28            | КЗ            | Input            | Z                                       | PCS: Parallel interface: active-low chip select.  SS: Serial interface: active-low slave select.                                                                                                                                   |  |  |

| PRD (PRD/<br>WR or SI)  | 29            | K1            | Input            | Z                                       | PRD: Parallel Separate Rd/Wr strobe: active-low read strobe. PRD/WR: Parallel Combined Rd/Wr strobe: active-high read control/active-low write control. SI: Serial interface: data input.                                          |  |  |

| PWR (PDS or SCK)        | 30            | K2            | Input            | Z                                       | PWR: Parallel Separate Rd/Wr strobe: active-low write strobe PDS: Parallel Combined Rd/Wr strobe: active-low data strobe. SCK: Serial interface: data clock.                                                                       |  |  |

| PD <sub>15</sub>        | 31            | L1            |                  |                                         |                                                                                                                                                                                                                                    |  |  |

| PD <sub>14</sub>        | 32            | M1            |                  |                                         |                                                                                                                                                                                                                                    |  |  |

| PD <sub>13</sub>        | 33            | L2            |                  | Z/Keeper                                |                                                                                                                                                                                                                                    |  |  |

| PD <sub>12</sub>        | 34            | M2            | Input/           |                                         | 16-bit parallel interface: bi-directional data bits 15-8.                                                                                                                                                                          |  |  |

| PD <sub>11</sub>        | 35            | L3            | Output           |                                         | Serial interface: reserved.                                                                                                                                                                                                        |  |  |

| PD <sub>10</sub>        | 37            | МЗ            |                  |                                         |                                                                                                                                                                                                                                    |  |  |

| PD <sub>9</sub>         | 42            | K4            |                  |                                         |                                                                                                                                                                                                                                    |  |  |

| PD <sub>8</sub>         | 44            | L4            |                  |                                         |                                                                                                                                                                                                                                    |  |  |

| PD <sub>7</sub> (SO)    | 46            | M4            | Input/<br>Output | Z/Pull-down<br>(Parallel)<br>Z (Serial) | PD <sub>7</sub> : Parallel interface: bi-directional data bit 7. SO: Serial interface: data output.                                                                                                                                |  |  |

| PD <sub>6</sub>         | 50            | K5            |                  |                                         |                                                                                                                                                                                                                                    |  |  |

| PD <sub>5</sub>         | 51            | L5            |                  |                                         |                                                                                                                                                                                                                                    |  |  |

| PD <sub>4</sub>         | 53            | M5            |                  |                                         |                                                                                                                                                                                                                                    |  |  |

| PD <sub>3</sub>         | 55            | K6            | Input/<br>Output | Z/Keeper                                | Parallel interface: bi-directional data bits 6 through 0. Serial interface: reserved.                                                                                                                                              |  |  |

| PD <sub>2</sub>         | 59            | L6            | Output           |                                         | Serial interface, reserved.                                                                                                                                                                                                        |  |  |

| PD <sub>1</sub>         | 62            | M6            | 1                |                                         |                                                                                                                                                                                                                                    |  |  |

| PD <sub>0</sub>         | 63            | K7            | ĺ                |                                         |                                                                                                                                                                                                                                    |  |  |

| PWAIT                   | 23            | J3            | Output           | Z                                       | Parallel interface: programmable active-low or active-high signal to extend the current access cycle. PWAIT should be connected to a resistor pulled to the inactive state. If unused, let pin float.  Serial interface: reserved. |  |  |

| PADDR                   | 27            | J2            | Input            | Z                                       | Parallel interface: signal to indicate the start of a command sequence.  Serial interface: reserved.                                                                                                                               |  |  |

| ĪNT                     | 22            | H2            | Output           | Z/Pull-up                               | Host Interrupt indicator (active low).                                                                                                                                                                                             |  |  |

Table 2 - Le79124 VCP Device Pin Description (Host Interface Pins)

| Pin<br>Name | TQFP<br>Pin# | LBGA<br>Pin# | Reset <sup>1</sup> | Description            |                                   |                                                                                                                                                                                                                                                    |  |  |

|-------------|--------------|--------------|--------------------|------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PCLKA       | 69           | J12          | Z                  |                        | Clock input.                      | Mutually exclusive with PCLKB operation.                                                                                                                                                                                                           |  |  |

| FSA         | 68           | K12          | Z                  |                        | Framing input. <sup>2</sup>       | Mutually exclusive with FSB operation.                                                                                                                                                                                                             |  |  |

| DXA         | 66           | M12          | Z                  |                        | PCM data output.3                 | Mutually exclusive with DXB operation.                                                                                                                                                                                                             |  |  |

| DRA         | 67           | L12          | Z                  |                        | PCM data input. <sup>2</sup>      | Mutually exclusive with DRB operation.                                                                                                                                                                                                             |  |  |

| TSCXA       | 65           | L11          | Z                  | Slave PCM<br>Highway A | PCM data output tristate control. | Mutually exclusive with TSCXB operation. This output is active low when DXA is transmitting. The output is open-drain and is normally inactive (high impedance). A pull-up load should be connected to DVDD. If output not used, leave node float. |  |  |

| TSCRA       | 64           | K11          | Z                  |                        | PCM data input tristate control.  | Mutually exclusive with TSCRB operation. This output is active low when DRA is transmitting. The output is open-drain and is normally inactive (high impedance). A pull-up load should be connected to DVDD. If output not used, leave node float. |  |  |

| PCLKB       | 70           | M11          | Z                  |                        | Clock input.                      | Mutually exclusive with PCLKA operation. If not used, tie pin to DVSS.                                                                                                                                                                             |  |  |

| FSB         | 73           | H12          | Z                  |                        | Framing input. <sup>2</sup>       | Mutually exclusive with FSA operation. If not used, tie pin to DVSS.                                                                                                                                                                               |  |  |

| DXB         | 75           | J11          | Z                  |                        | PCM data output.3                 | Mutually exclusive with DXA operation. If not used, tie pin to DVSS.                                                                                                                                                                               |  |  |

| DRB         | 74           | H11          | Z                  | Redundant<br>Slave PCM | PCM data input. <sup>2</sup>      | Mutually exclusive with DRA operation. If not used, tie pin to DVSS.                                                                                                                                                                               |  |  |

| TSCXB       | 81           | F10          | Z                  | Highway                | PCM data output tristate control. | Mutually exclusive with TSCXA operation. This output is active low when DXB is transmitting. The output is open-drain and is normally inactive (high impedance). A pull-up load should be connected to DVDD. If output not used, leave node float. |  |  |

| TSCRB       | 84           | E10          | Z                  |                        | PCM data input tristate control.  | Mutually exclusive with TSCRA operation. This output is active low when DRB is transmitting. The output is open-drain and is normally inactive (high impedance). A pull-up load should be connected to DVDD. If output not used, leave node float. |  |  |

| MPCLK       | 6            | D1           | Z                  |                        | Clock input. <sup>2</sup>         |                                                                                                                                                                                                                                                    |  |  |

| MFS         | 5            | C1           | Z                  | Slave PCM<br>Highway B | Framing input. <sup>2</sup>       | If not used, tie pin to DVSS.                                                                                                                                                                                                                      |  |  |

| MDX         | 4            | B1           | Z                  | (Optional)             | PCM data output.3                 | יוו ווטנ עספע, עפ אווו נט טיסס.                                                                                                                                                                                                                    |  |  |

| MDR         | 3            | A1           | Z                  |                        | PCM data input. <sup>2</sup>      |                                                                                                                                                                                                                                                    |  |  |

Table 3 - Le79124 VCP Device Pin Description (PCM Interface Pins)

Slave PCM Highway A has a Redundant Slave PCM Highway which can be used in parallel to PCM Highway A. When enabled, the VCP will automatically switch between Highway A and Redundant when either highway suffers a system failure. Slave PCM Highway A, or the Redundant Slave PCM Highway, is programmed by selecting VP\_OPTION\_HWY\_A from the API.

Slave PCM Highway B use is optional. It can be used as a second PCM Highway or as a Test Highway. Slave PCM Highway B is programmed by selecting VP\_OPTION\_HWY\_B from the API. Refer to the *Next Generation Carrier Chipset Hardware Design Guide* for diagrams on supported PCM Highway usage.

| Pin Name | TQFP<br>Pin # | LBGA<br>Pin # | Туре         | Reset <sup>1</sup> | Descr                                                        | iption                           |

|----------|---------------|---------------|--------------|--------------------|--------------------------------------------------------------|----------------------------------|

| TRST     | 108           | C7            | Input        | Pull-up            | Debug reset input. Tie to DVSS through 1 $K\Omega$ resistor. | These pins are for Microsemi     |

| TCK      | 118           | B6            | Input        | Pull-up            | Debug clock input.                                           | debug use only. Refer to the     |

| TMS      | 109           | C6            | Input        | Pull-up            | Debug mode select input.                                     | Debug Interface section for more |

| TDI      | 119           | B5            | Input        | Pull-up            | Debug data input.                                            | information.                     |

| TDO      | 120           | A5            | Output       | Z                  | Debug data output.                                           |                                  |

| EE0      | 110           | B8            | Input/Output | Z/Pull-down        | Emulator control pin.                                        | For Microsemi development use    |

| EE1      | 111           | C8            | Input/Output | Z/Pull-down        | Emulator debug output pin.                                   | only, leave pins float.          |

| UARTTX   | 94            | C11           | Output       | 1                  | Transmit pin.                                                | For Microsemi development use    |

| UARTRX   | 95            | C10           | Input        | Z/Pullup           | Receive pin.                                                 | only, leave pins float.          |

Table 4 - Le79124 VCP Device Pin Description (Debug and Development Ports)

| Pin Name (Alternate) | TQFP<br>Pin # | LBGA<br>Pin# | Туре             | Reset <sup>1</sup> | Description                                                                                     |

|----------------------|---------------|--------------|------------------|--------------------|-------------------------------------------------------------------------------------------------|

| SPI1_CLK             | 58            | K10          | Output           | 0                  | SPI1 clock output.                                                                              |

| SPI1_MOSI            | 54            | M10          | Input/<br>Output | Z                  | SPI1 Master output, Slave input.                                                                |

| SPI1_MISO            | 52            | L10          | Input            | Z                  | SPI1 Master input, Slave output.                                                                |

| SPI2_CS              | 41            | K9           | Output           | 1                  | SPI2 alternate chip select output.                                                              |

| SPI2_CLK             | 38            | K8           | Output           | 0                  | SPI2 clock output.                                                                              |

| SPI2_MOSI            | 43            | M9           | Input/<br>Output | Z                  | SPI2 Master output, Slave input. If unused, tie to DVSS through 10 K $\Omega$ resistor.         |

| SPI2_MISO            | 45            | L9           | Input            | Z                  | SPI2 Master input, Slave output. If unused, tie to DVSS through 10 $\mathrm{K}\Omega$ resistor. |

| GPIO0 (MINTO/TIMER0) | 76            | H10          |                  |                    | General Purpose I/O. Can function as an Interrupt input when                                    |

| GPIO1 (MINT1/TIMER1) | 77            | G11          |                  |                    | connected to a SLAC device. Also has timer input/output functionality.                          |

| GPIO2 (MINT2)        | 78            | G12          |                  |                    |                                                                                                 |

| GPIO3 (MINT3)        | 79            | F11          |                  |                    |                                                                                                 |

| GPIO4 (MINT4)        | 82            | F12          |                  |                    |                                                                                                 |

| GPIO5 (MINT5)        | 83            | E11          |                  |                    |                                                                                                 |

| GPIO6 (MINT6)        | 85            | D10          |                  |                    |                                                                                                 |

| GPIO7 (MINT7)        | 92            | D11          | Input/           | Z/Pullup           |                                                                                                 |

| GPIO8 (MINT8)        | 98            | B11          | Output           | Z/Fullup           | General Purpose I/O. Can function as an Interrupt input when                                    |

| GPIO9 (MINT9)        | 99            | A11          |                  |                    | connected to a SLAC device.                                                                     |

| GPIO10 (MINT10)      | 100           | B10          |                  |                    |                                                                                                 |

| GPIO11 (MINT11)      | 101           | A10          |                  |                    |                                                                                                 |

| GPIO12 (MINT12)      | 102           | C9           |                  |                    |                                                                                                 |

| GPIO13 (MINT13)      | 103           | В9           |                  |                    |                                                                                                 |

| GPIO14 (MINT14)      | 106           | A9           |                  |                    |                                                                                                 |

| GPIO15 (MINT15)      | 107           | A8           |                  |                    |                                                                                                 |

Table 5 - Le79124 VCP Device Pin Description (Peripheral Logic Pins)

| Pin Name (Alternate) | TQFP<br>Pin # | LBGA<br>Pin# | Туре   | Reset <sup>1</sup> | Description                                                                                                                       |             |  |                            |  |

|----------------------|---------------|--------------|--------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------|--|----------------------------|--|

| GPIO16 (MCSO)        | 36            | НЗ           |        |                    |                                                                                                                                   |             |  |                            |  |

| GPIO17 (MCS1)        | 7             | C2           |        |                    |                                                                                                                                   |             |  |                            |  |

| GPIO18 (MCS2)        | 8             | D2           |        |                    |                                                                                                                                   |             |  |                            |  |

| GPIO19 (MCS3)        | 12            | E2           |        |                    | General Purpose I/O. Can function as a gated Chip Select for a                                                                    |             |  |                            |  |

| GPIO20 (MCS4)        | 13            | F2           |        |                    | Serial slave device.                                                                                                              |             |  |                            |  |

| GPIO21 (MCS5)        | 15            | G2           |        |                    |                                                                                                                                   |             |  |                            |  |

| GPIO22 (MCS6)        | 19            | E3           |        | Z/Pull-down        |                                                                                                                                   |             |  |                            |  |

| GPIO23 (MCS7)        | 20            | F3           | Input/ | Input/             | Input/ (Note this                                                                                                                 | (Note, this |  |                            |  |

| GPIO24 (MCS8)        | 2             | A2           | Output | pull-down is       |                                                                                                                                   |             |  |                            |  |

| GPIO25 (MCS9)        | 1             | B2           |        |                    | ]                                                                                                                                 |             |  | present only during reset) |  |

| GPIO26 (MCS10)       | 128           | А3           |        |                    |                                                                                                                                   |             |  |                            |  |

| GPIO27 (MCS11)       | 127           | В3           |        |                    | General Purpose I/O. Can function as a gated Chip Select for a Serial slave device. These pins serve a dual purpose, they provide |             |  |                            |  |

| GPIO28 (MCS12)       | 126           | D3           |        |                    | boot up options for Microsemi use. Do not use pull-up devices on these nodes. Refer to Table 12 for more information.             |             |  |                            |  |

| GPIO29 (MCS13)       | 125           | C3           |        |                    | these hodes. Nelet to rable 12 for more information.                                                                              |             |  |                            |  |

| GPIO30 (MCS14)       | 124           | C4           |        |                    |                                                                                                                                   |             |  |                            |  |

| GPIO31 (MCS15)       | 123           | C5           |        |                    |                                                                                                                                   |             |  |                            |  |

| AUXOUT               | 96            | L7           | Output | 0                  | General Purpose I/O. Can function as a gated Chip Select for a Serial slave device.                                               |             |  |                            |  |

Table 5 - Le79124 VCP Device Pin Description (Peripheral Logic Pins)

| Pin Name  | TQFP<br>Pin # | LBGA<br>Pin# | Туре   | Description                                                                                                                                                                    |

|-----------|---------------|--------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLL_VDD   | 115           | A6           | Supply | Analog power supply, which must be connected to the digital power supply externally. It is important to provide a decoupling capacitor of 0.1 µF from PLL_VDD to PLL_VSS.      |

| PLL_VSS   | 114           | В7           | Ground | Analog ground. Analog and digital grounds must be connected externally to the same ground plane.                                                                               |

| DVDD1     | 121           | G3           |        |                                                                                                                                                                                |

| DVDD2     | 104           | D4           |        |                                                                                                                                                                                |

| DVDD3     | 87            | E4           |        |                                                                                                                                                                                |

| DVDD4     | 71            | J4           | Cumple | +3.3 V Digital power supply. This supply handles the 3.3 V external digital I/O devices. It is                                                                                 |

| DVDD5     | 57            | F6           | Supply | important to provide local decoupling capacitors of $0.1\mu\text{F}$ to the ground plane on each pin in addition to a parallel 10 $\mu\text{F}$ capacitor on the ground plane. |

| DVDD6     | 40            | E9           |        |                                                                                                                                                                                |

| DVDD7     | 26            | Н9           |        |                                                                                                                                                                                |

| DVDD8     | 10            | J9           |        |                                                                                                                                                                                |

| VDD18_1   | 17            | G4           |        |                                                                                                                                                                                |

| VDD18_2   | 49            | D6           | Supply | +1.8 V Digital power supply. It is important to provide local decoupling capacitors of 0.1 μF to                                                                               |

| VDD18_3   | 80            | G6           |        | the ground plane on each pin in addition to a parallel 10 µF capacitor on the ground plane.                                                                                    |

| VDD18_4   | 112           | J7           |        |                                                                                                                                                                                |

| VDD18_5   | _             | D9           |        |                                                                                                                                                                                |

| VDD18_6   | _             | G10          |        |                                                                                                                                                                                |

| DVSS1     | 122           | G1           |        |                                                                                                                                                                                |

| DVSS2     | 105           | F4           |        |                                                                                                                                                                                |

| DVSS3     | 89            | H4           |        |                                                                                                                                                                                |

| DVSS4     | 72            | D5           |        |                                                                                                                                                                                |

| DVSS5     | 56            | J5 (         |        |                                                                                                                                                                                |

| DVSS6     | 39            | J6           | Ground | Digital ground. Digital and analog grounds must be connected.                                                                                                                  |

| DVSS7     | 24            | D7           |        |                                                                                                                                                                                |

| DVSS8     | 9             | F7           |        |                                                                                                                                                                                |

| DVSS9     | 88            | D8           |        |                                                                                                                                                                                |

| DVSS10    | 25            | J8           |        |                                                                                                                                                                                |

| DVSS11    | 7             | F9           |        |                                                                                                                                                                                |

| DVSS12    | - 1           | G9           |        |                                                                                                                                                                                |

| VDD18CTRL | 113           | A7           | Output | +1.8 V linear regulator gate drive output. Generally not used, leave pin float.                                                                                                |

Table 6 - Le79124 VCP Device Pin Description (Power Supply Pins)

| Pin Name | TQFP Pin #                                 | LBGA Pin #                                                          | Type   | Reset <sup>1</sup> | Description                                                                                                                                                                                                                                                                      |

|----------|--------------------------------------------|---------------------------------------------------------------------|--------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RST      | 21                                         | H1                                                                  | Input  | Z                  | Active Low reset input returns chip to default state. RST pulse width must be a minimum of 100 ns. If a capacitor to DVSS is used on this pin, as required by some applications, then the minimum RST pulse width is increased to 100 µs. This pin must be externally pulled up. |

| WDT_OUT  | 18                                         | J1                                                                  | Output | Z                  | Active Low, open-drain output from Watchdog timer function. Triggers on watchdog timer expiration and power on reset. The minimum pulse width for WDT_OUT is 1 ms. This pin must be shorted to RST if the watchdog function is desired to reset the VCP or system.               |

| RSVD     | 11, 14, 47,<br>48, 60, 61,<br>97, 116, 117 | A4, A12, B4,<br>B12, E1, F1,<br>L8, M7, M8                          |        |                    | Reserved. These pins are internally connected. Pins must be left floating.                                                                                                                                                                                                       |

| NC       | 16, 93                                     | E5, E6, E7,<br>E8, F5, F8,<br>G5, G7, G8,<br>H5, H6, H7,<br>H8, J10 |        |                    | No connect. These pins are not internally connected. Pins can be used as tie points.                                                                                                                                                                                             |

Table 7 - Le79124 VCP Device Pin Description (Control Pins)

#### Note:

1. Logic state after reset.

Z = No state driven, high impedance.

1 = Logic high.

0 = Logic low.

Keeper = Kept in current state, not allowed to float.

Pull-up = Internal pull-up provided.

Pull-down = Internal pull-down provided.

- 2. Used as an input, but pin has I/O capability.

- 3. Used as an output, but pin has I/O capability.

| CONF <sub>2</sub> - CONF <sub>0</sub> | Host Interface | Parallel Data Width | Parallel Read/Write Strobes |

|---------------------------------------|----------------|---------------------|-----------------------------|

| 000                                   | Parallel       | 8                   | Combined                    |

| 001                                   | Parallel       | 8                   | Separate                    |

| 010                                   | Parallel       | 16                  | Combined                    |

| 011                                   | Parallel       | 16                  | Separate                    |

| 100                                   | Serial         | NA                  | NA                          |

| 101                                   |                |                     | ·                           |

| 110                                   |                | Reserved            |                             |

| 111                                   |                |                     |                             |

Table 8 - Configuration Assignments (CONF<sub>2</sub> - CONF<sub>0</sub>)

## 3.0 Electrical Characteristics

### 3.1 Absolute Maximum Ratings

Stresses greater than those listed under *Absolute Maximum Ratings* can cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods can affect device reliability.

| Storage Temperature                           | -60 °C ≤ T <sub>A</sub> ≤ +125 °C |

|-----------------------------------------------|-----------------------------------|

| Ambient Temperature, under Bias               | -40 °C ≤ T <sub>A</sub> ≤ +85 °C  |

| Ambient relative humidity (non condensing)    | 5 % to 95 %                       |

| PLL_VDD with respect to PLL_VSS or DVSS       | -0.4 V to +4.0 V                  |

| DVDD with respect to PLL_VSS or DVSS          | -0.4 V to +4.0 V                  |

| VDD18 with respect to DVSS or PLL_VSS         | -0.4 V to +1.98 V                 |

| Latch up immunity (any pin)                   | ±100 mA                           |

| Any other pin with respect to DVSS or PLL_VSS | -0.4 V to (DVDD + 0.4 V)          |

| ESD Immunity (Human Body Model)               | JESD22 Class 1C compliant         |

## 3.1.1 Package Assembly

The green package devices are assembled with enhanced, environmental compatible lead-free, halogen-free, and antimony-free materials. The leads possess a matte-tin plating which is compatible with conventional board assembly processes or newer lead-free board assembly processes. Refer to IPC/JEDEC J-Std-020 for recommended peak soldering temperature and solder reflow temperature profile.

## 3.2 Operating Ranges

Microsemi guarantees the performance of this device over commercial (0 °C to 70 °C) and industrial (-40 °C to 85 °C) temperature ranges by conducting electrical characterization over each range and by conducting a production test with single insertion coupled to periodic sampling. These characterization and test procedures comply with the Telcordia GR-357-CORE Generic Requirements for Assuring the Reliability of Components Used in Telecommunications Equipment.

## 3.2.1 Environmental Ranges

| Ambient Temperature       | -40 °C to +85 °C |

|---------------------------|------------------|

| Ambient Relative Humidity | 15 % to 85 %     |

### 3.2.2 Electrical Ranges

| DVDD                              | +3.3 V ± 5% (see note)               |

|-----------------------------------|--------------------------------------|

| PLL_VDD                           | +3.3 V ± 5%, DVDD ± 50 mV (see note) |

| VDD18                             | +1.8 V ± 5% (see note)               |

| DVSS                              | 0 V                                  |

| PLL_VSS                           | DVSS ±10 mV                          |

| Digital pins with respect to DVSS | DVSS to +3.465 V                     |

Note: +3.3 V supply should ramp and reach a steady final value before +1.8 V supply ramps.  $\overline{RST}$  should be held low until both supplies have reached final values. If +3.3 V supply and +1.8 V supply ramps and sequence can not be guaranteed, both  $\overline{RST}$  and  $\overline{TRST}$  should be held low until both supplies have reached final values. In the case where +3.3 V supply and +1.8 V supply ramps and sequence can not be guaranteed,  $\overline{TRST}$  is typically tied low via a 1  $K\Omega$  resistor to ground.

# 3.3 DC Specifications

| No. | Item                             | Condition              | Min.      | Тур.  | Max. | Unit | Note |

|-----|----------------------------------|------------------------|-----------|-------|------|------|------|

| 1   | Input Low Voltage                |                        | - 0.5     | -     | 0.8  | V    | 1    |

| 2   | Input High Voltage               |                        | 2.0       |       | 3.6  | V    | 1    |

| 3   | RST Input Low Voltage            |                        | - 0.5     |       | 0.5  | V    |      |

| 4   | RST Input High Voltage           |                        | 1.1       |       | 3.6  | V    |      |

| 5a  | Innuit Lockogo Current           | 0 to DVDD, outputs in  | -10       | ı     | +10  | μΑ   | 3    |

| 5b  | Input Leakage Current            | high-Z state.          | -100      | _     | +100 | μA   | 4    |

| 6   | Input hysteresis                 |                        | 0.15      | 0.225 | 0.3  | V    | 2    |

| 7   | Output Low Voltage               | lol = 10 mA            | _         | ١     | 0.4  | V    | 5    |

| 8   | Output High Voltage              | Ioh = 400 μA           | DVDD -0.4 | 1     |      |      | 5    |

| 9   | DVDD / PLL_VDD Power Dissipation | DSP in peak operation. | _         |       | 50   | mW   | 6    |

| 10  | VDD18 Power Dissipation          | DSP in peak operation. |           |       | 800  | mW   | 6    |

#### Notes:

- 1. Applies to all digital input pins except  $\overline{RST}$ .

- 2. Applies to all digital input pins.

- 3. Applies to all digital pins with no pull-up, pull-down or keeper.

- 4. Applies to all digital pins with pull-up, pull-down or keeper.

- 5. Applies to all digital output pins.

- 6. No external DC loads present.

## 4.0 Host Bus Interface (HBI) Overview

The Host Bus Interface provides a means for exchanging control, configuration, and status information with an external host processor. The HBI is able to sustain 16-bit transactions up to 10 MHz rate with minimal latency.

This interface is implemented through a combination of hardware and firmware. The design is layered as shown in <u>Figure 4</u>. Hardware provides a generic means for transporting data between the host and internal memory. The interpretation of the data is provided by firmware running on the VCP. This layered architecture allows the definition of the application level interface to change by modifying the firmware.

Figure 4 - Host Bus Interface Layers

## 4.0.0.1 Transport Layer

The transport layer moves 16-bit data words between the physical interface and internal memory or registers on an internal bus. It defines the structure of a transport frame, which consists of a 16-bit command word followed by 0 or more 16-bit payload data words. It also defines the interface address model, and provides mapping between interface and internal addresses.

## 4.0.0.2 Application Layer

The application layer defines the programmer's interface, and is almost entirely implemented in firmware. The exception is a handful of configuration registers implemented in hardware. This layer defines the meaning of the payload data delivered by the transport layer. Because it is implemented in firmware, the definition of the programmer's interface can change by providing new software.

#### 4.0.0.3 Physical Layer

The physical layer provides the functionality needed to electrically interface with a host processor. It defines the pins, signal timing and electrical characteristics of the interface. Two physical interfaces are provided. The General Purpose Parallel Interface (GPI) implements an 8-bit or 16-bit wide parallel interface. Options are selected via the configuration pins, refer to <u>Table 8</u>. The Serial Peripheral Interface (SPI) implements a 4-wire synchronous serial slave interface.

The NG chipset (Le79271 SLIC, Le79238 SLAC, and Le79124 VCP) supports use of the GPI 16-bit interface.

Refer to the Next Generation Carrier Chipset Hardware Design Guide for connection diagrams.

# 5.0 Transport Layer

The primary responsibility of the transport layer is to move 16-bit data words between the physical interface and the device's internal memory. Data is organized into transport frames, which consist of a 16-bit command word followed by 0 or more data words. The command word provides address and length information to the transport hardware. In a sense, this hardware provides an internal DMA-like function, moving data over the internal bus under host control. Both the GPI and SPI physical layers share a common transport layer.

## 5.1 Interface Addressing

The transport command word provides address information to the interface hardware.

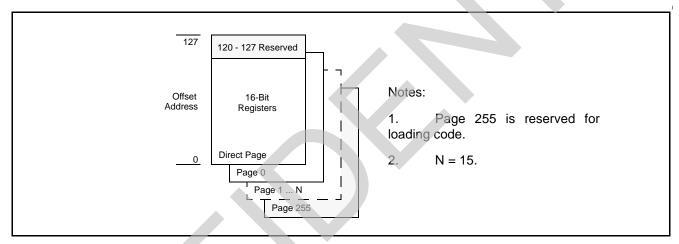

The host interface address model is based on a paged memory scheme as shown in <u>Figure 5</u>. The command design permits up to 257 pages, with up to 128 offset-addressable 16-bit wide register locations. Therefore, an interface address is composed of an 8-bit page number and a 7-bit register offset. Pages are selected by using a command to write the page register. All data access commands operate on the selected page. One exception is the direct page, which can be accessed at any time without changing the page register.

Figure 5 - Host Bus Interface Address Mode

#### 5.2 Command Structure

All transport frames start with a 16-bit command word followed by 0 or more 16-bit data words. The same command format is used for both the GPI and the SPI. <u>Table 9</u> provides a list of transport commands followed by a short description of each command.

|                        |                       |    | Con | nmand    | Bit Posi              | ition     |   |                  | Number of   |

|------------------------|-----------------------|----|-----|----------|-----------------------|-----------|---|------------------|-------------|

| Transport Command      | 15                    | 14 | 13  | 12       | 11                    | 10        | 9 | 8                | 16-bit      |

|                        | 7                     | 6  | 5   | 4        | 3                     | 2         | 1 | 0                | Data Words  |

| D 10" 14               | 0                     |    |     | Offset A | ddress                | (0 - 127) | ) |                  |             |

| Paged Offset Access    | r/w <sup>a</sup>      |    |     | Len      | gth (0 -              | 127)      |   |                  | Length + 1  |

| Dissal Office A Access | 1                     |    | (   | Offset A | ddress <sup>b</sup>   | (0 - 119  | ) |                  |             |

| Direct Offset Access   | rw <sup>a</sup>       |    |     | Lenç     | gth <sup>b</sup> (0 - | 119)      |   |                  | Length + 1  |

| 0, 15                  | 1                     | 1  | 1   | 1        | 1                     | 0         | 0 | r/w <sup>a</sup> |             |

| Start Paged Access     | Length (0 - 255)      |    |     |          |                       |           |   | Length + 1       |             |

| Ocations Described     | 1                     | 1  | 1   | 1        | 1                     | 0         | 1 | r/w <sup>a</sup> | Transfer of |

| Continue Paged Access  | Length (0 - 255)      |    |     |          |                       |           |   | Length + 1       |             |

| Configura Interfere    | 1                     | 1  | 1   | 1        | 1                     | 1         | 0 | 1                |             |

| Configure Interface    | Interface Option Bits |    |     |          |                       |           |   | 0                |             |

| Calast Bara            | 1                     | 1  | 1   | 1        | 1                     | 1         | 1 | 0                |             |

| Select Page            | Page Number (0 - 255) |    |     |          |                       |           |   | 0                |             |

| NOD                    | 1                     | 1  | 1   | 1        | 1                     | 1         | 1 | 1                |             |

| NOP                    | 1                     | 1  | 1   | 1        | 1                     | 1         | 1 | 1                | 0           |

**Table 9 - Host Bus Interface Transport Commands**

#### 5.2.1 Paged Offset Access

This command accesses one or more contiguous 16-bit registers on the currently selected page. The 7-bit offset specifies the starting address on the page. The command is followed by (Length + 1) 16-bit data words. The 7-bit Length field allows accessing between 1 and 128 locations with a single transport frame. For nonzero Lengths, the address automatically increments, and consecutive locations are accessed.

#### 5.2.2 Direct Offset Access

Direct Offset Access is the same as Paged Offset Access, except that the direct page is the target. By using this command, the direct page can be accessed at any time without modifying the page register.

## 5.2.3 Start Paged Access

This command accesses a contiguous stream of 16-bit data words starting from offset 0 on the currently selected page. The command is followed by (Length + 1) 16-bit data words. The 8-bit Length field allows accessing between 1 and 256 locations (i.e., up to 512 bytes) with a single transport frame. Access always begins from offset 0, and the address automatically increments.

a. Read/Write select bit. 0 = Read. 1 = Write.

b. Addresses 120 - 127 on the Direct Page are reserved.

### 5.2.4 Continue Paged Access

Continue Paged Access is the same as the Start Paged Access, except that access starts from where the last paged access left off. By using this command, packets of arbitrary length can be supported. This gives the host the flexibility to split packets transfer into smaller sizes if desired.

### 5.2.5 Select Page

This command selects the active interface page. It is a write only command and is followed by 0 data words. The 8-bit page field allows up to 256 selectable pages to be defined.

#### **HBI Page Selection (PGSEL)**

Command 0xFE (W)

| D7 | D6 | D5 | D4    | D3       | D2 | D1 | D0 |

|----|----|----|-------|----------|----|----|----|

|    |    |    | PG_SE | EL [7:0] |    |    |    |

PG\_SEL:

Page addressed by any non-direct HBI access.

### 5.2.6 Configure Interface

This command is used to configure various physical interface options. It is a write-only command and is followed by 0 data words. The Interface Option Bits field allows the following features to be programmed by the host: Wait Pin Polarity (active High or active Low), Wait Pin Enable (default is tri-state), Wait Pin Drive Mode (open-source/opendrain or TTL), Interrupt Pin Drive Mode (open-drain or TTL), and Endian Control (Big or Little). If this register is not programmed correctly, it is possible that the host may not be able to communicate with the VCP device properly. This should be part of the HAL (Hardware Abstraction Layer) function used to initialize the device.

#### HBI User Interface Pin Configuration (PINCONFIG)

Command 0xFD (W)

| D7   | D6   | D5   | D4      | D3        | D2       | D1        | D0      |

|------|------|------|---------|-----------|----------|-----------|---------|

| RSVD | RSVD | RSVD | INT_DRV | PWAIT_DRV | PWAIT_EN | PWAIT_POL | END_SEL |

RSVD:

Should be written as 0.

INT\_DRV:

INT pin drive mode.

0: Open drain (default).

1: TTL.

PWAIT DRV:

PWAIT pin drive mode.

<u>O: CMOS-drive</u> (default). Pin is actively driven to both polarities. When PCS is deasserted (High), the PWAIT pin is driven inactive.

PCS is deasserted (High), the PWAIT pin is driven inactive.

1: Open source or drain depending on polarity. Pin is actively <u>driven</u> to its active polarity as specified by the PWAIT\_POL setting. When PCS is

deasserted (High), the PWAIT pin is tri-stated.

PWAIT EN:

PWAIT pin enable.

0: Disabled (default).

1: Enabled.

PWAIT POL:

PWAIT pin polarity.

0: Active Low (default).

1: Active High.

END\_SEL: Endian select.

0: Big endian (default).

1: Little endian.

#### Note:

The commands are not affected by endianness; their order must be maintained per documentation. Hence, little-endian systems will need to reverse the command structure.

#### 5.2.7 NOP

A command is reserved to serve as a NOP. Note that all commands except for the Offset Access commands are implemented by reserving an address from the direct page.

# 5.3 VCP Direct Page Hardware Register Summary

<u>Table 10</u> provides an overview listing of the hardware derived registers. These registers reside on the Direct Page.

| Register Name                   | Mnemonic   | Register Description                                             | Offset | Notes |

|---------------------------------|------------|------------------------------------------------------------------|--------|-------|

| Interrupt Indication            | INTIND     | Used by VpGetEvent() to get the next event from the queue.       | 0x00   |       |

| Interrupt Parameter             | INTPARAM   | Used by VpGetEvent() to get the next event's parameter.          | 0x01   |       |

| Page Offset                     | PGOFFSET   | Allows for interleaved page accesses. Not used by the VP-API.    | 0x02   |       |

| Mailbox Flag                    | MBFLAG     | Used by the VCP firmware and VP-API to provide page handshaking. | 0x03   |       |

| Page 255 Checksum (High)        | CHKSUM     | Charles and Dark Lond date                                       | 0x04   |       |

| Page 255 Checksum (Low)         | CHKSUM     | Checksum of Boot Load data.                                      | 0x05   |       |

| Page 255 Base Address<br>(High) | DAGE ADDD  | Hard Barthard                                                    | 0x06   |       |

| Page 255 Base Address<br>(Low)  | BASE_ADDR  | Used for Boot Load.                                              | 0x07   |       |

| PCLKB Select                    | PCLKB_SEL  | PCLK A and B Select Register: VCP defaults                       | 0x08   |       |

| PCLKA Select                    | PCLKA_SEL  | to autodetect the PCLK rate.                                     | 0x09   |       |

| Clock Status                    | CLKSTAT    | System Clock status                                              | 0x0A   |       |

| MCLK Configuration              | MCLKCONFIG | Reference Clock configuration                                    | 0x0B   |       |

| System Real Time Status         | SYSSTAT    | System Interrupt (fault) status.                                 | 0x0C   |       |

| System Interrupt Mask           | SYSMASK    | System Interrupt (fault) mask.                                   | 0x0D   |       |

Table 10 - VoiceEdge VCP Hardware Derived Register Space

| Register Name        | Mnemonic                                                                                                                                                  | Register Description                                                      | Offset | Notes                          |