## Dual Ringing Subscriber Line Interface Circuit VE950 Series

**Data Sheet**

#### **Features**

- · Dual Architecture

- Two fully independent integrated SLIC channels

- No impulse noise crosstalk in any operation states to the listening channel in forward or reverse active states

- Two Power Supplies

- · Single user adjusted battery input per channel

- 3.3 V for Vcc

- · High Voltage Design

- Meets Comcast Ringing requirements without clipping distortion

- Robust solution with no damage during extended ringing cycles or switching the ringer on and off

- Allows use of 50 Ω protection resistors and lower cost lower current rated protectors

- Two Grades

- Up to -145 V ringing battery Le9530D

- Up to -100 V ringing battery Le9530C

- · Channel Independent Eight Operating States

- Scan state for minimal power dissipation

- Active Forward 25 mA DC Current Limit (Default Power Up Mode)

- Active Reverse 25 mA DC Current Limit

- Active Forward 40 mA DC Current Limit

- Active Reverse 40 mA DC Current Limit

- Tip Open Ground Start

- Ringing

- Disconnect

- Per Channel Ringing Inputs for Optimized Interface to BCM SoC Devices

- Allows to accept driving signals from per channel voice outputs as well as from PWM outputs

- Ultra-Low On-Hook Power

Document ID#: 081571 Version 11 August 2013

| Ordering | Information | ١ |

|----------|-------------|---|

|          |             |   |

| Le9530CETC 48-pin eTQFP Tr  | ay         |

|-----------------------------|------------|

| Le9530DETC 48 pin eTQFP Tr  | ay         |

|                             | ay         |

| Le9530DPQC 48-pin QFN Tr    | ay         |

|                             |            |

| Le9530CETCT 48-pin eTQFP Ta | ape and Re |

| Le9530CETCT | 48-pin eTQFP | Tape and Reel |

|-------------|--------------|---------------|

| Le9530DETCT | 48 pin eTQFP | Tape and Reel |

| Le9530CPQCT | 48-pin QFN   | Tape and Reel |

| Le9530DPQCT | 48-pin QFN   | Tape and Reel |

|             |              |               |

- All devices are in green packages. The green package meets RoHS Directive 2002/95/EC of the European Council to minimize the environmental impact of electrical equipment.

- Loop Start, Ring Trip, and Ground Start Detections

- Loop closure detection with hysteresis to minimize dial pulse distortion

- Thermal Shutdown Protection with Hysteresis

- Test Load Switch

- Supports integrated test algorithms

### **Applications**

- Optimized design to work with BCM3378/80/82 and BCM6816 Broadcom SoCs

- · Other short loop residential gateway

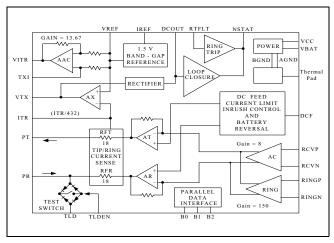

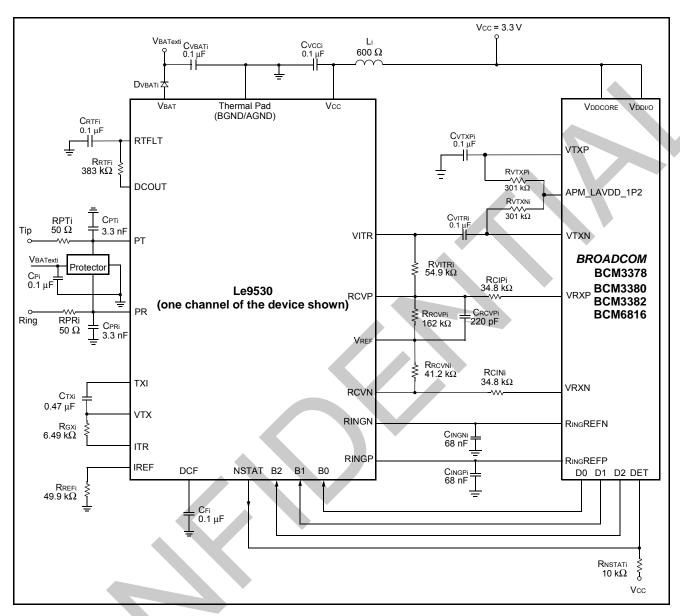

Figure 1 - Block Diagram (Le9530 - one channel shown)

## **Description**

The Le9530 Dual Ringing SLIC device is a dual-channel device optimized to provide battery feed, ringing, and supervision on voice loops found in short-loop VoIP applications. This device is optimized to interface to the Broadcom BCM3378/3380/3382 and BCM6816 devices, or a similar codec. The Le9530 device operates independently from a single, user-adjusted battery and a +3.3 V Vcc per channel. Each channel provides forward and reverse battery feed, voice transmission, power ringing, an ultra low-power scan state, ground start (Tip open), and a disconnect state. A test load switch is also included to support integrated test algorithms.

# **Table of Contents**

| Features                                     |      |

|----------------------------------------------|------|

| Applications                                 | 1    |

| Description                                  |      |

| Product Description                          | 5    |

| Connection Diagrams                          |      |

| Pin Descriptions                             |      |

| Absolute Maximum Ratings                     |      |

| Thermal Resistance                           |      |

| Package Assembly                             |      |

| Operating Ranges                             |      |

| Environmental Ranges                         |      |

| Electrical Ranges                            |      |

| Electrical Characteristics                   |      |

| Supply Currents                              |      |

| Power Dissipation                            |      |

| Line Characteristics                         |      |

| Test Switch Specifications                   |      |

| Operating States                             |      |

| Operating State Definitions                  |      |

| Scan                                         | 21   |

| Active—Forward Battery—Low DC Current Limit  |      |

| Active—Forward Battery—High DC Current Limit |      |

| Active—Reverse Battery—Low DC Current Limit  |      |

| Active—Reverse Battery—High DC Current Limit |      |

| Disconnect                                   |      |

| Ringing                                      |      |

| Ground Start                                 |      |

| Thermal Shutdown                             |      |

| Test Circuit                                 | . 23 |

| Applications                                 | . 26 |

| DC Loop Current Limit                        |      |

| Overhead Voltage                             |      |

| Supervision                                  | . 27 |

| Power Ring                                   | . 27 |

| Design Examples                              |      |

| Application Circuit Parts List               | . 31 |

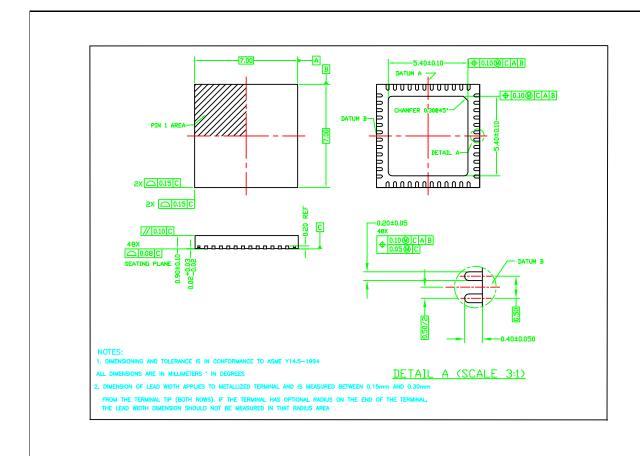

| Physical Dimensions                          | . 32 |

| 48-Pin eTQFP                                 | . 32 |

| 48-pin QFN                                   |      |

| Revision history                             | . 34 |

| A1 to B1                                     |      |

| B1 to C1                                     |      |

| C1 (Version 3) to Version 4                  |      |

| Version 4 to Version 5                       |      |

| Version 5 to Version 6                       |      |

| Version 6 to Version 7                       |      |

| Version 7 to Version 8                       |      |

| Version 8 to Version 9                       |      |

| Version 9 to Version 10                      |      |

| Version 10 to Version 11                     | . 35 |

# Le9530

# **List of Figures**

| Figure 1 - Block Diagram (Le9530 - one channel shown)                                       |   | . ' |

|---------------------------------------------------------------------------------------------|---|-----|

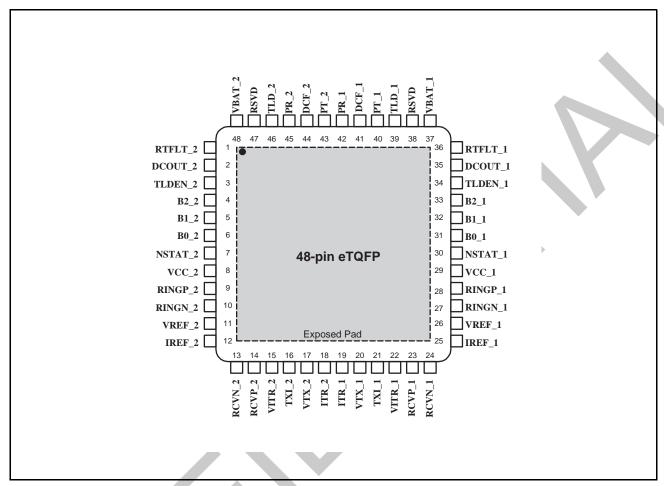

| Figure 2 - 48 Pin eTQFP                                                                     |   | . 7 |

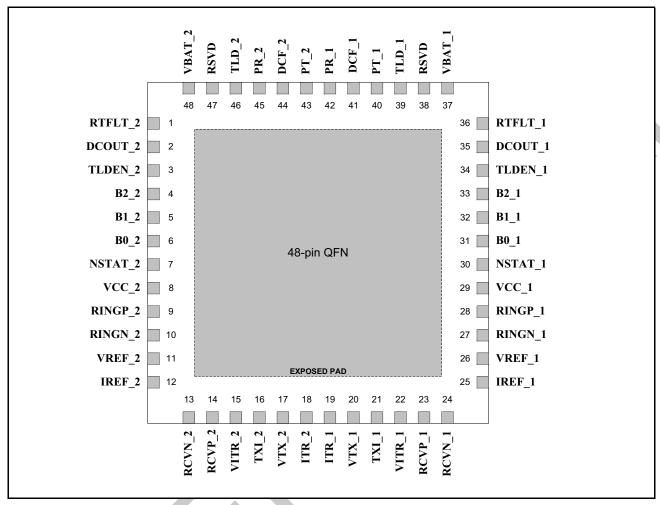

| Figure 3 - 48 Pin QFN                                                                       |   | . 8 |

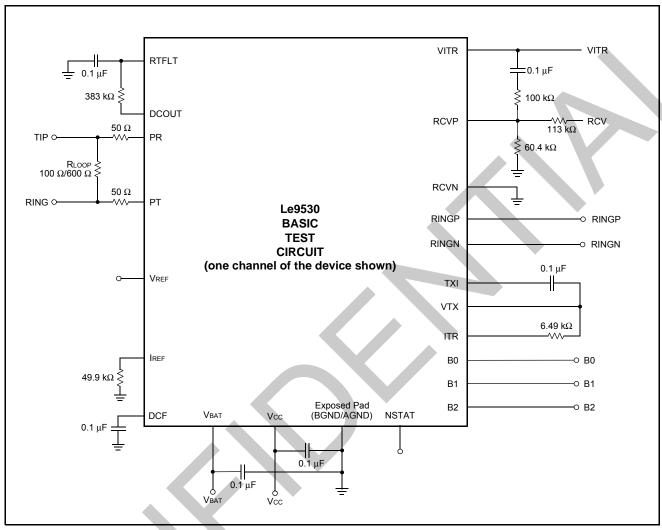

| Figure 4 - Le9530 Basic Test Circuit (one channel of the device shown)                      |   | 23  |

| Figure 5 - Metallic PSRR                                                                    |   | 24  |

| Figure 6 - Longitudinal PSRR                                                                |   | 24  |

| Figure 7 - Longitudinal Balance                                                             |   | 2!  |

| Figure 8 - AC Gains                                                                         | , | 2!  |

| Figure 9 - Le9530 Reference Schematic Interfacing Broadcom Codec                            |   | 29  |

| Figure 10 - Le9530 Reference Schematic Interfacing Broadcom Codec with Shared Driving Paths |   | 30  |

## **Product Description**

The Le9530 device is a dual-channel device optimized to provide battery feed, ringing, and supervision on short plain old telephone service (POTS) loops. This device is optimized to interface to Broadcom Cable Modem and GPON devices. Each channel of this device provides power ringing to the subscriber loop through amplification of a low-voltage input. It also provides forward and reverse battery feed states with a clamped T/R voltage during high battery application, a low-power scan state also with a clamped T/R voltage during high battery application, ground start (tip open), and a disconnect state. The active forward low dc current limit state is the default power up state.

The Le9530 device requires a Vcc and battery to operate per channel. The ringing signal is derived from the high-voltage battery. High voltage battery for ringing is graded for –100 V or –145 V. This device assumes use of a switching power supply which will put out different voltages in different SLIC operation states; therefore, no battery switch is included.

Loop closure, ring trip, and ground start detection are available. The loop closure detector has a fixed threshold with hysteresis. The ring trip detector requires a single-pole filter, thus minimizing external components required.

The active forward/reverse low DC current limit SLIC operation states set the DC current limit to be 25 mA. The active forward/reverse high DC current limit SLIC operation states set the DC current limit to be 40 mA. The DC current limit is fixed in scan state.

The device is offered with differential ringing and receive inputs, but may be operated in single ended mode by simply connecting the unused input to VREF.

This device is designed for ultra-low power in all operating states.

Each channel of the Le9530 device offers eight operating states and assumes use of a single user adjusted battery for talk, ringing and scanning. The battery amplitude to the SLIC device is expected to vary according to the operation state. A user should carefully choose and provide the proper battery externally to the SLIC. The battery voltage is graded, up to -100 V for scan and ring for the Le9530C device, and -100 V for scan and up to -145 V for ring for the Le9530D device. For the Le9530D device, during ringing only the battery supply voltage may be extended to -145 V. The supply has to be externally adjusted back to no more than -100 V for other operations. Also, when -145 V is used for ringing special care should be taken to prevent certain faults from happening, such as tip to ring, tip or ring to ground, or similar alike.

To minimize on-hook power, a low-power scan state is available. In this state, all functions except off-hook supervision are turned off to conserve power. On-hook transmission is not allowed in the scan state. In the scan state, with a primary battery whose magnitude is greater than a nominal 51 V, the magnitude of the tip-to-ground and ring-to-ground voltage is clamped at less than 56.5 V.

Forward and Reverse Battery Active Transmission mode serve as both an off-hook talk mode and on-hook transmission mode, as may be required during the quiet interval of ringing. The device depends on the switching power supply to reduce the battery during off-hook conditions, to avoid potential thermal issues, and by doing so may save overall operating power consumption.

Because on-hook transmission is not allowed in the scan state, during the on-hook transmission in the active state the magnitude of the tip-to-ground and ring-to-ground voltage is clamped at less than 56.5 V, with a primary battery whose magnitude is greater than a nominal 56.5 V. The magnitude of the overhead voltage for batteries whose magnitude is less than 56.5 V has a typical default value of 6 to 8 V, allowing for an on-hook transmission of an undistorted signal of 3.14 dBm into 900  $\Omega$ . Additionally, this allows sufficient overhead for 500 mV of meter pulse if desired. This overhead is fixed. The ring trip detector is turned off during Active states to conserve power.

A disconnect state is provided where all circuits are turned off and power is denied to the loop.

In the Ringing state a power ring signal is provided to the tip/ring pair. During the Ringing state, a user-supplied, low-voltage ring signal is differentially input to the device's RINGP and RINGN inputs. These signals are amplified to produce the power ring signal at Tip-Ring. This signal may be a sine wave or filtered square wave to produce a sine wave or trapezoidal output. A DC offset may also be applied. The Ring Trip detector is active during the Ringing state.

Both the ring trip and loop closure supervision functions are included. The loop closure has a fixed on-hook to off-hook threshold in the active and scan states. In either case, there is a hysteresis. The ring trip detector requires only a single-pole filter at the input, minimizing external components. The ring trip threshold at a given battery voltage is fixed.

In the ground start state, the tip drive amplifier is turned off. The device presents a high impedance (>100 k $\Omega$ ) to PT and a current-limited battery (VBAT) to PR. VBAT is clamped to less than 56.5 V in this state at PR. The NSTAT loop current detector is used for ring ground detection. In the ground start state, since the loop current is common mode, the loop closure threshold is reduced in half, thus maintaining loop supervision at specified levels.

Upon reaching the thermal shutdown temperature, the device will enter an all off state. Upon cooling, the device will re-enter the state it was in prior to thermal shutdown. Hysteresis is built in to prevent oscillation.

Each channel's state is controlled via a parallel unlatched control scheme.

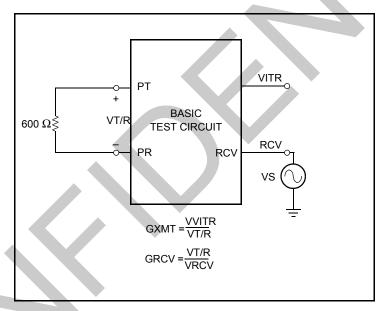

The Le9530 device uses a voltage feed and current sense architecture; thus, the transmit gain is a transimpedance. The trans-impedance is set via a single external resistor, and is designed for optimal performance with a trans-impedance at 205 V/A. This interface is single-ended. The interface at the receive can be differential, with a gain of 8.

There is a 1.5-V internal reference voltage each channel. This reference voltage is output at the VREF. The VITR output is also referenced to VREF. The RCVP/RCVN pins are floating inputs.

A test load switch and an integrated diode bridge is included to support integrated test algorithms.

The Exposed Pad is to be connected to a ground plane on the printed circuit board for thermal conduction. Also, the internal analog grounds and battery grounds are connected to the exposed pad. The ground plane to which the exposed pad connects has to be good for both analog signal ground and battery ground.

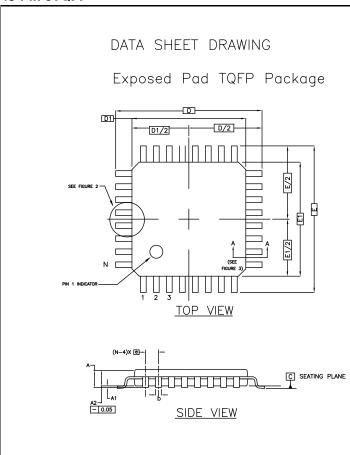

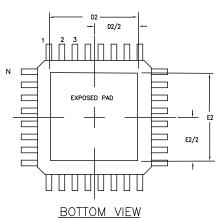

The device is available in a 48-pin eTQFP (7mm x 7mm) package or a 48-pin QFN (7mm x 7mm) package.

## **Connection Diagrams**

Figure 2 - 48 Pin eTQFP

Note: Internally two analog grounds and two battery grounds are connected to the Exposed Pad.

Figure 3 - 48 Pin QFN

Note: Internally two analog grounds and two battery grounds are connected to the Exposed Pad.

## **Pin Descriptions**

NAME\_1 for channel 1 and NAME\_2 for channel 2.

| Pin<br>Name        | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NSTAT_1<br>NSTAT_2 | Output           | <b>Loop Closure Detector Output and Ring Trip Detector Output.</b> When Low, this logic output indicates that an off-hook condition exists or ringing is tripped or a ring ground has occurred or thermal shutdown happened. Internally, it is an output from a NPN transistor with 60 k $\Omega$ pull up. See Table 3 for more information regarding output characteristics. |

| VITR_1<br>VITR_2   | Output           | <b>Transmit AC Output Voltage.</b> Output of internal AAC amplifier. This output is a voltage that is directly proportional to the differential AC tip/ring current.                                                                                                                                                                                                          |

| RCVP_1<br>RCVP_2   | Input            | Receive AC Signal Input (Non inverting). This high-impedance input controls to AC differential voltage on tip and ring, for voice in Active states. This node is a floating input.                                                                                                                                                                                            |

| RCVN_1<br>RCVN_2   | Input            | Receive AC Signal Input (Inverting). This high-impedance input controls to AC differential voltage on tip and ring, for voice in Active states. This node is a floating input.                                                                                                                                                                                                |

| RINGP_1<br>RINGP_2 | Input            | <b>Power Ring Signal Input (Non inverting).</b> Couple to a sine wave or lower crest factor low-voltage ring signal. The input here is amplified to provide the full power ring signal at tip and ring. This signal may be applied continuously, even during non-ringing states.                                                                                              |

| RINGN_1<br>RINGN_2 | Input            | <b>Power Ring Signal Input (Inverting).</b> Couple to a sine wave or lower crest factor low-voltage ring signal. The input here is amplified to provide the full power ring signal at tip and ring. This signal may be applied continuously, even during non-ringing states.                                                                                                  |

| DCOUT_1<br>DCOUT_2 | Output           | <b>DC Output Voltage.</b> This output is a voltage that is directly proportional to the absolute value of the differential tip/ring current. This is used to set ring trip threshold.                                                                                                                                                                                         |

| DCF_1<br>DCF_2     | Input            | Filter Capacitor. Connect a capacitor from this node to ground.                                                                                                                                                                                                                                                                                                               |

| RTFLT_1<br>RTFLT_2 | Input            | <b>Ring Trip Filter.</b> Connect this lead to DCOUT via a resistor and to GND with a capacitor to filter the ring trip circuit to prevent spurious responses. A single-pole filter is needed.                                                                                                                                                                                 |

| VREF_1<br>VREF_2   | Output           | SLIC Device Internal Reference Voltage. Output of internal 1.5 V reference voltage.                                                                                                                                                                                                                                                                                           |

| IREF_1<br>IREF_2   | Input            | SLIC Device Internal Reference Current. Connect a 49.9 k $\Omega$ resistor to low noise analog ground.                                                                                                                                                                                                                                                                        |

| VCC_1<br>VCC_2     | Power            | Analog Power Supply. 3.3 V typical.                                                                                                                                                                                                                                                                                                                                           |

| VBAT_1<br>VBAT_2   | Power            | Battery Supply. User adjusted supply per SLIC operation state and device grade.                                                                                                                                                                                                                                                                                               |

| PT_1<br>PT_2       | Input/<br>Output | <b>Protected Tip.</b> The output drive of the tip amplifier and input to the loop-sensing circuit. Connect to loop through over-voltage and over-current protection.                                                                                                                                                                                                          |

| Pin<br>Name        | Туре             | Description                                                                                                                                                            |

|--------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PR_1<br>PR_2       | Input/<br>Output | <b>Protected Ring.</b> The output drive of the ring amplifier and input to the loop sensing circuit. Connect to loop through over-voltage and over-current protection. |

| B2_1<br>B2_2       | Input            | State Control Input. These pins have an internal 150 k $\Omega$ typical pull-down.                                                                                     |

| B1_1<br>B1_2       | Input            | State Control Input. These pins have an internal 150 kΩ typical pull-down.                                                                                             |

| B0_1<br>B0_2       | Input            | State Control Input. These pins have an internal 150 kΩ typical pull-down.                                                                                             |

| ITR_1<br>ITR_2     | Input            | <b>Transmit Gain.</b> Input to AX amplifier. Connect a 6.49 $k\Omega$ resistor from this node to VTX to set transmit gain of 205V/A.                                   |

| VTX_1<br>VTX_2     | Output           | AC Output Voltage. Output of internal AX amplifier. The voltage at this pin is directly proportional to the differential tip/ring current.                             |

| TXI_1<br>TXI_2     | Input            | <b>AC/DC Separation.</b> Input to internal AAC amplifier. Connect a capacitor from this pin to VTX.                                                                    |

| TLD_1<br>TLD_2     | Input            | Test Load. A test load may be connected to this pin.                                                                                                                   |

| TLDEN_1<br>TLDEN_2 | Input            | <b>Test Load</b> Enable. Active HIGH to turn on test switch. Drive it LOW or leave it floating if not in use. It has an internal 100 $k\Omega$ typical pull-down.      |

| RSVD               |                  | Reserved. Leave it floating on PCB layout.                                                                                                                             |

| Exposed Pad        |                  | <b>Thermal and Circuit Ground</b> . Connect to a ground plane on the printed circuit board for thermal conduction and for analog signal ground and battery ground.     |

## **Absolute Maximum Ratings**

Stresses above those listed under *Absolute Maximum Ratings* can cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.  $T_A = 25$  °C

| Parameter                                                            | Symbol           | Min.                 | Max.                      | Unit |

|----------------------------------------------------------------------|------------------|----------------------|---------------------------|------|

| DC Supply (Vcc)                                                      | Vcc              | -0.4                 | 4.0                       | V    |

| Battery Supply (V <sub>BAT</sub> )<br>(Le9530C, Le9530D Non-Ringing) | Vват             | GND                  | -110                      | V    |

| Battery Supply (V <sub>BAT</sub> ) (Le9530D Ringing)                 | V <sub>BAT</sub> | GND                  | -155 + Vcc                | V    |

| Logic Input Voltage                                                  |                  | -0.4                 | Vcc + 0.5                 | V    |

| Logic Output Voltage                                                 |                  | -0.4                 | Vcc + 0.5                 | V    |

| Operating Temperature Range                                          |                  | -40                  | 125                       | °C   |

| Storage Temperature Range                                            |                  | -40                  | 150                       | °C   |

| Relative Humidity Range                                              |                  | 5                    | 95                        | %    |

| PT or PR Fault Voltage (DC)                                          | VPT, VPR         | V <sub>BAT</sub> – 5 | 3                         | V    |

| PT or PR Fault Voltage (10 x 1000 µs)                                | VPT, VPR         | VBAT - 15            | 15                        | V    |

| ESD Immunity (Human Body Model)                                      |                  |                      | JESD22 Class 1C compliant |      |

#### **Thermal Resistance**

The thermal performance of a thermally enhanced package is assured through optimized printed circuit board layout. Specified performance requires that the exposed thermal pad be soldered to an equally sized exposed copper surface, which, in turn, conducts heat through multiple vias to a large internal copper plane. Thermal performance depends on number of PCB layers and the size of copper area. Continuous operation above 145°C junction temperature may degrade device reliability.

The typical thermal protection shutdown (TjC) temperature is 190°C, with minimum at 175°C.

#### **Package Assembly**

Green package devices are assembled with enhanced environmental compatible lead-free, halogen-free, and antimony-free materials. The leads possess a matte-tin plating which is compatible with conventional board assembly processes or newer lead-free board assembly processes. The peak soldering temperature should not exceed 245°C during printed circuit board assembly.

Refer to IPC/JEDEC J-Std-020B Table 5-2 for the recommended solder reflow temperature profile.

## **Operating Ranges**

### **Environmental Ranges**

Microsemi guarantees the performance of this device over commercial (0 to 70° C) and industrial (-40 to 85°C) temperature ranges by conducting electrical characterization over each range and by conducting a production test with single insertion coupled to periodic sampling. These characterization and test procedures comply with section 4.6.2 of Bellcore GR-357-CORE Component Reliability Assurance Requirements for Telecommunications Equipment.

| Ambient Temperature       | -40° C < T <sub>A</sub> < +85° C |  |

|---------------------------|----------------------------------|--|

| Ambient Relative Humidity | 5 to 95%                         |  |

### **Electrical Ranges**

| Parameter                                                    | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------------|------|------|------|------|

| 3.3 V DC Supplies (Vcc)                                      | 3.13 | 3.3  | 3.47 | V    |

| Office Battery Supply (VBAT) (Le9530C)                       | -12  |      | -100 | V    |

| Office Battery Supply (VBAT) (Le9530D)                       | -12  |      | -100 | V    |

| Office Battery Supply (VBAT) (Le9530D) (during ringing only) | -12  |      | -145 | V    |

Note that ringing with battery supply |VBAT| < |-60| V constant is not recommended.

## **Electrical Characteristics**

## **Supply Currents**

Values are per channel. On-hook with no loop current. Vcc = 3.3 V. Test switch is off.

| Parameter                                   | Min. | Тур. | Max. | Unit |

|---------------------------------------------|------|------|------|------|

| Scan state, VBAT= -60 V:                    |      |      |      |      |

| l <sub>vcc</sub>                            | _    | 3.20 | 4.30 | mA   |

| I <sub>VBAT</sub>                           | _    | 0.22 | 0.27 | mA   |

| Active state, VBAT= -60 V:                  |      |      |      |      |

| lvcc                                        | _    | 4.10 | 5.10 | mA   |

| I <sub>VBAT</sub>                           | _    | 1.28 | 1.45 | mA   |

| Active state, VBAT= –21 V:                  |      |      |      |      |

| lvcc                                        | _    | 4.00 | 5.00 | mA   |

| I <sub>VBAT</sub>                           | _    | 1.22 | 1.36 | mA   |

| Disconnect state, VBAT= -60 V               |      |      |      |      |

| lvcc                                        | _    | 2.45 | 3.50 | mA   |

| IVBAT                                       | _    | 0.03 | 0.07 | mA   |

| Ground start state, VBAT= –60 V             |      |      |      |      |

| lvcc                                        |      | 2.90 | 4.00 | mA   |

| I <sub>VBAT</sub>                           | - 1  | 0.19 | 0.24 | mA   |

| Ring state, no load, VBAT= -100 V (Le9530C) |      |      |      |      |

| lvcc                                        | -    | 4.33 | 5.35 | mA   |

| IVBAT                                       | _    | 1.94 | 2.23 | mA   |

| Ring state, no load, VBAT= -145 V (Le9530D) |      |      |      |      |

| lvcc                                        | _    | 4.38 | 5.47 | mA   |

| I <sub>VBAT</sub>                           | _    | 2.13 | 2.50 | mA   |

## **Power Dissipation**

Values are per channel. On-hook with no loop current. Vcc = 3.3 V. Test switch is off.

| Parameter                                                | Min. | Тур. | Max. | Unit |

|----------------------------------------------------------|------|------|------|------|

| Scan state, V <sub>BAT</sub> = -60 V                     | _    | 25   | 35   | mW   |

| Active state, Forward/Reverse, V <sub>BAT</sub> = -60 V  | _    | 90   | 105  | mW   |

| Active state, Forward/Reverse, V <sub>BAT</sub> = –21 V  | _    | 42   | 46   | mW   |

| Disconnect state, V <sub>BAT</sub> = -60 V               | _    | 10   | 15   | mW   |

| Ground start state, V <sub>BAT</sub> = –60 V             | _    | 29   | _    | mW   |

| Ring state, no load, V <sub>BAT</sub> = -100 V (Le9530C) | _    | 207  | 242  | mW   |

| Ring state, no load, V <sub>BAT</sub> = -145 V (Le9530D) |      | 324  | 435  | mW   |

#### **Line Characteristics**

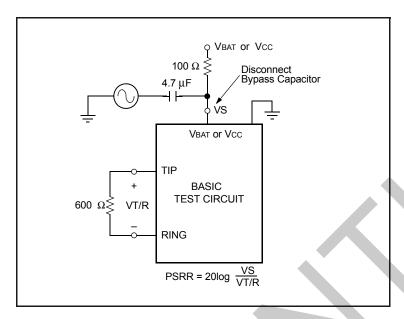

Unless specified the test condition is specified in Figure 4 - Le9530 Basic Test Circuit.

Typical values are characteristic of the device and are the result of engineering evaluations. Typical values are for information purposes only and are not a part of the testing requirements. Minimum and maximum values apply across the operating temperature range and the entire battery range unless otherwise specified. Typical is defined as Ta=25° C, Vcc = 3.3V, VBAT= -60V for scan and disconnect state, -30V for active states, -100V/-145V for ringing state (for Le9530C/D). Test Switch is OFF.

| Parameter                                                                                                       | Min. | Тур. | Max. | Unit  |

|-----------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Tip or Ring Drive Current = DC + Longitudinal + Signal Currents, Active states <sup>1</sup>                     | 105  |      | -    | mApk  |

| Tip or Ring Drive Current = Ringing + Longitudinal, Ring state <sup>1</sup>                                     | 65   | _    | -    |       |

| Signal Current, Active state <sup>1</sup>                                                                       | 10   | _    | 7    | mArms |

| Longitudinal Current Capability per Wire (Longitudinal current is independent of DC loop current.) <sup>1</sup> | 8.5  | 15   | _    |       |

| Ringing Current (RLOAD = 1386 $\Omega$ + 40 $\mu$ F) <sup>1</sup>                                               | 29   | _    | _    |       |

| DC Loop Current Limit, ILIM, (RLOOP = 100 Ω):                                                                   |      |      |      |       |

| Active Low DC Current Limit States                                                                              | _    | 25   | _    | mA    |

| Active High DC Current Limit States                                                                             | _    | 40   | _    | mA    |

| DC Loop Current Limit Variation                                                                                 |      | _    | ±8   | %     |

| DC Loop Current Limit, Scan Mode (RLOOP = 100 Ω)                                                                | _    | 45   | _    | mA    |

| DC Feed Resistance (at PT-PR, Active states, non-current limit)                                                 | _    | 40   | _    | Ω     |

| Open Loop Voltages:                                                                                             |      |      |      | V     |

| Scan state:                                                                                                     |      |      |      |       |

| VBAT  > 51 V,  VTIP – VRING                                                                                     | 44   | 49   | _    |       |

| VTIP ,  VRING  to Battery Ground                                                                                | _    | _    | 56.5 |       |

| Active state:                                                                                                   |      |      |      | V     |

| VBAT  > 51 V,  VTIP – VRING                                                                                     | 41   | 46   | _    |       |

| VTIP ,  VRING  to Battery Ground                                                                                | _    | _    | 56.5 |       |

| VBAT  < 51 V,  VBAT  –  VTIP-VRING                                                                              | 5.75 | 7.2  | 8.5  |       |

| Ring state:                                                                                                     |      |      |      |       |

| VTIP ,  VBAT – VRING                                                                                            | _    | 2.4  | _    |       |

| Loop Closure Threshold (On-hook to Off-hook):                                                                   |      |      |      |       |

| Active states                                                                                                   | _    | 11.2 | _    | mA    |

| Scan state                                                                                                      | _    | 11.2 | _    | mA    |

| Accuracy                                                                                                        | 15   | _    | 15   | %     |

| Loop Closure Threshold Hysteresis:                                                                              |      |      |      |       |

| Active states                                                                                                   | _    | 2.2  | _    | mA    |

| Scan state                                                                                                      | _    | 2.2  | _    | mA    |

Table 1 - Two-Wire Port

| Parameter                                               | Min. | Тур. | Max. | Unit |

|---------------------------------------------------------|------|------|------|------|

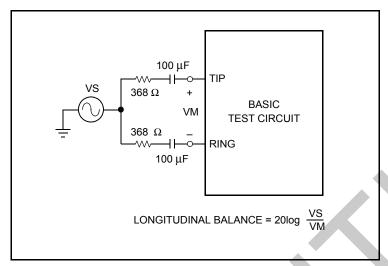

| Longitudinal to Metallic Balance at Tip/Ring:           |      |      |      |      |

| Test Method: Q552 (11/96) Section 2.1.2 and IEEE ® 455: |      |      |      |      |

| 300 Hz to 3.4 kHz <sup>2</sup>                          | 52   | _    | _    | dB   |

| Metallic to Longitudinal (HARM) Balance <sup>3</sup> :  |      |      |      |      |

| 100 Hz to 4000 Hz                                       | 40   | _    |      | dB   |

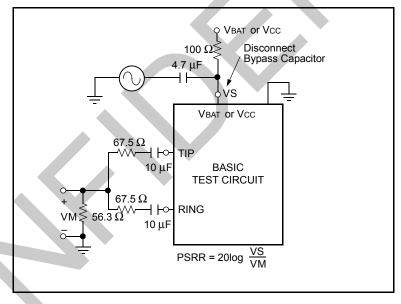

| PSRR 500 Hz to 3000 Hz <sup>1</sup> :                   |      |      |      |      |

| VBAT                                                    | 45   | -    | -    | dB   |

| Vcc                                                     | 25   | 30   | _    | dB   |

Note 1: This parameter is not tested in production. It is guaranteed by design and device characterization.

Note 2: Tested at 1kHz.

Note 3: Tested with DC signals.

Table 1 - Two-Wire Port

| Parameter                                               | Min.     | Тур. | Max.           | Unit |

|---------------------------------------------------------|----------|------|----------------|------|

| TXI (input impedance)                                   |          | 100  | _              | kΩ   |

| Output Offset (VTX)                                     | -10      | 0    | 10             | mV   |

| Output Offset (VITR)                                    | <b>—</b> | _    | 100            | mV   |

| Output Drive Current (VTX)                              | ±300     | _    | _              | μm   |

| Output Drive Current (VITR)                             | ±10      | _    | _              | μΑ   |

| Output Voltage Swing:                                   |          |      |                |      |

| Maximum (VTX, VITR)                                     | 0        | _    | Vcc            | V    |

| Minimum (VTX)                                           | + 0.25   | _    | Vcc – 0.5      | V    |

| Minimum (VITR)                                          | + 0.35   | _    | Vcc – 0.4      | V    |

| Output Short-circuit Current                            | _        | _    | ±50            | mA   |

| Output Load Resistance <sup>1</sup>                     | 10       | _    | _              | kΩ   |

| Output Load Capacitance <sup>1</sup>                    | _        | 20   | _              | pF   |

| RCVN and RCVP (Active States):                          |          |      |                |      |

| Input Voltage Range (Vcc = 3.3 V)                       | 0        | _    | $V_{cc} - 0.3$ | V    |

| Input Bias Current                                      | _        | 0.12 | _              | μΑ   |

| Differential PT/PR Current Sense (DCOUT) <sup>2</sup> : |          |      |                |      |

| Gain (PT/PR to DCOUT)                                   | _        | 30.1 | _              | V/A  |

| Offset Voltage                                          | -30      | _    | 30             | mV   |

| Total Harmonic Distortion (200 Hz—4 kHz) <sup>1</sup> : |          |      |                |      |

| Off-hook                                                | _        | _    | 0.3            | %    |

| On-hook                                                 | _        | _    | 1.0            | %    |

**Table 2 - Analog Pin Characteristics**

| Parameter                                                             | Min.       | Тур. | Max.       | Unit  |

|-----------------------------------------------------------------------|------------|------|------------|-------|

| Transmit Gain (f = 1004 Hz, 1020 Hz) <sup>3</sup>                     |            |      |            |       |

| PT/PR Current to VITR                                                 | -199       | -205 | -211       | V/A   |

| Receive Gain, f = 1004 Hz, 1020 Hz Open Loop                          |            |      |            |       |

| RCVP or RCVN to PT/PR                                                 | 7.76       | 8.00 | 8.24       | V/V   |

| Gain vs. Frequency (transmit and receive), 600 $\Omega$               |            |      |            |       |

| Termination, 1004 Hz, 1020 Hz Reference <sup>1</sup> :                |            |      |            |       |

| 200 Hz to 300 Hz                                                      | -0.3       | 0    | 0.05       |       |

| 300 Hz to 3.4 kHz                                                     | -0.05      | 0    | 0.05       | dB    |

| 3.4 kHz to 20 kHz                                                     | -3.0       | 0    | 0.05       |       |

| 20 kHz to 266 kHz                                                     | _          | -    | 2.0        | •     |

| Gain vs. Level (transmit and receive), 0 dBV Reference <sup>1</sup> : |            |      |            |       |

| -55 dB to +3.0 dB                                                     | -0.05      | 0    | 0.05       | dB    |

| Idle-channel Noise (Tip/Ring), 600 $\Omega$ Termination:              |            |      |            |       |

| C-Message                                                             | <i>→</i> − | 8    | 13         | dBrnC |

| Psophometric <sup>1</sup>                                             |            | -82  | <b>–77</b> | dBrnp |

| 3 kHz Flat <sup>1</sup>                                               |            | _    | 20         | dBrn  |

| Crosstalk between channels                                            |            |      |            |       |

| 0dBm0 single frequency signals 1000 Hz <sup>1</sup>                   |            | _    | -80        | dB    |

| 0dBm0 single frequency signals 12 kHz, 16 kHz <sup>1</sup>            | <u> </u>   | _    | -60        | dB    |

Note 1: This parameter is not tested in production. It is guaranteed by design and device characterization.

Note 2:  $DCOUT\_Gain = \Delta(V_{DCOUT})/\Delta(|ITR|)$ , tested with DC loop current, |ITR|, of 5mA and 20mA, and measure voltage at DCOUT as  $V_{DCOUT}$ . Further, Offset\_voltage =  $V_{DCOUT} - |ITR| \times DCOUT\_Gain$ , |ITR| is 5mA and above.

Note 3: VITR transconductance depends on the resistor from ITR to VTX. This gain assumes an ideal 6.49 k $\Omega$ , (the recommended value). Positive current is defined as the differential current flowing from PT to PR.

**Table 2 - Analog Pin Characteristics**

| Parameter                                                                  | Symbol | Min. | Тур. | Max. | Unit |

|----------------------------------------------------------------------------|--------|------|------|------|------|

| B0/1/2 and TLDEN<br>Input Voltage:                                         |        |      |      |      |      |

| Low Level                                                                  | VIL    | -0.5 | 0.2  | 0.5  | V    |

| High Level                                                                 | Vıн    | 2.0  | 2.5  | Vcc  | V    |

| B0/1/2 and TLDEN<br>Input Current:                                         |        |      |      |      |      |

| Low Level (Vcc = 3.46 V, Vı = 0.4 V)                                       | lı∟    | _    | _    | ±10  | μΑ   |

| High Level ( $V_{cc} = 3.46 \text{ V}$ , $V_{l} = 2.4 \text{ V}$ ), B0/1/2 | Іін    | _    | _    | 30   | μΑ   |

| High Level ( $V_{CC}$ = 3.46 V, $V_I$ = 2.4 V), TLDEN                      | Іін    | _    |      | 35   | μΑ   |

| NSTAT<br>Output Voltage:                                                   |        |      |      |      |      |

| Low Level ( $V_{CC} = 3.13 \text{ V}$ , $I_{OL} = 360 \mu\text{A}$ )       | Vol    | 0    | 0.2  | 0.5  | V    |

| High Level ( $V_{cc}$ = 3.13 V, IOH = $-5 \mu$ A)                          | Vон    | 2.2  | _    | Vcc  | V    |

Table 3 - Logic Inputs and Output (Vcc = 3.3 V)

| Parameter                          | Min. | Тур. | Max. | Unit |    |

|------------------------------------|------|------|------|------|----|

| Tip Open state Tip Input Impedance |      | 150  | _    | _    | kΩ |

| Threshold                          |      |      | 11.2 | _    | mA |

| Hysteresis                         |      | _    | 2.2  | _    | mA |

**Table 4 - Ground Start**

| Parameter                                                                                                                      | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| RINGP/N (Ringing State): Input Voltage Swing                                                                                   | 0    | _    | Vcc  | V    |

| Ring Signal Isolation: PT/PR to VITR Ringing state                                                                             | _    | 60   | _    | dB   |

| Ring Signal Isolation: RINGP/N to PT/PR Non-ringing state                                                                      | _    | 80   | _    | dB   |

| Ring Signal Distortion <sup>1</sup> :                                                                                          |      |      |      |      |

| For Le9530C                                                                                                                    |      |      |      |      |

| VBAT = -100 V, RINGP/N = 0.6 Vpp, RLOAD = open or 5 REN*                                                                       |      | 3    | _    | %    |

| For Le9530D                                                                                                                    |      |      |      |      |

| VBAT = -145 V, RINGP/N = 0.9 Vpp, RLOAD = open or 5 REN*                                                                       |      | 3    |      | %    |

| * 5 REN (Ringing Equivalency Number) is equivalent of 1386 $\Omega$ in series with 40 $\mu\text{F},$ Rloop = 0 to 100 $\Omega$ |      |      |      |      |

| Differential Gain RINGP/N to PT/PR                                                                                             |      |      |      |      |

| For Le9530C                                                                                                                    |      |      |      |      |

| VBAT = -100 V, RINGP/N = 0.6 Vpp, RLOAD = open                                                                                 | 146  | 153  | 160  | V/V  |

| For Le9530D                                                                                                                    |      |      |      |      |

| VBAT = -145 V, RINGP/N = 0.9 Vpp, RLOAD = open                                                                                 | 146  | 153  | 160  | V/V  |

Table 5 - Ringing Specifications

Note 1: This parameter is not tested in production. It is guaranteed by design and device characterization.

| Parameter                                                    | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------------|------|------|------|------|

| Ring Trip (NSTAT = 0): Loop Resistance (total) VBAT Applied  | 100  | _    | 600  | Ω    |

| Ring Trip (NSTAT = 1):  Loop Resistance (total) VBAT Applied | _    | _    | 10   | kΩ   |

| Trip Time (f = 20 Hz) <sup>1</sup>                           | _    | _    | 100  | ms   |

| Hysteresis <sup>1</sup>                                      |      | 10   | —    | mA   |

Table 6 - Ring Trip

Note 1: This parameter is not tested in production. It is guaranteed by design and device characterization.

## **Test Switch Specifications**

| Item        | Condition                                   | Min. | Тур. | Max. | Unit. |

|-------------|---------------------------------------------|------|------|------|-------|

| Test Switch | ON-Resistance, (V(25 mA) – V(20 mA)) / 5 mA | 10   | 19   | 30   | Ω     |

|             | On-Voltage drop at ±20 mA <sup>1</sup>      | -3   |      | +3   | V     |

|             | Off-state Leakage                           |      | _    | 5    | μA    |

Note 1: Additional 10% variations to the minimum and maximum limits at -40 $^{\circ}$  C.

## **Operating States**

Note: Internal 100  $k\Omega$  pull downs on B0, B1, B2 and 100  $k\Omega$  pull down on TLDEN.

| В0 | B1 | B2 | TLDEN   | Operating State                                                                                |  |  |  |

|----|----|----|---------|------------------------------------------------------------------------------------------------|--|--|--|

| 0  | 0  | 0  | 0/float | Active forward battery, Low DC current limit (25mA), Test Switch Off. (Default Power Up State) |  |  |  |

| 0  | 0  | 1  | 0/float | Active forward battery, High DC current limit (40mA), Test Switch Off.                         |  |  |  |

| 0  | 1  | 0  | 0/float | Active reverse battery, Low DC current limit (25mA), Test Switch Off.                          |  |  |  |

| 0  | 1  | 1  | 0/float | Active reverse battery, High DC current limit (40mA), Test Switch Off.                         |  |  |  |

| 1  | 1  | 0  | 0/float | Ground start, Test Switch Off.                                                                 |  |  |  |

| 1  | 0  | 0  | 0/float | Scan, Test Switch Off.                                                                         |  |  |  |

| 1  | 1  | 1  | 0/float | Disconnect, Test Switch Off.                                                                   |  |  |  |

| 1  | 0  | 1  | 0/float | Ring, Test Switch Off.                                                                         |  |  |  |

| 0  | 0  | 0  | 1       | Active forward battery, Low DC current limit (25mA), Test Switch On.                           |  |  |  |

| 0  | 0  | 1  | 1       | Active forward battery, High DC current limit (40mA), Test Switch On.                          |  |  |  |

| 0  | 1  | 0  | 1       | Active reverse battery, Low DC current limit (25mA), Test Switch On.                           |  |  |  |

| 0  | 1  | 1  | 1       | Active reverse battery, High DC current limit (40mA), Test Switch On.                          |  |  |  |

| 1  | 1  | 0  | 1       | Ground start, Test Switch On.                                                                  |  |  |  |

| 1  | 0  | 0  | 1       | Scan, Test Switch On.                                                                          |  |  |  |

| 1  | 1  | 1  | 1       | Disconnect, Test Switch On.                                                                    |  |  |  |

| 1  | 0  | 1  | 1       | Ring, Test Switch On.                                                                          |  |  |  |

## **NSTAT**

0 = off-hook or ring trip or thermal shutdown or ring ground.1 = on-hook and no ring trip and no thermal shutdown and no ring ground.

**Table 7 - Supervision Coding**

## **Operating State Definitions**

#### Scan

- Except for loop closure, all circuits (including ring trip and ground start detector) are powered down.

- On-hook transmission is disabled.

- Pin PT is positive with respect to PR.

- The tip to ring on-hook differential voltage will be typically between –44 V and –51 V with a –51 V to –100 primary battery.

### Active—Forward Battery—Low DC Current Limit

- · Pin PT is positive with respect to PR.

- DC loop current limit is 25 mA.

- · Loop closure detector is active.

- Ring trip detector is turned off to conserve power.

- On-hook transmission is allowed, supports undistorted transmission of 3.14 dBm into 900 ohms with 500 mVrms of PPM for any supported loop length.

- The tip to ring on-hook differential voltage will be typically between –41 V and –49 V with a –51 V to –100 V primary battery.

- Default power up state.

#### Active—Forward Battery—High DC Current Limit

- Pin PT is positive with respect to PR.

- DC loop current limit is 40 mA.

- Loop closure detector is active

- Ring trip detector is turned off to conserve power.

- On-hook transmission is allowed.

- The tip to ring on-hook differential voltage will be typically between -41 V and -49 V with a -51 V to -100 V primary battery.

- Supports undistorted transmission of 3.14 dBm into 900 ohms with 500 mVrms of PPM for any supported loop length and on-hook transmission

#### Active—Reverse Battery—Low DC Current Limit

- Pin PR is positive with respect to PT.

- DC loop current limit is 25 mA.

- Loop closure detector is active.

- Ring trip detector is turned off to conserve power.

- On-hook transmission is allowed.

- The tip to ring on-hook differential voltage will be typically between –41 V and –49 V with a –51 V to –100 V primary battery.

- Supports undistorted transmission of 3.14 dBm into 900 ohms with 500 mVrms of PPM for any supported loop length and on-hook transmission

#### Active—Reverse Battery—High DC Current Limit

- · Pin PR is positive with respect to PT.

- DC loop current limit is 40 mA.

- · Loop closure detector is active.

- · Ring trip detector is turned off to conserve power.

- On-hook transmission is allowed.

- The tip to ring on-hook differential voltage will be typically between –41 V and –49 V with a –51 V to –100 V primary battery.

- Supports undistorted transmission of 3.14 dBm into 900 ohms with 500 mVrms of PPM for any supported loop length and on-hook transmission

#### **Disconnect**

- The tip/ring amplifiers and all supervision are turned off.

- · The SLIC device goes into a high-impedance state.

- NSTAT is forced high (on-hook).

#### Ringing

- · Power ring signal is applied to tip and ring.

- Input wave form at RINGP/N is amplified with a high gain.

- Ring trip supervision is active; loop closure is inactive.

- Overhead voltage is reduced to typically 2.4 V.

#### **Ground Start**

- Tip drive amplifier is turned off.

- Device presents a high impedance (>100 kΩ) to pin PT.

- Device presents amplitude clamped (<56.5 V) current-limited battery (VBAT) to PR.</li>

- · Ground Start detector is active, threshold adjusted for common mode current

#### **Thermal Shutdown**

- Not controlled via truth table inputs.

- This mode is caused by excessive heating of the device, such as may be encountered in an extended power cross situation. NSTAT output is forced low or off-hook during a thermal shutdown event.

## **Test Circuit**

Figure 4 - Le9530 Basic Test Circuit (one channel of the device shown)

Figure 5 - Metallic PSRR

Figure 6 - Longitudinal PSRR

Figure 7 - Longitudinal Balance

Figure 8 - AC Gains

## **Applications**

#### **DC Loop Current Limit**

In the Active Modes the DC current limit is determined by the operation state. The Low DC current limit is 25 mA. The High DC current limit is 40 mA. Note that there is in the order of 10 k $\Omega$  slope to the I/V characteristic in the current-limit region; thus, once in current limit, the actual loop current will increase slightly, as loop length decreases.

Upon off-hook in the Active or standby modes there will be a transient response of the current-limit circuit upon an on- to off-hook transition.

| Parameter                                                                               | Value     | Unit |

|-----------------------------------------------------------------------------------------|-----------|------|

| DC Loop Current:<br>$R_{LOOP}$ = 100 $\Omega$ , On- to Off-hook Transition time < 5 ms  | ILIM + 60 | mA   |

| DC Loop Current:<br>$R_{LOOP}$ = 100 $\Omega$ , On- to Off-hook Transition time < 50 ms | ILIM + 20 | mA   |

| DC Loop Current: $R_{LOOP}$ = 100 $\Omega$ , On- to Off-hook Transition time < 300 ms   | ILIM      | mA   |

Table 8 - Typical Active or Standby state On-Hook to Off-Hook Tip/Ring Current-Limit Transient Response

#### **Overhead Voltage**

#### Scan State

If the magnitude of the primary battery is greater than 51 V (but no more than 100 V), the magnitude of the open loop tip-to-ring open loop voltage is clamped typically between 44 V and 51 V. If the magnitude of the primary battery is less than a nominal 51 V, the overhead voltage will track the magnitude of the battery voltage, i.e., the magnitude of the open circuit tip-to-ring voltage will be about 4 V less than battery.

#### **Active Transmission States**

If the magnitude of the primary battery is greater than 51 V (but no more than 100 V), the magnitude of the open loop tip-to-ring open loop voltage is clamped typically between 41 and 49 V. If the magnitude of the primary battery is less than a nominal 51 V, the overhead voltage will track the magnitude of the battery voltage, i.e., the magnitude of the open circuit tip-to-ring voltage will be 6 to 8 V less than battery. Overhead is adequate for an on-hook transmission of 3.14 dBm into 900  $\Omega$  with additional head room for a 500-mV PPM signal under any specified loop or any specified battery.

#### **Ringing State**

In the Ringing state, to maximize ringing loop length, the overhead is decreased to the saturation of the tip ring drive amplifiers, a nominal 2.4 V.

During the Ringing state the ringing input is coming from RINGP/N path with a gain of 150. During the Ringing state, to conserve power, the AAC amplifier in the transmit direction at VITR is deactivated. However, the AX amplifier at VTX is active during the ring state; differential ring current may be sensed at VTX during the ring state.

#### Supervision

The Le9530 device offers the loop closure and ring trip supervision functions. Internal to the device, the outputs of these detectors are multiplexed into a single package output, NSTAT. The ring trip detector is valid on NSTAT during the ring state, and loop closure detector is valid on NSTAT during active and on-hook transmission states. Additionally, common-mode current is detected for ground start applications. This status is output onto NSTAT and is valid during ground start mode.

#### **Loop Closure**

The loop closure has a fixed typical 11.2 mA on-hook to off-hook threshold in the Active and Scan states. In either case, there is a 2.2-mA hysteresis.

For systems designed to set the SLIC in Scan state while the loop is in on hook condition and to set the SLIC in Active state when the loop condition becomes off hook and to operate with a less negative potential battery it is desirable to set the SLIC in the Active state first before ramping the battery from a more negative potential to a less negative potential for enhanced system performance.

#### **Ring Trip**

The ring trip detector requires only a single-pole filter at the input, minimizing external components. An R/C combination of 383 k $\Omega$  and 0.1  $\mu$ F, for a filter pole at 4.15 Hz, is recommended.

The ring trip threshold is internally fixed as a function of battery voltage and is given by the following:

$$R_T$$

(mA) = 33 \* {(0.0045 \* VBAT) + 1.146}

where:

R<sub>T</sub> is ring trip current in mA.

V<sub>BAT</sub> is the magnitude of the ring battery in volts.

The ring trip detection hysteresis is about 10mA.

#### **Ground Start**

In the ground start applications, the loop closure detector is also used to indicate ring-ground has occurred. During ground start mode, loop current will be common mode, rather than differential as in loop start mode. Thus, in ground start the threshold of the loop closure detector is reduced by one half the threshold seen in the loop start mode. This output is seen at the NSTAT output pin.

#### **Power Ring**

The device offers a ring state, in which a balanced power ring signal is provided to the tip/ring pair. During the ring state, a user-supplied low-voltage ring signal is input to the device's RINGP/N inputs. This signal is amplified to produce the balanced power ring signal. The user may supply a sine wave input, PWM input, or a square wave to produce sinusoidal or trapezoidal ringing at tip and ring.

### Sine Wave Input Signal and Sine Wave Power Ring Signal Output

The low-voltage sine wave input is applied differentially or single ended to the Le9530 device at pins RINGP/N. During the ring state, the signals at pins RINGP/N are amplified and presented to the subscriber loop. The differential gain from RINGP/N to tip and ring in the Ringing mode, which is different when the channel is in Active state, is specified in the device specifications.

When the device enters the Ring state, the clamp circuit is disabled, allowing the voltage magnitude of the power ring signal to be maximized. Additionally, in the Ring state, the loop current limit is increased and is not limited by DC loop current limit.

The magnitude of the power ring voltage will be a function of the gain of the ring amplifier, the high-voltage battery, and the input signal at RINGP/N. The input range of the signal at RINGP/N is 0 V to Vcc. As the input voltage at RINGP/N is increased, the magnitude of the power ring voltage at tip and ring will increase linearly, until the tip and ring drive amplifiers begin to saturate. Once the tip and ring amplifiers reach saturation, further increases of the input signal will cause clipping distortion of the power ring signal at tip and ring. The ring signal will appear balanced on tip and ring. That is, the power ring signal is applied to both tip and ring, with the signal on tip 180 degree out of phase from the signal on ring.

The point at which clipping of the power ring signal begins at tip and ring is a function of the battery voltage and the input signal at RINGP/N.

#### Power Ringing with Le9530D

For operation of the Le9530D device with a high magnitude on VBAT greater than 100 V, special attention must be given to the following areas at the system level. VBAT may be more negative than -100 V only during the actual power ringing. The amplitude of VBAT should not exceed 100 V when the SLIC device is not in the Ringing mode. The amplitude of VBAT may not exceed 100 V during the silent period of ringing or any other non-ringing mode of operation.

#### **Design Examples**

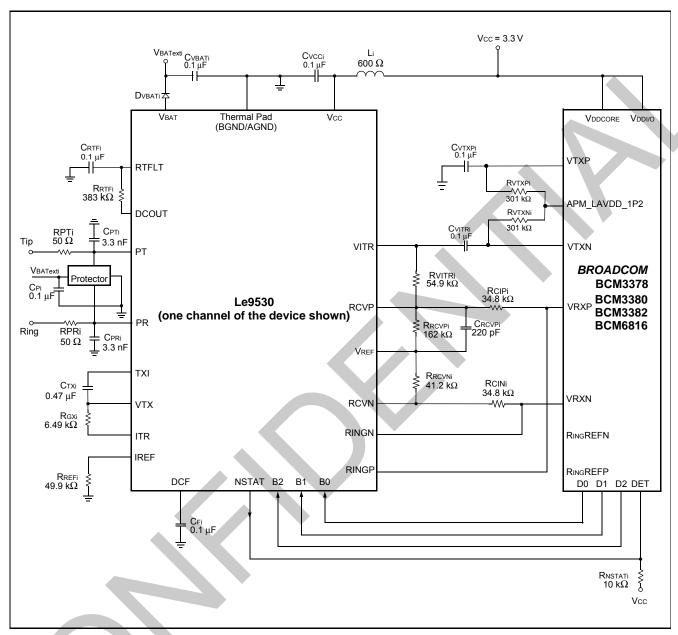

The following reference circuit shows the complete SLIC device schematic for interface to the new Broadcom ICs such as BCM3378/3380/3382/6816. One channel of the SLIC device is shown. Components with i being 1 are for channel 1 and with i being 2 for channel 2. This circuit has a natural  $700-\Omega$  AC termination impedance. The Broadcom IC has programmable registers to modify the external  $700-\Omega$  termination to any other real or complex terminations, as well as to set transmit and receive gains, and other AC parameters. The Broadcom IC also drives ringing inputs, sets SLIC operation states, and monitors NSTAT. The voltage of the battery supply to the SLIC VBAT is expected to be properly set and may vary depending upon SLIC operational states. The ringing maybe driven by the same voice outputs or by the separate PWM outputs.

Figure 9 shows the ringing is driven by PWM output path.

Figure 10 shows the ringing is driven by the same voice path.

Contact your Microsemi account representative for assistance with other applications.

Figure 9 - Le9530 Reference Schematic Interfacing Broadcom Codec

Figure 10 - Le9530 Reference Schematic Interfacing Broadcom Codec with Shared Driving Paths

### **Application Circuit Parts List**

The following parts list is for the Microsemi Le9530 SLIC device and Broadcom BCM3378/3380/3382/6816 fully programmable codec. Components for channel 1 ends with i=1 and components for channel 2 ends with i=2.

| Item                | Туре        | Value                                             | Tolerance                   | Rating         | Comments                                                                                                                               |

|---------------------|-------------|---------------------------------------------------|-----------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------|

|                     |             |                                                   | Fault Protection            | on             |                                                                                                                                        |

| RPTi,<br>RPRi       | Resistor    | $50~\Omega^1$                                     | 20% absolute<br>1% mismatch | Fusible or PTC | Protection resistor                                                                                                                    |

| Protector           |             |                                                   | _                           | _              | One for each channel or possibly a dual version.                                                                                       |

| CPi                 | Capacitor   | 0.1 μF                                            | 20%                         | 200 V          | Consult protector vendor for recommended value. This capacitor may or may not be required depending upon the type of protector in use. |

|                     |             |                                                   | Power Supply                | y              |                                                                                                                                        |

| C <sub>VBATi</sub>  | Capacitor   | 0.1 μF                                            | 20%                         | 200 V          | VBAT filter capacitor                                                                                                                  |

| D <sub>VBATi</sub>  | Diode       | 1N4004                                            | _                           |                | Reverse current                                                                                                                        |

| C <sub>VCCi</sub>   | Capacitor   | 0.1 μF                                            | 20%                         | 10 V           | Ceramic bypass capacitor                                                                                                               |

| L <sub>i</sub>      |             | 600 Ω, <i>Murata</i> <sup>®</sup><br>BLM11A601SPB | -                           |                | Ferrite Bead for filtering                                                                                                             |

| C <sub>Fi</sub>     | Capacitor   | 0.1 μF                                            | 20%                         | 100 V          | Filter capacitor.                                                                                                                      |

| R <sub>REFi</sub>   | Resistor    | 49.9 kΩ                                           | 1%                          | 1/16 W         | Sets internal reference current                                                                                                        |

|                     |             |                                                   | Ring Trip                   |                |                                                                                                                                        |

| C <sub>RTFi</sub>   | Capacitor   | 0.1 μF                                            | 20%                         | 10 V           | Ring trip filter capacitor                                                                                                             |

| R <sub>RTFi</sub>   | Resistor    | 383 kΩ                                            | 1%                          | 1/16 W         | Ring trip filter resistor                                                                                                              |

|                     |             |                                                   | AC Interface                |                |                                                                                                                                        |

| R <sub>GXi</sub>    | Resistor    | 6.49 kΩ                                           | 1%                          | 1/16 W         | Sets trans-impedance                                                                                                                   |

| C <sub>TXi</sub>    | Capacitor   | 0.47 μF                                           | 20%                         | 10 V           | AC/DC separation                                                                                                                       |

| C <sub>VITRi</sub>  | Capacitor   | 0.1 μF                                            | 20%                         | 10 V           | DC blocking capacitor                                                                                                                  |

| C <sub>VTXPi</sub>  | Capacitor   | 0.1 μF                                            | 20%                         | 10 V           | DC blocking capacitor                                                                                                                  |

| $R_{VITRi}$         | Resistor    | 54.9 kΩ                                           | 1%                          | 1/16 W         | AC interface                                                                                                                           |

| R <sub>VTXPi</sub>  | Resistor    | 301 kΩ                                            | 1%                          | 1/16 W         | AC interface                                                                                                                           |

| R <sub>VTXNi</sub>  | Resistor    | 301 kΩ                                            | 1%                          | 1/16 W         | AC interface                                                                                                                           |

| R <sub>CIPi</sub>   | Resistor    | 34.8 kΩ                                           | 1%                          | 1/16 W         | AC interface                                                                                                                           |

| R <sub>RCVPi</sub>  | Resistor    | 162 kΩ                                            | 1%                          | 1/16 W         | AC interface                                                                                                                           |

| C <sub>RCVPi</sub>  | Capacitor   | 220 pF                                            | 20%                         | 10 V           | AC interface                                                                                                                           |

| C <sub>INGPi</sub>  | Capacitor   | 0.068 μF                                          | 20%                         | 10 V           | Ringing interface                                                                                                                      |

| C <sub>INGNi</sub>  | Capacitor   | 0.068 μF                                          | 20%                         | 10 V           | Ringing interface                                                                                                                      |

| R <sub>NSTATi</sub> | Resistor    | 10 kΩ                                             | 1%                          | 1/16 W         | Control                                                                                                                                |

| $C_{PTi,} C_{PRi}$  | Capacitor   | 3.3 nF <sup>2</sup>                               | 20%                         | 200 V          | EMC                                                                                                                                    |

| Le9530              | SLIC device | _                                                 | _                           | _              | Dual-channel SLIC device                                                                                                               |

Note 1: Minimum  $40\Omega$  required for loop stability.

Note 2: Consult Microsemi for further enhanced performance

## **Physical Dimensions**

### 48-Pin eTQFP

FIGURE 2: EVEN LEAD SIDES

TOP VIEW

FIGURE 3: SECTION A-A

CONTROL DIMENSIONS ARE IN MILLIMETERS.

| N = 48         |            |      |      |               |       |       |

|----------------|------------|------|------|---------------|-------|-------|

| SYMBOL         | MILLIMETER |      |      | INCH          |       |       |

|                | MIN.       | NOM. | MAX. | MIN.          | NOM.  | MAX.  |

| Α              | _          | _    | 1.20 | _             | _     | 0.047 |

| A1             | 0.05       |      | 0.15 | 0.002         | _     | 0.006 |

| A2             | 0.95       | 1.00 | 1.05 | 0.037         | 0.039 | 0.041 |

| D              | 9.00 BSC.  |      |      | 0.354 BSC.    |       |       |

| D1             | 7.00 BSC.  |      |      | 0.276 BSC.    |       |       |

| E              | 9.00 BSC.  |      |      | 0.354 BSC.    |       |       |

| E1             | 7.00 BSC.  |      |      | 0.276 BSC.    |       |       |

| D <sub>2</sub> | 5.21 BSC.  |      |      | 0.205 BSC.    |       |       |

| E2             | 5.21 BSC.  |      |      | 0.205 BSC.    |       |       |

| е              | 0.50 BSC.  |      |      | 0.019685 BSC. |       |       |

| b              | 0.17       | 0.20 | 0.27 | 0.007         | 0.008 | 0.011 |

| R <sub>1</sub> | 0.08       | —    | —    | 0.003         | _     | —     |

| R2             | 0.08       |      | 0.20 | 0.003         |       | 0.008 |

| С              | 0.09       |      | 0.20 | 0.004         |       | 0.008 |

| L              | 0.45       | 0.60 | 0.75 | 0.018         | 0.024 | 0.030 |

| L <sub>1</sub> | 1.00 REF   |      |      | 0.039 REF     |       |       |

| S              | 0.20       |      | _    | 0.008         |       |       |

Note: Packages may have mold tooling markings on the surface. These markings have no impact on the form, fit or function of the device. Markings will vary with the mold tool used in manufacturing.

## 48-pin QFN

Note: Packages may have mold tooling markings on the surface. These markings have no impact on the form, fit or function of the device. Markings will vary with the mold tool used in manufacturing.

## **Revision history**

#### A1 to B1

- · Updated the Connection Diagram (pin out assignment) on page 5.

- · Updated descriptions in the Loop Closure section on page 16.

#### B1 to C1

Added capacitor C<sub>RCVP</sub> on page 18, 19, and 20.

#### C1 (Version 3) to Version 4

- · Descriptions in the Feature list on page 1.

- Updated the table of Supply Currents on page 8

- · Updated Table 5 Ringing Specifications on page 11.

- · Further updated descriptions in the Loop Closure section on page 16.

- Updated drawings in the Physical Dimensions on page 21.

#### **Version 4 to Version 5**

- Updated Operation States, page 19, and various other places related through out the data sheet.

- Updated Table 3 Logic Inputs and Outputs, on page 16.

#### **Version 5 to Version 6**

- Updated Table 2 Analog Pin Characteristics regarding crosstalk between channels, on page 15.

- Corrected Figure 1 Block Diagram regarding current sensing ratio from ITR/325 to ITR/432, on page 1.

#### **Version 6 to Version 7**

- Modified the descriptions of "Parameter" regarding "Open Loop Voltage" in Table 1, Page 13.

- Modified "Longitudinal Balance at PT/PR" to "Longitudinal Balance at Tip/Ring" in Table 1, Page 14.

- · Removed specification of "Idle Channel Noise (VTX)" in Table 2, Page 15.

- Corrected "C<sub>VCCi</sub>" value from 0.47μF to 0.1μF in the table on Page 30.

#### **Version 7 to Version 8**

· Added device offering in QFN package.

#### **Version 8 to Version 9**

- Added Microsemi logo