# Atmel ATPL210A

# **PRIME compliant Power Line Communications SoC**

### DATASHEET

### **Features**

- Core

- ADD8051C3A enhanced 8051 core

- Speedups up to x5 vs. standard 8051 microcontroller

- Modem

- Power Line Carrier Modem for 50 and 60 Hz mains

- 97-carrier OFDM PRIME compliant

- Baud rate Selectable: 21400 to 128600 bps

- Differential BPSK, QPSK, 8-PSK modulations

- Memories

- 32Kbytes on-chip SRAM

- Up to 256Kbytes external SRAM

- In-circuit serial flash programming

- Auto boot-loading program from serial flash

- Automatic Gain Control and signal amplitude tracking

- Embedded on-chip DMAs

- Automatic code encryption during boot loading

- Media Access Control

- · Viterbi decoding and CRC PRIME compliant

- 128-bit AES encryption

- Channel sensing and collision pre-detection

- Peripherals

- Two 2-wire UARTs

- Two SPI. SPI to serial flash and External RTC. Buffered SPI to external metering IC

- Programmable Watchdog

- Up to 14 I/O lines

- Package

- 120-lead LQFP, 14 x 14 mm, pitch 0.4 mm

- Pb-free and RoHS compliant

- Typical Applications

- Automated Meter Reading (AMR) & Advanced Meter Management (AMM)

- Street lighting

- Home Automation

### Description

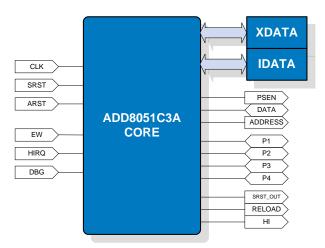

The ATPL210A is a Power Line Communications System on Chip, which implements a full PRIME compliant PLC modem. It includes an enhanced 8051 microcontroller (IP core ADD8051C3A), a Medium Access Controller (MAC) (IP core ADD1221) and a Modem circuit (IP core ADD1321) for power line medium using OFDM modulation compatible with PRIME specifications.

ATPL210A is oriented to high performance & robust AMR systems. The ATPL210A is designed to be used by meter manufacturers to provide a low cost and compact solutions for AMR (Automated Meter Reading) & AMM (Advanced Meter Management) systems using narrow band power line communications.

This device has been developed to reduce CPU computational load in PLC systems running PRIME protocols. ATPL210A includes all necessary resources to be used as main controller in metering applications, and allows an external device to communicate according to PLC PRIME specifications.

# **Table of Contents**

| 1. | Block Diagram     |                                                                          |    |  |  |  |  |

|----|-------------------|--------------------------------------------------------------------------|----|--|--|--|--|

| 2. | Pac<br>2.1<br>2.2 | kage and Pinout<br>120-Lead LQFP Package Outline<br>120-Lead LQFP Pinout | 8  |  |  |  |  |

| 3. | Pin               | Description                                                              | 11 |  |  |  |  |

| 4  | PRI               | ME overview                                                              | 18 |  |  |  |  |

| т. | 4.1               | Kev Features                                                             |    |  |  |  |  |

|    | 4.1               | PRIME physical layer overview                                            |    |  |  |  |  |

|    | 7.2               | 4.2.1 Main features                                                      |    |  |  |  |  |

|    |                   | 4.2.2 Orthogonal Frequency Division Multiplexing (OFDM)                  |    |  |  |  |  |

|    | 4.3               | PRIME MAC layer overview                                                 |    |  |  |  |  |

|    |                   | 4.3.1 Base Node                                                          |    |  |  |  |  |

|    |                   | 4.3.2 Service Node                                                       |    |  |  |  |  |

|    | 4.4               | Convergence Layer                                                        | 21 |  |  |  |  |

| 5. | Proc              | cessor and Architecture                                                  | 23 |  |  |  |  |

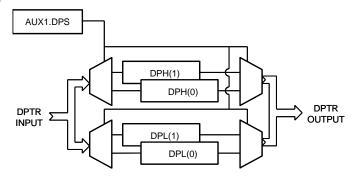

|    | 5.1               | ADD8051C3A Microcontroller Description                                   | 23 |  |  |  |  |

|    | 5.2               | Core Pinout Description                                                  |    |  |  |  |  |

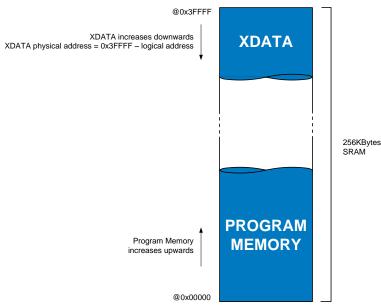

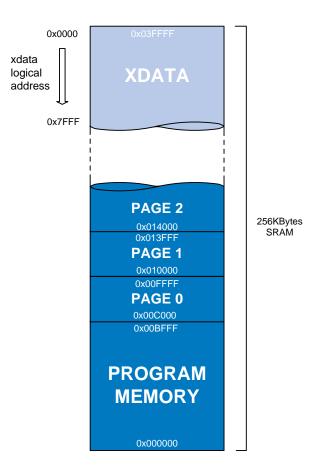

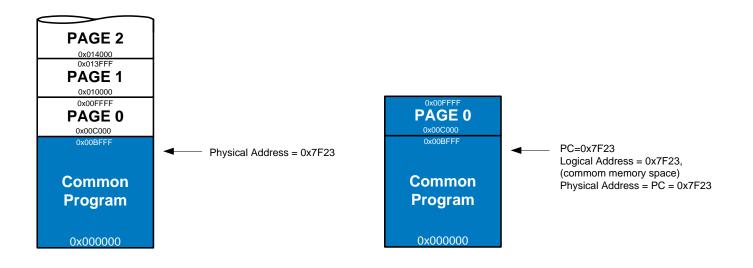

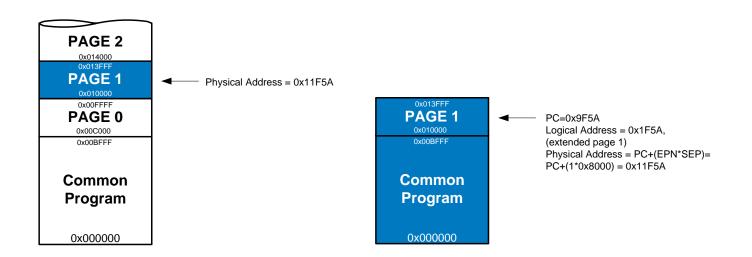

|    | 5.3               | Memory Organization                                                      |    |  |  |  |  |

|    |                   | 5.3.2 Program Memory                                                     |    |  |  |  |  |

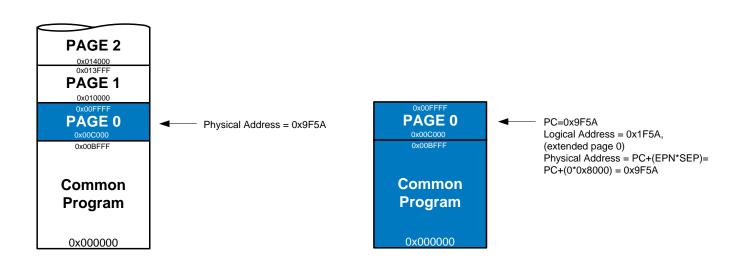

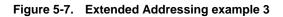

|    |                   | 5.3.3 Extended Addressing                                                |    |  |  |  |  |

|    |                   | 5.3.4 Data Memory                                                        |    |  |  |  |  |

|    | 5.4               | 5.3.5 SFR Registers<br>Instruction Set                                   |    |  |  |  |  |

|    | 5.4               | 5.4.1 Program Status Word                                                |    |  |  |  |  |

|    |                   | 5.4.2 Addressing Modes                                                   |    |  |  |  |  |

|    |                   | 5.4.3 Arithmetic Instructions                                            |    |  |  |  |  |

|    |                   | 5.4.4 Logical Instructions                                               |    |  |  |  |  |

|    |                   | 5.4.5 Data Transfer Instructions                                         |    |  |  |  |  |

|    |                   | 5.4.6 Boolean Instructions                                               |    |  |  |  |  |

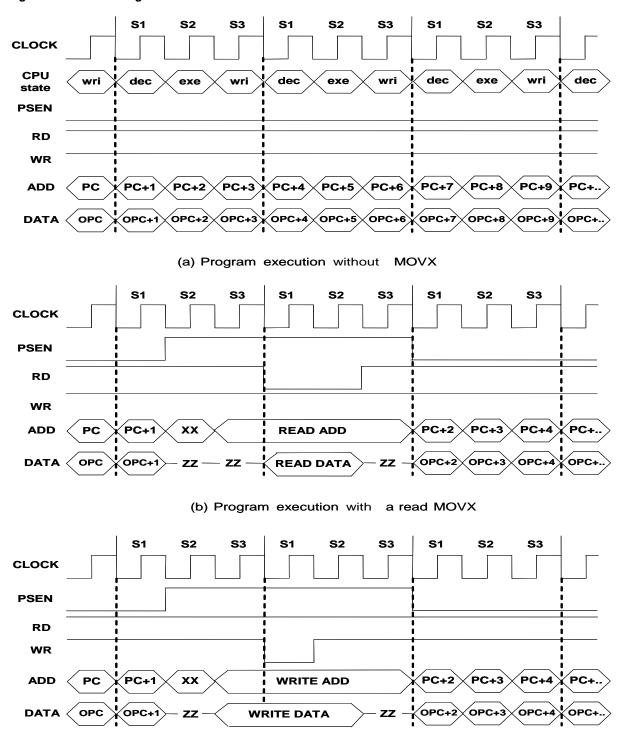

|    | 5.5               | 5.4.7 Jump Instructions<br>CPU Timing                                    |    |  |  |  |  |

|    | 5.5               | 5.5.2 Reset Modes                                                        |    |  |  |  |  |

|    |                   | 5.5.3 Power Saving Modes                                                 |    |  |  |  |  |

|    |                   | 5.5.4 Idle Mode                                                          |    |  |  |  |  |

|    |                   | 5.5.5 Power-Down Mode                                                    |    |  |  |  |  |

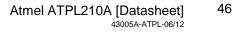

|    | 5.6               | Interrupts                                                               |    |  |  |  |  |

|    |                   | 5.6.1 Interrupt Enabling                                                 |    |  |  |  |  |

|    |                   | 5.6.2 Interrupt Priorities                                               |    |  |  |  |  |

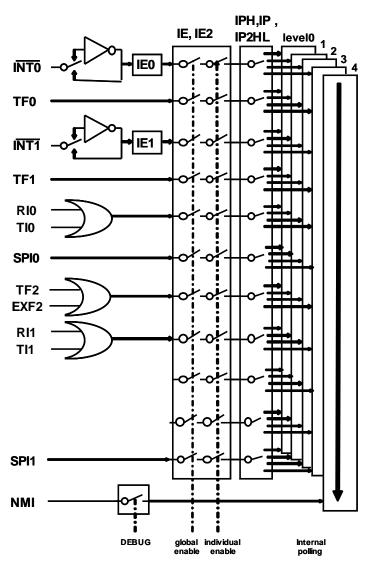

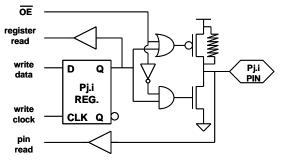

|    | 5.7               | 5.6.3 Interrupt Handling<br>I/O Ports                                    |    |  |  |  |  |

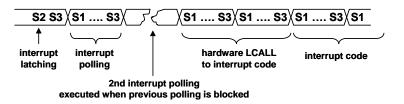

|    | 5.7               | 5.7.2 I/O Configurations                                                 |    |  |  |  |  |

|    |                   | 5.7.3 Read-Modify-Write Feature                                          |    |  |  |  |  |

|    |                   | 5.7.4 Accessing External Memories                                        |    |  |  |  |  |

|    | 5.8               | Debug Mode                                                               |    |  |  |  |  |

| 6. | Time              | ers 55                                                                   |    |  |  |  |  |

|    | 6.1               | Timer 0 and Timer 1                                                      | 55 |  |  |  |  |

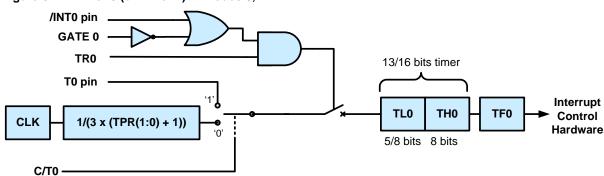

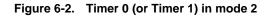

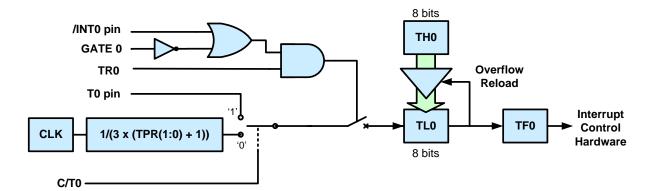

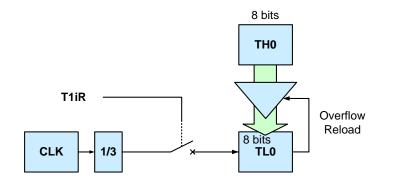

|    | 0.1               | 6.1.1 Timer Mode 0                                                       |    |  |  |  |  |

|     | 6.1.1    | Timer Mode 0 | 56 |

|-----|----------|--------------|----|

|     | 6.1.2    | Timer Mode 1 | 57 |

|     | 6.1.3    | Timer Mode 2 | 57 |

|     | 6.1.4    | Timer Mode 3 | 57 |

| 6.2 | Timer 2. |              | 58 |

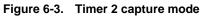

|     | 6.2.2    | Capture mode | 59 |

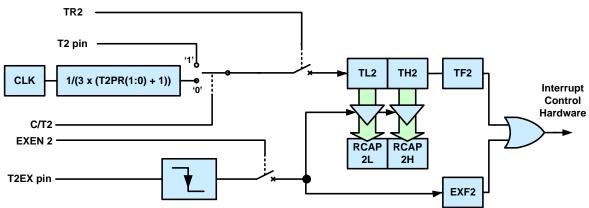

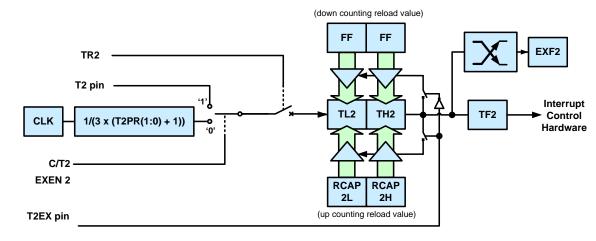

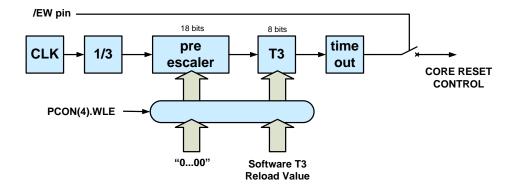

|    | 6.3          | <ul> <li>6.2.3 Auto-Reload mode</li> <li>6.2.4 Clock-Out mode</li> <li>6.2.5 Baud rate Generator mode</li> <li>Watchdog (timer 3)</li> </ul> | 60<br>61 |

|----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 7. |              |                                                                                                                                              |          |

| 1. |              | ndard Serial Interfaces                                                                                                                      |          |

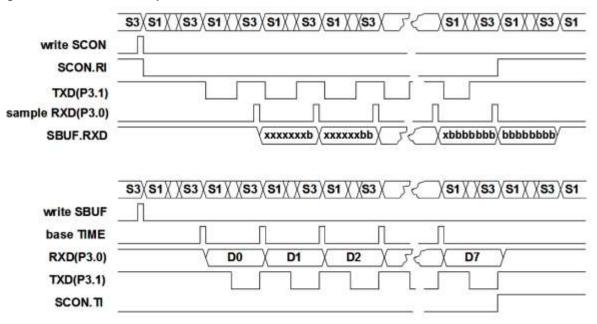

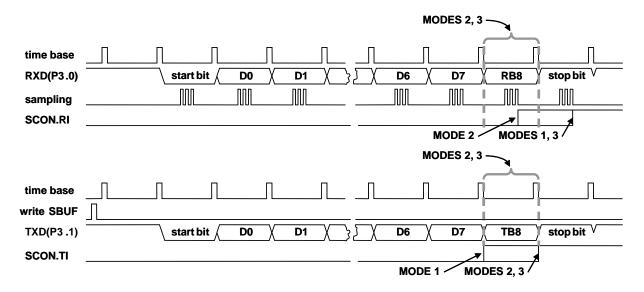

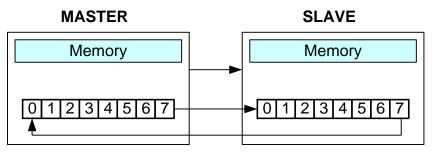

|    | 7.1          | Serial Port modes<br>7.1.1 Mode 0 (shift register mode)                                                                                      |          |

|    |              | 7.1.2 Mode 1 (8-bit UART)                                                                                                                    |          |

|    |              | 7.1.3 Modes 2 and 3 (9-bit UART)                                                                                                             | 65       |

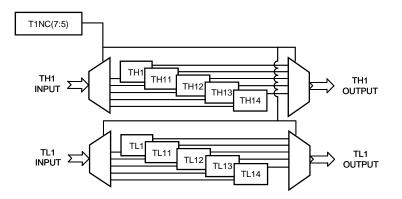

|    | 7.2          | Serial Port Timers (Timers 11 &12)                                                                                                           |          |

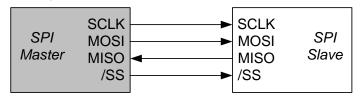

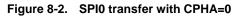

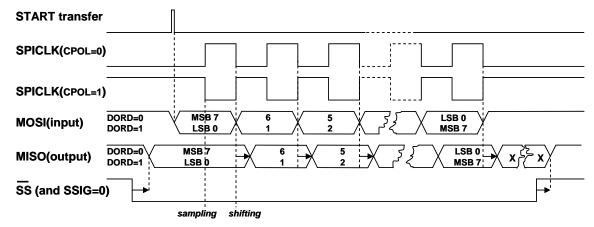

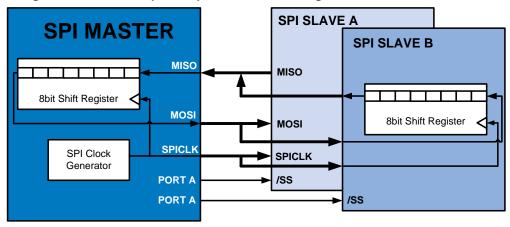

| 8. | Seria        | al Peripheral Interfaces SPI0 and SPI1                                                                                                       | 69       |

|    | 8.1          | SPI description                                                                                                                              | 69       |

|    |              | 8.1.2 SPI clock phase, polarity and operation                                                                                                | 71       |

|    | 8.2          | 8.1.3 SPI0 write collision<br>SPI Modes                                                                                                      |          |

|    | 0.2<br>8.3   | SPI Modes                                                                                                                                    |          |

| 0  |              | ·                                                                                                                                            |          |

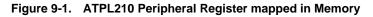

| 9. | Penp         | pheral Registers                                                                                                                             |          |

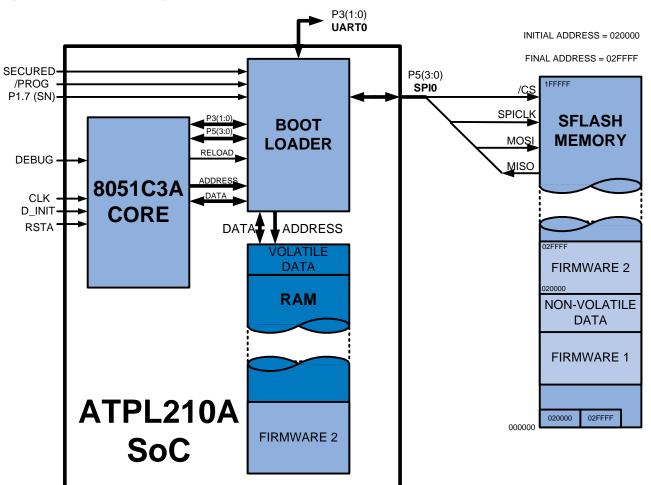

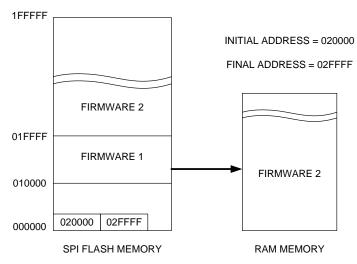

| 10 | . Boot       | t Loader                                                                                                                                     | 78       |

|    | 10.2         | Pin Description                                                                                                                              | 79       |

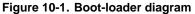

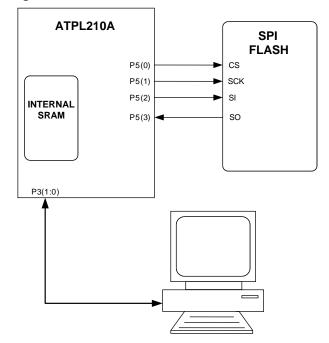

|    | 10.3         | 5 5                                                                                                                                          |          |

|    |              | 10.3.1 In-System programming                                                                                                                 |          |

|    | 10.4         | 10.3.2 SPI Flash programming<br>System startup                                                                                               |          |

|    | 10.1         | 10.4.2 Encrypted firmware requirements                                                                                                       |          |

|    |              | 10.4.3 Supported Devices                                                                                                                     | 83       |

|    | 105          | 10.4.3.1 Serial Number Device                                                                                                                |          |

|    | 10.5         | Boot loader registers                                                                                                                        |          |

|    | _            |                                                                                                                                              |          |

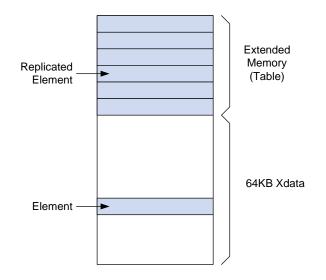

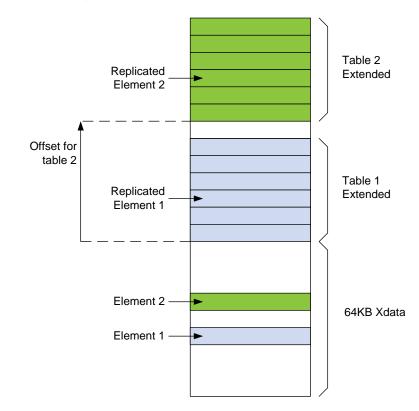

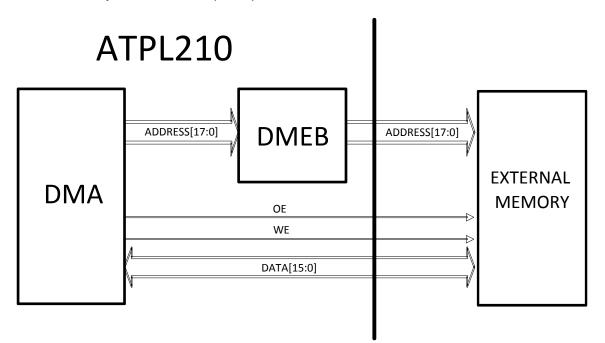

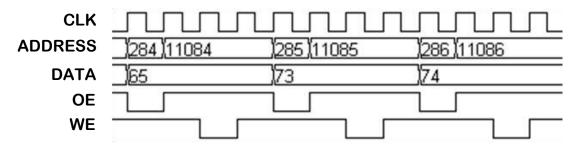

| 11 |              | a Memory Extension Block                                                                                                                     |          |

|    | 11.1         |                                                                                                                                              |          |

|    | 11.2         | DMEB Configuration Registers<br>11.2.2 TABLE_ELEMENT_SIZE registers                                                                          |          |

|    |              | 11.2.3 TABLE_INDEX registers                                                                                                                 |          |

|    |              | 11.2.4 TABLE_ELEMENT_INIT registers                                                                                                          |          |

|    | 44.0         | 11.2.5 TABLE_OFFSET registers                                                                                                                |          |

|    | 11.3         | Code Example                                                                                                                                 | 92       |

| 12 | . Direc      | ct Memory Access (DMA)                                                                                                                       | 96       |

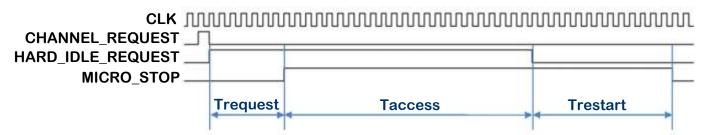

|    | 12.1         | DMA Management                                                                                                                               |          |

|    | 12.2         | DMA Hardware                                                                                                                                 |          |

|    | 12.3<br>12.4 |                                                                                                                                              |          |

|    | 12.4         | •                                                                                                                                            |          |

|    | 12.6         | DMA Flags                                                                                                                                    |          |

|    | 12.7         |                                                                                                                                              |          |

|    | 12.8         | Physical DMA channels                                                                                                                        |          |

|    | 12.9         | PHY_RX DMA channel                                                                                                                           |          |

|    |              | 0 PHY_TX DMA channel                                                                                                                         |          |

|    | 12.11        | 1 DMA Configuration Registers<br>12.11.1 PHY_SFR Register                                                                                    |          |

|    |              | 12.11.1 DMA_SFR Register                                                                                                                     |          |

|    |              | 12.11.3 PHY_TX Registers                                                                                                                     | 104      |

|    |              | 12.11.4 PHY_RX Registers                                                                                                                     |          |

|    |              | 12.11.5 ADDR_PHY_INI_RX Registers<br>12.11.6 ADDR_PHY_INI_TX Registers                                                                       |          |

|    |              |                                                                                                                                              |          |

|     |      |                  | ADDR_DMA1_SRC Registers                               |     |

|-----|------|------------------|-------------------------------------------------------|-----|

|     |      |                  | ADDR_DMA1_DTN Registers                               |     |

|     |      |                  | SIZE_DMA1_SRC Registers                               |     |

|     |      | 12.11.10         | )SIZE_DMA1_DTN Registers<br> SIZE_RQ_DMA1 Registers   | 112 |

|     |      |                  | 2DMA1_CHN_CTL Register                                |     |

|     |      |                  | ADDR_DMA2_SRC Registers                               |     |

|     |      |                  | ADDR_DMA2_DTN Registers                               |     |

|     |      |                  | SIZE_DMA2_SRC Registers                               |     |

|     |      |                  | SIZE_DMA2_DTN Registers                               |     |

|     |      |                  | SIZE_RQ_DMA2 Registers                                |     |

|     |      |                  |                                                       |     |

| 13. | ATPL | _210 M           | AC Coprocessor 1                                      | 20  |

|     | 13.2 |                  | edundancy Check (CRC)                                 |     |

|     | 13.3 |                  | ed Encryption Standard                                |     |

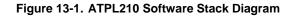

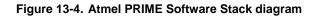

|     | 13.4 |                  | RIME Software Stack                                   |     |

|     | 13.5 | MAC Co           | processor Registers                                   | 125 |

|     |      | 13.5.1           | SNA Registers                                         | 125 |

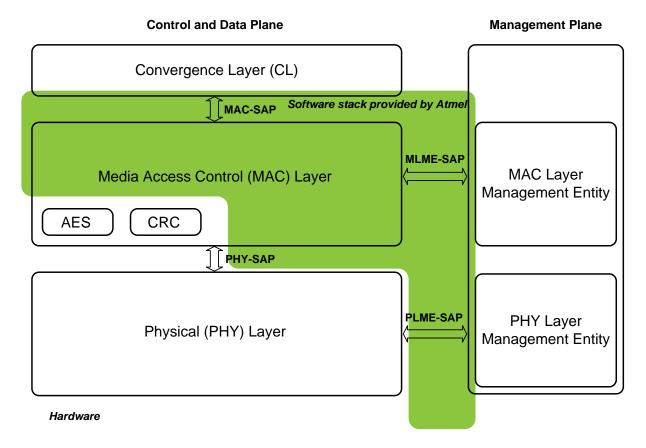

|     |      | 13.5.2           | VITERBI_BER_HARD Register                             |     |

|     |      | 13.5.3           | VITERBI_BER_SOFT Register                             |     |

|     |      | 13.5.4           | ERR_CRC32_MAC Registers                               |     |

|     |      | 13.5.5<br>13.5.6 | ERR_CRC8_MAC Registers<br>ERR_CRC8_AES Registers      |     |

|     |      | 13.5.7           | ERR_CRC8_MAC_HD Registers                             |     |

|     |      | 13.5.8           | ERR_CRC8_PHY Registers                                |     |

|     |      | 13.5.9           | FALSE_DET_CONFIG Register                             |     |

|     |      | 13.5.10          | FALSE_DET Registers                                   |     |

|     |      |                  | MAX_LEN_DBPSK Register                                |     |

|     |      | 13.5.12          | MAX_LEN_DBPSK_VTB Register                            | 136 |

|     |      |                  | MAX_LEN_DQPSK Register                                |     |

|     |      |                  | MAX_LEN_DQPSK_VTB Registers                           |     |

|     |      |                  | MAX_LEN_D8PSK Registers<br>MAX_LEN_D8PSK_VTB Register |     |

|     |      |                  | AES_PAD_LEN Register                                  |     |

|     |      |                  | AES_DATA_IN Registers                                 |     |

|     |      |                  | AES_DATA_OUT Registers                                |     |

|     |      | 13.5.20          | KEY_PERIPH Registers                                  | 144 |

|     |      |                  | KEY_PHY Registers                                     |     |

|     |      | 13.5.22          | AES_SFR Register                                      | 146 |

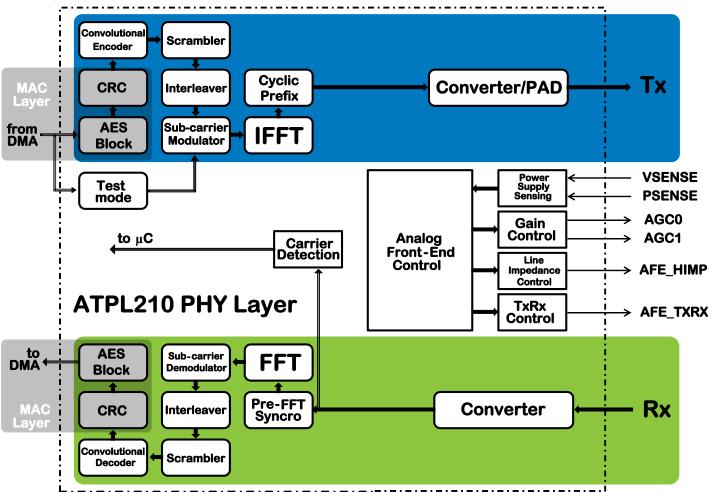

| 14. | ATPL | _210 PF          | RIME PHY Layer 1                                      | 47  |

|     |      |                  | 0 PHY Layer                                           |     |

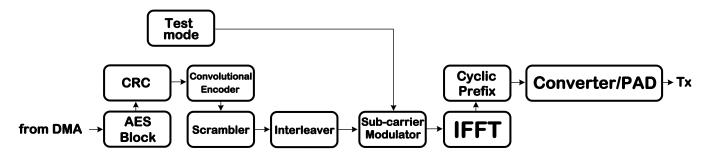

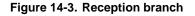

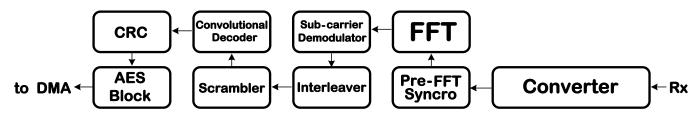

|     |      | 14.1.2           | Transmission and Reception branches                   |     |

|     |      | 14.1.3           | Carrier Detection.                                    |     |

|     |      | 14.1.4           | Analog Front End control                              | 149 |

|     |      |                  | 14.1.4.1 Power Supply Sensing: VSENSE and PSENSE      |     |

|     |      |                  | 14.1.4.2 Gain Control                                 |     |

|     |      |                  | 14.1.4.3 Line Impedance Control                       |     |

|     | 14.2 | DHV nau          | 14.1.4.4 TxRx Control                                 |     |

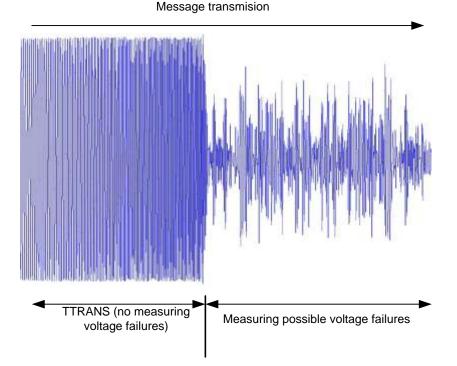

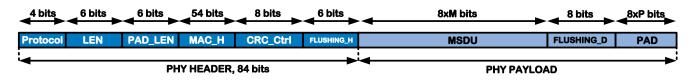

|     | 14.3 |                  | otocol Data Unit (PPDU) Format                        |     |

|     | 14.4 |                  | rvice Specification                                   |     |

|     | 14.5 |                  | /er registers                                         |     |

|     | 14.5 | 14.5.1           | PHY_SFR Register                                      |     |

|     |      | 14.5.2           | SYS_CONFIG Register                                   |     |

|     |      | 14.5.3           | PHY_CONFIG Register                                   |     |

|     |      | 14.5.4           | ATTENUATION Register                                  |     |

|     |      | 14.5.5           | ATT_CHIRP Register                                    |     |

|     |      | 14.5.6           | ATT_SIGNAL Register                                   |     |

|     |      | 14.5.7           | TX_TIME Registers.                                    |     |

|     |      | 14.5.8           | TIMER_FRAME Registers                                 | 101 |

|              | 14.5.10   | TIMER_BEACON_REF Registers  |

|--------------|-----------|-----------------------------|

|              | 14.5.12   | RSSI_AVG Register           |

|              |           | CINR_MIN Register           |

|              |           | CINR_AVG Register           |

|              |           | CINR_MAX Register           |

|              |           | EVM_HEADER Registers        |

|              |           | EVM_PAYLOAD Registers       |

|              |           | EVM_PAYLOAD_ACUM Registers  |

|              |           | RMS_CALC Register           |

|              | 14.5.22   | VSENSE_CONFIG Register      |

|              |           | NUM_FAILS Register          |

|              | 14.5.24   | TTRANS Register             |

|              |           | AGC0_KRSSI Register         |

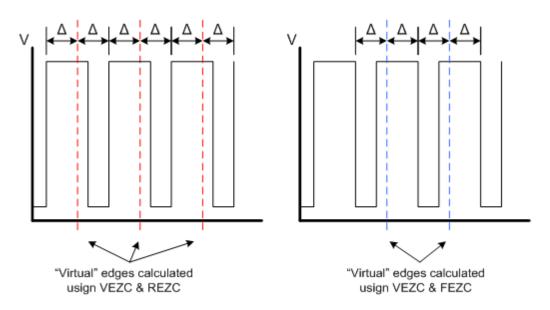

|              |           | ZERO_CROSS_TIME Registers   |

|              | 14.5.28   | ZERO_CROSS_CONFIG Register  |

|              | 14.5.29   | PSENSECYCLES Registers      |

|              |           | MEAN Registers              |

|              |           | PMAX Registers              |

|              | 14.5.32   | P_TH Registers              |

|              |           | MAXPOT Registers            |

|              |           | NUMCYCLEŠ Register          |

|              | 14.5.36   | A_NUMMILIS Register         |

|              |           | EMIT_CONFIG Register        |

|              |           | AFE_CTL Register            |

|              | 14.5.40   | PHY_ERRORS Registers        |

|              | 14.5.41   | FFT_MODE Registers 194      |

|              | 14.5.42   | AGC_CONFIG Register         |

|              | 14.5.43   | SAT_TH Registers            |

|              |           | AGC1_TH Registers           |

|              |           | AGC_PADS Register           |

| Elect        |           | aracteristics               |

| 15.1         | Absolute  | Maximum Ratings             |

| 15.2         | Recomm    | nended Operating Conditions |

| 15.3         | DC Char   | acteristics                 |

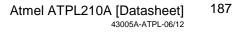

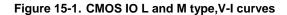

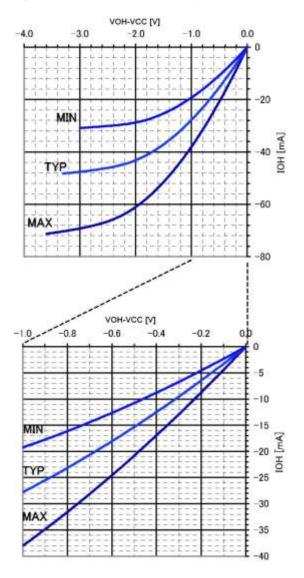

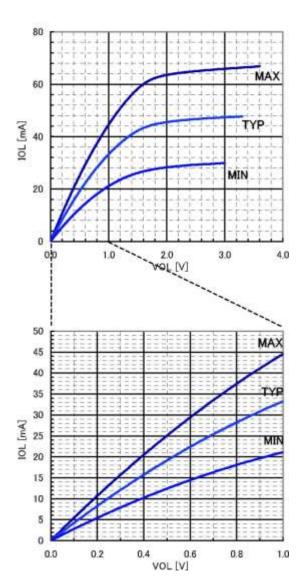

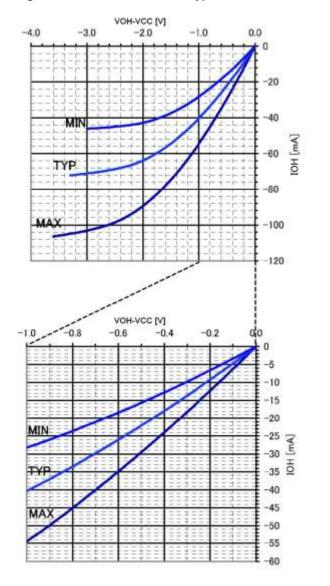

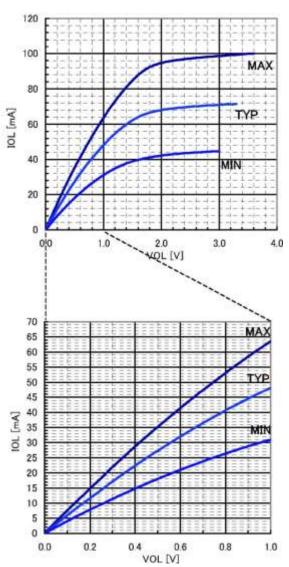

|              |           | V-I curves                  |

| 15.4         |           | onsumption                  |

| 15.5         |           | Data                        |

| 15.6<br>15.7 |           | r                           |

| 10.7         | r ower o  |                             |

| Mech         | nanical ( | Characteristics             |

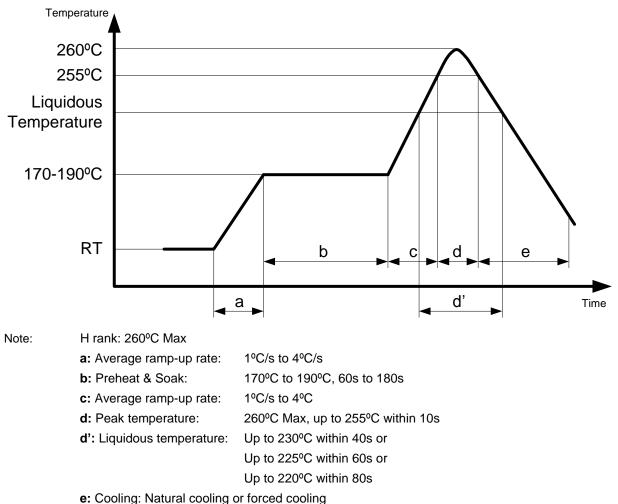

| Reco         |           | led mounting conditions 212 |

| 17.1         |           | ns of Standard Reflow212    |

| 17.2         | Manual S  | Soldering                   |

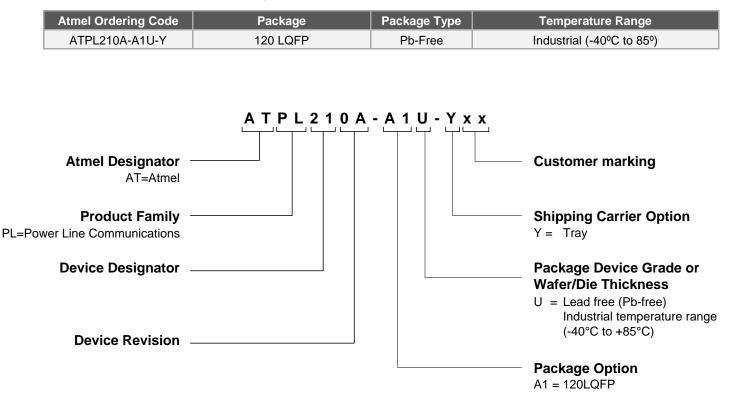

| Orde         | ring Info | prmation                    |

| Revis        | sion His  | tory 215                    |

15.

16.

17.

18.

19.

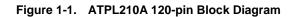

# 1. Block Diagram

# 2. Package and Pinout

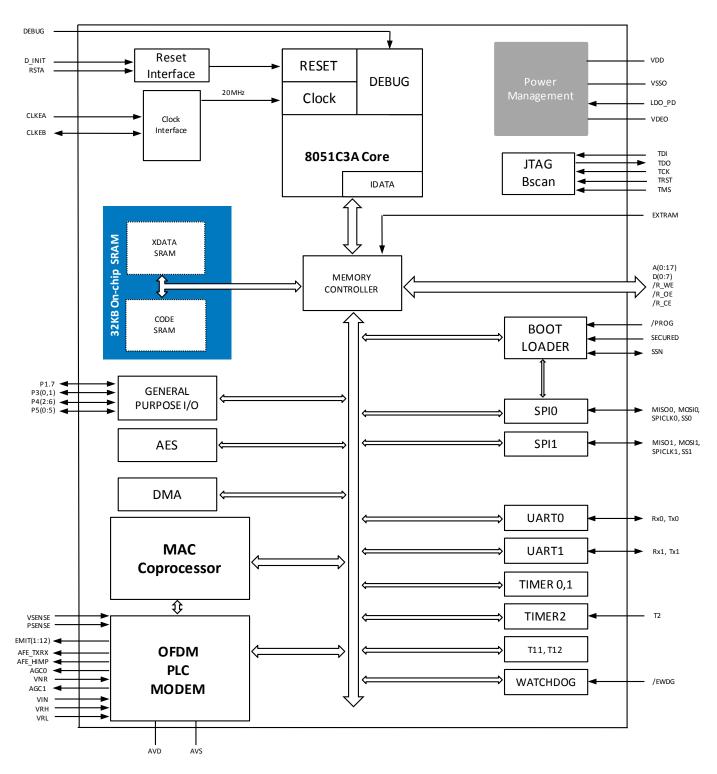

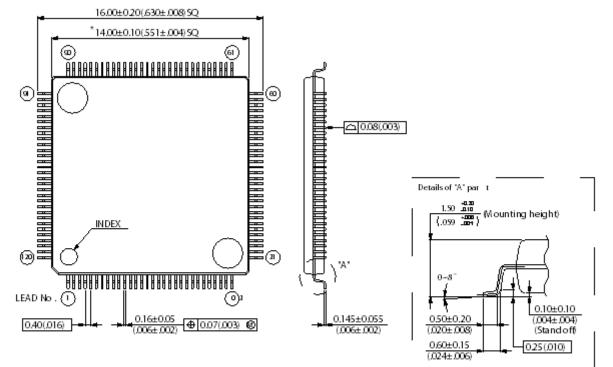

## 2.1 120-Lead LQFP Package Outline

Figure 2-1. Orientation of the 120-Lead Package

## 2.2 120-Lead LQFP Pinout

Table 2-1. ATPL210A 120-Lead LQFP pinout

| PinNo | Pin Name     | I/O     | l(mA) | Res | HY  |  |

|-------|--------------|---------|-------|-----|-----|--|

| 1     | A17          | 0       | ±2    | -   | -   |  |

| 2     | A9           | 0       | ±2    | -   | -   |  |

| 3     | GND          | Р       | -     | -   | -   |  |

| 4     | VCC          | Р       | -     | -   | -   |  |

| 5     | /R_WE        | 0       | ±2    | PU  | -   |  |

| 6     | D4           | I/O     | ±2    | -   | -   |  |

| 7     | D3           | I/O     | ±2    | -   | -   |  |

| 8     | D5           | I/O     | ±2    | -   | -   |  |

| 9     | D2           | I/O     | ±2    | -   | -   |  |

| 10    | D6           | I/O     | ±2    | -   | -   |  |

| 11    | D1           | I/O     | ±2    | -   | -   |  |

| 12    | D7           | I/O     | ±2    | -   | -   |  |

| 13    | D0           | I/O     | ±2    | _   | -   |  |

| 14    | VCC          | Р       | -     | -   | -   |  |

| 15    | GND          | Р       | -     | -   | -   |  |

| 16    | VDD          | Р       | -     |     |     |  |

| 17    | /R_OE        | _OE 0 ± |       | -   | -   |  |

| 18    | /R_CE        | 0       | ±2    | -   | -   |  |

| 19    | A8           | 0       | ±2    | 2 - |     |  |

| 20    | A0           | 0       | ±2    |     |     |  |

| 21    | A7           | 0       | ±2    |     |     |  |

| 22    | A1           | 0       | ±2    |     |     |  |

| 23    | A6           | 0       | ±2    |     |     |  |

| 24    | A2           | 0       | ±2    |     |     |  |

| 25    | A5           | 0       | ±2    | -   | -   |  |

| 26    | GND          | Р       | -     | -   | -   |  |

| 27    | VCC          | Р       | -     | -   | -   |  |

| 28    | A3           | 0       | ±2    | -   | - ] |  |

| 29    | A4           | 0       | ±2    | -   | -   |  |

| 30    | P4.5/MISO1   | I/O     | ±2    | PU  | -   |  |

| 31    | P4.4/MOSI1   | I/O     | ±2    | PU  | -   |  |

| 32    | P4.3/SPICLK1 | I/O     | ±2    | PU  | -   |  |

| 33    | P4.2/SS1     | I/O     | ±2    | PU  | -   |  |

| 34    | P3.0/RxD0    | I/O     | ±2    | PU  | -   |  |

| 35    | P3.1/TxD0    | I/O     | ±2    | PU  | -   |  |

| 36    | VCC          | Р       | -     | -   | -   |  |

| 37    | GND          | Р       | -     | -   | -   |  |

| 38    | EMIT.1       | 0       | ±Χ    | -   | -   |  |

| PinNo | Pin Name           | I/O    | l(mA)  | Res | HY |

|-------|--------------------|--------|--------|-----|----|

| 39    | EMIT.2             | 0      | ±X -   |     | -  |

| 40    | EMIT.3             | O ±X - |        | -   |    |

| 41    | EMIT.4             | 0      | ±Χ     | -   | -  |

| 42    | VCC                | Р      | -      | -   | -  |

| 43    | GND                | Р      | -      | -   | -  |

| 44    | EMIT.5             | 0      | ±Χ     | -   | -  |

| 45    | EMIT.6             | 0      | ±Χ     | -   | -  |

| 46    | EMIT.7             | 0      | ±Χ     | -   | -  |

| 47    | EMIT.8             | 0      | ±Χ     | -   | -  |

| 48    | VCC                | Р      | -      | -   | -  |

| 49    | GND                | Р      | -      | -   | -  |

| 50    | EMIT.9             | 0      | ±Χ     | -   | -  |

| 51    | EMIT.10            | 0      | ±Χ     | -   | -  |

| 52    | EMIT.11            | 0      | ±Χ     | -   | -  |

| 53    | EMIT.12            | 0      | ±Χ     | -   | -  |

| 54    | VCC                | Р      | P      |     | -  |

| 55    | 55 GND P           |        | -      | -   | -  |

| 56    | AFE_HIMP           | 0      | ±Χ     | -   | -  |

| 57    | AFE_TXRX           | 0      | ±Χ     | -   | -  |

| 58    | VSENSE             | I      | -      | -   | Y  |

| 59    | PSENSE             | I      | -      | -   | Y  |

| 60    | VNR                | I      | -      | - Y |    |

| 61    | TDI                | I      | I - PU |     | -  |

| 62    | TMS                | I      | -      | PU  | -  |

| 63    | TDO                | 0      | ±2     | -   | -  |

| 64    | GND <sup>(1)</sup> | Р      | -      | -   | -  |

| 65    | GND                | Р      | -      | -   | -  |

| 66    | VCC                | Р      | -      | -   | -  |

| 67    | TRST               | I      | -      | PU  | -  |

| 68    | тск                | I      | -      | -   |    |

| 69    | RSTA               | I      | -      | PD  | Y  |

| 70    | D_INIT             | I      | -      | PD  | Y  |

| 71    | GND                | Р      | -      | -   | -  |

| 72    | VCC                | Р      | -      | -   | -  |

| 73    | GND                | Р      | -      | -   | -  |

| 74    | VDD                | Р      | -      | -   | -  |

| 75    | LDO_PD             | I      | -      | -   | -  |

| 76    | VSS0               | Р      | -      | -   | -  |

| PinNo | Pin Name      | I/O | I(mA)    | Res | HY |

|-------|---------------|-----|----------|-----|----|

| 77    | VDE0          | 0 P |          | -   | -  |

| 78    | VDE0 P        |     | -        | -   |    |

| 79    | GND           | Р   | -        | -   | -  |

| 80    | GND           | Р   | -        | -   | -  |

| 81    | VCC           | Р   | -        | -   | -  |

| 82    | CLKEA         | Ι   | -        | -   | -  |

| 83    | GND           | Р   | -        | -   | -  |

| 84    | CLKEB         | I/O | -        | -   | -  |

| 85    | 85 VCC P -    |     | -        | -   |    |

| 86    | 86 /EWDG I -  |     | PD       | Y   |    |

| 87    | 87 DEBUG I    |     | -        | PD  | Y  |

| 88    | 88 EXTRAM I - |     | -        | Y   |    |

| 89    | /PROG I - PU  |     | PU       | Y   |    |

| 90    | SECURED       | I   | I - PD Y |     | Y  |

| 91    | P5.4/RxD1     | I/O | ±2       | PU  | -  |

| 92    | P5.5/TxD1     | I/O | ±2       | PU  | -  |

| 93    | NC            | -   | -        | -   | -  |

| 94    | P4.6/T2/AGC1  | I/O | ±Χ       | PU  | -  |

| 95    | AGC0          | 0   | ±Χ       | -   | -  |

| 96    | GND           | Р   | -        | -   | -  |

| 97    | VCC           | Р   | -        |     |    |

| 98    | AVS2          | Р   | -        | -   | -  |

| PinNo | Pin Name     | I/O | I(mA) | Res | HY |

|-------|--------------|-----|-------|-----|----|

| 99    | AVD2         | Р   | -     | -   | -  |

| 100   | AVS1         | Р   | -     | -   | -  |

| 101   | AVD1         | Р   | -     | -   | -  |

| 102   | VRH          | I   | -     | -   | -  |

| 103   | VIN          | I   | -     | -   | -  |

| 104   | VRL          | I   | -     | -   | -  |

| 105   | GND          | Р   | -     | -   | -  |

| 106   | VCC          | Р   | -     | -   | -  |

| 107   | P5.0/SS0     | I/O | ±2    | PU  | -  |

| 108   | P5.3/MISO0   | I/O | ±2    | PU  | -  |

| 109   | P5.2/MOSI0   | I/O | ±2    | PU  | -  |

| 110   | P5.1/SPICLK0 | I/O | ±2    | PU  | -  |

| 111   | P1.7/SSN     | I/O | ±2    | PU  | -  |

| 112   | A13          | 0   | ±2    | -   | -  |

| 113   | A14          | 0   | ±2    | -   | -  |

| 114   | GND          | Р   | -     | -   | -  |

| 115   | VCC          | Р   | -     | -   | -  |

| 116   | A12          | 0   | ±2    | -   | -  |

| 117   | A15          | 0   | ±2    | -   | -  |

| 118   | A11          | 0   | ±2    | -   | -  |

| 119   | A16          | 0   | ±2    | -   | -  |

| 120   | A10          | 0   | ±2    | -   | -  |

Notes: 1. Mandatory to be tied down

I/O=pin direction:I=input, O=Output, P=PowerI(mA)=nominal current:+=source, -=sink, X=fixed by external resistor

RES=pin pullup/pulldown resistor: PU=pullup, PD=pulldown,

HY=Input Hysteresis

# 3. Pin Description

### Table 3-1. Pin Description List

| Pin Number                                                                             | Pin Name | Туре   | Comments                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------------------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 19, 20, 21,<br>22, 23, 24, 25,<br>28, 29, 112,113,<br>116, 117, 118,<br>119, 120 | A(0:17)  | Output | <ul> <li>External Memory data/program Address bus.</li> <li>This bus is enabled when the system is configured to work with an external memory device (EXTRAM pin = '1'). If the system is configured to work with the on-chip SRAM configuration (EXTRAM pin = '0'), then these pins output is '0'.</li> </ul>                                                                                        |

| 3, 15, 26, 37, 43,<br>49, 55, 64, 65,<br>71, 73, 79,80, 83,<br>96, 105, 114            | GND      | Power  | Digital Ground                                                                                                                                                                                                                                                                                                                                                                                        |

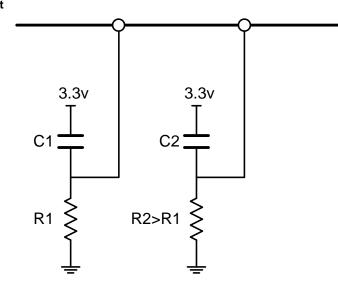

| 4, 14, 27, 36, 42,<br>48, 54, 66, 72,<br>81, 85, 97,106,<br>115                        | VCC      | Power  | 3.3v digital supply. Digital power supply must be decoupled by external capacitors                                                                                                                                                                                                                                                                                                                    |

| 5                                                                                      | /R_WE    | Output | <ul> <li>External Memory Write Enable signal.</li> <li>This output is enabled when the system is configured to work with an external memory device (EXTRAM='1'). If the system is configured to work with the on-chip SRAM configuration (EXTRAM='0'), then this output must be left unconnected.</li> <li>/R_WE is active low</li> <li>Internal configuration: 33kΩ typ. pull-up resistor</li> </ul> |

| 6, 7, 8, 9, 10, 11,<br>12, 13                                                          | D(0:7)   | I/O    | <ul> <li>External Memory Data bus.</li> <li>This bus is enabled when the system is configured to work with an external memory device (EXTRAM='1'). If the system is configured to work with the on-chip SRAM (EXTRAM='0'), then these pins are in Hi-Z.</li> </ul>                                                                                                                                    |

| 16, 74.                                                                                | VDD      | Power  | LDO Power Output. A capacitor in the range 0.1µF-10µF must be connected to each pin                                                                                                                                                                                                                                                                                                                   |

| 17                                                                                     | /R_OE    | Output | <ul> <li>External Memory Output Enable signal.</li> <li>This output is enabled when the system is configured to work with an external memory device (EXTRAM='1'). If the system is configured to work with the on-chip SRAM configuration (EXTRAM='0'), then this pin output is '1'.</li> <li>/R_OE is active low</li> </ul>                                                                          |

| 18                                                                                     | /R_CE    | Output | <ul> <li>External Memory Chip Enable signal.</li> <li>This output is enabled when the system is configured to work with an external memory device (EXTRAM='1'). If the system is configured to work with the on-chip SRAM configuration (EXTRAM='0'), then this pin output is '1'.</li> <li>/R_CE is active low</li> </ul>                                                                            |

| Pin Number                                           | Pin Name     | Туре   | Comments                                                                                                                   |

|------------------------------------------------------|--------------|--------|----------------------------------------------------------------------------------------------------------------------------|

|                                                      |              |        | Microcontroller port 4.5 / SPI1 Master In Slave Out.                                                                       |

| 30                                                   | P4.5/MISO1   | I/O    | <ul> <li>When configured as P4.5, this pin is a pseudo-<br/>bidirectional microcontroller I/O port</li> </ul>              |

| 30                                                   | F4.5/MISO1   | 1/0    | <ul> <li>When configured as MISO1, this pin is the SPI1 Master<br/>In Slave Out</li> </ul>                                 |

|                                                      |              |        | <ul> <li>Internal configuration: 33kΩ typ. pull-up resistor</li> </ul>                                                     |

|                                                      |              |        | Microcontroller port 4.4 / SPI1 Master Out Slave In                                                                        |

| 31                                                   | P4.4/MOSI1   | I/O    | <ul> <li>When configured as P4.2, this pin is a pseudo-<br/>bidirectional microcontroller I/O port</li> </ul>              |

| 51                                                   |              | 1/0    | <ul> <li>When configured as MOSI1, this pin is the SPI1 Master<br/>Out Slave In</li> </ul>                                 |

|                                                      |              |        | <ul> <li>Internal configuration: 33kΩ typ. pull-up resistor</li> </ul>                                                     |

|                                                      |              |        | Microcontroller port 4.3 / SPI1 Clock                                                                                      |

| 32                                                   | P4.3/SPICLK1 | I/O    | <ul> <li>When configured as P4.3, this pin is a pseudo-<br/>bidirectional microcontroller I/O port</li> </ul>              |

|                                                      |              |        | <ul> <li>When configured as SPICLK1, this pin is the SPI1 clock<br/>signal</li> </ul>                                      |

|                                                      |              |        | <ul> <li>Internal configuration: 33kΩ typ. pull-up resistor</li> </ul>                                                     |

|                                                      | P4.2/SS1     |        | Microcontroller port 4.2 / SPI1 Slave Select                                                                               |

| 33                                                   |              | I/O    | <ul> <li>When configured as P4.2, this pin is a pseudo-<br/>bidirectional microcontroller I/O port</li> </ul>              |

| 55                                                   |              |        | <ul> <li>When configured as SS1, this pin is the SPI1 Slave<br/>Select. Active low</li> </ul>                              |

|                                                      |              |        | <ul> <li>Internal configuration: 33kΩ typ. pull-up resistor</li> </ul>                                                     |

|                                                      |              |        | Microcontroller port 3.0 / Standard Serial Port 0 Rx                                                                       |

| 34                                                   | P3.0/RxD0    | I/O    | <ul> <li>When configured as P3.0, this pin is a pseudo-<br/>bidirectional microcontroller I/O port</li> </ul>              |

| 04                                                   | 10.0/1000    |        | <ul> <li>When configured as RxD0, this pin is the digital input of<br/>the asynchronous standard serial port 0</li> </ul>  |

|                                                      |              |        | Internal configuration: $33k\Omega$ typ. pull-up resistor                                                                  |

|                                                      |              |        | Microcontroller port 3.1 / Standard Serial Port 0 Tx                                                                       |

| 35                                                   | P3.1/TxD0    | I/O    | <ul> <li>When configured as P3.1, this pin is a pseudo-<br/>bidirectional microcontroller I/O port</li> </ul>              |

|                                                      |              |        | <ul> <li>When configured as TxD0, this pin is the digital output<br/>of the asynchronous standard serial port 0</li> </ul> |

|                                                      |              |        | Internal configuration: 33kΩ typ. pull-up resistor                                                                         |

| 38, 39, 40, 41,<br>44, 45, 46, 47,<br>50, 51, 52, 53 | EMIT(1:12)   | Output | PLC Transmission ports <sup>(1)</sup>                                                                                      |

| Pin Number | Pin Name            | Туре   | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|---------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |                     |        | Analog Front-End High-Impedance                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 56         | AFE_HIMP            | Output | • This digital output is used by the chip to select between<br>low-impedance and high-impedance transmission<br>branch (when working with a "two half-H-bridge<br>branches" analog front end configuration). This way, the<br>system adapts its transmission external circuitry to the<br>net impedance, improving transmission behavior. The<br>polarity of this pin can be inverted by hardware. Please<br>refer to the Reference Design for further information. |

|            |                     |        | Analog Front-End Transmission/Reception                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 57         | AFE_TxRx            | Output | <ul> <li>This digital output is used to select between external<br/>Transmission and Reception branches. The suitable<br/>value depends on the external circuitry configuration.<br/>The polarity of this pin can be inverted by hardware.<br/>Please refer to the Reference Design for further<br/>information.</li> </ul>                                                                                                                                         |

|            |                     |        | Voltage Level Sensing                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 58         | VSENSE              | Input  | <ul> <li>This input tracks the voltage level in the power supply to<br/>avoid power supply malfunction.</li> </ul>                                                                                                                                                                                                                                                                                                                                                  |

|            |                     |        | Power Level Sensing                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 59         | PSENSE              | Input  | <ul> <li>This input tracks the power level in the power supply to<br/>avoid power supply malfunction.</li> </ul>                                                                                                                                                                                                                                                                                                                                                    |

|            |                     |        | Zero Crossing Detection Signal                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 60         | VNR                 | Input  | <ul> <li>This input detects the zero-crossing of the mains<br/>voltage, needed to determine proper switching times.<br/>Depending on whether an isolated or a non-isolated<br/>power supply is being used, isolation of this pin should<br/>be taken into account in the circuitry design. Please<br/>refer to the Reference Design for further information.</li> </ul>                                                                                             |

| 61         | TDI <sup>(2)</sup>  | Input  | Test Data In                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|            |                     |        | <ul> <li>Internal configuration: 33kΩ typ. pull-up resistor</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                              |

| 62         | TMS <sup>(2)</sup>  | Input  | <ul> <li>Test Mode Select</li> <li>Internal configuration: 33kΩ typ. pull-up resistor</li> </ul>                                                                                                                                                                                                                                                                                                                                                                    |

| 63         | TDO <sup>(2)</sup>  | Output | Test Data out                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 67         | TRST <sup>(2)</sup> | Input  | <ul> <li>Test Reset</li> <li>Internal configuration: 33kΩ typ. pull-up resistor</li> </ul>                                                                                                                                                                                                                                                                                                                                                                          |

| 68         | TCK <sup>(2)</sup>  | Input  | Test Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|            |                     |        | Asynchronous reset                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 69         | RSTA                | Input  | <ul> <li>RSTA is a digital input pin used to perform a hardware reset of the ASIC</li> </ul>                                                                                                                                                                                                                                                                                                                                                                        |

|            |                     |        | RSTA is active high                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            |                     |        | <ul> <li>Internal configuration: 33kΩ typ. pull-down resistor</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                            |

| Pin Number | Pin Name             | Туре  | Comments                                                                                                                                                                                                                                                                                                                                                  |

|------------|----------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

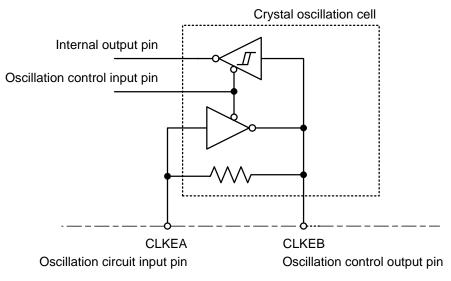

| 70         | D_INIT               | Input | <ul> <li>Initialization Signal</li> <li>During power-on, D_INIT should be released before asynchronous reset signal RSTA, in order to ensure proper system start up. Not minimum time is required between both releases, Δt&gt;0</li> <li>D_INIT is active high</li> <li>Internal configuration: 33kΩ typ. pull-down resistor</li> </ul>                  |

| 75         | LDO_PD               | Input | LDO Power-down <ul> <li>This digital input is used to put the internal linear regulator into power down mode <ul> <li>'0': Power down mode disabled</li> <li>'1': Power down mode enabled</li> </ul> </li> </ul>                                                                                                                                          |

| 76         | VSS0                 | Power | LDO ground                                                                                                                                                                                                                                                                                                                                                |

| 77, 78     | VDE0                 | Power | LDO 3.3v power supply                                                                                                                                                                                                                                                                                                                                     |

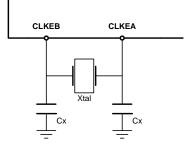

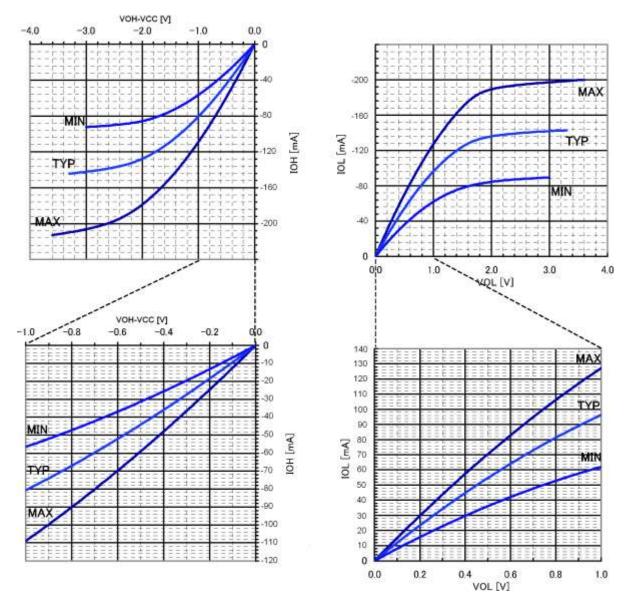

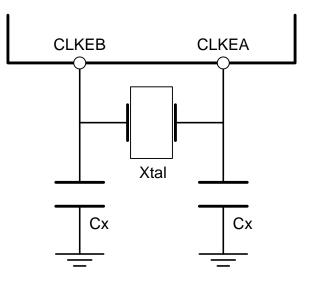

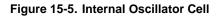

| 82         | CLKEA <sup>(3)</sup> | Input | <ul> <li>External clock reference</li> <li>CLKEA must be connected to one terminal of a crystal<br/>(when a crystal is being used) or tied to ground if a<br/>compatible oscillator is being used</li> </ul>                                                                                                                                              |

| 84         | CLKEB <sup>(3)</sup> | I/O   | <ul> <li>External clock reference</li> <li>CLKEB must be connected to one terminal of a crystal<br/>(when a crystal is being used) or to one terminal of a<br/>compatible oscillator (when a compatible oscillator is<br/>being used)</li> </ul>                                                                                                          |

| 86         | /EWDG                | Input | <ul> <li>Watchdog enable</li> <li>/EWDG digital input enables watchdog timer. This pin is internally connected to the /EW signal of the ADD8051C3A microcontroller</li> <li>'0': Watchdog timer enabled</li> <li>'1': Watchdog timer disabled</li> <li>Internal configuration: 33kΩ typ. pull-down resistor</li> </ul>                                    |

| 87         | DEBUG                | Input | <ul> <li>Debug mode enable</li> <li>DEBUG digital input is internally connected to DBG signal of the ADD8051C3A microcontroller, and it is intended to implement software debugging tools         <ul> <li>'0': Debug mode disabled</li> <li>'1': Debug mode enabled</li> <li>Internal configuration: 33kΩ typ. pull-down resistor</li> </ul> </li> </ul> |

| Pin Number | Pin Name               | Туре  | Comments                                                                                                                                                                                                                                                                                               |

|------------|------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |                        |       | SRAM device selection                                                                                                                                                                                                                                                                                  |

| 88         | EXTRAM                 | Input | <ul> <li>This digital input allows selecting between working with an external SRAM device or with the internal SRAM embedded on chip.</li> <li>'0': 32Kbytes on-chip SRAM selected.</li> <li>'1': External memory device selected. (The on-chip SRAM is not accessible when working in this</li> </ul> |

|            |                        |       | mode).                                                                                                                                                                                                                                                                                                 |

|            |                        |       | SPI Flash programming pin                                                                                                                                                                                                                                                                              |

| 89         | /PROG                  | Input | <ul> <li>/PROG digital input is read during power up and sets<br/>the system into "execution" mode or "serial flash<br/>programming" mode</li> </ul>                                                                                                                                                   |

|            |                        |       | '0': Serial flash programming mode                                                                                                                                                                                                                                                                     |

|            |                        |       | '1': Execution mode (normal mode)                                                                                                                                                                                                                                                                      |

|            |                        |       | <ul> <li>Internal configuration: 33kΩ typ. pull-up resistor</li> </ul>                                                                                                                                                                                                                                 |

|            |                        | Input | Encryption enable                                                                                                                                                                                                                                                                                      |

| 90         | SECURED <sup>(4)</sup> |       | <ul> <li>SECURED digital input enables encrypted firmware<br/>storage and execution when the board configuration<br/>supports it</li> </ul>                                                                                                                                                            |

|            |                        |       | <ul> <li>'0': Encrypted storage/execution disabled</li> </ul>                                                                                                                                                                                                                                          |

|            |                        |       | <ul> <li>'1': Encrypted storage/execution enabled</li> </ul>                                                                                                                                                                                                                                           |

|            |                        |       | <ul> <li>Internal configuration: 33kΩ typ. pull-down resistor</li> </ul>                                                                                                                                                                                                                               |

|            |                        |       | Microcontroller port 5.4 / Standard Serial Port 1 Rx                                                                                                                                                                                                                                                   |

| 91         | P5.4/RxD1              | 1/0   | <ul> <li>When configured as P5.4, this pin is a pseudo-<br/>bidirectional microcontroller I/O port</li> </ul>                                                                                                                                                                                          |

| 91         | F3.4/KXD1              | 1/0   | <ul> <li>When configured as RxD1, this pin is the digital input of<br/>the asynchronous standard serial port 1</li> </ul>                                                                                                                                                                              |

|            |                        |       | <ul> <li>Internal configuration: 33kΩ typ. pull-up resistor</li> </ul>                                                                                                                                                                                                                                 |

|            |                        |       | Microcontroller port 5.5 / Standard Serial Port 1 Tx                                                                                                                                                                                                                                                   |

| 02         |                        |       | <ul> <li>When configured as P5.5, this pin is a pseudo-<br/>bidirectional microcontroller I/O port</li> </ul>                                                                                                                                                                                          |

| 92         | P5.5/TxD1              | I/O   | <ul> <li>When configured as TxD1, this pin is the digital output<br/>of the asynchronous standard serial port 1</li> </ul>                                                                                                                                                                             |

|            |                        |       | <ul> <li>Internal configuration: 33kΩ typ. pull-up resistor</li> </ul>                                                                                                                                                                                                                                 |

| 93         | NC                     |       | No connect                                                                                                                                                                                                                                                                                             |

| Pin Number | Pin Name           | Туре   | Comments                                                                                                                                                         |  |  |  |

|------------|--------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|            |                    |        | Microcontroller port 4.6/T2/AGC1                                                                                                                                 |  |  |  |

|            |                    |        | <ul> <li>When configured as P4.6, this pin is a pseudo-<br/>bidirectional microcontroller I/O port</li> </ul>                                                    |  |  |  |

| 94         | P4.6/T2/AGC1       | I/O    | <ul> <li>When configured as T2, this pin works as the external<br/>T2 pin described in Timer2 section</li> </ul>                                                 |  |  |  |

|            |                    |        | <ul> <li>When configured as AGC1, this pin is managed by AGC<br/>hardware logic to drive external circuitry if input signal<br/>attenuation is needed</li> </ul> |  |  |  |

|            |                    |        | <ul> <li>Internal configuration: 33kΩ typ. pull-up resistor</li> </ul>                                                                                           |  |  |  |

|            |                    |        | Automatic Gain Control 0                                                                                                                                         |  |  |  |

| 95         | AGC0               | Output | <ul> <li>This digital output is managed by AGC hardware logic<br/>to drive external circuitry if input signal attenuation is<br/>needed</li> </ul>               |  |  |  |

| 98, 100    | AVS1, AVS2         | Power  | Analog ground                                                                                                                                                    |  |  |  |

| 99, 101    | AVD1, AVD2         | Power  | 3.3v analog power                                                                                                                                                |  |  |  |

| 102        | VRH <sup>(5)</sup> | Input  | Analog input high voltage reference                                                                                                                              |  |  |  |

| 103        | VIN <sup>(5)</sup> | Input  | Direct-analog input voltage                                                                                                                                      |  |  |  |

| 104        | VRL <sup>(5)</sup> | Input  | Analog input low voltage reference                                                                                                                               |  |  |  |

|            |                    |        | Microcontroller port 5.0 / SPI0 Slave Select                                                                                                                     |  |  |  |

| 107        | P5.0/SS0           | I/O    | <ul> <li>When configured as P5.0, this pin is a pseudo-<br/>bidirectional microcontroller I/O port</li> </ul>                                                    |  |  |  |

| 107        | F3.0/330           | 1/0    | <ul> <li>When configured as SS0, this pin is the SPI0 Slave<br/>Select. Active low</li> </ul>                                                                    |  |  |  |

|            |                    |        | <ul> <li>Internal configuration: 33kΩ typ. pull-up resistor</li> </ul>                                                                                           |  |  |  |

|            |                    |        | Microcontroller port 5.3 / SPI0 Master In Slave Out                                                                                                              |  |  |  |

| 108        | P5.3/MISO0         | I/O    | <ul> <li>When configured as P5.3, this pin is a pseudo-<br/>bidirectional microcontroller I/O port</li> </ul>                                                    |  |  |  |

| 100        | 1 3.3/101000       | 1/0    | <ul> <li>When configured as MISO0, this pin is the SPI0 Master<br/>In Slave Out</li> </ul>                                                                       |  |  |  |

|            |                    |        | <ul> <li>Internal configuration: 33kΩ typ. pull-up resistor</li> </ul>                                                                                           |  |  |  |

|            |                    |        | Microcontroller port 5.2 / SPI0 Master Out Slave In                                                                                                              |  |  |  |

| 109        | P5.2/MOSI0         | I/O    | <ul> <li>When configured as P5.2, this pin is a pseudo-<br/>bidirectional microcontroller I/O port</li> </ul>                                                    |  |  |  |

| 109        | F 3.2/100010       | 1/0    | <ul> <li>When configured as MOSI0, this pin is the SPI0 Master<br/>Out Slave In</li> </ul>                                                                       |  |  |  |

|            |                    |        | <ul> <li>Internal configuration: 33kΩ typ. pull-up resistor</li> </ul>                                                                                           |  |  |  |

| Pin Number | Pin Name     | Туре | Comments                                                                                                                                                                                                                                                                                                                                                               |

|------------|--------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |              |      | Microcontroller port 5.1 / SPI0 Clock                                                                                                                                                                                                                                                                                                                                  |

| 110        | P5.1/SPICLK0 | 1/0  | <ul> <li>When configured as 5.1, this pin is a pseudo-<br/>bidirectional microcontroller I/O port</li> </ul>                                                                                                                                                                                                                                                           |

| 110        | F3.1/SFICERU |      | <ul> <li>When configured as SPICLK0, this pin is the SPI0 clock<br/>signal</li> </ul>                                                                                                                                                                                                                                                                                  |

|            |              |      | <ul> <li>Internal configuration: 33kΩ typ. pull-up resistor</li> </ul>                                                                                                                                                                                                                                                                                                 |

|            |              |      | Microcontroller port 1.7 / Silicon Serial Number                                                                                                                                                                                                                                                                                                                       |

|            |              | I/O  | <ul> <li>When configured as P1.7, this pin is a pseudo-<br/>bidirectional microcontroller I/O port</li> </ul>                                                                                                                                                                                                                                                          |

| 111        | P1.7/SSN     |      | <ul> <li>This pin is the digital input used to read a Serial number<br/>if a valid SSN device is being used. This Serial Number<br/>is used for encryption purposes. Precaution should be<br/>taken if used as generic control port since it searches<br/>for a Silicon Serial Number device at start-up and could<br/>put out undesirable transient values</li> </ul> |

|            |              |      | <ul> <li>Internal configuration: 33kΩ typ. pull-up resistor</li> </ul>                                                                                                                                                                                                                                                                                                 |

Notes: 1. Different configurations allowed depending on external topology and net behavior

- 2. This pin is part of the JTAG Boundary Scan interface and is only used for boundary scan purposes

- 3. The crystal should be located as close as possible to CLKEA and CLKEB pins. Recommended value for Cx is 18pF. This value may depend on the specific crystal characteristics

- 4. See supported devices section 10.4.3

- 5. See Reference Design for suitable values

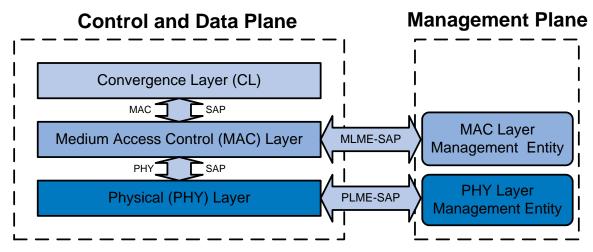

## 4. **PRIME overview**

The PRIME (PoweRline Intelligent Metering Evolution) initiative was originally conceived as an answer to the need for a future-proof, cost-effective Automatic Meter Management (AMM) solution. During its evolution in the last two years, it has evolved into a solution for an entire Smart Grid environment which will contribute definitively to energy efficiency improvement and ultimately to addressing the pressing issue of climate change.

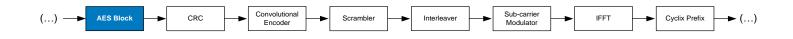

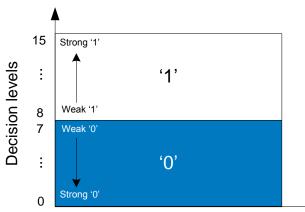

The overall performance of the system fully complies with requirements for a new, stable metering infrastructure that is set to become a fundamental part of the Smart Grids. The revolutionary openness of the PRIME solution and its focus on interoperability as a way to decrease costs in a competitive framework, has been arising an unprecedented level of interest within the industry and markets. For this very reason a decision was taken by several of the most committed parties to set up the PRIME Alliance.