# **Atmel AT86RF215 Device Family**

Sub-1GHz/2.4GHz Transceiver and I/Q Radio for IEEE Std 802.15.4<sup>™</sup>-2015 IEEE Std 802.15.4g<sup>™</sup>-2012 ETSI TS 102 887-1

# AT86RF215 / AT86RF215IQ / AT86RF215M

# **DATASHEET**

#### Features AT86RF215

Fully integrated radio transceiver covering 389.5-510MHz / 779-1020MHz / 2400-2483.5MHz including:

European band: 863-870MHz / 870-876MHz / 915-921MHz

Chinese band: 470-510MHz / 779-787MHz

North American band: 902-928MHz

Korean band: 917-923.5MHz

Japanese band: 920-928MHz

World-wide ISM band: 2400-2483,5MHz

- I/Q data interface:

- One TX and two RX serial low voltage differential signal (LVDS) interfaces

- 13-bit I/Q data interface with a sampling frequency of up to 4MHz

- Transceiver Control interface: SPI (serial peripheral interface)

- Supported PHYs (\*proprietary)

- MR-FSK

- Symbol rates: 50, 100, 150, 200, 300\*, 400ksymbol/s

- Rate 1/2-FEC: RSC and NRNSC, with and without interleaving

- Order: 2-level, 4-level

- MR-OFDM

- Option 1: 100, 200, 400, 800, 1200\*, 1600\*, 2400\*kb/s

- Option 2: 50, 100, 200, 400, 600, 800, 1200\*kb/s

- Option 3: 50, 100, 200, 300, 400, 600kb/s

- Option 4: 50, 100, 150, 200, 300kb/s

- MR-O-QPSK

- 100kchip/s with 6.25, 12.5, 25, 50kb/s data rate

- 200kchip/s with 12.5, 25\*, 50\*, 100\*kb/s data rate

- 1000kchip/s with 31.25, 125, 250, 500kb/s data rate

- 2000kchip/s with 31.25, 125, 250, 500, 1000\*kb/s data rate

- O-QPSK

- 1000kchip/s with 250kb/s and 500\*kb/s data rate

- 2000kchip/s with 250kb/s and 1000\*kb/s data rate

- Bi-directional differential RF signal ports for:

- Band I: 433/470/780/863/868/915/917/920MHz

- Band II: 2450MHz

- Simultaneous operation of sub-1GHz and 2.4GHz transceiver

- Separate 2kbytes RX and TX frame buffer

- IEEE MAC support

- Frame filter (IEEE Std 802.15.4-2006)

- FCS handling

- Automatic acknowledgement (IEEE Std 802.15.4-2006)

- CCA with automatic transmit

- Industry leading link budget

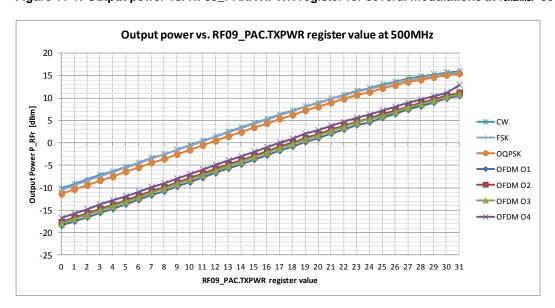

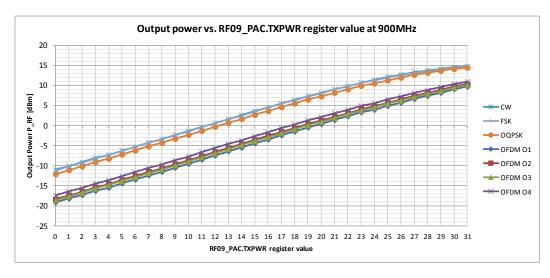

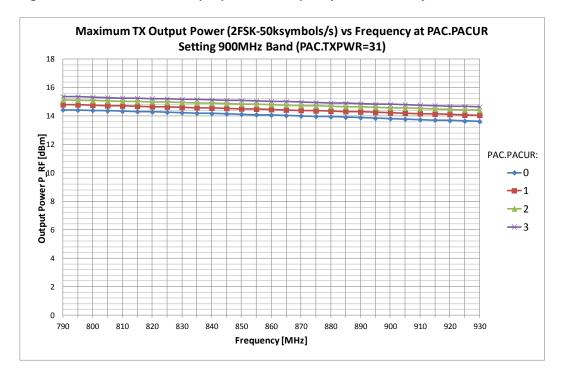

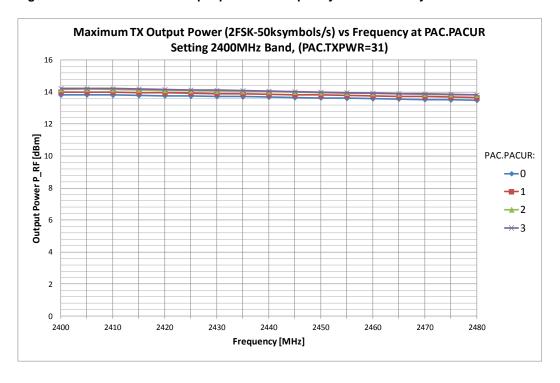

- Programmable TX output power up to +14.5dBm@900MHz band

- Noise figure below 5dB for sub-1GHz and 2.4GHz transceiver

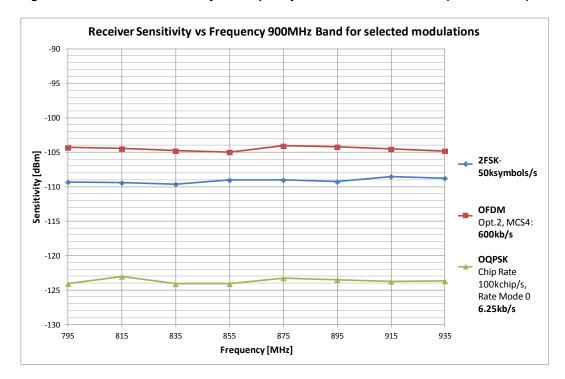

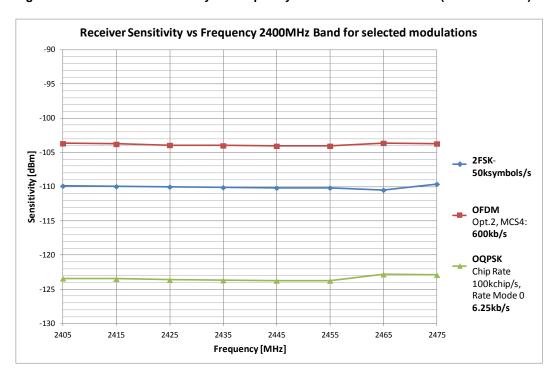

- Receiver sensitivity down to -123dBm at 6.25kb/s MR-O-QPSK

- Radio transceiver features

- Integrated TX/RX switch, LNA, PLL loop filter and RF frontend control

- Fast settling PLL supporting frequency hopping

- Automatic filter calibration

- Received signal strength indicator / energy detection

- True random number generator

- Optimized for low BOM cost and ease of production

- Low power supply voltage from 1.8V to 3.6V

- Internal voltage regulators and battery monitor

- Reduced power consumption (RPC) modes for MR-FSK and MR-OQPSK

- Low current consumption (incl. baseband processing / without I/Q interface)

Deep sleep 30nA

RX listen

6..28mA (RPC mode dependent)

RX active 28mA

TX 62mA @14dBm output power

- Industrial temperature range from –40°C to +85°C

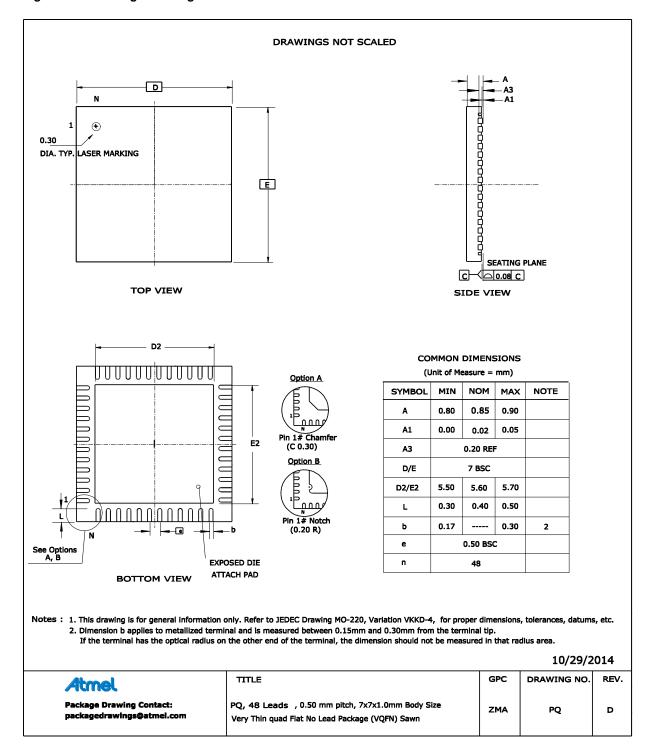

- 48-pin low-profile lead-free plastic QFN package

# 1. Description

The AT86RF215 is a multi-band radio transceiver for various sub-1GHz bands and the 2.4GHz band specially designed for smart metering and applications implementing IEEE Std 802.15.4g<sup>™</sup>-2012 [3], ETSI TS 102 887-1 [5], IEEE Std 802.15.4<sup>™</sup>-2015 [7].

The device is comprised of two independent transceivers, each with its own baseband and I/Q data interface. The AT86RF215 incorporates two transceivers and two baseband cores forming two independent radio systems. The transceivers are highly integrated minimizing the number of external components required on the printed circuit board (PCB). The supply voltage ranges from 1.8V to 3.6V. A 26MHz temperature controlled oscillator (TCXO) or a crystal oscillator (XTAL) is used as a reference clock.

The AT86RF215 allows simultaneous independent reception in the sub-1GHz and 2.4GHz bands. Each radio frequency (RF) port is accessed with balanced differential signal pairs. Optimal sensitivity and output power are achieved with  $50\Omega$  differential load. The device offers a high link budget with maximum TX output power of 14.5 dBm@900MHz and sensitivity down to -123 dBm@MR-OQPSK-6.25kb/s.

The device is controlled via a fast serial peripheral interface (SPI). Dedicated MAC hardware, random number generator and on-board battery monitoring improve overall system efficiency and timing.

The AT86RF215 can be operated with an external microcontroller (e.g. Atmel SAM4 Family) and/or an external baseband processor.

# 1.1 Device Family

#### 1.1.1 Overview

Table 1-1. Device Family Overview

| Device      | Description                                                                                                                                                                                                                                                                                               |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AT86RF215   | <ul> <li>Dual band transceiver and I/Q radio</li> <li>Embedded baseband supporting MR-FSK, MR-OFDM, MR-O-QPSK, and O-QPSK</li> <li>Compliant to IEEE Std 802.15.4g<sup>™</sup>-2012 [3]; IEEE Std 802.15.4<sup>™</sup>-2011 [2]; ETSI TS 102 887-1 [5], IEEE Std 802.15.4<sup>™</sup>-2015 [7]</li> </ul> |

| AT86RF215IQ | I/Q radio (13-bit I/Q low voltage differential signal (LVDS) interface)                                                                                                                                                                                                                                   |

| AT86RF215M  | <ul> <li>Sub-1GHz Transceiver and I/Q radio</li> <li>Embedded baseband supporting MR-FSK, MR-OFDM, MR-O-QPSK, and O-QPSK</li> <li>Compliant to IEEE Std 802.15.4g™-2012 [3]; ETSI TS 102 887-1 [5]</li> </ul>                                                                                             |

Note: For operation of the AT86RF215M see "Basic Operation of AT86RF215M" on page 42.

#### 1.1.2 Device Identification

The device identifier can be read from the register RF\_PN. The version number of the device can be read from the register RF\_VN.

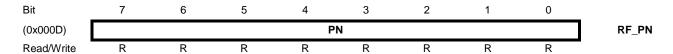

#### 1.1.3 Register Description

#### 1.1.3.1 RF PN - Device Part Number

The register contains the part number of the device.

# • Bit 7:0 - RF\_PN.PN: Device Part Number

The register contains the part number of the device.

Table 1-2. PN

| Sub-register | Value | Description |

|--------------|-------|-------------|

| PN           | 0x34  | AT86RF215   |

| 0x           | 0x35  | AT86RF215IQ |

|              | 0x36  | AT86RF215M  |

## 1.1.3.2 RF\_VN - Device Version Number

The register contains the version number of the device.

| Bit               | 7 | 6 | 5 | 4 | 3  | 2 | 1 | 0 | _     |

|-------------------|---|---|---|---|----|---|---|---|-------|

| (0x000E)          |   |   |   | ٧ | 'N |   |   |   | RF_VN |

| Read/Write        | R | R | R | R | R  | R | R | R |       |

| Initial Value v.1 | 0 | 0 | 0 | 0 | 0  | 0 | 0 | 1 |       |

| Initial Value v.3 | 0 | 0 | 0 | 0 | 0  | 0 | 1 | 1 |       |

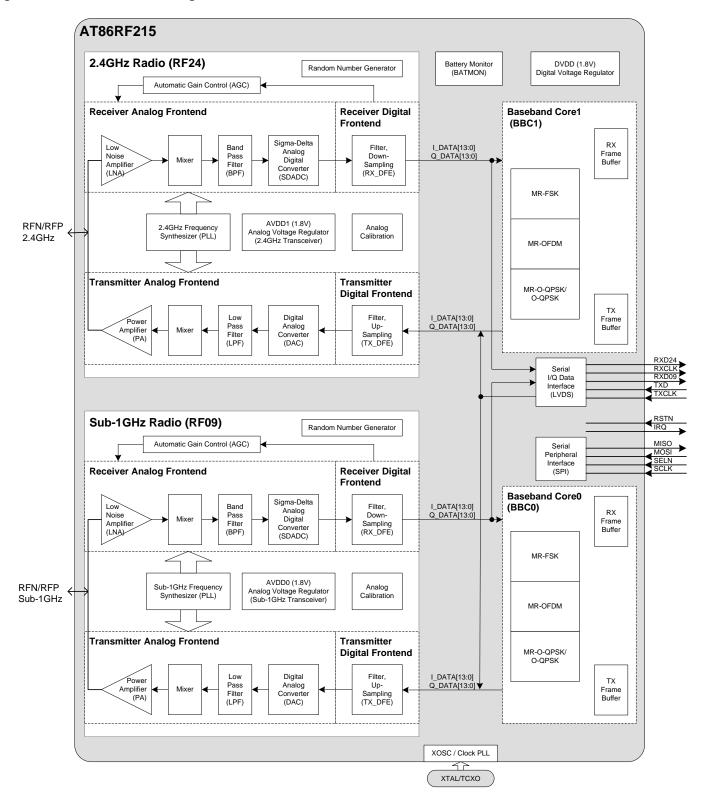

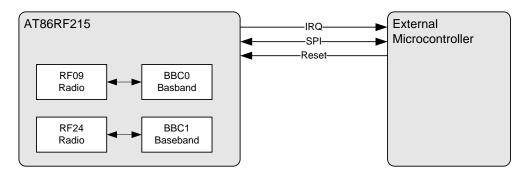

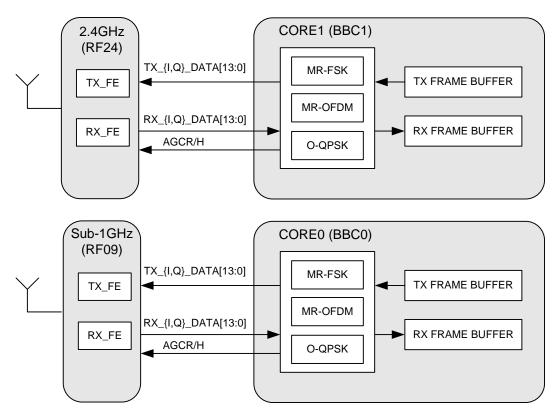

# 1.2 Block Diagram

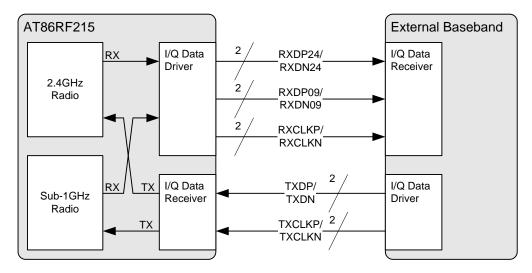

The device features two independent radio systems. It contains one sub-1GHz transceiver and one 2.4GHz transceiver. Each transceiver is paired with a baseband core optimized to demodulate signals commonly used in the associated band, thus providing complete RF-to-Baseband operation. The internal baseband cores support MR-FSK, O-QPSK/MR-O-QPSK and MR-OFDM modulation schemes. Alternatively users can route the I/Q data stream directly to an external processor for advanced signal processing using the 13-bit LVDS interface.

The AT86RF215 block diagram is shown in Figure 1-1.

Figure 1-1. AT86RF215 Block Diagram

Notes: 1. Baseband Core0/1 are not available at AT86RF215IQ

2. 2.4GHz Radio (RF24) and Baseband Core1 (BBC1) are not available at AT86RF215M

# 1.3 Control Logic and Naming Conventions

Both radio and baseband cores have separate register blocks. The sub-1GHz radio register names are prefixed by "RF09\_". The 2.4GHz radio transceiver register names are prefixed by "RF24\_". The register descriptions, including sub-register descriptions, for both radios and their respective basebands are identical. In rare cases where a register is only valid for one specific radio (or baseband), the register for the other radio (or baseband) is ignored.

The baseband processor Core0 is connected to the sub-1GHz radio and Core1 is connected to the 2.4GHz radio.

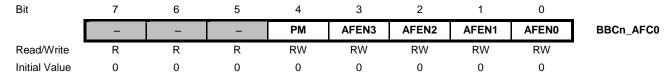

The baseband registers of Core0 are prefixed by "BBC0\_". The baseband register of Core1 are prefixed by "BBC1\_". The general reference for both core registers is prefixed by "BBCn\_". Both cores are identical and have separate register spaces.

Common registers of the AT86RF215 which are not specific for the radio or baseband are prefixed by "RF\_".

Note, the datasheet refers to the naming convention of IEEE Std 802.15.4g<sup>™</sup>-2012 [3] in regards to multi rate and multi regional frequency (MR) PHYs. The IEEE Std 802.15.4<sup>™</sup>-2015 [7] names the PHYs SUN, i.e. smart metering utility network.

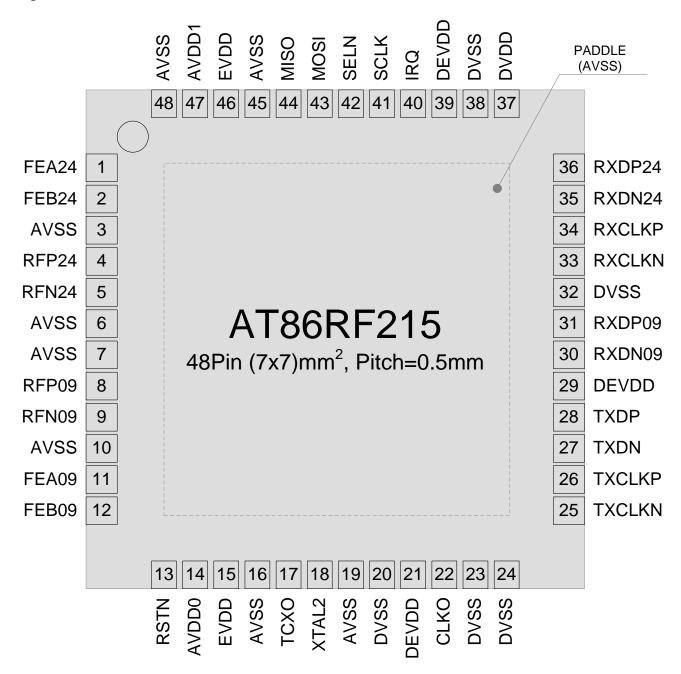

# 2. Pin-out Diagram and Description

# 2.1 Pin-out Diagram

The pin-out of the AT86RF215 is shown in Figure 2-1.

Figure 2-1. Pin-out

Table 2-1. Pin Description

| # Pin | Name   | Туре   | Description                                                                                                                  |

|-------|--------|--------|------------------------------------------------------------------------------------------------------------------------------|

| 1     | FEA24  | Output | RF frontend control; digital output for the 2.4GHz transceiver                                                               |

| 2     | FEB24  | Output | RF frontend control; digital output for the 2.4GHz transceiver                                                               |

| 3     | AVSS   | In/Out | Analog ground (RF)                                                                                                           |

| 4     | RFP24  | In/Out | Differential RF input/output 2.4GHz (positive)                                                                               |

| 5     | RFN24  | In/Out | Differential RF input/output 2.4GHz (negative)                                                                               |

| 6     | AVSS   | In/Out | Analog ground (RF)                                                                                                           |

| 7     | AVSS   | In/Out | Analog ground (RF)                                                                                                           |

| 8     | RFP09  | In/Out | Differential RF input/output for sub-1GHz transceiver (positive)                                                             |

| 9     | RFN09  | In/Out | Differential RF input/output for sub-1GHz transceiver (negative)                                                             |

| 10    | AVSS   | In/Out | Analog ground (RF)                                                                                                           |

| 11    | FEA09  | Output | RF frontend control; digital output for the sub-1GHz transceiver                                                             |

| 12    | FEB09  | Output | RF frontend control; digital output for the sub-1GHz transceiver                                                             |

| 13    | RSTN   | Input  | Reset input (active low)                                                                                                     |

| 14    | AVDD0  | In/Out | Internal regulated analog 1.8V supply output voltage (internally generated) for analog circuitry of the sub-1GHz transceiver |

| 15    | EVDD   | Input  | External analog supply voltage (VDD); 3.0V typical                                                                           |

| 16    | AVSS   | In/out | Analog ground                                                                                                                |

| 17    | TCXO   | Input  | TCXO or crystal oscillator (26MHz) input                                                                                     |

| 18    | XTAL2  | Output | Crystal oscillator                                                                                                           |

| 19    | AVSS   | In/Out | Analog ground                                                                                                                |

| 20    | DVSS   | In/Out | Digital ground                                                                                                               |

| 21    | DEVDD  | Input  | External digital supply voltage (V <sub>DD</sub> ); 3.0V typical                                                             |

| 22    | CLKO   | Output | Clock output                                                                                                                 |

| 23    | DVSS   | In/Out | Digital ground                                                                                                               |

| 24    | DVSS   | In/Out | Digital ground                                                                                                               |

| 25    | TXCLKN | Input  | Differential TX I/Q clock interface input (negative)                                                                         |

| 26    | TXCLKP | Input  | Differential TX I/Q clock interface input (positive)                                                                         |

| 27    | TXDN   | Input  | Differential TX I/Q data interface input (negative)                                                                          |

| 28    | TXDP   | Input  | Differential TX I/Q data interface input (positive)                                                                          |

| 29    | DEVDD  | Input  | External digital supply voltage (V <sub>DD</sub> ); 3.0V typical                                                             |

| 30    | RXDN09 | Output | Differential RX I/Q data interface output sub-1GHz transceiver (negative)                                                    |

| 31    | RXDP09 | Output | Differential RX I/Q data interface output sub-1GHz transceiver (positive)                                                    |

| 32    | DVSS   | In/Out | Digital ground                                                                                                               |

| 33    | RXCLKN | Output | Differential RX I/Q clock interface output (negative)                                                                        |

| 34    | RXCLKP | Output | Differential RX I/Q clock interface output (positive)                                                                        |

| 35    | RXDN24 | Output | Differential RX I/Q data interface output 2.4GHz transceiver (negative)                                                      |

| 36    | RXDP24 | Output | Differential RX I/Q data interface output 2.4GHz transceiver (positive)                                                      |

| 37    | DVDD   | In/Out | Internal regulated supply output voltage (internally generated) for digital circuitry                                        |

| 38    | DVSS   | In/Out | Digital ground                                                                                                               |

| # Pin | Name  | Туре   | Description                                                                                                                 |

|-------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------|

| 39    | DEVDD | Output | External digital supply voltage (V <sub>DD</sub> ); 3.0V typical                                                            |

| 40    | IRQ   | Output | Interrupt output                                                                                                            |

| 41    | SCLK  | Input  | SPI interface clock input                                                                                                   |

| 42    | SELN  | Input  | SPI select input (active low)                                                                                               |

| 43    | MOSI  | Input  | SPI data input                                                                                                              |

| 44    | MISO  | Output | SPI data output                                                                                                             |

| 45    | AVSS  | In/Out | Analog ground                                                                                                               |

| 46    | EVDD  | Input  | External analog supply voltage (VDD); 3.0V typical                                                                          |

| 47    | AVDD1 | In/Out | Internal regulated analog 1.8V supply output voltage (internally generated) for analog circuitry for the 2.4GHz transceiver |

| 48    | AVSS  | In/Out | Analog ground                                                                                                               |

# 2.2 Pin Description

### 2.2.1 RFP09/RFN09, RFP24/RFN24

The differential RF pins (RFP09/RFN09; RFP24/RFN24) provide common-mode rejection to suppress the switching noise of the internal and external digital signal processing blocks.

A  $50\Omega$  differential load at the RF ports ensures high sensitivity and output power. A DC path between the RF pins is supported; a DC path to ground or supply voltage is not supported. When connecting an RF load providing a DC path to the power supply or ground, AC coupling is required.

The pins RFP24/RFN24 of AT86RF215M are shortened to AVSS internally and may not be connected.

## 2.2.2 EVDD, DEVDD (V<sub>DD</sub>)

EVDD is the external analog supply voltage. DEVDD is the external digital supply voltage. External decoupling capacitors must be placed close to these device pins. EVDD and DEVDD must be shorted at board level and should always have the same potential.

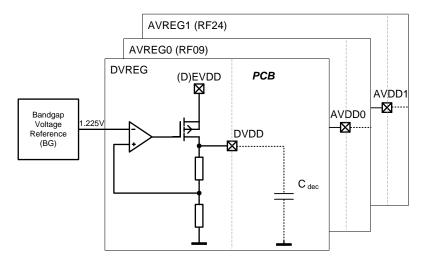

### 2.2.3 AVDD0, AVDD1

AVDD0 and AVDD1 are internally generated/regulated analog supply voltages. External compensation capacitors must be placed close to these device pins. These supplies are activated, and de-activated, by the sleep-mode logic. Do not use these signals as references or power supplies. AVDD0 and AVDD1 must not be shorted. For further information about the analog supply voltages are described in section "Voltage Regulator" on page 75.

An external compensation capacitor at the pin AVDD1 is not required for AT86RF215M, the pin can have no connections.

## 2.2.4 **DVDD**

DVDD is an internally generated/regulated digital supply voltage. An external compensation capacitor must be placed close to this device pin. For further information about the digital supply voltage are described in section "Voltage Regulator" on page 75.

## 2.2.5 AVSS, DVSS

AVSS is the analog ground; DVSS is the digital ground voltage. The analog and the digital grounds should be separated on the PCB and only connected at a single point on the PCB.

## 2.2.6 MISO, MOSI, SCLK, SELN

Pins MISO, MOSI, SCLK and SELN are SPI specific pins which provide register read/write access for device operation. For further information about the control interface see section "SPI Transceiver Control Interface" on page 16.

#### 2.2.7 RXDN09/RXDP09, RXDN24/RXDP24, RXCLKP/RXCLKN, TXDP/TXDN, TXCLKP/TXCLKN

Pins RXDN09/RXDP09, RXDN24/RXDP24, RXCLKP/RXCLKN, TXDP/TXDN and TXCLKP/TXCLKN are low voltage differential signal (LVDS) I/Q data interface pins. For further information see section "Serial I/Q Data Interface" on page 22.

The pins RXDN24/RXDP24 are not supported for AT86RF215M, the pins shall have no connections.

#### 2.2.8 IRQ

Pin IRQ is the interrupt pin from the transceiver to the microcontroller and is controlled by both radios and basebands. The interrupt source can be detected by reading the interrupt status registers using the device control interface (SPI). For further information about IRQ configuration see section "Interrupt Signalling" on page 19.

#### 2.2.9 RSTN

Pin RSTN is the active low reset pin. For further information see section "Reset Modes" on page 13.

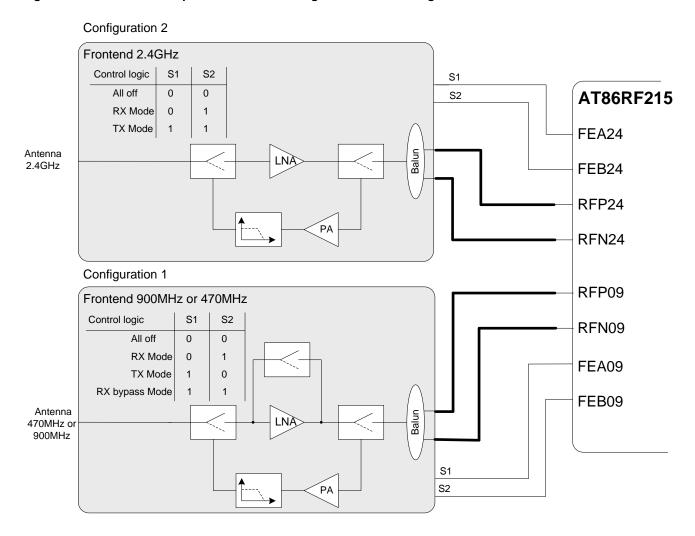

#### 2.2.10 FEA09/FEB09, FEA24/FEB24

The digital output pins FEAnn and FEBnn can control an external RF analog frontend device, in general external LNA, PA. For each transceiver band two frontend control pins are specified. The pins are not differential. For further information see section "External Frontend Control" on page 70.

The pins FEA24/FEB24 are not supported for AT86RF215M, the pins shall have no connections.

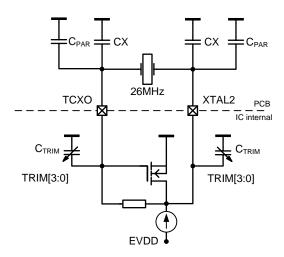

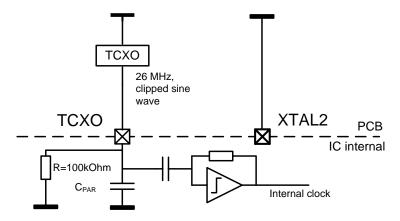

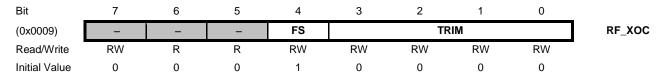

#### 2.2.11 TCXO/XTAL2

Pin TCXO (Temperature Controlled Crystal Oscillator) is the input pin of a 26MHz clock from a TCXO device. Pin XTAL2 must be grounded if operating the device with a TCXO.

Alternatively, the device can be operated with a 26MHz Crystal (XTAL) which must be connected between pin TCXO and pin XTAL2. For further information see section "Crystal Oscillator and TCXO" on page 67.

#### 2.2.12 CLKO

Pin CLKO provides a clock output signal. An external microcontroller can use this clock signal as an input clock source. For further information about the clock output configuration see "Clock Output" on page 20.

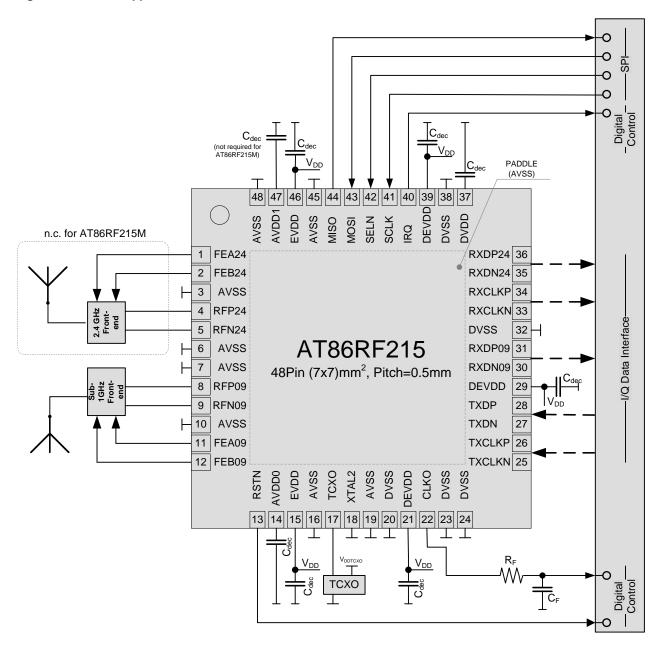

# 3. Application Schematic

A basic application schematic of the AT86RF215 is shown in Figure 3-1. The RF ports require a  $50\Omega$  differential load for best RF performance. The transceiver is operated with a 26MHz TCXO.

Figure 3-1. Basic Application Schematic

The external analog power supply EVDD, the external digital power supply DEVDD and the integrated voltage regulators outputs AVDD0, DVDD and AVDD1 must be decoupled by a capacitor (C<sub>dec</sub>). All decoupling capacitors should be placed as close as possible to the pins and should have low-resistance and low-inductance connection to ground. EVDD and DEVDD must be shorted at PCB level and should always have the same potential (V<sub>DD</sub>).

A low-pass filter  $(C_F, R_F)$  should be placed close to pin CLKO to reduce the emission of CLKO signal harmonics. This is not needed if pin CLKO is not used as a microcontroller clock source. In this case, clock output signal should be disabled during device initialization, see register RF\_CLKO.

The pins RFP24/RFN24 of the AT86RF215M are connected to AVSS and must not be connected. The pins RXDP24/RXDN24 are not supported for the AT86RF215M and can be left opened.

# 4. Control and Data Interfaces

## 4.1 Reset Modes

## 4.1.1 Summary Reset Modes

The AT86RF215 can be reset by the following conditions:

- Power-on reset or voltage drop, see section "Power-on Reset" below

- Chip Reset command, see section "Chip Reset" on page 14

- Chip Reset via pulse at pin RSTN, see section "Chip Reset" on page 14

- Transceiver Reset, see section "Transceiver Reset" on page 14

- State SLEEP, see section "State SLEEP" on page 34

- State DEEP\_SLEEP, see section "State DEEP\_SLEEP and Wake-up Procedure" on page 34

The AT86RF215 registers can be classified into register groups for common chip functionality, for the I/Q data interface, for the sub-1GHz transceiver and for the 2.4GHz transceiver. Table 4-1 shows which register groups are reset by which reset source.

Table 4-1. AT86RF215 Reset Modes

| Reset Source               | Common Chip<br>Register                       | I/Q Data Interface<br>Register | Sub-1GHz<br>Transceiver<br>Register | 2.4GHz<br>Transceiver<br>Register |

|----------------------------|-----------------------------------------------|--------------------------------|-------------------------------------|-----------------------------------|

|                            | RF_CFG,<br>RF_XOC,<br>RF_CLKO and<br>RF_BMDVC | RF_IQIFC0 and<br>RF_IQIFC1     | RF09_* and<br>BBC0_*                | RF24_* and<br>BBC1_*              |

| Power-On Reset             | reset                                         | reset                          | reset                               | reset                             |

| Chip Reset                 | reset                                         | reset                          | reset                               | reset                             |

| Sub-1GHz Transceiver Reset |                                               |                                | reset                               |                                   |

| 2.4GHz Transceiver Reset   |                                               |                                |                                     | reset                             |

| Sub-1GHz Transceiver SLEEP |                                               |                                | reset                               |                                   |

| 2.4GHz Transceiver SLEEP   |                                               |                                |                                     | reset                             |

| DEEP_SLEEP                 |                                               | reset                          | reset                               | reset                             |

#### 4.1.2 Power-on Reset

A power-on reset is initiated if the supply voltage drops below the operating range of the voltage regulator (see section "Voltage Regulator" on page 75) and returns back to the supported range again. For further information about the operation range see section "Operating Range" on page 187.

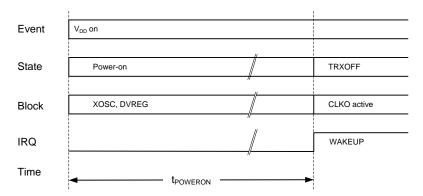

The power-on procedure is shown in Figure 4-1.

Figure 4-1. Power-on Procedure

When the external supply voltage (VDD) is initially supplied to the AT86RF215, the device enables the crystal oscillator (XOSC) and the internal 1.8V voltage regulator for the digital domain (DVREG). After the output clock signal is available at pin CLKO at default clock rate of 26MHz. During the power-on procedure, all registers are set to their default values. As soon as the state TRXOFF is reached, the SPI is enabled and it can be used to control the device. At the same time, the interrupt IRQS.WAKEUP at both transceivers is set to 1 and the pin IRQ is asserted high.

## 4.1.3 Chip Reset

The Chip Reset procedure resets the entire device (i.e. both radios, sub-1GHz and 2.4GHz and both baseband cores), all registers are set to their default values.

The Chip Reset is triggered by the pin RSTN or by writing the Chip Reset command. The Chip Reset is triggered by pulling the pin RSTN to low, keeping it low for t<sub>RST</sub> and to release it to high again; for further timing information see section "Power-on Reset Characteristics" on page 188. To trigger the Chip Reset via the Chip Reset command, the value 0x07 needs to be written to the sub-register RF\_RST.CMD.

After initiating the Chip Reset procedure, the device enters the internal state RESET. After the reset procedure is completed, the state RESET is left and the state TRXOFF is reached. The completion of the reset procedure is indicated by the interrupt IRQS.WAKEUP for both transceivers.

For further information about state changes see section "State Machine" on page 33.

#### 4.1.4 Transceiver Reset

While the Chip Reset procedure resets the entire device (sub-1GHz/BBC0 and 2.4GHz/BBC1), the Transceiver Reset is used to reset only a single transceiver (RF09/BBC0 or RF24/BBC1). The Transceiver Reset is initiated by writing the command RESET to the register RFn\_CMD of the corresponding transceiver. During the reset procedure the corresponding transceiver state machine is reset and the corresponding transceiver (RFn\_\*) and baseband registers (BBCn\_\*) are set to their default values. The common device registers (RF\_\*) are not reset.

Once the reset procedure is completed, the state TRXOFF is reached and the interrupt IRQS.WAKEUP is issued for the corresponding transceiver.

#### 4.1.5 Register Description

#### 4.1.5.1 RF\_RST - Chip Reset

The register RF\_RST allows resetting the entire device via an SPI command.

| Bit           | 7 | 6 | 5 | 4 | 3 | 2  | 1   | 0  | _      |

|---------------|---|---|---|---|---|----|-----|----|--------|

| (0x0005)      | - | - | - | - | _ |    | CMD |    | RF_RST |

| Read/Write    | R | R | R | R | R | RW | RW  | RW | •      |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0  | 0   | 0  |        |

# • Bit 2:0 - RF\_RST.CMD: Chip Reset Command

Writing the value 0x7 to the sub-register CMD triggers the reset procedure of the entire device; the values 0x0 to 0x6 have no effect.

Table 4-2. CMD

| Sub-register | Name     | Value | Description |

|--------------|----------|-------|-------------|

| CMD          | RF_RESET | 0x7   | CHIP RESET  |

## 4.2 SPI Transceiver Control Interface

#### 4.2.1 Introduction

The control interface comprises an SPI slave and provides access to registers and frame buffers of the AT86RF215. Table 4-3 shows the SPI signals.

Table 4-3. SPI Signals

| SPI Signal | Direction | Description                                |

|------------|-----------|--------------------------------------------|

| SCLK       | Input     | SPI clock signal                           |

| SELN       | Input     | SPI select signal, active low              |

| MOSI       | Input     | SPI data master output, slave input signal |

| MISO       | Output    | SPI data master input, slave output signal |

The SPI is byte-oriented with bi-directional communication between master and slave. Each byte is transferred with the MSB first. The SPI select signal SELN is active low. The number of clocks at SCLK must be a multiple of eight. The AT86RF215 SPI provides register and frame buffer access in a linear address space. The access mode is configured by the address in the COMMAND bytes.

#### 4.2.2 SPI Protocol

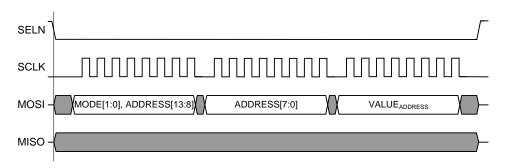

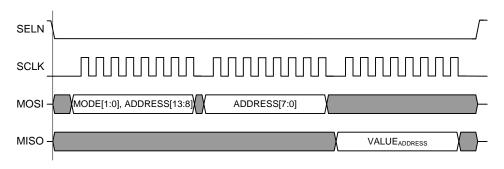

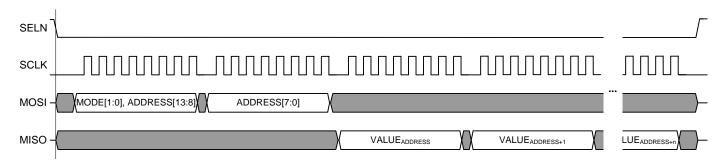

Each SPI sequence starts by setting SELN to low and finishes by releasing SELN to high. After setting SELN to low, the two COMMAND bytes are transferred from the SPI master via pin MOSI followed by SPI clock signals to read or to write data. The two COMMAND bytes define the SPI access mode (read or write access) and the 14-bit address (see Table 4-4).

Table 4-4. SPI COMMAND Definition

| Bit[15]<br>MODE[1] | Bit[14]<br>MODE[0] | Bit[13:8]<br>ADDRESS[13:8] | Bit[7:0]<br>ADDRESS[7:0] | SPI Access Mode |

|--------------------|--------------------|----------------------------|--------------------------|-----------------|

| COMMAND[1          | 5:8]               |                            | COMMAND[7:0]             |                 |

| 0                  | 0                  | ADDRESS[13:8]              | ADDRESS[7:0]             | Read            |

| 1                  | 0                  | ADDRESS[13:8]              | ADDRESS[7:0]             | Write           |

| 0                  | 1                  | ADDRESS[13:8]              | ADDRESS[7:0]             | Reserved        |

| 1                  | 1                  | ADDRESS[13:8]              | ADDRESS[7:0]             | Reserved        |

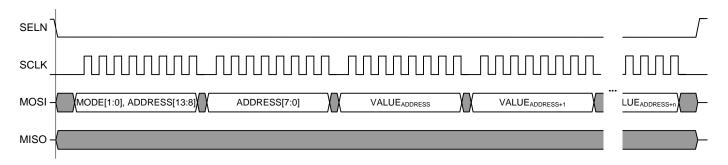

The SPI can be operated in single or block access mode. The single access mode (see section 4.2.4) is used to read or to write a single register value. The block access mode (see section 4.2.4) is used to read or to write a block of data with a variable number of data bytes.

#### 4.2.3 Single Access Mode

The single access mode is a three byte operation. First the two COMMAND bytes are transferred on MOSI. If MODE indicates a write access, then the third byte contains the value that is written to the selected address (see Figure 4-2). If MODE indicates a read access, then the content of the selected address is returned with the third byte on pin MISO (see Figure 4-3).

Figure 4-2. SPI Single Write Access

Figure 4-3. SPI Single Read Access

#### 4.2.4 Block Access Mode

The block access mode is entered when SELN remains low after the third byte of the single access mode. During block write access the fourth byte on MOSI is written to the next address (ADDRESS+1) and so on. The same procedure applies to the block read access, where the content of the next address (ADDRESS+1) is returned with the fourth byte on pin MISO. The block mode can access the whole address space (see Figure 4-4 and Figure 4-5).

Figure 4-4. SPI Block Write Access

Figure 4-5. SPI Block Read Access

# 4.2.5 SPI Timing

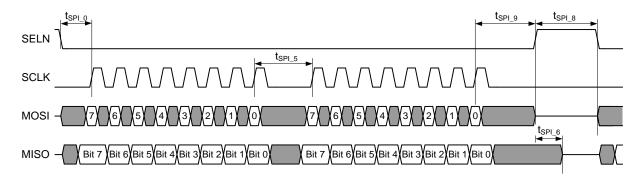

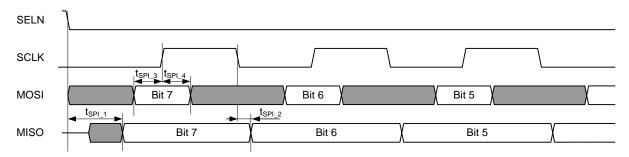

Figure 4-6 and Figure 4-7 illustrate the SPI timing and its parameters. The corresponding timing parameter values t<sub>SPI\_0</sub> - t<sub>SPI\_9</sub> are defined in section "SPI Timing Characteristics" on page 204.

Figure 4-6. SPI Timing, Definition of Timing Parameters tspl\_0, tspl\_6, tspl\_6, tspl\_8, tspl\_9.

Figure 4-7. SPI Timing, Definition of Timing Parameters tspl\_1 to tspl\_4.

SELN low enables the MISO output driver of the AT86RF215. The MSB of values transferred via MISO is valid after t<sub>SPl\_1</sub> and is updated at each falling edge of SCLK. If the MISO driver is disabled (during inactive SPI periods), no internal pull-up circuitry is connected to it. Driving the appropriate signal level must be ensured by the master device or an external pull-up resistor.

Referring to Figure 4-6 and Figure 4-7, the AT86RF215 MOSI is sampled at the rising edge of the SCLK signal. The signal MOSI must be stable before and after the rising edge of SCLK as specified by tspl\_3 and tspl\_4. The output (MISO) is initiated at the falling edge of SCLK.

The SPI command is processed at the last rising clock edge of SCLK.

# 4.3 Interrupt Signalling

The radios and the basebands of the AT86RF215 generate interrupt events. All enabled interrupt events are logically OR'd to form the single external interrupt signal at pin IRQ.

The IRQ behavior and the pad driver strength can be configured by the register RF\_CFG. The register RF\_CFG content is maintained during state DEEP\_SLEEP and is cleared during RESET.

The active polarity of pin IRQ can be configured by sub-register RF\_CFG.IRQP. After a reset procedure the polarity is set to active high.

For further information see section "Interrupts" on page 38.

## 4.3.1 Register Description

#### 4.3.1.1 RF\_CFG - IRQ Configuration

The register RF\_CFG contains bits to configure the IRQ behavior.

| Bit           | 7 | 6 | 5 | 4 | 3     | 2    | 1  | 0  | _      |

|---------------|---|---|---|---|-------|------|----|----|--------|

| (0x0006)      | - | - | - | - | IRQMM | IRQP | D  | RV | RF_CFG |

| Read/Write    | R | R | R | R | RW    | RW   | RW | RW | _      |

| Initial Value | 0 | 0 | 0 | 0 | 1     | 0    | 0  | 1  |        |

#### Bit 3 – RF\_CFG.IRQMM: IRQ Mask Mode

The bit IRQMM configures the IRQ mask mode.

Table 4-5. IRQMM

| Sub-register | Value      | Description                                       |

|--------------|------------|---------------------------------------------------|

| IRQMM        | 0x0        | Masked IRQ reasons do not appear in IRQS register |

|              | <u>0x1</u> | Masked IRQ reasons do appear in IRQS register     |

#### Bit 2 – RF\_CFG.IRQP: IRQ Polarity

The bit IRQP configures the IRQ pin polarity.

Table 4-6. IRQP

| Sub-register | Value      | Description |

|--------------|------------|-------------|

| IRQP         | <u>0x0</u> | Active high |

|              | 0x1        | Active low  |

## • Bit 1:0 - RF\_CFG.DRV: Output Driver Strength of Pads

The bits DRV configure the pads driver strength of the pins IRQ, MISO, and the frontend control (i.e. FEA09, FEB09, FEA24, FEB24) pins.

Table 4-7. DRV

| Sub-register | Name    | Value      | Description |

|--------------|---------|------------|-------------|

| DRV          | RF_DRV2 | 0x0        | 2mA         |

|              | RF_DRV4 | <u>0x1</u> | 4mA         |

|              | RF_DRV6 | 0x2        | 6mA         |

|              | RF_DRV8 | 0x3        | 8mA         |

# 4.4 Clock Output

The AT86RF215 provides a clock output signal at pin CLKO.

The clock output signal is generated by the oscillator module using the external crystal or TCXO; see section "Crystal Oscillator and TCXO" on page 67 for further information about the oscillator configuration.

After reset or power-on the clock output signal is enabled and set to the default clock rate value of 26MHz. The signal's driver strength and the clock frequency can be configured by register RF\_CLKO.

Resetting AT86RF215 via Chip Reset causes the register RF CLKO to be reset to its default value.

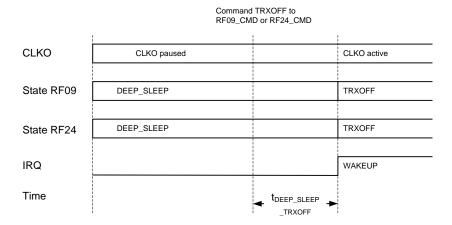

In state DEEP\_SLEEP the clock output signal is paused. If the device is woken up by writing command TRXOFF to one of the transceiver command registers, the clock output signal continues after t<sub>DEEP\_SLEEP\_TRXOFF</sub> with the configuration that has been set before entering state DEEP\_SLEEP.

If the clock output signal is not used, it is recommended to switch it off. The output signal can be switched off by the sub-register RF\_CLKO.OS.

For electrical parameter of the clock output signal see section "Clock Output – pin CLKO" on page 189 and "General Transceiver Specifications" on page 188.

# 4.4.1 Register Description

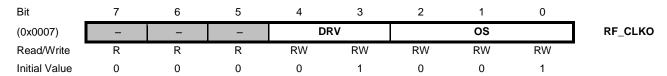

#### 4.4.1.1 RF\_CLKO - Clock Output

The register RF\_CLKO contains configuration bits for the clock output signal. The register setting is maintained during state DEEP\_SLEEP.

#### Bit 4:3 – RF\_CLKO.DRV: Output Driver Strength CLKO

The bit DRV configures the CLKO pad driver strength.

Table 4-8. DRV

| Sub-register | Name        | Value      | Description |

|--------------|-------------|------------|-------------|

| DRV          | RF_DRVCLKO2 | 0x0        | 2mA         |

|              | RF_DRVCLKO4 | <u>0x1</u> | 4mA         |

|              | RF_DRVCLKO6 | 0x2        | 6mA         |

|              | RF_DRVCLKO8 | 0x3        | 8mA         |

#### Bit 2:0 – RF\_CLKO.OS: Clock Output Selection

The bit OS configures the clock output frequency of the CLKO output signal. The change of the clock output frequency occurs immediately and spike free.

20

# Table 4-9. OS

| Sub-register | Value      | Description |

|--------------|------------|-------------|

| os           | 0x0        | OFF         |

|              | <u>0x1</u> | 26MHz       |

|              | 0x2        | 32MHz       |

|              | 0x3        | 16MHz       |

|              | 0x4        | 8MHz        |

|              | 0x5        | 4MHz        |

|              | 0x6        | 2MHz        |

|              | 0x7        | 1MHz        |

### 4.5 Serial I/Q Data Interface

#### 4.5.1 Introduction

A point-to-point, low voltage differential signalling (LVDS) interface is used for the data transfer between the AT86RF215 and an external baseband processor. The implemented interface is based on the IEEE standard 1596.3-1996 (see [4]). The specific interface of the AT86RF215 has a data rate of 128Mb/s composed of 16 data bits at 4MHz for each of the I and Q data streams from the device. The LVDS clock frequency is 64MHz. The interface uses double data rate (DDR). A new data bit is received and transmitted at both the falling and rising edge of the LVDS clock.

In order to decrease current consumption, a proprietary scalable LVDS (SLVDS) interface is implemented in addition to the IEEE standard functionality.

The AT86RF215 data interface consists of two receive and one transmit signal paths. The interface signals are all implemented as differential pairs. Two receive pairs and one clock pair form the LVDS driver. One transmit pair and one clock pair form the LVDS receiver. Within this document the terminologies of I/Q data *driver* and *receiver* are used with reference to the external baseband processor, see Figure 4-8.

Figure 4-8. I/Q Data Interface

The TXCLK must have the same frequency as the RXCLK signal. There is no requirement on the phase alignment. The RXCLK driver is also enabled while transmitting data, so that the external baseband can derive the TXCLK from the RXCLK, see Table 10-34 on page 206 and Table 10-35 on page 207 for the required phase relation between clock and data.

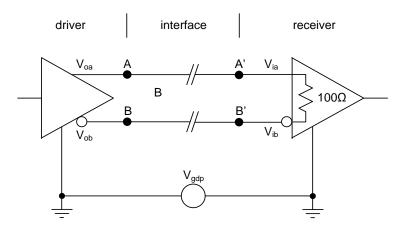

The driver and receiver should be on the same printed circuit board (PCB) and have a small ground potential  $V_{gdb}$  (see Figure 4-9 on page 23) difference. The length of the PCB wires between the devices is expected to be short and their differential impedance should be  $100\Omega$ .

Figure 4-9. I/Q Data Interface Structure (Refer to [4])

#### 4.5.2 Configuration

The proprietary SLVDS link has a low voltage swing of 200mV with a common mode offset voltage of 200mV. The differential lines must be terminated with a  $100\Omega$  differential impedance. This termination is included in the I/Q data receiver of the AT86RF215. Voltage swing and offset can be adjusted with sub-registers IQIFC0.DRV and IQIFC0.CMV. Note that a higher voltage swing also increases the current consumption.

The I/Q data interface can also be operated with a common mode voltage of 1.2V. In this way the AT86RF215 can communicate with common LVDS interfaces compliant to the IEEE standard 1596.3-1996 [4]. The higher common mode voltage is selected if bit IQIFC0.CMV1V2 is set to 1. If it is set to 1, the sub-register IQIFC0.CMV has no function.

The I/Q data interface receivers operate over a wide input common mode range. They have a differential input hysteresis and a fail safe circuit. The hysteresis avoids amplifying small signal noise at zero input voltages. Input voltages can be zero when receiver inputs are open or the connected drivers are powered down. The hysteresis means that an input signal must change by more than Vhyst (see Table 10-32 on page 206) to toggle the receiver output. If no driver circuit is connected to the inputs, the fail safe circuit sets the sub-register IQIFC1.FAILSF to 1 and the internal pull-ups force the open inputs to DEVDD.

Refer to chapter "Electrical Characteristics" on page 187 for a complete list of all DC and AC characteristics of the LVDS interface.

#### 4.5.3 Characteristics and Timing

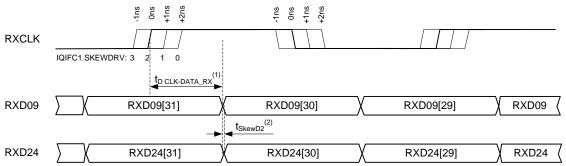

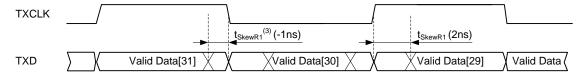

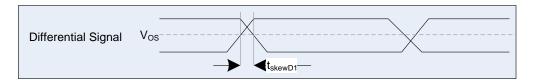

Double data rate is implemented to clock the data using both negative and positive clock edges. The data sent by the AT86RF215 (transceiver state RX) is center aligned. The data received from an external baseband processor (transceiver TX) must be edge aligned. Uneven data bits are related to the rising clock edge. Even data bits are related to the falling clock edge (see Figure 4-10 on page 24).

The skew between RX clock and data can be adjusted to match the timing requirement of the LVDS input of an external baseband processor. The skew alignment parameter is set by the sub-register IQIFC1.SKEWDRV. Figure 4-10 shows the functionality of the skew alignment. The skew settings must only be altered when the LVDS interface is off (for example in state TRXOFF).

Figure 4-10. Clock to Data Timing Alignment

# RX Link - I/Q Driver (AT86RF215 OUTPUT)

#### TX Link - I/Q Receiver (AT86RF215 INPUT)

Notes:

- 1. Programmable clock to data delay at the I/Q data interface driver (for details refer to register IQIFC1.SKEWDRV on page 28 and section "I/Q Data Interface Driver AC Specification" on page 206)

- LVDS data channel to LVDS data channel skew (see section "I/Q Data Interface Driver AC Specification" on page 206)

- 3. Skew tolerable at receiver input to meet setup and hold time requirements (see section "I/Q Data Interface Receiver AC Specification" on page 207)

The data sampling rate f<sub>s</sub> ranges from 400ksample/s to 4Msample/s and is defined by the registers RFn\_TXDFE and RFn\_RXDFE. The interface transfers the I/Q data in 32-bit data words with a fixed rate of 4Mword/s. This results in a fixed rate of 128Mb/s with a double data rate clock frequency of 64MHz at the interface.

An IDLE period must be inserted between each 32-bit data word if a lower sampling rate f<sub>s</sub> is used. During the IDLE period zero words are transmitted. A zero word consists of 32 zero bits.

The interface must be DC coupled, because the bit stream is not DC balanced.

#### 4.5.4 Word Format

The I/Q data interface is based on serializing/de-serializing a 32-bit word. The 32-bit word is composed of a two bit I synchronization pattern followed by a 14-bit I data word and a two bit Q synchronization pattern followed by a 14-bit Q data word (see Table 4-10 below).

Table 4-10. I/Q Data Interface Word Frame Format

| Bit[31:30]    | Bit[29:16]   | Bit[15:14]    | Bit[13:0]    |

|---------------|--------------|---------------|--------------|

| I_SYNC = 0b10 | I_DATA[13:0] | Q_SYNC = 0b01 | Q_DATA[13:0] |

The actual baseband signal data is contained in sub-fields I\_DATA[13:1] and Q\_DATA[13:1], each interpreted as 13-bit 2's complement signed values with  $\{I,Q\}_DATA[13]$  being the sign bit and  $\{I,Q\}_DATA[1]$  being the least significant bit.

For the transmit I/Q data (pin TXD) TX control information can be embedded in the bit I\_DATA[0]. In this case, embedded TX control must be enabled in the register IQIFC0.EEC and the bit Q\_DATA[0] must be zero. If embedded TX control is not enabled, the bits {I,Q}\_DATA[0] are not interpreted.

For the receive I/Q data (pin RXD09/24) the bits {I,Q}\_DATA[0] are not used and always equal to 0.

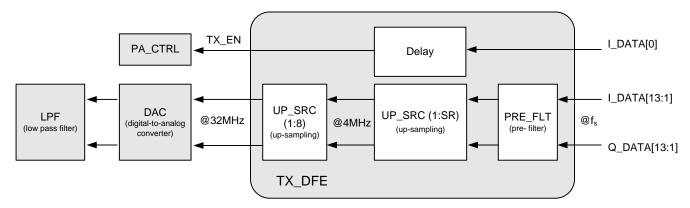

For details on the I/Q data processing refer to section "Transmitter Digital Frontend" on page 43 and "Receiver Digital Frontend" on page 53. Embedded TX control is described in section "Transmit Control" on page 46.

### 4.5.5 Sample Rate

The sample rate (SR) of the I/Q data stream at TXD must be the same as the transmit sample rate configured in register TXDFE.SR. A number of m = TXDFE.SR-1 zero words must be inserted between the data carrying 32-bit words (refer to Figure 4-11 below).

The sample rate of the I/Q data stream at RXD09 and RXD24 is the same as the receive sample rate configured in register RXDFE.SR. Zero words are inserted in the same format as for the TXD stream.

Sample Rate 32Bit 4Msample/s Data 32Bit 32Bit Zero 2Msample/s Word Data Data Word Data Zero Zero 32Bit Zero 32Bit Zero Zero 32Bit Zero Zero 32Bit Zero 32Bit Zero Zero 32Bit Zero Zero 32Bit Zero Zero 4/3Msample/s Word Word 32Bit Zero Zero Zero 32Bit 1Msample/s Word Word Data Word Word Word Word Word Data Word Word 32Bit Zero Zero Zero Zero 32Bit Zero Zero Zero 32Bit Zero Zero Zero Zero 32Bit Zero 32Bit 800ksample/s Word Word Word Word Word Word Word Word Word Data Word Word Word Data Word Word Data Word Word Data Data Zero Zero 32Bit Zero Zero Zero Zero 32Bit Zero Zero Zero 32Bit Zero Zero Zero 32Bit 2/3Msample/s Data Word Word Word Word Word Data Word Word Word Word Word Data Word Word Word Word Word Data Word Word 32Bit Zero Zero Zero Zero Zero Zero 32Bit Zero Zero Zero Zero Zero Zero Zero 32Bit Zero Zero Zero Zero Zero 500ksample/s Word Word Word Word Word Data Word Word Word Word Word Word Word Word 32Bit Zero Zero Zero Zero 32Bit Zero Zero Zero 32Bit 400ksample/s Word \ \ Word \ | Word | Word | Word | Word Word Data

2µs

Figure 4-11. I/Q Data at Different Sample Rates

#### 4.5.6 Operation and Synchronization

1us

0µs

If the AT86RF215 operates in I/Q radio mode, it automatically enables the required I/Q data interface driver and receiver. The TX link (TXD and TXCLK receiver) is enabled in the states TXPREP and TX. In addition, the RXCLK driver is activated because the AT86RF215 operates as I/Q data interface clock master. The RX link is enabled in state RX and incorporates the RXCLK and RXD09 or RXD24 driver for the sub-1GHz or 2.4GHz transceiver, respectively. For details about the transceiver operating modes and states refer to chapter "Basic Operation" on page 30

3us

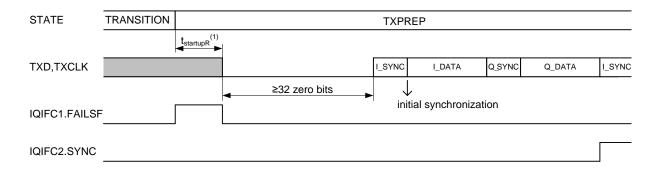

After enabling the TX link, the TXD and TXCLK driver require a start-up time (see section "I/Q Data Interface Driver DC and Startup Specification" on page 205). The start-up phase is followed by the initial synchronization. If the I\_SYNC pattern is detected after 32 or more zero bits, the de-serialization of the I/Q data is started. The synchronization of the TX link is validated at each expected I\_SYNC and Q\_SYNC pattern. An I\_SYNC pattern is expected either 16 bits after a Q\_SYNC pattern or 32 or more zero bits after a 32-bit data word. A Q\_SYNC pattern is expected 16 bits after an I\_SYNC pattern. Figure 4-12 on page 26 shows the start-up phase and initial synchronization of the TX link.

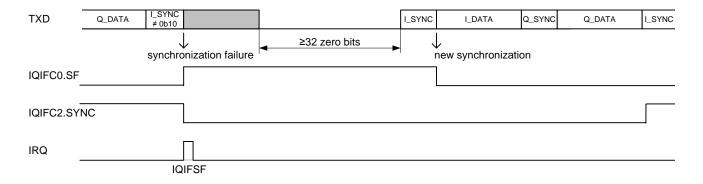

The successful reception of a I/Q data word is indicated by the synchronization status bit IQIFC2.SYNC. The bit is cleared at each read access and set again at the reception of the next I/Q data word.

5µs

4us

If the validation of the synchronization fails, the received data word is ignored, the synchronization status bit IQIFC2.SYNC is cleared and an error status is indicated together with an interrupt (see bit IQIFC0.SF and IRQS.IQIFSF). A synchronization failure is also indicated if a bit pattern other than I\_SYNC is detected during the IDLE condition. The error status is cleared after a new successful initial word synchronization. Figure 4-13 below shows an example of a synchronization failure caused by a wrong I\_SYNC pattern followed by a new synchronization.

Disabling the I/Q data driver (transceiver is set to state TRXOFF) resets the bits IQIFC2.SYNC and IQIFC0.SF to zero.

Between the last 32-bit word of a TX baseband frame and the first 32-bit word of the following TX baseband frame, zero bits must be inserted for a minimum of 2.5µs (400ksample/s period) to ensure a correct resynchronization of the I/Q data interface.

Figure 4-12. I/Q Data Interface Initial Synchronization

Note: I/Q data interface receiver start-up time (see section "I/Q Data Interface Driver DC and Startup Specification" on page 205)

Figure 4-13. I/Q Data Interface Synchronization Failure

## 4.5.7 Loop-back Test

An external loop-back feature is available to test the I/Q data interface by sending the data from the receiver TXD directly to the driver RXD09 and RXD24. Like in normal operation mode, the TXCLK is expected to be a looped back version of RXCLK with no guaranteed phase alignment. Due to the synchronization of the loop-back data to the driver clock RXCLK, the delay from TXD to RXD09/24 is up to 18-bit periods.

The loop-back mode is enabled setting bit IQIFC0.EXTLB to 1. Note, the loop-back mode must not be enabled in normal transmit operation mode, the loop-back mode shall be used for interface test and setup.

## 4.5.8 Register Description

#### 4.5.8.1 RF\_IQIFC0 - Transceiver I/Q Data Interface Configuration Register 0

The register configures the I/Q data interface.

| Bit           | 7     | 6  | 5  | 4  | 3  | 2  | 1      | 0   | _         |

|---------------|-------|----|----|----|----|----|--------|-----|-----------|

|               | EXTLB | SF | DF | ۲V | CI | ΜV | CMV1V2 | EEC | RF_IQIFC0 |

| Read/Write    | RW    | R  | RW | RW | RW | RW | RW     | RW  | <b>-</b>  |

| Initial Value | 0     | 0  | 0  | 1  | 0  | 1  | 0      | 0   |           |

## Bit 7 – IQIFC0.EXTLB: I/Q IF External Loopback

The bit enables the external loopback functionality. If the bit is set to 1, the received data of the I/Q IF pin TXDn/p is fed back via the pins RXDxxn/p.

#### Table 4-11. EXTLB

| Sub-register | Value      | Description                |

|--------------|------------|----------------------------|

| EXTLB        | <u>0x0</u> | External loopback disabled |

|              | 0x1        | External loopback enabled  |

## Bit 6 – IQIFC0.SF: I/Q IF Synchronization Failure

The bit indicates whether the data stream of the I/Q data interface is synchronized correctly.

Table 4-12. SF

| Sub-register | Value      | Description                |

|--------------|------------|----------------------------|

| SF           | <u>0x0</u> | No synchronization failure |

|              | 0x1        | Synchronization failure    |

## Bit 5:4 – IQIFC0.DRV: I/Q IF Driver Output Current

The sub-register configures the I/Q data interface driver output current.

Table 4-13. DRV

| Sub-register | Value      | Description |

|--------------|------------|-------------|

| DRV          | 0x0        | 1mA         |

|              | <u>0x1</u> | 2mA         |

|              | 0x2        | 3mA         |

|              | 0x3        | 4mA         |

## Bit 3:2 – IQIFC0.CMV: I/Q IF common mode voltage

The sub-register configures the common mode voltage of the I/Q data interface signals.

Table 4-14. CMV

| Sub-register | Value      | Description |

|--------------|------------|-------------|

| CMV          | 0x0        | 150mV       |

|              | <u>0x1</u> | 200mV       |

|              | 0x2        | 250mV       |

|              | 0x3        | 300mV       |

## Bit 1 – IQIFC0.CMV1V2: I/Q IF Common Mode Voltage Compliant to IEEE Std 1596

The common mode voltage of 1.2V compliant to the IEEE Std 1596 is set. Sub-register CMV has no effect.

#### Table 4-15. CMV1V2

| Sub-register | Value      | Description                     |

|--------------|------------|---------------------------------|

| CMV1V2       | <u>0x0</u> | CMV sub-register value is valid |

|              | 0x1        | Common mode of 1.2V is set      |

#### Bit 0 – IQIFC0.EEC: I/Q IF Enable Embedded TX Start Control

The bit enables the ability to start and finish transmitting by a control bit within the I/Q data stream (I\_DATA[0]). If this bit is set to 1, the transmit start and finish cannot be controlled by SPI commands.

#### Table 4-16. EEC

| Sub-register | Value      | Description                      |

|--------------|------------|----------------------------------|

| EEC          | <u>0x0</u> | Embedded control is not enabled. |

|              | 0x1        | Embedded control is enabled.     |

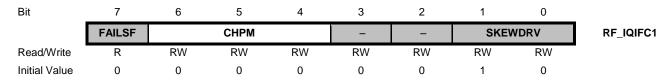

## 4.5.8.2 RF\_IQIFC1 - Transceiver I/Q Data Interface Configuration Register 1

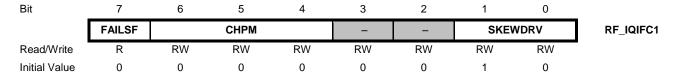

The register configures the skew behavior, the chip mode of the I/Q data interface and contains the status of the I/Q data interface receiver.

#### Bit 7 – IQIFC1.FAILSF: I/Q IF Receiver Failsafe Status

This bit indicates that the LVDS receiver is in failsafe mode. The failsafe mode is entered if the LVDS receiver is not driven by an LVDS driver.

#### Bit 6:4 – IQIFC1.CHPM: Chip Mode

This sub-register configures the working mode of the chip and define which parts (RF, baseband, I/Q IF) are in operation. Note, the AT86RF215IQ supports chip mode one (CHPM=1) only. Also note, the AT86RF215M generally does not support operation of BBC1 and RF24.

Table 4-17. CHPM

| Sub-register | Name           | Value      | Description                                                                                     |

|--------------|----------------|------------|-------------------------------------------------------------------------------------------------|

| СНРМ         | RF_MODE_BBRF   | <u>0x0</u> | RF enabled, baseband (BBC0, BBC1) enabled, I/Q IF disabled                                      |

|              | RF_MODE_RF     | 0x1        | RF enabled, baseband (BBC0, BBC1) disabled, I/Q IF enabled                                      |

|              | RF_MODE_BBRF09 | 0x4        | RF enabled, baseband (BBC0) disabled and (BBC1) enabled, I/Q IF for sub-GHz Transceiver enabled |

|              | RF_MODE_BBRF24 | 0x5        | RF enabled, baseband (BBC1) disabled and (BBC0) enabled, I/Q IF for 2.4GHz Transceiver enabled  |

#### Bit 1:0 – IQIFC1.SKEWDRV: Skew alignment I/Q IF driver

This sub-register configures the alignment of the I/Q data interface RXDxxn/p signal edges relative to the RXCLKn/p clock edges. The register values define the time from the RXCLKn/p clock edge to the next RXDxxn/p signal edge. The reset value of 2 (3.906ns) corresponds to a half bit period with the data center aligned in reference to the clock.

## Table 4-18. SKEWDRV

| Sub-register | Value      | Description |

|--------------|------------|-------------|

| SKEWDRV      | 0x0        | 1.906ns     |

|              | 0x1        | 2.906ns     |

|              | <u>0x2</u> | 3.906ns     |

|              | 0x3        | 4.906ns     |

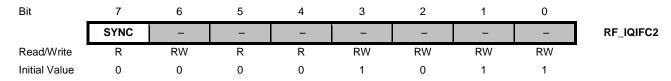

# 4.5.8.3 RF\_IQIFC2 - Transceiver I/Q Data Interface Configuration Register 2

The register contains the status of the I/Q data interface deserializer.

# • Bit 7 - IQIFC2.SYNC: I/Q IF Deserializer Synchronization Status

This bit indicates that the I/Q IF has synchronized to the incoming I/Q data stream.

29

# 5. Basic Operation

# 5.1 Operating Modes

### 5.1.1 Operating Modes Description

The AT86RF215 contains two transceivers. Each transceiver comprises a radio and a baseband module. Each transceiver can be operated in two different modes:

- Baseband mode

- I/Q radio mode.

The AT86RF215IQ only provides the I/Q radio mode for both transceivers. For device differentiation see section "Device Family" on page 3.

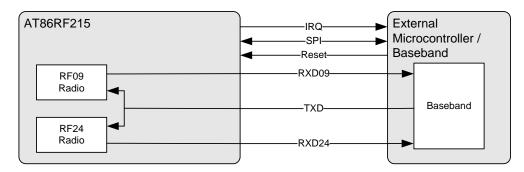

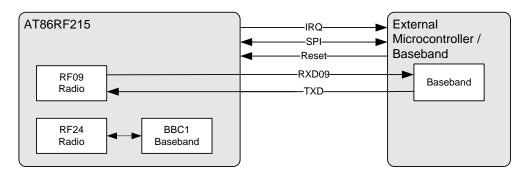

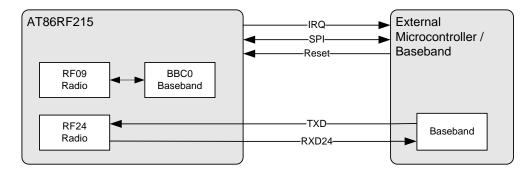

In the baseband mode, the internal baseband controls the radio and processes the data encoding/decoding for transmit and receive from the internal frame buffer. Figure 5-1 shows a sample system setup if both transceivers are operated in this mode.

In the I/Q radio mode, the radio is controlled from an external microcontroller via SPI and the data are exchanged via the I/Q data interface which is described in section "Serial I/Q Data Interface" on page 22. This allows the usage of an external baseband. In the I/Q radio mode any access to BBCn\_\* registers of the respective baseband has no effect. This implies that no baseband interrupts are issued and the registers BBCn\_IRQS are not changed. An example setup for both transceivers operated in I/Q radio mode is shown in Figure 5-2.

If one transceiver is operated in I/Q radio mode and the other transceiver is operated in baseband controlled mode, a mixed setup applies (see Figure 5-3 and Figure 5-4).

After reset or wakeup from state DEEP\_SLEEP, the baseband mode is set for both transceivers as default. The mode can be configured by the sub-register IQIFC1.CHPM; see Table 5-1 below.

Table 5-1. Chip mode Configurations

| One wating Made              | TRX09          |      |       | TRX24          |      |       | TVD |  |

|------------------------------|----------------|------|-------|----------------|------|-------|-----|--|

| Operating Mode               | RF09           | ввсо | RXD09 | RF24           | BBC1 | RXD24 | TXD |  |

| IOIEO4 OUDM DE MODE DODE     | on             | on   | off   | on             | on   | off   |     |  |

| IQIFC1.CHPM = RF_MODE_BBRF   | Baseband i     | mode |       | Baseband mode  |      |       | off |  |

| IOIEO4 OURM DE MORE DE       | on             | off  | on    | on             | off  | on    |     |  |

| IQIFC1.CHPM = RF_MODE_RF     | I/Q radio mode |      |       | I/Q radio mode |      |       | on  |  |

| IOIEO4 OURM DE MORE PRRESS   | on             | off  | on    | on             | on   | off   |     |  |

| IQIFC1.CHPM = RF_MODE_BBRF09 | I/Q radio mode |      |       | Baseband mode  |      |       | on  |  |

| IOIEO, OUBLA DE MODE DEDESA  | on             | on   | on    | on             | off  | on    |     |  |

| IQIFC1.CHPM = RF_MODE_BBRF24 | Baseband mode  |      |       | I/Q radio mode |      |       | on  |  |

Note: See sub-register IQIFC1.CHPM for chip mode enumerations

Figure 5-1. System Setup Using Baseband Mode for both Transceivers

Figure 5-2. System Setup Using I/Q Radio Mode for both Radios

Figure 5-3. System Setup for mixed Setup (TRX09 in I/Q Radio Mode, TRX24 in Baseband Mode)

Figure 5-4. System Setup for mixed Setup (TRX24 in I/Q Radio Mode, TRX09 in Baseband Mode)

# 5.1.2 Register Description

## 5.1.2.1 RF\_IQIFC1 - Transceiver I/Q Data Interface Configuration Register 1

The register configures the skew behavior, the chip mode of the I/Q data interface and contains the status of the I/Q data interface receiver.

# • Bit 6:4 - IQIFC1.CHPM: Chip Mode

This sub-register configures the working mode of the chip and define which parts (RF, baseband, I/Q IF) are in operation. Note, the AT86RF215IQ supports chip mode one (CHPM=1) only. Also note, the AT86RF215M generally does not support operation of BBC1 and RF24.

Table 5-2. CHPM

| Sub-register | Name           | Value      | Description                                                                                     |

|--------------|----------------|------------|-------------------------------------------------------------------------------------------------|

| СНРМ         | RF_MODE_BBRF   | <u>0x0</u> | RF enabled, baseband (BBC0, BBC1) enabled, I/Q IF disabled                                      |

|              | RF_MODE_RF     | 0x1        | RF enabled, baseband (BBC0, BBC1) disabled, I/Q IF enabled                                      |

|              | RF_MODE_BBRF09 | 0x4        | RF enabled, baseband (BBC0) disabled and (BBC1) enabled, I/Q IF for sub-GHz Transceiver enabled |

|              | RF_MODE_BBRF24 | 0x5        | RF enabled, baseband (BBC1) disabled and (BBC0) enabled, I/Q IF for 2.4GHz Transceiver enabled  |

## 5.2 State Machine

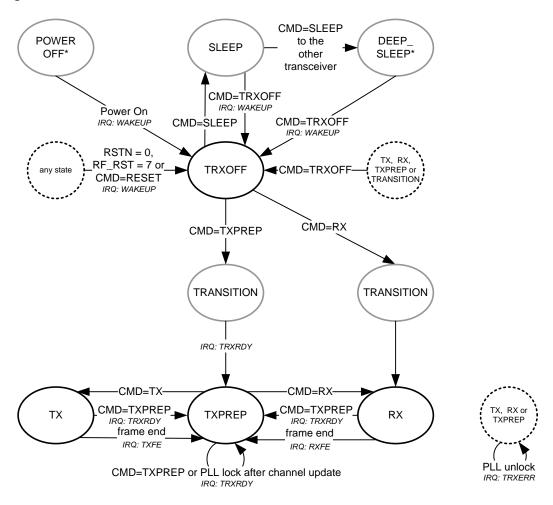

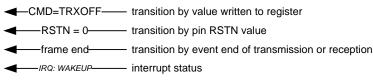

The AT86RF215 state machine forms the basis for both operating modes. Figure 5-5 shows the state machine of one of the transceiver. This section describes the different states and how to initiate state transitions.

Figure 5-5. State Machine

#### Legend:

<sup>\*</sup> Internal state, cannot be read from register RFn\_STATE

The current transceiver state is determined by reading the register RFn\_STATE. A state change is initiated by writing a command to the register RFn\_CMD. The provided command is appended to the command queue. The command queue has a depth of one element. As soon as the previous command has been executed, the next command is fetched and handled. For example, if in the state TRXOFF the commands TXPREP and TX are written consecutively to the register RFn\_CMD, the transition from state TRXOFF to TXPREP is executed before the transition to state TX is started.

An interrupt indication may be associated with some state changes. In this case the corresponding interrupt can be read from the registers RFn\_IRQS or BBCn\_IRQS, for further information see sections "Interrupt Signalling" on page 19 and "Interrupts" on page 38.

The following paragraphs describe the different states and the state transitions.

#### 5.2.2 Power-on Procedure

For further information see section "Power-on Reset" on page 13.

#### 5.2.3 General State Transitions

From each state a Chip Reset or Transceiver Reset can be initiated that forces the entire device or a certain transceiver to be reset and afterwards to enter state TRXOFF. For further information see section "Reset Modes" on page 13.

#### 5.2.4 State TRXOFF

In state TRXOFF all registers can be accessed via SPI.

By default the 1.8V analog voltage regulator (AVDD) is off. The analog voltage regulator is turned on during the transition to the states TXPREP or RX and turned off when returning to the state TRXOFF. To shorten the transition time, the analog voltage regulator (AVDD) can be configured by the sub-register AUXS.AVEN to remain on in state TRXOFF.

After the transceiver has completed the power-on procedure, it automatically reaches the state TRXOFF and the interrupt IRQS.WAKEUP is issued. The state TRXOFF can be reached from all states by writing the command TRXOFF to the register RFn\_CMD.

#### 5.2.5 State SLEEP

While the one of the transceiver is in state SLEEP, all registers of the transceiver are reset. In contrast to the state DEEP\_SLEEP, the digital voltage regulator (DVREG) stays on.

From state TRXOFF the transceiver is set to state SLEEP by writing the command SLEEP to the register RFn\_CMD. The state SLEEP can be left again by writing command TRXOFF to the register RFn\_CMD. If the transceiver reaches the state TRXOFF, the interrupt IRQS.WAKEUP is issued.

#### 5.2.6 State DEEP\_SLEEP and Wake-up Procedure

During state DEEP\_SLEEP the DVREG is turned off and the clock output signal (CLKO) is paused; see section "Clock Output" on page 20 for further information about CLKO. In state DEEP\_SLEEP the lowest current consumption value IDEEP\_SLEEP is reached.

If one of the transceivers (sub1-GHz or 2.4GHz) has been set to state SLEEP and the other transceiver (2.4GHz or sub1-GHz) is set to the state SLEEP as well, the state DEEP\_SLEEP is entered automatically (i.e. both transceivers need to be set to SLEEP to enter state DEEP\_SLEEP). Figure 5-6 shows the procedure to enter state DEEP\_SLEEP.

Figure 5-6. Procedure entering state DEEP\_SLEEP

|            |             | Command SLEEP to<br>RF09_CMD |  |  |  |

|------------|-------------|------------------------------|--|--|--|

| CLKO       | CLKO active | CLKO paused                  |  |  |  |

|            |             |                              |  |  |  |

| State RF09 | TRXOFF      | DEEP_SLEEP                   |  |  |  |

|            |             |                              |  |  |  |

| State RF24 | SLEEP       | DEEP_SLEEP                   |  |  |  |

|            |             |                              |  |  |  |

Writing command TRXOFF, via SPI, while in state DEEP\_SLEEP causes the transition from state DEEP\_SLEEP to TRXOFF. Writing the command TRXOFF to one of the registers RFn\_CMD wakes-up both transceivers. Figure 5-7 shows the procedure to leave state DEEP\_SLEEP and to wake-up.

Figure 5-7. Wake-up from DEEP\_SLEEP Procedure

Once the command TRXOFF is written to one of the radio register RFn\_CMD, the XOSC and DVREG are started. After tobeep\_sleep\_trxoff both transceivers enter the state TRXOFF and both interrupts IRQS.WAKEUP are issued. The clock output signal is available and provided to pin CLKO if enabled before the state DEEP\_SLEEP has been entered. This procedure is similar to the power-on procedure. All registers are set to their reset values. However the registers RF\_CFG, RF\_CLKO, RF\_XOC and RF\_BMDVC are not reset. These registers keep their values during state DEEP\_SLEEP, see section "AT86RF215 Reset Modes" on page 13.

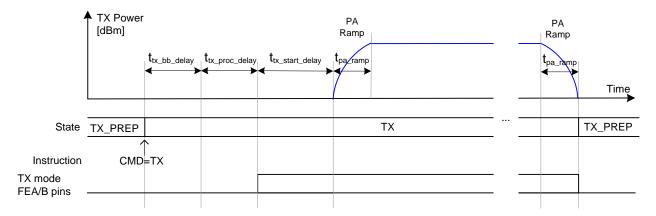

## 5.2.7 State TXPREP

The state TXPREP is used to prepare the transceiver for transmission or reception. In the state TXPREP, the analog voltage regulator is powered up, the PLL is locked to the configured frequency and analog calibrations are initiated (see section "Analog Calibrations" on page 80). To achieve maximum performance, the TX output power (register PAC.TXPWR) and the center frequency (see section "Frequency Synthesizer (PLL)" on page 62) must be configured in state TRXOFF. The analog transmitter and receiver are still disabled.

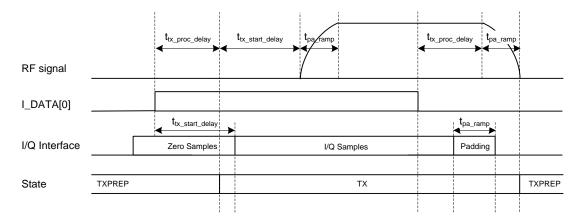

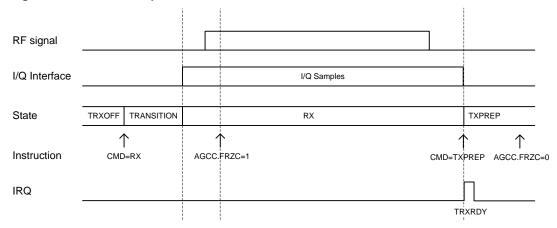

In the I/Q radio mode the I/Q data interface (pins RXCLKP/N, TXCLKP/N and TXDP/N) is enabled.

The state TXPREP can be reached from any state, except from the sleep states (i.e. SLEEP and DEEP\_SLEEP), by writing the command TXPREP to the register RFn\_CMD. Depending on the state in which the command TXPREP is written different transition durations are required to reach the state TXPREP. For example, from state TRXOFF the duration ttrxoff\_txprep is required to reach TXPREP.

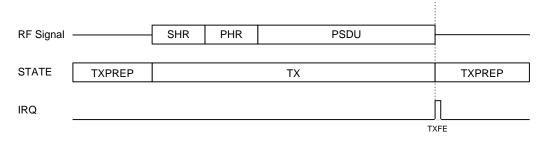

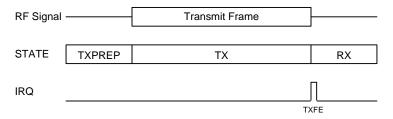

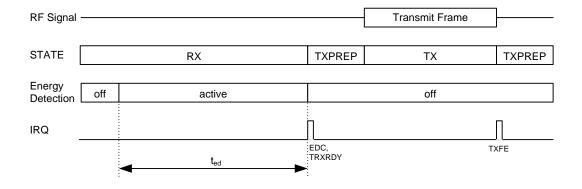

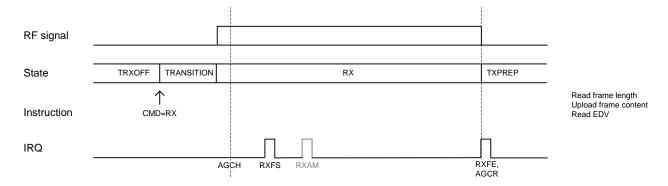

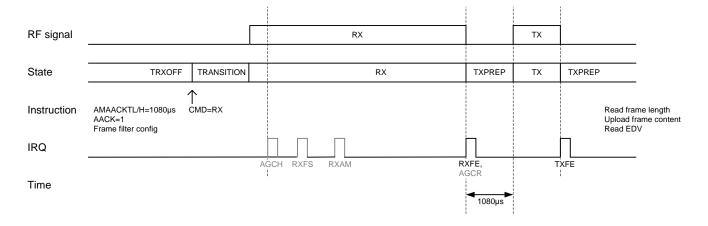

In the baseband mode, the baseband switches automatically from the state TX to the state TXPREP once frame transmission is completed. It switches automatically from state RX to state TXPREP, once a frame reception is completed.

Entering the state TXPREP by writing the command TXPREP causes the device to issue the interrupt IRQS.TRXRDY once the state TXPREP is reached.

#### 5.2.8 State TX

The state TX is used to transmit data. The PLL is locked to the transmit frequency. The analog voltage regulator, the transmitter analog frontend and transmitter digital frontend are all enabled.

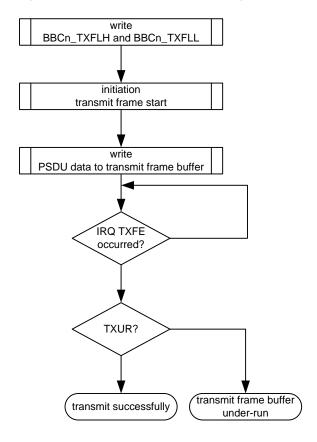

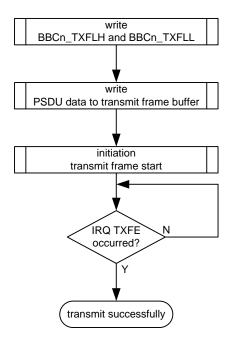

In the baseband mode, the baseband enables the transmitter and provides I/Q data to the radio. The samples are handled by the radio and transmitted over-the-air. If all samples are sent, the baseband (operated in basic mode) disables the transmitter and sets the state TXPREP automatically. For further information see sections "Example Transmit Procedure Using Basic Mode" on page 172 and "Example Transmit Procedure Using Auto Mode" on page 174.

In the I/Q radio mode, the external microcontroller controls the transmitter via SPI and the I/Q data is provided by the I/Q interface. The transmitter control is described in section "Transmit Control" on page 46. In the I/Q radio mode, the I/Q data interface (pins RXCLKP/N, TXCLKP/N and TXDP/N) is enabled. For further information see section "Transmitter Usage in I/Q Radio Mode" on page 178.

The state TX is reached from the state TXPREP by writing the command TX to the register RFn\_CMD. If the command TXPREP or TRXOFF is written to the transceiver while being in state TX, an ongoing transmission is aborted.

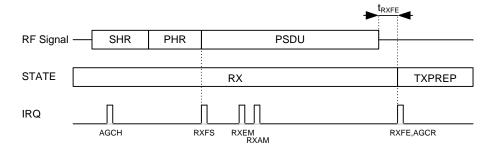

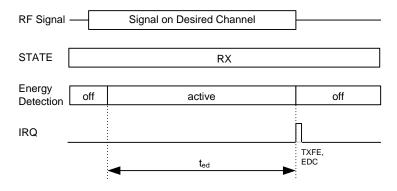

#### 5.2.9 State RX

The state RX is used to receive data. The PLL is locked to the receive frequency. The analog voltage regulator, the receiver analog frontend and the receiver digital frontend are all enabled.

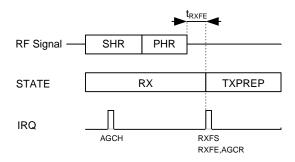

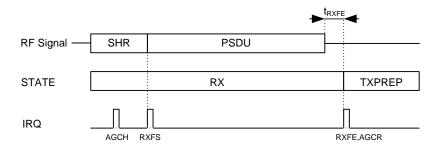

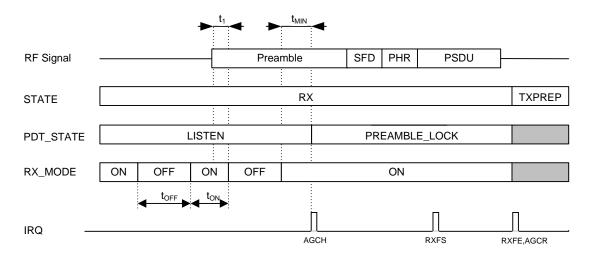

In the baseband mode, the baseband decodes received data. If the baseband has received a complete frame and the interrupt IRQS.RXFE occurs, it stops the reception and the transceiver is switched to the state TXPREP automatically. For further information about the receive procedure see sections "Example Receive Procedure Using Basic Mode" on page 173 and "Example Receive Procedure Using Auto Mode" on page 176.

In the I/Q radio mode, the I/Q data interface (pins RXCLKP/N, RXDP/N09 (sub1-GHz) or RXDP/N24 (2.4GHz)) is enabled.

The state RX is reached from the state TXPREP or from the state TRXOFF by writing the command RX to the register RFn\_CMD. If the command TXPREP or TRXOFF is written to the transceiver while being in state RX, an ongoing reception is aborted.

## 5.2.10 Register Description

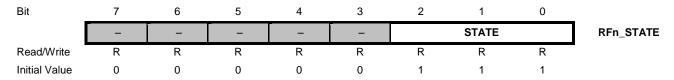

# 5.2.10.1 RFn\_STATE - Transceiver State

The register contains the current transceiver state.

#### Bit 2:0 – STATE.STATE: Transceiver State

The current transceiver state can be determined by reading the sub-register STATE. A state transition is triggered by writing a new command to the sub-register CMD.

Table 5-3. STATE

| Sub-register | Name          | Value      | Description                                    |

|--------------|---------------|------------|------------------------------------------------|

| STATE        | RF_TRXOFF     | 0x2        | TRXOFF (Transceiver off, SPI active)           |

|              | RF_TXPREP     | 0x3        | TXPREP (Transmit preparation)                  |

|              | RF_TX         | 0x4        | TX (Transmit)                                  |

|              | RF_RX         | 0x5        | RX (Receive)                                   |

|              | RF_TRANSITION | 0x6        | TRANSITION (State transition in progress)      |

|              | RF_RESET      | <u>0x7</u> | RESET (Transceiver is in state RESET or SLEEP) |

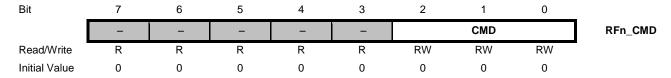

# 5.2.10.2 RFn\_CMD - Transceiver Command

This register allows control of the transceiver.

## • Bit 2:0 - CMD.CMD: Transceiver Command

The sub-register controls the transceiver states. Writing a new command to the sub-register triggers a state transition. The current state can be read from sub-register STATE.

Table 5-4. CMD

| Sub-register | Name      | Value | Description                                                                                |

|--------------|-----------|-------|--------------------------------------------------------------------------------------------|

| CMD          | ID RF_NOP |       | NO OPERATION                                                                               |

|              | RF_SLEEP  | 0x1   | SLEEP                                                                                      |

|              | RF_TRXOFF | 0x2   | TRXOFF (Transceiver off, SPI active)                                                       |

|              | RF_TXPREP | 0x3   | TXPREP (Transmit preparation)                                                              |

|              | RF_TX     | 0x4   | TX (Transmit)                                                                              |

|              | RF_RX     | 0x5   | RX (Receive)                                                                               |

|              | RF_RESET  | 0x7   | RESET (transceiver reset, the transceiver state will automatically end up in state TRXOFF) |

# 5.3 Interrupts

## 5.3.1 Description

The AT86RF215 generates in certain scenarios interrupt events (IRQ). Depending on the interrupt configuration, all interrupt events (from the sub-1GHz radio, 2.4GHz radio, baseband core 0 and baseband core 1) are combined to a single interrupt signal.

Interrupts can be enabled / disabled for each radio and baseband core separately by the registers RFn\_IRQM and BBCn\_IRQM. After a reset procedure and a wake-up from DEEP\_SLEEP procedure, all interrupt sources are disabled except the interrupt WAKEUP.

The pending interrupt event(s) or source(s) can be determined by reading the radio and baseband IRQ status registers RFn\_IRQS and BBCn\_IRQS. Each radio and baseband block provides its own interrupt status register. Altogether there are four interrupt status registers.

The radio interrupt status registers RFn\_IRQS indicate interrupt events that are related to radio functionality, such as IRQS.TRXERR, IRQS.EDC or IRQS.TRXRDY, or general transceiver functionality, such as IRQS.IQIFSF, IRQS.BATLOW, IRQS.WAKEUP. Table 5-5 summarizes the radio interrupts status and refers to sections that provide further information about the corresponding interrupt.

Table 5-5. Radio Interrupt Status

| Interrupt   | Section for further information                                        | Comment                                                                                                                                                                                                                        |

|-------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRQS.WAKEUP | "State DEEP_SLEEP and Wake-up<br>Procedure" on page 34                 | Returning from the state DEEP_SLEEP, the interrupt IRQS.WAKEUP is always set for both radios together. On the other hand, the interrupt IRQS.WAKEUP is set only for the corresponding radio that returns from the State SLEEP. |

|             | "Reset Modes " on page 13                                              | Once a Chip Reset procedure is completed, the interrupt IRQS.WAKEUP is issued for both transceivers. A Transceiver Reset completion is indicated by the interrupt IRQS.WAKEUP for the corresponding transceiver only.          |

| IRQS.TRXRDY | "Frequency Synthesizer (PLL)" on page 62 and "State TXPREP" on page 35 |                                                                                                                                                                                                                                |

| IRQS.EDC    | "Energy Measurement" on page 56                                        |                                                                                                                                                                                                                                |

| IRQS.BATLOW | "Battery Monitor (BATMON) " on page 78                                 | The IRQ IRQS.BATLOW is issued pair wise, i.e. this IRQ is always set for both radios (sub1-GHz and 2.4GHz) at the same time.                                                                                                   |

| IRQS.TRXERR | "Frequency Synthesizer (PLL)" on page 62                               |                                                                                                                                                                                                                                |

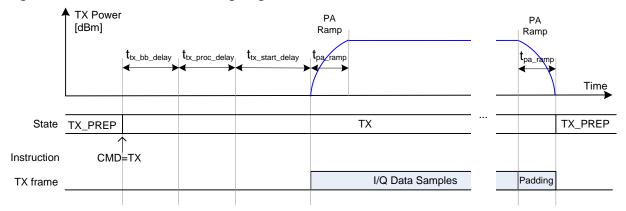

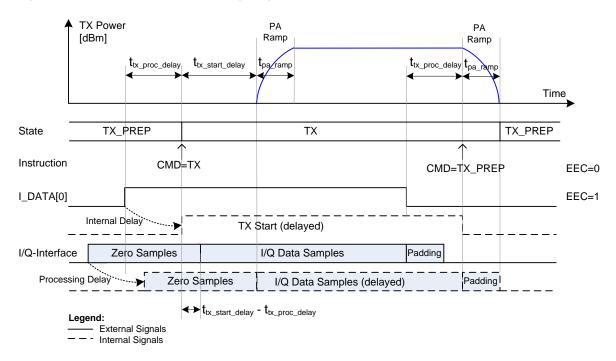

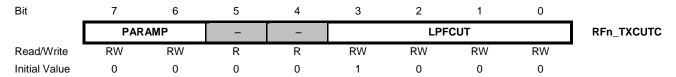

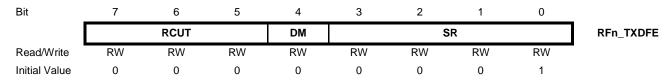

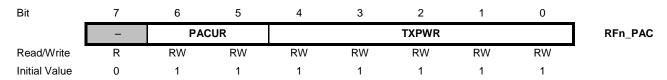

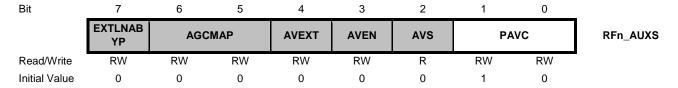

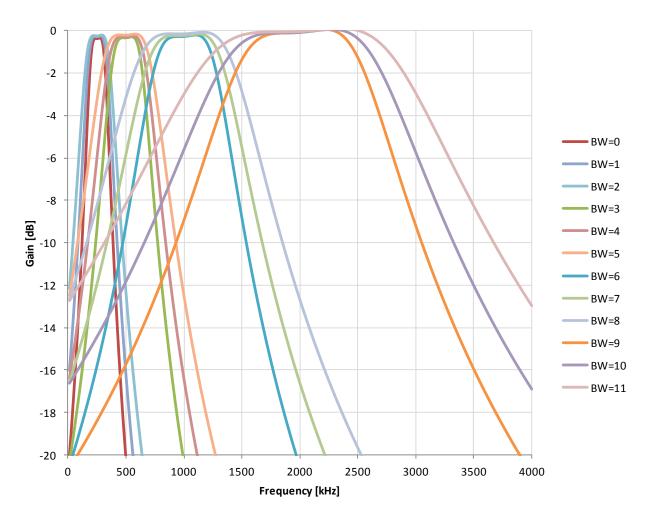

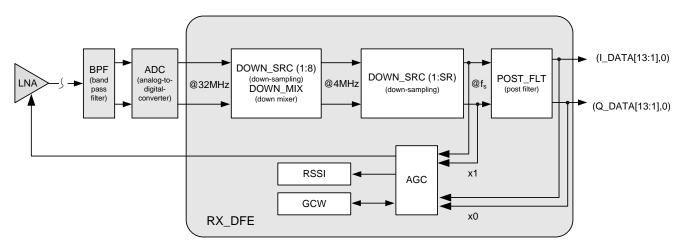

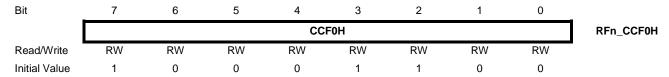

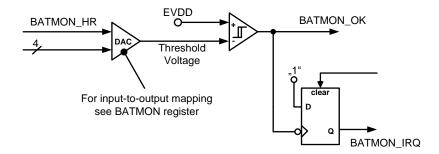

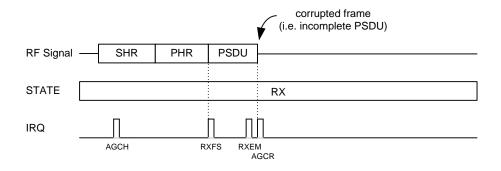

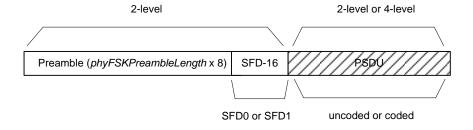

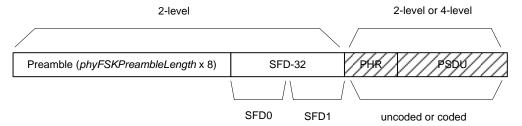

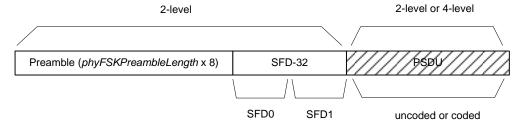

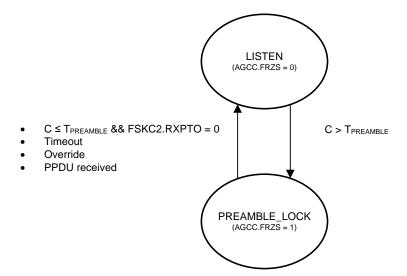

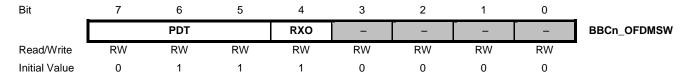

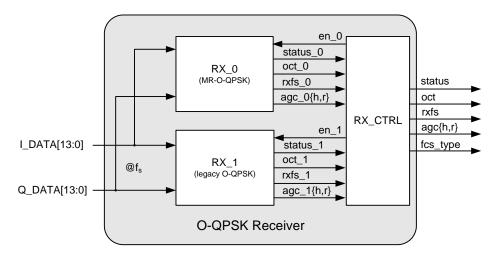

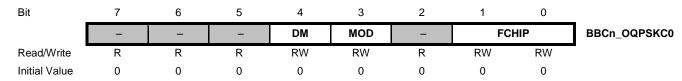

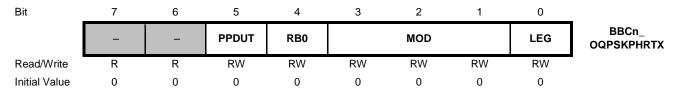

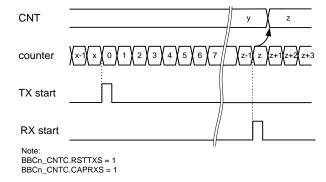

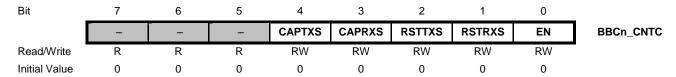

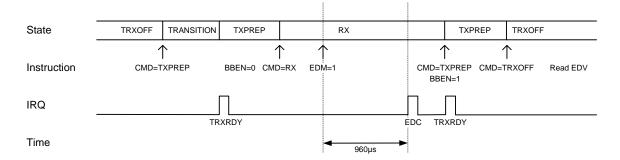

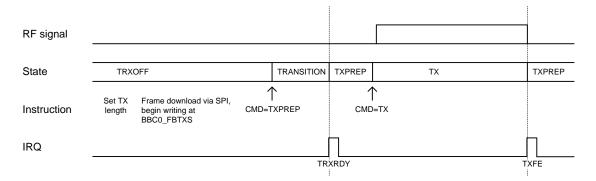

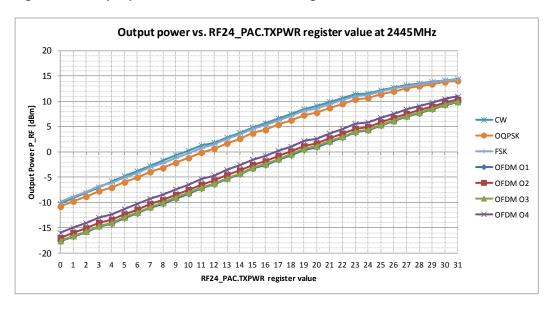

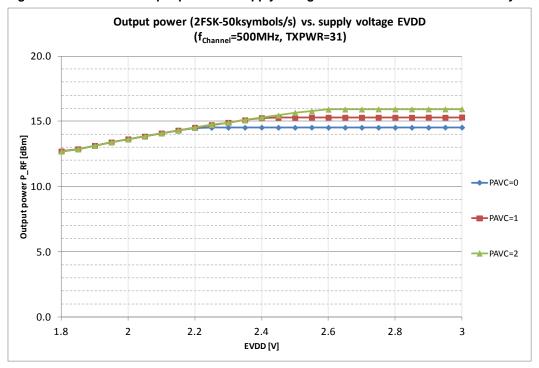

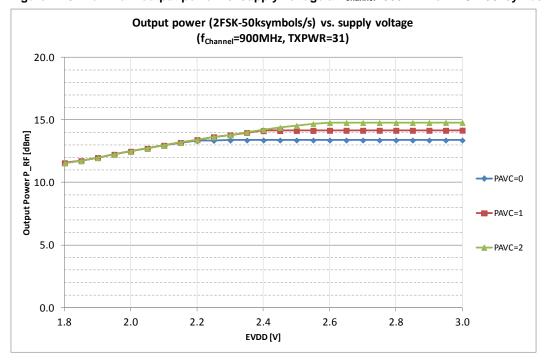

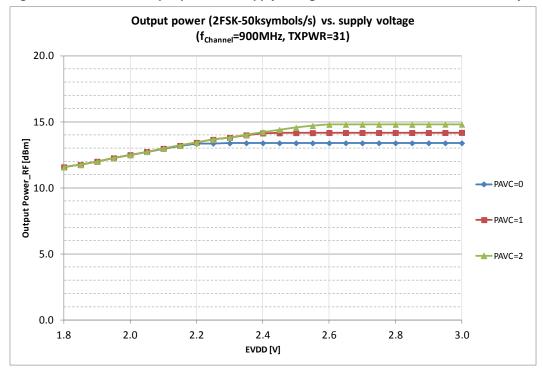

| IRQS.IQIFSF | "Serial I/Q Data Interface" on page 22                                 | Applicable in I/Q radio mode only.                                                                                                                                                                                             |