# Two output ultra-low additive phase noise PCIe Gen 1 to 5, and UPI/QPI fanout buffer

#### **Features**

- One differential input which accepts any differential format.

- Two differential HCSL outputs

- Ultra-low additive jitter: 32fs (in 12kHz to 20MHz integration band at 400MHz clock frequency)

- Supports clock frequencies from 0 to 400MHz

- Supports 2.5V or 3.3V power supplies for HCSL outputs

- Embedded Low Drop Out (LDO) Voltage regulator provides superior Power Supply Noise Rejection

- Maximum output to output skew of 50ps

- Individual Output Enable pin for each differential pair

- Transfers Spread-Spectrum without attenuation

ZL40262LDG1 ZL40262LDF1

20 pin QFN Trays 20 pin QFN Tape

**Ordering Information**

QFN Tape and Reel

Package size: 4 x 4 mm -40°C to +85°C

#### **Applications**

- PCI Express generation 1/2/3/4/5 clock distribution

- UPI/QPI clock distribution

- Low jitter clock trees

- Logic translation

- Clock and data signal restoration

- High performance microprocessor clock distribution

- Test Equipment

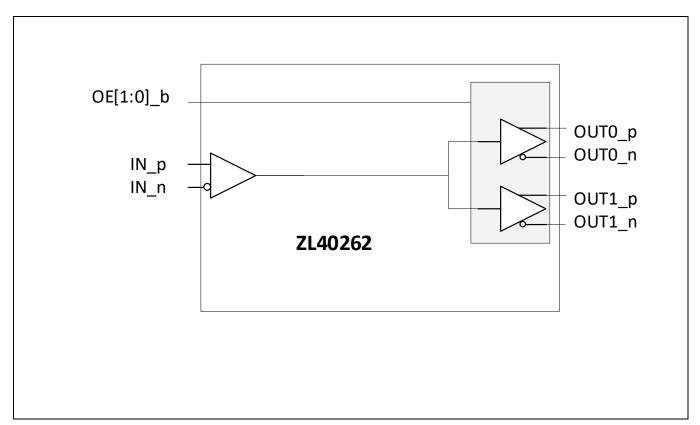

#### Figure 1. Functional Block Diagram

# **Table of Contents**

Microsemi

а 🐼 Міскоснір company

| Features                             |    |

|--------------------------------------|----|

| Applications                         | 1  |

| Table of Contents                    | 2  |

| Pin Diagram                          | 5  |

| Pin Descriptions                     | 6  |

| Functional Description               | 7  |

| Clock Inputs                         | 7  |

| Clock Outputs                        | 10 |

| Termination of unused outputs        | 11 |

| Power Consumption                    | 11 |

| Power Supply Filtering               | 11 |

| Power Supplies and Power-up Sequence | 12 |

| Device Control                       |    |

| Typical phase noise performance      | 13 |

| AC and DC Electrical Characteristics | 14 |

| Absolute Maximum Ratings             | 14 |

| Recommended Operating Conditions     | 14 |

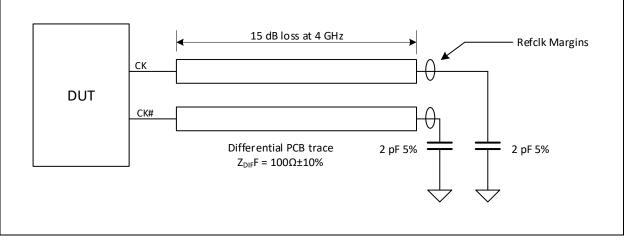

| Package Outline                      |    |

| Change history:                      | 25 |

# List of Figures

| Figure 1.  | Functional Block Diagram                                           | 1  |

|------------|--------------------------------------------------------------------|----|

| Figure 2.  | Functional Block Diagram<br>Pin Diagram                            | 5  |

| Figure 3.  | Input driven by source terminated HCSL                             | 8  |

| Figure 4.  | Input driven by receiver terminated HCSL                           | 8  |

| Figure 5.  | Input driven by AC coupled LVPECL output                           |    |

| Figure 6.  | Input driven by AC coupled LVDS                                    | 9  |

| Figure 7.  | Input driven by a single ended output                              | 9  |

| Figure 8.  | Source terminated HCSL                                             |    |

| Figure 9.  | Receiver terminated HCSL                                           |    |

| Figure 10. | Power Supply Filtering                                             | 12 |

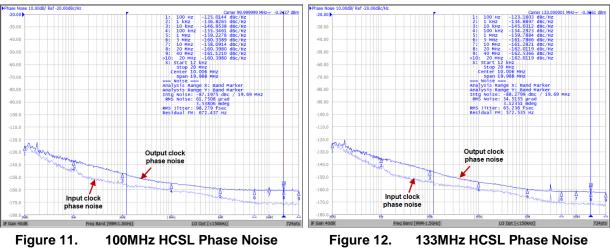

| Figure 11. | 100MHz HCSL Phase Noise                                            | 13 |

| Figure 12. | 133MHz HCSL Phase Noise                                            | 13 |

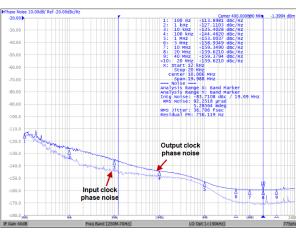

| Figure 13. | 400MHz HCSL Phase Noise                                            | 13 |

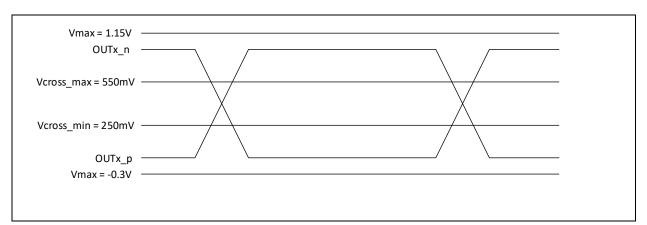

| Figure 14. | Single-Ended Measurement Points for Absolute Cross Point and Swing |    |

| Figure 15. | Single-Ended Measurement Points for Delta Cross Point              | 21 |

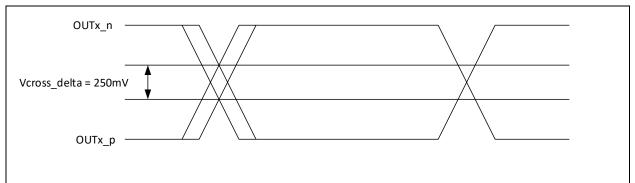

| Figure 16. | Single-Ended Measurement Points for Rise and Fall Time Matching    | 21 |

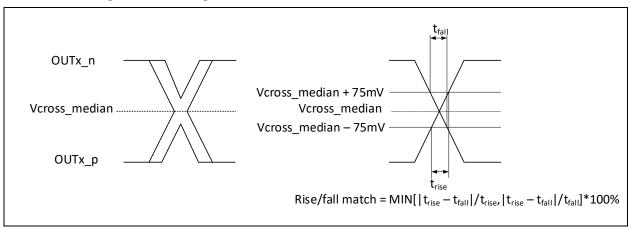

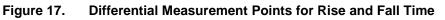

| Figure 17. | Differential Measurement Points for Rise and Fall Time             |    |

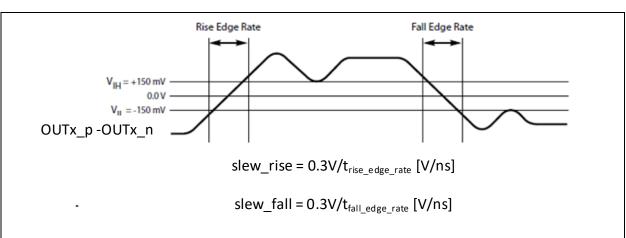

| Figure 18. | Differential Measurement Points for Ringback                       |    |

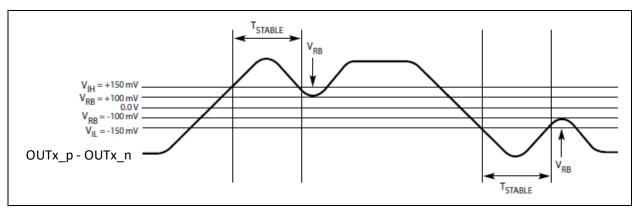

| Figure 19. | Test Circuit                                                       |    |

# List of Tables

| Table 1 Pin Descriptions                                    | 6  |

|-------------------------------------------------------------|----|

| Table 2 Absolute Maximum Ratings*                           |    |

| Table 3 Recommended Operating Conditions*                   |    |

| Table 4 Current consumption                                 |    |

| Table 5 Input Characteristics*                              | 15 |

| Table 6 Power Supply Rejection Ratio for VDD = VDDO = 3.3V* | 15 |

| Table 7 Power Supply Rejection Ratio for VDD = VDDO = 2.5V* | 16 |

| Table 8 HCSL Outputs for VDDO = 3.3V*                       | 17 |

| Table 9 HCSL (PCIe) Jitter Performance for VDDO = 3.3V      | 18 |

| Table 10 HCSL Outputs for VDDO = 2.5V*                      | 19 |

| Table 11 HCSL (PCIe) Jitter Performance for VDDO = 2.5V     | 20 |

| Table 12 4x4mm QFN Package Thermal Properties               | 23 |

Data Sheet

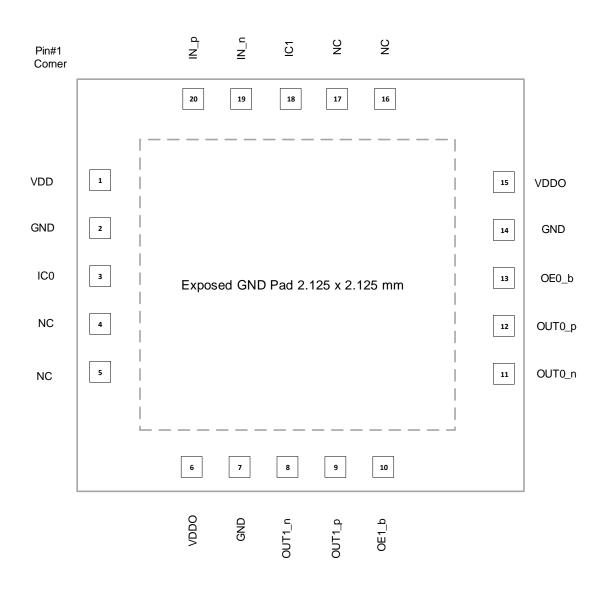

# **Pin Diagram**

The device is packaged in a 4x4mm 20-pin QFN.

Figure 2. Pin Diagram

# **Pin Descriptions**

All device inputs and outputs are HCSL unless described otherwise. The I/O column uses the following symbols: I – input,  $I_{PU}$  – input with 300k $\Omega$  internal pull-up resistor,  $I_{PD}$  – input with 300k $\Omega$  internal pull-down resistor,  $I_{APU}$  – input with 31k $\Omega$  internal pull-up resistor,  $I_{APD}$  – input with 30k $\Omega$  internal pull-down resistor,  $I_{APU/APD}$  – input biased to VDD/2 with 60k $\Omega$  internal pull-up and pull-down resistors (30 k $\Omega$  equivalent), O – output, I/O – Input/Output pin, NC-No connect pin, P – power supply pin.

Table 1Pin Descriptions

| #                  | Name                                 | I/O                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                           | Description                                                                                            |  |  |  |  |  |

|--------------------|--------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Input Refe         | erence                               |                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                        |  |  |  |  |  |

| 20<br>19           | IN_p<br>IN_n                         | I <sub>APD</sub><br>I <sub>APU/APD</sub><br>I <sub>APD</sub><br>I <sub>APU/APD</sub> | Input Differential or Single Ended Reference<br>Input frequency range 0Hz to 400MHz.<br>Non-inverting inputs (_p) are pulled down with internal $30k\Omega$ pull-down re<br>Inverting inputs (_n) are pulled up and pulled down with $60k\Omega$ internal resistor<br>equivalent) to keep inverting input voltages at VDD/2 when inverting inputs<br>floating (device fed with a single ended reference). |                                                                                                        |  |  |  |  |  |

| Output Cl          | ocks                                 | 1                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                        |  |  |  |  |  |

| 12<br>11<br>9<br>8 | OUT0_p<br>OUT0_n<br>OUT1_p<br>OUT1_n | 0                                                                                    | Ultra-Low Additive Jitter Differential HCSL Outputs 0 to 1<br>Output frequency range 0 to 400MHz                                                                                                                                                                                                                                                                                                          |                                                                                                        |  |  |  |  |  |

| Control            | I                                    |                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                        |  |  |  |  |  |

| 13<br>10           | OE0_b<br>OE1_b                       | I <sub>PD</sub>                                                                      | Output Enal                                                                                                                                                                                                                                                                                                                                                                                               | <b>ble.</b> Logic level on these pins enables/disables corresponding outputs.                          |  |  |  |  |  |

|                    |                                      |                                                                                      | OEn_b                                                                                                                                                                                                                                                                                                                                                                                                     | OUTn_p/n                                                                                               |  |  |  |  |  |

|                    |                                      |                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                         | Active                                                                                                 |  |  |  |  |  |

|                    |                                      |                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                         | High-Z (outputs p/n will be low/low because of 50Ω shunt resistors—see recommended output termination) |  |  |  |  |  |

| Power and          | d Ground                             |                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                        |  |  |  |  |  |

| 1                  | VDD        | Р               | Positive Supply Voltage. Connect to 3.3V or 2.5V supply.                                                                                                        |

|--------------------|------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>15            | VDDO       | Р               | <b>Positive Supply Voltage for Differential Outputs</b> Connect 3.3V or 2.5V power supply. VDDO does not have to be connected to the same voltage level as VDD. |

| 3<br>18            | IC0<br>IC1 | I <sub>PD</sub> | Internal Connection For normal operation connect to VDD or pull-up with $1k\Omega$ resistor.                                                                    |

| 4<br>5<br>16<br>17 | NC         | NC              | No Connect Leave open                                                                                                                                           |

| 2<br>7<br>14       | GND        | Р               | Ground Connect to the ground                                                                                                                                    |

| E-Pad              | GND        | Р               | Ground. Connect to the ground                                                                                                                                   |

#### **Functional Description**

The ZL40262 is an ultra-low additive jitter, low power 1 to 2 HCSL fanout buffer.

The device operates from 2.5V+/-5% or 3.3V+/-5% supply. Its operation is guaranteed over the industrial temperature range -40°C to +85°C.

#### **Clock Inputs**

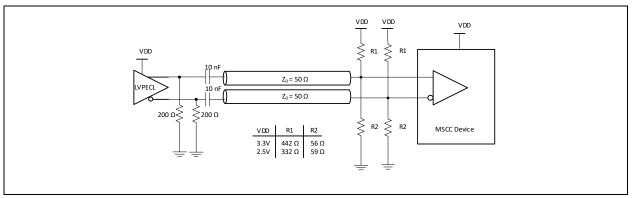

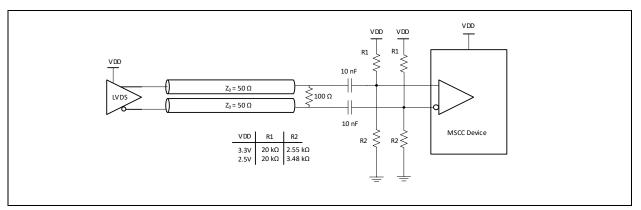

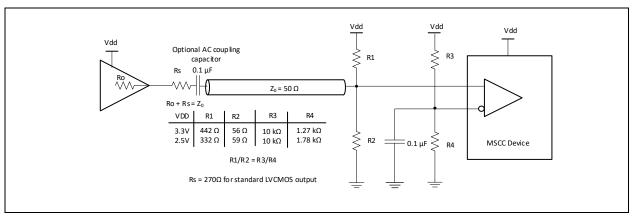

The following blocks diagram shows how to terminate different signals fed to the ZL40262 inputs.

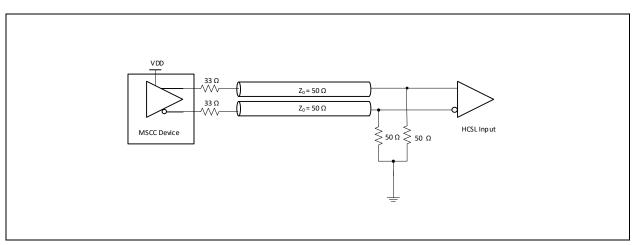

Figure 3 and Figure 4 show how to terminate the input when driven from an HCSL driver.

The input buffer in ZL40262 in a native HCSL receiver so other differential formats need to be AC coupled as shown in Figure 5 and Figure 6 for LVPECL and LVDS signals respectively.

Figure 7 shows how to terminate a single ended output such as LVCMOS. Ideally, resistors R1 and R2 should be  $100\Omega$  each and Ro + Rs should be  $50\Omega$  so that the transmission line is terminated at both ends with characteristic impedance. If the driving strength of the output driver is not sufficient to drive low impedance, the value of series resistor Rs should be increased. This will reduce the voltage swing at the input but this should be fine as long as the input voltage swing requirement is not violated (Table 5). The source resistors of Rs = 270 $\Omega$  could be used for standard LVCMOS driver. This will provide 516mV of voltage swing for 3.3V LVCMOS driver with load current of  $(3.3V/2) *(1/(270\Omega + 50\Omega)) = 5.16$ mA.

For optimum performance both differential input pins (\_p and \_n) need to be DC biased to the same voltage. Hence, the ratio R1/R2 should be equal to the ratio R3/R4.

Figure 3. Input driven by source terminated HCSL

Figure 4. Input driven by receiver terminated HCSL

Figure 5. Input driven by AC coupled LVPECL output

#### Figure 6. Input driven by AC coupled LVDS

Figure 7. Input driven by a single ended output

#### **Clock Outputs**

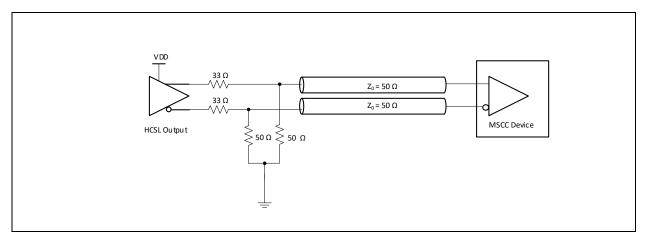

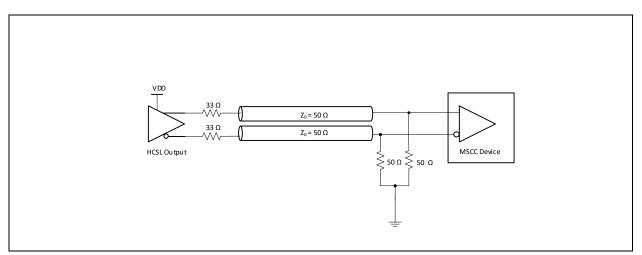

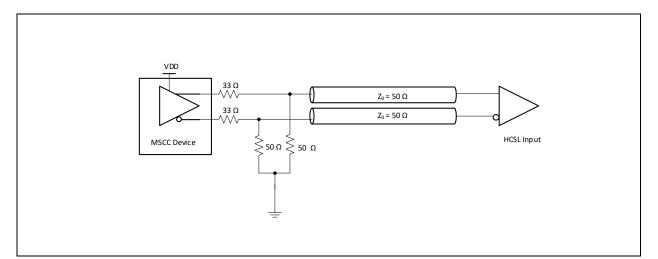

Differential HCSL outputs should be terminated as shown in Figure 8 or Figure 9.

Figure 8. Source terminated HCSL

Figure 9. Receiver terminated HCSL

#### Termination of unused outputs

Unused outputs should be left unconnected.

#### **Power Consumption**

The device total power consumption can be calculated as:  $P_T = P_S + P_C + P_{O_DIFF}$ Where:

$P_{\rm S} = V_{DD} * I_{\rm S}$

$P_C = V_{DDO} * I_{DD\_CM}$

$P_{O_DIF} = V_{DDO} * I_{DD_HCSL} * N$

Core power consumed by the input buffer. The static current  $(I_S)$  is specified in Table 4.

Common output power shared between two outputs. The current IDD\_CM is specified in Table 4.

Output power where output current per output ( $I_{DD\_HCSL}$ ) is specified in Table 4. N is number of enabled outputs.

Power dissipated inside the device can be calculated by subtracting power dissipated in termination/biasing resistors from the power consumption:

$P_D = P_T - N * P_{HCSL}$

Where:

$P_{HCSL} = (V_{SW} / 50\Omega)^2 * (50\Omega + 33\Omega)$

$V_{SW}$  is voltage swing of HCSL output. 50 $\Omega$  is termination resistance and 33 $\Omega$  is series resistance of the HCSL output.

#### **Power Supply Filtering**

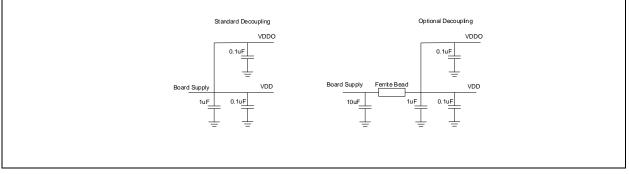

Each power pin (VDD and VDDO) should be decoupled with  $0.1\mu$ F capacitor with minimum equivalent series resistance (ESR) and minimum series inductance (ESL). For example, 0402 X5R Ceramic Capacitors with 6.3V minimum rating could be used. These capacitors should be placed as close as possible to the power pins. To reduce the power noise from adjacent digital components on the board each power supply could optionally be further insulated with low resistance ferrite bead with  $10\mu$ F and  $1\mu$ F capacitors. Following figure shows the standard and optional decoupling method.

Data Sheet

Figure 10. Power Supply Filtering

#### **Power Supplies and Power-up Sequence**

The device has two different power supplies: VDD and VDDO which should always be connected to the same voltage supply. Voltages supported by each of these power supplies are specified in Table 3. VDD and VDDO should always be turned on and off at the same time.

#### **Device Control**

ZL40262 outputs are controlled via OE[1:0]\_b pins. When an OE\_b pin is low the corresponding outputs will be active and when this pin is high the output will be high-Z. When the output driver is in high-Z mode, the output pins will be pulled low via external  $50\Omega$  HCSL termination resistors.

# Typical phase noise performance

The following plots show typical phase noise performance for 100 MHz, 133 MHz and 400 MHz respectively.

Figure 13. 400MHz HCSL Phase Noise

# **AC and DC Electrical Characteristics**

#### **Absolute Maximum Ratings**

#### Table 2 Absolute Maximum Ratings\*

|   | Parameter             | Sym.                 | Min. | Тур. | Max. | Units | Notes |

|---|-----------------------|----------------------|------|------|------|-------|-------|

| 1 | Supply voltage (3.3V) | $V_{DD}$ / $V_{DDO}$ | -0.5 |      | 4.6  | V     |       |

| 2 | Supply voltage (2.5V) | $V_{DD}$ / $V_{DDO}$ | -0.5 |      | 3.5  | V     |       |

| 3 | Storage temperature   | T <sub>ST</sub>      | -55  |      | 125  | °C    |       |

\* Exceeding these values may cause permanent damage \* Functional operation under these conditions is not implied

\* Voltages are with respect to ground (GND) unless otherwise stated

#### **Recommended Operating Conditions**

#### **Table 3 Recommended Operating Conditions\***

|   | Characteristics       | Sym.                              | Min.  | Тур. | Max.                  | Units | Notes |

|---|-----------------------|-----------------------------------|-------|------|-----------------------|-------|-------|

| 1 | Supply voltage 3.3V   | $V_{DD}$ / $V_{DDO}$              | 3.135 | 3.30 | 3.465                 | V     |       |

| 2 | Supply voltage 2.5V   | V <sub>DD</sub> /V <sub>DDO</sub> | 2.375 | 2.50 | 2.625                 | V     |       |

| 5 | Operating temperature | T <sub>A</sub>                    | -40   | 25   | 85                    | °C    |       |

| 6 | Input voltage         | V <sub>DD-IN</sub>                | - 0.3 |      | V <sub>DD</sub> + 0.3 | V     |       |

\* Voltages are with respect to ground (GND) unless otherwise stated \* The device core supports two power supply modes (3.3V and 2.5V)

#### Data Sheet

#### **Table 4 Current consumption**

|     | Characteristics                     | Sym.                | Min. | Тур.  | Max.  | Units | Notes         |

|-----|-------------------------------------|---------------------|------|-------|-------|-------|---------------|

| 1   | Core device current                 | I <sub>s_3.3V</sub> |      | 49    | 53    | mA    | VDD= 3.3V+5%  |

| l ' |                                     | I <sub>s_2.5V</sub> |      | 48    | 53    | mA    | VDD = 2.5V+5% |

| 2   | 2 Common output current             | IDD_CM_3.3V         |      | 5.24  | 5.82  | mA    | VDDO= 3.3V+5% |

| 2   |                                     | IDD_CM_2.5V         |      | 4.72  | 5.32  | mA    | VDDO= 2.5V+5% |

| 3   | Current dissipation per HCSL output | IDD_HCSL_3.3V       |      | 14.92 | 17.18 | mA    | VDDO= 3.3V+5% |

| 3   | Current dissipation per HCSE output | IDD_HCSL_2.5V       |      | 14.61 | 16.62 | mA    | VDDO= 2.5V+5% |

#### Table 5 Input Characteristics\*

|    | Characteristics                                                                                         | Sym.                          | Min.                     | Тур. | Max.                   | Units | Notes                          |

|----|---------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------|------|------------------------|-------|--------------------------------|

| 1a | CMOS high-level input voltage for control inputs                                                        | V <sub>CIH_3.3V</sub>         | 0.7 *<br>V <sub>DD</sub> |      |                        | V     | $V_{DD} = 3.3 V$               |

| 1b | CMOS high-level input voltage for control inputs                                                        | V <sub>CIH_2.5V</sub>         | 0.8 *<br>V <sub>DD</sub> |      |                        | V     | $V_{DD} = 2.5 V$               |

| 2  | CMOS low-level input voltage for control inputs                                                         | VcIL                          |                          |      | 0.32 * V <sub>DD</sub> | V     |                                |

| 3  | CMOS input leakage current for control inputs (includes current due to pull down resistors)             | ΙL                            | -25                      |      | 50                     | μA    | $V_{I} = V_{DD} \text{ or } 0$ |

| 4  | Differential input common mode voltage for IN_p/n                                                       | V <sub>см</sub>               | 0.1                      |      | 0.8                    | V     |                                |

| 5  | Differential input voltage for IN_p/n                                                                   | VID                           | 0.2                      |      | V <sub>DD</sub> + 0.3  | V     |                                |

| 6  | Differential input leakage current for IN_p/n (includes current due to pull-up and pull-down resistors) | ΙL                            | -150                     |      | 150                    | μA    | $V_1 = 2V \text{ or } 0V$      |

| 7  | Single ended input voltage for IN_p                                                                     | Vsi                           | -0.3                     |      | 2.7                    | V     | VDD = 3.3V<br>or 2.5V          |

| 8  | Single ended input common mode voltage IN_p                                                             | V <sub>SIC</sub>              | 0.1                      |      | 0.8                    | V     | VDD = 3.3V<br>or 2.5V          |

| 9  | Single ended input voltage swing for IN_p                                                               | V <sub>SID</sub>              | 0.3                      |      | 1.3                    | V     | VDD = 3.3V<br>or 2.5V          |

| 10 | Input frequency (differential)                                                                          | f <sub>IN</sub>               | 0                        |      | 400                    | MHz   |                                |

| 11 | Input duty cycle                                                                                        | dc                            | 35%                      |      | 65%                    |       |                                |

| 13 | Input slew rate                                                                                         | slew                          | 0.6                      | 2    |                        | V/ns  |                                |

| 14 | Input pull-up/ pull-down resistance                                                                     | $R_{\text{PU}}/R_{\text{PD}}$ |                          | 60   |                        | kΩ    |                                |

| 15 | Input pull-down resistance for IN_p                                                                     | R <sub>PD</sub>               |                          | 30   |                        | kΩ    |                                |

| 16 | Control input (OE_b) pull-down resistance                                                               | R <sub>PDOE</sub>             |                          | 300  |                        | kΩ    |                                |

$^*$  Values are over Recommended Operating Conditions  $^*$  Values are over all two power supply modes (V\_{DD} = 3.3V and V\_{DD} = 2.5V) (1) low frequency only

#### Table 6 Power Supply Rejection Ratio for VDD = VDDO = 3.3V\*

|   | Characteristics      | Sym.                 | Min. | Тур.  | Max. | Units | Notes                      |

|---|----------------------|----------------------|------|-------|------|-------|----------------------------|

|   |                      |                      |      | -80.7 |      |       | $f_{IN} = 100 \text{ MHz}$ |

| 1 | PSRR for HCSL output | PSRR <sub>HCSL</sub> |      | -76.4 |      | dBc   | f <sub>IN</sub> = 133 MHz  |

|   |                      |                      |      | -66.5 |      |       | $f_{IN} = 400 \text{ MHz}$ |

\* Values are over Recommended Operating Conditions

\* Noise injected to VDD/VDDO power supply with frequency 100 kHz and amplitude 100 mVpp

\* PSRR is measured as amplitude of 100 kHz spur in dBc on the output clock phase noise plot

|   | Characteristics      | Sym.     | Min. | Тур.  | Max. | Units | Notes                      |

|---|----------------------|----------|------|-------|------|-------|----------------------------|

|   |                      |          |      | -73.5 |      |       | $f_{IN} = 100 \text{ MHz}$ |

| 3 | PSRR for HCSL output | PSRRHCSL |      | -69.8 |      | dBc   | f <sub>IN</sub> = 133 MHz  |

|   |                      |          |      | -61.2 |      |       | $f_{IN} = 400 \text{ MHz}$ |

# Table 7 Power Supply Rejection Ratio for VDD = VDDO = 2.5V\*

\* Values are over Recommended Operating Conditions

\* Noise injected to VDD/VDDO power supply with frequency 100 kHz and amplitude 100 mVpp

\* PSRR is measured as amplitude of 100 kHz spur in dBc on the output clock phase noise plot

| ing edge rate<br>iing edge rate<br>erential High Voltage<br>erential Low Voltage<br>gle ended high voltage<br>gle ended low voltage<br>solute Crossing Voltage<br>iation of V <sub>CROSS</sub> over all rising clock edges<br>g back voltage margin | Rise_rate       Fall_rate       VIH       VIL       VSIH       VSIL       VCROSS       ΔVCROSS                                                        | 1.3<br>1.3<br>0.6<br>-0.9<br>0.6<br>-0.01<br>0.26                                                                                                                                                                                                                                   | 1.7<br>1.7<br>0.74<br>0                                                                                                                                                                                                                                                                                                        | 2<br>2<br>0.9<br>-0.6<br>0.85                                                                                                                                                                                                                                                                                                                                             | V/ns<br>V/ns<br>V<br>V<br>V                                                                                                                                                                                                                                                                                                                                                                                     | (2), (3)<br>(2), (3)<br>(2)<br>(2)<br>(2)                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| erential High Voltage<br>erential Low Voltage<br>gle ended high voltage<br>gle ended low voltage<br>solute Crossing Voltage<br>iation of V <sub>CROSS</sub> over all rising clock edges<br>g back voltage margin                                    | VIH<br>VIL<br>VSIH<br>VSIL<br>VCROSS<br>ΔVCROSS                                                                                                       | 0.6<br>-0.9<br>0.6<br>-0.01<br>0.26                                                                                                                                                                                                                                                 | 0.74                                                                                                                                                                                                                                                                                                                           | 0.9<br>-0.6<br>0.85                                                                                                                                                                                                                                                                                                                                                       | V<br>V                                                                                                                                                                                                                                                                                                                                                                                                          | (2) (2)                                                                                                                                                                                                                                   |

| erential Low Voltage<br>gle ended high voltage<br>gle ended low voltage<br>solute Crossing Voltage<br>iation of V <sub>CROSS</sub> over all rising clock edges<br>g back voltage margin                                                             | V <sub>IL</sub><br>V <sub>SIH</sub><br>V <sub>SIL</sub><br>V <sub>CROSS</sub>                                                                         | -0.9<br>0.6<br>-0.01<br>0.26                                                                                                                                                                                                                                                        | -                                                                                                                                                                                                                                                                                                                              | -0.6<br>0.85                                                                                                                                                                                                                                                                                                                                                              | V                                                                                                                                                                                                                                                                                                                                                                                                               | (2)                                                                                                                                                                                                                                       |

| gle ended high voltage<br>gle ended low voltage<br>solute Crossing Voltage<br>iation of V <sub>CROSS</sub> over all rising clock edges<br>g back voltage margin                                                                                     | Vsih<br>Vsil<br>Vcross<br>AVcross                                                                                                                     | 0.6<br>-0.01<br>0.26                                                                                                                                                                                                                                                                | -                                                                                                                                                                                                                                                                                                                              | 0.85                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                           |

| gle ended low voltage<br>solute Crossing Voltage<br>iation of V <sub>CROSS</sub> over all rising clock edges<br>g back voltage margin                                                                                                               | Vsil<br>Vcross<br>AVcross                                                                                                                             | -0.01<br>0.26                                                                                                                                                                                                                                                                       | -                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                           | V                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                           |

| solute Crossing Voltage<br>iation of V <sub>CROSS</sub> over all rising clock edges<br>g back voltage margin                                                                                                                                        | V <sub>CROSS</sub><br>ΔV <sub>CROSS</sub>                                                                                                             | 0.26                                                                                                                                                                                                                                                                                | 0                                                                                                                                                                                                                                                                                                                              | 0.01                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                 | DC Measurement                                                                                                                                                                                                                            |

| iation of V <sub>CROSS</sub> over all rising clock edges<br>g back voltage margin                                                                                                                                                                   | $\Delta V_{CROSS}$                                                                                                                                    |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                | 0.01                                                                                                                                                                                                                                                                                                                                                                      | V                                                                                                                                                                                                                                                                                                                                                                                                               | DC Measurement                                                                                                                                                                                                                            |

| g back voltage margin                                                                                                                                                                                                                               |                                                                                                                                                       |                                                                                                                                                                                                                                                                                     | 0.32                                                                                                                                                                                                                                                                                                                           | 0.38                                                                                                                                                                                                                                                                                                                                                                      | V                                                                                                                                                                                                                                                                                                                                                                                                               | (1), (4), (5)                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                     |                                                                                                                                                       | 0.039                                                                                                                                                                                                                                                                               | 0.050                                                                                                                                                                                                                                                                                                                          | 0.061                                                                                                                                                                                                                                                                                                                                                                     | V                                                                                                                                                                                                                                                                                                                                                                                                               | (1), (4), (9)                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                     | VRB                                                                                                                                                   | 0.534                                                                                                                                                                                                                                                                               | 0.674                                                                                                                                                                                                                                                                                                                          | 0.809                                                                                                                                                                                                                                                                                                                                                                     | V                                                                                                                                                                                                                                                                                                                                                                                                               | (2), (11)                                                                                                                                                                                                                                 |

| ne before V <sub>RB</sub> is allowed                                                                                                                                                                                                                | <b>t</b> STABLE                                                                                                                                       | 4.6                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                           | ns                                                                                                                                                                                                                                                                                                                                                                                                              | (2), (11)                                                                                                                                                                                                                                 |

| cle-to-cycle additive jitter                                                                                                                                                                                                                        | T <sub>JCC</sub>                                                                                                                                      |                                                                                                                                                                                                                                                                                     | 6.5                                                                                                                                                                                                                                                                                                                            | 8.1                                                                                                                                                                                                                                                                                                                                                                       | ps<br>peak to<br>peak                                                                                                                                                                                                                                                                                                                                                                                           | (2)                                                                                                                                                                                                                                       |

| solute Maximum voltage                                                                                                                                                                                                                              | V <sub>MAX</sub>                                                                                                                                      |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                | 0.92                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                 | (1), (7)                                                                                                                                                                                                                                  |

| solute Minimum voltage                                                                                                                                                                                                                              | V <sub>MIN</sub>                                                                                                                                      | -0.05                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                 | (1), (8)                                                                                                                                                                                                                                  |

| tput Duty-Cycle (when input has 50% duty-cycle)                                                                                                                                                                                                     | Duty_cycle                                                                                                                                            | 48                                                                                                                                                                                                                                                                                  | 50                                                                                                                                                                                                                                                                                                                             | 52                                                                                                                                                                                                                                                                                                                                                                        | %                                                                                                                                                                                                                                                                                                                                                                                                               | (2)                                                                                                                                                                                                                                       |

| ing to falling edge matching                                                                                                                                                                                                                        | r/f match                                                                                                                                             |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                | 15                                                                                                                                                                                                                                                                                                                                                                        | %                                                                                                                                                                                                                                                                                                                                                                                                               | (1), (12)                                                                                                                                                                                                                                 |

| ck Source DC impedance (CK)                                                                                                                                                                                                                         | Z <sub>C-DC_CK</sub>                                                                                                                                  | 49                                                                                                                                                                                                                                                                                  | 50                                                                                                                                                                                                                                                                                                                             | 51                                                                                                                                                                                                                                                                                                                                                                        | Ω                                                                                                                                                                                                                                                                                                                                                                                                               | DC Measurement<br>(1), (13)                                                                                                                                                                                                               |

| ck Source DC impedance (CK#)                                                                                                                                                                                                                        | Zc-dc_ck#                                                                                                                                             | 49                                                                                                                                                                                                                                                                                  | 50                                                                                                                                                                                                                                                                                                                             | 51                                                                                                                                                                                                                                                                                                                                                                        | Ω                                                                                                                                                                                                                                                                                                                                                                                                               | DC Measurement<br>(1), (13)                                                                                                                                                                                                               |

| tput frequency                                                                                                                                                                                                                                      | FMAX                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                | 400                                                                                                                                                                                                                                                                                                                                                                       | MHz                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                           |

| tput to output skew                                                                                                                                                                                                                                 | t <sub>ооsк</sub>                                                                                                                                     |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                | 50                                                                                                                                                                                                                                                                                                                                                                        | ps                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                           |

| vice to device output skew                                                                                                                                                                                                                          | tdoosk                                                                                                                                                |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                | 129                                                                                                                                                                                                                                                                                                                                                                       | ps                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                     | tiop                                                                                                                                                  | 0.75                                                                                                                                                                                                                                                                                | 0.84                                                                                                                                                                                                                                                                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                         | ns                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                           |

| ut to output delay                                                                                                                                                                                                                                  |                                                                                                                                                       |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                | 3                                                                                                                                                                                                                                                                                                                                                                         | cycles                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                           |

| ut to output delay<br>iput enable time                                                                                                                                                                                                              | t <sub>EN</sub>                                                                                                                                       |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                                                                                                                                                                                         |