# ZL40241

# Ten LVCMOS Output Low Additive Jitter Fanout Buffer

#### Features

- 3-to-1 Input Multiplexer: Two Inputs Accept Any Differential (LVPECL, HCSL, LVDS, SSTL, CML, LVCMOS) or a Single Ended Signal and the Third Input Accepts a Crystal or a Single Ended Signal

- Ten 1.5V/1.8V/2.5V/3.3V LVCMOS Outputs

- Supports Frequencies from 0 MHz to 200 MHz

- Supports Crystals from 8 MHz to 60 MHz

- Ultra-Low Additive Jitter: 17 fs (12 kHz to 20 MHz)

- Ultra-Low Noise Floor of -170 dBc/Hz

- Supports 2.5V or 3.3V Power Supplies

- Output to Output Skew of 30 ps (Typical)

- Input to Output Delay of 2 ns (Typical)

#### Applications

- General Purpose Clock Distribution

- Low Jitter Clock Trees

- Logic Translation

- Clock and Data Signal Restoration

- Wired and Wireless Communications

- High Performance Microprocessor Clock Distribution

- Medical Imaging

- Test Equipment

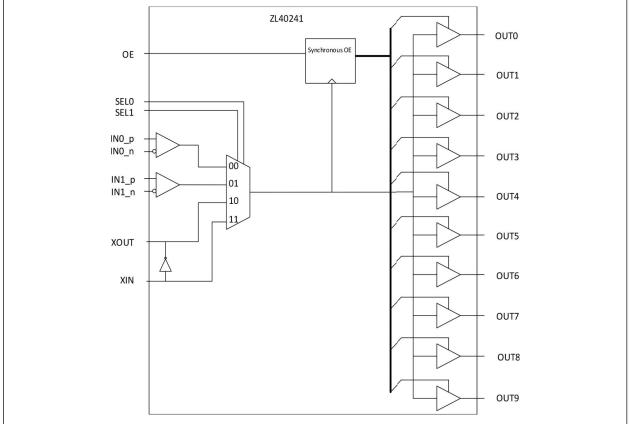

FIGURE 0-1: Functional Block Diagram.

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

- To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# TABLE OF CONTENTS

| 1.0"Pin Description and Configuration"        | 6 |

|-----------------------------------------------|---|

| 2.0"Functional Description"                   | 9 |

| 2.1"Clock Inputs"                             |   |

| 2.2"Clock Outputs"                            |   |

| 2.3"Crystal Oscillator Input"                 |   |

| 2.4"Termination of Unused Inputs and Outputs" |   |

| 2.5"Power Consumption"                        |   |

| 2.6"Power Supply Filtering"                   |   |

| 2.7"Device Control"                           |   |

| 3.0"Electrical Characteristics"               |   |

| 4.0"Package Outline"                          |   |

| Appendix A:"Data Sheet Revision History"      |   |

| "Product Identification System"               |   |

| "Microchip Information"                       |   |

# List of Figures

| FIGURE 0-1:"Functional Block Diagram."                                                  | 1  |

|-----------------------------------------------------------------------------------------|----|

| FIGURE 1-1:"32-Lead 3.10 mm × 3.10 mm VQFN with E-Pad."                                 |    |

| FIGURE 2-1:"Input Driven by a Single-Ended Output."                                     |    |

| FIGURE 2-2:"Input Driven by DC-Coupled LVPECL Output."                                  | 9  |

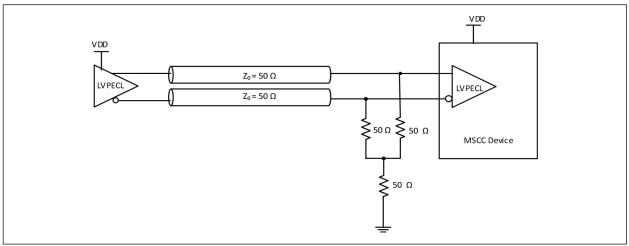

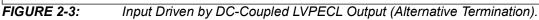

| FIGURE 2-3:"Input Driven by DC-Coupled LVPECL Output (Alternative Termination)."        | 10 |

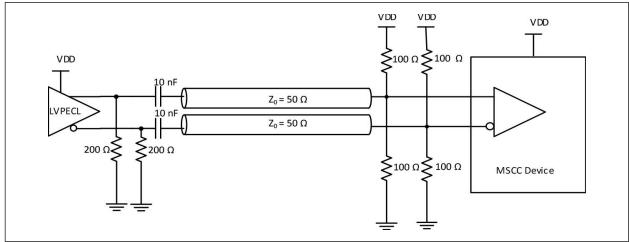

| FIGURE 2-4:"Input Driven by AC-Coupled LVPECL Output."                                  | 10 |

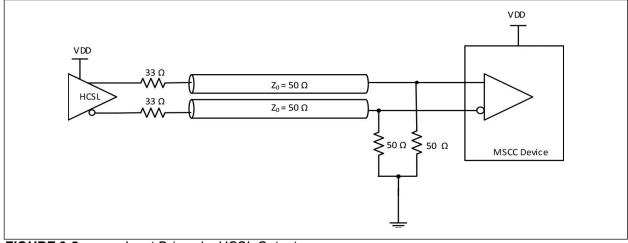

| FIGURE 2-5:"Input Driven by HCSL Output."                                               | 10 |

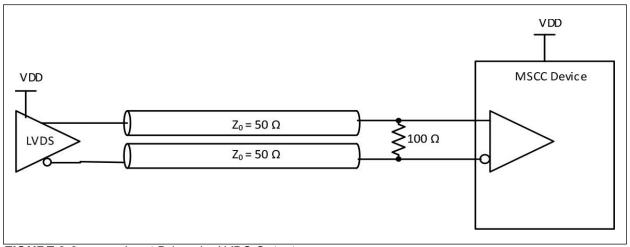

| FIGURE 2-6:"Input Driven by LVDS Output."                                               |    |

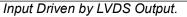

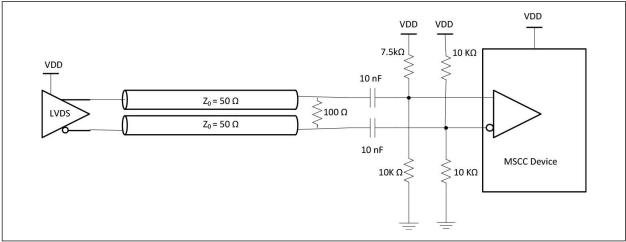

| FIGURE 2-7:"Input Driven by AC-Coupled LVDS."                                           | 11 |

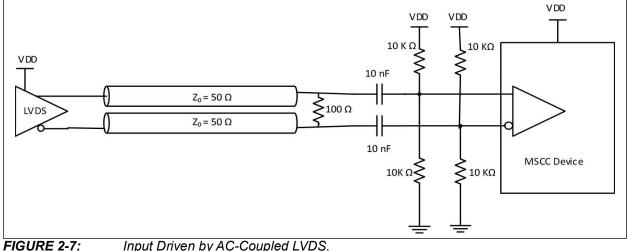

| FIGURE 2-8:"Input Driven by an SSTL Output."                                            |    |

| FIGURE 2-9:"Termination for LVCMOS Outputs."                                            | 12 |

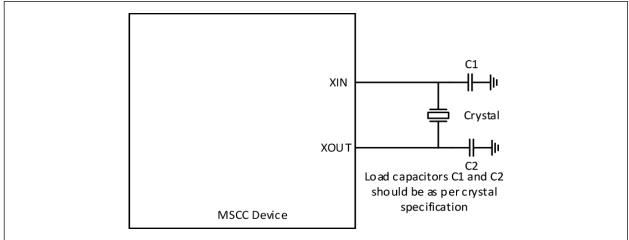

| FIGURE 2-10:"Crystal Oscillator Circuit in Hardware Controlled Mode."                   | 12 |

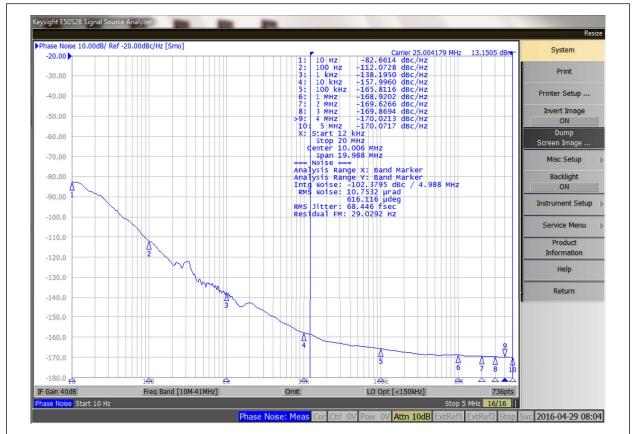

| FIGURE 2-11:"Phase Noise Plot with 25 MHz Crystal."                                     | 13 |

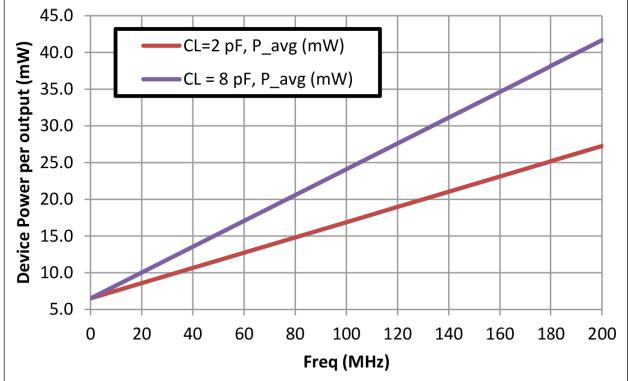

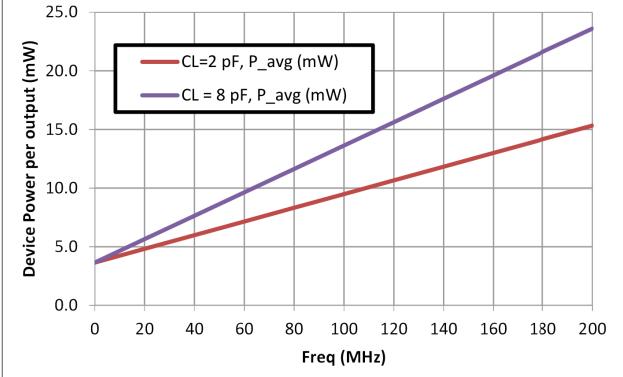

| FIGURE 2-12:"Device Power Consumption per Output for V <sub>DD = VDDO = 3.465V.</sub> " | 14 |

| FIGURE 2-13:"Device Power Consumption per Output for V <sub>DD</sub> = VDDO = 2.625V."  | 14 |

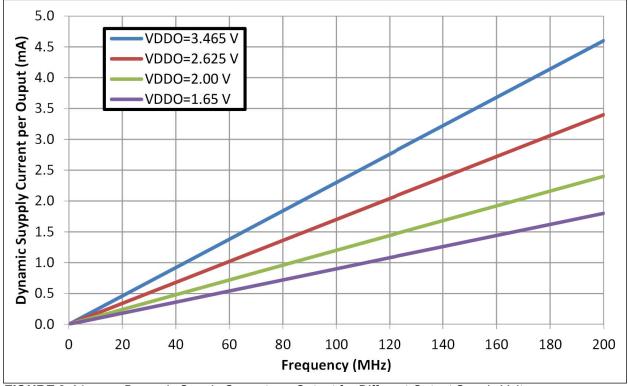

| FIGURE 2-14: "Dynamic Supply Current per Output for Different Output Supply Voltages."  | 15 |

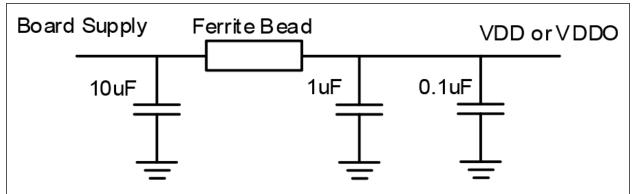

| FIGURE 2-15:"Power Supply Filtering."                                                   | 15 |

|                                                                                         |    |

# **List of Tables**

| TABLE 1-1:"Pin Descriptions"                                           | 7 |

|------------------------------------------------------------------------|---|

| TABLE 3-1:"Absolute Maximum Ratings (Note 1, Note 2, Note 3)"          |   |

| TABLE 3-2:"Recommended Operating Conditions (Note 1, Note 2)"          |   |

| TABLE 3-3: "Current Consumption"                                       |   |

| TABLE 3-4: "Input Characteristics (Note 1, Note 2)"                    |   |

| TABLE 3-5: "Crystal Oscillator Characteristics (Note 1)"               |   |

| TABLE 3-6: "LVCMOS Output Characteristics (Note 1)"                    |   |

| TABLE 3-7: "LVCMOS Output Additive Jitter and Phase Noise (Note 1)"    |   |

| TABLE 3-8:"LVCMOS Output Jitter Phase Noise with 25 MHz XTAL (Note 1)" |   |

| TABLE 3-9:"5 mm × 5 mm VQFN Package Thermal Properties"                |   |

| TABLE A-1:"Revision History"                                           |   |

|                                                                        |   |

#### 1.0 PIN DESCRIPTION AND CONFIGURATION

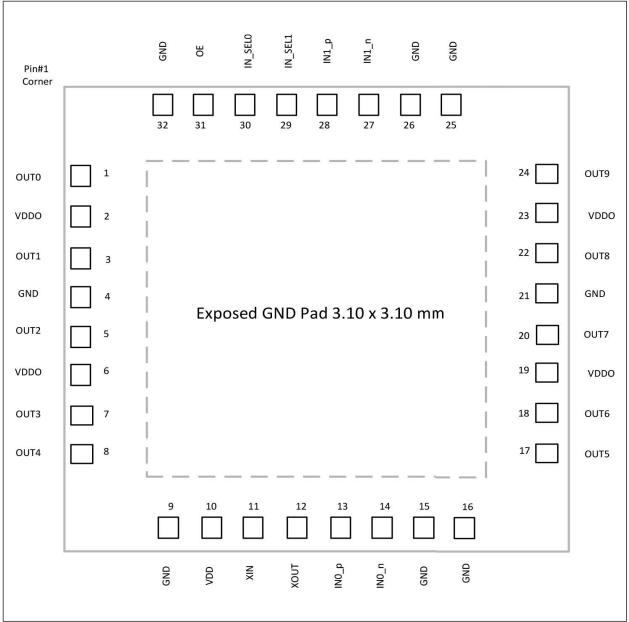

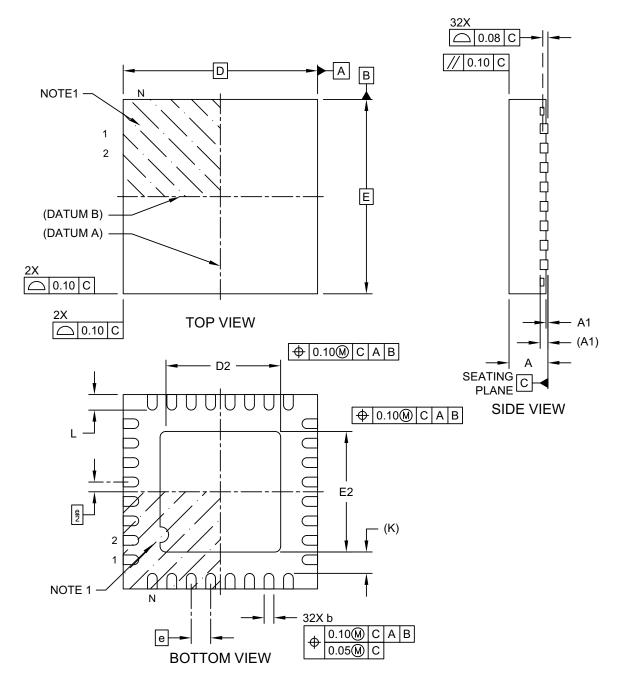

The device is packaged in a 5 mm × 5 mm 32-lead VQFN.

FIGURE 1-1:

32-Lead 3.10 mm × 3.10 mm VQFN with E-Pad.

All device inputs and outputs are LVPECL unless described otherwise. The I/O column uses the following symbols: I – input,  $I_{PU}$  – input with 300 k $\Omega$  internal pull-up resistor,  $I_{PD}$  – input with 300 k $\Omega$  internal pull-down resistor,  $I_{APU}$  – input with 30 k $\Omega$  internal pull-up resistor,  $I_{APD}$  – input with 30 k $\Omega$  internal pull-up resistor,  $I_{APD}$  – input with 30 k $\Omega$  internal pull-up resistor,  $I_{APD}$  – input with 30 k $\Omega$  internal pull-up resistor,  $I_{APD}$  – input with 30 k $\Omega$  internal pull-up resistor,  $I_{APD}$  – input with 30 k $\Omega$  internal pull-up resistor,  $I_{APD}$  – input with 30 k $\Omega$  internal pull-up resistor,  $I_{APD}$  – input with 30 k $\Omega$  internal pull-up resistor,  $I_{APD}$  – input with 30 k $\Omega$  internal pull-up resistor,  $I_{APD}$  – input biased at VDD/2 with 60 k $\Omega$  internal pull-up and 60 k $\Omega$  pull-down resistors, O – output, I/O – Input/Output pin, P – power supply pin.

| Pin<br>Number | Pin Name | Туре                 | Description                                                                                                                                                                                                                                                                                                           |                                                                                            |                                                      |  |  |  |  |  |

|---------------|----------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------|--|--|--|--|--|

| Input Refer   | ences    |                      |                                                                                                                                                                                                                                                                                                                       |                                                                                            |                                                      |  |  |  |  |  |

| 13            | IN0_p    | I <sub>APD</sub>     | Input Differential or Si                                                                                                                                                                                                                                                                                              | Input Differential or Single Ended References 0 and 1                                      |                                                      |  |  |  |  |  |

| 14            | IN0_n    | I <sub>APU/APD</sub> |                                                                                                                                                                                                                                                                                                                       |                                                                                            |                                                      |  |  |  |  |  |

| 28            | IN1_p    | I <sub>APD</sub>     | Input frequency range (                                                                                                                                                                                                                                                                                               | Input frequency range 0 Hz to 200 MHz.                                                     |                                                      |  |  |  |  |  |

| 27            | IN1_n    | I <sub>APU/APD</sub> | Non inverting inputs (_p) are pulled down with internal 30 k $\Omega$ pull-down resistors. Inverting inputs (_n) are biased at VDD/2 with 60 k $\Omega$ pull-up and pull-down resistors to keep inverting input voltages at VDD/2 when inverting inputs are left floating (device fed with a single ended reference). |                                                                                            |                                                      |  |  |  |  |  |

| Output Clo    | cks      |                      |                                                                                                                                                                                                                                                                                                                       |                                                                                            |                                                      |  |  |  |  |  |

| 1             | OUT0     |                      |                                                                                                                                                                                                                                                                                                                       |                                                                                            |                                                      |  |  |  |  |  |

| 3             | OUT1     |                      |                                                                                                                                                                                                                                                                                                                       |                                                                                            |                                                      |  |  |  |  |  |

| 5             | OUT2     |                      |                                                                                                                                                                                                                                                                                                                       |                                                                                            |                                                      |  |  |  |  |  |

| 7             | OUT3     |                      |                                                                                                                                                                                                                                                                                                                       |                                                                                            |                                                      |  |  |  |  |  |

| 8             | OUT4     | 0                    | Ultra Low Additive Jit                                                                                                                                                                                                                                                                                                | Ultra Low Additive Jitter LVCMOS Outputs 0 to 9<br>Output frequency range 0 Hz to 200 MHz. | 0 to 9                                               |  |  |  |  |  |

| 17            | OUT5     | 0                    | Output frequency range                                                                                                                                                                                                                                                                                                |                                                                                            |                                                      |  |  |  |  |  |

| 18            | OUT6     |                      |                                                                                                                                                                                                                                                                                                                       |                                                                                            |                                                      |  |  |  |  |  |

| 20            | OUT7     |                      |                                                                                                                                                                                                                                                                                                                       |                                                                                            |                                                      |  |  |  |  |  |

| 22            | OUT8     |                      |                                                                                                                                                                                                                                                                                                                       |                                                                                            |                                                      |  |  |  |  |  |

| 24            | OUT9     |                      |                                                                                                                                                                                                                                                                                                                       |                                                                                            |                                                      |  |  |  |  |  |

| Control       | •        |                      |                                                                                                                                                                                                                                                                                                                       |                                                                                            |                                                      |  |  |  |  |  |

|               |          |                      | Input Select Pins. Log passed to the output.                                                                                                                                                                                                                                                                          | ic level on these pins s                                                                   | elects which input will be                           |  |  |  |  |  |

|               |          |                      | IN_SEL1                                                                                                                                                                                                                                                                                                               | IN_SEL0                                                                                    | OUTN                                                 |  |  |  |  |  |

| 30            | IN_SEL0  |                      | 0                                                                                                                                                                                                                                                                                                                     | 0                                                                                          | Input 0 (IN0)                                        |  |  |  |  |  |

| 29            | IN_SEL1  | I <sub>PD</sub>      | 0                                                                                                                                                                                                                                                                                                                     | 1                                                                                          | Input 1 (IN1)                                        |  |  |  |  |  |

|               |          |                      | 1                                                                                                                                                                                                                                                                                                                     | 0                                                                                          | Crystal Oscillator or<br>Overdrive                   |  |  |  |  |  |

|               |          |                      | 1                                                                                                                                                                                                                                                                                                                     | 1                                                                                          | Crystal Bypass                                       |  |  |  |  |  |

| 31            | OE       | I <sub>PD</sub>      | Output Enable. When high-Z.                                                                                                                                                                                                                                                                                           | high outputs are enabl                                                                     | ed. When low outputs are                             |  |  |  |  |  |

| Crystal Osc   | illator  |                      | -                                                                                                                                                                                                                                                                                                                     |                                                                                            |                                                      |  |  |  |  |  |

| 11            | XIN      | I                    | Crystal Oscillator Inpu<br>drive Mode. If crystal o<br>it to ground.                                                                                                                                                                                                                                                  |                                                                                            | Mode or Crystal Over-<br>Il down this pin or connect |  |  |  |  |  |

| 12            | XOUT     | 0                    | Crystal Oscillator Output.                                                                                                                                                                                                                                                                                            |                                                                                            |                                                      |  |  |  |  |  |

| Power and     | Ground   |                      | -                                                                                                                                                                                                                                                                                                                     |                                                                                            |                                                      |  |  |  |  |  |

| 10            | VDD      | Р                    | Positive Supply Voltage must be higher or equa                                                                                                                                                                                                                                                                        |                                                                                            | 2.5V supply. VDD voltage                             |  |  |  |  |  |

TABLE 1-1: PIN DESCRIPTIONS

| Pin<br>Number | Pin Name | Туре | Description                                                     |

|---------------|----------|------|-----------------------------------------------------------------|

| 2             |          |      |                                                                 |

| 6             | VDDO     | Р    | Positive Supply Voltage for LVCMOS Outputs. Connect 3.3V, 2.5V, |

| 19            |          | F    | 1.8V or 1.5V power supply.                                      |

| 23            |          |      |                                                                 |

| 4             |          |      |                                                                 |

| 9             |          |      |                                                                 |

| 15            |          |      |                                                                 |

| 16            |          |      |                                                                 |

| 21            | GND      | Р    | Ground. Connect to ground.                                      |

| 25            |          |      |                                                                 |

| 26            |          |      |                                                                 |

| 32            |          |      |                                                                 |

| E-Pad         |          |      |                                                                 |

#### TABLE 1-1: PIN DESCRIPTIONS (CONTINUED)

#### 2.0 FUNCTIONAL DESCRIPTION

The ZL40241 is a programmable or hardware pin controlled low additive jitter, low power 3 × 10 LVCMOS fanout buffer.

Two inputs can accept signal in differential (LVPECL, SSTL, LVDS, HSTL, CML) or single ended (LVPECL or LVCMOS) format and the third input can accept a single ended signal or it can be used to build a crystal oscillator by connecting an external crystal resonator between its XIN and XOUT pins.

The ZL40241 has ten LVCMOS outputs which can be powered from 3.3V, 2.5V, 1.8V, or 1.5V supply. Output can be synchronously enabled/disabled via OE pin.

The device operates from 2.5V+/-5% or 3.3V+/-5% supply. Its operation is guaranteed over the industrial temperature range -40°C to +85°C.

#### 2.1 Clock Inputs

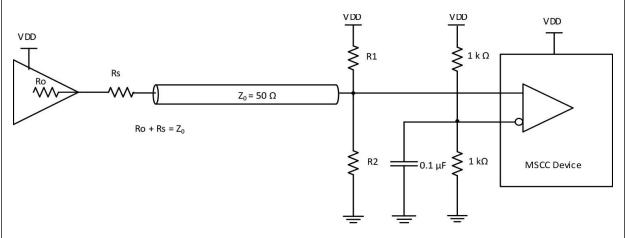

The following block diagrams show how to terminate different signals fed to the ZL40241 inputs. Figure 2-1 shows how to terminate a single ended output such as LVCMOS. Ideally, resistors R1 and R2 should be  $100\Omega$  each so that the transmission line is terminated with matched impedance (50 $\Omega$ ). However, if the driving strength of the output driver is not sufficient resistor values should be increased.

FIGURE 2-1: Input Driven by a Single-Ended Output.

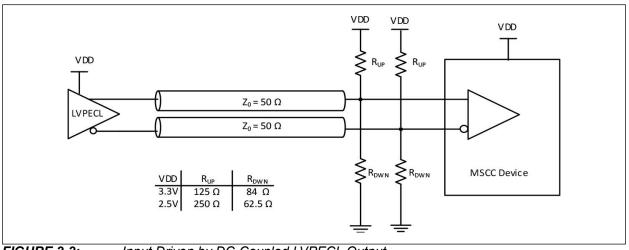

FIGURE 2-2:

Input Driven by DC-Coupled LVPECL Output.

FIGURE 2-4: Input Driven by AC-Coupled LVPECL Output.

FIGURE 2-5: Input Driven by HCSL Output.

Input Driven by AC-Coupled LVDS.

#### 2.2 Clock Outputs

LVCMOS outputs require only series termination resistor whose value is depending on LVCMOS output voltage as shown in Figure 2-9.

FIGURE 2-9: Termination for LVCMOS Outputs.

#### 2.3 Crystal Oscillator Input

The crystal oscillator circuit can work with crystal resonators from 8 MHz to 160 MHz. Load capacitors C1 and C2 shall be selected as per crystal vendor recommendation. Shunt resistor is implemented inside the device. If the crystal is not used, connect XIN pin to ground.

FIGURE 2-10: Crystal Oscillator Circuit in Hardware Controlled Mode.

The phase noise plot for 25 MHz crystal is shown in Figure 2-11. The phase noise floor of the device is below 170 dBc/Hz as can be seen on the figure.

FIGURE 2-11: Phase Noise Plot with 25 MHz Crystal.

#### 2.4 Termination of Unused Inputs and Outputs

Unused inputs can be left unconnected or alternatively IN\_0/1 can be pulled-down by 1 K $\Omega$  resistor. Unused outputs should be left unconnected.

#### 2.5 **Power Consumption**

The total device power consumption can be calculated as:

#### EQUATION 2-1:

$$P_T = P_S + P_{XTAL} + P_C + P_L$$

| Where: |  |

|--------|--|

|--------|--|

| $P_{S} = V_{DD} \times I_{S}$                                                                                    | This is static power consumed by input buffers. If XTAL is running, this power should be set to zero. The static current $(I_S)$ is specified in Table 3-2.                                        |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $P_{XTAL} = V_{DD} \times I_{DD_{XTAL}}$                                                                         | This is the power consumption of the XTAL circuit. The current of the XTAL circuit is provided in Table 3-2. If XTAL is not used, the power consumption is equal to zero.                          |

| $P_{C} = V_{DDO} \times I_{DDC}$                                                                                 | Common output power shared among all ten outputs. The current $I_{\text{DDC}}$ is specified in Table 3-2.                                                                                          |

| $P_{D} = V_{DDO} \times (I_{DD} \times n \times f / 100 \text{ MHz} + V_{DD} \times C_{LOAD} \times f \times n)$ | Dynamic power where dynamic current $(I_{DD})$ is specified in Table 3-2. $C_{LOAD}$ is capacitive load driven by an output, f is frequency of hte output clock and n is number of active outputs. |

The power consumption for different clock frequencies and power supply voltages can be quickly estimated from Figure 2-12, Figure 2-13, and Figure 2-14.

**FIGURE 2-12:** Device Power Consumption per Output for  $V_{DD} = V_{DDO} = 3.465V$ .

**FIGURE 2-13:** Device Power Consumption per Output for  $V_{DD} = V_{DDO} = 2.625V$ .

FIGURE 2-14: Dynamic Supply Current per Output for Different Output Supply Voltages.

#### 2.6 Power Supply Filtering

Each power pin (VDD and VDDO) should be decoupled with 0.1 µF capacitor with minimum equivalent series resistance (ESR) and minimum series inductance (ESL). For example, 0402 X5R Ceramic Capacitors with 6.3V minimum rating could be used. These capacitors should be placed as close as possible to the power pins. To reduce the power noise from adjacent digital components on the board, each power supply could be further insulated with low resistance ferrite bead with two capacitors. The ferrite bead will also insulate adjacent component from the noise generated from the device. Figure 2-15 shows the recommended decoupling for each power pin.

FIGURE 2-15: Power Supply Filtering.

#### 2.7 Device Control

ZL30241 is controlled via Output Enable (OE) and Input Select (SEL0/1) input pins.

NOTES:

# 3.0 ELECTRICAL CHARACTERISTICS

#### TABLE 3-1: ABSOLUTE MAXIMUM RATINGS (Note 1, Note 2, Note 3)

| Parameter                 | Symbol                            | Min. | Max.   | Units |

|---------------------------|-----------------------------------|------|--------|-------|

| Supply voltage, 3.3V      | V <sub>DD</sub> /V <sub>DDO</sub> | -0.5 | +4.6   | V     |

| Supply voltage, 2.5V      | V <sub>DD</sub> /V <sub>DDO</sub> | -0.5 | +4.6   | V     |

| Supply voltage, 1.8V      | V <sub>DDO</sub>                  | -0.5 | +2.5   | V     |

| Supply voltage, 1.5V      | V <sub>DDO</sub>                  | -0.5 | +2.0   | V     |

| Storage temperature range | T <sub>ST</sub>                   | -55  | +125.0 | °C    |

Note 1: Exceeding these values may cause permanent damage.

2: Functional operation under these conditions is not implied.

**3:** Voltages are with respect to ground (GND) unless otherwise stated.

#### TABLE 3-2: RECOMMENDED OPERATING CONDITIONS (Note 1, Note 2)

| Parameter             | Symbol                            | Min.    | Тур.    | Max.                    | Units |

|-----------------------|-----------------------------------|---------|---------|-------------------------|-------|

| Supply voltage, 3.3V  | V <sub>DD</sub> /V <sub>DDO</sub> | 3.135   | 3.300   | 3.465                   | V     |

| Supply voltage, 2.5V  | V <sub>DD</sub> /V <sub>DDO</sub> | 2.375   | 2.500   | 2.625                   | V     |

| Supply voltage, 1.8V  | V <sub>DDO</sub>                  | 1.600   | 1.800   | 2.000                   | V     |

| Supply voltage, 1.5V  | V <sub>DDO</sub>                  | 1.350   | 1.500   | 1.650                   | V     |

| Operating temperature | T <sub>A</sub>                    | -40.000 | +25.000 | +85.000                 | °C    |

| Input voltage         | V <sub>DD-IN</sub>                | -0.300  |         | V <sub>DD</sub> + 0.300 | V     |

Note 1: Voltages are with respect to ground (GND) unless otherwise stated.

**2:** The device supports two power supply modes (3.3V and 2.5V).

#### TABLE 3-3:CURRENT CONSUMPTION

| Characteristics                                                                                        | Symbol                   | Min. | Тур. | Max. | Units | Notes                    |

|--------------------------------------------------------------------------------------------------------|--------------------------|------|------|------|-------|--------------------------|

| Static device current                                                                                  | I <sub>S_3.3V</sub>      | —    | 15   | 18   | mA    | V <sub>DD</sub> = 3.465V |

|                                                                                                        | I <sub>S_2.5V</sub>      | —    | 12   | 15   | mA    | V <sub>DD</sub> = 2.625V |

| Device current with 25 MHz XTAL input                                                                  | IDD_XTAL_3.3V            | —    | 24   | 27   | mA    | V <sub>DD</sub> = 3.465V |

|                                                                                                        | IDD_XTAL_2.5V            | _    | 18   | 20   | mA    | V <sub>DD</sub> = 2.625V |

| Dynamic current per output (f = 100MHz),                                                               | I <sub>DD_3.3V</sub>     | —    | 4.2  | 4.7  | mA    | V <sub>DD</sub> = 3.465V |

| Note 1, Note 2                                                                                         | I <sub>DD_2.5V</sub>     | —    | 3.0  | 3.5  | mA    | V <sub>DD</sub> = 2.625V |

| Needs to be scaled for different frequen-<br>cies by f/100 MHz, Driving Strength = 1                   | I <sub>DD_1.8V</sub>     | —    | 2.1  | 2.4  | mA    | V <sub>DD</sub> = 2.000V |

| (registers 0x09, 0x0A)                                                                                 | I <sub>DD_1.5V</sub>     | —    | 1.6  | 1.8  | mA    | V <sub>DD</sub> = 1.650V |

| Dynamic current per output (f = 100MHz),                                                               | I <sub>DD_3.3V</sub>     | —    | 2.3  | 3.0  | mA    | V <sub>DD</sub> = 3.465V |

| Note 1, Note 2<br>Needs to be scaled for different frequen-<br>cies by f/100 MHz, Driving Strength = 0 | I <sub>DD_2.5V</sub>     | —    | 1.7  | 1.8  | mA    | V <sub>DD</sub> = 2.625V |

|                                                                                                        | <br>I <sub>DD_1.8V</sub> |      | 1.2  | 1.3  | mA    | V <sub>DD</sub> = 2.000V |

| (registers 0x09, 0x0A)                                                                                 | I <sub>DD_1.5V</sub>     | _    | 0.9  | 1.0  | mA    | V <sub>DD</sub> = 1.650V |

Note 1: Needs to be scaled for different frequencies by f/100 MHz.

2: To calculate total power consumption use following formula: P = (I<sub>S</sub> + I<sub>DD\_XTAL</sub>) × V<sub>DD</sub> + (I<sub>DDC</sub> + I<sub>DD</sub> × n × f/100 MHz + V<sub>DDO</sub> × C<sub>LOAD</sub> × f × n) × V<sub>DDO</sub>, where I<sub>DD\_XTAL</sub>: should be set to zero if XTAL is not used or Is should be set to zero if XTAL is used. Also, n = number of active outputs; f = frequency of the clock; C<sub>LOAD</sub> = capacitive load driven by an output.

**3:** This current is consumed by device whenever one or more outputs are enabled. It is independent of the number of active outputs.

#### TABLE 3-3: CURRENT CONSUMPTION (CONTINUED)

| Characteristics               | Symbol               | Min. | Тур. | Max. | Units | Notes                    |

|-------------------------------|----------------------|------|------|------|-------|--------------------------|

| Common output current, Note 3 | I <sub>DD_3.3V</sub> | —    | 3.8  | 8.0  | mA    | V <sub>DD</sub> = 3.465V |

|                               | I <sub>DD_2.5V</sub> | —    | 1.9  | 3.3  | mA    | V <sub>DD</sub> = 2.625V |

|                               | I <sub>DD_1.8V</sub> | _    | 1.2  | 1.7  | mA    | V <sub>DD</sub> = 2.000V |

|                               | I <sub>DD_1.5V</sub> | _    | 1.0  | 1.4  | mA    | V <sub>DD</sub> = 1.650V |

Note 1: Needs to be scaled for different frequencies by f/100 MHz.

2: To calculate total power consumption use following formula: P = (I<sub>S</sub> + I<sub>DD\_XTAL</sub>) × V<sub>DD</sub> + (I<sub>DDC</sub> + I<sub>DD</sub> × n × f/100 MHz + V<sub>DDO</sub> × C<sub>LOAD</sub> × f × n) × V<sub>DDO</sub>, where I<sub>DD\_XTAL</sub>: should be set to zero if XTAL is not used or Is should be set to zero if XTAL is used. Also, n = number of active outputs; f = frequency of the clock; C<sub>LOAD</sub> = capacitive load driven by an output.

**3:** This current is consumed by device whenever one or more outputs are enabled. It is independent of the number of active outputs.

| Characteristics                                                                                                          | Symbol                           | Min. | Тур.  | Max.                   | Units | Notes           |

|--------------------------------------------------------------------------------------------------------------------------|----------------------------------|------|-------|------------------------|-------|-----------------|

| CMOS high-level input voltage for SPI_CLK, SPI_CS and SPI_SDI                                                            | V <sub>CIH</sub>                 | 1.20 | _     | _                      | V     | _               |

| CMOS low-level input voltage for SPI_CLK, SPI_CS and SPI_SDI                                                             | V <sub>CIL</sub>                 | _    | _     | 0.45                   | V     |                 |

| CMOS input leakage current for<br>SPI_CLK, SPI_CS and SPI_SDI,<br>Note 3                                                 | Ι <sub>ΙL</sub>                  | -40  | _     | 10                     | μA    | VI = VDD or 0 V |

| Differential input common mode voltage for IN0_p/n and IN1_p/n                                                           | V <sub>CM</sub>                  | 0.5  | _     | V <sub>DD</sub> – 0.85 | V     | _               |

| Differential input voltage difference for IN0_p/n and IN1_p/n                                                            | V <sub>ID</sub>                  | 0.15 | _     | 1.3                    | V     |                 |

| Differential input leakage current for IN0_p/n and IN1_p/n (includes current in pull-up and pull-down resistors), Note 4 | IIL                              | -200 | _     | 100                    | μΑ    | VI = VDD or 0 V |

| Single ended input high voltage for                                                                                      | V <sub>SIH</sub>                 | 2    | _     | V <sub>DD</sub> + 0.3  | V     | VDD = 3.3V+/-5% |

| IN_0_p and IN_1_p                                                                                                        | V SIH                            | 1.6  | —     | V <sub>DD</sub> + 0.3  | V     | VDD = 2.5V+/-5% |

| Single ended input low voltage for                                                                                       | M                                | -0.3 | —     | 1.3                    | V     | VDD = 3.3V+/-5% |

| IN_0_p and IN_1_p                                                                                                        | V <sub>SIL</sub>                 | -0.3 | —     | 0.9                    | V     | VDD = 2.5V+/-5% |

| Input frequency                                                                                                          | f <sub>IN</sub>                  | 0    | —     | 200                    | MHz   | —               |

| Input duty cycle<br>(200 MHz Input Clock)                                                                                | DC                               | 35   | —     | 65                     | %     | Note 5          |

| Input slew rate                                                                                                          | slew                             | _    | 2     |                        | V/ns  | —               |

| Input pull-up/pull-down resistance                                                                                       | R <sub>PU</sub> /R <sub>PD</sub> |      | 60 kΩ |                        | kΩ    | _               |

| Input pull-down resistance (INx_p)                                                                                       | R <sub>PD</sub>                  | —    | 30 kΩ |                        | kΩ    | _               |

#### TABLE 3-4: INPUT CHARACTERISTICS (Note 1, Note 2)

**Note 1:** Values are over recommended operating conditions.

2: Values are over all two power supply modes (V<sub>DD</sub> = 3.3V and V<sub>DD</sub> = 2.5V).

3: CMOS input leakage is due to 300 kΩ pull-up/pull-down resistors.

**4:** Differential input leakage is due to 60 kΩ pull-up/pull-down resistors INx\_n and due to 30 kΩ pull-down resistor for INx\_p.

**5:** Minimum and maximum duty cycles should be scaled for different input frequencies. For example, a 10 MHz input clock would have the minimum duty cycle of 2% and the maximum duty cycle of 98%.

| TABLE 3-5: | <b>CRYSTAL OSCILLATOR CHARACTERISTICS (</b> | Note 1) | ) |

|------------|---------------------------------------------|---------|---|

|            |                                             |         |   |

| Characteristics                        | Symbol          | Min. | Тур.   | Max. | Units | Notes                                                                                                           |

|----------------------------------------|-----------------|------|--------|------|-------|-----------------------------------------------------------------------------------------------------------------|

| Mode of oscillation                    | mode            | Fι   | undame | ntal | _     | —                                                                                                               |

| Frequency                              | f               | 8    | _      | 160  | MHz   | —                                                                                                               |

| On chip shunt resistor                 | R               | —    | 0.5    | _    | MΩ    | —                                                                                                               |

| On chip capacitance                    | С               | —    | 12     |      | pF    | —                                                                                                               |

| Frequency in overdrive mode,<br>Note 2 | f <sub>OV</sub> | 0.1  |        | 200  | MHz   | Functional but may not meet AC<br>parameters. Minimum depends on<br>AC coupling. Capacitor (0.1 uF<br>assumed). |

| Frequency in bypass mode,<br>Note 3    | f <sub>BP</sub> | —    |        | 200  | MHz   | Functional but may not meet AC parameters.                                                                      |

Note 1: Values are over recommended operating conditions. Values are over all two power supply modes ( $V_{DD}$  = 3.3V and  $V_{DD}$  = 2.5V).

- 2: Maximum input level is 2.0V.

- **3:** Maximum output level is V<sub>DD</sub>.

| TABLE 3-6: | LVCMOS OUTP | UT CHA | RACTERIST | ICS (I | Note 1) |

|------------|-------------|--------|-----------|--------|---------|

|            |             |        |           |        |         |

| Characteristics                     | Symbol                          | Min.                   | Тур. | Max.                 | Units | Notes                       |

|-------------------------------------|---------------------------------|------------------------|------|----------------------|-------|-----------------------------|

|                                     |                                 | 0.8 × V <sub>DDO</sub> | —    |                      | V     | V <sub>DDO</sub> = 3.3V±5%  |

| Output high voltage                 | V                               | $0.8 \times V_{DDO}$   | —    | _                    | V     | V <sub>DDO</sub> = 2.5V±5%  |

| Output high voltage                 | V <sub>OH</sub>                 | $0.7 \times V_{DDO}$   | _    | _                    | V     | V <sub>DDO</sub> = 1.8V±10% |

|                                     |                                 | $0.7 \times V_{DDO}$   | —    | _                    | V     | V <sub>DDO</sub> = 1.5V±10% |

|                                     |                                 | _                      | _    | $0.2 \times V_{DDO}$ | V     | V <sub>DDO</sub> = 3.3V±5%  |

| Output low voltage                  |                                 | —                      | _    | $0.2 \times V_{DDO}$ | V     | V <sub>DDO</sub> = 2.5V±5%  |

| Output low voltage                  | V <sub>OL</sub>                 | —                      | —    | $0.3 \times V_{DDO}$ | V     | V <sub>DDO</sub> = 1.8V±10% |

|                                     |                                 | —                      | —    | $0.3 \times V_{DDO}$ | V     | V <sub>DDO</sub> = 1.5V±10% |

|                                     |                                 | —                      | 17   | —                    | Ω     | V <sub>DDO</sub> = 3.3V     |

| Output impedance                    | R <sub>O</sub>                  | —                      | 21   | _                    | Ω     | V <sub>DDO</sub> = 2.5V     |

|                                     |                                 | _                      | 30   | _                    | Ω     | V <sub>DDO</sub> = 1.8V     |

|                                     |                                 | —                      | 42   | _                    | Ω     | V <sub>DDO</sub> = 1.5V     |

|                                     |                                 | 3.19                   | 5.14 | 6.33                 | V/ns  | V <sub>DDO</sub> = 3.3V±5%  |

| Output slew rate, rise or fall (20% | + +                             | 1.72                   | 3.74 | 4.61                 | V/ns  | V <sub>DDO</sub> = 2.5V±5%  |

| to 80%)                             | t <sub>r</sub> , t <sub>f</sub> | 1.64                   | 2.52 | 3.32                 | V/ns  | V <sub>DDO</sub> = 1.8V±10% |

|                                     |                                 | 1.20                   | 1.96 | 2.54                 | V/ns  | V <sub>DDO</sub> = 1.5V±10% |

| Output frequency                    | Fo                              | 0                      | —    | 200                  | MHz   | —                           |

| Output duty cycle                   |                                 | 50.26                  | —    | 53.18                | %     | Input. duty-cycle 50%       |

| Output enable or disable time       |                                 | —                      | —    | 2                    | cycle | —                           |

| Output to output skew               | t <sub>oosk</sub>               | —                      | —    | 27                   | ps    | —                           |

| Device-to-device output skew        | t <sub>DOOSK</sub>              |                        | _    | 1.6                  | ns    | —                           |

| Input to output delay               | +                               | 1.15                   | 2.09 | 2.54                 | ns    | VDD = 3.3V                  |

| Input to output delay               | t <sub>IOD</sub>                | 1.57                   | 2.27 | 2.77                 | ns    | VDD = 2.5V                  |

| Input multiplexer isolation         | ISO                             | 75                     | _    |                      | dB    | Tested with 125 MHz clocks  |

**Note 1:** Values are over recommended operating conditions. Values are over all two power supply modes ( $V_{DD}$  = 3.3V and  $V_{DD}$  = 2.5V). Load 50 $\Omega$  to  $V_{DDO}/2$ .

| Characteristics                 | Symbol | Min. | Тур.    | Max.    | Units    | Notes                                                                                            |

|---------------------------------|--------|------|---------|---------|----------|--------------------------------------------------------------------------------------------------|

|                                 |        | _    | 17      |         | fs – RMS | $V_{DD}$ = 3.3V, $V_{DDO}$ = 3.3V<br>f <sub>in</sub> = 125 MHz, single ended input               |

| System level additive jitter,   |        | _    | 31      | _       | fs – RMS | $V_{DD}$ = 2.5V, $V_{DDO}$ = 1.5V to 2.5V<br>f <sub>in</sub> = 125 MHz, single ended input       |

| Note 2                          |        | _    | 22      | _       | fs – RMS | V <sub>DD</sub> = 3.3V, V <sub>DDO</sub> = 3.3V<br>f <sub>in</sub> = 125 MHz, differential input |

|                                 |        |      | 37      | _       | fs – RMS | $V_{DD}$ = 2.5V, $V_{DDO}$ = 1.5V to 2.5V<br>f <sub>in</sub> = 125 MHz, differential input       |

|                                 |        | _    | 45.18   | 93.11   | fs – RMS | $V_{DD}$ = 3.3V, $V_{DDO}$ = 3.3V<br>f <sub>in</sub> = 125 MHz, single ended input               |

| Additive jitter, Note 3, Note 4 |        | _    | 80.46   | 126.92  | fs – RMS | $V_{DD}$ = 2.5V, $V_{DDO}$ = 1.5V to 2.5V<br>f <sub>in</sub> = 125 MHz, single ended input       |

| Additive Jittel, Note 5, Note 4 |        | _    | 39.95   | 68.98   | fs – RMS | V <sub>DD</sub> = 3.3V, V <sub>DDO</sub> = 3.3V<br>f <sub>in</sub> = 125 MHz, differential input |

|                                 |        |      | 67.18   | 117.26  | fs – RMS | $V_{DD}$ = 2.5V, $V_{DDO}$ = 1.5V to 2.5V<br>f <sub>in</sub> = 125 MHz, differential input       |

|                                 |        | _    | -145.08 | -138.67 | dBc/Hz   | @10 kHz, f <sub>in</sub> = 125 MHz, single<br>ended input                                        |

|                                 |        | —    | -152.46 | -145.82 | dBc/Hz   | @100 kHz, f <sub>in</sub> = 125 MHz, single<br>ended input                                       |

|                                 |        | _    | -160.67 | -155.66 | dBc/Hz   | @1 MHz, f <sub>in</sub> = 125 MHz, single<br>ended input                                         |

|                                 |        | _    | -162.66 | -160.55 | dBc/Hz   | @10 MHz, f <sub>in</sub> = 125 MHz, single<br>ended input                                        |

| Phase noise floor (VDD = 3.3V,  |        |      | -162.71 | -160.19 | dBc/Hz   | @20 MHz, f <sub>in</sub> = 125 MHz, single<br>ended input                                        |

| VDDO = 3.3V)                    |        |      | -145.34 | -137.83 | dBc/Hz   | @10 kHz, f <sub>in</sub> = 125 MHz, single<br>ended input                                        |

|                                 |        | _    | -152.60 | -146.93 | dBc/Hz   | @100 kHz, f <sub>in</sub> = 125 MHz, single<br>ended input                                       |

|                                 |        | _    | -161.06 | -156.99 | dBc/Hz   | @1 MHz, f <sub>in</sub> = 125 MHz, single<br>ended input                                         |

|                                 |        | _    | -163.22 | -160.84 | dBc/Hz   | @10 MHz, f <sub>in</sub> = 125 MHz, single<br>ended input                                        |

|                                 |        | _    | -163.38 | -161.42 | dBc/Hz   | @20 MHz, f <sub>in</sub> = 125 MHz, single<br>ended input                                        |

#### LVCMOS OUTPUT ADDITIVE JITTER AND PHASE NOISE (Note 1) **TABLE 3-7:**

Note 1: Values are over recommended operating conditions. Values are over all two power supply modes (V<sub>DD</sub> = 3.3V and  $V_{DD} = 2.5V$ ).

2: System level additive jitter is calculated as  $J_{RMS\_SYS\_AJ} = J_{RMS\_OUT} - J_{RMS\_IN}$ . 3: Additive jitter is calculated as  $J_{RMS\_AJ} = \text{sqrt} (J_{RMS\_OUT}^2 - J_{RMS\_IN}^2)$  where jitter is integrated in 12 kHz to 20 MHz band.

4: Tester measures jitter at 156.25 MHz. Since this frequency won't appear in the data sheet, it should be removed from the PPGT. Data sheet jitter is guaranteed by lab char. The ATE jitter measurement will be used to screen outliers only, with limits based on ATE distribution.

| Characteristics                | Symbol | Min. | Тур.    | Max.    | Units   | Notes                                                      |                                                           |                                                            |

|--------------------------------|--------|------|---------|---------|---------|------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------|

|                                |        | _    | -139.93 | -134.59 | dBc/Hz  | @10 kHz, f <sub>in</sub> = 125 MHz, single<br>ended input  |                                                           |                                                            |

|                                |        | _    | -147.22 | -144.21 | dBc/Hz  | @100 kHz, f <sub>in</sub> = 125 MHz, single<br>ended input |                                                           |                                                            |

|                                |        |      | _       | -157.11 | -154.78 | dBc/Hz                                                     | @1 MHz, f <sub>in</sub> = 125 MHz, single<br>ended input  |                                                            |

|                                |        |      |         | _       | -160.58 | -158.21                                                    | dBc/Hz                                                    | @10 MHz, f <sub>in</sub> = 125 MHz, single<br>ended input  |

| Phase noise floor (VDD = 2.5V, |        |      |         | _       | -160.78 | -158.19                                                    | dBc/Hz                                                    | @20 MHz, f <sub>in</sub> = 125 MHz, single<br>ended input  |

| VDDO = 2.5V)                   |        |      | —       | -141.69 | -134.26 | dBc/Hz                                                     | @10 kHz, f <sub>in</sub> = 125 MHz, single<br>ended input |                                                            |

|                                |        |      |         | _       | -149.19 | -144.73                                                    | dBc/Hz                                                    | @100 kHz, f <sub>in</sub> = 125 MHz, single<br>ended input |

|                                |        |      |         |         |         | _                                                          | -158.66                                                   | -156.22                                                    |

|                                |        | _    | -161.60 | -159.32 | dBc/Hz  | @10 MHz, f <sub>in</sub> = 125 MHz, single<br>ended input  |                                                           |                                                            |

|                                |        | _    | -161.85 | -159.36 | dBc/Hz  | @20 MHz, f <sub>in</sub> = 125 MHz, single<br>ended input  |                                                           |                                                            |

#### TABLE 3-7: LVCMOS OUTPUT ADDITIVE JITTER AND PHASE NOISE (Note 1) (CONTINUED)

Note 1: Values are over recommended operating conditions. Values are over all two power supply modes ( $V_{DD} = 3.3V$  and  $V_{DD} = 2.5V$ ).

2: System level additive jitter is calculated as  $J_{RMS_SYS_AJ} = J_{RMS_OUT} - J_{RMS_IN}$ .

**3:** Additive jitter is calculated as J<sub>RMS\_AJ</sub> = sqrt (J<sub>RMS\_OUT</sub><sup>2</sup> - J<sub>RMS\_IN</sub><sup>2</sup>) where jitter is integrated in 12 kHz to 20 MHz band.

4: Tester measures jitter at 156.25 MHz. Since this frequency won't appear in the data sheet, it should be removed from the PPGT. Data sheet jitter is guaranteed by lab char. The ATE jitter measurement will be used to screen outliers only, with limits based on ATE distribution.

| Characteristics         | Symbol | Min. | Тур.    | Max. | Units  | Notes                                                     |

|-------------------------|--------|------|---------|------|--------|-----------------------------------------------------------|

| Jitter RMS in 12 kHz to |        |      | 72.63   |      | fs     | V <sub>DD</sub> = 3.3V, V <sub>DDO</sub> = 3.3V           |

| 20 MHz band             |        |      | 87.59   | —    | fs     | V <sub>DD</sub> = 2.5V; V <sub>DDO</sub> = 2.5V           |

|                         |        | —    | -75.96  | _    | dBc/Hz | @10 Hz, V <sub>DD</sub> = 3.3V, V <sub>DDO</sub> = 3.3V   |

|                         |        |      | -107.50 | _    | dBc/Hz | @100 Hz, V <sub>DD</sub> = 3.3V, V <sub>DDO</sub> = 3.3V  |

|                         |        | —    | -132.34 | —    | dBc/Hz | @1 kHz, V <sub>DD</sub> = 3.3V, V <sub>DDO</sub> = 3.3V   |

|                         |        | —    | -157.36 |      | dBc/Hz | @10 kHz, V <sub>DD</sub> = 3.3V, V <sub>DDO</sub> = 3.3V  |

|                         |        |      | -165.82 | _    | dBc/Hz | @100 kHz, V <sub>DD</sub> = 3.3V, V <sub>DDO</sub> = 3.3V |

|                         |        | —    | -168.85 | —    | dBc/Hz | @1 MHz, V <sub>DD</sub> = 3.3V, V <sub>DDO</sub> = 3.3V   |

| Phase noise floor       |        | —    | -168.88 |      | dBc/Hz | @5 MHz, V <sub>DD</sub> = 3.3V, V <sub>DDO</sub> = 3.3V   |

| Filase noise nooi       |        | —    | -70.52  | —    | dBc/Hz | @10 Hz, V <sub>DD</sub> = 2.5V; V <sub>DDO</sub> = 2.5V   |

|                         |        | —    | -102.60 | —    | dBc/Hz | @100 Hz, V <sub>DD</sub> = 2.5V; V <sub>DDO</sub> = 2.5V  |

|                         |        | —    | -129.14 |      | dBc/Hz | @1 kHz, V <sub>DD</sub> = 2.5V; V <sub>DDO</sub> = 2.5V   |

|                         |        | —    | -153.93 | —    | dBc/Hz | @10 kHz, V <sub>DD</sub> = 2.5V; V <sub>DDO</sub> = 2.5V  |

|                         |        |      | -164.00 | —    | dBc/Hz | @100 kHz, V <sub>DD</sub> = 2.5V; V <sub>DDO</sub> = 2.5V |

|                         |        | _    | -167.34 |      | dBc/Hz | @1 MHz, V <sub>DD</sub> = 2.5V; V <sub>DDO</sub> = 2.5V   |

|                         |        | _    | -167.41 | _    | dBc/Hz | @5 MHz, V <sub>DD</sub> = 2.5V; V <sub>DDO</sub> = 2.5V   |

#### TABLE 3-8: LVCMOS OUTPUT JITTER PHASE NOISE WITH 25 MHZ XTAL (NOTE 1)

**Note 1:** Values are over recommended operating conditions. Values are over all two power supply modes (V<sub>DD</sub> = 3.3V and V<sub>DD</sub> = 2.5V). XTAL frequency is 25 MHz.

#### TABLE 3-9: 5 MM × 5 MM VQFN PACKAGE THERMAL PROPERTIES

| Parameter                                                 | Symbol              | Conditions      | Value | Units |

|-----------------------------------------------------------|---------------------|-----------------|-------|-------|

| Maximum ambient temperature                               | T <sub>A</sub>      | _               | 85    | °C    |

| Maximum junction temperature                              | T <sub>J(MAX)</sub> | —               | 125   | °C    |

|                                                           |                     | Still air       | 26.8  | °C/W  |

| Junction to ambient thermal resistance, Note 1            | θ <sub>JA</sub>     | 1 m/s airflow   | 21.8  | °C/W  |

|                                                           |                     | 2.5 m/s airflow | 19.9  | °C/W  |

| Junction to board thermal resistance                      | θ <sub>JB</sub>     | —               | 10.8  | °C/W  |

| Junction to case thermal resistance                       | θ <sub>JC</sub>     |                 | 19.5  | °C/W  |

| Junction to pad thermal resistance, Note 2                | θ <sub>JP</sub>     | Still air       | 6.5   | °C/W  |

| Junction to top-center thermal characterization parameter | Ψ <sub>JT</sub>     | Still air       | 0.6   | °C/W  |

**Note 1:**  $\theta_{JA}$  is the thermal resistance from junction to ambient when the package is mounted on a 4-layer JEDEC standard test board and dissipating maximum power.

**2:**  $\theta_{JP}$  is the thermal resistance from junction to the center exposed pad on the bottom of the package.

# 4.0 PACKAGE OUTLINE

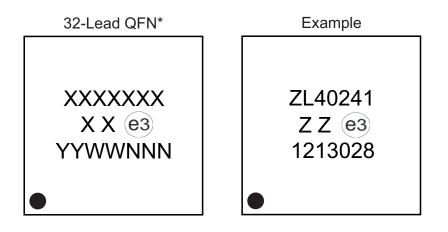

# 4.1 Package Marking Information

| Legend | Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                                                                                                  | Product code or customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |  |  |  |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Note:  | Note: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information. Package may or may not include the corporate logo. |                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|        | Underbar                                                                                                                                                                                                                                                         | (_) and/or Overbar (⁻) symbol may not be to scale.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

#### 32-Lead 5 mm x 5 mm VQFN Package Outline and Recommended Land Pattern

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-25400 Rev A Sheet 1 of 2

#### 32-Lead 5 mm x 5 mm VQFN Package Outline and Recommended Land Pattern

For the most current package drawings, please see the Microchip Packaging Specification located at http:/ Note: /www.microchip.com/packaging

|                         | Units  |      |          |      |

|-------------------------|--------|------|----------|------|

| Dimension               | Limits | MIN  | NOM      | MAX  |

| Number of Terminals     | Ν      |      | 32       |      |

| Pitch                   | е      |      | 0.50 BSC |      |

| Overall Height          | Α      | 0.80 | 0.90     | 1.00 |

| Standoff                | A1     | 0.00 | 0.02     | 0.05 |

| Terminal Thickness      | A3     |      | 0.20 REF |      |

| Overall Length          | D      |      | 5.00 BSC |      |

| Exposed Pad Length      | D2     | 3.00 | 3.10     | 3.20 |

| Overall Width           | E      |      | 5.00 BSC |      |

| Exposed Pad Width       | E2     | 3.00 | 3.10     | 3.20 |

| Terminal Width          | b      | 0.20 | 0.25     | 0.30 |

| Terminal Length         | L      | 0.35 | 0.40     | 0.45 |

| Terminal-to-Exposed-Pad | Κ      | 0.20 | -        | -    |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-25400 Rev A Sheet 2 of 2

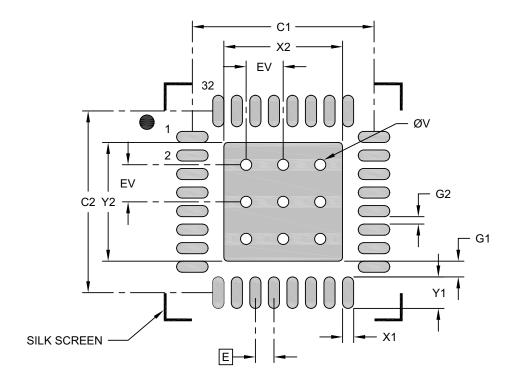

#### 32-Lead 5 mm x 5 mm VQFN Package Outline and Recommended Land Pattern

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                                  | Ν      | <b>IILLIMETER</b> | S        |      |

|----------------------------------|--------|-------------------|----------|------|

| Dimension                        | Limits | MIN               | NOM      | MAX  |

| Contact Pitch                    | E      |                   | 0.50 BSC |      |

| Optional Center Pad Width        | X2     |                   |          | 3.20 |

| Optional Center Pad Length       | Y2     |                   |          | 3.20 |

| Contact Pad Spacing              | C1     |                   | 4.90     |      |

| Contact Pad Spacing              | C2     |                   | 4.90     |      |

| Contact Pad Width (X32)          | X1     |                   |          | 0.30 |

| Contact Pad Length (X32)         | Y1     |                   |          | 0.85 |

| Contact Pad to Center Pad (X32)  | G1     | 0.23              |          |      |

| Contact Pad to Contact Pad (X28) | G2     | 0.20              |          |      |

| Thermal Via Diameter             | V      |                   | 0.30     |      |

| Thermal Via Pitch                | EV     |                   | 1.00     |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing C04-27400 Rev A

NOTES:

# APPENDIX A: DATA SHEET REVISION HISTORY

#### TABLE A-1: REVISION HISTORY

| Revision              | Section/Figure/Entry | Correction                                                                                                                                                  |

|-----------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DS20006783A (11-2023) | Various              | Converted Microsemi data sheet ZL40241 to Micro-<br>chip DS20006783A. Updated Figure 2-9 as<br>requested by Applications. Minor text changes<br>throughout. |

| DS20006783B (02-2025) | Table 3-4            | Updated input duty cycle row and added note 5 to Table 3-4.                                                                                                 |

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

|                   |                            |                                                                 |            |        | Example   | s:                                                                                                                                                                              |  |

|-------------------|----------------------------|-----------------------------------------------------------------|------------|--------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Device            | <u>X</u>                   | X                                                               | X          | X      | a) ZL4024 | 41LDG1:                                                                                                                                                                         |  |

| Part<br>Number    | Chip Carrier<br>Type       | Package                                                         | Media Type | Finish |           | Ten LVCMOS Output Low Additive<br>Jitter Fanout Buffer, Leadless Chip<br>Carrier, 32-Lead 5 mm x 5 mm VQFN,                                                                     |  |

| Device:           |                            | ZL40241: Ten LVCMOS Output Low Additive Jitter Fanout<br>Buffer |            |        |           | 490/Tray, Pb Free with Matte Sn Lead<br>Finish, RoHS e3 Compliant                                                                                                               |  |

|                   | Duilei                     |                                                                 |            |        |           | b) ZL40241LDF1:                                                                                                                                                                 |  |

| Chip Carrier Type | : L = Leadles              | L = Leadless Chip Carrier                                       |            |        |           | Ten LVCMOS Output Low Additive<br>Jitter Fanout Buffer, Leadless Chip<br>Carrier, 32-Lead 5 mm x 5 mm VQFN,                                                                     |  |

| Package:          | D = 32-Lead                | D = 32-Lead 5 mm x 5 mm VQFN                                    |            |        |           | 4,000/Reel, Pb Free with Matte Sn<br>Lead Finish, RoHS e3 Compliant                                                                                                             |  |

| Media Type:       | G = 490/Tra<br>F = 4,000/R |                                                                 |            |        |           |                                                                                                                                                                                 |  |

| Finish:           | 1 = Pb Free                | 1 = Pb Free with Matte Sn Lead Finish, RoHS e3 Compliant        |            |        |           |                                                                                                                                                                                 |  |

|                   |                            |                                                                 |            |        | Note 1:   | Tape and Reel identifier only appears in the catalog part number description. This identifie                                                                                    |  |

|                   |                            |                                                                 |            |        |           | is used for ordering purposes and is not<br>printed on the device package. Check with<br>your Microchip Sales Office for package<br>availability with the Tape and Reel option. |  |

# ZL40241

NOTES:

# **Microchip Information**

#### Trademarks

The "Microchip" name and logo, the "M" logo, and other names, logos, and brands are registered and unregistered trademarks of Microchip Technology Incorporated or its affiliates and/or subsidiaries in the United States and/or other countries ("Microchip Trademarks"). Information regarding Microchip Trademarks can be found at https://www.microchip.com/en-us/about/legal-information/microchip-trademarks.

ISBN: 979-8-3371-0751-6

#### Legal Notice

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at www.microchip.com/en-us/support/design-help/client-support-services.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

# **Microchip Devices Code Protection Feature**

Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not mean that we are guaranteeing the product is "unbreakable". Code protection is constantly evolving. Microchip is committed to continuously improving the code protection features of our products.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Microchip:

ZL40241LDF1 ZL40241LDG1