# ZL38012 Design Manual

Part Number: ZL38012

Revision Number: 3.0

Issue Date: November 2012

# Voice Processor with Dual Narrow Band Codecs

**Design Manual**

#### **Features**

- 100 MHz (200 MIPs) Microsemi voice processor with hardware accelerator.

- Dual 8 kHz sampling  $\Delta\Sigma$  ADCs with input buffer gain selection

- Dual 8 kHz  $\Delta\Sigma$  DACs with internal output driver

- Dual function Inter-IC Sound (I<sup>2</sup>S) port or TDM Port

- PCM port supports TDM (ST BUS, GCI or McBSP framing) or SSI modes at bit rates of 128, 256, 512, 1024, 2048, 4096, 8192 or 16384 Kb/sec

- Separate slave (microcontroller) and master (Flash) SPI ports, maximum clock rate = 25 MHz

- 5 General Purpose Input/Output (GPIO) pins

- · General purpose UART port

- Bootloadable for future Microsemi software upgrades

- · External oscillator or crystal/ceramic resonator

November 2012

#### **Ordering Information**

ZL38012LDG1

56 Pin QFN\*

\*Pb Free Matte Tin

-40°C to +85°C

1.2 V Core; 3.3 V IO with 5 V-tolerant inputs

## **Applications**

- · Hands-free car kits

- Full duplex speaker-phone for digital telephone

- Echo cancellation for video conferences

- Intercom Systems

- · Security Systems

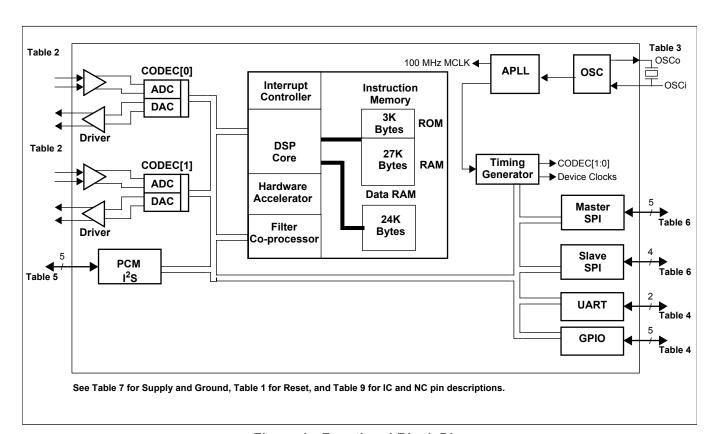

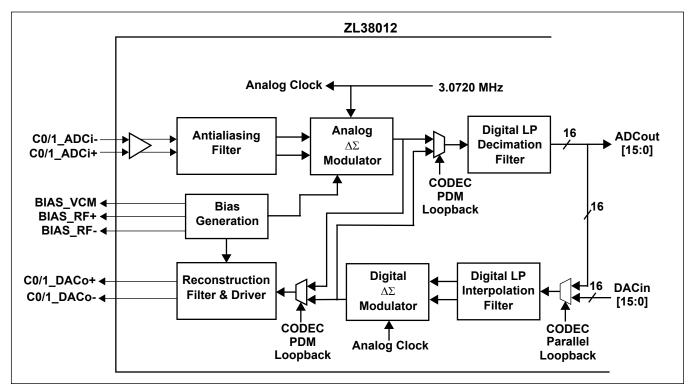

Figure 1 - Functional Block Diagram

## **Change Summary**

Changes from March 2011 issue to November 2012 issue. Page, section, figure and table numbers refer to this current issue.

| Page     | Item                            | Change                              |  |

|----------|---------------------------------|-------------------------------------|--|

| Multiple | Zarlink logo and name reference | Updated to Microsemi logo and name. |  |

Changes from September 2010 issue to March 2011 issue. Page, section, figure and table numbers refer to this current issue.

| Page | Item                            | Change                               |

|------|---------------------------------|--------------------------------------|

| 46   | "DC Electrical Characteristics" | Removed Theta JA                     |

| 73   | Figure 56                       | Corrected crystal frequency options  |

| 74   | Figure 57                       | Corrected crystal frequency options. |

# **Table of Contents**

| 1.0 | Functional Description                                  | 13 |

|-----|---------------------------------------------------------|----|

| 2.0 | Core DSP Functional Block                               | 13 |

|     | 2.1 DSP                                                 | 14 |

| 3.0 | Codec[1:0]                                              | 15 |

|     | 3.1 Input Buffer                                        |    |

|     | 3.2 Reconstruction Filter and Driver (DAC Output)       |    |

| 4.0 | PCM Port                                                |    |

|     | 4.1 PCM Port.                                           |    |

|     | 4.2 PCM Port Modes of Operation                         |    |

|     | 4.3 TDM - ST-BUS, GCI & McBSP Operation                 |    |

|     | 4.4 SSI Operation                                       |    |

|     | 4.5 I2S Port Description.                               | 31 |

| 5.0 | Host Microprocessor and Peripheral Interfaces           | 34 |

|     | 5.1 Master SPI (FLASH Port)                             |    |

|     | 5.2 Slave SPI (Host Port)                               | 35 |

|     | 5.3 UART                                                |    |

|     | 5.4 Host Interface Operation (Slave SPI and UART Ports) | 37 |

|     | 5.5 GPIO                                                | 42 |

| 6.0 | Device Operation                                        | 42 |

|     | 6.1 Initialization                                      | 42 |

|     | 6.2 Boot                                                |    |

|     | 6.3 Timing Architecture and Mode Selection at Power-Up  | 43 |

| 7.0 | AC/DC Electrical Characteristics                        | 45 |

| 8.0 | Applications                                            | 70 |

|     | 8.1 Power Supply                                        | 70 |

|     | 8.1.1 Power Sequencing                                  | 70 |

|     | 8.1.2 Supply Isolation                                  | 71 |

|     | 8.2 External Clock Requirements                         |    |

|     | 8.2.1 Crystal Oscillator Specification                  |    |

|     | 8.2.2 Clock Oscillator                                  |    |

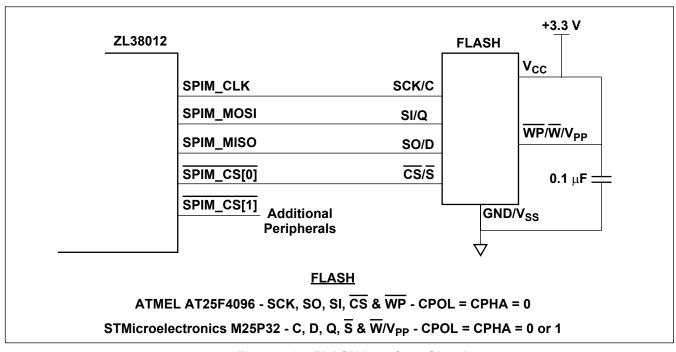

|     | 8.3 FLASH Specification                                 |    |

|     | 8.4 Internal CODEC Interface                            |    |

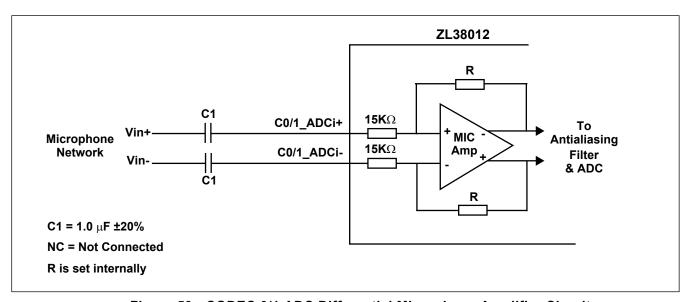

|     | 8.4.1 CODEC Microphone Amplifier ADC Circuit            |    |

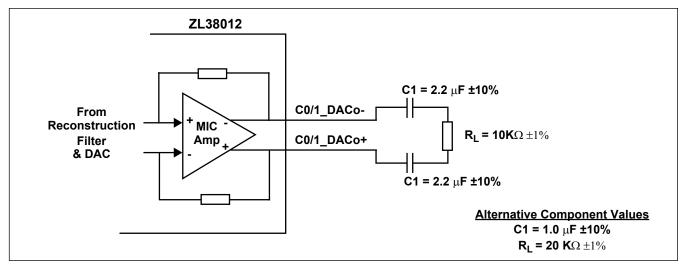

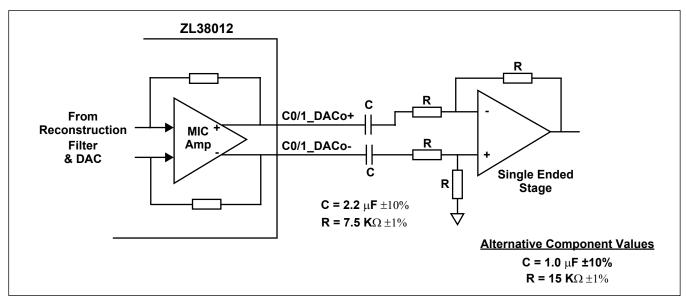

|     | 8.4.2 CODEC DAC Driver Circuit                          |    |

|     | 8.4.3 CODEC Bias Circuit                                |    |

|     | 8.5 Host Microprocessor Access Examples                 | 79 |

# **List of Figures**

| Figure 1 - Functional Block Diagram                                                    |    |

|----------------------------------------------------------------------------------------|----|

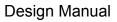

| Figure 2 - ZL38012 56-Lead QFN 8 mm x 8 mm, 0.5 mm pitch, JEDEC MO-026 (Top View)      | 8  |

| Figure 3 - CODEC Block Diagram                                                         | 15 |

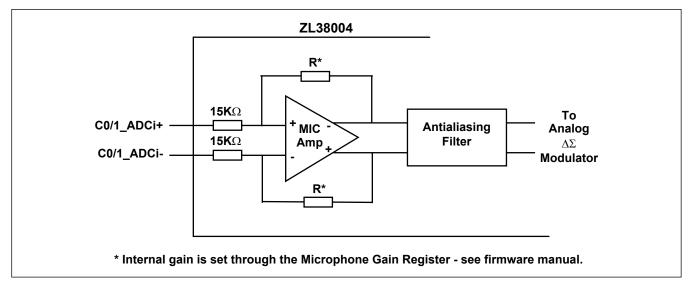

| Figure 4 - CODEC 0/1 ADC Microphone Amplifier Selected                                 | 16 |

| Figure 5 - PCM Port Signal Configurations for Master/Slave Operation                   | 17 |

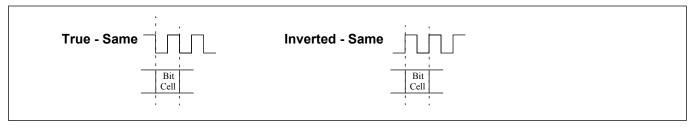

| Figure 6 - Clock Polarity versus Data Rate                                             | 18 |

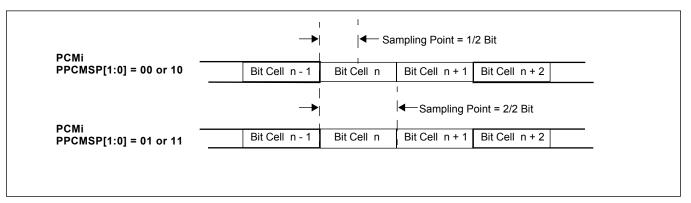

| Figure 7 - PCM Serial Data Input Sampling Points                                       | 18 |

| Figure 8 - PCM and DSP Loopbacks                                                       | 19 |

| Figure 9 - SSI Mode: Separated Channels                                                |    |

| Figure 10 - Mode 6 - SSI Slave with Automatic Rate Detection                           | 21 |

| Figure 11 - TDM - ST-BUS Slave/Master Functional Timing Diagram                        | 26 |

| Figure 12 - TDM - GCI Slave Functional Timing Diagram                                  | 27 |

| Figure 13 - TDM - GCI Master Functional Timing Diagram                                 | 27 |

| Figure 14 - TDM - McBSP Slave/Master Functional Timing Diagram                         | 28 |

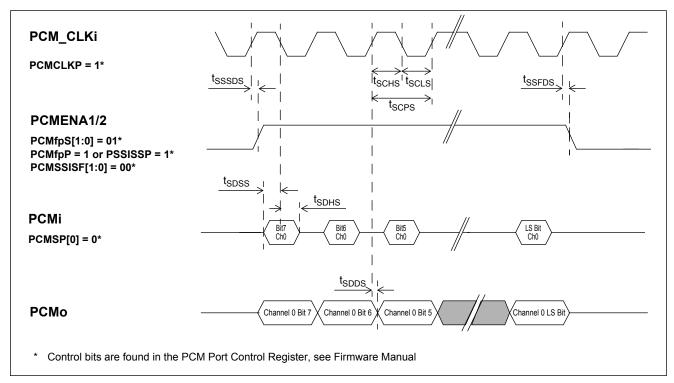

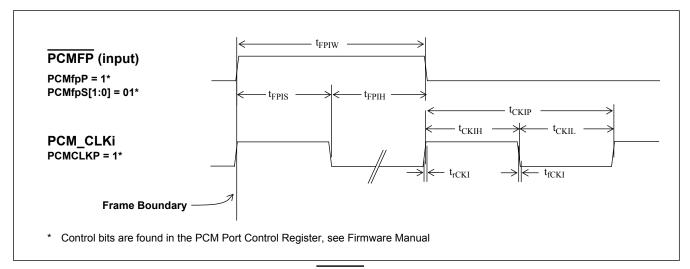

| Figure 15 - SSI Slave/Master Enable and Bit Clock Functional Timing                    | 29 |

| Figure 16 - SSI Mode: Separated Channels Functional Timing                             | 30 |

| Figure 17 - SSI Mode: Adjacent Channels Functional Timing                              | 31 |

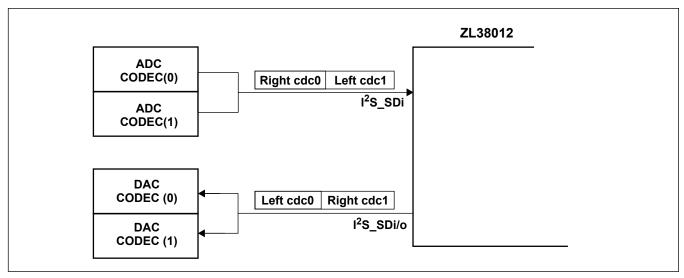

| Figure 18 - Dual CODEC Configuration                                                   |    |

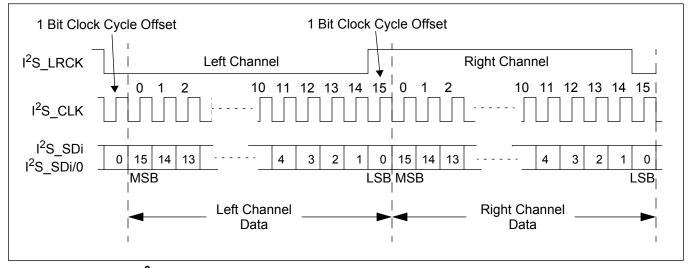

| Figure 19 - I2S Audio Interface with Left Channel Enable Low/Right Channel Enable High | 32 |

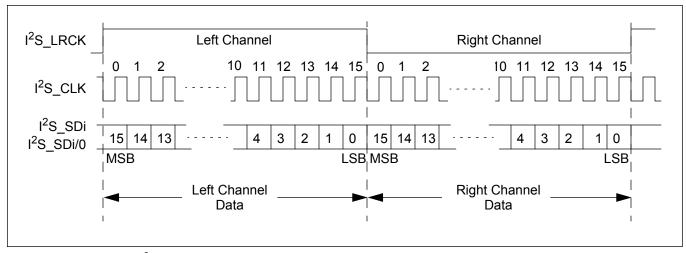

| Figure 20 - I2S Audio Interface with Left Channel Enable High/Right Channel Enable Low | 33 |

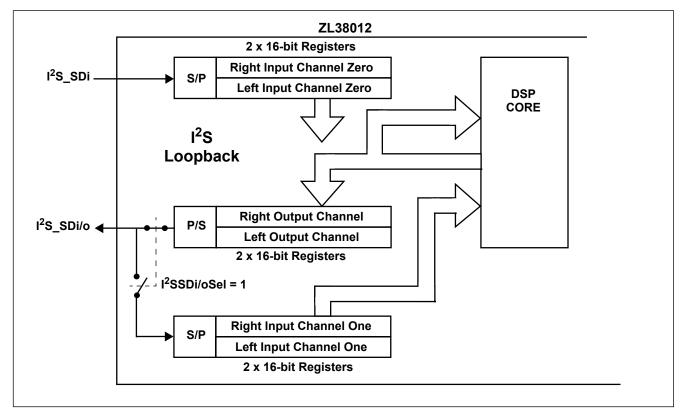

| Figure 21 - Inter-IC Sound (I2S) Loopback                                              |    |

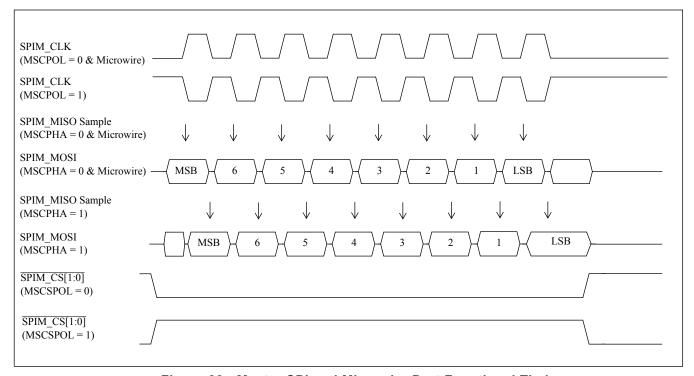

| Figure 22 - Master SPI and Microwire Port Functional Timing                            | 34 |

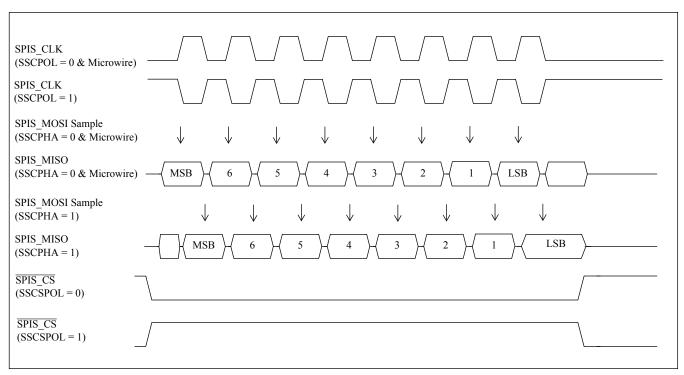

| Figure 23 - Slave SPI and Microwire Port Functional Timing                             |    |

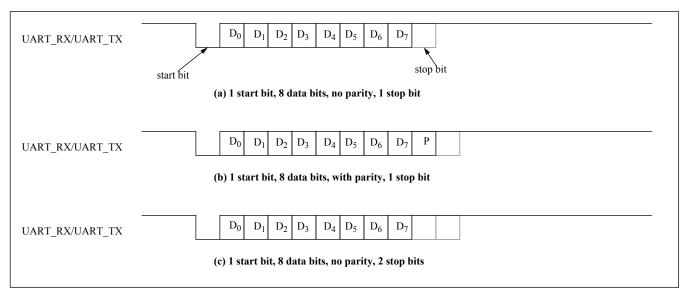

| Figure 24 - Example of Some the Supported UART Interface Timing                        |    |

| Figure 25 - Slave SPI and UART Port Access                                             |    |

| Figure 26 - Example of a Port Write Access to the Slave SPI Port (8-bit data)          |    |

| Figure 27 - Example of a Port Read Access to the Slave SPI Port (8-bit data)           |    |

| Figure 28 - Example of a Port Read Access to the Slave SPI Port (8-bit data)           | 40 |

| Figure 29 - Example of a Read Access to the Slave UART Port                            |    |

| Figure 30 - Example of a Write Access to the Slave UART Port                           |    |

| Figure 31 - Initialization Timing                                                      |    |

| Figure 32 - ZL38012 Master/Slave Timing Selection and Clock Distribution               |    |

| Figure 33 - Timing Parameter Measurement Digital Voltage Levels                        |    |

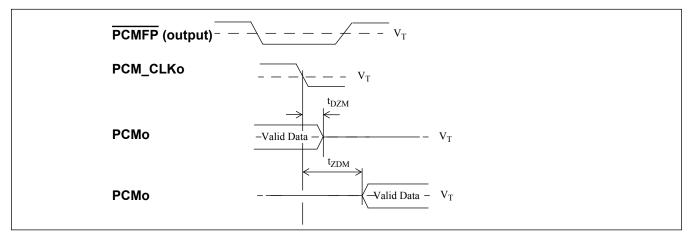

| Figure 34 - PCM SSI Slave Mode Timing Diagram                                          | 54 |

| Figure 35 - PCM SSI Master Mode Timing Diagram                                         |    |

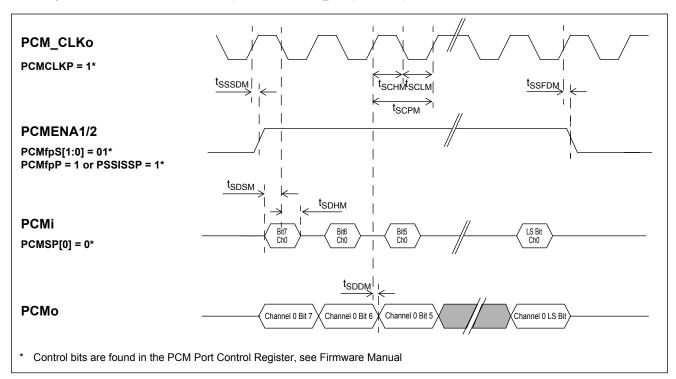

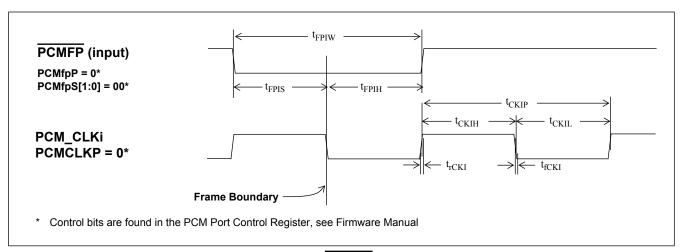

| Figure 36 - TDM - ST-BUS PCMFP and PCM_CLKi Input Timing                               |    |

| Figure 37 - TDM - GCI PCMFP and PCM_CLKi Input Timing                                  |    |

| Figure 38 - TDM - McBSP PCMFP and PCM_CLKi Input Timing                                |    |

| Figure 39 - TDM Slave Mode Timing Diagram (clock rate equals data rate)                |    |

| Figure 40 - TDM Master Mode Timing Diagram (clock rate equals data rate)               | 59 |

| Figure 41 - Output Tristate Timing in TDM Slave Mode                                   |    |

| Figure 42 - Output Tristate Timing in TDM Master Mode                                  | 60 |

| Figure 43 - PCMFP and PCM_CLKo TDM Master Mode Timing                                  |    |

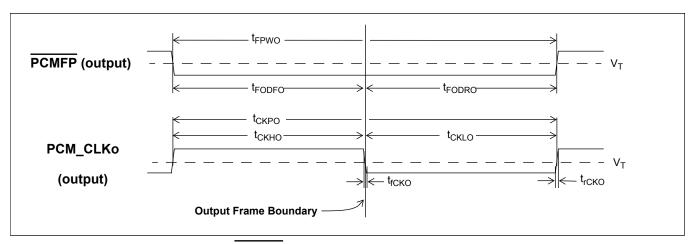

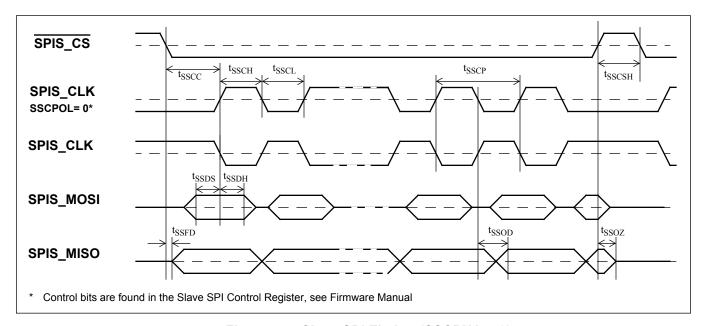

| Figure 44 - Slave SPI Timing (SSCPHA = 0)                                              |    |

| Figure 45 - Slave SPI Timing (SSCPHA = 1)                                              |    |

| Figure 46 - Slave SPI Timing (Microwire mode)                                          |    |

| Figure 47 - Master SPI Timing (MSCPHA = 0)                                             |    |

| Figure 48 - Master SPI Timing (MSCPHA = 1)                                             | 66 |

# **List of Figures**

| Figure 49 - Slave I2S Timing                                        | 67 |

|---------------------------------------------------------------------|----|

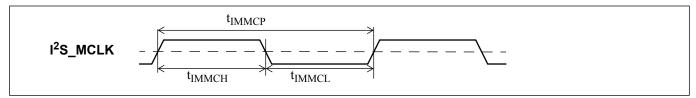

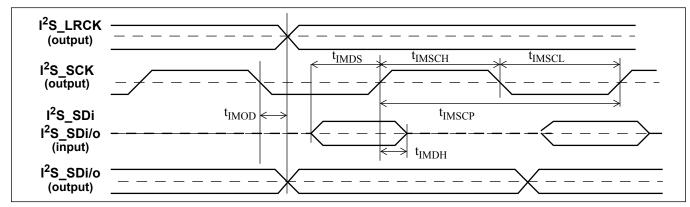

| Figure 50 - I2S Master Clock (MCLK) Timing                          | 68 |

| Figure 51 - Master I2S Timing                                       | 68 |

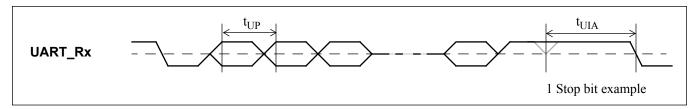

| Figure 52 - UART_Rx Timing                                          | 69 |

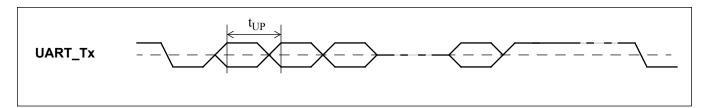

| Figure 53 - UART_Tx Timing                                          | 69 |

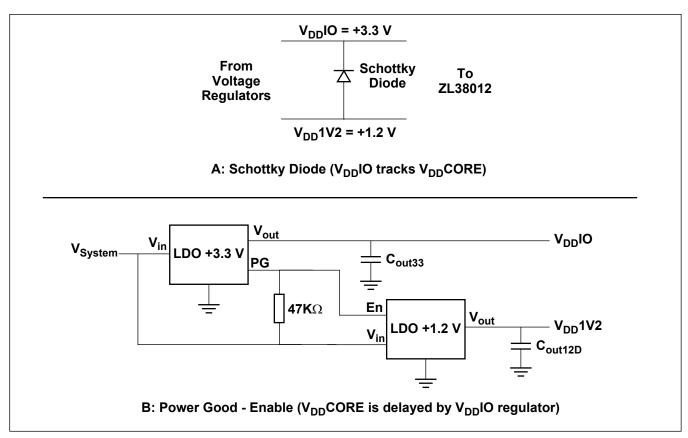

| Figure 54 - Latch-Up Prevention Circuit Options                     | 70 |

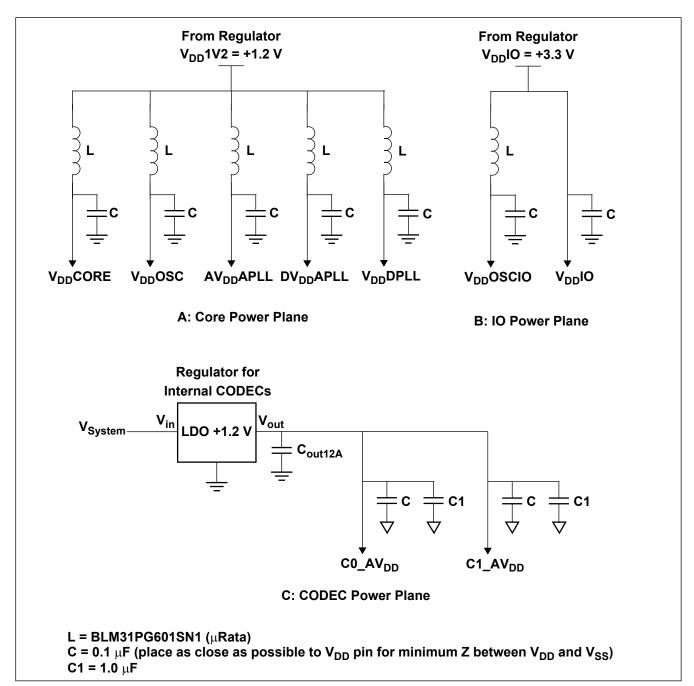

| Figure 55 - Power Supply Isolation                                  | 72 |

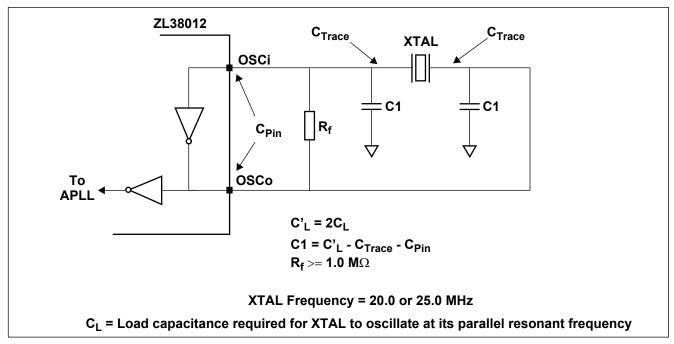

| Figure 56 - Crystal Application Circuit                             | 73 |

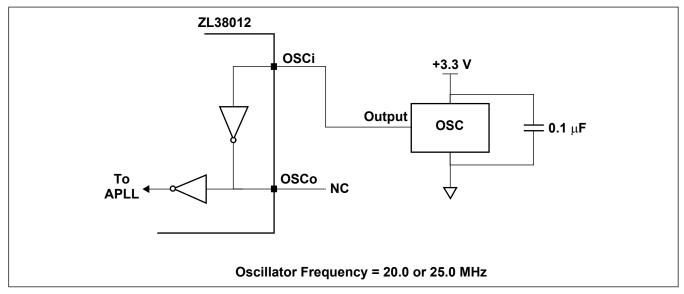

| Figure 57 - Crystal Oscillator Application Circuit                  | 74 |

| Figure 58 - FLASH Interface Circuit                                 | 75 |

| Figure 59 - CODEC 0/1 ADC Differential Microphone Amplifier Circuit | 76 |

| Figure 60 - CODEC 0/1 DAC Differential Driver Circuit               | 77 |

| Figure 61 - CODEC 0/1 DAC Single Ended Driver Circuit               | 77 |

| Figure 62 - CODEC 0/1 Bias Circuit                                  | 78 |

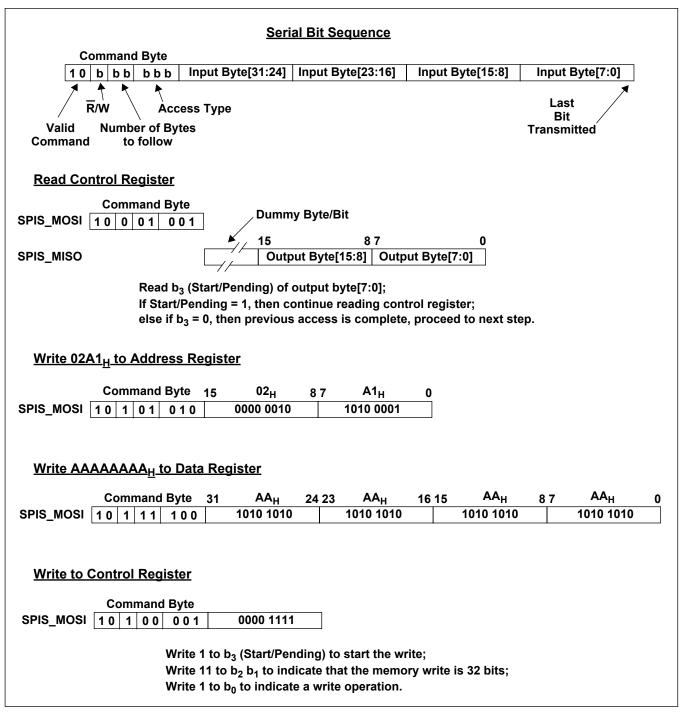

| Figure 63 - SSPI Write AAAAAAAAH to Register Address 02A1H          | 79 |

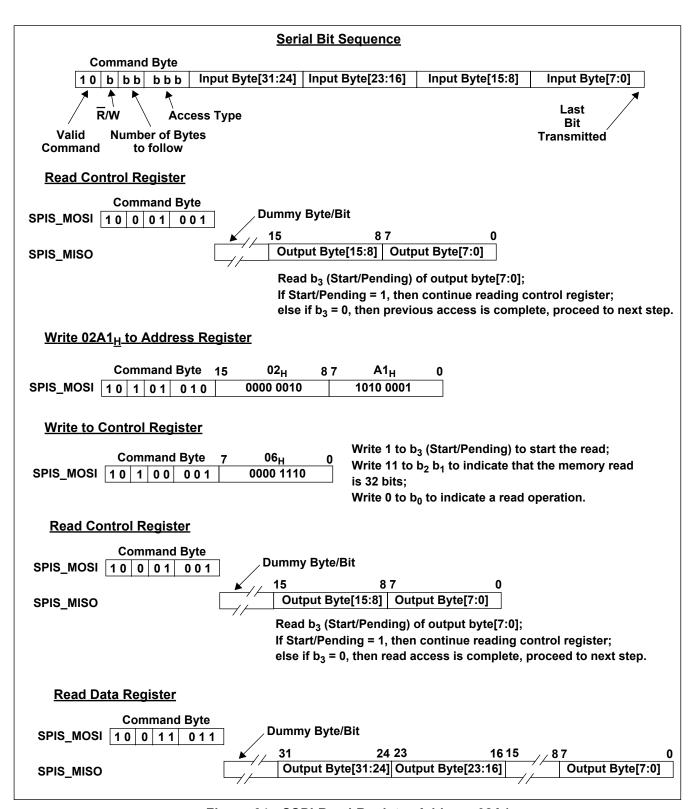

| Figure 64 - SSPI Read Register Address 02A1H                        | 80 |

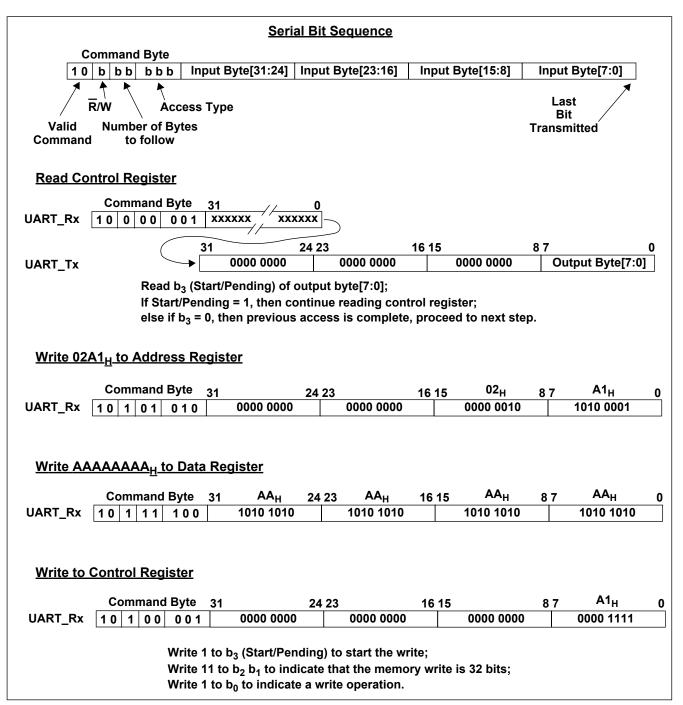

| Figure 65 - UART Write AAAAAAAH to Register Address 02A1H           | 81 |

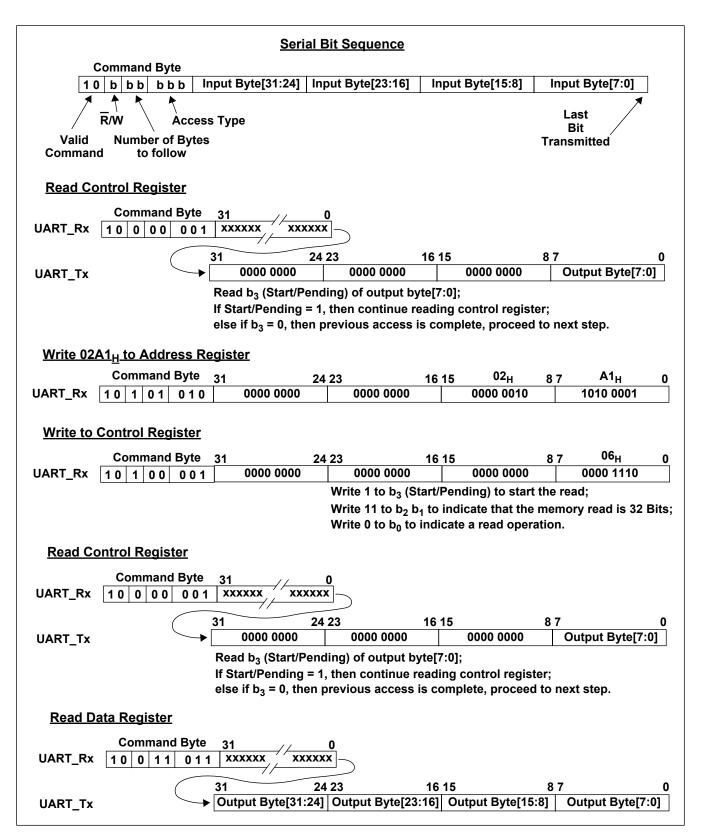

| Figure 66 - LIART Read Register Address 02A1H                       | 82 |

# ZL38012

# **List of Tables**

| Table 1 - JTAG and Reset Pin Description                                                   | 9    |

|--------------------------------------------------------------------------------------------|------|

| Table 2 - Codec[1:0] Pin Description                                                       | 9    |

| Table 3 - Clock and Oscillator Pin Description                                             | . 10 |

| Table 4 - UART and GPIO Pin Description                                                    | . 10 |

| Table 5 - Inter-IC Sound and PCM Port One Pin Description                                  | . 12 |

| Table 6 - Master and Slave SPI Port Pin Descriptions                                       | . 12 |

| Table 7 - Supply and Ground Pin Description                                                | . 12 |

| Table 8 - PCM Port Bit Swapping                                                            | . 19 |

| Table 9 - Stream Data Rates and Associated 8-Bit Time Slot Numbering                       | . 20 |

| Table 10 - PCM Port Mode Description                                                       | . 21 |

| Table 11 - PCM Timing Mode 0 Output Clock and Data Rate Selection                          | . 22 |

| Table 12 - PCM Timing Mode 1 Required Clock Rates for Port Inputs                          | . 22 |

| Table 13 - PCM Timing Mode 2, Required Frame Signal and Clock Rates for Clock = Data Rates | . 23 |

| Table 14 - PCM Timing Mode 3 Output Clock and Data Rate Selection                          | . 24 |

| Table 15 - PCM Timing Mode 4 Required Clock Rates for PCM Port Inputs                      | . 24 |

| Table 16 - PCM Timing Mode 6 Measured Clock Rate of PCM_CLKi Input                         | . 25 |

| Table 17 - TDM Frame Pulse Selection                                                       | . 26 |

| Table 18 - TDM - ST-BUS, GCI and McBSP Selection                                           | . 26 |

| Table 19 - SSI Enable Start; Enable Finish Position Selection                              | . 29 |

| Table 20 - I2S Port Clock Rate and Mode Selection                                          | . 31 |

| Table 21 - ZL38012 Timing Reference Selection at Power-up                                  | . 44 |

| Table 22 - Recommended Crystals                                                            | . 74 |

| Table 23 - Recommended Crystal Oscillators                                                 | . 75 |

| Table 24 - External FLASH Memory Requirements                                              | . 76 |

Figure 2 - ZL38012 56-Lead QFN 8 mm x 8 mm, 0.5 mm pitch, JEDEC MO-026 (Top View)

## **Pin Description**

| QFN<br>Pin# | Name | Description                                                                                                                                                                                    |

|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3           | RST  | Reset (Schmitt Trigger Input). When low this device is in its reset state and all tristate outputs will be in a high impedance state. This input must be high for normal device operation.     |

|             |      | In order to properly initialize this device during power-on reset this input must be held low for the duration of the core power supply voltage rise to normal operating levels plus 0.5 msec. |

|             |      | After the power-on reset this device may be asynchronously reset by making this input low for a minimum of 0.5 msec.                                                                           |

Table 1 - JTAG and Reset Pin Description

| QFN<br>Pin # | Name     | Description                                                                                                                                                                                                                                                                                                                                 |

|--------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2            | DGUARD   | Digital Guard Ring. Codec digital substrate isolation. Connect to digital ground.                                                                                                                                                                                                                                                           |

| 43           | C0_DACo+ | Codec Zero Digital-to-Analog Converter Out Plus (Analog Output). This is the positive output signal of the differential analog output buffer for DAC zero. The complementary output signal of this differential pair is C0_DACo This output should be AC coupled to a maximum load (minimum impedance) of 10 $K\Omega$ .                    |

| 44           | C0_DACo- | Codec Zero Digital-to-Analog Converter Out Minus (Analog Output). This is the negative output signal of the differential analog output buffer for DAC zero. The complementary output signal of this differential pair is C0_DACo+. This output should be AC coupled to a maximum load (minimum impedance) of 10 K $\Omega$ .                |

| 46           | C0_ADCi- | Codec Zero Analog-to-Digital Converter In Minus (Analog Input). This is the negative input signal of the differential analog input buffer for ADC zero. The complementary input signal of this differential pair is C0_ADCi+. This input should be AC coupled. In MIC mode on-chip resistors are used to set the gain of this buffer stage. |

| 47           | C0_ADCi+ | Codec Zero Analog-to-Digital Converter In Plus (Analog Input). This is the positive input signal of the differential analog input buffer for ADC zero. The complementary input signal of this differential pair is C0_ADCi This input should be AC coupled. In MIC mode on-chip resistors are used to set the gain of this buffer stage.    |

| 48           | AGUARD   | Analog Guard Ring. Codec analog substrate isolation. Connect to analog ground.                                                                                                                                                                                                                                                              |

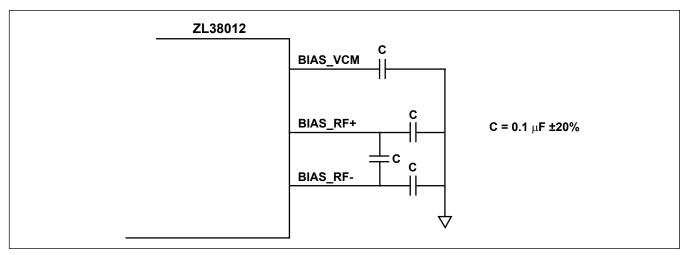

| 49           | BIAS_VCM | Bias Voltage Common Mode (Analog Output). Common mode bias voltage output signal for the DAC output buffers. This signal is to be decoupled through a $0.1~\mu F$ ceramic capacitor to analog ground. This output signal should not be used to bias external circuits. See 8.0, "Applications" on page 70 of this design manual.            |

| 50           | BIAS_RF+ | Bias Reference Plus (Analog Output). Analog-to-digital converter reference voltage. Connect a 0.1 $\mu$ F ceramic capacitor between this signal and BIAS_RF Additionally, this signal may also be decoupled through a 0.1 $\mu$ F ceramic capacitor to analog ground. See 8.0, "Applications" on page 70 of this design manual.             |

| 51           | BIAS_RF- | Bias Reference Minus (Analog Output). Analog-to-digital converter reference voltage. Connect a 0.1 $\mu$ F ceramic capacitor between this signal and BIAS_RF+. Additionally, this signal may also be decoupled through a 0.1 $\mu$ F ceramic capacitor to analog ground. See 8.0, "Applications" on page 70 of this design manual.          |

Table 2 - Codec[1:0] Pin Description

| QFN<br>Pin # | Name     | Description                                                                                                                                                                                                                                                                                                                               |

|--------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52           | C1_ADCi+ | Codec One Analog-to-Digital Converter In Plus (Analog Input). This is the positive input signal of the differential analog input buffer for ADC one. The complementary input signal of this differential pair is C0_ADCi This input should be AC coupled. In MIC mode on-chip resistors are used to set the gain of this buffer stage.    |

| 53           | C1_ADCi- | Codec One Analog-to-Digital Converter In Minus (Analog Input). This is the negative input signal of the differential analog input buffer for ADC one. The complementary input signal of this differential pair is C0_ADCi+. This input should be AC coupled. In MIC mode on-chip resistors are used to set the gain of this buffer stage. |

| 55           | C1_DACo- | Codec One Digital-to-Analog Converter Out Minus (Analog Output). This is the negative output signal of the differential analog output buffer for DAC one. The complementary output signal of this differential pair is C1_DACo+. This output should be AC coupled to a maximum load (minimum impedance) of 10 $K\Omega$ .                 |

| 56           | C1_DACo+ | Codec One Digital-to-Analog Converter Out Plus (Analog Output). This is the positive output signal of the differential analog output buffer for DAC one. The complementary output signal of this differential pair is C1_DACo This output should be AC coupled to a maximum load (minimum impedance) of $10~\mathrm{K}\Omega$ .           |

Table 2 - Codec[1:0] Pin Description

| QFN<br>Pin# | Name | Description                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 38          | OSCo | Oscillator Output (Output). Drive output for an external crystal to form a crystal oscillator circuit with the internal driver. The crystal is to be connected between OSCo and OSCi. This pin should be left open when an external oscillator is used instead of an external crystal. This signal is not tristated by the device RST function. See 8.2.1, "Crystal Oscillator Specification" on page 73. |

| 39          | OSCi | <b>Oscillator Input (Input).</b> Input for an external crystal to form a crystal oscillator circuit with the internal driver. The crystal is to be connected between OSCo and OSCi. This pin is the oscillator input when an external 3.3 V +/-10% oscillator is used instead of an external crystal. See 8.2.2, "Clock Oscillator" on page 74 and 8.2.1, "Crystal Oscillator Specification" on page 73.  |

**Table 3 - Clock and Oscillator Pin Description**

| QFN<br>Pin #             | Name      | Description                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4                        | UART_Rx   | Universal Asynchronous Receiver/Transmitter Receive (Schmitt Trigger Input). Receive serial data in. In slave mode this port (UART_Tx/Rx) functions as a peripheral interface for an external controller and supports access to the internal registers and memory of the device. The MiniCore3 may use this port in master mode to access external peripherals. |

| 5                        | UART_Tx   | Universal Asynchronous Receiver/Transmitter Transmit (Tristate Output). Transmit serial data out. In slave mode this port (UART_Tx/Rx) functions as a peripheral interface for an external controller and supports access to the internal registers and memory of the device. The MiniCore3 may use this port in master mode to access external peripherals.    |

| 13, 15,<br>16, 27,<br>28 | GPIO[0:4] | General Purpose I/O Zero (Input Internal Pull-Down/Tristate Output). This pin can be configured as an input or output and is intended for low-frequency signalling. GPIO [1:4] must be pulled low on power up.                                                                                                                                                  |

Table 4 - UART and GPIO Pin Description

| QFN<br>Pin# | Name                                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6           | I <sup>2</sup> S_SCK/<br>P1ENA2           | Inter-IC Sound Port Serial Clock (Schmitt Trigger Input/Tristate Output). This is the $I^2S$ port bit clock and operates at selectable rates of 256, 512, 1024, 1411.2 and 1536 kHz, which is $32 \times f_S$ (sampling frequency) of the peripheral converter. In $I^2S$ port master mode this clock is an output and drives the bit clock input of slave mode peripheral converters. In $I^2S$ port slave mode this clock is an input and is driven from a converter operating in master mode. After power-up this signal is in $I^2S$ slave mode, an input.                                                             |

|             |                                           | Port One SSI Enable Strobe Two (Input/Tristate Output). This is an 8/16 kHz 8/16-bit wide enable strobe that operates in SSI mode only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|             |                                           | This signal is an enable strobe input for applications where the Port 1 PCM Bus interface must be frame aligned to an external frame signal (slave mode). In master mode this signal is an enable strobe output. The default state of this signal is input after power up reset.                                                                                                                                                                                                                                                                                                                                           |

| 8           | I <sup>2</sup> S_MCLK/<br>P1P_CLKi/o      | Inter-IC Sound Port Master Clock (Schmitt Trigger Input/Tristate Output). For $I^2S$ port master mode operation this is the master clock output for external codec or ADC's MCLK input. $I^2S$ _MCLK clock rates are selectable to be 2.048, 4.096, 8.192, 11.2896 and 12.288 MHz, which is 256 x $f_S$ (sampling frequency) of the peripheral converter. When the $I^2S$ port is in slave mode, this signal is in a high impedance state.                                                                                                                                                                                 |

|             |                                           | <b>Port One PCM Clock Input/Output.</b> When secondary TDM operation is selected this clock operates at 128, 256, 512, 1024, 2048, 4096, 8192 or 16384 kHz and will be either equal or twice the data rate of signals SPCMi/o. In TDM master mode this clock is an output and in TDM slave mode this clock is an input.                                                                                                                                                                                                                                                                                                    |

| 10          | I <sup>2</sup> S_LRCK/<br>P1FP/<br>P1ENA1 | Inter-IC Sound Port Left/Right Clock (Input/Tristate Output). This is the I <sup>2</sup> S port left or right word select clock and operates at selectable rates of 8, 16, 32, 44.1 and 48 kHz, which is equal to the f <sub>S</sub> (sampling frequency) of the peripheral converter. In I <sup>2</sup> S port master mode this clock is an output and drives the left/right clock input of slave mode peripheral converters. In I <sup>2</sup> S port slave mode this clock is an input and is driven from a converter operating in master mode. After power-up this signal is in I <sup>2</sup> S slave mode, an input. |

|             |                                           | Port One PCM Bus Frame Pulse/Port One Enable Strobe One. This is an 8/16 kHz TDM frame alignment reference signal in TDM (ST BUS, GCI or McBSP framing) and in SSI modes. In SSI mode this signal is a 8/16 bit wide enable strobe.                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                                           | This signal may be used as a PCM frame reference input for applications where the PCM bus interface must be frame aligned to an external frame signal (slave mode). In master mode this signal is a frame pulse output. The default state of this signal is input after power up reset.                                                                                                                                                                                                                                                                                                                                    |

| 11          | I <sup>2</sup> S_SDo<br>P1PCMo            | Inter-IC Sound Port Serial Data Output (Tristate Output). This is the I <sup>2</sup> S port data input signal when the port is in master mode and configured to work with two ADC's. This is the I <sup>2</sup> S port data output signal when the port is in master mode and configured to work with a single codec.                                                                                                                                                                                                                                                                                                      |

|             |                                           | <b>Port One PCM Serial Stream Output.</b> This serial data stream operates in either TDM (ST BUS, GCI or McBSP framing) or SSI modes at data rates of 128, 256, 512, 1024, 2048, 4096, 8192 or 16384 Kb/s. Each 8 kHz frame supports 16, 32, 64, 128, 256, 512, 1024 or 2048 channels of 8 bits or half as many 16 bit channels. Two 8 or 16 bit channels may be processed per frame.                                                                                                                                                                                                                                      |

| QFN<br>Pin # | Name                            | Description                                                                                                                                                                                                                                                                                                                                                                                  |  |

|--------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 12           | I <sup>2</sup> S_SDi/<br>P1PCMi | Inter-IC Sound Port Serial Data Input (Input). This is the I <sup>2</sup> S port serial data input.                                                                                                                                                                                                                                                                                          |  |

|              |                                 | <b>Port One PCM Serial Stream Input (Input).</b> This serial data stream operates in either TDM (ST BUS, GCI or McBSP framing) or SSI modes at data rates of 128, 256, 512, 1024, 2048, 4096, 8192 or 16384 Kb/s. Each 8 kHz frame supports 16, 32, 64, 128, 256, 512, 1024 or 2048 channels of 8 bits or half as many 16 bit channels. Two 8 or 16 bit channels may be processed per frame. |  |

Table 5 - Inter-IC Sound and PCM Port One Pin Description

| QFN<br>Pin # | Name       | Description                                                                                                                                                                                                                                                              |  |  |

|--------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 17           | SPIS_MOSI  | Serial Peripheral Interface Slave Port Data Input (Input). Data input signal for the Slave SPI port.                                                                                                                                                                     |  |  |

| 18           | SPIS_CS    | Serial Peripheral Interface Slave Chip Select (Input). This active low chip select signal activates the Slave SPI port. This port functions as a peripheral interface for an external controller and supports access to the internal registers and memory of the device. |  |  |

| 19           | SPIS_MISO  | Serial Peripheral Interface Slave Port Data Output (Tristate Output). Data output signal for the Slave SPI port.                                                                                                                                                         |  |  |

| 20           | SPIS_CLK   | Serial Peripheral Interface Slave Port Clock (Schmitt Trigger Input). Clock input for the Slave SPI port. Maximum frequency = 25 MHz.                                                                                                                                    |  |  |

| 22           | SPIM_CLK   | Serial Peripheral Interface Master Port Clock (Tristate Output). Clock output for the Master SPI port. Maximum frequency = 25 MHz.                                                                                                                                       |  |  |

| 23           | SPIM_MOSI  | Serial Peripheral Interface Master Port Data Input (Tristate Output). Data output signal for the Master SPI port.                                                                                                                                                        |  |  |

| 25           | SPIM_CS[0] | Serial Peripheral Interface Master Port Select Zero (Tristate Output). This active low chip select is normally used to access an external peripheral such as FLASH memory.                                                                                               |  |  |

| 26           | SPIM_MISO  | Serial Peripheral Interface Master Port Data Output (Input). Data input signal for the master SPI port.                                                                                                                                                                  |  |  |

Table 6 - Master and Slave SPI Port Pin Descriptions

| QFN<br>Pin #                | Name                 | Description                                     |

|-----------------------------|----------------------|-------------------------------------------------|

| 1, 14,<br>30, 32,<br>34, 42 | V <sub>SS</sub>      | Core Ground. Connect to digital ground.         |

| 7, 24,<br>33                | V <sub>DD</sub> CORE | Core Supply. Connect to +1.2 V ±5% core supply. |

Table 7 - Supply and Ground Pin Description

| QFN<br>Pin#  | Name                  | Description                                                                               |  |  |

|--------------|-----------------------|-------------------------------------------------------------------------------------------|--|--|

| 9, 21,<br>31 | V <sub>DD</sub> IO    | I/O Supply. Connect to +3.3 V ±10% supply for Input/Output drivers.                       |  |  |

| 35           | V <sub>DD</sub> DPLL  | Digital PLL Supply. Connect to +1.2 V ±5% DPLL supply.                                    |  |  |

| 36           | V <sub>DD</sub> OSC   | Oscillator Supply. Connect to +1.2 V ±5% oscillator supply.                               |  |  |

| 37           | V <sub>DD</sub> OSCIO | Oscillator I/O Supply. Connect to +3.3 V ±10% supply for oscillator Input/Output drivers. |  |  |

| 40           | DV <sub>DD</sub> APLL | Analog PLL Digital Supply. Connect to +1.2 V ±5% APLL digital supply.                     |  |  |

| 41           | AV <sub>DD</sub> APLL | Analog PLL Analog Supply. Connect to +1.2 V ±5% APLL analog supply.                       |  |  |

| 45           | C0_AV <sub>DD</sub>   | Codec Zero Analog Supply. Connect to +1.2 V ±5% voice codec [0] analog supply.            |  |  |

| 54           | C1_AV <sub>DD</sub>   | Codec One Analog Supply. Connect to +1.2 V ±5% voice codec [1] analog supply.             |  |  |

| 29           | NC                    | No Connection. These pins are to be left unconnected.                                     |  |  |

Table 7 - Supply and Ground Pin Description

#### 1.0 Functional Description

The ZL38012 is a hardware platform designed to support advanced acoustic echo canceller (with noise reduction) firmware applications available from Microsemi. These applications are resident in external memory and are downloaded by the ZL38012 resident boot code during initialization.

The firmware products and manuals available at the release of this data sheet are: ZLS385xx: Acoustic Echo Canceller with Noise Reduction for Hands-Free Car Kits. If these applications do not meet your requirements, please contact your local Microsemi CMPG Sales Office for the latest firmware releases.

The ZL38012 Advanced Acoustic Echo Canceller with Noise Reduction platform integrates Microsemi's Voice Processor (ZVP) DSP Core with a number of internal peripherals. These peripherals include the following:

- Two independent  $\Delta\Sigma$  CODECs

- PCM ports ST BUS, GCI, McBSP or SSI operation/2S interface port

- A 2048 tap Filter Co-processor (LMS, FIR and FAP realizations)

- · Two Auxiliary Timers and a Watchdog Timer

- 5 GPIO pins

- A UART interface

- · A Slave SPI port and a Master SPI port

- A timing block that supports master and slave operation

- An IEEE 1149.1 compatible JTAG port

The DSP Core can process up to two 8-bit audio channels or two 16-bit audio channels. These audio channels may originate and terminate with the  $\Sigma\Delta$  CODECs, or be communicated to and from the DSP Core through the PCM/ the I<sup>2</sup>S port.

#### 2.0 Core DSP Functional Block

The ZL38012 DSP Core functional block, illustrated in Figure 1, is made up of a DSP Core, Interrupt Controller, Data RAM, Instruction RAM, BOOT ROM and a ButterFly Hardware Accelerator. This block controls the timing (APLL and Timing Generator), peripheral interfaces and Filter Co-processor through a peripheral address/data/control bus.

The ZL38012 implementation of DSP core and Filter Co-processor have been optimized to efficiently support voice processing applications. These applications are described in detail in the Firmware Manuals associated with this hardware platform.

#### 2.1 DSP

The Core DSP is a 100 MIPS processor realized with two internal memory busses (Harvard architecture) to allow multiple accesses during the same instruction cycle. Instruction memory space consists of a 1 k x 24 bit Boot ROM (3 k bytes) and 8 k x 24 bits of RAM (24 k bytes). Data memory space consists of 1 k x 32 bits of register space (16 k bytes), plus 2 k x 16 bits and 2 k x 24 bits of RAM (26 k bytes) dedicated for the filter co processor that can be reused for different applications. Data memory RAM is 16/32 bit addressable.

The Filter Co-Processor is used by the application firmware to realize the LMS filters up to a maximum of 2048 coefficients (taps).

## 3.0 Codec[1:0]

The ZL38012 has two 16-bit fully differential  $\Delta\Sigma$  CODECs (CODEC 0/1) that meet G.712 requirements at 8 kHz sampling, see Figure 3. The ADC path consists of input signal pins C0/1\_ADCi+ and C0/1\_ADCi- which feed selectable Microphone Amplifier. Once past the buffer the analog signal goes through a low pass antialiasing filter and to a 4<sup>th</sup> order feed-forward  $\Delta\Sigma$  Modulator that produces a Pulse Density Modulated (PDM) signal. Next the PDM signal goes through a Low Pass Decimation Filter and then is converted into a 16-bit parallel word that can be read by the ZL38012 DSP (ADCout[15:0], Figure 3).

The ZL38012 DSP will send 16-bit parallel word samples (DACin[15:0], Figure 3) to the DAC where they are converted to serial data and passed through an interpolation filter followed by a digital  $\Delta\Sigma$  Modulator. The  $\Delta\Sigma$  Modulator generates PDM data, which then passes through a 32-tap FIR reconstruction filter. The reconstructed analog signal is then passed to a unity voltage gain differential output driver and to pins C0/1\_DACo+ and C0/1\_DACo-.

The CODEC bias voltages are generated by an internal bandgap circuit (BIAS\_VCM, BIAS\_RF+ and BIAS\_RF-). See 8.0, "Applications" on page 70 of this design manual for external circuit requirements.

Each ZL38012 CODEC has two loopbacks, see Firmware Manual. When activated, the input analog signal on pins C0/1\_ADC+/- is looped around to C0/1\_DAC+/-. Pulse Density Modulated (PDM) serial data from the ADC Analog  $\Delta\Sigma$  Modulator output is looped around to the input of the DAC Reconstruction Filter. At the same time 16-bit parallel data is looped around from DACin[15:0] to ADCout[15:0]. PDM serial data from the DAC Digital  $\Delta\Sigma$  Modulator is looped around to the input of the ADC Digital Low Pass Decimation Filter.

When the Parallel Loopback is activated the input analog signal on pins C0/1\_ADC+/- is looped around to the C0/1\_DAC+/- output. 16-bit parallel data from the ADC Digital Low Pass Decimation Filter is looped around to the DAC Digital Low Pass Interpolation Filter. This data may be read by the DSP, but parallel data written to the DAC by the DSP will be lost.

CODEC0 and CODCE1 of the ZL38012 may be powered down if they are not required. See Firmware Manual.

Figure 3 - CODEC Block Diagram

#### 3.1 Input Buffer

The internal differential input buffer of the ZL38004 CODECs is configured with a Microphone Amplifier interface with internal gain. The internal feedback resister (R) is programmable for gain settings of 0, 6.02, 12.04, 18.06, 24.08 and 30.10 dB for an input maximum differential voltage of 800 to 25 mVppd. Full scale ADC input voltage is 800 mVppd (9 dBm0), which represents full scale 2s complement codes of ±32767. In this application C0/1\_BFo+/-outputs should be left open and C0/1\_ADCi+/- are to be capacitively coupled.

Figure 4 - CODEC 0/1 ADC Microphone Amplifier Selected

#### 3.2 Reconstruction Filter and Driver (DAC Output)

The full scale DAC output voltage is 1200 mVppd (9 dBm0), which represents full scale 2s complement codes of  $\pm 32767$  when driving a minimum load of 10 K $\Omega$ . See section 8.0, "Applications" on page 70 of this design manual for details.

The DAC reconstruction filter reduces the out of band noise at the DAC output caused by the DAC delta-sigma modulator. The modulator contributes very little noise up to 30 kHz. However, even with the reconstruction filter, the DAC output will look noisy when view on an oscilloscope due to residual out of band modulator noise. At 1 MHz, the noise contained within a 300 Hz band is less than -40 dBm0.

#### 4.0 PCM Port

#### 4.1 PCM Port

The PCM port support data communication between an external peripheral device and the ZL38012 DSP Core using separate input (PCMi) and output (PCMo) serial streams with TDM (i.e., ST-BUS, GCI or McBSP) or SSI interface timing. Access to the control and status registers associated with these ports is through the Slave SPI port (Pin Description Table 6) or UART (Pin Description Table 4). The PCM Port pin functions are described in Table 5. These port signals are either in their input or high impedance states after a power-on reset and outputs signals PCMo may be put in a high impedance state at any time during normal operation. Refer to the associated Firmware Manual for PCM port control, status and mode selection.

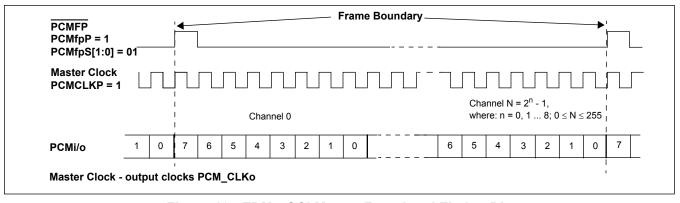

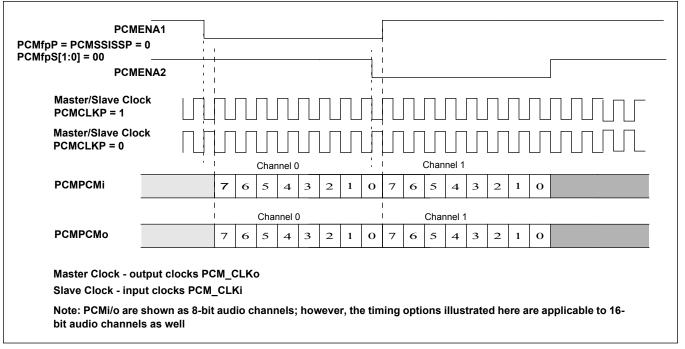

Figure 5 illustrates the signals associated with the Master and Slave timing modes of operation for PCM Port. Insert A: PCM port Master TDM (Mode 0), shows data clock (PCM\_CLKo) and frame pulse (PCMFP) as outputs derived from the ZL38012 internal PLL. PCM\_CLKo clocks data into the ZL38012 on PCMCMi and out of the ZL38012 on PCMo, and PCMFP delineates the 8 kHz frame boundaries for these signals. Insert B: PCM Master SSI (Mode3), functions the same way as the TDM Master except that selected channels are defined by enable outputs P0ENA1 and P0ENA2.

With slave operation the source of timing is not the ZL38012, so PCM\_CLKi is the input clock and PCMFP is the 8 kHz input frame pulse. This is illustrated by Figure 5 C: PCM Port Slave TDM (Modes 1 & 2) and D: PCM Port Slave SSI (Modes 4, 5 & 6). See 4.2, "PCM Port Modes of Operation" for port mode descriptions.

Figure 5 - PCM Port Signal Configurations for Master/Slave Operation

The ZL38012 will process audio channels of up to 16 bits in length. Audio channel sizes are designated as either 8-bit (Short) or 16-bit (Long) on the PCM interfaces. With TDM operation each audio channel is mapped on to one or more 8-bit time slots that are defined by the associated frame alignment signal. Each PCM port (0 & 1) supports from 1 to 4 Short Channels; 1 or 2 Short Channels and 1 Long (16-bit) Channel; or 2 Long Channels. Audio channels are defined as First and Second Long, and First, Second, Third and Fourth Short, see the Firmware Manual for assignment details. These channels may be assigned to different time slots on the input and output streams.

In SSI mode each PCM port supports 1 or 2 Short or Long channels, which are defined on PCMi/0 by the position and length of enable signals P0ENA1 and P0ENA2. Audio channels are defined as First and Second Long, and First and Third Short, see the Firmware Manual for assignment details. Channel positions and length are common to input and output signals.

The data clock rate (PCM\_CLKi) of the PCM interface may be selected to be either true and inverted polarity, see Figure 6. The frame rate is 8 kHz.

Figure 6 - Clock Polarity versus Data Rate

Audio channel data clocked in on PCMi may be sampled at either the 1/2 or 2/2 bit positions.

Figure 7 - PCM Serial Data Input Sampling Points

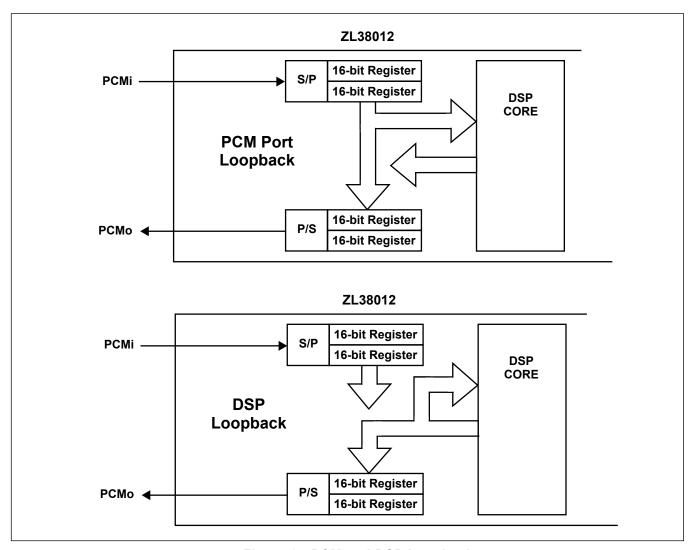

The PCM Ports support two loopbacks, which function in both TDM and SSI modes of operation. That is, a PCM Port Loopack that loops the assigned input audio channels on PCMi to the assigned output audio channels on PCMo, see Figure 8. Throughput delay for specific audio channel bits from PCMi to PCMo is two frames when the data clock rate is twice the data rate and the number of clock cycles/frame  $\geq$  42 or when the clock rate is the same as the data rate and the number of clock cycles/frame  $\geq$  21, otherwise throughput delay is three frames. Audio channel data is also passed to the DSP Core input. The DSP Loopback loops the audio channel data output from the DSP Core to the DSP Core input. Audio channel data is also passed to the PCMo output.

Figure 8 - PCM and DSP Loopbacks

The bit sequence used for 8 and 16-bit audio channels may be reversed (swapped) between the PCM inputs/outputs and the DSP Core. Table 8 shows that when bit swapping is activated and  $b_{15}/b_7$  is the bit transmitted first (MSB) on PCMi/o, the DSP Core will process audio channels as if  $b_0$  is the Most Significant Bit (MSB).

| Bit<br>Swapping | Audio Channel<br>Length (bits) | PCMi/o Transmission<br>(First Last)                                                                                       | DSP Core Processing (MSB LSB)                                                                                                                                                                                                                            |

|-----------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| De-activated 8  |                                | b <sub>7</sub> b <sub>6</sub> b <sub>5</sub> b <sub>4</sub> b <sub>3</sub> b <sub>2</sub> b <sub>1</sub> b <sub>0</sub>   | b <sub>7</sub> b <sub>6</sub> b <sub>5</sub> b <sub>4</sub> b <sub>3</sub> b <sub>2</sub> b <sub>1</sub> b <sub>0</sub>                                                                                                                                  |

|                 | 16                             | $\begin{array}{c} b_{15}b_{14}b_{13}b_{12}b_{11}b_{10}b_{9}b_{8}b_{7}b_{6}b_{5}b_{4}b_{3} \\ b_{2}b_{1}b_{0} \end{array}$ | b <sub>15</sub> b <sub>14</sub> b <sub>13</sub> b <sub>12</sub> b <sub>11</sub> b <sub>10</sub> b <sub>9</sub> b <sub>8</sub> b <sub>7</sub> b <sub>6</sub> b <sub>5</sub> b <sub>4</sub> b <sub>3</sub><br>b <sub>2</sub> b <sub>1</sub> b <sub>0</sub> |

| Activated       | 8                              | b <sub>7</sub> b <sub>6</sub> b <sub>5</sub> b <sub>4</sub> b <sub>3</sub> b <sub>2</sub> b <sub>1</sub> b <sub>0</sub>   | b <sub>0</sub> b <sub>1</sub> b <sub>2</sub> b <sub>3</sub> b <sub>4</sub> b <sub>5</sub> b <sub>6</sub> b <sub>7</sub>                                                                                                                                  |

|                 | 16                             | $\begin{array}{c} b_{15}b_{14}b_{13}b_{12}b_{11}b_{10}b_9b_8b_7b_6b_5b_4b_3 \\ b_2b_1b_0 \end{array}$                     | $\begin{array}{c} b_0b_1b_2b_3b_4b_5b_6b_7b_8b_9b_{10}b_{11}b_{12}b_{13} \\ b_{14}b_{15} \end{array}$                                                                                                                                                    |

**Table 8 - PCM Port Bit Swapping**

#### 4.2 PCM Port Modes of Operation

PCM ports 0 and 1 can function in any of seven operational modes numbered 0 to 6. These modes may be grouped into modes with pre-defined time slots (Modes 0, 1, 3 & 4), modes with flexible timing (Modes 2 & 5) and an automatic rate detection mode (Mode 6).

The modes with pre-defined time slots are TDM Master (0), TDM Slave (1), SSI Master (3) and SSI Slave (4), where Master/Slave refers to timing. The data rates, frame rates, bits/frame and 8-bit time slot numbering (TDM modes only) for these modes are listed in Table 9. In the TDM modes each short channel must be assigned to one of these unassigned 8-bit time slots. Each long channel must be assigned to two 8-bit unassigned contiguous time slots in SSI modes, or two 8-bit unassigned contiguous or non-contiguous time slots that do not straddle the physical frame boundaries defined by the frame pulse alignment signals PCMFP in TDM modes.

| Data Rate<br>(kb/sec) | 8-Bit Time Slot Numbering<br>(Bits/frame) |

|-----------------------|-------------------------------------------|

|                       | PCMFP or PCMENA1/2 = 8 kHz                |

| 128                   | 0 - 1 (16)                                |

| 256                   | 0 - 3 (32)                                |

| 512                   | 0 - 7 (64)                                |

| 1024                  | 0 - 15 (128)                              |

| 2048                  | 0 - 31 (256)                              |

| 4096                  | 0 - 63 (512)                              |

| 8192                  | 0 - 127 (1024)                            |

| 16384                 | 0 - 255 (2048)                            |

Table 9 - Stream Data Rates and Associated 8-Bit Time Slot Numbering

Mode 2 is defined as TDM Slave operation with Flexible Clocks and mode 5 is SSI Slave operation with Flexible Clocks. In these modes the number of bits in an 8 kHz frame is programmable. When the data rate is the same as the clock rate on inputs PCM\_CLKi the number of clock/cycles per frame can be any number between 8 to 2047 inclusive. The number of clock/cycles per frame can be any even number between 16 and 2046 when the data rate is half the clock rate.

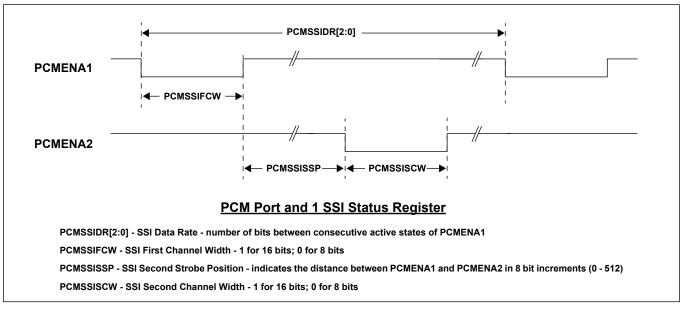

With mode 6, SSI Slave with Automatic Rate Detection, the clock rate must be programmed to be equal to the data rate. Other options that must be programmed are clock polarity, enable signal polarity and the input bit sampling points on PCMi. The ZL38012 will automatically detect the number of clock cycles between consecutive active states of PCMENA1, the width of the active state of ENA1 to be either 8 or 16 bits, the width of the active state of PCMENA2 to be either 8 or 16 bits, and the number of bits between the end of the active state of PCMENA1 and the beginning of the active state of PCMENA2. This is illustrated by Figure 10. These variables are reported in the SSI Status registers for verification purposes and do not need to be written to other registers for normal mode 6 operation.

In SSI mode applications PCMENA1 must always be used. If two audio channels are to be processed, then PCMENA1 and PCMENA2 will both be used.

Figure 10 - Mode 6 - SSI Slave with Automatic Rate Detection

Table 10 shows the Control bit states that select each of the PCM modes. Refer to the Firmware Manual for programming specifics.

| Mada  | DOM Dout Timing Mode Description                                                            | PCM Port Control Register |               |              |         |

|-------|---------------------------------------------------------------------------------------------|---------------------------|---------------|--------------|---------|

| Mode  | PCM Port Timing Mode Description                                                            | Mstr/Slv                  | SSI Md        | SSI Reg      | Flx Clk |

| 0     | TDM Master                                                                                  | 1                         | 0             | Х            | 0       |

| 1     | TDM Slave                                                                                   | 0                         | 0             | Х            | 0       |

| 2     | TDM Slave with Flexible Clocks - see Table 13 to select number of clock cycles per frame.   | 0                         | 0             | Х            | 1       |

| 3     | SSI Master                                                                                  | 1                         | 1             | 1            | 0       |

| 4     | SSI Slave - see Table 15 for bits/frame                                                     | 0                         | 1             | 1            | 0       |

| 5     | 5 SSI Slave with Flexible Clocks - see Table 13 to select number of clock cycles per frame. |                           | 1             | 1            | 1       |

| 6     | 6 SSI Slave with Automatic Rate Detection - see Table 16 for expected bits/frame.           |                           | 1             | 0            | 0       |

| Not r | Not recommended; not considered normal operation.                                           |                           | Remaining bit | combinations | 3       |

**Table 10 - PCM Port Mode Description**

It should be noted that the control bit PPCMRst (PCM Reset) should be programmed from low to high as the last register write when any of the control bits associated with the respective PCM ports is changed. See Firmware Manual for more details.

**Mode 0 (TDM Master)** - in this mode PCMFP and PCM\_CLKo are output signals sourced from the ZL38012 internal timing block. They provide TDM frame, bit alignment and clocking for the time slots of signals PCMPCMi/o. PCMENA2 are in a high impedance state.

In this mode the PCM Port Control Register bits PPCMDR[2:0] is used to establish the PCM data rates of PCMi/o, frame pulse rate of PCMFP and clock rate of PCM CLKo. See Table 11 below.

| Port PCM Control Register - Firmware Manual |                      |                         |  |  |

|---------------------------------------------|----------------------|-------------------------|--|--|

| PPCMDR<br>[2:0]                             | Number of bits/frame | PCM_CLKo Clock<br>Rates |  |  |

| 000                                         | 16*                  | 128                     |  |  |

| 001                                         | 32                   | 256                     |  |  |

| 010                                         | 64                   | 512                     |  |  |

| 011                                         | 128                  | 1024                    |  |  |

| 100                                         | 256                  | 2048                    |  |  |

| 101                                         | 512                  | 4096                    |  |  |

| 110                                         | 1024                 | 8192                    |  |  |

| 111                                         | 2048                 | 16384                   |  |  |

Table 11 - PCM Timing Mode 0 Output Clock and Data Rate Selection

**Mode 1 (TDM Slave)** - in this mode PCMFP is an input, one of the PCM\_CLKi inputs is used as a clock signal (see Pin Description Table 3), and PCMi/o transports PCM data. PCMENA2 and PCM\_CLKo are in a high impedance state. The functional relationship between control bits PCMDR[2:0] and clock signals PCM\_CLKi are shown in Table 12. The frame pulse input must be 8 kHz.

| Port PCM Control Register - Firmware Manual |      |                         |  |  |

|---------------------------------------------|------|-------------------------|--|--|

| PPCMDR [2:0] Number of bits/frame           |      | PCM_CLKi<br>Clock Rates |  |  |

| 000                                         | 16*  | NA                      |  |  |

| 001                                         | 32   | NA                      |  |  |

| 010                                         | 64   | NA                      |  |  |

| 011                                         | 128  | NA                      |  |  |

| 100                                         | 256  | 2048                    |  |  |

| 101                                         | 512  | 4096                    |  |  |

| 110                                         | 1024 | 8192                    |  |  |

| 111                                         | 2048 | 16384                   |  |  |

Table 12 - PCM Timing Mode 1 Required Clock Rates for Port Inputs

<sup>\*</sup> It should be noted that when 8 bits/frame operation is selected only one short virtual channel can enabled; when 16 bits/frame operation is selected only two short or one long virtual channel can be enabled.

<sup>\*</sup> It should be noted that when 8 bits/frame operation is selected only one short virtual channel can enabled; when 16 bits/frame operation is selected only two short or one long virtual channel can be enabled.

**Mode 2 (TDM Slave with Flexible Clocks)** - in this mode PCMFP in an input, one of the or PCM\_CLKi inputs is used as a clock signal, and PPCMi/o transports PCM data. PENA2 and PPCM\_CLKo are in a high impedance state.

In this mode Port PCM Control Register bits PPCMDR[2:0] have no function. PCMi/o data rates are determined from the CCPF[10:0] control bits, the frame signal input PCMFP and input clocks PCM\_LBi or PCM\_CLKi. See Table 13 below.

The CCPF[10:0] can be any number from 8 to 2047 (00000008 $_{\rm H}$  to 000007FF $_{\rm H}$ ), see Table 13.

| CCPF[10:0]<br>(Clock | (Mode 2) Input Signal PCMFP = 8 kHz/<br>(Mode 5) Input Signal PCMENA1/2 = 8 kHz |                  |                   |  |

|----------------------|---------------------------------------------------------------------------------|------------------|-------------------|--|

| Cycles/<br>Frame)    | PCMi/o<br>(Kb/sec)                                                              | PCM_LBi<br>(kHz) | PCM_CLKi<br>(kHz) |  |

| 8                    | 64                                                                              | 64               | NA                |  |

| 9                    | 72                                                                              | 72               | NA                |  |

| 10                   | 80                                                                              | 80               | NA                |  |

|                      |                                                                                 |                  |                   |  |

| 127                  | 1016                                                                            | 1016             | NA                |  |

| 128                  | 1024                                                                            | 1024             | 1024              |  |

| 129                  | 1032                                                                            | 1032             | NA                |  |

|                      |                                                                                 |                  |                   |  |

| 255                  | 2040                                                                            | 2040             | NA                |  |

| 256                  | 2048                                                                            | 2048             | 2048              |  |

| 257                  | 2056                                                                            | 2056             | NA                |  |

|                      |                                                                                 |                  |                   |  |

| 511                  | 4088                                                                            | 4088             | NA                |  |

| 512                  | 4096                                                                            | 4096             | 4096              |  |

| 513                  | 4104                                                                            | 4104             | NA                |  |

|                      |                                                                                 |                  |                   |  |

| 1023                 | 8184                                                                            | 8184             | NA                |  |

| 1024                 | 8192                                                                            | 8192             | 8192              |  |

| 1025                 | 8200                                                                            | 8200             | NA                |  |

|                      |                                                                                 |                  |                   |  |

| 2046                 | 16368                                                                           | 16368            | NA                |  |

| 2047                 | 16376                                                                           | 16376            | NA                |  |

Table 13 - PCM Timing Mode 2, Required Frame Signal and Clock Rates for Clock = Data Rates

**Mode 3 (SSI Master)** - in this mode PCMENA1/2 and PCM\_CLKo are output signals sourced from the ZL38012 internal timing block and PCMi/o transport PCM data, see Table 14. PCMENA1 and PCMENA2 are enable outputs that determine the positions of either 8 or 16 bit audio channels in the PCMi/o streams, see Firmware Manual for programming.

| PCM port Control Register - Firmware Manual |                      |                            |  |  |

|---------------------------------------------|----------------------|----------------------------|--|--|

| PPCMDR<br>[2:0]                             | Number of bits/frame | PCM_CLKo Clock Rates (kHz) |  |  |

| 000                                         | 16*                  | 128                        |  |  |

| 001                                         | 32                   | 256                        |  |  |

| 010                                         | 64                   | 512                        |  |  |

| 011                                         | 128                  | 1024                       |  |  |

| 100                                         | 256                  | 2048                       |  |  |

| 101                                         | 512                  | 4096                       |  |  |

| 110                                         | 1024                 | 8192                       |  |  |

| 111                                         | 2048                 | 16384                      |  |  |

Table 14 - PCM Timing Mode 3 Output Clock and Data Rate Selection

**Mode 4 (SSI Slave)** - in this mode PCMENA1/2 are inputs, one of the PCM\_CLKi inputs for PCM Port are used as clock signals (see Pin Description table), and PCMi/o transport PCM data. PCM\_CLKo is in a high impedance state. The frame pulse input is 8 kHz.

| PCM Port Control Register - Firmware Manual |                      |                    |  |  |

|---------------------------------------------|----------------------|--------------------|--|--|

| PPCMDR<br>[2:0]                             | Number of bits/frame | PCM Port<br>Clocks |  |  |

|                                             |                      | PCM_CLKi<br>(kHz)  |  |  |

| 000                                         | 16*                  | NA                 |  |  |

| 001                                         | 32                   | NA                 |  |  |

| 010                                         | 64                   | NA                 |  |  |

| 011                                         | 128                  | NA                 |  |  |

| 100                                         | 256                  | 2048               |  |  |

| 101                                         | 512                  | 4096               |  |  |

| 110                                         | 1024                 | 8192               |  |  |

| 111                                         | 2048                 | 16384              |  |  |

Table 15 - PCM Timing Mode 4 Required Clock Rates for PCM Port Inputs

In this mode the SSIDR[2:0] bits of the SSI Status Register (See Firmware Manual) can be used to monitor the number of bits per frame with 8 kHz strobe signals.

<sup>\*</sup> It should be noted that when 8 bits/frame operation is selected only one short virtual channel can enabled; when 16 bits/frame operation is selected only two short or one long virtual channel can be enabled.

<sup>\*</sup> It should be noted that when 8 bits/frame operation is selected only one short virtual channel can enabled; when 16 bits/frame operation is selected only two short or one long virtual channel can be enabled.

**Mode 5 (SSI Slave with Flexible Clocks)** - in this mode PCMENA1/2 are inputs, one of the or PCM\_CLKi inputs for PCM Port are used as clock signals (see Pin Description table), and PCMi/o transport PCM data. PPCM\_CLKo is in a high impedance state.

In this mode PCM Port Control Register bits PPCMDR[2:0] have no function. PCMi/o data rates are determined from the CCPF[10:0] control bits (see Firmware Manual), the frame signal input ENA1, and input clocks PCM\_LBi and PCM\_CLKi. The PCMENA2 strobe input is used to delineate the second SSI short or long audio channel on PCMi/o. See Table 13.

**Mode 6 (SSI Slave with Automatic Rate Detection)** - in this mode PCMENA1/2 are inputs, one of the or PCM\_CLKi inputs for PCM Port is used as a clock signal (see Pin Description table), and PCMi/o transports PCM data. PCM\_CLKo is in a high impedance state. In this mode the PCM interface port will automatically detect the data rate, strobe positions, clock rate and virtual channel sizes. PPCMDR[2:0] have no function. It should be noted that the relationship between the Number of bits/frame and Clock Rates shown in Table 16 is only true when the PCMENA1 input strobe is 8 kHz. When the PCMENA1 input signal is neither 8 kHz, the SSIDR[2:0] status register will indicate the number of bits (clock cycles) per frame.

| PCM Port Control Register - Firmware Manual ZL38500 |                      |                |  |

|-----------------------------------------------------|----------------------|----------------|--|

| SSIDR<br>[2:0]                                      | Number of bits/frame | PCM_CLKi (kHz) |  |

| 000                                                 | 16*                  | NA             |  |

| 001                                                 | 32                   | NA             |  |

| 010                                                 | 64                   | NA             |  |

| 011                                                 | 128                  | NA             |  |

| 100                                                 | 256                  | 2048           |  |

| 101                                                 | 512                  | 4096           |  |

| 110                                                 | 1024                 | 8192           |  |

| 111                                                 | 2048                 | 16384          |  |

Table 16 - PCM Timing Mode 6 Measured Clock Rate of PCM\_CLKi Input

<sup>\*</sup> It should be noted that when 8 bits/frame operation is selected only one short virtual channel can enabled; when 16 bits/frame operation is selected only two short or one long virtual channel can be enabled.

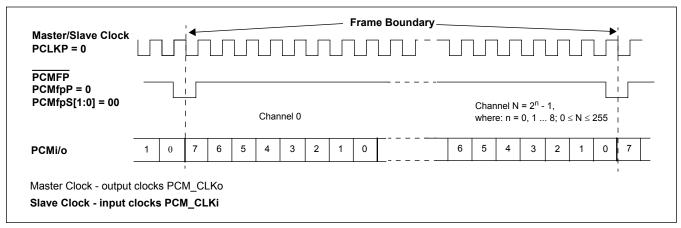

#### 4.3 TDM - ST-BUS, GCI & McBSP Operation

Default frame pulse position is ST-BUS format with the active phase straddling the frame boundary, see Table 17. The frame pulse may also be programmed to have its active phase complete on the frame boundary for McBSP format; and to have its active phase begin on the frame boundary for GCI format. See Firmware Manual for the selection of frame pulse PCMfpS[1:0], clock polarity PCLKP, frame pulse polarity PCMfpP and data rate PPCMDR[2:0].

| Frame Pulse PCMfpS[1:0] | Bus Format | Description                                                        |

|-------------------------|------------|--------------------------------------------------------------------|

| 00                      | ST-BUS     | Active phase straddles frame boundary.                             |

| 01                      | GCI        | Active phase starts at the frame boundary.                         |

| 10                      | McBSP      | Active phase starts one TDM clock cycle before the frame boundary. |

| 11                      | Reserved   | Reserved.                                                          |

**Table 17 - TDM Frame Pulse Selection**

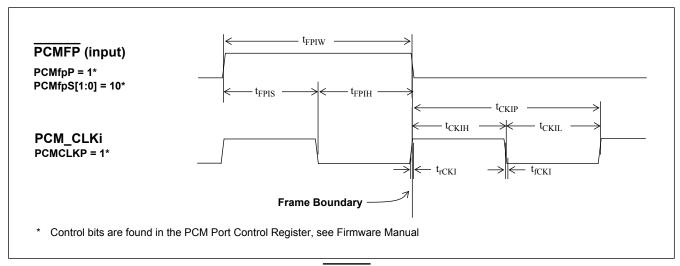

Figure 11 illustrates the ST-BUS format with master or slave timing (see Table 10). This requires selecting the frame pulse as ST-BUS, the frame pulse polarity must be active low (PCMfpP = 0), the PCM clock polarity must be set so the clock falling edge occurs on the frame boundary (PCLKP = 0). In this format frames are delineated by the last falling edge of the bit clock that occurs during the active low frame pulse, see AC Electrical Characteristics. The frame pulse rate is 8 kHz. This programming is shown in Table 18.

| Bus Format | PCMfpS[1:0] | PCMfpP | PCLKP |

|------------|-------------|--------|-------|

| ST-BUS     | 00          | 0      | 0     |

| GCI        | 01          | 1      | 1     |

| McBSP      | 10          | 1      | 1     |

Table 18 - TDM - ST-BUS, GCI and McBSP Selection

Figure 11 - TDM - ST-BUS Slave/Master Functional Timing Diagram

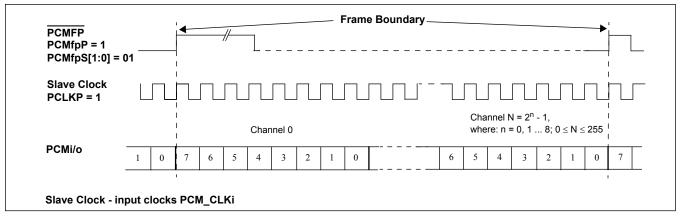

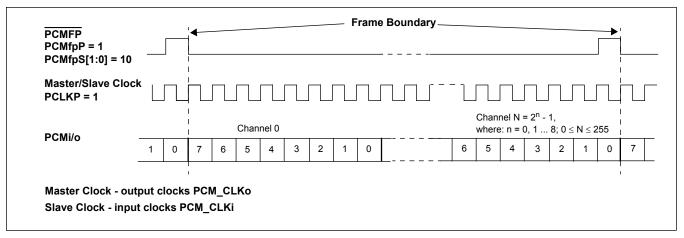

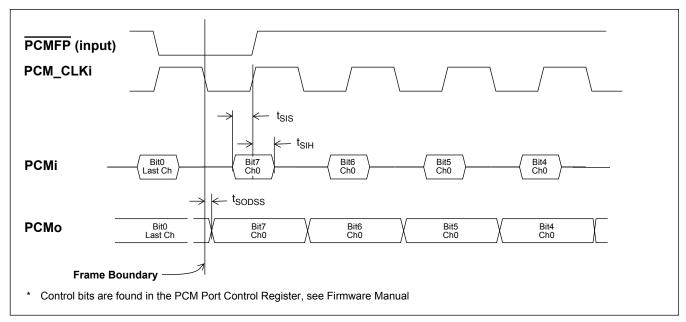

Figure 12 illustrates the GCI format with slave timing (see Table 10). This requires selecting the frame pulse as GCI, the frame pulse polarity must be active high (PCMfpP = 1), the PCM clock polarity must be set so the clock rising edge occurs on the frame boundary (PCLKP = 1). In this format frames are delineated by the rising edge of the bit clock that occurs immediately before the first falling edge of the bit clock during the active high frame pulse, see AC Electrical Characteristics. The frame pulse rate is 8 kHz. This programming is shown in Table 18.

Figure 12 - TDM - GCI Slave Functional Timing Diagram

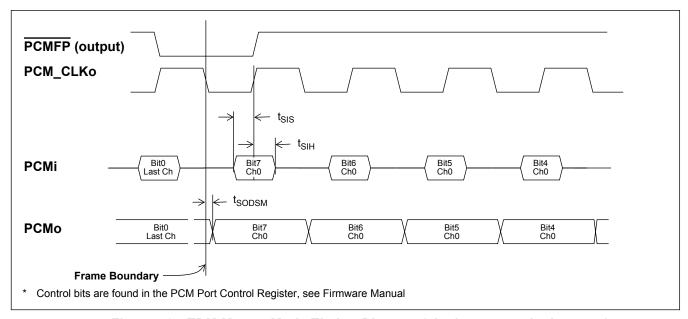

Figure 13 illustrates the GCI format with master timing (see Table 10). This requires selecting the frame pulse as GCI, the frame pulse polarity must be active high (PCMfpP = 1), the PCM clock polarity must be set so the clock rising edge occurs on the frame boundary (PCLKP = 1). In this format frames are delineated by the rising edge of the bit clock that coincides with the rising edge of the active high frame pulse, see AC Electrical Characteristics. This programming is shown in Table 18.

Figure 13 - TDM - GCI Master Functional Timing Diagram

Figure 14 illustrates the McBSP format with master and slave timing (see Table 10). This requires selecting the frame pulse as McBSP, the frame pulse polarity must be active high (PCMfpP = 1), the PCM clock polarity must be set so the clock rising edge occurs on the frame boundary (PCLKP = 1). In this format frames are delineated with slave timing by the last rising edge of the bit clock that occurs immediately after the last falling edge of the bit clock during the active high frame pulse. Frames are delineated in with master timing by the rising edge of the bit clock that coincides with the falling edge of the active high frame pulse, see AC Electrical Characteristics. This programming is shown in Table 18.

Figure 14 - TDM - McBSP Slave/Master Functional Timing Diagram

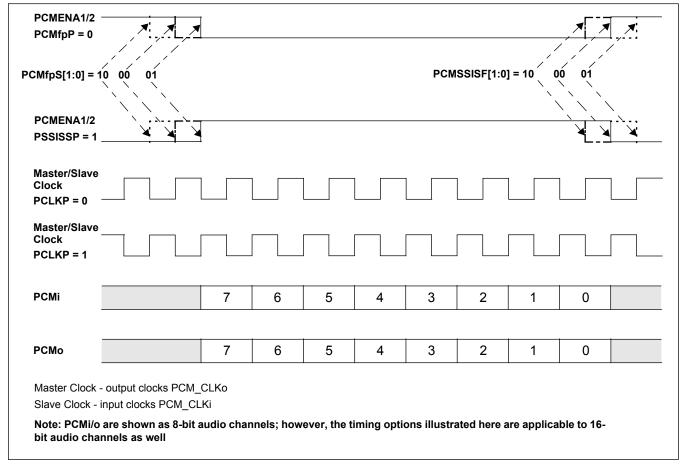

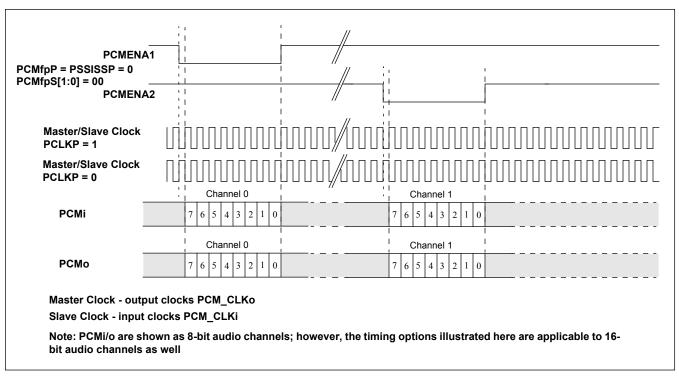

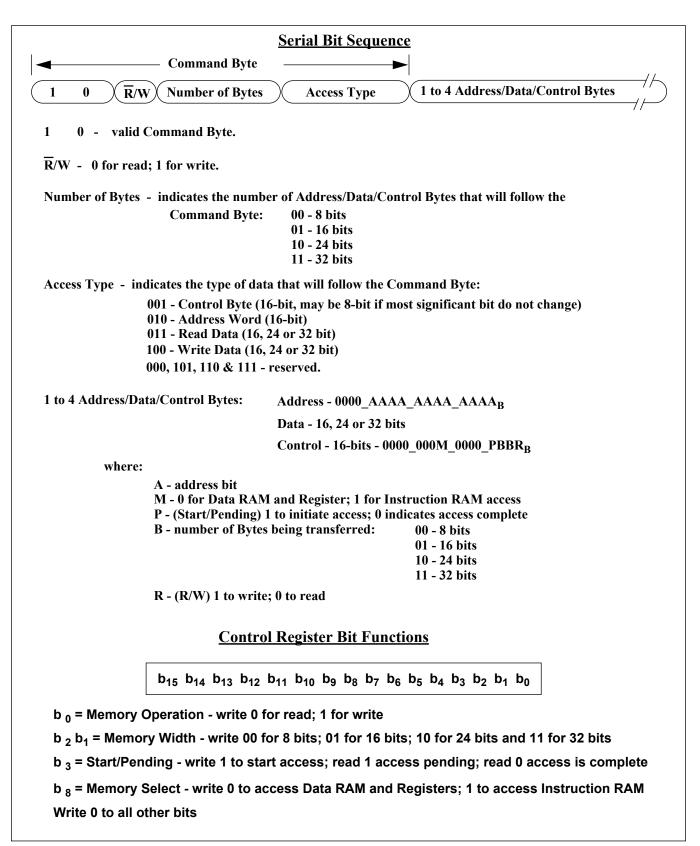

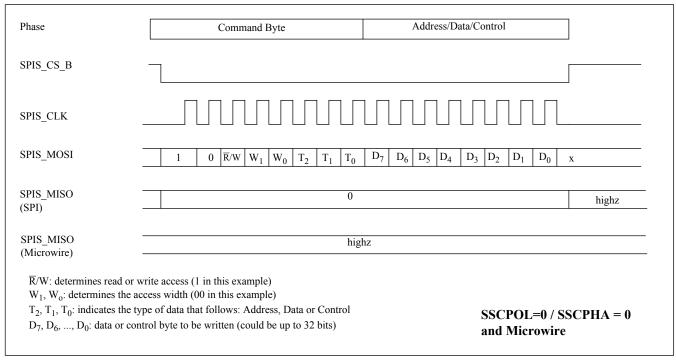

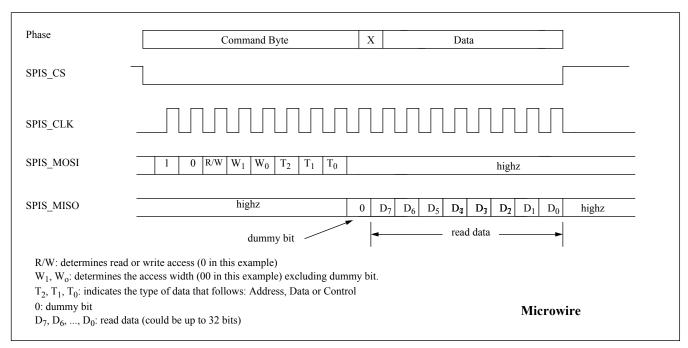

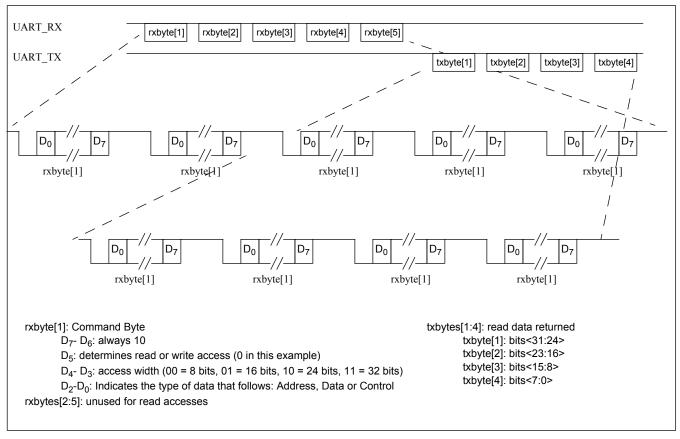

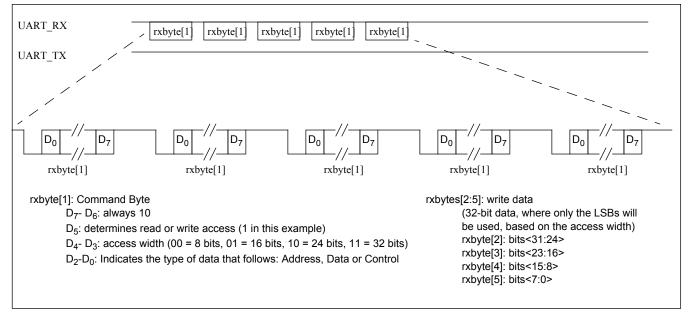

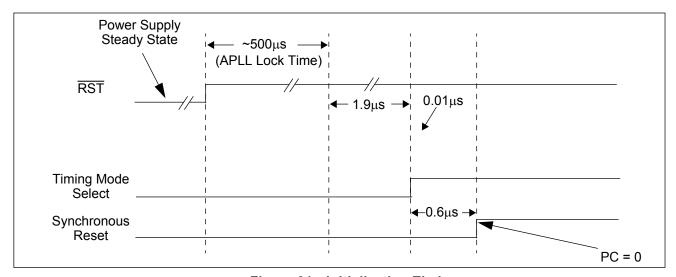

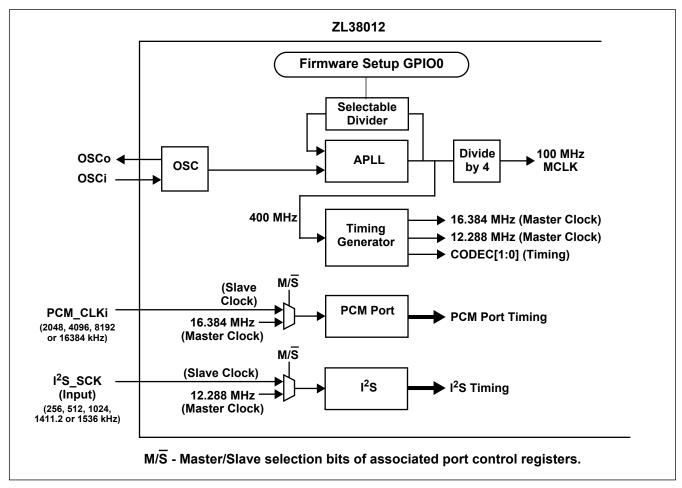

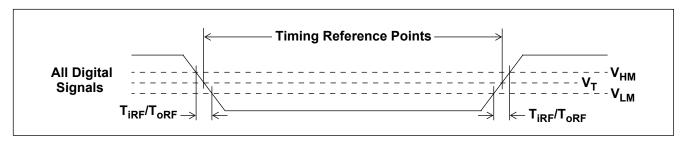

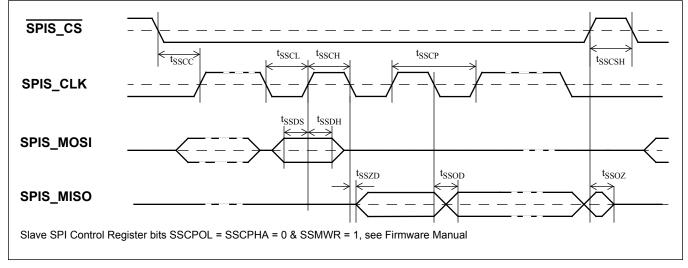

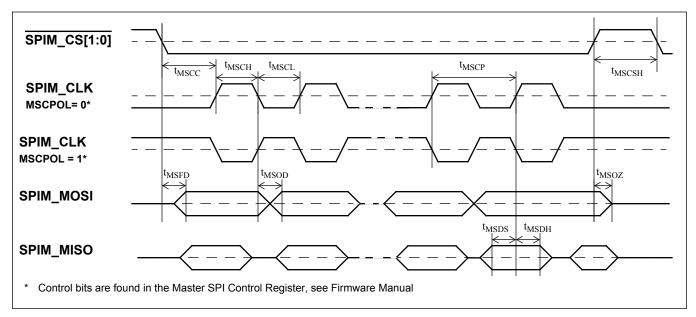

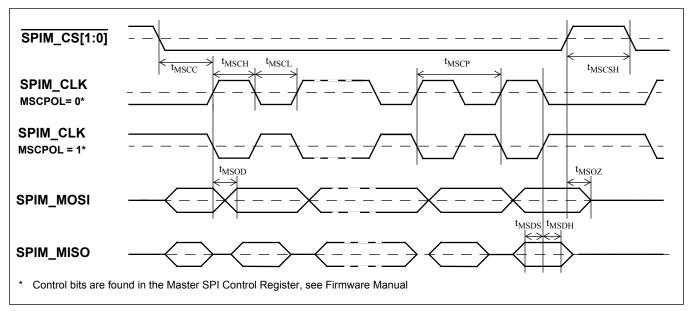

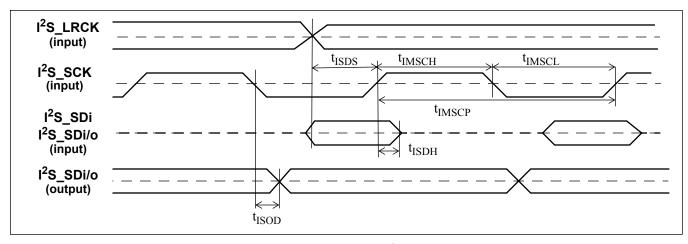

#### 4.4 SSI Operation