# VSC8228-01 Dual Signal Conditional and Retimer

Datasheet

VMDS-10206 Revision 4.1 January 2009

Confidential

Vitesse Corporate Headquarters 741 Calle Plano Camarillo, California 93012 United States

www.vitesse.com

Copyright© 2007, 2009 by Vitesse Semiconductor Corporation

Vitesse Semiconductor Corporation ("Vitesse") retains the right to make changes to its products or specifications to improve performance, reliability or manufacturability. All information in this document, including descriptions of features, functions, performance, technical specifications and availability, is subject to change without notice at any time. While the information furnished herein is held to be accurate and reliable, no responsibility will be assumed by Vitesse for its use. Furthermore, the information contained herein does not convey to the purchaser of microelectronic devices any license under the patent right of any manufacturer.

Vitesse products are not intended for use in life support products where failure of a Vitesse product could reasonably be expected to result in death or personal injury. Anyone using a Vitesse product in such an application without express written consent of an officer of Vitesse does so at their own risk, and agrees to fully indemnify Vitesse for any damages that may result from such use or sale.

Vitesse Semiconductor Corporation is a registered trademark. All other products or service names used in this publication are for identification purposes only, and may be trademarks or registered trademarks of their respective companies. All other trademarks or registered trademarks mentioned herein are the property of their respective holders.

# Contents

| Revi | sion    | History                                                      | .8        |

|------|---------|--------------------------------------------------------------|-----------|

| 1    | Pro     | duct Overview                                                | 9         |

| -    | 1.1     | General Description                                          |           |

|      | 1.2     | Features                                                     |           |

|      | 1.3     | Applications                                                 |           |

|      | 1.4     | Block Diagram                                                |           |

|      |         |                                                              |           |

| 2    | Fun     | ctional Descriptions1                                        | 12        |

|      | 2.1     | Input Buffers                                                |           |

|      |         | 2.1.1 Equalization and Termination                           | 12        |

|      |         | 2.1.2 Analog Signal Detect                                   | 13        |

|      | 2.2     | FibreTimer Clock Recovery Units (CRU)                        | 14        |

|      |         | 2.2.1 Repeater Mode                                          | 14        |

|      |         | 2.2.2 Retimer Mode                                           |           |

|      |         | 2.2.3 Bypass Mode                                            |           |

|      |         | 2.2.4 Controlling the PIO[6:0] and Multiplexer Mode Settings |           |

|      |         | 2.2.5 Considerations for Non-Fibre Channel Applications      |           |

|      |         | 2.2.6 Fibre Channel Protocol Detection.                      |           |

|      |         | 2.2.7 Run-Length Limit (RLL) Detection                       |           |

|      |         | 2.2.8 K28.5– Detection                                       |           |

|      |         | 2.2.9 Protocol Error Signaling                               |           |

|      |         | 2.2.10 Reference Clock                                       |           |

|      |         | 2.2.11 Data Rate Selection                                   |           |

|      | 2.3     | Output Drivers                                               |           |

|      | 2.0     | 2.3.1 De-Emphasis                                            |           |

|      |         | 2.3.2 SGMII Clock Output                                     |           |

|      | 2.4     | TTL Inputs and Outputs                                       |           |

|      | 2.5     | Pattern Generation, Pattern Checking, and Loopback Modes     |           |

|      | 2.6     | Serial Interface Port                                        |           |

|      | 2.0     | 2.6.1 SPI Interface                                          |           |

|      |         | 2.6.2 Two-Wire Serial Interface                              |           |

|      | 2.7     | Power Supply Filtering                                       |           |

|      |         | ······································                       |           |

| 3    | Reg     | isters2                                                      | <u>29</u> |

|      | 3.1     | Register Map                                                 |           |

|      | 3.2     | CMU Status                                                   |           |

|      | 3.3     | Rx Status                                                    | 31        |

|      | 3.4     | Tx Status                                                    |           |

|      | 3.5     | FIFO Status                                                  |           |

|      | 3.6     | Rx Signal Detect Control                                     |           |

|      | 3.7     | Rx Analog Signal Detect Control                              |           |

|      | 3.8     | Tx Signal Detect Control                                     |           |

|      | 3.9     | Tx Analog Signal Detect Control                              |           |

|      |         | Chip Mode Select                                             |           |

|      |         | Receiver Channel FIFO Control                                |           |

|      |         | Transmitter Channel FIFO Control                             |           |

|      |         | Rx Fibre Timer Control                                       |           |

|      |         | Tx Fibre Timer Control                                       |           |

|      | - · · · | Rx Channel Data Control                                      |           |

|      |         | Tx Channel Data Control                                      |           |

|      | 5.10    |                                                              | -11       |

|   | 3.17                                   | CMU Rate Control                                                                                                                                                                                                                                                            |

|---|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 3.18                                   | Rx Clock Divider                                                                                                                                                                                                                                                            |

|   | 3.19                                   | Tx Clock Divider                                                                                                                                                                                                                                                            |

|   | 3.20                                   | Reference Clock Control                                                                                                                                                                                                                                                     |

|   |                                        | RX Channel Input Control                                                                                                                                                                                                                                                    |

|   | 3.22                                   | RX Channel Output Control                                                                                                                                                                                                                                                   |

|   | 3.23                                   | TX Channel Input Control                                                                                                                                                                                                                                                    |

|   | 3.24                                   | Tx Channel Output Control                                                                                                                                                                                                                                                   |

|   | 3.25                                   | Rx Clock Control                                                                                                                                                                                                                                                            |

|   | 3.26                                   | Pattern Checker                                                                                                                                                                                                                                                             |

|   | 3.27                                   | Pattern Checker Timer Setting                                                                                                                                                                                                                                               |

|   | 3.28                                   | Pattern Checker Timer Readback                                                                                                                                                                                                                                              |

|   | 3.29                                   | Pattern Checker Error Counter                                                                                                                                                                                                                                               |

|   | 3.30                                   | Pattern Checker Control                                                                                                                                                                                                                                                     |

|   | 3.31                                   | Pattern Checker Status                                                                                                                                                                                                                                                      |

|   | 3.32                                   | Pattern Generator Pattern                                                                                                                                                                                                                                                   |

|   | 3.33                                   | Pattern Generator Control                                                                                                                                                                                                                                                   |

|   | 3.34                                   | Chip Revision                                                                                                                                                                                                                                                               |

|   |                                        | Chip Identification                                                                                                                                                                                                                                                         |

|   | 3.36                                   | Register Reset                                                                                                                                                                                                                                                              |

| 4 | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | S4S4DC Characteristics54AC Characteristics554.2.1 Two-Wire Serial Interface604.2.2 Serial Peripheral Interface61Operating Conditions63Stress Ratings63Power Sequencing64Termination for Input and Output644.6.1 CML/LVDS Input644.6.2 CML/LVDS Output654.6.3 REFCLK Input65 |

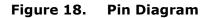

| 5 | Pin                                    | Descriptions                                                                                                                                                                                                                                                                |

|   | 5.1                                    | Pin Diagram                                                                                                                                                                                                                                                                 |

|   | 5.2                                    | Pin Identifications                                                                                                                                                                                                                                                         |

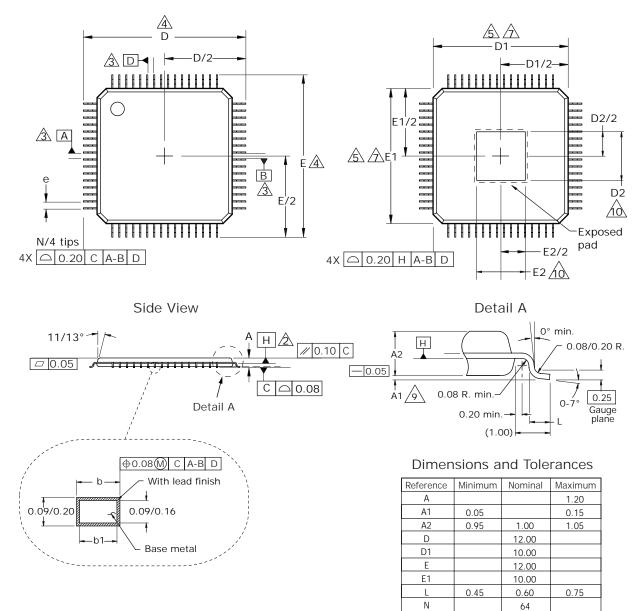

| 6 | Рас                                    | kage Information71                                                                                                                                                                                                                                                          |

|   | 6.1                                    | Package Drawing                                                                                                                                                                                                                                                             |

|   | 6.2                                    | Thermal Specifications                                                                                                                                                                                                                                                      |

|   | 6.3                                    | Moisture Sensitivity                                                                                                                                                                                                                                                        |

| 7 | Ord                                    | ering Information74                                                                                                                                                                                                                                                         |

# Figures

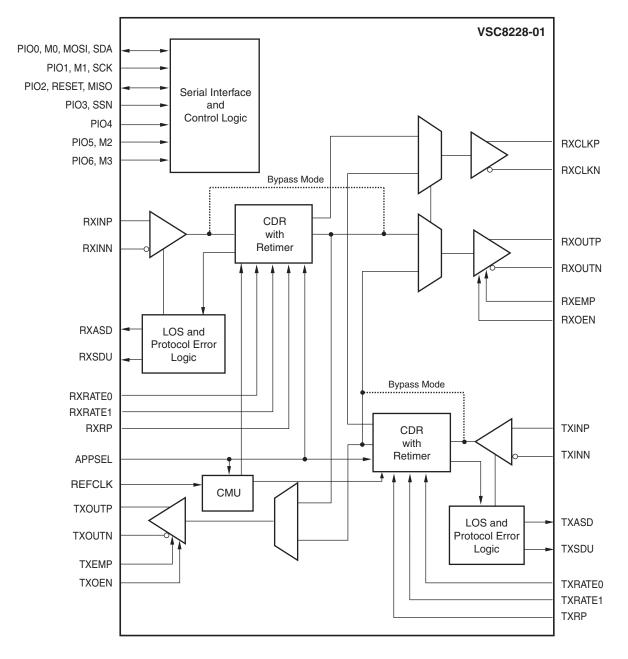

| Figure 1.  | Block Diagram                                               |    |

|------------|-------------------------------------------------------------|----|

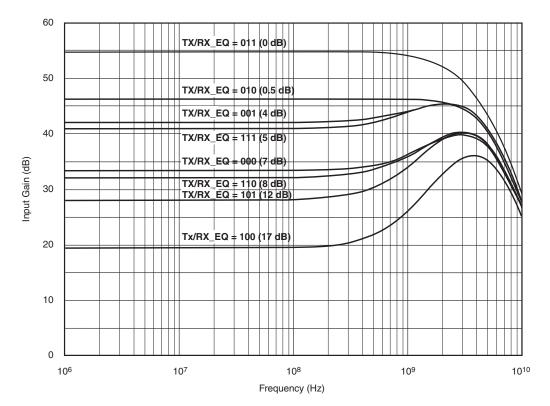

| Figure 2.  | Input Gain, Frequency, and Equalization Settings Comparison |    |

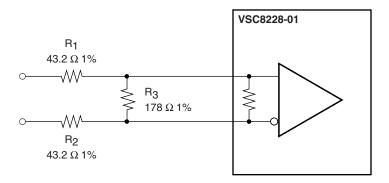

| Figure 3.  | Accommodating 150- $\Omega$ Applications                    |    |

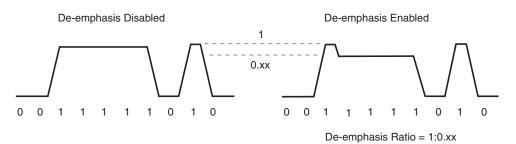

| Figure 4.  | Output De-Emphasis                                          |    |

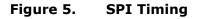

| Figure 5.  | SPI Timing                                                  |    |

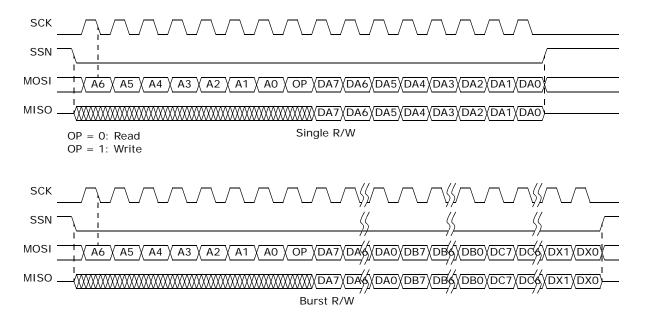

| Figure 6.  | Two-Wire Serial Interface Timing                            |    |

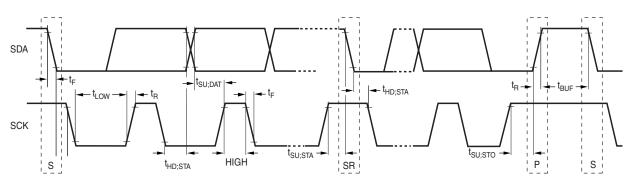

| Figure 7.  | Two-Wire Serial Interface Operation                         |    |

| Figure 8.  | Power Supply Filter                                         |    |

| Figure 9.  | STS-48 SONET Jitter Tolerance Mask                          | 59 |

| Figure 10. | SGMII Clock Timing                                          |    |

| Figure 11. | Two-Wire Serial Interface Timing                            | 61 |

| Figure 12. | Serial Peripheral Interface Timing                          |    |

| Figure 13. | CML/LVDS Inputs Terminated by an Internal 100-Ohm Resistor  | 64 |

| Figure 14. | No Pull-Up Inductor Needed for 1.8-V CML/LVDS Output        |    |

| Figure 15. | Optional Pull-Up Inductor for 1.2-V CML/LVDS Output         |    |

| Figure 16. | LVPECL Differential - DC Coupled                            |    |

| Figure 17. | LVPECL Differential - AC Coupled                            |    |

| Figure 18. |                                                             |    |

| Figure 19. | Package Drawing                                             |    |

# Tables

| Table 1.               | Receiver Loss of Signal Detect Threshold Values                   | . 14 |

|------------------------|-------------------------------------------------------------------|------|

| Table 2.               | PIOx and Multiplexer Mode Selection                               |      |

| Table 3.               | Pin Programming Mode Selection                                    | . 16 |

| Table 4.               | Reference Clock Configuration Support                             |      |

| Table 5.               | Reference Clock Rates by Application                              |      |

| Table 6.               | Hardware Control of Data Rate                                     |      |

| Table 7.               | De-Emphasis Values for Typical Conditions                         |      |

| Table 8.               | Output Slew Rate Values                                           |      |

| Table 9.               | Output Sking Levels                                               |      |

| Table 10.              | Two-Wire Serial Interface 7-Bit Slave Addresses                   |      |

| Table 11.              | Two-Wire Serial Interface Transaction Example Using Slave Address |      |

| Table 11.              | Power Supply Connection Groups by Configuration                   |      |

| Table 12.              | Register Memory Map                                               |      |

|                        |                                                                   |      |

| Table 14.              | CMU Status                                                        |      |

| Table 15.              | Rx Status                                                         |      |

| Table 16.              | Tx Status                                                         |      |

| Table 17.              | FIFO Status                                                       |      |

| Table 18.              | Rx Signal Detect Control                                          |      |

| Table 19.              | Rx Analog Signal Detect Control                                   |      |

| Table 20.              | Tx Signal Detect Control                                          |      |

| Table 21.              | Tx Analog Signal Detect Control                                   |      |

| Table 22.              | Chip Mode Select                                                  |      |

| Table 23.              | Receiver Channel FIFO Control                                     |      |

| Table 24.              | Transmitter Channel FIFO Control                                  |      |

| Table 25.              | Rx Fibre Timer Control                                            |      |

| Table 26.              | Tx Fibre Timer Control                                            | . 39 |

| Table 27.              | Rx Channel Data Control                                           | . 40 |

| Table 28.              | Tx Channel Data Control                                           | . 41 |

| Table 29.              | CMU Rate Control                                                  | . 42 |

| Table 30.              | Rx Clock Divider                                                  | . 42 |

| Table 31.              | Tx Clock Divider                                                  | . 43 |

| Table 32.              | Reference Clock Control                                           | . 43 |

| Table 33.              | RX Channel Input Control                                          | . 44 |

| Table 34.              | RX Channel Output Control                                         | . 45 |

| Table 35.              | TX Channel Input Control                                          | . 46 |

| Table 36.              | Tx Channel Output Control                                         |      |

| Table 37.              | Rx Clock Control                                                  |      |

| Table 38.              | Pattern Checker                                                   |      |

| Table 39.              | Pattern Checker Timer Setting                                     |      |

| Table 40.              | Pattern Checker Timer Readback                                    |      |

| Table 41.              | Pattern Checker Error Counter                                     |      |

| Table 42.              | Pattern Checker Control                                           |      |

| Table 43.              | Pattern Checker Status                                            |      |

| Table 44.              | Pattern Generator Pattern                                         |      |

| Table 45.              | Pattern Generator Control                                         |      |

| Table 46.              | Chip Revision                                                     |      |

| Table 47.              | Chip Identification                                               |      |

| Table 48.              | Register Reset                                                    |      |

| Table 48.              | DC Characteristics                                                |      |

| Table 50.              | AC Characteristics for 1 Gbps and 2 Gbps                          |      |

| Table 50.<br>Table 51. | AC Characteristics for 4 Gbps                                     |      |

| Table 51.<br>Table 52. | Reference Clock                                                   |      |

|                        | Two-Wire Serial Interface AC Signal Characteristics               |      |

| Table 53.              | INVO-VITE JETIAI THEFTALE AU JIVITAI UTATALETISTIUS               | . 00 |

| Table 54. | Serial Peripheral Interface AC Signal Characteristics | . 61 |

|-----------|-------------------------------------------------------|------|

|           | Recommended Operating Conditions                      |      |

|           | Stress Ratings                                        |      |

|           | Pin Identifications                                   |      |

| Table 58. | Thermal Resistances                                   | 73   |

| Table 59. | Ordering Information                                  | 74   |

# **Revision History**

This section describes the changes that were implemented in this document. The changes are listed by revision, starting with the most current publication.

## **Revision 4.1**

Revision 4.1 of this datasheet was published in January 2009. In revision 4.1 of the document, information about controlling modes of operation was added. When controlling modes of operation, it is necessary to power up the VSC8228-01 device in pin programming mode, then to switch to either SPI mode or two-wire serial mode as desired. For more information about the switching procedure, see "Controlling the PIO[6:0] and Multiplexer Mode Settings," page 15.

# **Revision 4.0**

Revision 4.0 of this datasheet was published in January 2007. This was the first production-level publication of the document.

# **1 Product Overview**

# **1.1** General Description

The VSC8228-01 device is a dual repeater or retimer for Fibre Channel, gigabit Ethernet, and Infiniband applications. The VSC8228-01 contains dual FibreTimer clock recovery units (CRU) for bidirectional signal conditioning in system interconnect and serial backplane applications. The device supports rates from 125 Mbps up to 4.25 Gbps. Using a single reference clock for acquisition, the VSC8228-01 retransmits the incoming serial data synchronously to the reference clock in retimer mode or to the incoming data in repeater mode. In retimer mode, add and drop elasticity buffers insert or delete Fibre Channel fill words to compensate for timing differences between the incoming data and the local reference clock.

An analog signal detect function is integrated into both channels. In the retimer and repeater modes, the device monitors the incoming data for run-length violations and K28.5– symbols. The inputs on both the transmit and receive channels can be looped back to the outputs of the opposite channels for diagnostic purposes. The device provides a built-in pattern generator and checker. The receive channel output includes an optional half-rate clock for SGMII applications.

A high degree of signal integrity is maintained by differential I/O, on-chip input and output terminations, input equalization, and output de-emphasis. The programmable input equalization circuit compensates for long printed circuit board (PCB) traces, backplanes, connectors, and cables. Equalization, de-emphasis, output drive levels, data rate, and other features are configured through industry standard serial interfaces (two-wire or SPI).

The device's core and high-speed I/O can be powered from a single 1.2-V power supply, single 1.8-V power supply, or both 1.2-V and 1.8-V power supply. The 1.8-V power supply is required to meet the LVPECL output swing levels. For compatibility with legacy controllers and ASICs, the TTL control and status I/O can be powered with a 1.2-V, 1.8-V, 2.5-V, or 3.3-V power supply. The device has current-mode logic (CML) inputs and outputs that can be AC-coupled for LVPECL and LVDS compatibility. Typical power dissipation for a 1.2-V supply is 360 mW.

## **1.2** Features

The features for the VSC8228-01 device are:

- Dual clock and data recovery architecture for gigabit Ethernet and Fibre Channel applications

- FibreTimer<sup>™</sup> configurable clock recovery unit (CRU): repeater, retimer, or bypassed

- Programmable input signal equalization, output de-emphasis, and output drive levels

- Analog signal detect and protocol monitor indicators

- SPI or two-wire serial interface

- Optional half-rate SGMII clock and repeated reference clock output

- Single 1.2-V power supply, single 1.8-V power supply, or both 1.2-V and 1.8-V power supplies

- 10 mm × 10 mm, 64-pin TQFP package

- 360-mW typical power dissipation

- -10 °C ambient to 105 °C case temperature

# **1.3** Applications

Some of the applications for the VSC8228-01 device are:

- Ethernet: 125 Mbps and 1.25 Gbps

- Fibre Channel: 1.0625 Gbps, 2.125 Gbps, and 4.25 Gbps

- In both retimer mode and repeater mode, the CRU also covers the following speeds: 155.52 Mbps, 622.08 Mbps, and 2488.32 Mbps

- Infiniband<sup>™</sup>: 2.5 Gbps

- ESCON/SBCON: 200 Mbps

- Fibre Channel switches, disk arrays, RAID subsystems, and host bus adapters

- iSCSI SAN host bus adapters and switches

- SFP/SFP signal clean-up

- Serial backplane

## **1.4 Block Diagram**

The block diagram for the VSC8228-01 device is shown in the following figure.

### Figure 1. Block Diagram

# 2 Functional Descriptions

The VSC8228-01 device is divided into four main sections: receive channel (Rx), transmit channel (Tx), pattern generator and checker, and serial interface port. Both the Rx and Tx channels are identical except the Rx channel has an optional half-rate clock for SGMII applications. Both channels contain an input buffer, FibreTimer clock recovery unit (CRU), provisions for loopback, and programmable output drivers. Each channel is controlled independently with separate control and status I/O.

# 2.1 Input Buffers

## 2.1.1 Equalization and Termination

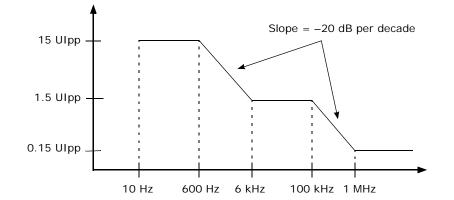

Each high-speed differential input contains an eight-level equalization circuit that attenuates low-frequency signals to compensate for the high-frequency loss that is characteristic of copper cables and traces. The amount of cable equalization can be programmed for each channel for optimal signal quality. The three TX/RX\_EQ[2:0] bits of the RXIN\_CTRL and TXIN\_CTRL registers select one of eight values of equalization. The following graph shows the simulated correlation between input buffer gain and the setting of TX/RX\_EQ[2:0].

#### Figure 2. Input Gain, Frequency, and Equalization Settings Comparison

As trace lengths increase, high-frequency attenuation causes deterministic jitter, or Inter-Symbol Interference (ISI), which increases jitter. Low-frequency components of the signal remain relatively unattenuated, so low-frequency gain is not as important. The VSC8228-01 equalization circuit reduces low-frequency gain, but increases the ratio of high-frequency gain relative to low-frequency gain to reduce the affects of ISI.

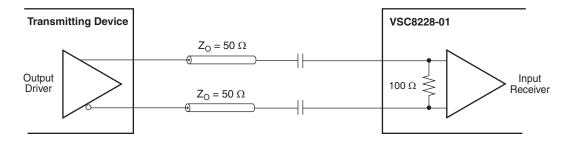

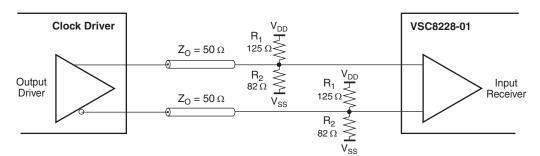

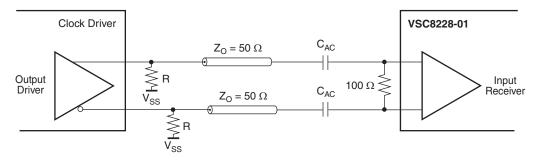

The current industry standards for 4.25-Gbps drives include support for only 100- $\Omega$  media. For applications requiring 150- $\Omega$  differential impedances, external resistors must be added to match the 150- $\Omega$  impedance of the media to the 100- $\Omega$  impedance of the VSC8228-01. The following figure shows an example of a simple external circuit that provides this impedance matching function. The impedance looking into the VSC8228-01 is ~150  $\Omega$ . The impedance looking out of the VSC8228-01 is ~100  $\Omega$ .

#### **Figure 3.** Accommodating $150-\Omega$ Applications

Position the external resistors as closely as possible to the VSC8228-01 device. Because this circuit attenuates the signal by approximately 3.95 dB (~64.3% of output swing), it is necessary to ensure the output signal of the VSC8228-01 has adequate amplitude so that the differential swing meets the minimum output swing specification.

## 2.1.2 Analog Signal Detect

Integrated into the input receivers are independent programmable Analog Signal Detect (ASD) circuits that monitor peak-to-peak signal amplitude as well as signal transitions. The signal is compared to one of four programmable levels. The default value is 100 mV. For more information about the programmable levels, see Table 1, page 14.

If the signal amplitude is below the programmed level or if there are less than 32 transitions within a period of approximately 700 ns, the signal is considered invalid. In the absence of a valid input signal, the condition is flagged by setting the respective ASD pin LOW and the ASD register bit to 0 (RXASD for the Rx Channel or TXASD for the Tx Channel). The device can be configured to squelch the data on a per-channel basis when the data is invalid.

The ASD pin sets itself automatically provided that the input signal is greater than the programmed analog threshold and that there are at least 32 transitions within a

700-ns period. The minimum pulse width of the ASD signal is 700 ns. The invalid signal bit (RXASDERR or TXASDERR) is only cleared after a read to that register.

| Loss of Signal Threshold Values |      |           |      |      |  |  |  |  |

|---------------------------------|------|-----------|------|------|--|--|--|--|

| RX/TX_LTH[1:0]                  | Low  | Undefined | High | Unit |  |  |  |  |

| 00                              | <71  | 71 - 166  | >166 | mV   |  |  |  |  |

| 01                              | <116 | 116 - 200 | >200 | mV   |  |  |  |  |

| 10                              | <168 | 168 - 266 | >266 | mV   |  |  |  |  |

| 11                              | <177 | 177 - 298 | >298 | mV   |  |  |  |  |

#### Table 1. Receiver Loss of Signal Detect Threshold Values

# 2.2 FibreTimer Clock Recovery Units (CRU)

The FibreTimer clock recovery units (CRU) can recover data, and repeat or retime the data. A 100 nF external loop filter capacitor must be connected from pin CMU\_FILT to GND. The device requires a single reference clock (REFCLK) for signal acquisition and lock. Table 5, page 19 describes the supported data rates, reference clock requirements for those rates, and internal register settings for each rate. The REFCLK input need not be phase-locked to the incoming data but must have a frequency within 200 ppm of the divided down recovered data PLL frequency.

Because a single REFCLK is used for both Rx and Tx data, the Rx and Tx recovered frequencies can differ by as much as 200 ppm. The device accepts single-ended or differential reference clock inputs that are LVPECL-, LVTTL-, or HSTL-compatible and meet the requirements listed in Table 52, page 59.

## 2.2.1 Repeater Mode

The term repeater is used for a CDR function where the recovered serial data is retransmitted synchronously to the recovered clock. Unlike standard PLL-based CDRs, this circuit is all digital, resulting in good jitter tolerance, excellent jitter transfer, and low latency in a circuit that performs identically across process, voltage, and temperature.

In repeater mode, serial data enters the CDR where the clock is extracted from the data and the data is resynchronized to the recovered clock. The resynchronized output of the CDR contains serial data with improved signal quality due to amplification of the signal and attenuation of input jitter. In repeater mode, not all of the jitter at the input is eliminated from the recovered data. However, any jitter that passes through the repeater is low-frequency and therefore is benign to downstream devices.

Repeater mode for the receiver and transmitter channel is selected using either the serial interface or by setting the RXRP or TXRP pin HIGH for their respective channels. When RXRP or TXRP are LOW, the retimer mode is selected. In both the repeater and retimer modes, the data is checked for Run Length Limit (RLL) violations and K28.5 violations. The RXSDU and TXSDU outputs can be programmed to indicate the various violations.

## 2.2.2 Retimer Mode

The term retimer is used for a CDR that retransmits the recovered serial data synchronously to the locally generated internal bit clock. This complex CDR function eliminates jitter transfer at the expense of latency. Due to the potential mismatch between the bit rate of the incoming data and the local reference clock ( $\pm$ 200 ppm), an add or drop elasticity buffer is needed to insert or delete special Fibre Channel ordered sets, called fill words, to accommodate this rate difference. The rules for adding and dropping fill words are delineated in documents generated by the T11 committee. By eliminating jitter transfer, compliance to signal quality standards is ensured.

In Retimer mode, serial data enters the CDR where the clock is extracted from the data and the data is resynchronized to the recovered clock. This data is then input to a 5-word deep add and drop FIFO. Data is removed from the FIFO and retransmitted from the CDR synchronously to the CMU's bit rate clock derived from REFCLK. Because the retransmitted data is synchronized with the bit clock and not the recovered clock, jitter does not pass through the retimer. The output of the retimer is compliant with all Fibre Channel signal quality specifications.

Retimer mode is most useful when the output of the CDR is exiting a system that must meet the Fibre Channel signal quality standards. Because the latency of the retimer is quite high, repeaters are preferable in situations where full Fibre Channel jitter compliance is not required.

Retimer mode for the receiver and transmitter channel is selected using either the serial interface or by setting the RXRP or TXRP pin LOW for their respective channels. When Rxrp or TXRP are HIGH, the Repeater mode is selected. In both the Repeater and Retimer modes, the data is checked for run length limit (RLL) violations and K28.5 violations. The RXSDU and TXSDU outputs can be programmed to indicate the various violations.

## 2.2.3 Bypass Mode

For system debugging, a bypass mode is provided where the CDR can be bypassed. Using bypassing mode means that the input buffer is directly connected to the output buffer without retiming. The de-emphasis does not work in this mode.

## 2.2.4 Controlling the PIO[6:0] and Multiplexer Mode Settings

The VSC8228-01 has multiple modes of operation for loopback, bypass, retiming or repeating, and pattern generation and checking. The PIOx pins provide an interface for either the serial peripheral interface (SPI), two-wire serial interface, or a pin programming mode compatible with the VSC7142 dual repeater and retimer.

Power up the VSC8228-01 device in pin programming mode (PIO4 = 1, PIO3 = 0), then switch to either two-wire serial mode or SPI mode, as follows:

- For two-wire serial mode, change the setting of the PIO3 pin to 1. The setting of the PIO4 pin remains 1.

- For SPI mode, change the setting of the PIO4 pin to 0. The setting of the PIO3 pin remains 0. After SPI mode is enabled, the PIO3 pin can be used as the (SSN) pin.

Alternatively, if the VSC8228-01 device is the only slave on the bus, power up the VSC8228-01 device in two-wire serial mode directly, and then send 11 STOP symbols from the two-wire serial master to the VSC8228-01, to put the two-wire serial engine of the device into IDLE state. At this point, normal communication resumes.

To power up the VSC8228-01 device in SPI mode directly, keep the SSN signal at low, and do not activate the SSN signal until power is stabilized.

To emulate the VSC7142 functions, set PIO4 = 1, PIO3 = 0. In this mode, the PIO6, PIO5, PIO1, and PIO0 (respectively) perform the same function as the M3, M2, M1, and M0 pins, for most settings. SPI does not support bus addressing. The SPI for each of the VSC8228-01 devices requires a separate SPI port to communicate with. The following table describes the settings for the PIO[6:0] pins.

#### Table 2. PIOx and Multiplexer Mode Selection

| PIO6/M3 | PIO5/M2 | PIO4 <sup>(1)</sup> | PIO3 <sup>(1)</sup> | PIO2  | PIO1/M1 | PIO0/M0 | Function/Mode             |

|---------|---------|---------------------|---------------------|-------|---------|---------|---------------------------|

| Х       | Х       | 0                   | SSN                 | MISO  | SCK     | MOSI    | SPI <sup>(2)</sup>        |

| A2      | A1      | 1                   | 1                   | AO    | SCK     | SDA     | Two-wire serial interface |

| M3      | M2      | 1                   | 0                   | RESET | M1      | MO      | Pin programming mode      |

1. When changing from pin programming mode to SPI or two-wire serial interface modes, PIO3 and PIO4 must be set to at least 500 ns before attempting to communicate by using serial interfaces.

2. SPI does not support bus addressing.

The following table provides the pin programming mode selection.

#### Table 3.Pin Programming Mode Selection

| #  | Operation<br>Mode                                    | PIO6<br>/M3 | PIO5<br>/M2 | PIO2  | PIO1<br>/M1 | PIO0<br>/M0 | RxOut <sup>(1)</sup> | TxOut <sup>(1)</sup> | Checker<br>Input <sup>(2)</sup> | VSC7142<br>Equivalent<br>Setting |

|----|------------------------------------------------------|-------------|-------------|-------|-------------|-------------|----------------------|----------------------|---------------------------------|----------------------------------|

| 0  | Receiver bypass                                      | 0           | 0           | Reset | 0           | 0           | RxIn Byp             | TxIn                 |                                 | Invalid                          |

| 1  | line-side<br>generator and<br>checker <sup>(3)</sup> | 0           | 0           | Reset | 0           | 1           |                      | PG <sup>(4)</sup>    | RxIn                            | Invalid                          |

| 2  | Bypass                                               | 0           | 0           | Reset | 1           | 0           | RxIn Byp             | TxIn Byp             |                                 | Removed                          |

| 3  | Test mode (Rx)                                       | 0           | 0           | Reset | 1           | 1           |                      |                      |                                 | Removed                          |

| 4  | Test mode (Tx)                                       | 0           | 1           | Reset | 0           | 0           |                      |                      |                                 | Invalid                          |

| 5  | Line broadcast <sup>(5)</sup>                        | 0           | 1           | Reset | 0           | 1           | RxIn                 | RxIn                 |                                 | Same                             |

| 6  | Transmitter<br>loopback bypass                       | 0           | 1           | Reset | 1           | 0           | TxIn                 | TxIn Byp             |                                 | Same                             |

| 7  | Transmitter<br>bypass                                | 0           | 1           | Reset | 1           | 1           | RxIn                 | TxIn Byp             |                                 | Same                             |

| 8  | Split loopback,<br>RxCLK on                          | 1           | 0           | Reset | 0           | 0           | TxIn                 | TxIn                 |                                 | Invalid                          |

| 9  | Normal, RxCLK<br>on                                  | 1           | 0           | Reset | 0           | 1           | RxIn                 | TxIn                 |                                 | Invalid                          |

| 10 | Receiver<br>loopback bypass                          | 1           | 0           | Reset | 1           | 0           | RxIn Byp             | RxIn                 |                                 | Removed                          |

| 11 | Host<br>broadcast <sup>(5)</sup>                     | 1           | 0           | Reset | 1           | 1           | TxIn                 | TxIn                 |                                 | Same                             |

| #  | Operation<br>Mode                                    | PIO6<br>/M3 | PIO5<br>/M2 | PIO2  | PIO1<br>/M1 | PIO0<br>/M0 | RxOut <sup>(1)</sup> | TxOut <sup>(1)</sup> | Checker<br>Input <sup>(2)</sup> | VSC7142<br>Equivalent<br>Setting            |

|----|------------------------------------------------------|-------------|-------------|-------|-------------|-------------|----------------------|----------------------|---------------------------------|---------------------------------------------|

| 12 | Host-side<br>generator and<br>checker <sup>(6)</sup> | 1           | 1           | Reset | 0           | 0           | PG                   |                      | TxIn                            | Invalid                                     |

| 13 | Split loopback                                       | 1           | 1           | Reset | 0           | 1           | TxIn                 | RxIn                 |                                 | Invalid:<br>transmitter<br>retimed<br>twice |

| 14 | Internal<br>generator and<br>checker                 | 1           | 1           | Reset | 1           | 0           |                      |                      | PG                              | Invalid:<br>transmitter<br>retimed<br>twice |

| 15 | Normal                                               | 1           | 1           | Reset | 1           | 1           | RxIn                 | TxIn                 |                                 | Same                                        |

#### Table 3.Pin Programming Mode Selection (continued)

1. Indicates the source of the data for that output.

2. Indicates the source of the data for the pattern checker.

3. In line-side generator and checker mode, TX\_FIFO\_CTRL must be set to 20'h.

4. PG indicates pattern generator.

5. In line broadcast and host broadcast modes, the Rx and Tx channels must be configured so that both Rx and Tx are both in the repeater mode. If one channel is in repeater mode and the other in retimer mode, the data will be corrupted.

6. In Host-side generator and checker mode, RX\_FIFO\_CTRL must be set to 20'h.

## 2.2.5 Considerations for Non-Fibre Channel Applications

The FibreTimer blocks of the VSC8228-01 are designed for use in Fibre Channel systems. The add or drop entities required for speed matching are not compatible with gigabit Ethernet, SONET/SDH, or other applications. If the VSC8228-01 is used in non-Fibre Channel applications, it must be configured for repeater or bypass mode.

## 2.2.6 Fibre Channel Protocol Detection

In the retimer and repeater mode, the incoming data is examined for run-length violations and K28.5– symbols. These signals can be optionally combined with RXASDERR or TXASDERR to confirm if there is incoming data and if it is valid Fibre Channel data.

The SDUSEL pin selects one of two different modes: single-window (LOW) or multiple-window (HIGH) error mode. When controlled by the serial interface, the RXSDUSEL and TXSDUSEL bits control this mode when enabled by setting RXSDUSEL\_SRC or TXSDUSEL\_SRC HIGH.

By default, single-window detection is enabled. Single-window error mode allows the user to develop their own algorithm for monitoring data and enabling control of the multiplexor mode settings. In multiple-window error mode, RXSDU or TXSDU is asserted LOW after four consecutive 32,768-bit windows containing ASD, RLL, or K28.5– errors. RXSDU or TXSDU remains asserted until four consecutive 32,768-bit windows occur error free.

## 2.2.7 Run-Length Limit (RLL) Detection

The retimer run-length limit (RLL) detection scheme uses 32,768-bit windows. If a run of six or more consecutive zeros or a run of six or more consecutive ones begins in the 32,768-bit window, that window is considered to have an RLL error. Otherwise, that window is considered to be RLL-clean. For a run-length limit error, the RXRLLERR or TXRLLERR bit is set HIGH. This bit is only cleared after a read to that register.

## 2.2.8 K28.5- Detection

The K28.5– character detection uses 32,768-bit windows. If at least one K28.5– character begins in the 32,768-bit window, that window is considered to have a K28.5– character within it. Otherwise, K28.5– characters are considered to be absent and in error.

In normal Fibre Channel traffic, an interframe gap with a minimum of two idle characters containing two K28.5– characters occurs every 21,000 bits. Therefore, in normal traffic, the detection scheme always declares the detection of K28.5– characters. For a K28.5– error, the RXK28ERR or TXK28ERR bit is set HIGH. This bit is only cleared after a read from the RXK28ERR or TXK28ERR register.

## 2.2.9 Protocol Error Signaling

The VSC8228-01 provides a programmable output signal that indicates protocol errors in the retimer and repeater modes. The RXSDU, TXSDU, RXASD, and TXASD signals can be programmed to indicate loss of signal, RLL violations, or K28.5 violations. The user selects which errors to monitor. If any of these errors occur, the respective RXSDU, TXSDU, RXASD, or TXASD output is set LOW.

By default, all of the following signals must indicate normal operation for RXSDU and TXSDU to be set HIGH: transition detector, peak-to-peak amplitude monitor, run-length limit detector, and K28.5– monitor. By default, the RXASD and TXASD signals are set HIGH when the transition detector and peak-to-peak amplitude monitor indicate normal operation.

## 2.2.10 Reference Clock

The VSC8228-01 derives all internal clock signals from an external reference clock on the REFCLKP/REFCLKN input pins. These inputs support a variety of oscillator output configurations as identified in Table 4, page 18. For optimized signal quality and minimal jitter, a differential AC-coupled LVPECL oscillator is recommended. Differential LVPECL and HSTL reference clocks require a 100- $\Omega$  external termination across the REFCLKP/REFCLKN inputs. Single-ended LVPECL and HSTL reference clocks require a 50- $\Omega$  external termination to ground.

#### Table 4. Reference Clock Configuration Support

| Reference Clock | DC-Cou                      | pled         | AC-Coupled                  |              |  |

|-----------------|-----------------------------|--------------|-----------------------------|--------------|--|

| Туре            | Single-Ended <sup>(1)</sup> | Differential | Single-Ended <sup>(1)</sup> | Differential |  |

| HSTL            | Yes <sup>(2)</sup>          | Yes          | Yes                         | Yes          |  |

| LVTTL           | Yes <sup>(3)</sup>          | No           | NA                          | NA           |  |

#### Table 4.Reference Clock Configuration Support (continued)

| Reference Clock       | DC-Cou                      | pled                    | AC-Coupled                  |              |  |

|-----------------------|-----------------------------|-------------------------|-----------------------------|--------------|--|

| Туре                  | Single-Ended <sup>(1)</sup> | Differential            | Single-Ended <sup>(1)</sup> | Differential |  |

| LVPECL <sup>(4)</sup> | See note <sup>(5)</sup>     | See note <sup>(5)</sup> | Yes                         | Yes          |  |

1. For the unused REFCLKN, a 0.1 µF capacitor to ground should be added to suppress noise.

2. REFCLKP driven with REFCLKN biased from 0.68 V to 0.9 V.

3. Requires a modified  $V_{IL}$  maximum of 0.5 V.

4. A minimum swing of 250 mV single-ended or 350 mV differential is required.

5. DC-coupled operation for LVPECL REFCLK+/- is allowed only if the LVPECL driver meets the modified common-mode signal level specified in Table 16, page 51.

## 2.2.11 Data Rate Selection

The VSC8228-01 supports the data rates and reference clocks listed in the following table. The data rate is configured through the RXRATEO/1 and TXRATEO/1 pins or through the programming interface. The channels can be programmed independently for multiples of a given service (Fibre Channel, Ethernet). For example, if one channel is programmed for 1 Gbps Fibre Channel (1 GFC), the other can be programmed for 2 GFC or 4 GFC but not gigabit Ethernet. If one channel is set to Infiniband or PCI Express<sup>™</sup>, the other can be set to gigabit Ethernet. The default register settings for a 125-MHz reference clock are for gigabit Ethernet for both channels.

#### Table 5.Reference Clock Rates by Application

|                                  | Data Service Setting for<br>Rate Both Channels |                    | Rate Multiplier<br>Setting for Each<br>Channel<br>(RX_DIVK/ | REFCLK<br>Frequency (MHz) |                |  |

|----------------------------------|------------------------------------------------|--------------------|-------------------------------------------------------------|---------------------------|----------------|--|

| Application                      | (Gbps)                                         | (CMU_DIV_SEL[1:0]) | TX_DIVK[2:0])                                               | RCK_SEL = 0               | RCK_SEL = 1    |  |

| ESCON/SBCON                      | 0.200                                          | 01                 | 001                                                         | 125                       | 62.5           |  |

| Fast Ethernet                    | 0.125                                          | 01                 | 000                                                         | 125                       | 62.5           |  |

| Gigabit Ethernet                 | 1.2500                                         | 11                 | 101                                                         | 125                       | 62.5           |  |

| 1× Fibre Channel                 | 1.0625                                         | 11<br>10           | 101<br>101                                                  | 106.25<br>125             | 53.125<br>62.5 |  |

| 2× Fibre Channel                 | 2.1250                                         | 11<br>10           | 110<br>110                                                  | 106.25<br>125             | 53.125<br>62.5 |  |

| 4× Fibre Channel                 | 4.2500                                         | 11<br>10           | 111<br>111                                                  | 106.25<br>125             | 53.125<br>62.5 |  |

| 2.5 InfiniBand or<br>PCI Express | 2.5000                                         | 11                 | 110                                                         | 125                       | 62.5           |  |

| STS-3/STM-1                      | 0.15552                                        | 01                 | 000                                                         | 155.52                    | 77.76          |  |

| STS-12/STM-4                     | 0.62208                                        | 01                 | 100                                                         | 155.52                    | 77.76          |  |

| STS-48/STM-16                    | 2.48832                                        | 01                 | 110                                                         | 155.52                    | 77.76          |  |

To provide fast rate-change response, two pins are provided to directly select the data rate. The user programs the rate multiplier for each of the four combinations for the RXRATEO/1 and TXRATEO/1 pins. When enabled, the device selects the programmed rate multiplier based on the state of the RXRATEO/1 and TXRATEO/1 pins. The pins settings for RXRATEO/1 and TXRATEO/1 are listed in the following table. Note that the Ethernet reference clock (125 MHz) can be used to support Fibre Channel, Ethernet,

and ESCON/SBCON with a single reference clock. Using the Fibre Channel reference clock setting requires a 100-MHz clock to support ESCON/SBCON.

| TXRATE1/<br>RXRATE1 | TXRATEO/<br>RXRATEO | APPSEL | REFCLK<br>Frequency<br>(MHz) | Application       | Data Rate<br>(Gbps) |

|---------------------|---------------------|--------|------------------------------|-------------------|---------------------|

| 0                   | 0                   | 0      | 106.25                       | 1× Fibre Channel  | 1.0625              |

|                     |                     | 0      | 125                          | Gigabit Ethernet  | 1.25                |

|                     |                     | 1      | 125                          | 1 × Fibre Channel | 1.0625              |

| 0                   | 1                   | 0      | 106.25                       | 2× Fibre Channel  | 2.125               |

|                     |                     | 0      | 125                          | Infiniband        | 2.50                |

|                     |                     | 1      | 125                          | 2× Fibre Channel  | 2.125               |

| 1                   | 0                   | 0      | 100                          | ESCON             | 0.200               |

|                     |                     | 1      | 125                          | ESCON             | 0.200               |

| 1                   | 1                   | 0      | 106.25                       | 4× Fibre Channel  | 4.25                |

|                     |                     | 1      | 125                          | 4× Fibre Channel  | 4.25                |

#### Table 6.Hardware Control of Data Rate

## 2.3 Output Drivers

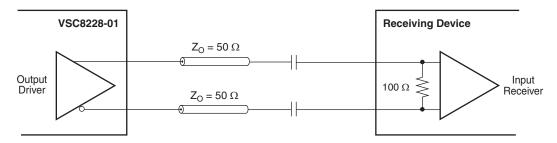

The output swing is user-programmable on a per-channel basis. When operating with a single 1.2-V power supply, the output levels are compatible with AC-coupled LVDS. When operating with a single 1.8-V power supply, the outputs can be programmed to one of three different levels. The outputs have  $50-\Omega$  back-termination resistors and should be AC-coupled.

## 2.3.1 De-Emphasis

All high-speed differential outputs contain a nine-level de-emphasis circuit, which is controlled by the RX/TX\_ED[3:0] bits in the RX/TXOUT\_CTRL register that can attenuate lower frequency signals in a transmitted data stream. Alternately, the RX/TXEMP pin can be used to set the de-emphasis to maximum (HIGH) or disable the de-emphasis (LOW).

The following figure shows with de-emphasis enabled that the initial amplitude of the signal after a transition is the same as when de-emphasis is disabled. However, after approximately a 1-bit delay, the amplitude of the signal drops by a programmable amount. By combining the amplitude control determined by the RX/TX\_HIV[1:0] bits in the RX/TXOUT\_CTRL register with the de-emphasis feature, the user has extremely flexible control of output amplitude. This feature can compensate for the loss of signal amplitude and the effect on the data eye opening, because of long cables or trace length runs. A maximum de-emphasis ratio of 1:0.5 produces more open data eyes at the end of a long cable or trace length run.

#### Figure 4. Output De-Emphasis

The following table shows the relative amplitude of the output as related to the output level controls, which are set by the RX/TX\_HIV[1:0] bits in the RX/TXOUT\_CTRL register and the de-emphasis controls, which are set by the RX/TX\_ED[1:0] bits in the RX/TXOUT\_CTRL register. The de-emphasis ratio is the non-de-emphasized signal (normalized to 1) compared to the de-emphasized signal. For a de-emphasized setting of 1:0.5, the reduced amplitude signal is one-half of the maximum signal.

#### Table 7. De-Emphasis Values for Typical Conditions

| RX_ED[3:0]       | De-Emphasis Ratio                                    |

|------------------|------------------------------------------------------|

| 0000             | 1:1.00 (no emphasis)                                 |

| 1001             | 1:0.94                                               |

| 0001             | 1:0.88                                               |

| 1010             | 1:0.81                                               |

| 0010             | 1:0.75                                               |

| 1011             | 1:0.68                                               |

| 0011             | 1:0.62                                               |

| 1100             | 1:0.55                                               |

| 0100             | 1:0.50 (maximum emphasis)                            |

| All other values | are reserved for future use. If the RX/TX_SLE bit is |

All other values are reserved for future use. If the RX/TX\_SLE bit is set, these inputs are ignored, and the de-emphasis ratio is 1:1.

The following table shows how the RX/TX\_SLE bit of the RX/TXOUT\_CTRL register controls the output slew rate. This feature is used to adjust the output slew rate to match the operating speed of the channel.

#### Table 8. Output Slew Rate Values

| RX/TX_SLE | Output Slew Rate |

|-----------|------------------|

| 0         | Fastest          |

| 1         | Slower by ~25%   |

The following table lists the output voltage swing levels of the channel. The values listed in the table are for 1.0625 Gbps and 2.125 Gbps operation measured per FC-PI-2, Section 9.3.1. The minimum values are inside the data eye, and maximum values are outside the data eye with the emphasis disabled for both.

|             | Output Swing<br>V <sub>DDIORX/TX</sub> = 1.2 V |          |         | Output Swing<br>V <sub>DDIORX/TX</sub> = 1.8 V |          |         |

|-------------|------------------------------------------------|----------|---------|------------------------------------------------|----------|---------|

| RX_HIV[1:0] | Minimum                                        | Typical  | Maximum | Minimum                                        | Typical  | Maximum |

| 00          | 770                                            | 970      | 1200    | 850                                            | 1050     | 1300    |

| 01          |                                                | Reserved |         | 950                                            | 1200     | 1700    |

| 10          |                                                | Reserved |         | 1050                                           | 1400     | 1800    |

| 11          | Reserved                                       |          |         |                                                | Reserved |         |

#### Table 9.Output Swing Levels

For 4.25-Gbps operation, the output is measured per FC-PI-2, session 9.3.3. With de-emphasis enabled, the measurement at both near-end and far-end after transmitter compliance transfer function (TCTF) is between 1600 mV and 310 mV differential respectively. The TCTF used is more stringent than the one defined by FC-PI-2. The attenuation frequencies are:

- 425 MHz: -3.1 dB

- 1.0625 GHz: -6.5 dB

- 2.125 GHz: -10.0 dB

- 4.25 GHz: -16.7 dB

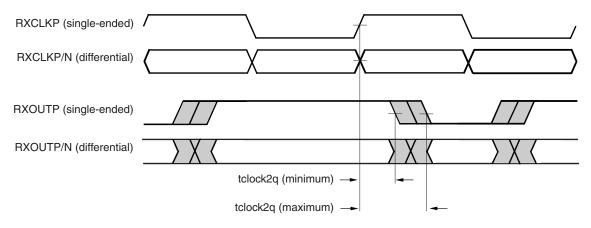

## 2.3.2 SGMII Clock Output

The VSC8228-01 device provides an SGMII output clock on the host-side of the device for gigabit Ethernet applications. This output is disabled unless enabled by the serial interface port. For more information about the timing for this clock, see Figure 10, page 59. This clock runs at half the selected data rate (625 MHz for gigabit Ethernet) and complies with SGMII levels. The clock is supported only at the gigabit Ethernet rate. When disabled, the RXCLKN and RXCLKP outputs float HIGH. The SGMII clock output should be terminated by a 50- $\Omega$  resistor to ground for AC coupling and should be terminated with 50- $\Omega$  resistor to 1.2-V power supply for DC coupling.

# 2.4 TTL Inputs and Outputs

The VSC8228-01 includes adjustable TTL I/O levels. By providing 1.2 V, 1.8 V, 2.5 V, and 3.3 V to the VDDTTL pins, the TTL inputs and outputs match the levels for the respective VDDTTL voltage provided in Table 14, page 47. All TTL inputs have internal pull-ups. For PIOO and PIO2, external 1 K $\Omega$  pull-up resistors to VDDTTL are required when these pins are used for outputs.

# 2.5 Pattern Generation, Pattern Checking, and Loopback Modes

A programmable pattern generator and pattern checker, as well as loopback features are provided to aid with system test and diagnostics. The device can generate and detect an unframed 2<sup>7</sup>, 2<sup>23</sup>, and 2<sup>31</sup> pseudo-random bit stream (PRBS), a user-defined pattern of exactly 40 bits or 64 bits, and the Fibre Channel CRPAT, CJTPAT, and CSPAT patterns. The pattern generator and pattern checker are independent.

The device supports various host-side and line-side loopback, as well as pattern generation and pattern checking modes. These modes can be accessed by using the serial port or using the PIO[6:0] pins as described in Table 2, page 16. For line-side pattern generation and pattern checker modes, TX\_FIFO\_CTRL must be set to 20'h. For host-side pattern generation and pattern checker modes, RX\_FIFO\_CTRL must be set to 20'h. For both line-side generator and checker (mode 1) and host-side generator and checker (mode 12), the VSC8228-01 device must be set to a retimer mode.

# 2.6 Serial Interface Port

Communication to and from the device occurs through either pin control or by using a programmable serial interface port that supports SPI or two-wire serial and is accessible by programmable I/O pins PIO[6:0]. Control inputs and status outputs can be written to and read from the device using the serial port. The port can be configured either as two-wire serial interface or SPI, or it can be disabled so that the user can control the more important features of the device directly through input pins. For more information about LVTTL input pins PIO[6:0], see Table 2, page 16. The serial port does not require an external reference clock.

When the serial interfaces (SPI or two-wire) are disabled, the PIO[6:0] pins determine the mode of the device (loopback, normal, pattern generation, checking, and so forth) and whether the clock output is enabled.

The device has a power-on reset circuit that puts the device in the default state. The device also has a hardware RESET signal assigned to pin PIO2 in the non-serial state defined by PIO[3:2] = 01, as shown in Table 2, page 16. Setting RESET to a 1 places the device in the default state.

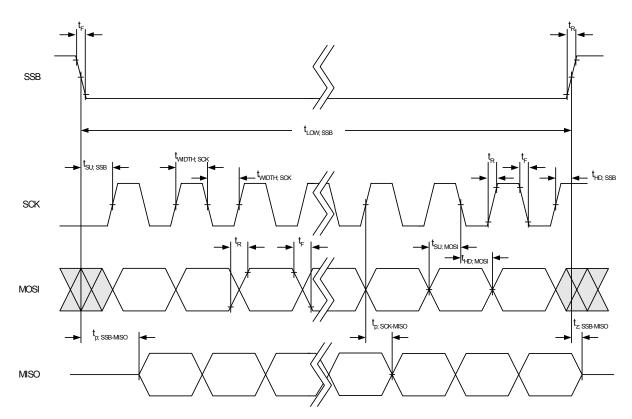

## 2.6.1 SPI Interface

The SPI protocol is described in the timing diagram of the following figure. Signal SSN is the active LOW serial select signal that must be LOW to activate the SPI port. Data is input into the device on signal MOSI (Master Out, Slave In), sampled on the falling edge of clock signal SCK. Data is output on signal MISO (Master In, Slave Out), synchronous with the rising edge of SCK. A 7-bit address is transferred first, followed by an OPCODE bit, which specifies whether a read (OP = 0) or write (OP = 1) operation is to take place, and then the data. Two read/write (R/W) modes are possible with the SPI protocol: single and burst. For more information about both modes, see Figure 5, page 24.

In single R/W mode, a single 8-bit word is transferred. After the 8 bits are transferred, the SSN line is brought HIGH, designating the end of the data transfer procedure. In burst mode, data bits transferred beyond the initial 8 bits are written to sequential

addresses until the SSN line is brought HIGH. If the SSN is brought HIGH before all 8 bits in a given word are transferred, none of the 8 bits in that word are transferred. All I/O levels are programmed based on the VDDTTL voltage. Internal pull-up resistors are weak on all PIO pins; therefore, external pull-up resistors should be added. SPI port does not support bus addressing, and the SPI of each the VSC8228 requires a separate SPI port to communicate with.

## 2.6.2 Two-Wire Serial Interface

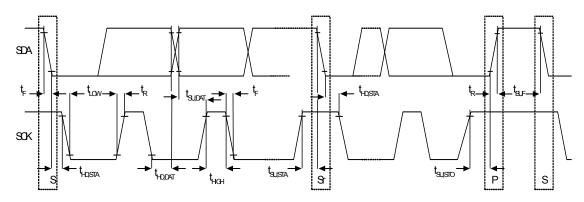

The VSC8228-01 supports a slave mode, two-wire serial interface, where an external master device controls the VSC8228-01 device. The slave two-wire serial interface operates in both standard mode (up to 100 kbps) and fast mode (up to 400 kbps) data transfer rates.

To enable two-wire serial mode, it is recommended that the VSC8228-01 device first be powered up in pin programming mode. For information about configuring the device for two-wire serial mode, see "Controlling the PIO[6:0] and Multiplexer Mode Settings," page 15.

A valid START condition is generated by a master device by transitioning SDA HIGH to LOW while SCK is HIGH. Data is then transferred on the SDA line, most significant bit (MSB) first, with the SCK line clocking data. Data transitions during SCK LOW periods and is valid (read) or latched (write) when SCK pulses HIGH then LOW. Data transfers are acknowledged (ACK) by the receiving device (VSC8228-01) for data writes and by the master for data reads. An acknowledge is signaled by holding the SDA signal LOW while pulsing SCK HIGH then LOW. The master terminates data transfer by generating a STOP condition by transitioning SDA LOW to HIGH while SCK is HIGH. For a detailed timing diagram, see the following figure.

#### Figure 6. Two-Wire Serial Interface Timing

The interface supports eight different 7-bit slave addresses within the 8-bit device address. The slave address is programmed by using the PIO pins as indicated in the following table. All I/O levels are programmed based on the VDDTTL voltage. Pull-up resistors are provided on all PIO pins. Because the read and write (R/W) bit is the LSB of the 8-bit device address, the device address changes from a read to a write as shown in the following table. The slave address is compared to bits 7:1 of the device address byte, which is the first byte transmitted to the device after a START condition. The 8-bit of the device address byte is set LOW to indicate a write or HIGH to indicate a read.

|   |             |          |   |   | Devie | Device Address (Read) |      | Device Address (Write) |   |          |                 |        |          |               |                          |            |               |                          |         |

|---|-------------|----------|---|---|-------|-----------------------|------|------------------------|---|----------|-----------------|--------|----------|---------------|--------------------------|------------|---------------|--------------------------|---------|

|   | PIO5<br>/A1 | РІО<br>4 |   |   |       |                       |      |                        |   | РІО<br>3 | PIO<br>2/<br>A0 | 2/ PIO | PIO<br>0 | Byte<br>Value | Slave<br>Address<br>Bits | R/W<br>Bit | Byte<br>Value | Slave<br>Address<br>Bits | R/W Bit |

| 0 | 0           | 1        | 1 | 0 | SCK   | SDA                   | 81′h | 1000 000               | 1 | 80′h     | 1000 000        | 0      |          |               |                          |            |               |                          |         |

| 0 | 0           | 1        | 1 | 1 | SCK   | SDA                   | 83′h | 1000 001               | 1 | 82′h     | 1000 001        | 0      |          |               |                          |            |               |                          |         |

| 0 | 1           | 1        | 1 | 0 | SCK   | SDA                   | 85′h | 1000 010               | 1 | 84′h     | 1000 010        | 0      |          |               |                          |            |               |                          |         |

| 0 | 1           | 1        | 1 | 1 | SCK   | SDA                   | 87′h | 1000 011               | 1 | 86′h     | 1000 011        | 0      |          |               |                          |            |               |                          |         |

| 1 | 0           | 1        | 1 | 0 | SCK   | SDA                   | 89′h | 1000 100               | 1 | 88′h     | 1000 100        | 0      |          |               |                          |            |               |                          |         |

| 1 | 0           | 1        | 1 | 1 | SCK   | SDA                   | 8B′h | 1000 101               | 1 | 8A'h     | 1000 101        | 0      |          |               |                          |            |               |                          |         |

| 1 | 1           | 1        | 1 | 0 | SCK   | SDA                   | 8D′h | 1000 110               | 1 | 8C′h     | 1000 110        | 0      |          |               |                          |            |               |                          |         |

| 1 | 1           | 1        | 1 | 1 | SCK   | SDA                   | 8F′h | 1000 111               | 1 | 8E'h     | 1000 111        | 0      |          |               |                          |            |               |                          |         |

#### Table 10. Two-Wire Serial Interface 7-Bit Slave Addresses

**Note** Because of the pull-up resistors on all PIO pins, the default serial address is 8F'h for read, 8E'h for write.

The first byte transferred is always the device address. Write accesses require a 3-byte transfer. The first byte is the device address with a write operation indicated. This is the 7-bit slave address followed by a HIGH R/W bit. The second byte contains the register address, and the third byte is the write data.

Read accesses require a 4-byte transfer. First a dummy write operation is sent, which is composed of two bytes: the device address with read operation indicated and the register address. Next, a START condition is sent. The third byte is a repeated device address with the R/W bit HIGH, and the fourth byte is the read data.

For write operations, the data is latched into the appropriate register during the acknowledge of the third byte. All transactions to or from the device are completed

during the acknowledge of the third byte, allowing the user to immediately initiate another transfer to the device or terminate transfers.

Multibyte read or write transactions are allowed and are extensions of the above protocol with additional data bytes added to the end of the transaction. All multibyte transactions cause the internal address to increment by one, regardless of the register address. For multibyte read transactions, the master terminates the data transfer by generating a not acknowledged (NACK) condition, holding SDA HIGH while pulsing SCK HIGH, then LOW, and then generating a STOP condition. See Figure 7, page 27 for illustrations of single-byte and multibyte R/W operations.

The following table shows a two-wire serial interface transaction example using slave address: 1000 111'b. The conventions used in the table are:

- [UPPERCASE] denotes a master's action.

- [lowercase] denotes a slave's action.

- [S] denotes a START: The master signals a start by transitioning SDA HIGH to LOW while SCK is HIGH.

- [P] denotes a STOP: The master signals a stop by transitioning SDA LOW to HIGH while SCK is HIGH.

- [A] denotes a master's ACK: The master signals an acknowledge by holding the SDA signal LOW while pulsing SCK HIGH then LOW.

- [N] denotes a master's NACK: The master signals an reverse acknowledge by holding the SDA signal LOW while pulsing SCK HIGH then LOW.

- [a] denotes a slave's ACK: The slave signals an acknowledge by holding the SDA signal LOW while pulsing SCK HIGH then LOW.

#### Table 11. Two-Wire Serial Interface Transaction Example Using Slave Address

| Transaction  | Sequence                                                                            |

|--------------|-------------------------------------------------------------------------------------|

| 1 byte write | [S] [0x8E] [a] [REGISTER ADDRESS] [a] [DATA] [a] [P]                                |

| N byte write | [S] [0x8E] [a] [REGISTER ADDRESS 1] [a] [DATA 1][a] [DATA 2] [a]                    |

|              | <br>[DATA N-1] [a] [DATA N] [a] [P]                                                 |

| 1 byte read  | [S] [0x8E] [a] [REGISTER ADDRESS] [a] [S] [0x8F] [a] [data] [N] [P]                 |

| N byte read  | [S] [0x8E] [a] [REGISTER ADDRESS 1] [a] [S] [0x8F] [a] [data 1] [A] [data 2]<br>[A] |

|              | <br>[data n-1] [A] [data n] [N] [P]                                                 |

Figure 7. Two-Wire Serial Interface Operation

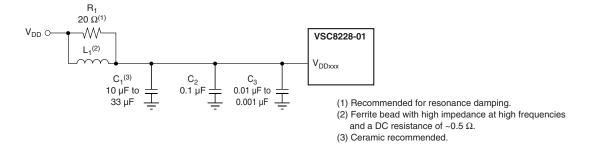

# 2.7 Power Supply Filtering

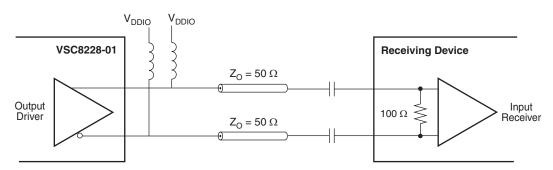

The VSC8228-01 power supplies can be configured in one of three ways: 1.2-V power supply only, 1.8-V power supply only, or both 1.2-V and 1.8-V power supplies. For the HIGH output swing setting, VDDIORX and VDDIOTX must be connected to a 1.8-V pull-up inductor or else a ferrite bead must be connected from each high-speed output to a 1.2-V power supply to restore the DC common-mode of the output.

Contact your local Vitesse sales representative for more information on using a ferrite bead for DC restoration with a 1.2-V power supply. The following table lists each of the power supply connection groups for the VSC8228-01. Each group should be separately filtered using the filter depicted in the following figure to reduce crosstalk, jitter, and noise. If VDDTTL is set to 1.8 V, it can be connected to the VDDB18 filter.

#### Configuration **Power Supply Pin Name Group Description** Connection 1.2 V only VDDA12, VDDA18 CMU power supply 1.2 V VDDTX18, VDDTX12, VDDIOTX 1.2 V Transmitter power supply VDDRX18, VDDRX12, VDDIORX Receiver power supply 1.2 V VDDB12, VDDB18 Serial interface and digital logic 1.2 V VDDTTL TTL power supply 1.2 V, 1.8 V, 2.5 V, or 3.3 V 1.8 V only VDDA18 CMU power supply 1.8 V VDDTX18, VDDIOTX Transmitter power supply 1.8 V VDDRX18, VDDIORX Receiver power supply 1.8 V VDDB18 Serial interface and digital logic 1.8 V VDDTX12, VDDRX12, VDDB12, Bypass capacitors<sup>(1)</sup> 1.2-V regulated power supply VDDA12 VDDTTL TTL power supply 1.2 V, 1.8 V, 2.5 V, or 3.3 V 1.2 V and 1.8 V VDDA12, VDDA18 CMU power supply 1.2 V VDDIOTX Transmitter I/O power supply 1.8 V VDDIORX Receiver I/O power supply 1.8 V VDDTX12, VDDTX18 Transmitter power supply 1.2 V VDDRX12, VDDRX18 Receiver power supply 1.2 V VDDB12, VDDB18 Serial interface and digital logic 1.2 V VDDTTL 1.2 V, 1.8 V, 2.5 V, or 3.3 V TTL power supply

#### Table 12. Power Supply Connection Groups by Configuration

1. When using only a 1.8-V power supply, bypass the 1.2-V connections with  $1-\mu F$  and  $0.001 \,\mu F$  capacitors.

#### Figure 8. Power Supply Filter

# 3 Registers