# VC-830

# LVPECL, LVDS, and HCSL Crystal Oscillator

#### Features

- 40 fs<sub>RMS</sub> Phase Jitter Typical, 12 kHz to 20 MHz

- 3rd OT or Fundamental Crystal Design

- Extended Operating Temperature Range: –55°C to +125°C

- 100 MHz to 320 MHz Output Frequencies

- Excellent Power Supply Rejection Ratio

- · Glitch Free Output upon Power-Up and Enable

- Hermetically Sealed 3.2 mm × 2.5 mm Ceramic Package

- Product is Compliant to RoHS Directive and Fully Compatible with Lead-Free Assembly

#### Applications

- Medical, Ultrasound

- Ethernet, GbE, SynchE

- Fibre Channel

- PON

- · Clock Source for A/Ds, D/As, FPGAs

- · Test and Measurement

- Storage Area Network

#### **General Description**

Microchip's VC-830 crystal oscillator is a quartz-stabilized, differential output oscillator that operates off a 1.8V, 2.5V, or 3.3V power supply in a hermetically sealed 3.2 mm × 2.5 mm ceramic package.

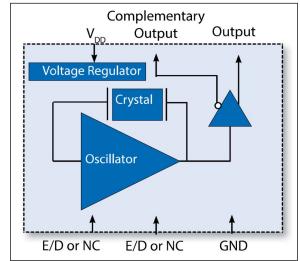

#### **Block Diagram**

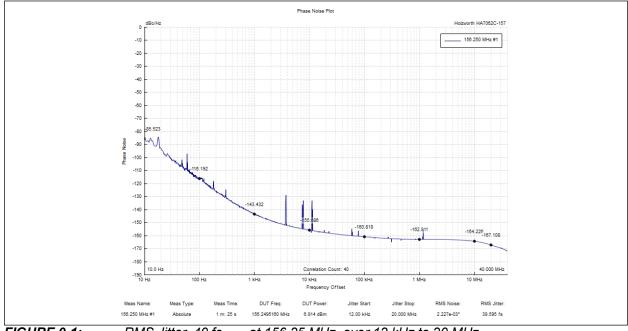

#### **Phase Noise Plot**

FIGURE 0-1: RMS Jitter, 40 fs<sub>RMS</sub> at 156.25 MHz, over 12 kHz to 20 MHz.

# 1.0 ELECTRICAL CHARACTERISTICS

#### Absolute Maximum Ratings †

| Supply Voltage                            | –0.3V to +4.5V |

|-------------------------------------------|----------------|

| Enable Disable Voltage                    |                |

| ESD Rating, Human Body Model (Note 1)     |                |

| ESD Rating, Charged Device Model (Note 1) |                |

| Storage Temperature (T <sub>S</sub> )     |                |

| Junction Temperature (T <sub>J</sub> )    |                |

**† Notice:** Stresses in excess of the Absolute Maximum Ratings can permanently damage the device. Functional operation is not implied at these or any other conditions in excess of conditions represented in the operational sections of this data sheet. Exposure to Absolute Maximum Ratings for extended periods may adversely affect device reliability.

**Note 1:** Although ESD protection circuitry has been designed into the VC-830, proper precautions should be taken when handling and mounting. Microchip employs a Human Body Model (HBM) and a Charged Device Model (CDM) for ESD susceptibility testing and design protection evaluation. ESD thresholds are dependent on the circuit parameters used to define the model. Although no industry standard has been adopted for the CDM, a standard resistance of 1.5 kΩ and capacitance of 100 pF is widely used and therefore can be used for comparison purposes.

# ELECTRICAL CHARACTERISTICS, LVPECL OPTION

| Parameter                        | Sym.            | Min.                       | Тур. | Max.                       | Units | Conditions              |

|----------------------------------|-----------------|----------------------------|------|----------------------------|-------|-------------------------|

| Cumple Valtage (Nata 4)          | N               | 2.375                      | 2.5  | 2.625                      | v     |                         |

| Supply Voltage (Note 1)          | $V_{DD}$        | 3.135                      | 3.3  | 3.465                      | V     | Ordering Option         |

| Current Consumption              |                 | _                          | _    | 66                         | A     | 200 MHz                 |

| Current Consumption              | I <sub>DD</sub> |                            |      | 70                         | mA    | 320 MHz                 |

| Frequency                        |                 |                            |      |                            |       |                         |

| Nominal Frequency                | f <sub>N</sub>  | 100                        | _    | 320                        | MHz   | Ordering Option         |

|                                  | _               | _                          | _    | ±20                        |       | Ordering Option         |

|                                  |                 | _                          | _    | ±25                        | ppm   |                         |

| Stability (Note 2)               |                 | _                          | _    | ±30                        |       |                         |

|                                  |                 | _                          |      | ±50                        |       |                         |

|                                  |                 | _                          | _    | ±100                       |       |                         |

| Outputs                          |                 |                            |      |                            |       |                         |

| Output Logic Level High (Note 3) | V <sub>OH</sub> | V <sub>DD</sub> –<br>1.085 | _    | V <sub>DD</sub> –<br>0.880 | v     | V <sub>DD</sub> = +2.5V |

| Output Logic Level Low (Note 3)  | V <sub>OL</sub> | V <sub>DD</sub> –<br>1.810 | —    | V <sub>DD</sub> –<br>1.620 |       |                         |

**Note 1:** The VC-830 power supply should be filtered. For example, a 10  $\mu$ F, 0.1  $\mu$ F, and 0.01  $\mu$ F capacitor.

- 2: Includes calibration tolerance, operating temperature, supply voltage variations, aging, and IR reflow.

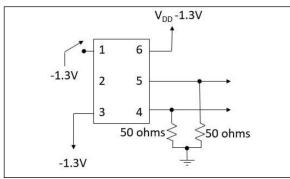

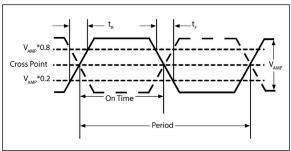

- 3: Figure 1-1 defines the test circuit and Figure 1-2 defines these parameters.

- **4:** Output rise and fall time will be 600 ps (max.) for -40°C to +105°C, -40°C to +125°C, and -55°C to +125°C operating temperature ranges.

- 5: Duty Cycle is measured as On/Time Period.

- 6: Measured using an Agilent E5052 Signal Source Analyzer at 25°C.

- 7: Outputs will be enabled if Enable/Disable is left open. There is an oscillation detection circuit that ensures glitch free output upon power-up or enable.

- 8: In order to reduce current, the pull-up resistance is higher when V<sub>DD</sub> is set to ground.

#### **ELECTRICAL CHARACTERISTICS, LVPECL OPTION (CONTINUED)**

| Parameter                                              | Sym.                           | Min.                       | Тур.                   | Max.                       | Units   | Conditions              |

|--------------------------------------------------------|--------------------------------|----------------------------|------------------------|----------------------------|---------|-------------------------|

| Output Logic Level High (Note 3)                       | V <sub>OH</sub>                | V <sub>DD</sub> –<br>1.085 | _                      | V <sub>DD</sub> –<br>0.880 | v       | V <sub>DD</sub> = +3.3V |

| Output Logic Level Low (Note 3)                        | V <sub>OL</sub>                | V <sub>DD</sub> –<br>1.810 | _                      | V <sub>DD</sub> –<br>1.620 | V       | v <sub>DD</sub> - +3.3v |

| Output Rise and Fall Time (Note 3)                     | t <sub>r</sub> /t <sub>f</sub> | _                          | _                      | 400                        | ps      | Note 4                  |

| Load                                                   | _                              | 50Ω                        | into V <sub>DD</sub> – | 2.0V                       |         | _                       |

| Duty Cycle (Note 5)                                    | DC                             | 45                         | _                      | 55                         | %       | —                       |

|                                                        | φ <sub>N</sub>                 | —                          | -79                    | _                          |         | 10 Hz                   |

|                                                        |                                | _                          | -110                   | _                          |         | 100 Hz                  |

|                                                        |                                | —                          | -130                   | _                          |         | 1 kHz                   |

| Phase Noise, 3.3V, 156.25 MHz                          |                                |                            | -154                   |                            | dDo/LI- | 10 kHz                  |

| (Note 6)                                               |                                | —                          | -160                   |                            | dBc/Hz  | 100 kHz                 |

|                                                        |                                | —                          | -163                   | _                          |         | 1 MHz                   |

|                                                        |                                | _                          | -163                   | _                          |         | 10 MHz                  |

|                                                        |                                | —                          | -167                   | _                          |         | 20 MHz                  |

| Phase Jitter, 156.25 MHz,<br>12 kHz to 20 MHz (Note 6) | φJ                             | _                          | 40                     | 60                         | fs      | _                       |

| Enable/Disable                                         |                                |                            |                        |                            |         |                         |

| Outputs Enabled (Note 7)                               | V <sub>IH</sub>                | 0.7 * V <sub>DD</sub>      | _                      | _                          | V       | _                       |

| Outputs Disabled                                       | V <sub>IL</sub>                | —                          | _                      | 0.3 * V <sub>DD</sub>      | V       | _                       |

| Disable Time                                           | t <sub>D</sub>                 | —                          | —                      | 200                        | ns      | —                       |

| E/D Pull-Up Resistance (Note 8)                        | _                              | 0.5                        | _                      | 2                          | MΩ      | E/D = GND               |

| E/D Pull-Up Resistance                                 | _                              | 30                         | _                      | 150                        | kΩ      | $E/D = V_{DD}$          |

| Start-Up Time                                          | t <sub>SU</sub>                | —                          |                        | 10                         | ms      |                         |

|                                                        |                                | -10                        |                        | 70                         |         |                         |

|                                                        |                                | -40                        |                        | 85                         | ]       |                         |

| Operating Temperature                                  | Т <sub>ОР</sub>                | -40                        | _                      | 105                        | °C      | Ordering Option         |

|                                                        |                                | -40                        | _                      | 125                        |         |                         |

|                                                        |                                | -55                        |                        | 125                        |         |                         |

Note 1: The VC-830 power supply should be filtered. For example, a 10 µF, 0.1 µF, and 0.01 µF capacitor.

2: Includes calibration tolerance, operating temperature, supply voltage variations, aging, and IR reflow.

**3:** Figure 1-1 defines the test circuit and Figure 1-2 defines these parameters.

**4:** Output rise and fall time will be 600 ps (max.) for -40°C to +105°C, -40°C to +125°C, and -55°C to +125°C operating temperature ranges.

- **5:** Duty Cycle is measured as On/Time Period.

- 6: Measured using an Agilent E5052 Signal Source Analyzer at 25°C.

- 7: Outputs will be enabled if Enable/Disable is left open. There is an oscillation detection circuit that ensures glitch free output upon power-up or enable.

- 8: In order to reduce current, the pull-up resistance is higher when V<sub>DD</sub> is set to ground.

FIGURE 1-2: LVPECL Output Rise/Fall Time.

FIGURE 1-1: LVPECL Test Circuit.

#### **ELECTRICAL CHARACTERISTICS, LVDS OPTION**

| Parameter                        | Sym.            | Min.  | Тур. | Max.  | Units | Conditions                 |

|----------------------------------|-----------------|-------|------|-------|-------|----------------------------|

|                                  |                 | 1.71  | 1.8  | 1.89  |       |                            |

| Supply Voltage (Note 1)          | V <sub>DD</sub> | 2.37  | 2.5  | 2.625 | V     | Ordering Option            |

|                                  |                 | 3.135 | 3.3  | 3.465 |       |                            |

|                                  |                 |       | —    | 25    |       | 1.8V, 175 MHz              |

|                                  |                 |       |      | 29    |       | 2.5V, 200 MHz              |

| Current Consumption              | I <sub>DD</sub> |       |      | 35    | mA    | 2.5V, 320 MHz              |

|                                  |                 |       | —    | 30    |       | 3.3V, 200 MHz              |

|                                  |                 |       | _    | 35    |       | 3.3V, 320 MHz              |

| Frequency                        |                 |       |      |       |       |                            |

| Nominal Frequency                | f <sub>N</sub>  | 100   |      | 320   | MHz   | Ordering Option,<br>Note 9 |

|                                  |                 | _     | _    | ±20   |       |                            |

|                                  |                 | _     |      | ±25   | ]     |                            |

| Stability (Note 2)               | —               | _     | _    | ±30   | ppm   | Ordering Option            |

|                                  |                 | _     |      | ±50   | 1     |                            |

|                                  |                 | _     |      | ±100  | ]     |                            |

| Outputs                          |                 |       |      |       |       |                            |

| Output Logic Level High (Note 3) | V <sub>OH</sub> |       | 1.43 | 1.6   |       |                            |

| Output Logic Level Low (Note 3)  | V <sub>OL</sub> | 0.9   | 1.10 |       | V     | -                          |

| Differential Output Amplitude    | _               | 247   | 350  | 454   | mV    | 100Ω Differential<br>load  |

Note 1: The VC-830 power supply should be filtered. For example, a 10  $\mu$ F, 0.1  $\mu$ F, and 0.01  $\mu$ F capacitor.

2: Includes calibration tolerance, operating temperature, supply voltage variations, aging, and IR reflow.

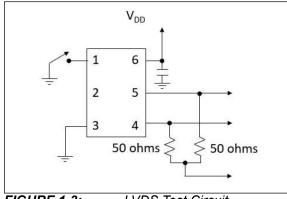

3: Figure 1-3 defines the test circuit and Figure 1-2 defines these parameters.

**4:** Output rise and fall time will be 600 ps (max.) for -40°C to +105°C, -40°C to +125°C, and -55°C to +125°C operating temperature ranges.

5: Duty Cycle is measured as On/Time Period.

6: Measured using an Agilent E5052 Signal Source Analyzer at 25°C.

7: Outputs will be enabled if Enable/Disable is left open. There is an oscillation detection circuit that ensures glitch free output upon power-up or enable.

8: In order to reduce current, the pull-up resistance is higher when V<sub>DD</sub> is set to ground.

**9:** 1.8V option available up to 175 MHz.

#### **ELECTRICAL CHARACTERISTICS, LVDS OPTION (CONTINUED)**

| Parameter                                              | Sym.                           | Min.                  | Тур.        | Max.                  | Units     | Conditions            |

|--------------------------------------------------------|--------------------------------|-----------------------|-------------|-----------------------|-----------|-----------------------|

| Differential Output Error                              | _                              | _                     | _           | 50                    | mV        | _                     |

| Offset Voltage                                         | _                              | 1.125                 | 1.25        | 1.375                 | V         | _                     |

| Offset Voltage Error                                   |                                | _                     |             | 50                    | mV        | _                     |

| Output Leakage Current, Outputs<br>Disabled            | _                              | _                     |             | 30                    | μA        | _                     |

| Output Rise and Fall Time (Note 3)                     | t <sub>r</sub> /t <sub>f</sub> | _                     |             | 300                   | ps        | Note 4                |

| Load                                                   | _                              | 10                    | 0Ω Differen | tial                  |           | _                     |

| Duty Cycle (Note 5)                                    | DC                             | 45                    |             | 55                    | %         | _                     |

|                                                        |                                | _                     | -79         | _                     |           | 10 Hz                 |

|                                                        | Φ <sub>N</sub>                 |                       | -110        | _                     |           | 100 Hz                |

|                                                        |                                |                       | -130        |                       |           | 1 kHz                 |

| Phase Noise, 3.3V, 156.25 MHz                          |                                | _                     | -154        | _                     | dD a/l != | 10 kHz                |

| (Note 6)                                               |                                |                       | -160        |                       | dBc/Hz    | 100 kHz               |

|                                                        |                                | _                     | -162        | _                     |           | 1 MHz                 |

|                                                        |                                | _                     | -163        | _                     |           | 10 MHz                |

|                                                        |                                | _                     | -164        | _                     |           | 20 MHz                |

| Phase Jitter, 156.25 MHz,<br>12 kHz to 20 MHz (Note 6) | φJ                             | _                     | 43          | 64                    | fs        | _                     |

| Enable/Disable                                         |                                |                       |             |                       |           |                       |

| Outputs Enabled (Note 7)                               | V <sub>IH</sub>                | 0.7 * V <sub>DD</sub> | _           | _                     | V         | _                     |

| Outputs Disabled                                       | V <sub>IL</sub>                | _                     | _           | 0.3 * V <sub>DD</sub> | V         | _                     |

| Disable Time                                           | t <sub>D</sub>                 | _                     | _           | 200                   | ns        | —                     |

| E/D Pull-Up Resistance (Note 8)                        |                                | 0.5                   | _           | 2                     | MΩ        | E/D = GND             |

| E/D Pull-Up Resistance                                 |                                | 30                    |             | 150                   | kΩ        | E/D = V <sub>DD</sub> |

| Start-Up Time                                          | t <sub>SU</sub>                |                       |             | 10                    | ms        | _                     |

|                                                        |                                | -10                   |             | 70                    |           |                       |

|                                                        |                                | -40                   |             | 85                    |           |                       |

| Operating Temperature                                  | T <sub>OP</sub>                | -40                   |             | 105                   | °C        | Ordering Option       |

|                                                        |                                | -40                   |             | 125                   |           |                       |

|                                                        |                                | -55                   |             | 125                   |           |                       |

Note 1: The VC-830 power supply should be filtered. For example, a 10  $\mu$ F, 0.1  $\mu$ F, and 0.01  $\mu$ F capacitor.

2: Includes calibration tolerance, operating temperature, supply voltage variations, aging, and IR reflow.

3: Figure 1-3 defines the test circuit and Figure 1-2 defines these parameters.

- **4:** Output rise and fall time will be 600 ps (max.) for -40°C to +105°C, -40°C to +125°C, and -55°C to +125°C operating temperature ranges.

- **5:** Duty Cycle is measured as On/Time Period.

- 6: Measured using an Agilent E5052 Signal Source Analyzer at 25°C.

- 7: Outputs will be enabled if Enable/Disable is left open. There is an oscillation detection circuit that ensures glitch free output upon power-up or enable.

- 8: In order to reduce current, the pull-up resistance is higher when V<sub>DD</sub> is set to ground.

- 9: 1.8V option available up to 175 MHz.

FIGURE 1-3: LVDS Test Circuit.

#### **ELECTRICAL CHARACTERISTICS, HCSL OPTION**

| Parameter                                   | Sym.                           | Min.  | Тур. | Max.  | Units | Conditions                           |

|---------------------------------------------|--------------------------------|-------|------|-------|-------|--------------------------------------|

|                                             |                                | 1.71  | 1.8  | 1.81  |       |                                      |

| Supply Voltage (Note 1)                     | $V_{DD}$                       | 2.375 | 2.5  | 2.625 | V     | Ordering Option                      |

|                                             |                                | 3.135 | 3.3  | 3.465 |       |                                      |

| Current Consumption                         |                                |       | _    | 46    |       | 1.8V: 175 MHz<br>2.5V, 3.3V: 200 MHz |

| Current Consumption                         | I <sub>DD</sub>                |       | _    | 53    | - mA  | 1.8V, 2.5V, 3.3V,<br>312 MHz         |

| Frequency                                   |                                |       |      |       |       |                                      |

| Nominal Frequency                           | f <sub>N</sub>                 | 100   | _    | 312   | MHz   | Ordering Option,<br>Note 8           |

|                                             |                                |       |      | ±20   | ppm   | Ordering Option                      |

|                                             | _                              |       |      | ±25   |       |                                      |

| Stability (Note 2)                          |                                |       |      | ±30   |       |                                      |

|                                             |                                |       |      | ±50   |       |                                      |

|                                             |                                | _     | —    | ±100  |       |                                      |

| Outputs                                     |                                |       |      |       |       |                                      |

| Output Logic Lovel High (Note 2)            | V                              | 0.55  | —    | 1.0   |       | 1.8V                                 |

| Output Logic Level High (Note 3)            | V <sub>OH</sub>                | 0.6   | —    | 0.9   | V     | 2.5V, 3.3V                           |

| Output Logic Level Low (Note 3)             | V <sub>OL</sub>                | -0.15 |      | 0.15  |       | _                                    |

| Output Leakage Current, Outputs<br>Disabled | _                              | —     | —    | 30    | μA    | _                                    |

| Output Rise and Fall Time (Note 3)          | t <sub>r</sub> /t <sub>f</sub> |       | _    | 600   | ps    | _                                    |

Note 1: The VC-830 power supply should be filtered. For example, a 10  $\mu$ F, 0.1  $\mu$ F, and 0.01  $\mu$ F capacitor.

2: Includes calibration tolerance, operating temperature, supply voltage variations, aging, and IR reflow.

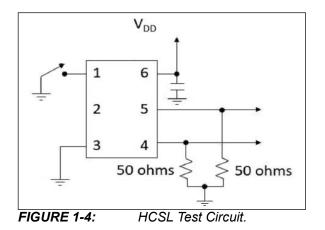

**3:** Figure 1-3 defines the test circuit and Figure 1-2 defines these parameters.

4: Duty Cycle is measured as On/Time Period.

5: Measured using an Agilent E5052 Signal Source Analyzer at 25°C.

6: Outputs will be enabled if Enable/Disable is left open. There is an oscillation detection circuit that ensures glitch free output upon power-up or enable.

7: In order to reduce current, the pull-up resistance is higher when  $V_{DD}$  is set to ground.

**8:** 1.8V option available up to 175 MHz.

# **ELECTRICAL CHARACTERISTICS, HCSL OPTION (CONTINUED)**

| Parameter                                               | Sym.            | Min.                  | Тур.       | Max.                  | Units  | Conditions      |

|---------------------------------------------------------|-----------------|-----------------------|------------|-----------------------|--------|-----------------|

| Load                                                    |                 |                       | 50Ω to GNE | )                     |        | _               |

| Duty Cycle (Note 4)                                     | DC              | 45                    | _          | 55                    | %      | _               |

|                                                         |                 | _                     | -79        | _                     |        | 10 Hz           |

|                                                         |                 | _                     | -110       | _                     |        | 100 Hz          |

|                                                         |                 | _                     | -130       | _                     |        | 1 kHz           |

| Phase Noise, 3.3V, 156.25 MHz                           |                 | _                     | -154       | _                     |        | 10 kHz          |

| (Note 5)                                                | φ <sub>N</sub>  | —                     | -160       | _                     | dBc/Hz | 100 kHz         |

|                                                         |                 | _                     | -162       | _                     |        | 1 MHz           |

|                                                         |                 |                       | -163       | _                     |        | 10 MHz          |

|                                                         |                 | _                     | -164       | _                     |        | 20 MHz          |

| Phase Jitter, 100.000 MHz,<br>12 kHz to 20 MHz (Note 5) | фJ              | _                     | 55         | _                     | fs     | _               |

| Enable/Disable                                          |                 |                       |            |                       |        |                 |

| Outputs Enabled (Note 6)                                | V <sub>IH</sub> | 0.7 * V <sub>DD</sub> | _          | _                     | V      | _               |

| Outputs Disabled                                        | V <sub>IL</sub> | _                     |            | 0.3 * V <sub>DD</sub> | V      | _               |

| Disable Time                                            | t <sub>D</sub>  | _                     |            | 200                   | ns     | —               |

| E/D Pull-Up Resistance (Note 7)                         | _               | 0.5                   |            | 2                     | MΩ     | E/D = GND       |

| E/D Pull-Up Resistance                                  | _               | 30                    |            | 150                   | kΩ     | $E/D = V_{DD}$  |

| Start-Up Time                                           | t <sub>SU</sub> | _                     |            | 10                    | ms     | _               |

|                                                         |                 | -10                   |            | 70                    |        |                 |

|                                                         | T <sub>OP</sub> | -40                   |            | 85                    | 1      |                 |

| Operating Temperature                                   |                 | -40                   |            | 105                   | °C     | Ordering Option |

|                                                         |                 | -40                   | _          | 125                   |        |                 |

|                                                         |                 | -55                   |            | 125                   |        |                 |

Note 1: The VC-830 power supply should be filtered. For example, a 10 µF, 0.1 µF, and 0.01 µF capacitor.

2: Includes calibration tolerance, operating temperature, supply voltage variations, aging, and IR reflow.

3: Figure 1-3 defines the test circuit and Figure 1-2 defines these parameters.

4: Duty Cycle is measured as On/Time Period.

5: Measured using an Agilent E5052 Signal Source Analyzer at 25°C.

**6:** Outputs will be enabled if Enable/Disable is left open. There is an oscillation detection circuit that ensures glitch free output upon power-up or enable.

7: In order to reduce current, the pull-up resistance is higher when V<sub>DD</sub> is set to ground.

8: 1.8V option available up to 175 MHz.

# 2.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 2-1.

| Pin Number | Pin Name        | Description                     |  |  |  |

|------------|-----------------|---------------------------------|--|--|--|

| 1          | E/D or NC       | Enable/Disable or No Connect.   |  |  |  |

| 2          | E/D or NC       | Enable/Disable or No Connect.   |  |  |  |

| 3          | GND             | Electrical and lid ground.      |  |  |  |

| 4          | f <sub>O</sub>  | Output frequency.               |  |  |  |

| 5          | Cf <sub>O</sub> | Complementary output frequency. |  |  |  |

| 6          | V <sub>DD</sub> | Supply voltage.                 |  |  |  |

Note: Pin 2 can be E/D and Pin 1 will be NC. Use Ordering Option B.

#### TABLE 2-2: ENABLE/DISABLE FUNCTION

| E/D Pin | Output         |  |  |  |

|---------|----------------|--|--|--|

| High    | Clock Output   |  |  |  |

| Open    | Clock Output   |  |  |  |

| Low     | High Impedance |  |  |  |

# 3.0 APPLICATION DIAGRAMS

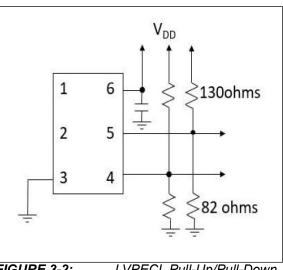

#### 3.1 LVPECL Application Diagrams

The VC-830 incorporates a standard LVPECL output scheme, which are unterminated FET drains. There are numerous application notes on terminating and interfacing LVPECL logic and the two most common methods are a single resistor to ground (Figure 3-1) and a pull-up/pull-down scheme as shown in Figure 3-2. AC-coupling capacitors are optional, depending on the application and the input logic requirements of the next stage.

One of the most important considerations is terminating the Output and Complementary Outputs equally. An unused output should not be left unterminated because if one of the two outputs is left open, it will result in excessive jitter on both. PCB layout must take this and  $50\Omega$  impedance matching into account. Load matching and power supply noise are the main contributors to jitter related problems.

**FIGURE 3-1:** LVPECL Pull-Down Resistor Termination Scheme.

Figure 3-1 shows one option to terminate LVPECL outputs and is optimized to reduce common mode noise. R1 is  $50\Omega$  for 3.3V supply voltage and  $18\Omega$  for 2.5V.

FIGURE 3-2:LVPECL Pull-Up/Pull-DownTermination.

Resistor values shown are typical for 3.3V operation. For 2.5V operation, the resistor to ground is  $62\Omega$  and the resistor to supply is  $250\Omega$ .

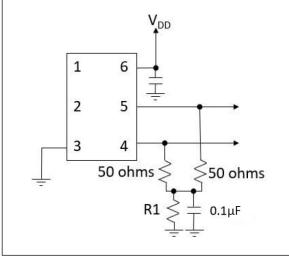

#### 3.2 LVDS Application Diagrams

One of the most important considerations is terminating the Output and Complementary Outputs equally. An unused output should not be left unterminated because if one of the two outputs is left open, it will result in excessive jitter on both. PCB layout must take this and  $50\Omega$  impedance matching into account. Load matching and power supply noise are the main contributors to jitter related problems.

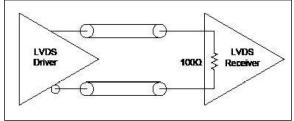

**FIGURE 3-3:** LVDS-to-LVDS Connection, Internal  $100\Omega$  Resistor.

Some LVDS structures have an internal  $100\Omega$  resistor on the input and do not need additional components. AC blocking capacitors can be used if the DC levels are incompatible.

Some input structures may not have an internal  $100\Omega$  resistor on the input and will need an external  $100\Omega$  resistor located at the receiver for impedance matching. Figure 3-4 is optimized to reduce common mode noise. Additionally, the input may have an internal DC bias that may not be compatible with LVDS levels. AC blocking capacitors, such as 0.1 µF, should be used in this case.

#### 4.0 RELIABILITY

Microchip qualification will include aging at various extreme temperatures, shock and vibration, temperature cycling, and IR reflow simulation. The VC-830 family is capable of meeting the following qualification tests.

| TABLE 4-1: | <b>ENVIRONMENTAL</b> | COMPLIANCE |

|------------|----------------------|------------|

|            |                      |            |

| Parameter                        | Conditions                                  |

|----------------------------------|---------------------------------------------|

| Mechanical Shock                 | MIL-STD-883, Method 2002                    |

| Mechanical Vibration             | MIL-STD-883, Method 2007                    |

| Temperature Cycle                | MIL-STD-883, Method 1010                    |

| Solderability                    | MIL-STD-883, Method 2003                    |

| Gross and Fine Leak              | MIL-STD-883, Method 1014                    |

| Resistance to Solvents           | MIL-STD-883, Method 2015                    |

| Moisture Sensitivity Level       | MSL 1                                       |

| Contact Pads                     | Gold (0.3 µm min., 1.0 µm max.) over Nickel |

| θ <sub>JC</sub> (Bottom of Case) | 28°C/W                                      |

| Maximum Junction Temperature     | 150°C                                       |

| Weight                           | 23 mg                                       |

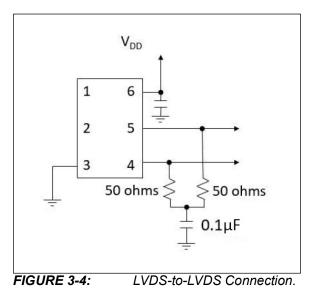

#### 5.0 IR REFLOW

Devices are built using lead-free epoxy and can be subjected to standard lead-free IR reflow conditions shown in Table 5-1. Contact pads are gold over nickel and lower maximum temperatures can also be used, such as 220°C.

FIGURE 5-1: Reflow Solder Profile.

| Parameter                | Symbol             | Value               |  |  |

|--------------------------|--------------------|---------------------|--|--|

| Pre-Heat Time            | t <sub>S</sub>     | 200 seconds maximum |  |  |

| Ramp Up                  | R <sub>UP</sub>    | 3°C/sec. maximum    |  |  |

| Time above 217°C         | t                  | 150 seconds maximum |  |  |

| Time to Peak Temperature | T <sub>AMB-P</sub> | 480 seconds maximum |  |  |

| Time at 260°C            | t <sub>P</sub>     | 30 seconds maximum  |  |  |

| Time at 240°C            | t <sub>P2</sub>    | 60 seconds maximum  |  |  |

| Ramp Down                | R <sub>DN</sub>    | 6°C/sec. maximum    |  |  |

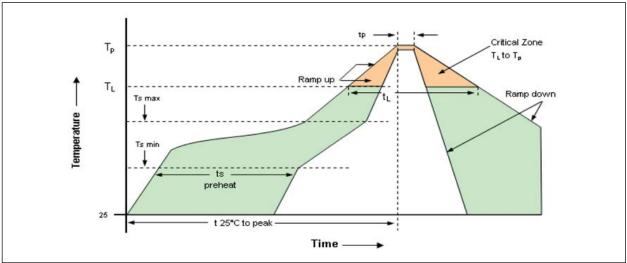

# 6.0 TAPE AND REEL

| Tape Dimensions (mm) |     |     |     |     | Reel Dimensions (mm) |     |     |     |     |     |     |     |       |

|----------------------|-----|-----|-----|-----|----------------------|-----|-----|-----|-----|-----|-----|-----|-------|

| Dimension            | W   | F   | Do  | Ро  | P1                   | Α   | В   | С   | D   | N   | W1  | W2  | # per |

| Tolerance            | Тур | Тур | Тур | Тур | Тур                  | Тур | Тур | Тур | Тур | Тур | Тур | Max | Reel  |

| VC-830               | 8   | 3.5 | 1.5 | 4   | 4                    | 178 | 2   | 13  | 21  | 60  | 10  | 14  | 3000  |

#### TABLE 6-1: TAPE AND REEL DIMENSIONS

FIGURE 6-1: Tape and Reel Diagram.

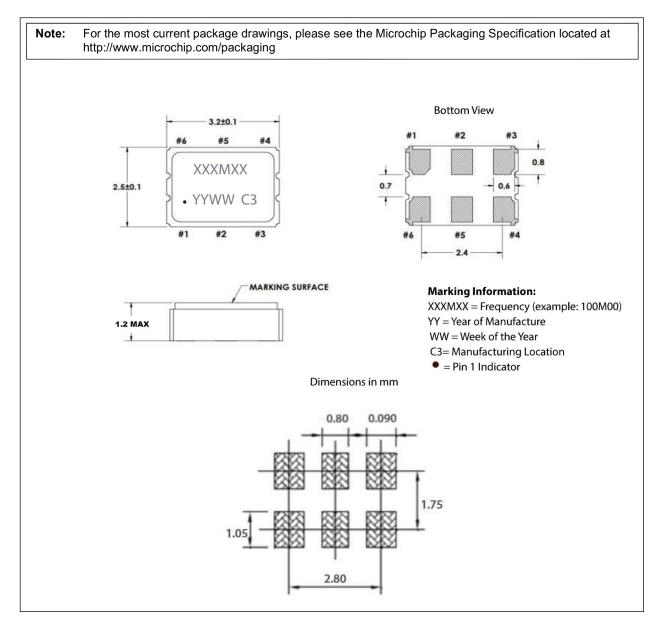

# 7.0 PACKAGING INFORMATION

#### 6-Lead 3.2 mm × 2.5 mm Package Outline and Recommended Land Pattern

#### APPENDIX A: REVISION HISTORY

#### Revision A (May 2021)

- Converted Vectron document VC-830 to Microchip data sheet template DS20006510A.

- Minor grammatical text changes throughout.

#### **Revision B (August 2021)**

- Added a plus/minus (±) symbol to each value listed for Output Amplitude in the Electrical Characteristics, LVDS Option table.

- Updated maximum package height to 1.2 mm.

#### Revision C (April 2024)

- Corrected the Storage Temperature range in the Absolute Maximum Ratings section.

- Added new HCSL ordering option details throughout document, including but not limited to the Electrical Characteristics, HCSL Option, table and Figure 1-4.

#### **Revision D (December 2024)**

- Updated Features.

- Updated Electrical Characteristics, LVPECL Option, Electrical Characteristics, LVDS Option, and Electrical Characteristics, HCSL Option.

- Updated the Product Identification System section.

NOTES:

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, contact your local Microchip representative or sales office.

| <u>Device</u>            | - <u>X</u>                                                                                                                                               |                  | <u>X</u>                                                                     | <u>x</u>                   | - <u>X</u>                                        | <u>x</u>  | <u>X</u>                                                                                                                                                                                                                                       | <u>X</u>                                                                              | - <u>XXXXXXXXXXX</u>                              | <u>XX</u>                      |  |  |  |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------|----------------------------|---------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------|--|--|--|

| Part No.                 | Power<br>Supply                                                                                                                                          |                  | Output                                                                       | Temp.<br>Range             | Stability                                         | E/D Logic | E/D Pi                                                                                                                                                                                                                                         | n Custom<br>Options                                                                   | Frequency                                         | Packaging                      |  |  |  |

| Device:                  | VC                                                                                                                                                       | -830:            |                                                                              |                            | LVDS Crystal Oscillator in<br>.2 mm x 2.5 mm VDFN |           |                                                                                                                                                                                                                                                | Examples:<br>a) VC-830-ECF-GAAN-156M250000TR:<br>VC-830, 3.3VDC, LVPECL Output, -40°0 |                                                   |                                |  |  |  |

| Power Supply:            | E<br>H<br>J                                                                                                                                              | =<br>=<br>=      | 3.3VDC ±5%<br>2.5VDC ±5%<br>1.8VDC ±5%                                       |                            |                                                   |           |                                                                                                                                                                                                                                                | +105°C Tem<br>Output Enal<br>Standard Opt                                             | p Range, ±30<br>bled, Pin 1 E<br>ion, 156.25 MHz, | ppm Stability<br>nable/Disable |  |  |  |

| Output:                  | C<br>D<br>H                                                                                                                                              | =<br>=<br>=      | LVPECL<br>LVDS<br>HCSL                                                       |                            |                                                   |           | b) VC-830-HDW-KAAN-125M000000TR:<br>VC-830, 2.5VDC, LVDS Output, -10°C t<br>+70°C Temp Range, ±50 ppm Stabilit<br>Output Enabled, Pin 1 Enable/Disable<br>Standard Option, 125 MHz, 3000/Reel                                                  |                                                                                       |                                                   |                                |  |  |  |

| Temperature<br>Range:    | E F W G C                                                                                                                                                | =<br>=<br>=<br>= | -40°C to +85<br>-40°C to +10<br>-10°C to +70<br>-40°C to +12<br>-55°C to +12 | 95°C<br>9°C<br>25°C        |                                                   |           | Note 1: Tape and Reel identifier only appears in the catalog part number description. This identifier used for ordering purposes and is not printed the device package. Check with your Microot Sales Office for package availability with the |                                                                                       |                                                   |                                |  |  |  |

| Stability:               | E F G K<br>S                                                                                                                                             | =<br>=<br>=<br>= | ±20 ppm<br>±25 ppm<br>±30 ppm<br>±50 ppm<br>±100 ppm                         |                            |                                                   |           |                                                                                                                                                                                                                                                | Tape and Reel o                                                                       | ption.                                            |                                |  |  |  |

| Enable/Disable<br>Logic: | A                                                                                                                                                        | =                | Output Enab                                                                  | led with a Lo              | gic High or Open                                  |           |                                                                                                                                                                                                                                                |                                                                                       |                                                   |                                |  |  |  |

| Enable/Disable<br>Pin:   | A<br>B                                                                                                                                                   | =<br>=           |                                                                              | = No Connec<br>= No Connec |                                                   |           |                                                                                                                                                                                                                                                |                                                                                       |                                                   |                                |  |  |  |

| Custom<br>Options:       | Ν                                                                                                                                                        | =                | Standard op                                                                  | ion                        |                                                   |           |                                                                                                                                                                                                                                                |                                                                                       |                                                   |                                |  |  |  |

| Frequency:               | ххх                                                                                                                                                      | Mxxxx            | xx=Frequency                                                                 | in MHz                     |                                                   |           |                                                                                                                                                                                                                                                |                                                                                       |                                                   |                                |  |  |  |

| Packaging:               | TR<br><black< td=""><td></td><td>3,000/Reel<br/>Cut Tape/ no</td><td>n-TR quantiti</td><td>es</td><td></td><td></td><td></td><td></td><td></td></black<> |                  | 3,000/Reel<br>Cut Tape/ no                                                   | n-TR quantiti              | es                                                |           |                                                                                                                                                                                                                                                |                                                                                       |                                                   |                                |  |  |  |

Note: Not all combinations of options are available. Other specifications may be available upon request.

NOTES:

# **Microchip Information**

#### Trademarks

The "Microchip" name and logo, the "M" logo, and other names, logos, and brands are registered and unregistered trademarks of Microchip Technology Incorporated or its affiliates and/or subsidiaries in the United States and/or other countries ("Microchip Trademarks"). Information regarding Microchip Trademarks can be found at https://www.microchip.com/en-us/about/legalinformation/microchip-trademarks.

ISBN: 979-8-3371-0278-8

#### Legal Notice

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at www.microchip.com/en-us/support/design-help/client-support-services.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

# **Microchip Devices Code Protection Feature**

Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not mean that we are guaranteeing the product is "unbreakable". Code protection is constantly evolving. Microchip is committed to continuously improving the code protection features of our products.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# Microchip:

VC-830-ECE-FAAN-156M250000

VC-830-ECE-FAAN-156M250000TR

VC-830-ECE-KAAN-155M520000

VC-830-ECE-KAAN-155M520000TR

VC-830-ECF

GAAN-155M520000

VC-830-ECE-KAAN-156M250000

VC-830-ECE-KAAN-156M250000TR

VC-830-ECF

GAAN-156M250000

VC-830-ECF-GAAN-156M250000TR

VC-830-EDE-FAAN-156M250000TR

VC-830-EDE-FAAN-156M250000TR

156M250000TR

VC-830-EDF-GAAN-156M250000TR

VC-830-EDF-GAAN-156M250000TR

VC-830-EDE-FAAN-156M250000TR

156M250000

VC-830-EDF-GAAN-156M250000TR

VC-830-EDF-GAAN-156M250000TR

VC-830-HCE-FAAN-156M250000TR

156M250000

VC-830-HCE-FAAN-156M250000TR

VC-830-0001-156M250000TR

VC-830-HCE-FAAN-156M250000TR