## **Three-Phase Brushless Motor Gate Driver SBC**

ATA6847 Data Sheet

## Description (Submit Feedback)

The ATA6847 is a Three-Phase Brushless Motor Gate Driver System Basis Chip (SBC) for brushless motor control, designed using advanced SOI technology. In combination with a microcontroller and six discrete power MOSFETs, the SBC forms a brushless DC motor control unit. Through six dedicated parallel inputs, the gate driver units (GDU) can be controlled independently, supporting duty cycle operations from 0% to 100%, due to the implementation of two charge pumps, for low and high-side gate drives. In addition, the circuit provides 5V and 3.3V low dropout voltage regulators, two current-sensing operational amplifiers, an integrated Back-EMF detection module and a window watchdog. The microcontroller controls the ATA6847 using an SPI interface.

## Features (Submit Feedback)

#### General

- Power Supply Voltage Range from 3V to 42V

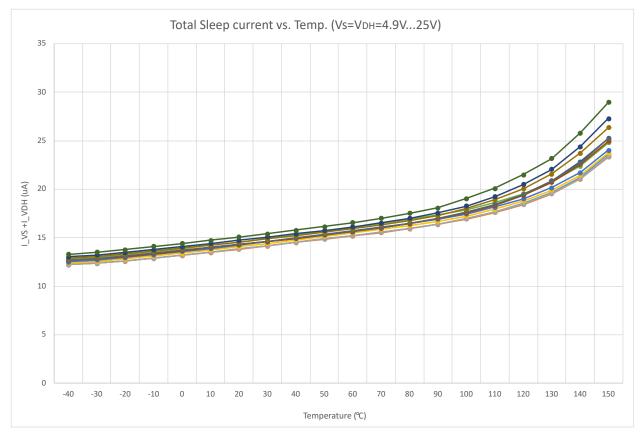

- Sleep (Deep Sleep) Mode with Maximum 15 µA Current Consumption with Full Wake-up Capability (Local Wake-up)

- 3.3V or 5V Microcontroller Interface

- Up to 4 MHz SPI Bus for Device Configuration and Register Access

- SPI Frame Error Detection

- Dedicated NIRQ Pin for MCU External Interrupt in order to Report Events Directly

- Input-Output Reset Pin (NRES) with Variable Reset Length to Support a Wide Variety of Microcontrollers

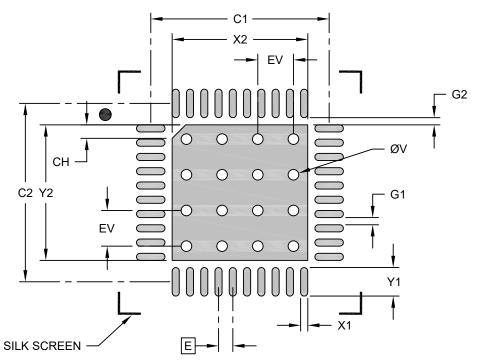

- Package: QFN40 with Wettable Flanks and Exposed Pad

### Motor Gate Driver Unit (GDU)

- VDH Motor Operating Voltage Range from 4.9V to 32V (Overvoltage Lockout Level)

- VS Undervoltage

- VDH Overvoltage Lockout selectable

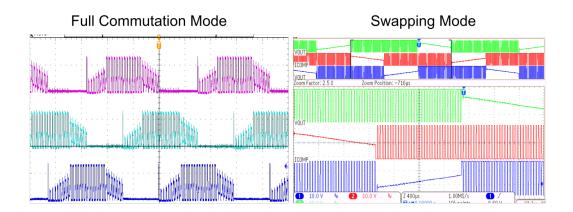

- Individual Driving of Six External NMOS Transistors or Complementary Driving of Three Half Bridges with Three Pairs of PWM Input Pins

- Maximum Switching Frequency of 50 kHz with 100 nC Gate Charge per MOSFET

- Charge Pumps for Supporting Crank Pulse Voltage Operation and 100% PWM Duty Cycle Control

- MOSFET VGS Undervoltage Monitoring, Configurable Undervoltage Lockout Level

- MOSFET VDS Monitoring, Configurable Short Circuit Detection Levels

- Cross Conduction Protection Timer

- Programmable Deadtime Insertion or Adaptive Deadtime Control

- Failure Detection Blanking Time for All Protection Features

- Configurable Fault Filter Times for VGSUV, ILIM and SCP

## **Current Sense Amplifier (CSA)**

- Two Integrated High-performance CSA with Configurable Gain and Output Offset

- One Advanced Power Stage Current Limitation Using OpAmp Output and Integrated DAC

## **Back-EMF Detection**

• Back-EMF Feedback Detector Including Motor Neutral Point Emulation

### **Voltage Regulators**

- VDD1 5V/3.3V, 100 mA

- ±2% accuracy

- Foldback short circuit limit (I<sub>VDD1</sub> + I<sub>VDD2</sub> = 105-135 mA)

- Short-circuit protection

- Undervoltage detection

- Overvoltage protection and detection

- VDD2 3.3V, 70 mA

- ±2% accuracy

- Current limitation 75 mA

- Short-circuit protection

- Undervoltage detection

- Overvoltage protection and detection

- High-voltage Output INH for Controlling an External Component, Like a Voltage Regulator (VDD2 Not Available in this Variant)

## Watchdog

- Window and Time-out Modes

- Optional Cyclic Wake-up in Time-out Mode

- Configurable Period and Reset Pulse Length

- Limp Home (LH) High-voltage Failure Output

## **Functional Safety Support**

- ISO 26262:2018 Functional Safety Ready up to ASIL B

- IEC 61508:2010 Functional Safety Ready up to SIL 2

## Applications (Submit Feedback)

- Home Appliances using BLDC Motor Control

- Power Tool Motors

- Hobby Aircraft, Boats, Drones or Vehicles

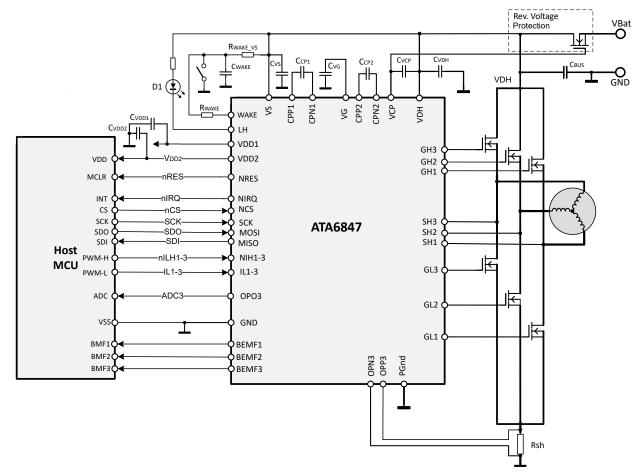

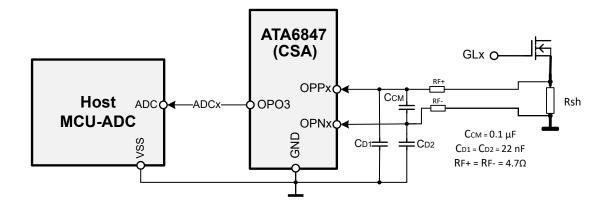

## 1. Typical Application Circuit(s) (Submit Feedback)

The typical application shows a B-EMF system configuration for a 6-step trapezoidal application and a shunt as a current limit sensor. The application circuit is also suited for a single-shunt FOC application, with the current limitation functionality of the single shunt and detect wind milling via the B-EMF sampler. The charge pump output (VCP) controls the reverse polarity protection N-channel MOSFET.

Figure 1-1. Typical Application Schematic: ATA6847

- R<sub>WAKE</sub> = 2.7 kΩ

- C<sub>WAKE</sub> = 100 nF

- R<sub>WAKE\_VS</sub> = 10 kΩ

- C<sub>VDD1</sub> = C<sub>VDD2</sub> = 2.2 μF

- $R_{NRES} = R_{NIRQ} = 10 \text{ k}\Omega$

- $C_{VS} = 10 \ \mu F \ | \ | \ 100 \ nF$

- $C_{VDH} = 47 \ \mu F \ | \ | \ 100 \ nF$

- C<sub>CP1</sub> = 330 nF

- C<sub>CP2</sub> = 220 nF

- $C_{VG} = C_{VCP} = 3.3 \,\mu F$

## 2. Product Family (Submit Feedback)

The name, features and package types of each device are listed in the following table. All devices integrate six dedicated parallel gate drivers and a B-EMF comparator.

#### Table 2-1. ATA6847 Family Overview

| Product Name | VDD1 LDO<br>(Note 1) | VDD2 LDO<br>(Note 1) | INH | OpAmps / OpAmps+ B-<br>EMF<br>(Note 2) | OpAmp output<br>rail,<br>MCU interface<br>voltage<br>[VIO] | Package |

|--------------|----------------------|----------------------|-----|----------------------------------------|------------------------------------------------------------|---------|

| ATA6847-5050 | 5V 100 mA            | 3.3V 70 mA           |     | 2 / 1 + 1                              | 5V                                                         | 40-VQFN |

| ATA6847-3333 | 3.3V 100 mA          |                      | x   | 2 / 1 + 1                              | 3.3V                                                       | 40-VQFN |

| ATA6847-5033 | 5V 100 mA            | 3.3V 70 mA           |     | 2 / 1 + 1                              | 3.3V                                                       | 40-VQFN |

### Notes:

- 1. Sum current ( $I_{VDD1} + I_{VDD2}$ ) maximum 100 mA

- Selectable via SPI: Two OpAmps or One OpAmp plus One B-EMF sampler

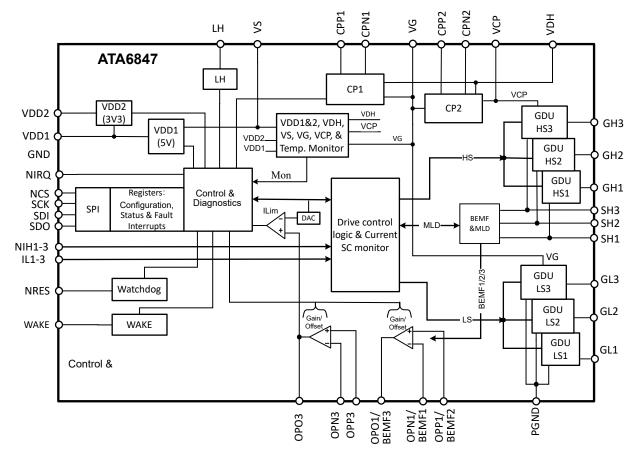

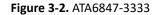

## 3. Block Diagram (Submit Feedback)

Figure 3-1. ATA6847-5050, ATA6847-5033

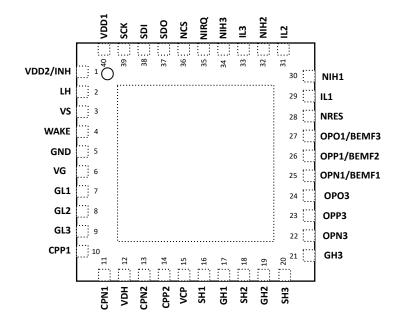

# 4. Pin Configuration (Submit Feedback)

| Pin Name    | 40 Pin | Pin Description                                                                                                                                   |

|-------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD2 / INH  | 1      | 70 mA, 3.3V supply voltage/INH is the high-voltage output designed to control an external voltage regulator.                                      |

| LH          | 2      | Limp Home – High-voltage failure output, Open drain                                                                                               |

| VS          | 3      | Battery supply pin                                                                                                                                |

| WAKE        | 4      | High-voltage input for local wake-up                                                                                                              |

| GND         | 5      | LDO and analog ground                                                                                                                             |

| VG          | 6      | 12V gate drive regulator/charge pump 1 output                                                                                                     |

| GL1         | 7      | Gate driver output for low-side MOSFET, phase 1                                                                                                   |

| GL2         | 8      | Gate driver output for low-side MOSFET, phase 2                                                                                                   |

| GL3         | 9      | Gate driver output for low-side MOSFET, phase 3                                                                                                   |

| CPP1        | 10     | Charge pump 1 flying capacitor positive connection 1                                                                                              |

| CPN1        | 11     | Charge pump 1 flying capacitor negative connection 1                                                                                              |

| VDH         | 12     | Supply for VG and charge pump, high-side drain-source voltage monitoring reference, reference voltage level for charge pump 2 reservoir capacitor |

| CPN2        | 13     | Charge pump 2 flying capacitor negative connection 2                                                                                              |

| CPP2        | 14     | Charge pump 2 flying capacitor positive connection 2                                                                                              |

| VCP         | 15     | Charge pump 2 reservoir capacitor, gate drive supply of high-side MOSFET gate drivers                                                             |

| SH1         | 16     | Motor connection terminal 1 and phase 1 high-side MOSFET source terminal                                                                          |

| GH1         | 17     | Gate driver output for high-side MOSFET, phase 1                                                                                                  |

| SH2         | 18     | Motor connection terminal 2 and phase 2 high-side MOSFET source terminal                                                                          |

| GH2         | 19     | Gate driver output for high-side MOSFET, phase 2                                                                                                  |

| SH3         | 20     | Motor connection terminal 3 and phase 3 high-side MOSFET source terminal                                                                          |

| GH3         | 21     | Gate driver output for the high-side MOSFET, phase 3                                                                                              |

| OPN3        | 22     | Current sense OpAmp 3 inverting input                                                                                                             |

| OPP3        | 23     | Current sense OpAmp 3 non-inverting input                                                                                                         |

| OPO3        | 24     | Current sense OpAmp 3 output                                                                                                                      |

| OPN1/ BEMF1 | 25     | Current sense OpAmp 1 inverting input/B-EMF feedback phase 1                                                                                      |

| OPP1/ BEMF2 | 26     | Current sense OpAmp 1 non-inverting input/B-EMF feedback phase 2                                                                                  |

| OPO1/ BEMF3 | 27     | Current sense OpAmp 1 output/B-EMF feedback phase 3                                                                                               |

| NRES        | 28     | Input/output pin for resetting microcontroller, pull-up to VIO, active low                                                                        |

| IL1         | 29     | Low-side digital driver input – use in direct control mode to activate GL1 or in complementary control mode as enable line for phase 1            |

| NIH1        | 30     | High-side digital driver input – use in direct control mode to activate GH1 or in complementary control mode as PWM input for phase 1, active low |

| IL2         | 31     | Low-side digital driver input – use in direct control mode to activate GL2 or in complementary control mode as enable line for phase 2            |

| NIH2        | 32     | High-side digital driver input – use in direct control mode to activate GH2 or in complementary control mode as PWM input for phase 2, active low |

| IL3         | 33     | Low-side digital driver input – use in direct control mode to activate GL3 or in complementary control mode as enable line for phase 3            |

| contir   | nued   |                                                                                                                                                   |

|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | 40 Pin | Pin Description                                                                                                                                   |

| NIH3     | 34     | High-side digital driver input – use in direct control mode to activate GH3 or in complementary control mode as PWM input for phase 3, active low |

| NIRQ     | 35     | Interrupt output, pull-up to VIO, active low                                                                                                      |

| NCS      | 36     | SPI chip-select, active low                                                                                                                       |

| SDO      | 37     | SPI Serial Data Output                                                                                                                            |

| SDI      | 38     | SPI Serial Data Input                                                                                                                             |

| SCK      | 39     | SPI Clock Input                                                                                                                                   |

| VDD1     | 40     | 100 mA, 5V/3.3V supply voltage                                                                                                                    |

| PGND     | EP     | Exposed Thermal Pad: Heat slug, general device ground                                                                                             |

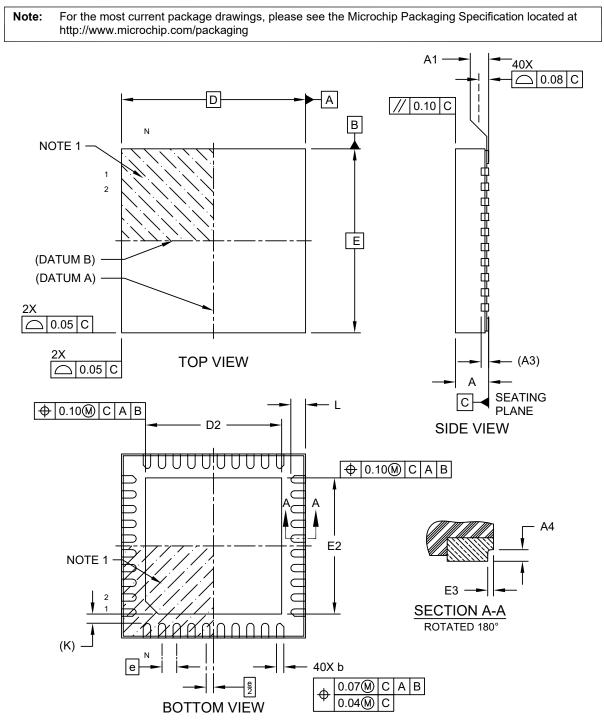

## 4.1 Package (Submit Feedback)

**Figure 4-1.** 40-VQFN (5x5x0.9 mm<sup>3</sup>)

## 5. Functional Description (Submit Feedback)

Safe operation is assured by a wide variety of integrated diagnostic and protection features.

The device has a wide operating voltage range and offers several power-saving operating modes for battery-based applications.

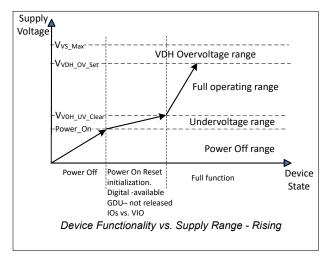

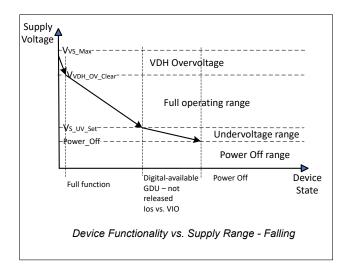

## 5.1 Supply Voltage Range vs. Device Functionality (Submit Feedback)

Figure 5-1. Device Functionality vs. Supply Range

## 5.2 Device Operating Modes (Submit Feedback) Initialization

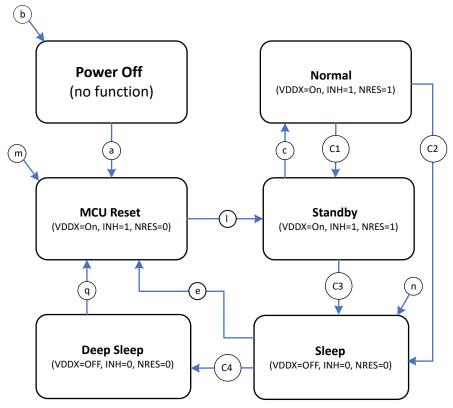

The device mode control unit of the ATA6847 implements six different modes (see Device Operating Modes):

- MCU Reset

- Normal

- Power Off

- Standby

- Deep Sleep

- Sleep

#### Figure 5-2. Device Operating Modes (DOPM)

- a: V<sub>VS</sub> ≥ V<sub>VS\_PWRON</sub> (4.2V...4.55V)

- b: V<sub>VS</sub> < V<sub>VS\_PWROFF</sub> (2.8V...3V)

- c: DOPM = Normal

- e: Wake-up/interrupt event

- f: DOPM = Standby

- g: DOPM = Sleep

- h: No wake-up and interupt event pending

- j: Illegal DOPM code configuration via SPI

- k: Number of enabled wake-up sources  $\geq 1$

- 1:

- ATA6847-5050: Reset pulse time expired & NRES not driven low externally & ((RSTLVL = 0 & V<sub>VDD1</sub> > V<sub>VDD1\_UV\_IO\_Clear</sub>) || (RSTLVL = 1 & V<sub>VDD1</sub> > V<sub>VDD1\_UV\_Clear</sub>))

- ATA6847-3333: Reset pulse time expired & NRES not driven low externally &  $V_{VDD1} > V_{VDD1\_UV\_I0\_Clear}$

- ATA6847-5033: Reset pulse time expired **&** NRES not driven low externally **&**  $V_{VDD2} > V_{VDD2\_UV\_I0\_Clear}$

- m:

- ATA6847: Watchdog activated & any Reset event

- ATA6847-5050: ( V<sub>VDD1</sub> < V<sub>VDD1\_UV\_Set</sub> & RSTLVL = 1 ) || V<sub>VDD1</sub> < V<sub>VDD1\_UV\_I0\_Set</sub>

- ATA6847-3333: V<sub>VDD1</sub> < V<sub>VDD1\_UV\_IO\_Set</sub>

- ATA6847-5033: V<sub>VDD2</sub> < V<sub>VDD2\_UV\_IO\_Set</sub>

- ATA6847: NRES pulled low externally

- n: VDDIOOVSD = 1 & VDDIO overvoltage has been detected

- p: DOPM = Deep Sleep

- q: Local wake-up has been detected

- r: Local wake-up enabled

- C1 = f || j || g & (!h || !k)

- C2 = g & h & k

- C3 = (g || p & r ) & h & k

- C4 = p & r

**Notes:** LH (Limp Home) will be activated in MCU Reset mode when:

- A watchdog failure event has been detected. (Watchdog timeout in Sleep mode will not activate LH.)

- The device enters MCU Reset mode due to a VDDx undervoltage event.

- VDDx undervoltage has been detected for longer than  $t_{\mbox{\scriptsize Reset}}$  after entering MCU Reset mode, triggered by (e).

- Mode switching triggered by condition a or q will not activate the LH pin.

- If DOPM = Normal mode and the CSCR [CSA1/3EN] bits are set, then CSA1/3 are enabled.

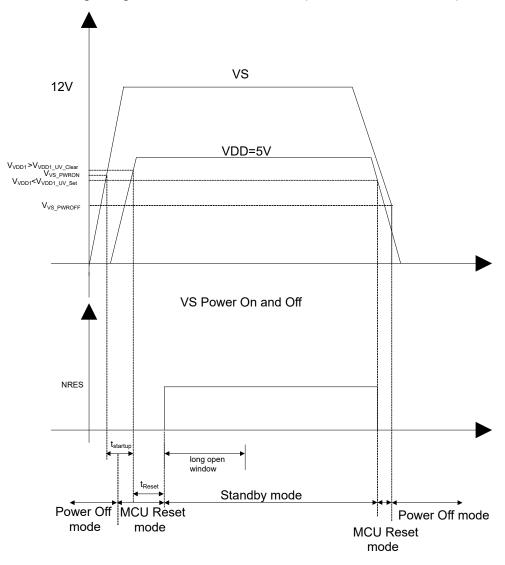

#### 5.2.1 POWER OFF MODE (Submit Feedback)

The ATA6847 is in Power OFF mode as long as the supply voltage of the device ( $V_{VS}$ ) is lower than the Power OFF Detection Voltage Threshold ( $V_{VS PWROFF}$ ).

- The watchdog is inactive.

- The LDO(s) is/are inactive.

As soon as  $V_{VS}$  rises above the Power ON Detection Threshold ( $V_{VS_PWRON}$ ), the device starts transitioning to MCU Reset mode. The device is reset, initialized and the VDDx LDOs are enabled, see Figure 5-3, "Mode Switching During Power ON Start and Power OFF (ATA6847-5050, RSTLVL = '1')".

```

Figure 5-3. Mode Switching During Power ON Start and Power OFF (ATA6847-5050, RSTLVL = '1')

```

#### 5.2.2 MCU RESET MODE (Submit Feedback)

The MCU Reset mode is the default mode of the ATA6847 after a Power-on Reset. It is the Reset execution state of the device. This mode ensures that the NRES pin is pulled down for a defined time to allow the microcontroller to be reset in a controlled manner.

The INH pin, if available, is driven high.

In the MCU Reset mode, the gate drive unit is in GDU OFF mode. The SPI is disabled. All registers will be reset. If the mode transition was triggered by the NRES pin being driven externally, the SPI communication is disabled only until t<sub>Reset</sub> expires. The LDO voltage regulators (VDDx) and the overtemperature detection are active. The watchdog is disabled.

In the MCU Reset mode, the DOPMCR Register cannot be programmed and is set to Standby.

The following events will cause the ATA6847 to transition to the MCU Reset mode:

- From Sleep mode or Deep Sleep mode after detecting a wake-up event or interrupt event.

- After a watchdog timeout or when the watchdog in the Window mode is triggered too early.

- An attempt is made to reconfigure the watchdog control register while the ATA6847 is in Normal mode.

- For the ATA6847-5050: If the RSTLVL bit in the DOPMCR register has been set to '1' and  $V_{VDD1} < V_{VDD1_UV_Set}$

- For the ATA6847: V<sub>VDD1</sub> < V<sub>VDD1\_UV\_IO\_Set</sub>

- For the ATA6847-5050, ATA6847-5033: V<sub>VDD2</sub> < V<sub>VDD2\_UV\_IO\_Set</sub>

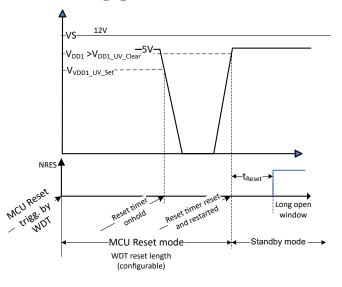

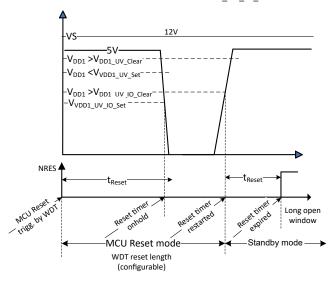

### 5.2.2.1 MCU Reset Mode and VDD Undervoltage Events (Submit Feedback)

For ATA6847-5050, if the RSTLVL bit is set to '1' (default), the device will enter MCU Reset mode after detecting a VDD1 undervoltage ( $V_{VDD1} < V_{VDD1_UV_{Set}}$ ).

The device will stay in the MCU Reset mode until VDD1 recovers ( $V_{VDD1} > V_{VDD1_UV_Clear}$ ) and then resets, restarting the Reset pulse length timer.

If VDD1 undervoltage is detected when the device is in MCU Reset mode, the Reset pulse length timer will remain on hold until VDD1 recovers and will then be reset and restarted.

The ATA6847 device will leave the MCU Reset mode and enter Standby mode after the t<sub>Reset</sub> time expires (see Device Operating Modes).

For ATA6847-3333 or ATA6847-5050, when the RSTLVL bit is set to '0', the device will enter MCU Reset mode only after Power-on start-up, after detecting a Watchdog Reset event, or after detecting  $V_{VDD1} < V_{VDD1\_UV\_I0\_Set}$ . In this case, the device will start the Reset pulse length timer after the device enters the MCU Reset mode and  $V_{VDD1} > V_{VDD1\_UV\_I0\_Clear}$  has been detected. As soon as the timer has expired, the device will transition to Standby mode.

Figure 5-4. VDD1 undervoltage (V<sub>VDD1</sub> < V<sub>VDD1</sub> UV Set) in the MCU Reset mode, RSTLVL = '1', ATA6847-5050

## 5.2.2.2 Reset Input and Output (NRES) (Submit Feedback)

The NRES pin is asserted when the ATA6847 enters MCU Reset mode. The ATA6847 also enters MCU Reset mode when the NRES pin is pulled low externally. The ATA6847 can only exit the MCU Reset mode when the NRES pin is not driven "low" externally.

**Figure 5-5.** MCU Reset mode during VDD undervoltage (V<sub>VDD</sub> < V<sub>VDD</sub> UV IO Set) when, RSTLVL = '0', ATA6847-5050

#### 5.2.3 STANDBY MODE (Submit Feedback)

In Standby mode, the gate drive unit is in GDU OFF mode. All available VDDx regulators are active. The INH pin, if available, is driven high. The watchdog is set to active by default.

A transition into Normal mode only can be achieved by setting the DOPM bits to '111'.

The ATA6847 provides various interrupt registers. Register bits (see SIR1 Register to SIR4 Register) are set to '1' by the device if a corresponding event has been detected. The detection of a wake-up or interrupt event is signaled via the NIRQ pin. The NIRQ pin voltage in high level (logic status '1') is the same as VIO voltage and will be forced to low (logic status '0') if an event has been captured and the corresponding interrupt mask bit is not set. The SPI interrupt registers can be read out to determine the corresponding trigger source.

The device will enter Standby mode in the following cases (see Device Operating Modes):

- From MCU Reset mode, after reset pulse length time expired.

- When DOPM is set to Sleep mode and a wake-up event occurs or all wake-up sources are disabled.

- From Normal mode, when DOPM is set to Standby mode via SPI.

- From Normal mode, when an invalid DOPM code was selected.

#### 5.2.3.1 Watchdog during Standby Mode (Submit Feedback)

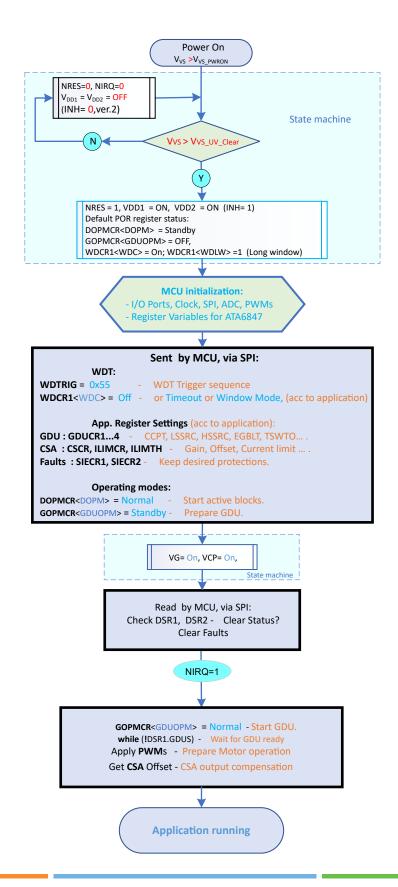

By default, the watchdog is activated when switching into Standby mode. The watchdog will start in Timeout mode by default. As a safety feature, the watchdog can **only** be configured in Standby mode. The intention is to avoid unwanted watchdog reconfiguration.

After start-up, the microcontroller is expected to initialize the ATA6847 registers. First, the microcontroller must write a valid watchdog trigger sequence (WDTRIG = 0x55).

#### 5.2.4 SLEEP MODE (Submit Feedback)

In Sleep mode, all available VDDx regulators are deactivated. The INH pin (if available) is high ohmic. The gate drive unit is in GDU OFF mode (see GDU OPERATION MODES). The device reacts to local wake-up and system interrupt events.

The device exits Sleep mode if a local wake up (WAKE) is detected. It will also exit Sleep mode as soon as an interrupt event or a Watchdog Reset occurs.

The device will enter Sleep mode in the following cases (see Device Operating Modes):

- From **Normal Mode** or **Standby Mode** via the DOPM SPI command 010 = Sleep mode, if no wake-up event is pending and at least one wake-up source is enabled. All interrupt flags must be cleared before the device can enter Sleep mode.

- From all modes when a VIO overvoltage has been detected and the VDDIOOVSD bit is set to '1'.

#### 5.2.5 DEEP SLEEP MODE (Submit Feedback)

The ATA6847 has the lowest current consumption in Deep Sleep mode. All functional blocks are deactivated, except for local wake up and VS Power OFF capture. The INH pin (if available) is high ohmic. All registers are reset.

The Deep Sleep mode can only be entered from Standby or Sleep mode, not directly from Normal mode.

Any interrupt must be cleared before entering Deep Sleep mode.

The local wake up (LOCWUE) must be activated.

Switching into Deep Sleep mode is initiated by setting the DOPM bits in the DOPMCR Register to 001 = Deep Sleep mode.

After detecting a wake-up event, the device is reset, initialized and enters MCU Reset Mode. The wake-up event initiating the wake up out of the Deep Sleep mode will be registered in the corresponding registers (SIR1 and SIR5 registers).

#### 5.2.6 NORMAL MODE (Submit Feedback)

In Normal mode, the ATA6847 provides full functionality. All available VDDx regulators are active. The INH pin (if available) is driven high.

Depending on the GDUOPM bits and failure detection status, the gate drive unit can be in GDU OFF, GDU Standby or GDU Normal mode (see GDU FSM in GDU OPERATION MODES).

#### 5.2.7 DEVICE OPERATION MODE CONTROL REGISTERS (Submit Feedback)

#### **Register 1: DOPMCR Register - Device Operation Mode Control Register (Address 0x01)**

| Bit           | 7      | 6         | 5 | 4 | 3 | 2   | 1          | 0   |

|---------------|--------|-----------|---|---|---|-----|------------|-----|

|               | RSTLVL | VDDIOOVSD | _ | — | — |     | DOPM [2:0] |     |

| Read/Write    | R/W    | R/W       | U | U | U | R/W | R/W        | R/W |

| Initial Value | 1      | 0         | 0 | 0 | 0 | 1   | 0          | 0   |

**Bit 7** - **RSTLVL** ATA6847-5050: When set to '1', a VDD1 undervoltage ( $V_{VDD1} < V_{VDD1_UV_Set}$ ) will trigger a mode switch to MCU Reset mode. When set to '0',  $V_{VDD1} < V_{VDD1_UV_IO_Set}$  will trigger a mode switch to MCU Reset mode.

This bit is unimplemented for ATA6847-3333 and ATA6847-5033.

**Bit 6 - VDDIOOVSD** The microcontroller should set the bit '1' to enable a VDD  $\mu$ C supply overvoltage shutdown when VDD ( $\mu$ C supply, the LDO connected to VIO) overvoltage has been detected. VDD  $\mu$ C supply:

- ATA6847-5050 / ATA6847-3333: VIO = VDD1

- ATA6847-5033: VIO = VDD2

#### Bits 5:3 - Unimplemented.

Bits 2:0 - DOPM [2:0] Select Device Operating mode (see Device Operating Modes):

'3' b001' = Deep Sleep mode

'3' b010' = Sleep mode

'3' b100' = Standby mode

'3' b111' = Normal mode

Other = invalid mode selection

## 5.3 Gate Drive Unit (GDU) (Submit Feedback)

#### 5.3.1 GDU FEATURES (Submit Feedback)

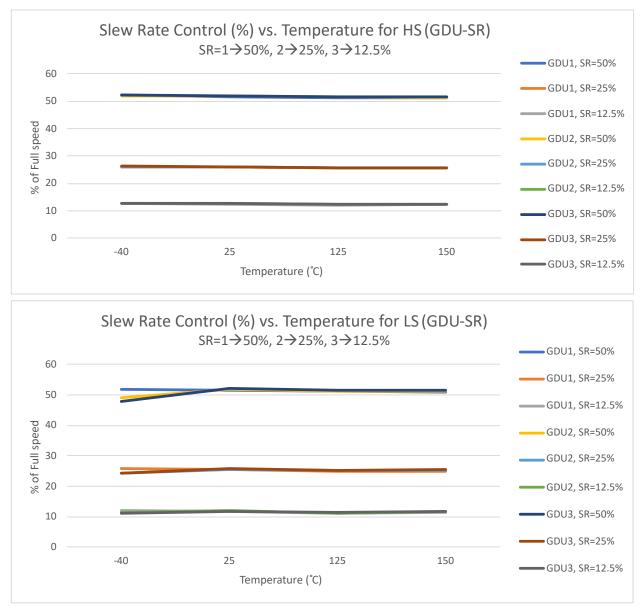

The Gate Drive Unit connects three low-side gate drive outputs (GLx) and three high-side gate drive outputs (GHx) to three gate drive half bridges. For VGSUV monitoring, the high-side gate drivers use as reference the signals between the GHx and SHx pins, whereas the low-side gate drivers use as reference the signals between the GLx and GND pins.

The GDU monitors the voltage drop between drain and source of the MOSFET for short circuit events.

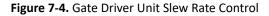

The Slew Rate Control unit optimizes EMC performance. This feature allows the control of the gate drive current injected into external MOSFET gates in four configurable levels. The slew rate of both high-side and low-side gate control are configurable individually to achieve the best trade-off between EMC performance and drive efficiency.

The module combines the following sub-modules:

- High-side gate drive unit, including control logic, an adaptive dead-time unit, slew rate control unit, level shifter and gate driver

- Low-side gate drive unit, including control logic, an adaptive dead-time unit, slew rate control unit, level shifter and gate driver

- VDS monitoring unit

- Temperature monitoring sensors

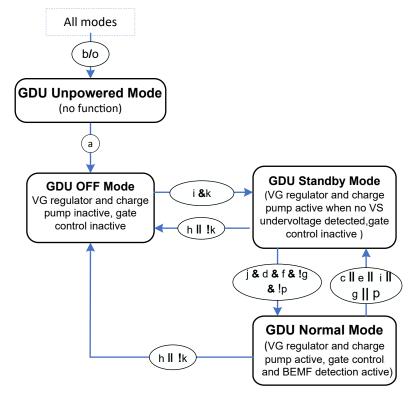

#### 5.3.2 GDU OPERATION MODES (Submit Feedback)

- **GDU OFF mode:** VG, VCP and Gate Control are deactivated.

- **GDU Standby mode:** VG and VCP are active as long as VS undervoltage has not been detected.

- **GDU Normal mode:** VG, VCP and Gate Control are active. Also, if selected, B-EMF is active. The state diagram is illustrated below.

#### Figure 5-6. GDU Operating Modes

- a: Power-on Reset

- b: Device in Power Off (V<sub>VS</sub> < V<sub>VS\_PowerOFF</sub>)

- c:  $V_{VG} < V_{VGS_{UV}_{Set}} \parallel$  ( $V_{VCP} V_{VDH}$ )  $< V_{VGS_{UV}_{Set}}$ , when VGS undervoltage monitoring is active.

- d: No VG and VCP detected

- e: V<sub>VS</sub> < V<sub>VS\_UV\_Set</sub>

- f: No VS undervoltage detected

- g: Any GDU related failure registered (overcurrent with ILIMSDEN=1 and/or short circuit event with CSDEN=1 and/or overtemperature shutdown, etc.)

- h: GDUOPM = GDU OFF mode

- i: GDUOPM = GDU Standby mode

- j: GDUOPM = GDU Normal mode and device is in Normal mode

- k: DOPM = Normal mode

- o: Device is in Deep Sleep mode

- p: VDH overvoltage & VDHOVSD = 1

#### Notes:

- VG and VCP are enabled at GDU transition from Off to Standby (default). The DSR1.GDUS flag is available if GDUOPM = Normal.

- CSA1/3 is available when DOPMCR.DOPM = Normal and CSCR.CSA1/3EN bits are activated.

- GDU = Normal mode can be written in any state of DOPM, but it will not be active if DOPM is switched in Normal mode while GDU = Normal. To activate the GDU, it is necessary to manually switch the GDU back into Standby, and then into Normal.

#### 5.3.3 GDU OPERATION MODE CONTROL REGISTERS (Submit Feedback)

The GOPMCR register is a control register. Therefore, the state of GDU will not be mirrored to this register. GDUOPM bits only define the expected state of the transceiver. In addition to setting up the GDUOPM appropriately, all conditions for entering the corresponding GDU Operation modes must be fulfilled before the mode transition occurs. GDU can also leave the expected Operation mode if the conditions to stay cannot be fulfilled.

**Register 2: GOPMCR Register - GDU Operation Mode Control Register (Address 0x03)**

| Bit           | 7 | 6 | 5 | 4 | 3 | 2   | 1           | 0   |

|---------------|---|---|---|---|---|-----|-------------|-----|

|               | — | _ | — | — | — |     | GDUOPM [2:0 | ]   |

| Read/Write    | U | U | U | U | U | R/W | R/W         | R/W |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0   | 0           | 1   |

### Bits 7:3 - Unimplemented.

Bits 2:0 - GDUOPM [2:0] Select GDU Operation mode, as shown below:

'3'b001' = GDU OFF mode

'3' b100' = GDU Standby mode

'3' b111' = GDU Normal mode

Other = Invalid mode selection

#### **Register 3: GDUCR1 Register - GDU Control Register 1 (Address** 0x05)

| Bit           | 7 6 5 4 3 2 |                 |     |     |     |     |     | 0      |

|---------------|-------------|-----------------|-----|-----|-----|-----|-----|--------|

|               |             | CCPT [5:0] CCEN |     |     |     |     |     | BEMFEN |

| Read/Write    | R/W         | R/W             | R/W | R/W | R/W | R/W | R/W | R/W    |

| Initial Value | 0           | 0               | 0   | 1   | 1   | 1   | 1   | 0      |

**Bits 7:2 - CCPT [5:0]** Cross conduction protection timer. The cross conduction protection time can be calculated as follows:  $t_{CC} = 100 \text{ ns} \times \text{N}$ , N = 0 to 63 [0x00 to 0x3F]. The role of CCPT is the prevention of shoot-through currents in the external MOSFET transistors (see CROSS CONDUCTION PROTECTION).

**Bit 1 - CCEN** Cross conduction protection enable bit. The CCEN bit enables the cross conduction protection feature. Disabling cross conduction protection leads to disabling both the cross conduction timer and adaptive dead-time generation. If CCEN is set to '0', "direct"/"complementary" Control mode is disabled (COMPEN = '0'). In this case, the MCU will generate PWM signals with the desired dead time between high side and low side.

#### Bit 0 - BEMFEN Back EMF comparator enable.

BEMFEN = '1' will activate Back EMF detection. The BEMF1, BEMF2 and BEMF3 pins are activated and signal the current ZCD state.

BEMFEN = '0' disables the Back EMF detection. The BEMFx pins are then released for OpAmp1 operation.

In case both the current sense amplifier '1' (CSA1EN = '1') and Back EMF comparator (BEMFEN = '1') are enabled, Back-EMF detection and current sense amplifier 1 will be disabled.

| Bit           | 7     | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-------|-------|-----|-----|-----|-----|-----|-----|

|               | HSOFF | LSOFF | TSV | VTO |     | EG  | BLT |     |

| Read/Write    | R/W   | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Initial Value | 0     | 0     | 0   | 1   | 0   | 0   | 0   | 1   |

#### Register 4: GDUCR2 Register - GDU Control Register 2 (Address 0x06)

**Bit 7 - HSOFF -** High-side gate driver inactive mode state. The microcontroller will set this bit to '0' if high-side gate drivers should become tri-state when GDU is in GDU Standby mode and will set the bit to '1' if high-side gate drivers should be driven low in GDU Standby mode.

**Bit 6 - LSOFF -** Low-side gate driver inactive mode state. The microcontroller will set this bit to '0' if low-side gate drivers should become tri-state when GDU is in GDU Standby mode and will set the bit to '1' if low-side gate drivers should be driven low in GDU Standby mode.

**Bits 5:4 - TSWTO -** Forces switch delay time control bits. For the definition of the delay, refer to CROSS CONDUCTION PROTECTION. Force to switch delay is set in ns, as shown below:

'2'b00'=225

'2'b01'=475

'2'b10'=975

'2'b11' = 1975

**Bits 3:0 - EGBLT -** The edge blanking time control bits. The edge blanking time can be configured as shown in Current Limitation Detection/Short Circuit Detection Time. Edge blanking time starts after the cross conduction time expires and the corresponding gate control input becomes active (NIHx = '0' or ILx = '1'). VDS monitoring is blanked out during this time.

#### Register 5: GDUCR3 Register - GDU Control Register 3 (Address 0x07)

| Bit           | 7   | 6    | 5   | 4    | 3   | 2   | 1   | 0   |

|---------------|-----|------|-----|------|-----|-----|-----|-----|

|               | ADD | OTHS | ADI | DTLS | HS  | SRC | LSS | SRC |

| Read/Write    | R/W | R/W  | R/W | R/W  | R/W | R/W | R/W | R/W |

| Initial Value | 0   | 0    | 0   | 0    | 0   | 0   | 0   | 0   |

Bits 7:6 - ADDTHS - Adaptive dead-time configuration bits (high side). Can be set as shown below:

'2'b00' = disabled

'2'b01' = 50-160 ns

'2'b10' = 150-210 ns

'2'b11' = 300-360 ns

Bits 5:4 - ADDTLS - Adaptive dead-time configuration bits (low side). Can be set as shown below:

- '2'b00' = disabled

- '2'b01' = 50-160 ns

- '2'b10' = 150-210 ns

- '2'b11' = 300-360 ns

Bits 3:2 - HSSRC - High-side slew rate control bits. Can be set as shown below ( Note 1 ):

'2'b00' = Full speed

'2'b01' = 50% of full speed

'2'b10' = 25% of full speed

'2'b11' = 12.5% of full speed

Bits 1:0 - LSSRC - Low-side slew rate control bits. Can be set as shown below ( Note 1 ):

'2'b00' = Full speed

'2'b01' = 50% of full speed

'2'b10' = 25% of full speed

'2'b11' = 12.5% of full speed

**Note 1:** Pay attention to the impact of the slew rate when handling negative voltage at phase pins.

| <b>Register 6:</b> | GDUCR4 Register - 0 | GDU Control Register | 4 (Address 0x08) |

|--------------------|---------------------|----------------------|------------------|

|                    |                     |                      |                  |

| Bit           | 7      | 6       | 5       | 4        | 3   | 2     | 1         | 0   |

|---------------|--------|---------|---------|----------|-----|-------|-----------|-----|

|               | COMPEN | VDHOVSD | UVVGSEN | UVVGSLVL |     | VGSUV | FLT [3:0] |     |

| Read/Write    | R/W    | R/W     | R/W     | R/W      | R/W | R/W   | R/W       | R/W |

| Initial Value | 0      | 1       | 1       | 1        | 1   | 0     | 0         | 0   |

**Bit 7: COMPEN -** Complementary control enable bit. The microcontroller shall set this bit to '1' if the complementary control of external MOSFETs is activated and set this bit to '0' if the external MOSFETs are controlled individually (direct) with the six gate control input signals (NIHx and ILx).

**Bit 6: VDHOVSD** - VDH overvoltage shutdown enable bit. The microcontroller shall set this bit to '1' when a VDH overvoltage event triggers a shutdown of the VG and VCP regulator (triggers transition from GDU Normal mode to GDU Standby mode). The microcontroller shall set this bit to '0' if a VDH overvoltage event will not trigger a shutdown of VG and VCP regulator.

**Bit 5: UVVGSEN -** VGS undervoltage detection enable bit. The microcontroller shall set this bit to '1' when VGS monitoring is active and set the bit to '0' when it is not. Effectively, the bit enables/ disables both VCP and VG monitoring.

**Bit 4: UVVGSLVL -** VGS/VG undervoltage detection level selection. The microcontroller shall set this bit to '1' when the higher detection level ( $V_{VGS_UV_Set_H}$ ) is used and set this bit to '0' if the lower detection level ( $V_{VGS_UV_Set_L}$ ) is used.

**Bits 3-0: VGSUVFLT [3:0] -** VGS undervoltage filter time ( $t_{VGS\_UV\_Blank}$ ). The filter time can be configured as follows: 770 ns × N, N = 1 to 16 [0x0 to 0x0F]. Filter time starts after an undervoltage event has been detected (comparator output changes to high). If VG and VCP voltage rise above the detection threshold during filter time, filter time will be reset and it will be restarted after VGS undervoltage occurs again.

| ILIMFLT [3:0], SCFLT [3:0], EGBLT [3:0] | Blanking/Filter time (ns), typical (±5%) |

|-----------------------------------------|------------------------------------------|

| 4′b0000                                 | 0                                        |

| 4'b0001                                 | 250                                      |

| 4'b0010                                 | 500                                      |

| 4'b0011                                 | 750                                      |

| 4'b0100                                 | 1000                                     |

| 4'b0101                                 | 1250                                     |

| 4'b0110                                 | 1500                                     |

| 4'b0111                                 | 1750                                     |

Table 5-1. Current Limitation Detection/Short Circuit Detection Time

| continued                               |                                          |

|-----------------------------------------|------------------------------------------|

| ILIMFLT [3:0], SCFLT [3:0], EGBLT [3:0] | Blanking/Filter time (ns), typical (±5%) |

| 4'b1000                                 | 2000                                     |

| 4'b1001                                 | 2500                                     |

| 4'b1010                                 | 3000                                     |

| 4'b1011                                 | 3500                                     |

| 4'b1100                                 | 4000                                     |

| 4'b1101                                 | 5000                                     |

| 4'b1110                                 | 6000                                     |

| 4'b1111                                 | 8000                                     |

## 5.4 Charge Pumps (CP1 and CP2) (Submit Feedback)

The ATA6847 supports 100% duty cycle operation by using two charge pumps. CP1 supplies the low-side gate drivers. Its input voltage is generated from the battery supply pin VDH. CP2 supplies the high-side gate drivers. It is generated out of the charge pump output of VG. Each charge pump (CP1 and CP2) charges from its input supply via an external flying capacitor into an external storage capacitor. VG is the output pin of CP1, whereas VCP is the output pin of CP2.

After the GDU transition into Standby mode, CP1 is turned on if VS < VCP\_START and turned off if VS > VCP\_STOP. In case VS > VCP\_STOP, a 12V LDO has been included to limit VG voltage to 12V.

The second charge pump, CP2, provides the high-side gate driver biasing, being active when the GDU is in Standby or Normal mode.

The module monitors the output voltages and delivers the undervoltage detection event, notified in the SIR3 Register, VCPUV and VGUV bits.

CP2 output may serve as a control output pin for a reverse voltage polarity protection MOSFET, see Figure 1-1.

## 5.5 Low Dropout Voltage Regulator (VDD1) (Submit Feedback)

Depending on the product, the VDD1 pin has a nominal voltage output level of 5V or 3.3V, see Product Family.

The voltage regulator needs an external capacitor to compensate and smooth any disturbances. It is recommended to use an MLC capacitor connected in parallel to a 100 nF ceramic capacitor.

During a short circuit at VDD1, the output current is limited to  $I_{VDD1_fb_sc}$ . In case the LDO temperature exceeds the  $T_{OT_sdwn}$  threshold, the VDD1 output will be switched off. As soon as the junction temperature decreases below  $T_{OT_release}$ , the regulator will be switched on again.

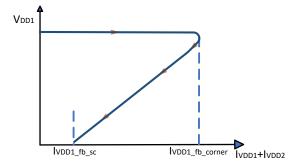

Exceeding the maximum sum load current of VDD1 and VDD2  $[I_{VDD1} + I_{VDD2}]$  beyond the output current foldback corner threshold  $I_{VDD1_{fbcorner}}$  leads to a current limitation of LDO1. The current is getting limited down to the foldback short circuit limit  $I_{VDD1_{fb_{sc}}}$  with decreasing load resistance. This feature reduces the dissipated power in overloading or short circuit conditions, and prevents LDO damage. This principle is illustrated in the Principle Foldback Current Waveform (Figure 5-7).

Figure 5-7. Principle Foldback Current Waveform

A proper connection between the exposed pad and a heat sink is recommended for sufficient power dissipation.

If the supply voltage (VS) is below the nominal output voltage of VDD1, the foldback current limitation is disabled and replaced with the standard current limitation (I<sub>VDD1lim</sub>).

## 5.6 Low Dropout Voltage Regulator (VDD2) (Submit Feedback)

ATA6847-5050, and ATA6847-5033 provide a voltage regulator with an output voltage of  $V_{VDD2}$  = 3.3V. The VDD2 is powered from the 5V output of the VDD1 regulator. The maximum output current is limited to  $I_{VDD2lim}$ .

The ATA6847-3333 provides an inhibit output pin, **INH**. The purpose of the INH pin is to control external devices, such as external voltage regulators.

When inactive, the INH pin output level is high ohmic. When active, the INH voltage is on VS level.

## 5.7 Current Sense Amplifier (CSA) (Submit Feedback)

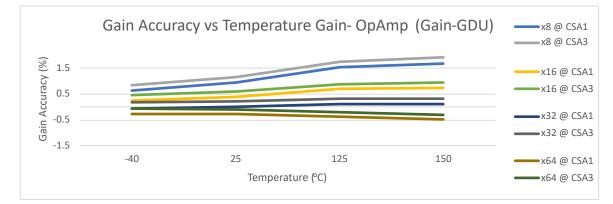

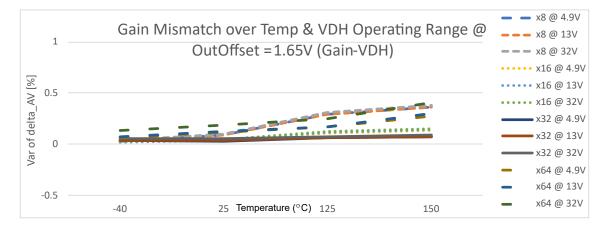

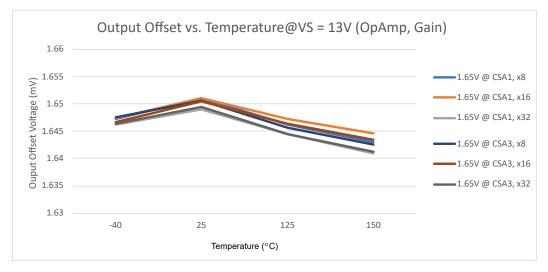

The ATA6847 provides two fully integrated operational amplifiers, tailored for measuring power stage currents by sensing currents across the shunt resistors. The gain and output offset voltage are configurable by setting the corresponding bits in the CSCR register via the SPI interface.

Optionally, the CSAs can be disabled.

The CSA output voltage range is adapted to the VIO voltage.

The CSA3 output voltage can be monitored with the ILim module, see OUTPUT CURRENT LIMITATION.

| Bit           | 7             | 6 | 5      | 4 | 3      | 2   | 1    | 0   |

|---------------|---------------|---|--------|---|--------|-----|------|-----|

|               | <b>CSA3EN</b> | — | CSA1EN | — | OFFSET |     | GAIN |     |

| Read/Write    | R/W           | U | R/W    | U | R/W    | R/W | R/W  | R/W |

| Initial Value | 1             | 0 | 1      | 0 | 0      | 0   | 0    | 0   |

#### Register 7: CSCR Register - Current Sensing OpAmp Control Register (Address 0x0C)

**Bit 7 - CSA3EN** Enable current sense amplifier 3. The CSA is enabled when the device is in Standby/ Normal mode and the corresponding enable bit is set to '1'. All current sense amplifiers will need a maximum of 20 µs to settle their output voltage after the enable signal is set to '1'.

#### Bit 6 - Unimplemented.

**Bit 5 - CSA1EN** Enable current sense amplifier 1. The CSA is enabled when the device is in Standby/Normal mode and the corresponding enable bit is set to '1'. If current sense amplifier 1 (CSA1EN = '1') is enabled and BEMFEN (in GDUCR1) is enabled, then both Back EMF detection and current sense amplifier 1 will be disabled. All current sense amplifiers will need a maximum of 20 µs to settle their output voltage after the enable bit is set to '1'.

#### Bit 4 - Unimplemented.

Bits 3:2 - OFFSET Current sensing amplifier output offset set point.

'2'b00'=V<sub>VIO</sub>/16

'2' b01'= V<sub>VIO</sub>/8

'2'b10'=V<sub>VIO</sub>/4

'2' b11'= V<sub>VIO</sub>/2

**Bits 1:0** - **GAIN** Current sensing OpAmp gain set point.

'2'b00'=8

'2'b01'=16

'2'b10'= 32

'2'b11'=64

## 5.8 Back EMF Sampler and Back EMF Detection (Submit Feedback)

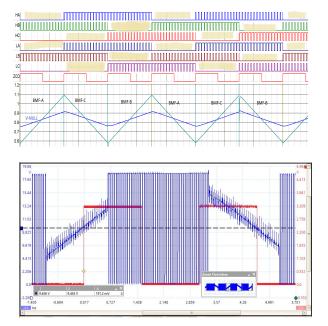

The ATA6847 comes with a fully-integrated B-EMF detection module, which converts the motor phase voltages into digital feedback signals. The B-EMF unit includes a resistor network and three high-speed, Zero-Cross Detection comparators (ZCD). The scaled phase signals VSHx are compared with the emulated motor neutral point voltage for estimating the virtual zero crossing. The ZCD comparator outputs provide three digital feedback signals via the BEMF1, BEMF2 and BEMF3 pins.

B-EMF detection is activated using the GDUCR1 Register.

## 5.9 Motor Line Diagnostics (Submit Feedback)

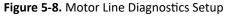

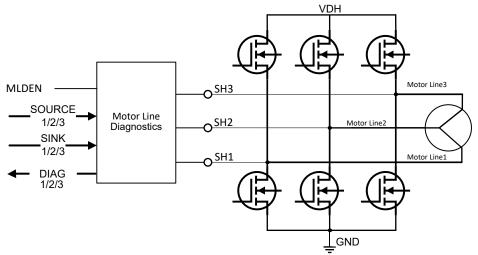

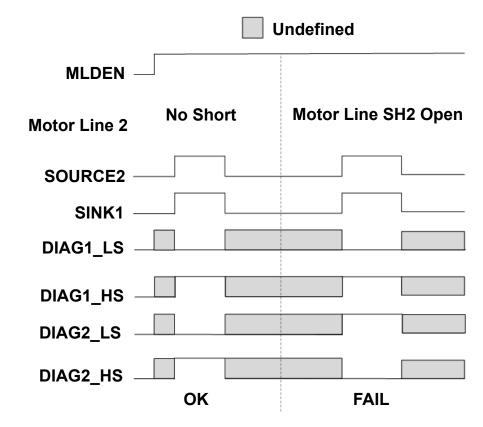

While the motor is not in operation, the B-EMF module can be used for motor line diagnostics. GDU must be in GDU Standby mode. Motor line (SHx) short to GND, short to VDH and open load can be evaluated, see Motor Line Diagnostics Setup. The MLDCR register is used to control the motor line diagnostics. As soon as the diagnostics are activated, the outputs of the diagnostics comparators will continuously update the MLDRR register. Enabling the motor line diagnostics disables the NIHX and ILX PWM input pins.

Motor Line Short to GND and Supply Test and Motor Line Open Connection Test show the motor clamp short to GND, short to V<sub>BUS</sub> or open load failure detection.

Figure 5-9. Motor Line Short to GND and Short to VDH Test

Figure 5-10. Motor Line Open Load Test.

A sufficient delay time is required before evaluating the MLDRR register, accounting for parasitic board and power MOSFET capacitances, and limited current capability of the diagnostics current sources.

Motor line diagnostics can be activated when VS is within the valid operating range, the ATA6847 is in Normal mode and the GDU is in GDU Standby mode.

## 5.9.1 MOTOR LINE DIAGNOSTICS CONTROL REGISTERS (Submit Feedback)

#### Register 8: MLDCR Register – Motor Line Diagnostics Control Register (Address 0x0E)

| Bit           | 7 | 6       | 5     | 4       | 3     | 2       | 1     | 0     |

|---------------|---|---------|-------|---------|-------|---------|-------|-------|

|               | — | SOURCE3 | SINK3 | SOURCE2 | SINK2 | SOURCE1 | SINK1 | MLDEN |

| Read/Write    | U | R/W     | R/W   | R/W     | R/W   | R/W     | R/W   | R/W   |

| Initial Value | 0 | 0       | 0     | 0       | 0     | 0       | 0     | 0     |

The motor line diagnostics circuitry is controlled by the MLDCR register.

#### Bit 7 - Unimplemented.

**Bit 6 - SOURCE3** Enables source current source 3 if SOURCE3 = '1' and disables source current Source 3 if SOURCE3 = '0'.

**Bit 5 - SINK3** Enables sink current source 3 if SINK3 = '1' and disables sink current Source 3 if SINK3 = '0'.

**Bit 4 - SOURCE2** Enables source current source 2 if SOURCE2 = '1' and disables source current Source 2 if SOURCE2 = '0'.

**Bit 3 - SINK2** Enables sink current source 2 if SINK2 = '1' and disables sink current Source 2 if SINK2 = '0'.

**Bit 2 - SOURCE1** Enables source current source 1 if SOURCE1 = '1' and disables source current Source 1 if SOURCE1 = '0'.

**Bit 1 - SINK1** Enables sink current source 1 if SINK1 = '1' and disables sink current Source 1 if SINK1 = '0'.

**Bit 0 - MLDEN** Enables (MLDEN = '1', default) and disable (MLDEN = '0') motor-line diagnostics only in GDU Standby mode.

#### Register 9: MLDRR Register - Motor Line Diagnostics Results Register (Address 0x12)

The motor-line diagnostics results can be read from the MLDRR register. The register is accessed via SPI. The results are available after each change in the MLDCR register.

| Bit           | 7 | 6 | 5        | 4        | 3        | 2        | 1        | 0        |

|---------------|---|---|----------|----------|----------|----------|----------|----------|

|               | _ | — | DIAG3_HS | DIAG3_LS | DIAG2_HS | DIAG2_LS | DIAG1_HS | DIAG1_LS |

| Read/Write    | U | U | R        | R        | R        | R        | R        | R        |

| Initial Value | 0 | 0 | 0        | 0        | 0        | 0        | 0        | 0        |

Bits 7:6 - Unimplemented.

**Bits 5:0 - DIAGx\_HS, DIAGx\_LS** Diagnostics results register bits. Interpret the results as described in Motor Line Short to GND and Short to VDH Test and Motor Line Open Load Test.

### 5.10 Wake-up Sources (Submit Feedback)

#### 5.10.1 LOCAL WAKE-UP VIA WAKE PIN (Submit Feedback)

The ATA6847 provides a high-voltage input pin (WAKE) with the purpose of waking up the device.

The local wake up is active after enabling it via the LOCWUE bit.

A local wake-up request is detected when a falling edge has been detected on the WAKE pin and the logic level on the pin has been stable for at least  $t_{local_wu}$ . The event will be signaled via the NIRQ pin in all Device Operation Modes (DOPM).

In Deep Sleep mode the local wake up is always active, independent of the LOCWUE bit value, as all SPI registers are cleared upon entering Deep Sleep mode. However, Deep Sleep mode cannot be entered without LOCWUE = '1'.

#### 5.10.2 WAKE-UP CONTROL REGISTER (Submit Feedback)

#### Register 11: WUCR Register - Wake-up Control Register (Address 0x04)

| Bit           | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

|---------------|---|---|---|---|---|---|---|--------|

|               | — | — | — | — | — | — | — | LOCWUE |

| Read/Write    | U | U | U | U | U | U | U | R/W    |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1      |

#### Bits 7:1 - Unimplemented.

**Bit 0 - LOCWUE** Local wake-up enable. Setting this bit to '1' will enable the local wake up via the WAKE pin, while setting the bit to '0' will disable it.

#### 5.11 Watchdog (Submit Feedback)

The watchdog is used to monitor the proper function of the microcontroller and to trigger a Reset, if the microcontroller stops serving the watchdog due to a lock-up in the software or other malfunction. The NRES pin is pulled to Low when a watchdog Reset event is detected.

#### 5.11.1 WATCHDOG BEHAVIOR DURING POWER-ON AND AFTER MCU RESET (Submit Feedback)

For a safe start-up, the microcontroller must issue a watchdog trigger command, followed by the configuration of the watchdog via the WDCR registers. Following this, the device enters Device Standby mode. As soon as the ATA6847 enters Standby mode, the watchdog starts with a long open window (t<sub>LW</sub>). **Within this long open window, the watchdog must be triggered.** If the watchdog trigger is missing, the watchdog will generate a Reset via the NRES pin. In case of a correct first trigger within the long open window time, the watchdog starts its normal operation.

The watchdog cannot be disabled and configured in the following cases:

- After the power-on of the device and before it receives the first trigger in long open window mode.

- In all other cases when the watchdog is enabled and the device moves from MCU Reset mode to Standby mode, before the watchdog receives the first trigger.

If the WDLW bit from the Watchdog Control Register 1 is set to '1' (default value), the watchdog timer will always be reset when the Reset pulse time expires and starts the long open window after the device enters Standby mode. Otherwise, the watchdog will continue with its normal operation immediately, and skip the long window.

### 5.11.2 WATCHDOG REGISTERS AND FEATURES (Submit Feedback)

The built-in watchdog is activated by default and starts after powering on the device. The watchdog can be reconfigured or disabled only after power-on AND the first trigger.

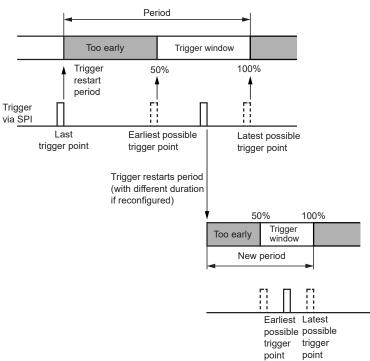

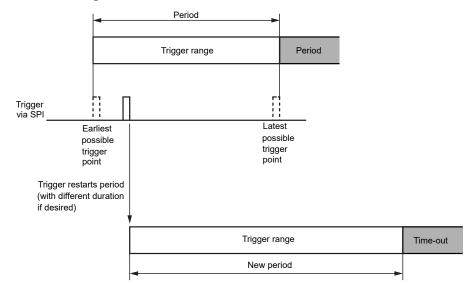

The watchdog supports two operating modes:

• Window mode

In Window mode, a watchdog trigger event within the watchdog trigger window resets the watchdog timer.

The Window Mode is only available in Normal mode.

Time-out mode

In Time-out mode, the watchdog can be triggered any time within the trigger range by a watchdog trigger.

Figure 5-11. Window Watchdog in Window Mode

Figure 5-12. Window Watchdog in Time-out Mode

In order to avoid unwanted configuration of the watchdog, the ATA6847 only allows configuration of the watchdog (write access to WDCR1 and WDCR2 registers) when the device is in Standby mode.

Every write access to the WDCR1 and WDCR2 registers via SPI will reset the Watchdog Timer and immediately apply the changes.

If Window mode is selected (WDC = 100), the watchdog will remain in (or switch to) Time-out mode until the device enters Normal mode (Window mode is only supported when the device is in Normal mode).

Any attempt to configure the watchdog (write access to WDCR1 Register and WDCR2 Register) while the device is not in Standby mode will trigger a Reset of the microcontroller, and the device will set the ILLCON bit in the Watchdog Status register, WDSR (illegal watchdog configuration).

The ATA6847 watchdog supports eight watchdog periods. The watchdog period is programmable via the Watchdog Period bits (WWDP) in the Watchdog Control Register 2 (WDCR2). The selected period is valid for both Window and Time-out modes. The default watchdog period value is 128 ms.

A watchdog trigger event (an SPI write access to the WDTRIG register with the pattern (01010101) resets the Watchdog Timer. The Watchdog Reset pulse width is configured via the WRPL bits in the WDCR2 Register.

| Register 12: WDCR1 | <b>Register – Watchdo</b> | g Configuration Register | 1 (Address 0x21)                      |

|--------------------|---------------------------|--------------------------|---------------------------------------|

| -0                 | -0                        |                          | · · · · · · · · · · · · · · · · · · · |

| Bit           | 7   | 6   | 5   | 4   | 3   | 2 | 1    | 0 |

|---------------|-----|-----|-----|-----|-----|---|------|---|

|               | WDC |     |     | WD  | PRE | — | WDLW | — |

| Read/Write    | R/W | R/W | R/W | R/W | R/W | U | R/W  | U |

| Initial Value | 0   | 1   | 0   | 0   | 0   | 0 | 1    | 0 |

#### Bits 7:5 - WDC Watchdog mode control:

- 001 = OFF mode

- 010 = Time-out mode (default)

- 100 = Window mode

### Bits 4:3 - WDPRE Watchdog period control:

- 00 = Watchdog prescale factor 1 (default)

- 01 = Watchdog prescale factor 1.5

- 10 = Watchdog prescale factor 2.5

- 11 = Watchdog prescale factor 3.5

### Bit 2 - Unimplemented.

#### Bit 1 - WDLW

If the bit is set to '1': After LH is released, the WDT is reset, and the first trigger window is long ( $t_{LW}$ ).

If the bit is set to '0': After LH is released, the WDT is reset, and the first trigger window is standard (as configured by WDPRE and WWDP).

### Bit 0 - Unimplemented.

#### **Register 13: WDCR2 Register - Watchdog Configuration Register 2 (Address 0x22)**

| Bit           | 7   | 6   | 5   | 4   | 3    | 2   | 1   | 0   |  |

|---------------|-----|-----|-----|-----|------|-----|-----|-----|--|

|               |     | WV  | VDP |     | WRPL |     |     |     |  |

| Read/Write    | R/W | R/W | R/W | R/W | R/W  | R/W | R/W | R/W |  |

| Initial Value | 0   | 1   | 0   | 0   | 0    | 0   | 0   | 1   |  |

**Bits 7:4 - WWDP** Watchdog period configuration (ms, prescale factor = 1, ± 20%):

1000 = 8

0001 = 16

- 0010 = 32

- 0011 = 64

- 0100 = 128 (default)

- 1101 = 256

- 1110 = 1024

- 0111 = 4096

Bits 3:0 - WRPL Watchdog reset pulse length (ms, ± 20%):

- 1000 = 1.25

- 0001 = 4.3 (default)

- 0010 = 11.25

- 1011 = 22.5

- 0100 = 45

- 1101 = 67.5

- 1110 = 112.5

0111 = 170

The watchdog is an important safety mechanism that must be configured correctly. Two mechanisms are provided to prevent watchdog parameters from being changed by mistake.

- All configuration bitfields in the registers WDC, WWDP and WRPL have a hamming distance of at least two for valid states.

- Reconfiguration protection: The configuration is only possible in Standby mode.

Having a hamming distance of at least two for all valid states for the control bitfields, WDC, WWDP and WRPL, ensures that a single bit error cannot cause the watchdog to be configured incorrectly (at least two bits must be flipped to reconfigure WDC, WWDP or WRPL). If an attempt is made to write an invalid code to the WDCR1 register or WDCR2 register, the SPI write to the WDCRx register is ignored and the CACC bit in the Watchdog Status register is set.

| Bit           | 7   | 6    | 5      | 4     | 3   | 2     | 1     | 0 |

|---------------|-----|------|--------|-------|-----|-------|-------|---|

|               | OFF | CACC | ILLCON | TRIGS | OF  | OFSLP | ETRIG | — |

| Read/Write    | R   | R/W  | R/W    | R     | R/W | R/W   | R/W   | U |

| Initial Value | 0   | 0    | 0      | 0     | 0   | 0     | 0     | 0 |

#### Register 14: WDSR Register - Watchdog Status Register (Address 0x23)

Bit 7 - OFF Value is '1' when Watchdog is OFF.

**Bit 6 - CACC** Corrupted write access to the watchdog configuration registers.

**Bit 5 - ILLCON** An attempt is made to reconfigure the watchdog control register while the device is not in Standby mode.

**Bit 4 - TRIGS** The device sets this bit to '1' if the Window mode watchdog is in the first half of the window and sets it to '0' if the Window mode watchdog is in the second half of the window. If the WD is not in Window mode, this bit will always be set to '0'.

Bit 3 - OF Watchdog overflow (Time-out/Window mode in Standby or Normal mode).

Bit 2 - OFSLP Watchdog overflow in Sleep mode (Time-out mode).

Bit 1 - ETRIG Watchdog triggered too early (Window mode).

#### Bit 0 - Unimplemented.

Writing '1' to the corresponding bit of the watchdog status register will reset the bit.

**A microcontroller Reset is triggered immediately** in response to an illegal watchdog configuration (configuration of the watchdog in Normal or Sleep mode), an incorrect Watchdog Trigger event in Window mode (watchdog overflow or triggered too early) or when the watchdog overflows in Time-out mode. If a Reset is triggered by the window watchdog the Window Watchdog Reset Event register will be set. The device will enter the μC Reset mode and enter Standby mode after the Reset is finished.

If a Reset is triggered by the watchdog, the respective Reset event register will be set. The device will enter the MCU Reset mode, followed by Standby mode, after the Reset takes place.

If there is a corrupted write access to the watchdog configuration registers and/or an illegal configuration of watchdog control register occurred when the watchdog is in OFF mode, the corresponding status register bit will be set.

If the fault register bits (CACC, ILLCON, OF, OFSLP and ETRIG bits) are not reset to zero before enabling the window watchdog, an MCU Reset will be triggered immediately after enabling the watchdog.

| Bit           | 7   | 7 6 5 4 3 2 1 0 |     |     |     |     |     |     |  |

|---------------|-----|-----------------|-----|-----|-----|-----|-----|-----|--|

|               |     | WDTRIG          |     |     |     |     |     |     |  |

| Read/Write    | R/W | R/W             | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Initial Value | 0   | 0               | 0   | 0   | 0   | 0   | 0   | 0   |  |

A watchdog trigger is an 8-bit wide SPI pattern written to the WDTRIG register.

A valid watchdog trigger event resets the watchdog timer. The only valid trigger pattern is **0b01010101**.

## 5.12 Serial Peripheral Interface (SPI) (Submit Feedback)

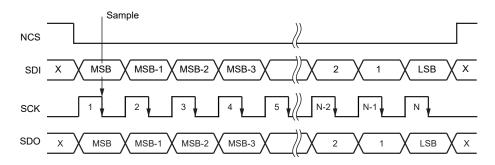

The SPI is used to communicate with a host microcontroller. The ATA6847 is configured and operated using SPI transfers. SPI transfers are disabled in Sleep and Deep Sleep modes.

The SPI allows full-duplex data transfer. Status information is returned when new control data are shifted in. The interface also offers read-only access, allowing registers to be read back without changing the register content.

Bit sampling is performed on the falling edge of the clock pin (SCK) and data is shifted in/out on the rising edge (see the figure below).

Figure 5-13. SPI Timing Protocol.

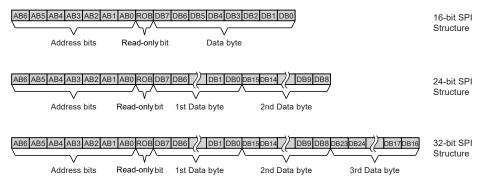

The SPI data is stored in dedicated 8-bit registers, and each register is assigned a unique 7-bit address. Sixteen bits must be transmitted to the device for a single register write operation.

The **first byte** contain the 7-bit address along with a 'read/write' bit (the LSB). The read/write bit must be '0' to indicate a write operation. If this bit is '1', a read operation is performed and any data after this bit is ignored.

The **second byte** contain the data meant to be written to the register. The contents of the addressed register(s) are returned via the SDO pin, while a read or write operation is performed.

For faster programming, 16, 24 and 32-bit read and write operations are supported. For 24 and 32-bit operations, the register address is automatically incremented: once for a 24-bit operation and twice for a 32-bit operation.

Attempting to write to a non-existing register is not prohibited. If the available address space is exceeded during a write operation, the data beyond the valid address range is ignored without generating an SPI failure event.

Figure 5-14. SPI Transfer Data Structure

The number of transmitted SPI bits is monitored during SPI transfers. If the number of bits is not equal to 16, 24 or 32, the transfer is aborted.

An SPI failure event is captured (SPIF = '1', see SIR1 Register) if the SPI failure detection is enabled (SPIFECE = '1') and at least one of the following SPI failures is detected:

- SPI clock count error: only 16, 24 and 32-bit commands are valid for both read and write operation

- Illegal DOPM code (see DOPMCR Register)

- · Attempted write access to locked register

If more than 32 bits are clocked in on the SDI pin during a read and write operation, the data stream on the SDI pin is looped back on the SDO pin from bit 33 onwards.

| Address | Name    | Bit 7         | Bit 6                    | Bit 5     | Bit 4     | Bit 3      | Bit 2      | Bit 1        | Bit 0    |

|---------|---------|---------------|--------------------------|-----------|-----------|------------|------------|--------------|----------|

| 0x01    | DOPMCR  | RSTLVL        | VDDIOOVSD                | _         | _         | —          |            | DOPM [2:0]   |          |

| 0x03    | GOPMCR  |               |                          |           |           | _          | (          | GDUOPM [2:0] |          |

| 0x04    | WUCR    |               |                          |           |           | _          |            |              | LOCWUE   |

| 0x05    | GDUCR1  |               |                          | CCP       | T [5:0]   |            |            | CCEN         | BEMFEN   |

| 0x06    | GDUCR2  | HSOFF         | LSOFF                    | TSV       | ло        |            | EGBLT      |              |          |

| 0x07    | GDUCR3  | ADI           | ADDTHS ADD               |           |           | HSS        | SRC        | LSS          | SRC      |

| 0x08    | GDUCR4  | COMPEN        | VDHOVSD                  | UVVGSEN   | UVVGSLVL  |            | VGSUVFI    | T [3:0]      |          |

| 0x09    | ILIMCR  | ILIMEN        |                          | ILIN      | //FLT     |            | ILIMSDEN   | _            | _        |

| 0x0A    | ILIMTH  |               | DAC6                     | DAC5      | DAC4      | DAC3       | DAC2       | DAC1         | DAC0     |

| 0x0B    | SCPCR   | SCSDEN        | SCFLT [3:0] SCTHSEL [2:0 |           |           |            |            |              |          |

| 0x0C    | CSCR    | <b>CSA3EN</b> |                          | CSA1EN    |           | OFF        | SET        | GAIN         |          |

| 0x0E    | MLDCR   |               | SOURCE3                  | SINK3     | SOURCE2   | SINK2      | SOURCE1    | SINK1        | MLDEN    |

| 0x0F    | RWPCR   |               |                          |           |           | _          | _          | _            | WP0      |

| 0x10    | DSR1    | SMTS          | VDD2OTPWS                | VDD10TPWS | GDUOTPWS  | _          | GDUS       | _            | —        |

| 0x11    | DSR2    |               | VDD2OVS                  | VDD10VS   | VDD2UVS   | VDD1UVHS   | VDD1UVLS   | VGUVS        | VCPUVS   |

| 0x12    | MLDRR   |               |                          | DIAG3_HS  | DIAG3_LS  | DIAG2_HS   | DIAG2_LS   | DIAG1_HS     | DIAG1_LS |

| 0x13    | SIR1    | VSUPF         | WAKE                     | SYS       | ILIM      | LDOF       | OVTF       | VDSSC        | VGSUV    |

| 0x14    | SIR2    |               | VDD2OV                   | VDD10V    | VDD2UV    | VDD1UVH    | VDD1UVL    | _            | _        |

| 0x15    | SIR3    | VGUV          | VCPUV                    | SCHS3     | SCHS2     | SCHS1      | SCLS3      | SCLS2        | SCLS1    |

| 0x16    | SIR4    | OVTSDVDD2     | OVTSDVDD1                | OVTSDGDU  |           | OVTPWVDD2  | OVTPWVDD1  | OVTPWGDU     | _        |

| 0x17    | SIR5    | VDHOV         | VSUV                     | LOCWU     |           | SPIF       | PWRON      | SYSERR       | OSCF     |

| 0x18    | SIECER1 | GSCECE        | VDHOVECE                 | ILIMECE   |           | _          | VSUVECE    | SPIFECE      | OVTPWECE |

| 0x19    | SIECER2 |               | _                        |           | VDD2UVECE | VDD1UVHECE | VDD1UVLECE | VDD2OVECE    | VDD10VEC |

| 0x20    | WDTRIG  | WDTRIG        |                          |           |           |            |            |              |          |

| 0x21    | WDCR1   |               | WDC                      |           | WI        | OPRE       | _          | WDLW         |          |

| 0x22    | WDCR2   |               | WW                       | VDP       | 1         | WRPL       |            |              |          |

| 0x23    | WDSR    | OFF           | CACC                     | ILLCON    | TRIGS     | OF         | OFSLP      | ETRIG        | _        |

#### 5.12.1 Register Summary (Submit Feedback)

## 5.13 Diagnostics and Protections (Submit Feedback)

#### 5.13.1 SLEEP MODE PROTECTION (Submit Feedback)

All interrupt bits must be cleared before the device transitions into Sleep or Deep Sleep mode. Otherwise, the device will switch to Standby mode in response to a Go-to-Sleep or Go-to-Deep-Sleep command (if DOPM = Sleep or Deep Sleep, see <u>Device Operating Modes</u>).

#### 5.13.2 VS SUPPLY UNDERVOLTAGE PROTECTION (Submit Feedback)

If  $V_{VS} < V_{VS\_UV\_Set}$  has been detected, the device will:

- Switch the GDU to GDU Standby mode, if it was in GDU Normal mode.

- Set the status register bit, VSUV (see SIR5 Register).

- In case the event capture enable register bit (VSUVECE) is set to '1' (see SIECER1 Register), an NIRQ interrupt will be generated.

#### 5.13.3 VDH SUPPLY OVERVOLTAGE PROTECTION (Submit Feedback)

The VDH supply overvoltage protection is active when setting the VDHOVSD bit to '1'. If a  $V_{VDH} > V_{VDH_{OV_{Set}}}$  event occurs, the device will switch the GDU to GDU Standby mode (when in GDU Normal mode) and the Charge Pump will be deactivated (as long as the overvoltage condition is valid).

If the VDHOVSD bit is set to '0', the device will not react to the overvoltage event, the GDU will remain in Normal mode and the Charge Pump will keep operating. Only an NIRQ interrupt event will be generated, presuming the VDHOVECE bit is set to '1'.

The device will set the status register bit (VDHOV, see the SIR1 Register), presuming the VDHOVECE bit is set to '1', and an NIRQ interrupt event will be generated. Set the VDHOVECE bit to '0' to disable VDH overvoltage event capture.

VDH overvoltage monitoring is only active in Normal mode.

### 5.13.4 VDD1/VDD2 UNDERVOLTAGE AND OVERVOLTAGE PROTECTION (Submit Feedback)

The ATA6847 provides various levels of VDD1 and VDD2 undervoltage monitoring. The feature is enabled by the RSTLVL bit.

If an undervoltage event has been detected at the VDD1 or VDD2 pin, the following will happen:

- The status bit VDDxUV (x = 1 or 2) and/or VDD1UVL will be set.

- The NIRQ pin will be asserted if the corresponding interrupt event capture enable register bit is set (see SIR2 Register).

- The device will switch to MCU Reset mode, causing the GDU to switch into GDU Standby mode.

If an overvoltage event has been detected on the microcontroller supply for longer than the overvoltage detection debouncing time,  $t_{VDD1_OV\_deb}$  or  $t_{VDD2\_OV\_deb}$ , the device is forced into Sleep mode, given that VDDIOOVSD is set to '1'. A number of actions are taken while switching into Sleep mode:

- All previously captured system interrupt events are cleared before the device switches to Sleep mode.

- Local wake up is enabled.

- Status bit SMTS is set to '1' (See DSR1 Register).

- The status register bit VDDIOOVSD (see #DOPMCR) will be set, presuming the VDD1OVECE or VDD2OVECE bit is set to '1'.

- The NIRQ pin will be asserted. Setting the VDD1OVECE and/or VDD2OVECE bits to '0' will disable VDD1 and/or VDD2 overvoltage event capture, respectively.

VDD1 and VDD2 overvoltage monitoring are active in Normal mode.

#### 5.13.5 VGS MONITORING AND EXTERNAL MOSFET PROTECTION (Submit Feedback)

The ATA6847 monitors the gate supply voltage for each of the low and high-side external MOSFETs. The VG pin buffers the low-side gate supply voltage, whereas the VCP pin buffers the high-side gate supply voltage. The device provides two undervoltage detection thresholds, valid for both low and high-side gate supply voltages. The used threshold can be selected via the UVVGSLVL bit (see GDUCR4 Register).

A gate supply undervoltage condition for the low-side gate drivers occurs if  $V_{VG} - V_{GND} < V_{VGS UV Set x}$ .

A gate supply undervoltage condition for the high-side gate drivers occurs if  $V_{VCP} - V_{VDH} < V_{VGS UV Set x}$ .

VDH ~ VGS\_UV\_Set\_

In both cases:

- The GDU will be switched into GDU Standby mode.

- The gate control inputs NIHx and ILx are ignored.

- The according status register bit(s) VGUV and/or VCPUV will be set (see the SIR3 register).

- The NIRQ pin will be asserted.

The external MOSFET gate source (VGS) undervoltage monitoring is active as soon as the VG and VCP regulators are enabled, and the UVVGSEN bit is set (see GDUCR4 Register). Both the VG and VCP regulators start operating when the transition to GDU Normal mode occurs. Transitioning to GDU Standby mode is not possible unless VG and VCP are within the valid range. The status of both VG and VCP output regulators can be seen in the DSR2 register (see DSR2 Register).

The VGS undervoltage event capturing is active in GDU Standby mode and GDU Normal mode. In GDU Standby mode, the VGS undervoltage event is filtered with  $t_{VGS\_U\_V\_Blank\_ADOO}$ , ensuring the VG and VCP regulators ramp up properly. The delay filter is activated only once, when both VG and VCP regulators are activated. In case the VG and/or VCP regulator/s are not able to reach the requested voltage level (undervoltage level) within the filter time, NIRQ will be asserted.

| UVVGSEN | VGS Monitoring                                                                                              |

|---------|-------------------------------------------------------------------------------------------------------------|

| 0       | VGS monitoring deactivated – GDU state machine ignores all VGS UV events.                                   |

| 1       | VGS monitoring activated – GDU switches into GDU Normal mode only if no VGS undervoltage has been detected. |

#### 5.13.6 OUTPUT CURRENT LIMITATION (Submit Feedback)

The ATA6847 provides an output current limitation feature for monitoring the external power MOSFETs sum current. The output of OpAmp3 is internally connected to a comparator. The limitation voltage is set in the ILIMTH Register. The limitation feature is active in Device Normal mode, as soon as it is activated via the ILIMEN bit, see the ILIMCR Register below.

On a current limitation event, different reactions can be configured, as following:

- If the ILIMSDEN bit is set to '1' (latched behavior), the interrupt event is latched and the GDU will switch into GDU Standby mode.

- If the ILIMSDEN bit is set to '0' (unlatched behavior), GDU Normal mode is maintained, but the six GHx and GLx gate driver outputs are deactivated until ILIM condition is resolved.

The interrupt register bit "ILIM" (see SIR1 Register) will be set, and an interrupt will be generated under the following conditions:

- Unlatched fault handling (ILIMEN = '1' AND ILIMSDEN = '0') and ILIMECE bit is set to '1'; or

- Latched fault handling (ILIMEN = '1' AND ILIMSDEN = '1')

The interrupt register bit "ILIM" will be cleared under the following conditions:

- When any of the six gate driver outputs become active while the unlatched fault handling is enabled; or

- When the ILIM bit is set to `1' via SPI.

The ATA6847 will ignore any current limitation event if the ILIMEN bit is set to '0'.

The current limitation detection delay filter can be configured using ILIMFLT in the ILIMCR Register. The following table explains the ILIM control bits in more detail:

| ILIMEN | ILIMECE | ILIMSDEN | Device Behavior                                                                                                                                        |

|--------|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0/1     | 0        | No action on current limitation events                                                                                                                 |

| 0      | 0/1     | 1        | No action on current limitation events                                                                                                                 |

| 1      | 1       | 0        | Interrupt generation, unlatched automatic fault handling, interrupt event delay is inactive as soon as the interrupt bit is reset by the gate control. |

| 1      | 0       | 0        | No interrupt, unlatched automatic fault handling                                                                                                       |

| 1      | 0/1     | 1        | Interrupt generation and latched fault handling                                                                                                        |

#### **Register 16: ILIMCR Register - Current Limitation Control Register (Address 0x09)**

| Bit           | 7      | 6   | 5       | 4   | 3   | 2        | 1 | 0 |

|---------------|--------|-----|---------|-----|-----|----------|---|---|

|               | ILIMEN |     | ILIMFLT |     |     | ILIMSDEN | — | — |

| Read/Write    | R/W    | R/W | R/W     | R/W | R/W | R/W      | U | U |

| Initial Value | 1      | 1   | 0       | 0   | 0   | 1        | 0 | 0 |

**Bit 7 - ILIMEN** Current limitation enable bit. Set to '1' activates the current limitation, whereas set to '0' deactivates it.

**Bits 6:3 - ILIMFLT** Current limitation filter time bits. The filter times are configured according to Current Limitation Detection/Short Circuit Detection Time. The filter time starts after the current limitation threshold has been reached. If the sensed current drops below the detection threshold during the filter time, the filter time will be reset and restarted.

**Bit 2 - ILIMSDEN** Current limitation shutdown enable bit. If set to '1', it will switch to GDU Standby mode and disable all gate drive outputs when a current limitation event has been detected, whereas if set to '0', the GDU stays in Normal mode. In the latter case, the unlatched automatic fault handling is activated.

#### Bits 1:0 - Unimplemented.

Register 17: ILIMTH Register - Current Limitation Threshold Register (Address 0x0A)

| Bit           | 7 | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------------|---|------|------|------|------|------|------|------|

|               | — | DAC6 | DAC5 | DAC4 | DAC3 | DAC2 | DAC1 | DAC0 |

| Read/Write    | U | R/W  |

| Initial Value | 0 | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

### Bit 7 - Unimplemented.

**Bits 6:0 - DACx** Current limitation threshold DAC input.

Formula to calculate the current threshold through the external power MOSFETs:

$$V_{ILIM\_TH} = \frac{V_{VIO}}{128} \sum_{x=0}^{6} DAC_x \times 2^x$$

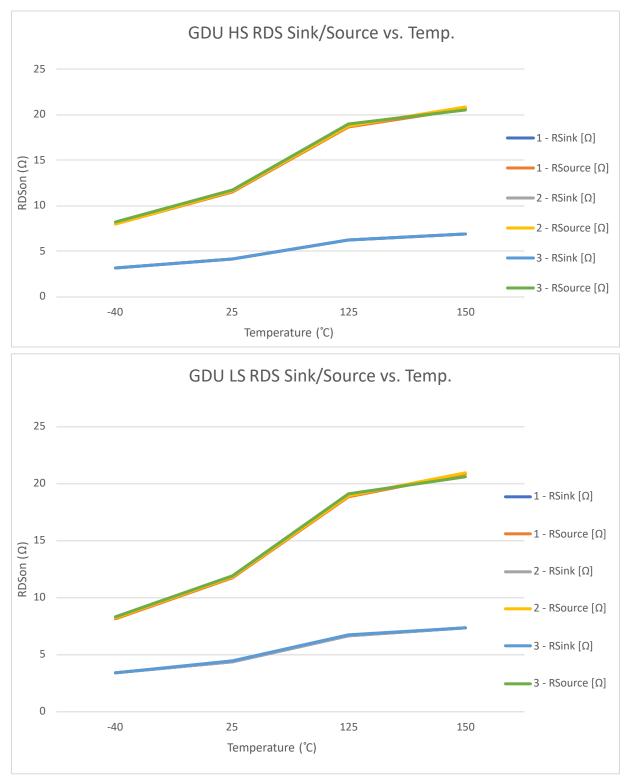

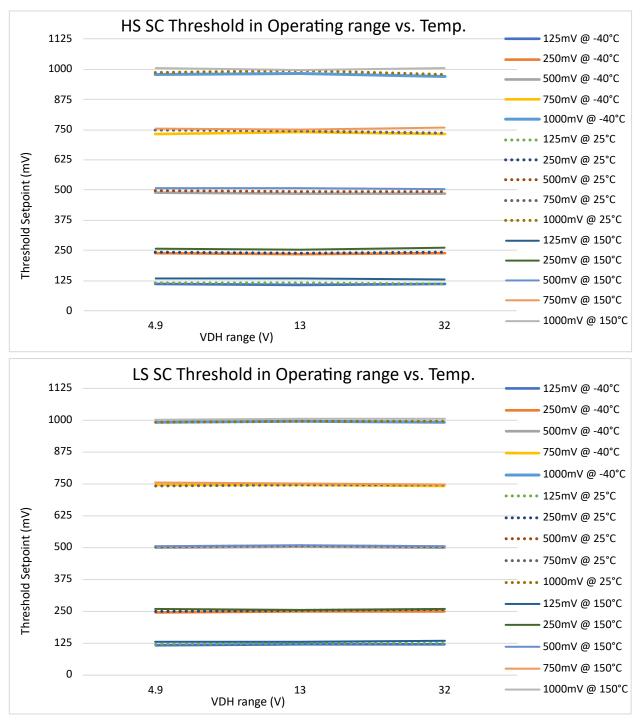

## 5.13.7 VDS DRAIN-SOURCE VOLTAGE MONITORING AND POWER STAGE SHORT CIRCUIT

## PROTECTION (Submit Feedback)