# PIC32MZ W1 and WFI32 Family

# PIC32MZ W1 MCU and WFI32 Module with Wi-Fi<sup>®</sup> and Hardware-Based Security Accelerator Data Sheet

### INTRODUCTION

The PIC32MZ W1 Family of devices are general purpose, low-cost, 32-bit Microcontroller (MCU) with the Wi-Fi<sup>®</sup> and network connectivity, hardware-based security accelerator, transceiver and Power Management Unit (PMU). It also supports interface to an External Front-End Module.

The PIC32MZ W1 SoC Family has the following variants:

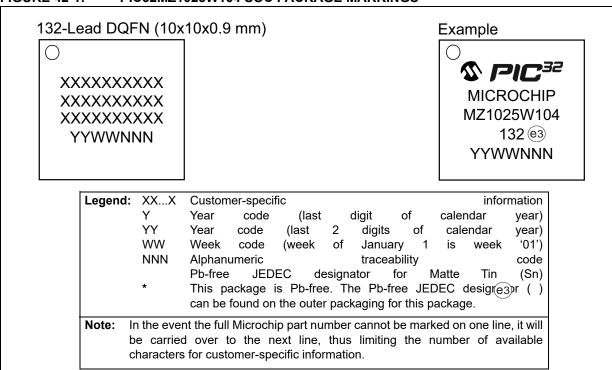

- PIC32MZ1025W104132

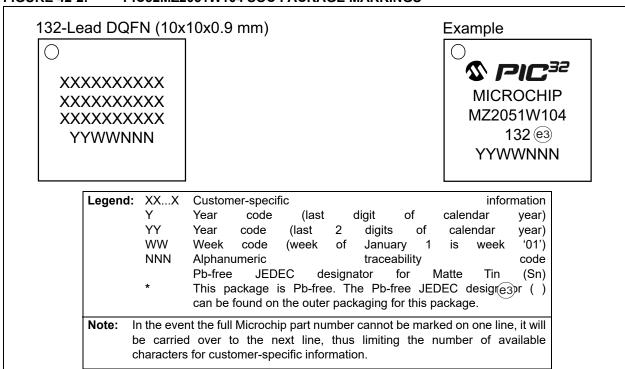

- PIC32MZ2051W104132

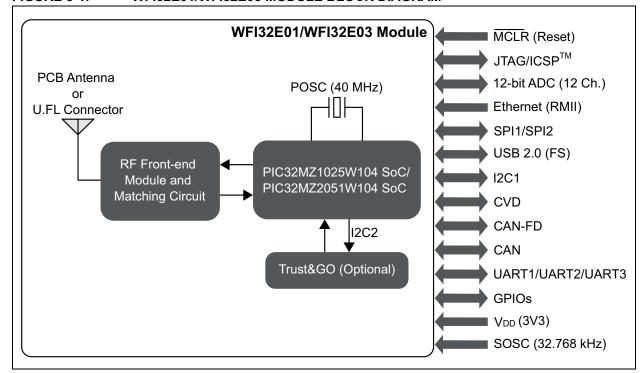

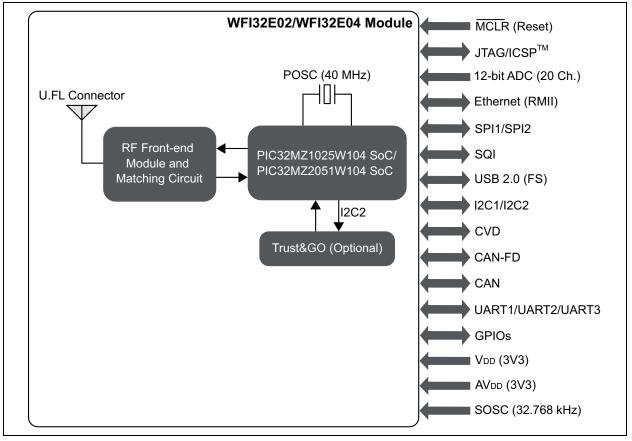

The WFI32 is a fully RF certified wireless Module that contains the PIC32MZ W1 SoC and an integrated Front-end Module (FEM). The WFI32 Module has the following variants:

- WFI32E01

- WFI32E02

- WFI32E03

- WFI32E04

Note:

The WFI32E01 and WFI32E02 Modules feature the PIC32MZ1025W104132 SoC, while the WFI32E03 and WFI32E04 Modules feature the PIC32MZ2051W104132 SoC.

The WFI32 Module is available with following antenna options:

- PCB Antenna (WFI32E01PC/WFI32E01PE/WFI32E03PC/ WFI32E03PE)

- U.FL Connector (WFI32E01UC/WFI32E01UE/ WFI32E02UC/WFI32E02UE/WFI32E03UC/WFI32E03UE/ WFI32E04UC/WFI32E04UE) for External Antenna

The PIC32MZ W1 Family supports rich set of standard PIC32 peripherals, such as Wi-Fi, Ethernet MAC, USB, CAN, CAN-FD, SPI, I<sup>2</sup>C, SQI, UART, CVD, ADC and JTAG.

TCP/IP based connectivity protocols along with SSL support enables a low-cost, low complexity system to obtain full-featured Internet connectivity and reliable information exchange.

# PIC32MZ W1 FAMILY FEATURES

The following section lists the PIC32MZ W1 related features.

### **Wireless Interfaces**

- · PHY:

- IEEE® 802.11 b/g/n WLAN link

- Single spatial stream of 20 MHz channel bandwidth

- External FEM support for Power Amplifier (PA), Low Noise Amplifier (LNA), Transmitter/Receiver (TX/RX) switch

- 2.4 GHz (2400 ~ 2483.5 MHz) ISM band

- MAC:

- Infrastructure BSS STA mode

- Soft-AP mode functionality

- Active and passive scanning

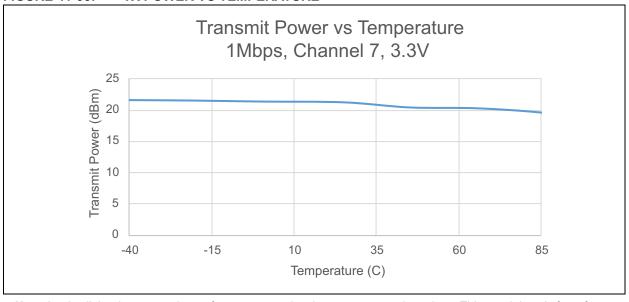

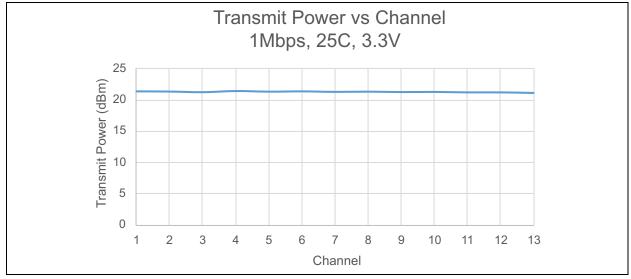

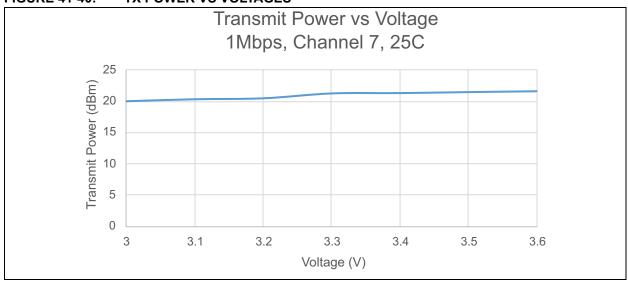

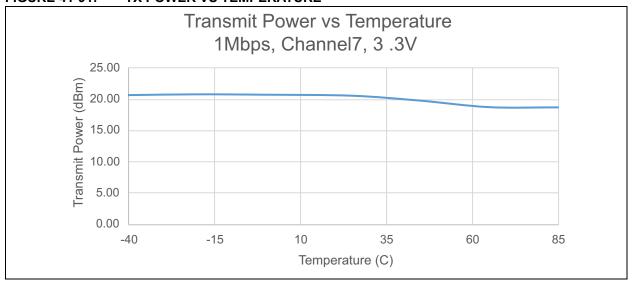

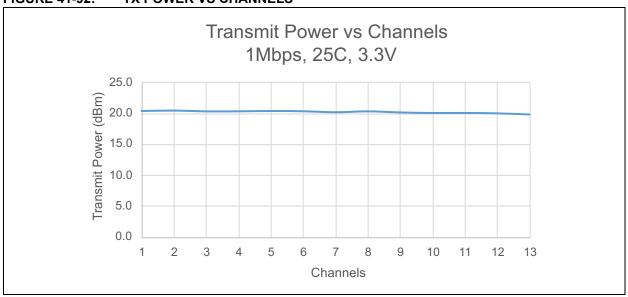

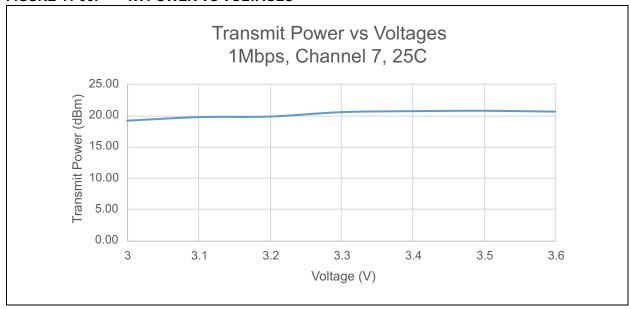

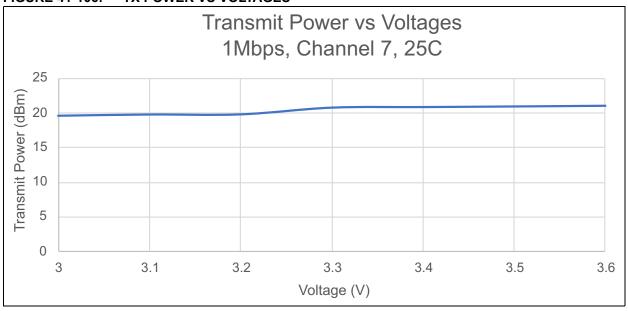

- Transmit power control support over temperature and voltage

- · Security:

- WPA3 personal (SAE and PMF-802.11w)

- WPA2 personal, with options for WPA compatibility and PMF

- WEP

- · Harmony Networking:

- Out-of-box support for MPLAB<sup>®</sup> Harmony v3 TCP/IP Stack

- TLS v1.2 with symmetric/asymmetric crypto acceleration

- · Wi-Fi Power Save Modes:

- Wireless Sleep mode (WSM)

- Wireless Deep Sleep mode (WDS)

- · Wi-Fi Time-stamping Support

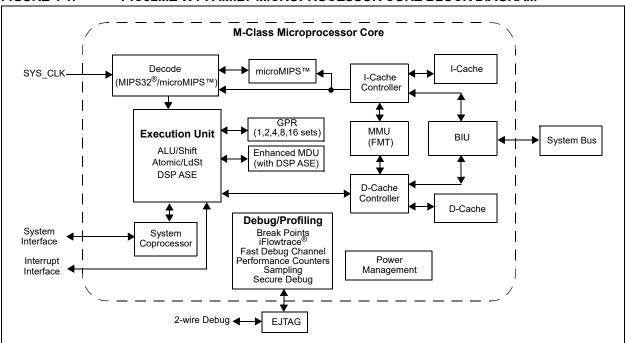

# 200 MHz, MIPS32® M-Class Microprocessor Core

- 16 KB I-Cache, 16 KB D-Cache

- Fixed Mapping Translation (FMT) based MMU for Optimum Embedded OS Execution

- microMIPS™ Mode for Up to 35% Smaller Code Size

- · DSP-enhanced Core:

- Four 64-bit accumulators

- Single-cycle MAC, saturating and fractional math

- · Code-Efficient (C and Assembly) Architecture

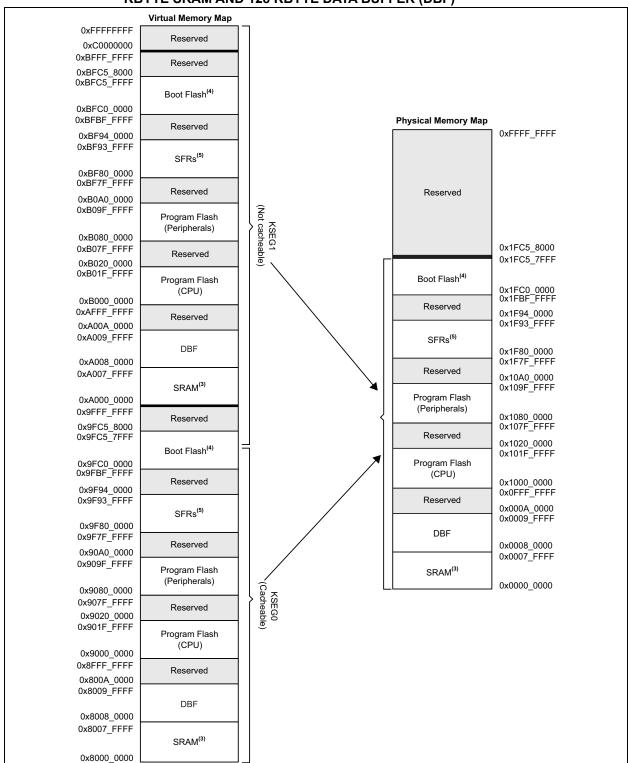

# **On-Chip Flash and SRAM**

- PIC32MZ1025W104:

- 1 MB Flash Program Memory

- 64 KB Boot Program Flash

- 256 KB SRAM (Program and Data)

- 64 KB Data Buffer (DBF)

- Dedicated Buffer for Peripherals

- PIC32MZ2051W104:

- 2 MB Flash Program Memory

- 128 KB Boot Program Flash

- 512 KB SRAM (Program and Data)

- 128 KB Data Buffer (DBF)

- Dedicated Buffer for Peripherals

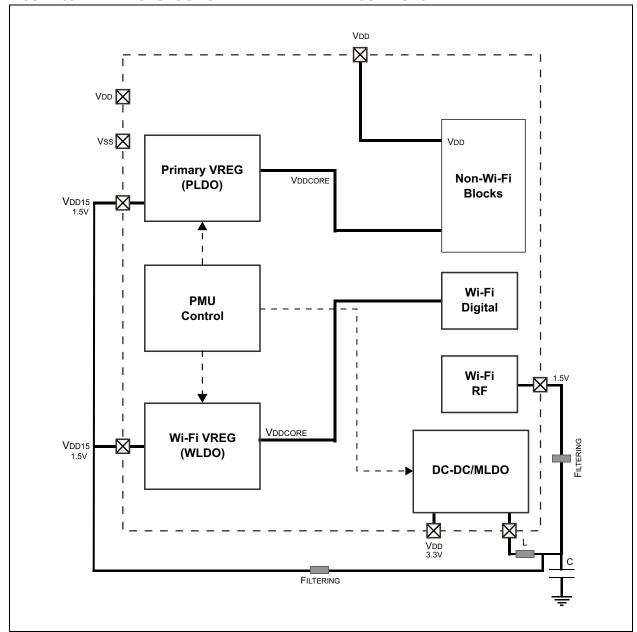

# **Power Management and System Recovery**

- Low-Power Modes (Dream, Sleep, Deep Sleep and Extreme Deep Sleep)

- 8 KB Context SRAM for Context Storage Under Low Power Modes

- · Deep Sleep Mode

- 32 Semaphore registers (32-bit wide) for context storage

- Current consumption: 1.9 µA (typical)

- PIC32MZ W1 SoC Utilizes a 32-bit Semaphore Register for Context Storage, with the Following Current Consumption Values in the Extreme Deep Sleep Mode:

- PIC32MZ1025W104132: 0.71 μA (typical)

- PIC32MZ2051W104132: 1.11 μA (typical)

- Integrated Power-on Reset (POR), Brown-out Reset (BOR), Zero-power BOR (ZPBOR) and Programmable Low Voltage Detect (PLVD)

# PIC32MZ W1 and WFI32 Family

- · Secondary Oscillator and Fail Safe Clock

- Fast Power-up and Brown-out Recovery

#### Security

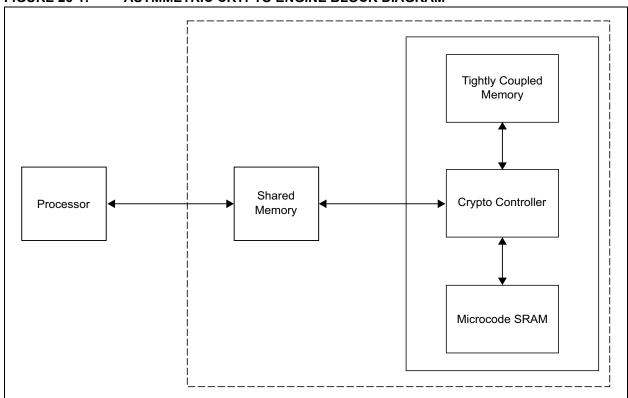

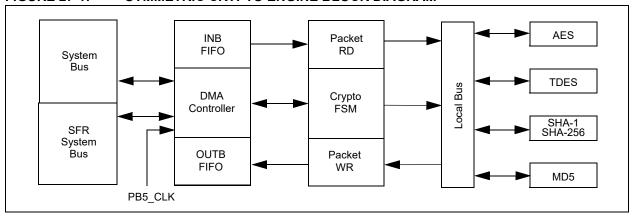

- Hardware Accelerated Security Modes (with Built-in DMA Support)

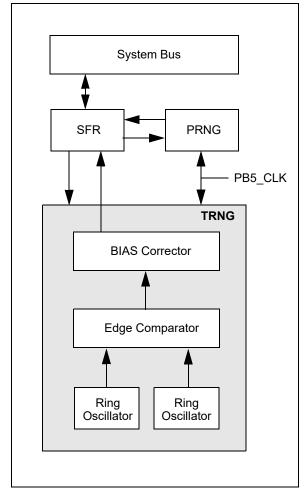

- Crypto Engine with True Random Number Generator (TRNG) for Data Encryption/Decryption and Authentication (AES, 3DES, SHA, MD5 and HMAC)

- · AES Modes:

- Electronic Codebook (ECB)

- Cipher Block Chaining (CBC)

- Counter Mode (CTR)

- Cipher Feedback Mode (CFB)

- Output Feedback Mode (OFB)

- Galois/Counter Mode (GCM)

- Hardware Accelerated Public Key Cryptography with Support for:

- 16-DSP multipliers configuration

- 256-bit ECC/ECDH/ECDSA/Curve25519

- 256-bit Ed25519

- 512-bit ECC/ECDH/ECDSA generation

#### **Clock Management**

- 40 MHz Primary Oscillator (POSC)

- 32.768 kHz Secondary Oscillator (SOSC)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Fail-Safe Clock Monitor (FSCM)

- · On-chip Clock Sources:

- 8 MHz Fast RC (FRC) oscillator

- 32.768 kHz Low-Power RC (LPRC) oscillator

- · Programmable PLLs and Oscillator Clock Sources

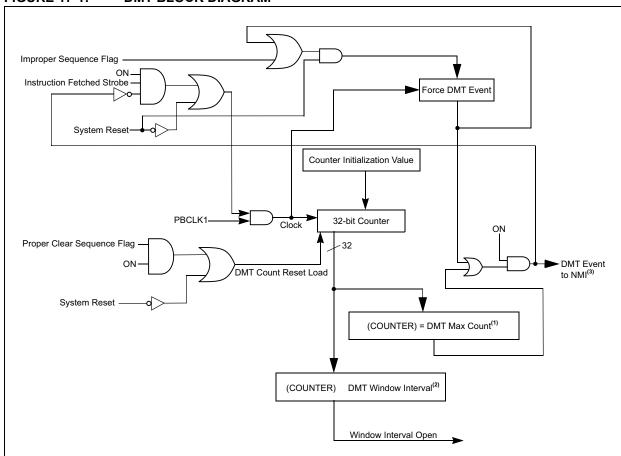

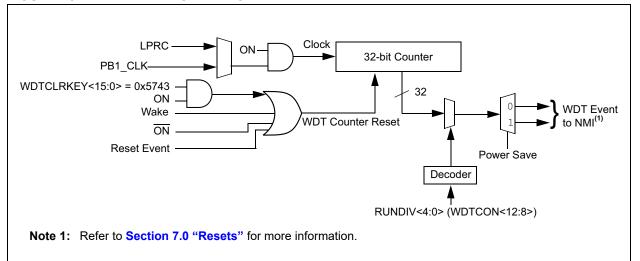

- Independent Watchdog Timer (WDT), Deadman Timer (DMT) and Independent Deep Sleep Watchdog Timer

- · Fast Wake-up and Start-up

- · Support for Precise Reference Clocks to External Devices

### **Direct Memory Access (DMA)**

- · Eight Channels with Automatic Data Size Detection

- Programmable 32-Bit Cyclic Redundancy Check (CRC)

# **Advanced Analog**

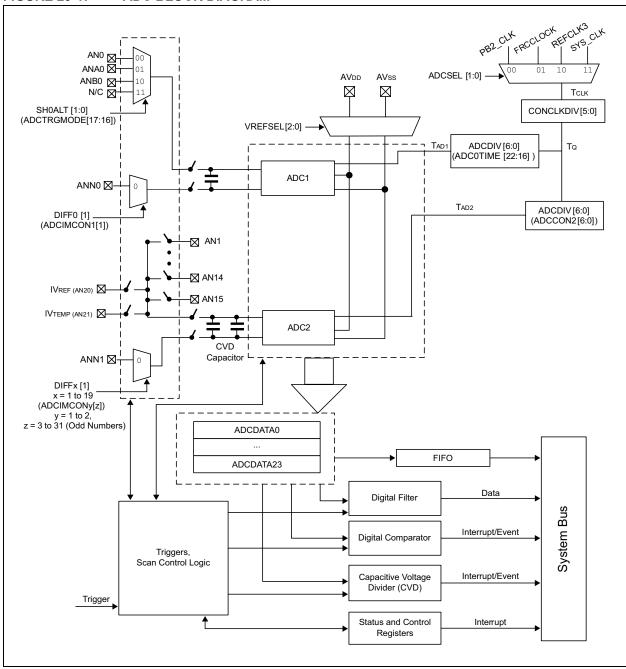

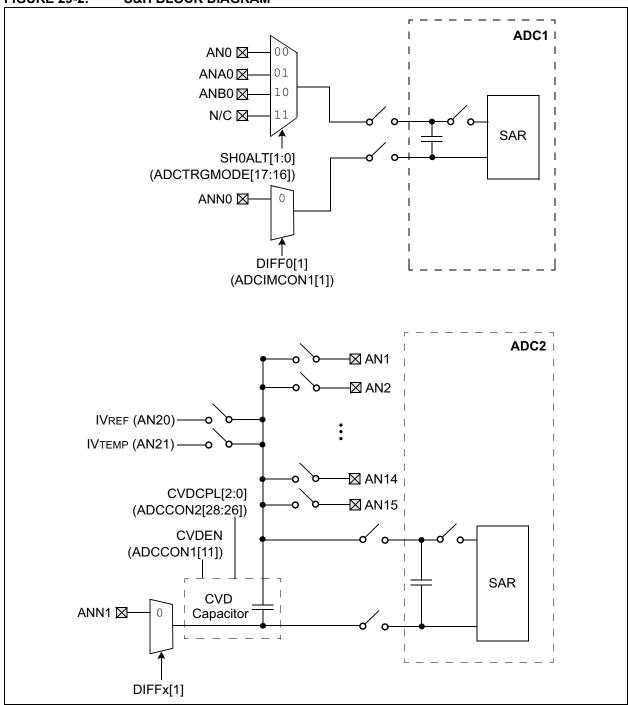

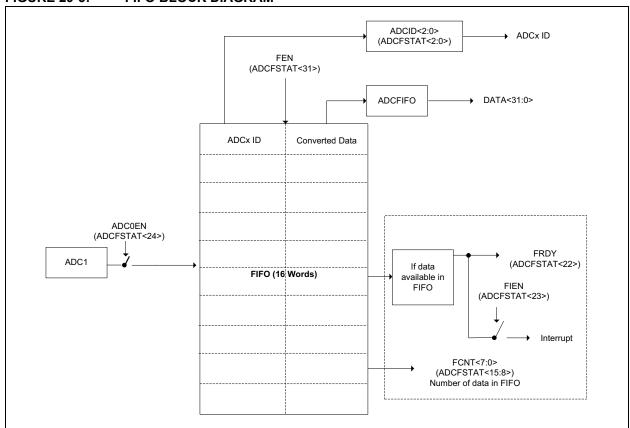

- 12-Bit ADC Module:

- 2 MSPS with two Sample and Hold (S&H) circuits (one dedicated and one shared)

- Up to 20 analog input channels

- Sleep and Idle mode operations

- Multiple trigger sources

- Two digital comparators and two digital filters

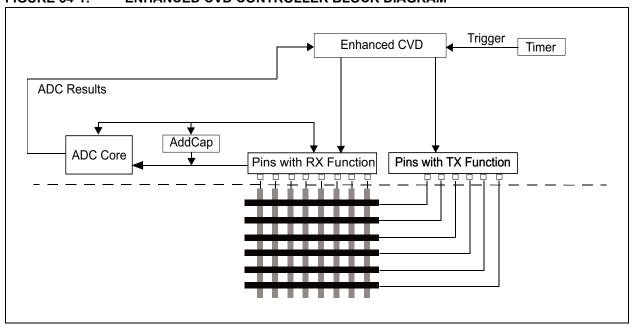

- Supports self capacitance touch interface with a maximum of 18 touch buttons and one driven shield

# **Communication Interfaces**

face and Dedicated DMA:

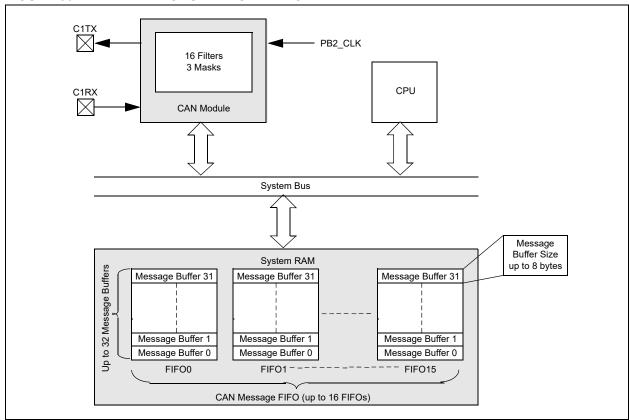

- Up to Two CAN Modules (CAN and CAN-FD)

- 2.0B Active with DeviceNet™ addressing support

- Up to Three UART Modules (Speed Up to 10 Mbps):

- Supports RS-232, RS-485, LIN 2.1 and IrDA Protocols

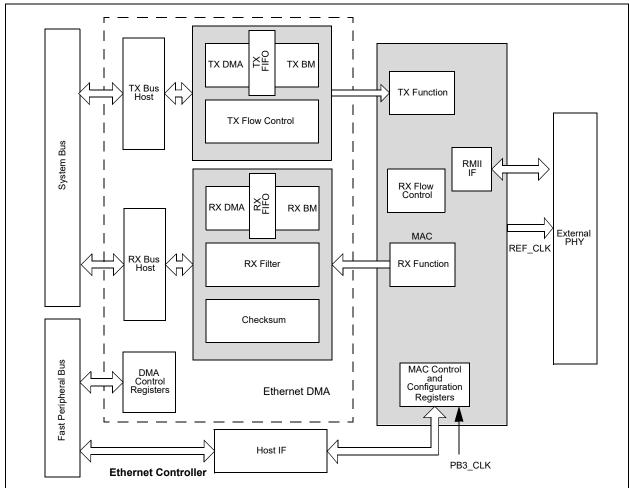

One Ethernet MAC Module (10/100 Mbps) with RMII Inter-

- IEEE 1588 Precision Time Protocol (PTP)

- Time synchronization support between Wi-Fi and Ethernet

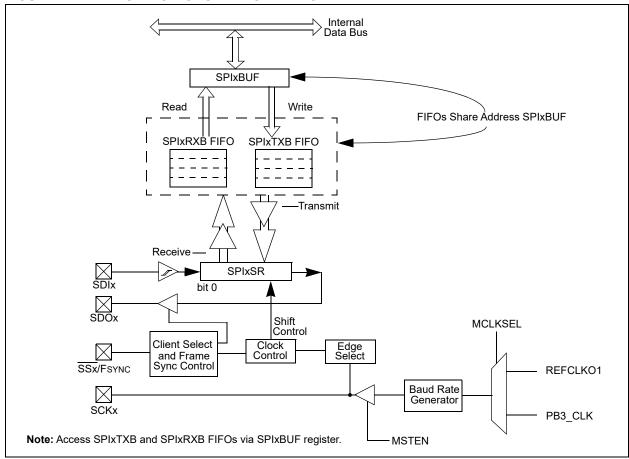

- Up to Two SPI (Four-Wire) Modules with Speed Up to 40 MHz

- · SQI Configurable as an Additional SPI Module

- One Full-Speed USB 2.0 Host and Device Interface with Dedicated DMA

- Two I<sup>2</sup>C (Up to 1M Baud) with SMBus Support

# **Timers/Output Compare/Input Capture**

- Seven 16-bit or Up to Three 32-Bit Timers/Counters

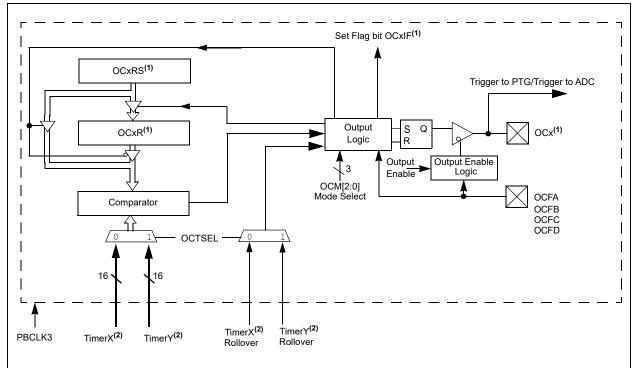

- · Four Output Compare (OC) Modules

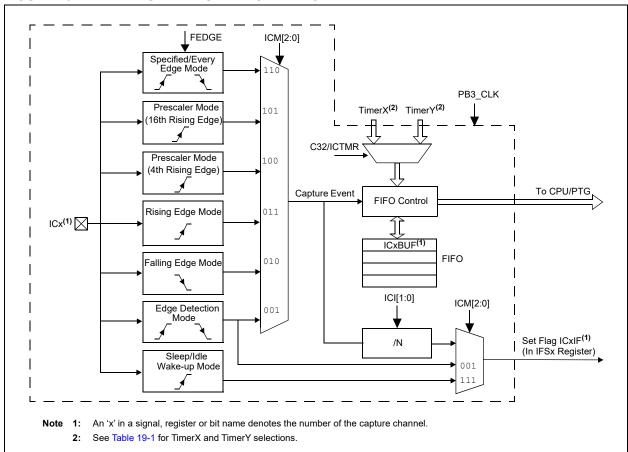

- · Four Input Capture (IC) Modules

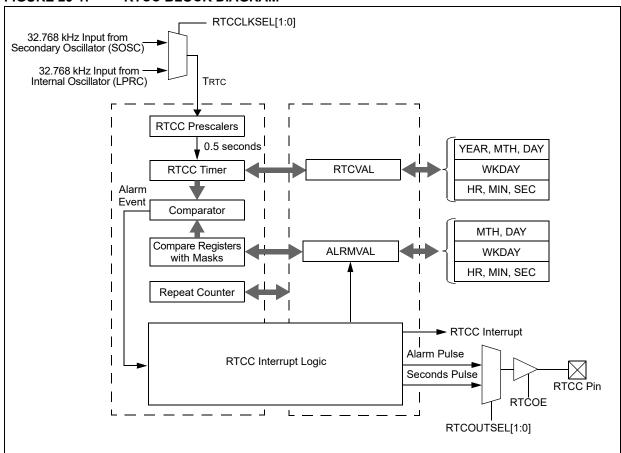

- Low-Power Precision Real-Time Clock and Calendar (RTCC)

# Input/Output

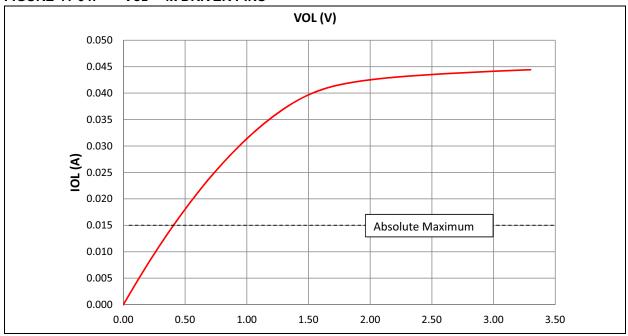

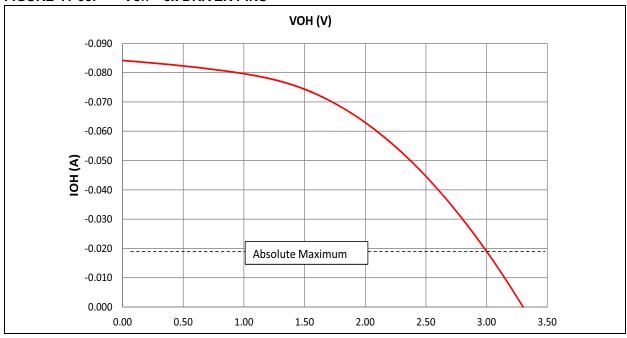

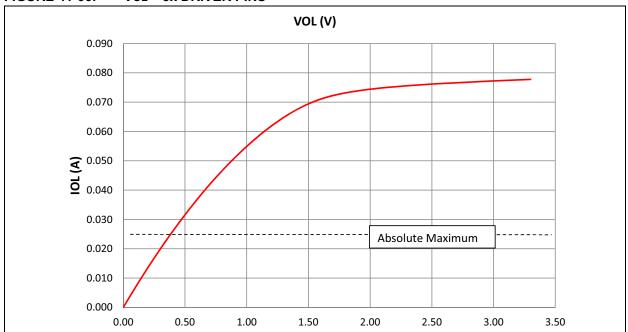

- High Current Source/Sink (Up to 25 mA) on All I/O Pins

- Configurable Open-Drain, Pull-up, Pull-Down and Slew Rate Controls

- · External Interrupts on All I/O Pins

- Peripheral Pin Select (PPS) to Enable Function Remap

- · Up to 62 GPIO Pins

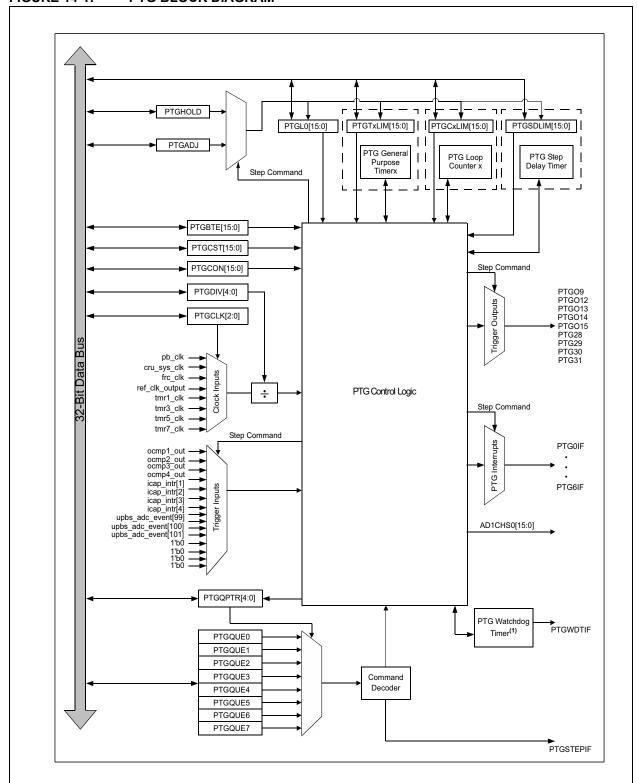

# **Peripheral Trigger Generator (PTG)**

PTG with 8-Bit User Command for Scheduling Complex Sequences

# **Qualification and Class B Support**

· Class B Safety Library, IEC 60730

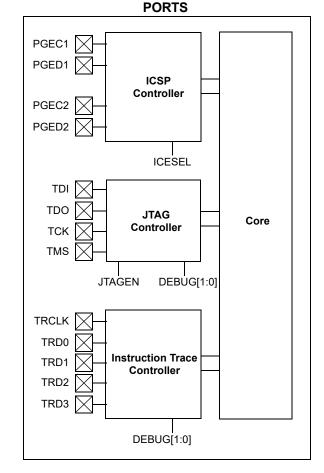

# **Debugger Development Support**

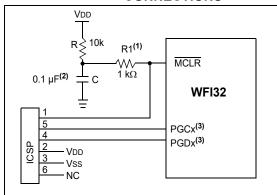

- · In-Circuit and In-Application Programming

- 4-Wire MIPS<sup>®</sup> Enhanced JTAG Interface

- Unlimited Software, 8 Instruction and 4 Data Complex Hardware Breakpoints

- IEEE 1149.2-Compatible (JTAG) Boundary Scan

- · iFlowtrace Functionality Support:

- Off-chip Buffering of iFlowTrace Messages

# **Software and Tools Support**

- C/C++ Compiler with Native DSP/Fractional

- MPLAB<sup>®</sup> Harmony Integrated Software Framework:

- TCP/IP, USB, Graphics and mTouch™ Middleware

- MFi. Android™

- RTOS Kernels: Express Logic ThreadX, FreeRTOS™, OPENRTOS<sup>®</sup>, Micriµm<sup>®</sup> µC/OS™ and SEGGER embOS<sup>®</sup>

- Supports Over-the-Air (OTA) Firmware Update Modes

# **Package and Operating Conditions**

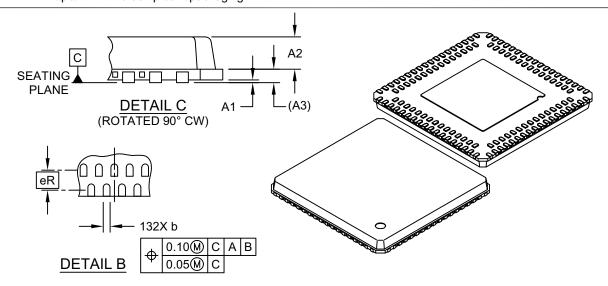

- · Package:

- 132-pin DQFN Dual Row

- Size 10 mm x 10 mm x 0.9 mm

- · Operating Conditions:

- 2.97V to 3.63V, -40°C to +85°C, DC to 200 MHz

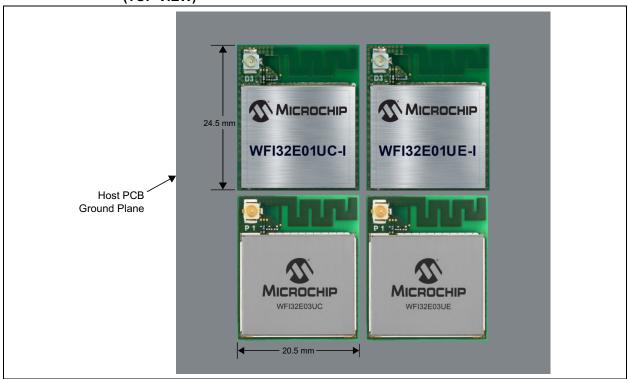

# WFI32 MODULE FEATURES

The following section lists the WFI32 Module related features, which complement SoC features.

### **Antenna Options**

- PCB Antenna Variants:

- WFI32E01PC

- WFI32E01PE

- WFI32E03PC

- WFI32E03PE

- External Antenna Variants:

- WFI32E01UC

- WFI32E01UE

- WFI32E02UC

- WFI32E02UE

- WFI32E03UC

- WFI32E03UE

- WFI32E04UC

- WFI32E04UE

### **Wireless Feature**

On-Board FEM/PA to Meet the TX Power Requirements:

• Maximum 20.5 dBm TX Power in 802.11b Mode

### Security

• Integrated Trust&GO (Optional)

# **Clock Management**

· Integrated 40 MHz POSC

# **Advanced Analog**

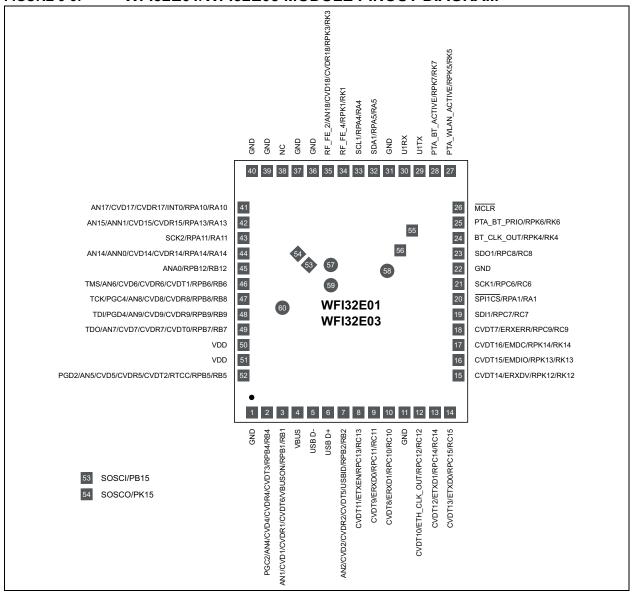

- 12 Analog Channels for WFI32E01 and WFI32E03

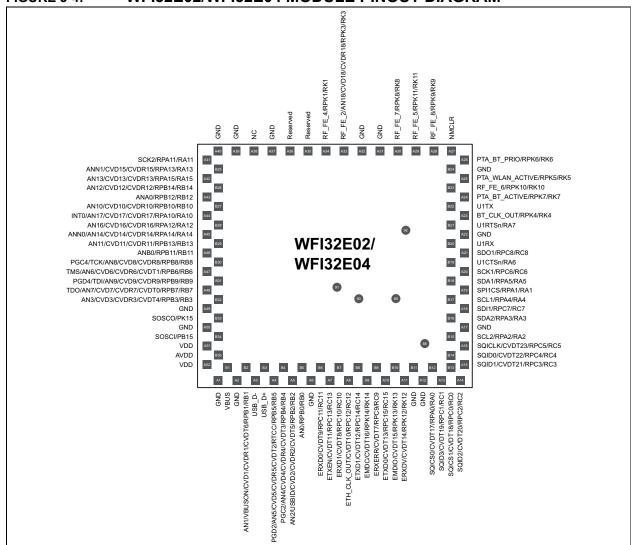

- 20 Analog Channels for WFI32E02 and WFI32E04

# Input/Output

- 37 GPIO Pins for WFI32E01 and WFI32E03

- 60 GPIO Pins for WFI32E02 and WFI32E04

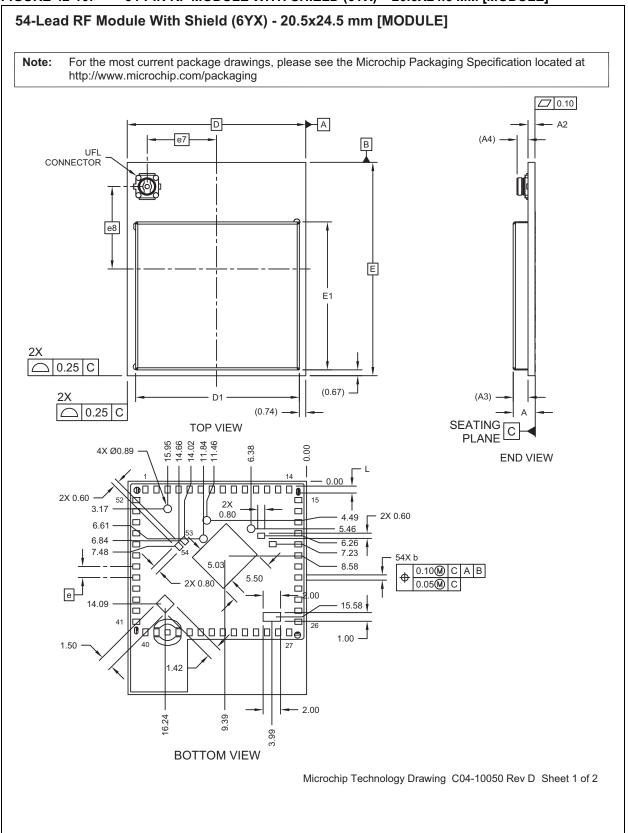

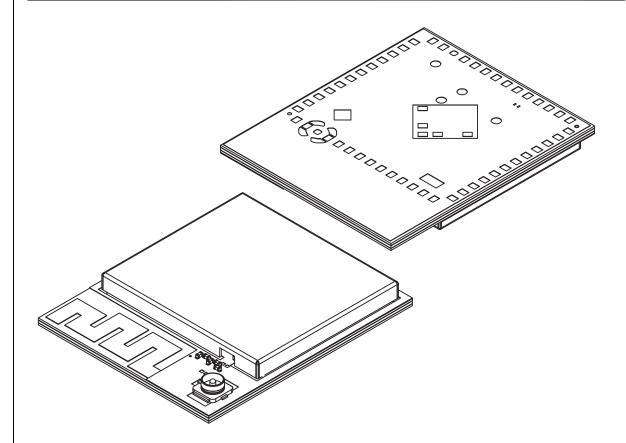

# **Package and Operating Conditions**

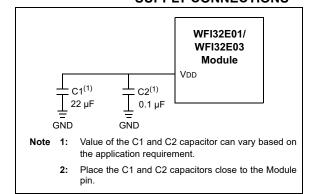

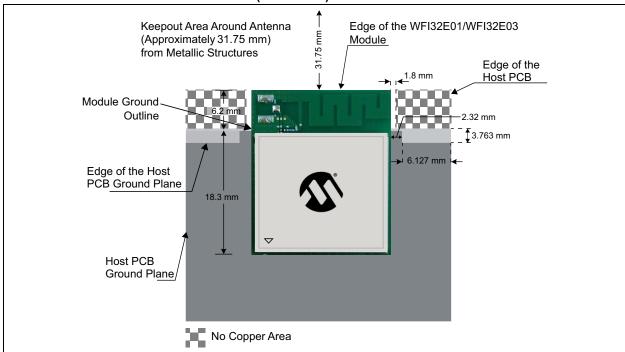

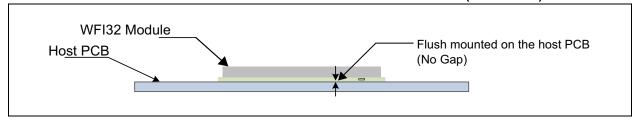

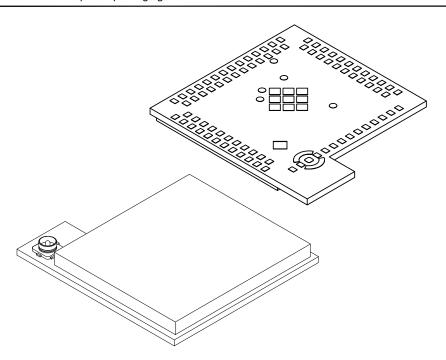

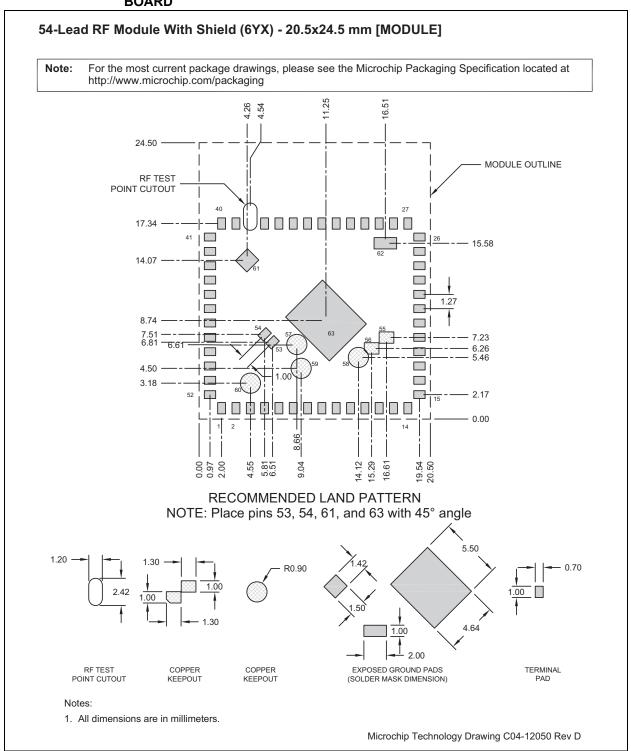

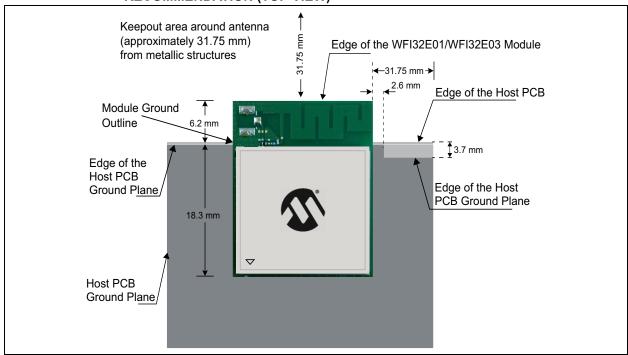

- WFI32E01 and WFI32E03 Package:

- 54-pin SMD package with Shield Can

- Size 24.5 mm x 20.5 mm x 2.5 mm

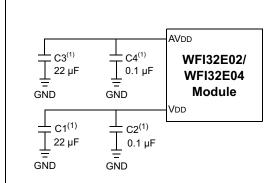

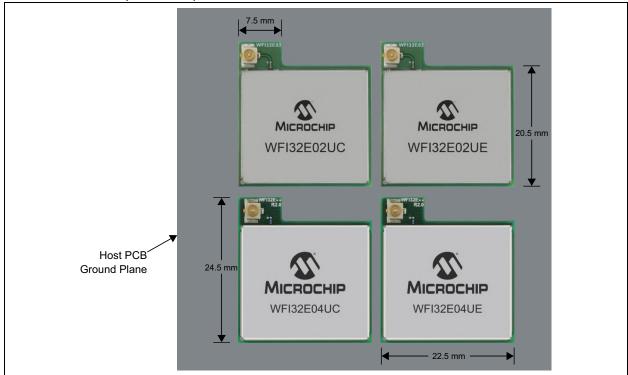

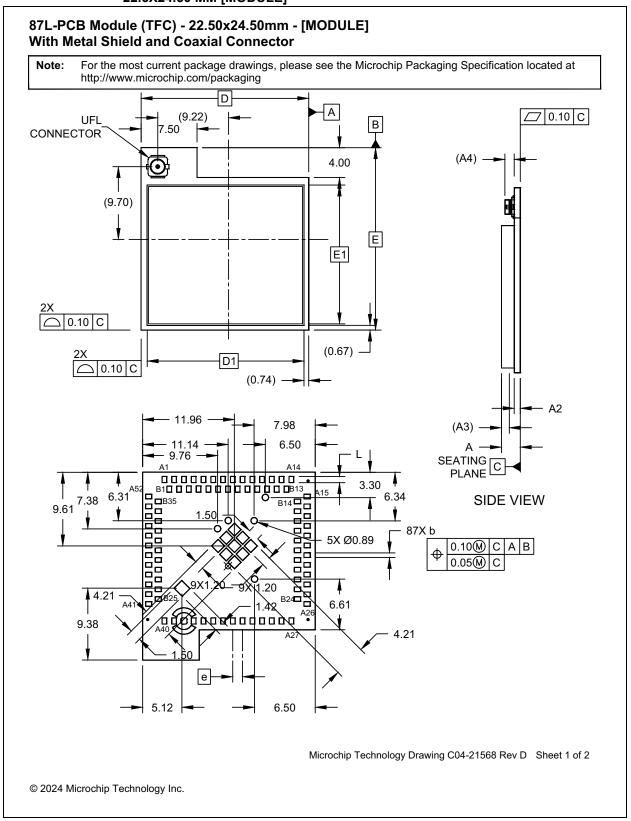

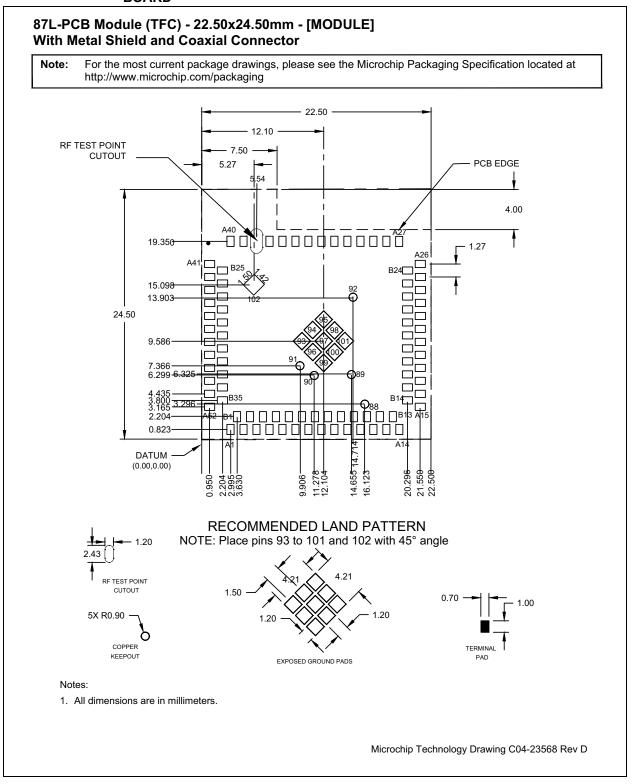

- WFI32E02 and WFI32E04 Package:

- 87-pin dual-row SMD package with Shield Can

- Size 24.5 mm x 22.5 mm x 2.5 mm

- · Operating Conditions:

- 3.0V to 3.6V, -40°C to +85°C, DC to 200 MHz

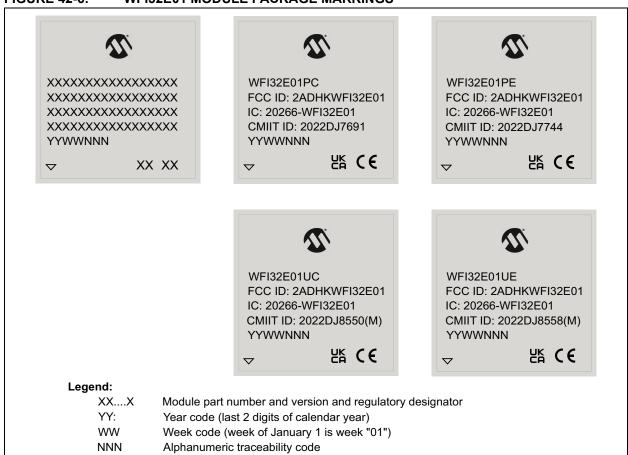

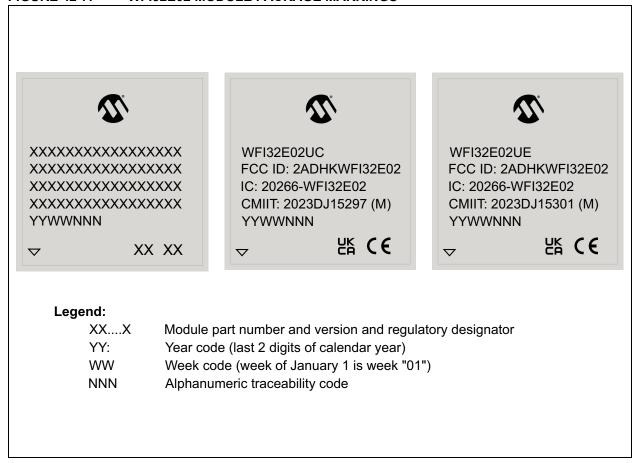

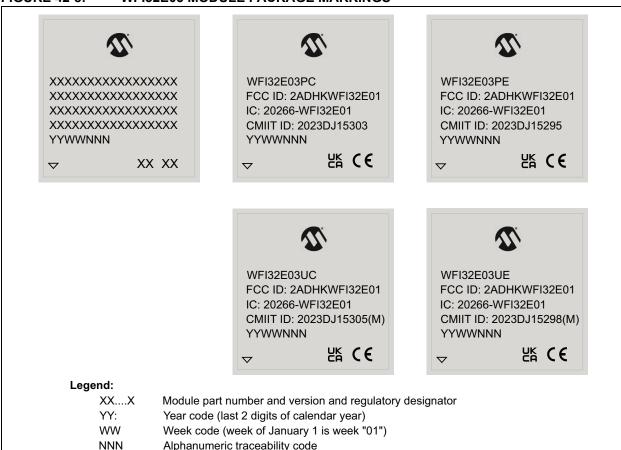

### Certifications

- WFI32 Module Certified to FCC, ISED, CE, UKCA, MIC, KCC, NCC and SRRC Radio Regulations

- RoHS and REACH Compliant

# TABLE 1: PIC32MZ W1 SoC FEATURES

| ате                | am<br>r (KB)    | ory (KB) | s   | age   | lash<br>' (KB)   | Wireles<br>u/6 | ss/RF<br>(WHZ) | Pins       | emappa                        | ble F | Perip                | (O:       | ls<br>( <u>B</u> / | g.   | c Crypto   | 093    | lσ  | annels<br>mable/<br>ited)     | annels | 'D  | ced CVD   |     | .0 FS  |                  |     | H    | ı   | ņ   | MAC      | ns     | TM   | 9   | 9    |

|--------------------|-----------------|----------|-----|-------|------------------|----------------|----------------|------------|-------------------------------|-------|----------------------|-----------|--------------------|------|------------|--------|-----|-------------------------------|--------|-----|-----------|-----|--------|------------------|-----|------|-----|-----|----------|--------|------|-----|------|

| Soc N              | Progr<br>Memory | Data Mem | Pin | Packa | Boot F<br>Memory | 802.11 b/ç     | Channel BW     | Remappable | Timers/<br>Capture<br>Compare | UART  | SPI/I <sup>2</sup> S | CAN-FD (1 | CAN (2.0 A         | Cryp | Asymmetric | Trust& | TRN | DMA Cha<br>(Program<br>Dedica | ADC Ch | CVI | ADC Enhan | PTG | USB 2. | l <sub>z</sub> c | SPI | UAR. | SQI | RTC | Ethernet | id 0/I | ICSP | JTA | Trac |

| PIC32MZ1025W104132 | 1024            | 256      | 132 | DQFN  | 64               | 1x1            | 20             | 58         | 7/4/4                         | 2     | 1                    | 1         | 1                  | Υ    | Υ          | N      | Υ   | 8                             | 20     | Υ   | Υ         | 1   | 1      | 2                | 1   | 1    | Υ   | Υ   | Υ        | 62     | Υ    | Y   | Y    |

| PIC32MZ2051W104132 | 2048            | 512      | 132 | DQFN  | 128              | 1x1            | 20             | 58         | 7/4/4                         | 2     | 1                    | 1         | 1                  | Υ    | Υ          | Ν      | Υ   | 8                             | 20     | Υ   | Υ         | 1   | 1      | 2                | 1   | 1    | Υ   | Υ   | Υ        | 62     | Υ    | Υ ' | Y    |

# TABLE 2: WFI32 MODULE FEATURES

|             |                        | <u> </u>         |      |         |                           | Wi           | reless       | /RF              | F               | Remappa                        | ble  | Perip                | hera         | ls            |        | 9                 |          |      |                                              |              |     | Q.               |     |            |                  |     |      |     |      |              |          |      |      |       |                 |

|-------------|------------------------|------------------|------|---------|---------------------------|--------------|--------------|------------------|-----------------|--------------------------------|------|----------------------|--------------|---------------|--------|-------------------|----------|------|----------------------------------------------|--------------|-----|------------------|-----|------------|------------------|-----|------|-----|------|--------------|----------|------|------|-------|-----------------|

| Module Name | Program<br>Memory (KB) | Data Memory (KB) | Pins | Package | Boot Flash<br>Memory (KB) | On-board FEM | 802.11 b/g/n | Channel BW (MHz) | Remappable Pins | Timers/<br>Capture/<br>Compare | UART | SPI/I <sup>2</sup> S | CAN-FD (1.0) | CAN (2.0 A/B) | Crypto | Asymmetric Crypto | Trust&GO | TRNG | DMA Channels<br>(Programmable/<br>Dedicated) | ADC Channels | CVD | ADC Enhanced CVD | PTG | USB 2.0 FS | 1 <sup>2</sup> C | SPI | UART | SQI | RTCC | Ethernet MAC | I/O Pins | ICSP | JTAG | Trace | Antenna Options |

| WFI32E01PE  | 1024                   | 256              | 54   | SMD     | 64                        | Υ            | 1x1          | 20               | 35              | 7/4/4                          | 2    | 1                    | 1            | 1             | Υ      | Υ                 | N        | Υ    | 8                                            | 12           | Υ   | Υ                | 1   | 1          | 1                | 1   | 1    | N   | Υ    | Υ            | 37       | Υ    | Υ    | Υ     | PCB             |

| WFI32E01PC  | 1024                   | 256              | 54   | SMD     | 64                        | Υ            | 1x1          | 20               | 35              | 7/4/4                          | 2    | 1                    | 1            | 1             | Υ      | Υ                 | Υ        | Υ    | 8                                            | 12           | Υ   | Υ                | 1   | 1          | 1                | 1   | 1    | N   | Υ    | Υ            | 37       | Υ    | Υ    | Υ     | PCB             |

| WFI32E01UE  | 1024                   | 256              | 54   | SMD     | 64                        | Υ            | 1x1          | 20               | 35              | 7/4/4                          | 2    | 1                    | 1            | 1             | Υ      | Υ                 | Ν        | Υ    | 8                                            | 12           | Υ   | Υ                | 1   | 1          | 1                | 1   | 1    | N   | Υ    | Υ            | 37       | Υ    | Υ    | Υ     | U.FL            |

| WFI32E01UC  | 1024                   | 256              | 54   | SMD     | 64                        | Υ            | 1x1          | 20               | 35              | 7/4/4                          | 2    | 1                    | 1            | 1             | Υ      | Υ                 | Υ        | Υ    | 8                                            | 12           | Υ   | Υ                | 1   | 1          | 1                | 1   | 1    | N   | Υ    | Υ            | 37       | Υ    | Υ    | Υ     | U.FL            |

| WFI32E02UE  | 1024                   | 256              | 87   | SMD     | 64                        | Υ            | 1x1          | 20               | 56              | 7/4/4                          | 2    | 1                    | 1            | 1             | Υ      | Υ                 | Ν        | Υ    | 8                                            | 20           | Υ   | Υ                | 1   | 1          | 2                | 1   | 1    | Υ   | Υ    | Υ            | 60       | Υ    | Υ    | Υ     | U.FL            |

| WFI32E02UC  | 1024                   | 256              | 87   | SMD     | 64                        | Υ            | 1x1          | 20               | 56              | 7/4/4                          | 2    | 1                    | 1            | 1             | Υ      | Υ                 | Υ        | Υ    | 8                                            | 20           | Υ   | Υ                | 1   | 1          | 2                | 1   | 1    | Υ   | Υ    | Υ            | 60       | Υ    | Υ    | Υ     | U.FL            |

| WFI32E03PE  | 2048                   | 512              | 54   | SMD     | 128                       | Υ            | 1x1          | 20               | 35              | 7/4/4                          | 2    | 1                    | 1            | 1             | Υ      | Υ                 | Ν        | Υ    | 8                                            | 12           | Υ   | Υ                | 1   | 1          | 1                | 1   | 1    | N   | Υ    | Υ            | 37       | Υ    | Υ    | Υ     | PCB             |

| WFI32E03PC  | 2048                   | 512              | 54   | SMD     | 128                       | Υ            | 1x1          | 20               | 35              | 7/4/4                          | 2    | 1                    | 1            | 1             | Υ      | Υ                 | Υ        | Υ    | 8                                            | 12           | Υ   | Υ                | 1   | 1          | 1                | 1   | 1    | N   | Υ    | Υ            | 37       | Υ    | Υ    | Υ     | PCB             |

| WFI32E03UE  | 2048                   | 512              | 54   | SMD     | 128                       | Υ            | 1x1          | 20               | 35              | 7/4/4                          | 2    | 1                    | 1            | 1             | Υ      | Υ                 | Ν        | Υ    | 8                                            | 12           | Υ   | Υ                | 1   | 1          | 1                | 1   | 1    | N   | Υ    | Υ            | 37       | Υ    | Υ    | Υ     | U.FL            |

| WFI32E03UC  | 2048                   | 512              | 54   | SMD     | 128                       | Υ            | 1x1          | 20               | 35              | 7/4/4                          | 2    | 1                    | 1            | 1             | Υ      | Υ                 | Υ        | Υ    | 8                                            | 12           | Υ   | Υ                | 1   | 1          | 1                | 1   | 1    | N   | Υ    | Υ            | 37       | Υ    | Υ    | Υ     | U.FL            |

| WFI32E04UE  | 2048                   | 512              | 87   | SMD     | 128                       | Υ            | 1x1          | 20               | 56              | 7/4/4                          | 2    | 1                    | 1            | 1             | Υ      | Υ                 | Ν        | Υ    | 8                                            | 20           | Υ   | Υ                | 1   | 1          | 2                | 1   | 1    | Υ   | Υ    | Υ            | 60       | Υ    | Υ    | Υ     | U.FL            |

| WFI32E04UC  | 2048                   | 512              | 87   | SMD     | 128                       | Υ            | 1x1          | 20               | 56              | 7/4/4                          | 2    | 1                    | 1            | 1             | Υ      | Υ                 | Ν        | Υ    | 8                                            | 20           | Υ   | Υ                | 1   | 1          | 2                | 1   | 1    | Υ   | Υ    | Υ            | 60       | Υ    | Υ    | Υ     | U.FL            |

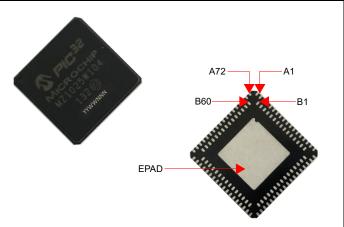

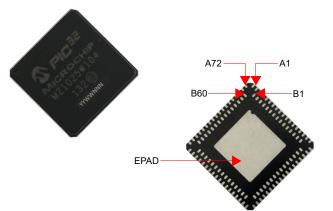

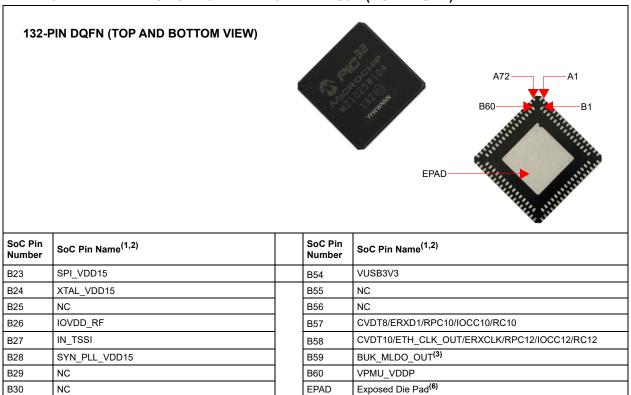

TABLE 3: PIN NAMES FOR 132-PIN PIC32MZ W1 SoC

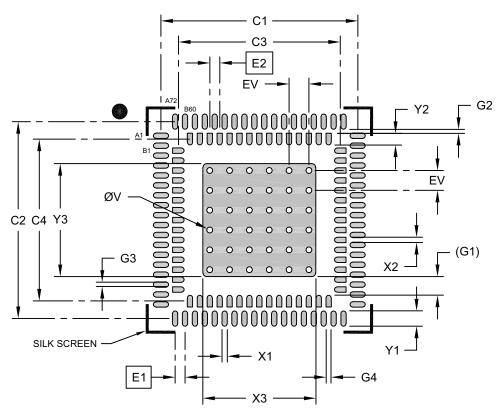

# 132-PIN DQFN (TOP AND BOTTOM VIEW)

| SoC Pin<br>Number | SoC Pin Name <sup>(1,2)</sup>  | SoC Pin<br>Number | SoC Pin Name <sup>(1,2)</sup>                            |

|-------------------|--------------------------------|-------------------|----------------------------------------------------------|

| A1                | NC                             | A36               | NC                                                       |

| A2                | PMU_VSENSE                     | A37               | NC                                                       |

| A3                | VDD33                          | A38               | NC                                                       |

| A4                | CVDT13/ETXD0/RPC15/IOCC15/RC15 | A39               | RXR_IN2                                                  |

| A5                | CVDT15/EMDIO/RPK13/IOCK13/RK13 | A40               | RXR_RIQ_VDD15                                            |

| A6                | CVDT14/ERXDV/RPK12/IOCK12/RK12 | A41               | NC                                                       |

| A7                | NC                             | A42               | TXR_UMX_VDD15                                            |

| A8                | VDD15                          | A43               | TXR_LPA_VOUT                                             |

| A9                | SQICS1/CVDT18/RPC0/IOCC0/RC0   | A44               | RF_FE_3/RPK0/IOCK0/RK0                                   |

| A10               | SQID2/CVDT20/RPC2/IOCC2/RC2    | A45               | RF_FE_1/AN19/CVD19/CVDR19/RPK2/IOCK2/RK2                 |

| A11               | VDD33                          | A46               | VDD33                                                    |

| A12               | SQICLK/CVDT23/RPC5/IOCC5/RC5   | A47               | SCK2/RPA11/IOCA11/RA11                                   |

| A13               | SDI1/RPC7/IOCC7/RC7            | A48               | AN15/ANN1/CVD15/CVDR15/RPA13/IOCA13/RA13                 |

| A14               | SS1/CS1/FSYNC1/RPA1/IOCA1/RA1  | A49               | TRD0/AN13/CVD13/CVDR13/RPA15/IOCA15/RA15                 |

| A15               | SCL2/RPA2/IOCA2/RA2            | A50               | TRD1/AN12/CVD12/CVDR12/RPB14/IOCB14/RB14                 |

| A16               | SCL1/RPA4/IOCA4/RA4            | A51               | TRD3/ANA0/RPB12/IOCB12/RB12                              |

| A17               | NC                             | A52               | AN10/CVD10/CVDR10/LVDIN/RPB10/IOCB10/RB10                |

| A18               | NC                             | A53               | NC                                                       |

| A19               | NC                             | A54               | NC                                                       |

| A20               | NC                             | A55               | NC                                                       |

| A21               | U1RTSn/U1BCLK/IOCA7/RA7        | A56               | TDI/PGED4/AN9/CVD9/CVDR9/RPB9/IOCB9/RB9                  |

| A22               | U1TX/IOCA9/RA9                 | A57               | TDO/AN7/CVD7/CVDR7/CVDT0/RPB7/IOCB7/RB7                  |

| A23               | MCLR                           | A58               | SOSCO/PK15 <sup>(4)</sup>                                |

| A24               | BT_PRIO/RPK6/IOCK6/RK6         | A59               | SOSCI/PB15 <sup>(4)</sup>                                |

| A25               | VDD33                          | A60               | VBAT                                                     |

| A26               | RF_FE_8/RPK9/IOCK9/RK9         | A61               | PGEC1/AN3/CVD3/CVDR3/CVDT4/USBOEN/RPB3/IOCB3/RB3         |

| A27               | RF_FE_5/RPK11/IOCK11/RK11      | A62               | AN1/CVD1/CVDR1/CVDT6/ETH_EXCLK_OUT/VBUSON/RPB1/IOCB1/RB1 |

| A28               | AFE_VDD15                      | A63               | D-                                                       |

The RPn pins can be used by re-mappable peripherals. Refer to Section 13.4 "Peripheral Pin Select (PPS)" for details. Every I/O port pin (RAx-RKx) can be used as a change notification pin (CNAx-CNKx). See Section 13.0 "I/O Ports" for more Note

- 3: Do not use BUCK/MLDO output to drive any other device.

- 4: A58 and A59 pins can be configured as GPI as an alternate function.

- Exact connection for each pin is available in the reference design package. Contact the Microchip Sales/Support Team for the package. 5:

- Connect Exposed Die Pad to GND.

TABLE 3: PIN NAMES FOR 132-PIN PIC32MZ W1 SoC (CONTINUED)

# 132-PIN DQFN (TOP AND BOTTOM VIEW)

| SoC Pin<br>Number | SoC Pin Name <sup>(1,2)</sup>  | SoC Pin<br>Number | SoC Pin Name <sup>(1,2)</sup>                   |

|-------------------|--------------------------------|-------------------|-------------------------------------------------|

| A29               | XTAL IN                        | A64               | D+                                              |

| A30               | XTAL OUT                       | A65               | VBUS                                            |

| A31               | NC                             | A66               | VDD15                                           |

| A32               | SYN SD VDD15                   | A67               | VDD33                                           |

| A33               | SYN_VCO_VDD15                  | A68               | CVDT9/ERXD0/RPC11/IOCC11/RC11                   |

| A34               | IOVDD_RF                       | A69               | CVDT11/ETXEN/RPC13/IOCC13/RC13                  |

| A35               | NC                             | A70               | VPMU_VDDP                                       |

| A71               | BUK_BK_LX                      | A30               | NC                                              |

| A72               | NC                             | B31               | MBS_EXTRA_48K                                   |

| B1                | PMU_VDDIO/VPMU_VDDC            | B32               | RXR_FE2_VDD15                                   |

| B2                | CVDT12/ETXD1/RPC14/IOCC14/RC14 | B33               | RXR_FE1_VDD15                                   |

| B3                | VDD33                          | B34               | BB_VDD15                                        |

| B4                | CVDT16/EMDC/RPK14/IOCK14/RK14  | B35               | NC                                              |

| B5                | CVDT7/ERXERR/RPC9/IOCC9/RC9    | B36               | TXR_LPA_VDD15                                   |

| B6                | SQICS0/CVDT17/RPA0/IOCA0/RA0   | B37               | RF_FE_4/RPK1/IOCK1/RK1                          |

| B7                | NC                             | B38               | RF_FE_2/AN18/CVD18/CVDR18/RPK3/IOCK3/RK3        |

| B8                | SQID3/CVDT19/RPC1/IOCC1/RC1    | B39               | AN17/CVD17/CVDR17/CTRTM0/INT0/RPA10/IOCA10/RA10 |

| B9                | SQID1/CVDT21/RPC3/IOCC3/RC3    | B40               | AN16/CVD16/CVDR16/CTRTM1/RPA12/IOCA12/RA12      |

| B10               | SQID0/CVDT22/RPC4/IOCC4/RC4    | B41               | TRCLK/AN14/ANN0/CVD14/CVDR14/RPA14/IOCA14/RA14  |

| B11               | SCK1/RPC6/IOCC6/RC6            | B42               | AVDD                                            |

| B12               | SDO1/RPC8/IOCC8/RC8            | B43               | TRD2/AN11/CVD11/CVDR11/RPB13/IOCB13/RB13        |

| B13               | VDD33                          | B44               | ANB0/RPB11/IOCB11/RB11                          |

| B14               | SDA2/RPA3/IOCA3/RA3            | B45               | AVss                                            |

| B15               | SDA1/RPA5/IOCA5/RA5            | B46               | TCK/PGEC4/AN8/CVD8/CVDR8/RPB8/IOCB8/RB8         |

| B16               | U1CTSn/IOCA6/RA6               | B47               | TMS/AN6/CVD6/CVDR6/CVDT1/RPB6/IOCB6/RB6         |

| B17               | U1RX/IOCA8/RA8                 | B48               | VDD33                                           |

| B18               | BT_CLK_OUT/RPK4/IOCK4/RK4      | B49               | PGED2/AN5/CVD5/CVDR5/CVDT2/RTCC/RPB5/IOCB5/RB5  |

| B19               | WLAN_ACTIVE/RPK5/IOCK5/RK5     | B50               | PGEC2/AN4/CVD4/CVDR4/CVDT3/RPB4/IOCB4/RB4       |

| B20               | BT_ACTIVE/RPK7/IOCK7/RK7       | B51               | PGED1/AN2/CVD2/CVDR2/CVDT5/USBID/RPB2/IOCB2/RB2 |

| B21               | RF_FE_7/RPK8/IOCK8/RK8         | B52               | AN0/RPB0/IOCB0/RB0                              |

| B22               | RF FE 6/RPK10/IOCK10/RK10      | B53               | NC                                              |

Note 1:

The RPn pins can be used by re-mappable peripherals. Refer to Section 13.4 "Peripheral Pin Select (PPS)" for details. Every I/O port pin (RAx-RKx) can be used as a change notification pin (CNAx-CNKx). See Section 13.0 "I/O Ports" for more

Do not use BUCK/MLDO output to drive any other device.

<sup>4:</sup> A58 and A59 pins can be configured as GPI as an alternate function.

Exact connection for each pin is available in the reference design package. Contact the Microchip Sales/Support Team for the package.

Connect Exposed Die Pad to GND.

TABLE 3: PIN NAMES FOR 132-PIN PIC32MZ W1 SoC (CONTINUED)

- Note 1:

- The RPn pins can be used by re-mappable peripherals. Refer to **Section 13.4 "Peripheral Pin Select (PPS)"** for details. Every I/O port pin (RAx-RKx) can be used as a change notification pin (CNAx-CNKx). See **Section 13.0 "I/O Ports"** for more

- Do not use BUCK/MLDO output to drive any other device. 3:

- 4: A58 and A59 pins can be configured as GPI as an alternate function.

- Exact connection for each pin is available in the reference design package. Contact the Microchip Sales/Support Team for the package. 5:

- Connect Exposed Die Pad to GND.

# PIC32MZ W1 and WFI32 Family

# **Table of Contents**

| Introduction                                                                 |     |

|------------------------------------------------------------------------------|-----|

| 1.0 Ordering Information                                                     | 11  |

| 2.0 PIC32MZ1025W104 SoC Description                                          | 15  |

| 3.0 WFI32E01 Module Description                                              | 31  |

| 4.0 CPU                                                                      | 63  |

| 5.0 Flash Program Memory                                                     | 75  |

| 6.0 Memory Organization                                                      | 89  |

| 7.0 Resets                                                                   | 117 |

| 8.0 CPU Exceptions and Interrupt Controller                                  | 125 |

| 9.0 Prefetch Module                                                          |     |

| 10.0 Direct Memory Access (DMA) Controller                                   | 161 |

| 11.0 Oscillator Configuration                                                | 185 |

| 12.0 Full-Speed USB                                                          | 207 |

| 13.0 I/O Ports                                                               |     |

| 14.0 Peripheral Trigger Generator (PTG)                                      | 269 |

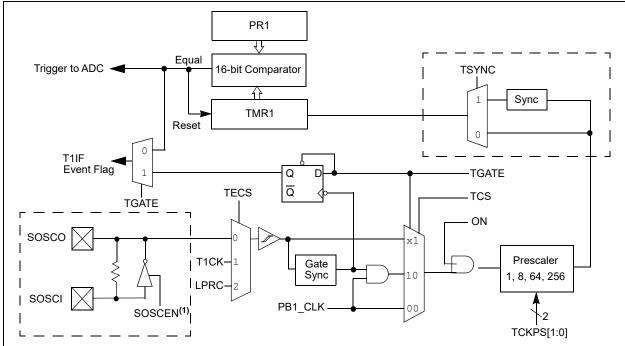

| 15.0 Timer1                                                                  | 289 |

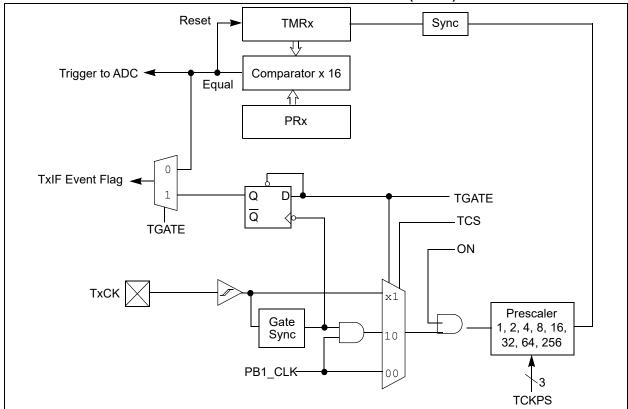

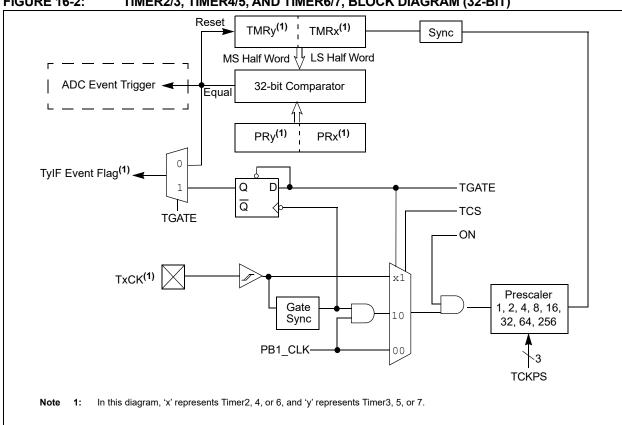

| 16.0 Timer2/3, Timer4/5, and Timer6/7                                        | 293 |

| 17.0 Deadman Timer (DMT)                                                     | 299 |

| 18.0 Watchdog Timer (WDT)                                                    |     |

| 19.0 Input Capture                                                           | 309 |

| 20.0 Output Compare                                                          | 313 |

| 21.0 Serial Peripheral Interface (SPI) and Inter-IC Sound (I <sup>2</sup> S) | 317 |

| 22.0 Serial Quad Interface (SQI)                                             |     |

| 23.0 Inter-Integrated Circuit (I <sup>2</sup> C)                             |     |

| 24.0 UART                                                                    |     |

| 25.0 Real-Time Clock and Calendar (RTCC)                                     |     |

| 26.0 Asymmetric Crypto Engine                                                | 375 |

| 27.0 Symmetric Crypto Engine                                                 | 377 |

| 28.0 True Random Number Generator (TRNG)                                     |     |

| 29.0 12-bit High-Speed Successive Approximation Register (SAR) ADC           | 407 |

| 30.0 Controller Area Network (CAN)                                           |     |

| 31.0 Controller Area Network-Flexible Data-Rate (CAN-FD) Module              | 479 |

| 32.0 Wi-Fi Controller                                                        | 529 |

| 33.0 Ethernet Controller                                                     |     |

| 34.0 Enhanced Capacitive Voltage Divider (CVD) Touch Controller              |     |

| 35.0 Power Management Unit (PMU)                                             | 589 |

| 36.0 Power-Saving Features                                                   |     |

| 37.0 Programmable Low Voltage Detect (PLVD)                                  |     |

| 38.0 Special Features                                                        |     |

| 39.0 Instruction Set                                                         |     |

| 40.0 Development Support                                                     | 645 |

| 41.0 Electrical Specifications                                               | 649 |

| 42.0 Packaging Information                                                   |     |

| Appendix A: Regulatory Approvals                                             | 789 |

| Appendix B: Document Revision History                                        | 803 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Website; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

# **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

#### **Referenced Sources**

This device data sheet is based on the following individual sections of the "PIC32 Family Reference Manual" and "PIC32MZ W1 Family Reference Man-

ual". These documents must be considered as the general reference for the operation of a particular module or device feature.

**Note:** To access the following documents, browse the documentation section of the Microchip website (www.microchip.com).

- Section 5. "Flash Program Memory with Support for Live Update" (DS60001640)

- Section 6. "Memory Organization and Permissions" (DS60001641)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupts" (DS60001108)

- Section 9. "Prefetch Module for Devices with L1 CPU Cache" (DS60001649)

- Section 9. "Watchdog, Deadman, and Power-up Timers" (DS60001114)

- Section 10. "Power-Saving Modes" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

- Section 14. "Timers" (DS60001105)

- Section 14. "Peripheral Trigger Generator (PTG)" (DS50003105)

- Section 15. "Input Capture" (DS60001122)

- Section 16. "Output Compare" (DS61111)

- Section 21. "UART" (DS60001107)

- Section 22. "12-bit High-Speed Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC)" (DS60001344)

- Section 23. "Serial Peripheral Interface (SPI)" (DS61106)

- Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116)

- Section 26. "Asymmetric Crypto Engine" (DS60001695)

- Section 27. "USB On-The-Go (OTG)" (DS61126)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125)

- Section 31. "DMA Controller" (DS60001117)

- Section 32. "Configuration" (DS60001124)

- Section 33. "Programming and Diagnostics" (DS61129)

# PIC32MZ W1 and WFI32 Family

- Section 34. "Controller Area Network (CAN)" (DS60001154)

- Section 34. "Enhanced Capacitive Voltage Divider (CVD) Controller" (DS60001684)

- Section 35. "Ethernet Controller" (DS60001155)

- Section 42. "Oscillators with Enhanced PLL" (DS60001250)

- Section 46. "Serial Quad Interface (SQI)" (DS60001244)

- Section 49. "Crypto Engine and Random Number Generator (RNG)" (DS60001246)

- Section 50. "CPU for Devices with MIPS32<sup>®</sup> microAptiv™ and M-Class Cores" (DS60001192)

- Section 56. "Controller Area Network with Flexible Data-rate (CAN FD)" (DS60001549)

# 1.0 ORDERING INFORMATION

This chapter provides the ordering information of the PIC32MZ W1 SoC and the WFI32 Module.

# 1.1 PIC32MZ W1 SoC Ordering Information

The following table describes the ordering information of the PIC32MZ W1 SoC.

TABLE 1-1: PIC32MZ W1 SOC ORDERING DETAILS

| SoC Name        | Pin and Package | Description                                                                     | Ordering Code           |

|-----------------|-----------------|---------------------------------------------------------------------------------|-------------------------|

| PIC32MZ1025W104 |                 | 32-bit MCU Wi-Fi Connectivity and<br>Security Accelerator                       | PIC32MZ1025W104132-I/NX |

| PIC32MZ2051W104 |                 | 32-bit MCU Wi-Fi Connectivity and<br>Security Accelerator with Higher<br>Memory | PIC32MZ2051W104132-I/NX |

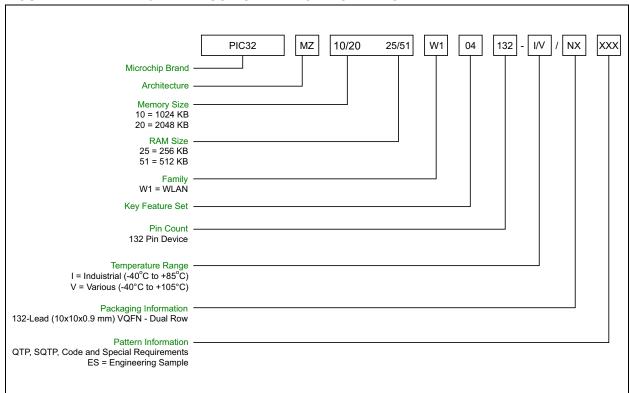

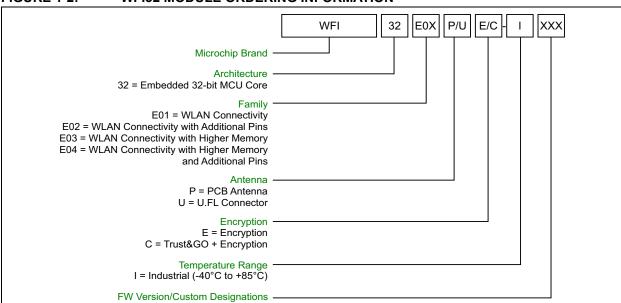

The following figure illustrates the details of the PIC32MZ W1 SoC ordering information.

FIGURE 1-1: PIC32MZ W1 SOC ORDERING INFORMATION

# 1.2 WFI32 Module Ordering Information

The following table describes the ordering information of the WFI32 Module.

TABLE 1-2: WFI32 MODULE ORDERING INFORMATION

| Model No.  | Module SoC              | Description                                                           | Regulatory<br>Certification                          | Ordering Code  |

|------------|-------------------------|-----------------------------------------------------------------------|------------------------------------------------------|----------------|

| WFI32E01PE | PIC32MZ1025W104132-I/NX | WFI32E01 Module with PCB antenna                                      | FCC, ISED, CE,<br>UKCA, MIC,<br>KCC, NCC and<br>SRRC | WFI32E01PE - I |

| WFI32E01PC |                         | WFI32E01 Module with PCB antenna and Trust&GO                         | FCC, ISED, CE,<br>UKCA, MIC,<br>KCC, NCC and<br>SRRC | WFI32E01PC - I |

| WFI32E01UE |                         | WFI32E01 Module with U.FL connector for external antenna              | FCC, ISED, CE,<br>UKCA, MIC,<br>KCC, NCC and<br>SRRC | WFI32E01UE - I |

| WFI32E01UC |                         | WFI32E01 Module with U.FL connector for external antenna and Trust&GO | FCC, ISED, CE,<br>UKCA, MIC,<br>KCC, NCC and<br>SRRC | WFI32E01UC - I |

| WFI32E02UE |                         | WFI32E02 Module with U.FL connector for external antenna              | FCC, ISED, CE,<br>UKCA, MIC,<br>KCC, NCC and<br>SRRC | WFI32E02UE - I |

| WFI32E02UC |                         | WFI32E02 Module with U.FL connector for external antenna and Trust&GO | FCC, ISED, CE,<br>UKCA, MIC,<br>KCC, NCC and<br>SRRC | WFI32E02UC - I |

| WFI32E03PE | PIC32MZ2051W104132-I/NX | WFI32E03 Module with PCB antenna                                      | FCC, ISED, CE,<br>UKCA, MIC,<br>KCC, NCC and<br>SRRC | WFI32E03PE - I |

| WFI32E03PC |                         | WFI32E03 Module with PCB Antenna and Trust&GO                         | FCC, ISED, CE,<br>UKCA, MIC,<br>KCC, NCC and<br>SRRC | WFI32E03PC - I |

| WFI32E03UE |                         | WFI32E03 Module with U.FL connector for external antenna              | FCC, ISED, CE,<br>UKCA, MIC,<br>KCC, NCC and<br>SRRC | WFI32E03UE - I |

| WFI32E03UC |                         | WFI32E03 Module with U.FL connector for external antenna and Trust&GO | FCC, ISED, CE,<br>UKCA, MIC,<br>KCC, NCC and<br>SRRC | WFI32E03UC - I |

| WFI32E04UE |                         | WFI32E04 Module with U.FL connector for external antenna              | FCC, ISED, CE,<br>UKCA, MIC,<br>KCC, NCC and<br>SRRC | WFI32E04UE - I |

| WFI32E04UC |                         | WFI32E04 Module with U.FL connector for external antenna and Trust&GO | FCC, ISED, CE,<br>UKCA, MIC,<br>KCC, NCC and<br>SRRC | WFI32E04UC - I |

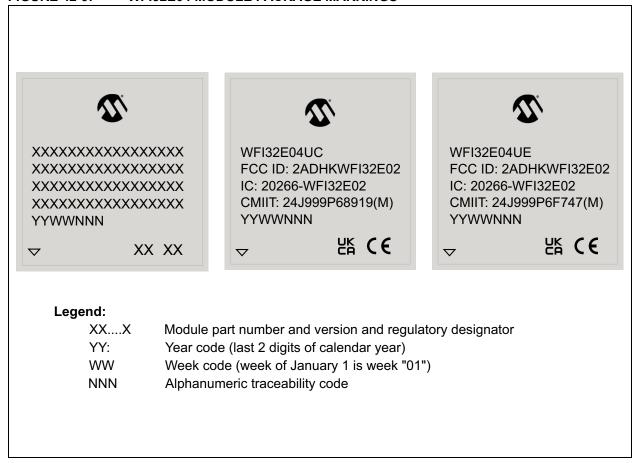

The following figure illustrates the details of the WFI32 Module ordering information.

FIGURE 1-2: WFI32 MODULE ORDERING INFORMATION

# 2.0 PIC32MZ W1 SOC DESCRIPTION

Note: This data sheet summarizes the features of the PIC32MZ W1 SoC. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "PIC32 Family Reference Manual", which is available from the Microchip website (www.microchip.com/PIC32).

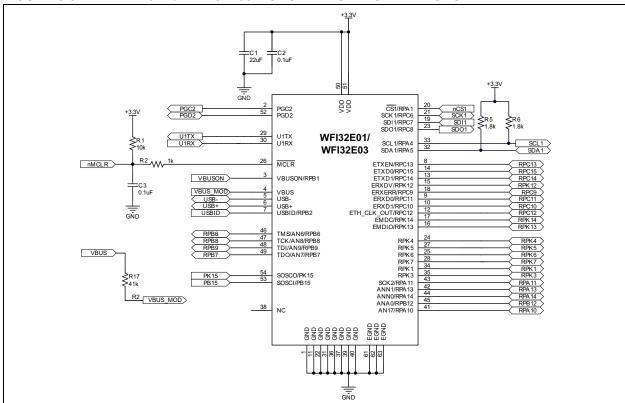

This chapter contains device-specific information for the PIC32MZ W1 SoC.

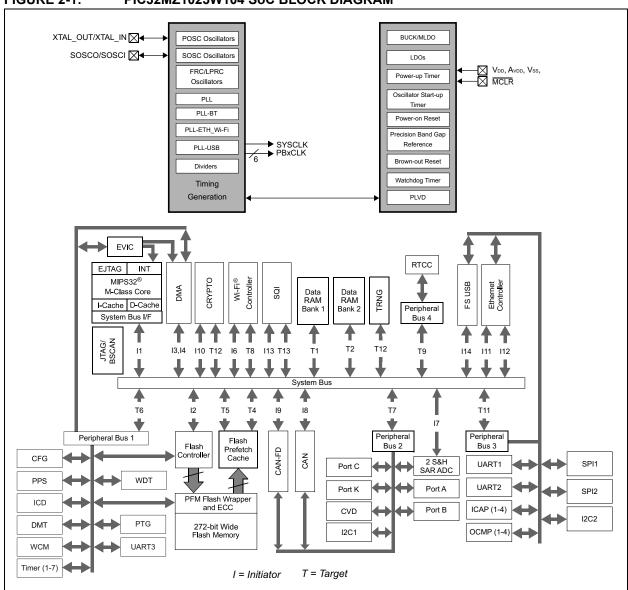

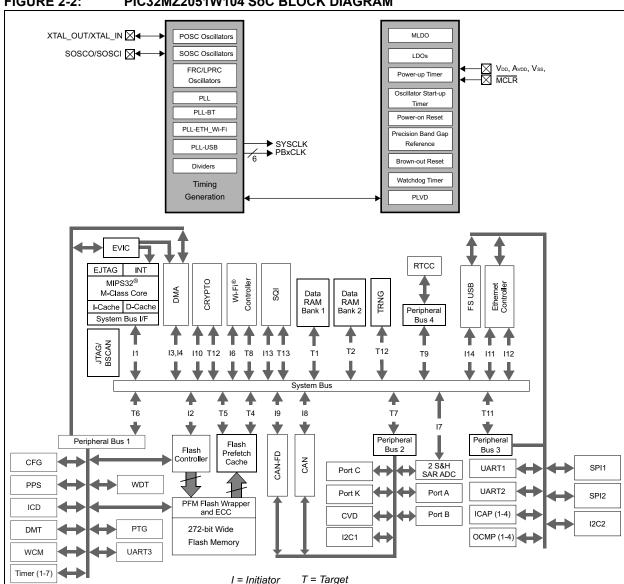

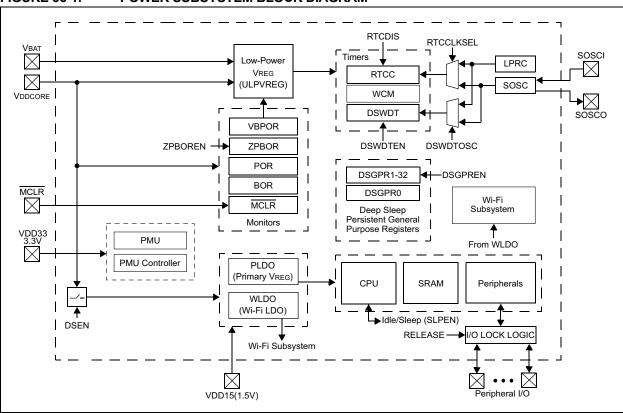

# 2.1 Block Diagram

The following figure illustrates the block diagram of the core and peripheral modules in the PIC32MZ W1 SoC.

# FIGURE 2-1: PIC32MZ1025W104 SoC BLOCK DIAGRAM

FIGURE 2-2: PIC32MZ2051W104 SoC BLOCK DIAGRAM

# 2.2 Function-wise Pinout Description

The following tables provide the function-wise pinout descriptions for the PIC32MZ W1 SoC and the WFI32 Module pins.

TABLE 2-1: ADC PINOUT DESCRIPTION

| PIC32I   | MZ W1         | WFI32E01    | /WFI32E03     | WFI32E02 | /WFI32E04     |          |                |                                 |

|----------|---------------|-------------|---------------|----------|---------------|----------|----------------|---------------------------------|

| Pin Name | Pin<br>Number | Pin Name    | Pin<br>Number | Pin Name | Pin<br>Number | Pin Type | Buffer<br>Type | Description                     |

| AN0      | B52           | _           | _             | AN0      | B5            | I        | Analog         | A/D Analog Input Channels       |

| AN1      | A62           | AN1         | 3             | AN1      | B2            | I        | Analog         |                                 |

| AN2      | B51           | AN2         | 7             | AN2      | A5            | I        | Analog         |                                 |

| AN3      | A61           | _           | _             | AN3      | B32           | I        | Analog         |                                 |

| AN4      | B50           | AN4         | 2             | AN4      | B4            | I        | Analog         |                                 |

| AN5      | B49           | AN5         | 52            | AN5      | A4            | I        | Analog         |                                 |

| AN6      | B47           | AN6         | 46            | AN6      | A47           | I        | Analog         |                                 |

| AN7      | A57           | AN7         | 49            | AN7      | A48           | I        | Analog         |                                 |

| AN8      | B46           | AN8         | 47            | AN8      | B30           | I        | Analog         |                                 |

| AN9      | A56           | AN9         | 48            | AN9      | B31           | I        | Analog         |                                 |

| AN10     | A52           | _           | _             | AN10     | B27           | I        | Analog         |                                 |

| AN11     | B43           | _           | _             | AN11     | B29           | I        | Analog         |                                 |

| AN12     | A50           | _           | _             | AN12     | B26           | I        | Analog         |                                 |

| AN13     | A49           | _           | _             | AN13     | A42           | I        | Analog         |                                 |

| AN14     | B41           | AN14        | 44            | AN14     | A45           | I        | Analog         |                                 |

| AN15     | A48           | AN15        | 42            | AN15     | B25           | I        | Analog         |                                 |

| AN16     | B40           | _           | _             | AN16     | B28           | I        | Analog         |                                 |

| AN17     | B39           | AN17        | 41            | AN17     | A44           | I        | Analog         |                                 |

| AN18     | B38           | _           | _             | _        | _             | I        | Analog         |                                 |

| AN19     | A45           | _           | _             | _        | _             | I        | Analog         |                                 |

| ANA0     | A51           | ANA0        | 45            | ANA0     | A43           | I        | Analog         |                                 |

| ANB0     | B44           | _           | _             | ANB0     | A46           | I        | Analog         | A/D Negative Analog Input Chan- |

| ANN0     | B41           | ANN0        | 44            | ANN0     | A45           | I        | Analog         | nels                            |

| ANN1     | A48           | ANN1        | 42            | ANN1     | B25           | I        | Analog         |                                 |

| Legend:  | Analog = A    | nalog input | I = Inp       | ut       |               |          |                |                                 |

TABLE 2-2: OSCILLATOR PINOUT DESCRIPTION

| PIC32MZ W | 1             | WFI32E01/ | WF132F03      | WFI32E02/ | WFI32F04      |          |                |                                                |

|-----------|---------------|-----------|---------------|-----------|---------------|----------|----------------|------------------------------------------------|

| Pin Name  | Pin<br>Number | Pin Name  | Pin<br>Number | Pin Name  | Pin<br>Number | Pin Type | Buffer<br>Type | Description                                    |

| XTAL_IN   | A29           | _         | _             | _         | _             | I        | _              | 40 MHz Primary Oscillator Crystal Input        |

| XTAL_OUT  | A30           | _         | _             | _         | _             | 0        | _              | 40 MHz Primary Oscillator Crystal Output       |

| SOSCI     | A59           | SOSCI     | 53            | SOSCI     | B34           | 1        | _              | 32.768 kHz Secondary Oscillator Crystal Input  |

| SOSCO     | A58           | sosco     | 54            | sosco     | B33           | 0        | _              | 32.768 kHz Secondary Oscillator Crystal Output |

| REFI      | PPS           | REFI      | PPS           | REFI      | PPS           | 1        | _              | Reference Clock Generator Input                |

| REFO1     | PPS           | REFO1     | PPS           | REFO1     | PPS           | 0        | _              |                                                |

| REFO2     | PPS           | REFO2     | PPS           | REFO2     | PPS           | 0        | _              |                                                |

| REFO3     | PPS           | REFO3     | PPS           | REFO3     | PPS           | 0        | _              |                                                |

| REFO4     | PPS           | REFO4     | PPS           | REFO4     | PPS           | 0        | _              | Reference Clock Generator Outputs 1-4          |

# TABLE 2-2: OSCILLATOR PINOUT DESCRIPTION

Legend: PPS = Peripheral Pin Select I = Input O = output

# TABLE 2-3: IC1 THROUGH IC4 PINOUT DESCRIPTION

| PIC32MZ V  | V1            | WFI32E01/\ | WFI32E03      | WFI32E02/V | VFI32E04      |          | Buffer |                          |

|------------|---------------|------------|---------------|------------|---------------|----------|--------|--------------------------|

| Pin Name   | Pin<br>Number | Pin Name   | Pin<br>Number | Pin Name   | Pin<br>Number | Pin Type | Туре   | Description              |

| Input Capt | ure           |            |               |            |               |          |        |                          |

| IC1        | PPS           | IC1        | PPS           | IC1        | PPS           | I        | ST     | Input Capture Inputs 1-4 |

| IC2        | PPS           | IC2        | PPS           | IC2        | PPS           | I        | ST     |                          |

| IC3        | PPS           | IC3        | PPS           | IC3        | PPS           | I        | ST     |                          |

| IC4        | PPS           | IC4        | PPS           | IC4        | PPS           | I        | ST     |                          |

Legend: ST = Schmitt Trigger input with CMOS levels I = Input PPS = Peripheral Pin Select

# TABLE 2-4: OC1 THROUGH OC4 PINOUT DESCRIPTION

| PIC32M            | Z W1          | WFI32E01/V | VFI32E03      | WFI32E02/ | WFI32E04      |          | Buffer |                              |

|-------------------|---------------|------------|---------------|-----------|---------------|----------|--------|------------------------------|

| Pin Name          | Pin<br>Number | Pin Name   | Pin<br>Number | Pin Name  | Pin<br>Number | Pin Type | Туре   | Description                  |

| <b>Output Com</b> | pare          |            |               |           |               |          |        |                              |

| OC1               | PPS           | OC1        | PPS           | OC1       | PPS           | 0        | _      | Output Compare Outputs 1-4   |

| OC2               | PPS           | OC2        | PPS           | OC2       | PPS           | 0        | _      |                              |

| OC3               | PPS           | OC3        | PPS           | OC3       | PPS           | 0        | _      |                              |

| OC4               | PPS           | OC4        | PPS           | OC4       | PPS           | 0        | _      |                              |

| OCFA              | PPS           | OCFA       | PPS           | OCFA      | PPS           | I        | ST     | Output Compare Fault A Input |

| OCFB              | PPS           | OCFB       | PPS           | OCFB      | PPS           | I        | ST     | Output Compare Fault B Input |

| OCFC              | PPS           | OCFC       | PPS           | OCFC      | PPS           | I        | ST     | Output Compare Fault C Input |

| OCFD              | PPS           | OCFD       | PPS           | OCFD      | PPS           | I        | ST     | Output Compare Fault D Input |

Legend: ST = Schmitt Trigger input with CMOS levels O = Output

PPS = Peripheral Pin Select

# TABLE 2-5: EXTERNAL INTERRUPTS PINOUT DESCRIPTION

| PIC32       | MZ W1         | WFI32E01/ | WFI32E03      | WFI32E02 | /WFI32E04     |          | Buffer |                      |

|-------------|---------------|-----------|---------------|----------|---------------|----------|--------|----------------------|

| Pin Name    | Pin<br>Number | Pin Name  | Pin<br>Number | Pin Name | Pin<br>Number | Pin Type | Туре   | Description          |

| External In | terrupts      |           |               |          |               |          |        |                      |

| INT0        | B39           | INT0      | 41            | INT0     | A44           | I        | ST     | External Interrupt 0 |

| INT1        | PPS           | INT1      | PPS           | INT1     | PPS           | I        | ST     | External Interrupt 1 |

| INT2        | PPS           | INT2      | PPS           | INT2     | PPS           | I        | ST     | External Interrupt 2 |

| INT3        | PPS           | INT3      | PPS           | INT3     | PPS           | I        | ST     | External Interrupt 3 |

| INT4        | PPS           | INT4      | PPS           | INT4     | PPS           | I        | ST     | External Interrupt 4 |

**\_egend:** ST = Schmitt Trigger input with CMOS levels I = Input PPS = Peripheral Pin Select

I = Input

TABLE 2-6: PORTA THROUGH PORTC AND PORTK PINOUT DESCRIPTION

| PIC32I   | MZ W1         | WFI32E01/ | WFI32E03      | WFI32E02/\ | WFI32E04      |          | D "            |                   |  |

|----------|---------------|-----------|---------------|------------|---------------|----------|----------------|-------------------|--|

| Pin Name | Pin<br>Number | Pin Name  | Pin<br>Number | Pin Name   | Pin<br>Number | Pin Type | Buffer<br>Type | Description       |  |

| PORTA    |               |           |               |            |               |          |                |                   |  |

| RA0      | B6            | _         | _             | RA0        | B12           | I/O      | DIG/ST         | PORTA Digital I/O |  |

| RA1      | A14           | RA1       | 20            | RA1        | A19           | I/O      | DIG/ST         |                   |  |

| RA2      | A15           | _         | _             | RA2        | B15           | I/O      | DIG/ST         |                   |  |

| RA3      | B14           | _         | _             | RA3        | B16           | I/O      | DIG/ST         |                   |  |

| RA4      | A16           | RA4       | 33            | RA4        | B17           | I/O      | DIG/ST         |                   |  |

| RA5      | B15           | RA5       | 32            | RA5        | B18           | I/O      | DIG/ST         |                   |  |

| RA6      | B16           | _         | _             | RA6        | B19           | I/O      | DIG/ST         |                   |  |

| RA7      | A21           | _         | _             | RA7        | B21           | I/O      | DIG/ST         |                   |  |

| RA8      | B17           | _         | _             | RA8        | B20           | I/O      | DIG/ST         |                   |  |

| RA9      | A22           | _         | _             | RA9        | B22           | I/O      | DIG/ST         |                   |  |

| RA10     | B39           | RA10      | 41            | RA10       | A44           | I/O      | DIG/ST         |                   |  |

| RA11     | A47           | RA11      | 43            | RA11       | A41           | I/O      | DIG/ST         |                   |  |

| RA12     | B40           | _         | _             | RA12       | B28           | I/O      | DIG/ST         |                   |  |

| RA13     | A48           | RA13      | 42            | RA13       | B25           | I/O      | DIG/ST         |                   |  |

| RA14     | B41           | RA14      | 44            | RA14       | A45           | I/O      | DIG/ST         |                   |  |

| RA15     | A49           | _         | _             | RA15       | A42           | I/O      | DIG/ST         |                   |  |

| PORTB    |               |           |               |            |               |          |                |                   |  |

| RB0      | B52           | _         | _             | RB0        | B5            | I/O      | DIG/ST         | PORTB Digital I/O |  |

| RB1      | A62           | RB1       | 3             | RB1        | B2            | I/O      | DIG/ST         |                   |  |

| RB2      | B51           | RB2       | 7             | RB2        | A5            | I/O      | DIG/ST         |                   |  |

| RB3      | A61           | _         | _             | RB3        | B32           | I/O      | DIG/ST         |                   |  |

| RB4      | B50           | RB4       | 2             | RB4        | B4            | I/O      | DIG/ST         |                   |  |

| RB5      | B49           | RB5       | 52            | RB5        | A4            | I/O      | DIG/ST         |                   |  |

| RB6      | B47           | RB6       | 46            | RB6        | A47           | I/O      | DIG/ST         |                   |  |

| RB7      | A57           | RB7       | 49            | RB7        | A48           | I/O      | DIG/ST         |                   |  |

| RB8      | B46           | RB8       | 47            | RB8        | B30           | I/O      | DIG/ST         |                   |  |

| RB9      | A56           | RB9       | 48            | RB9        | B31           | I/O      | DIG/ST         |                   |  |

| RB10     | A52           | _         | _             | RB10       | B27           | I/O      | DIG/ST         |                   |  |

| RB11     | B44           | _         | _             | RB11       | A46           | I/O      | DIG/ST         |                   |  |

| RB12     | A51           | RB12      | 45            | RB12       | A43           | I/O      | DIG/ST         |                   |  |

| RB13     | B43           | _         | _             | RB13       | B29           | I/O      | DIG/ST         |                   |  |

| RB14     | A50           | _         | _             | RB14       | B26           | I/O      | DIG/ST         |                   |  |

| PB15     | A59           | PB15      | 53            | PB15       | B34           | ı        | DIG/ST         |                   |  |

**Legend:** DIG = Digital input ST = Schmitt Trigger input with CMOS levels O = Output I = Input

TABLE 2-6: PORTA THROUGH PORTC AND PORTK PINOUT DESCRIPTION (CONTINUED)

| PIC32    | MZ W1         | WFI32E01/ | WFI32E03      | WFI32E02/ | WFI32E04      |          | D. effer       |                   |

|----------|---------------|-----------|---------------|-----------|---------------|----------|----------------|-------------------|

| Pin Name | Pin<br>Number | Pin Name  | Pin<br>Number | Pin Name  | Pin<br>Number | Pin Type | Buffer<br>Type | Description       |

| PORTC    |               |           |               |           |               |          |                |                   |

| RC0      | A9            | _         | _             | RC0       | _             | I/O      | DIG/ST         | PORTC Digital I/O |

| RC1      | B8            | _         | _             | RC1       | _             | I/O      | DIG/ST         |                   |

| RC2      | A10           | _         | _             | RC2       | _             | I/O      | DIG/ST         |                   |

| RC3      | В9            | _         | _             | RC3       | _             | I/O      | DIG/ST         |                   |

| RC4      | B10           | _         | _             | RC4       | _             | I/O      | DIG/ST         |                   |

| RC5      | A12           | _         | _             | RC5       | _             | I/O      | DIG/ST         |                   |

| RC6      | B11           | RC6       | 21            | RC6       | _             | I/O      | DIG/ST         |                   |

| RC7      | A13           | RC7       | 19            | RC7       | _             | I/O      | DIG/ST         |                   |

| RC8      | B12           | RC8       | 23            | RC8       | _             | I/O      | DIG/ST         |                   |

| RC9      | B5            | RC9       | 18            | RC9       | _             | I/O      | DIG/ST         |                   |

| RC10     | B57           | RC10      | 10            | RC10      | _             | I/O      | DIG/ST         |                   |

| RC11     | A68           | RC11      | 9             | RC11      | _             | I/O      | DIG/ST         |                   |

| RC12     | B58           | RC12      | 12            | RC12      | _             | I/O      | DIG/ST         |                   |

| RC13     | A69           | RC13      | 8             | RC13      | _             | I/O      | DIG/ST         |                   |

| RC14     | B2            | RC14      | 13            | RC14      | _             | I/O      | DIG/ST         |                   |

| RC15     | A4            | RC15      | 14            | RC15      | _             | I/O      | DIG/ST         |                   |

| PORTK    |               |           | ·             |           | •             |          | ,              |                   |

| RK0      | A44           |           | _             | RK0       | _             | I/O      | DIG/ST         | PORTK Digital I/O |

| RK1      | B37           | RK1       | 34            | RK1       | _             | I/O      | DIG/ST         |                   |

| RK2      | A45           | _         | _             | RK2       | _             | I/O      | DIG/ST         |                   |

| RK3      | B38           | RK3       | 35            | RK3       | _             | I/O      | DIG/ST         |                   |

| RK4      | B18           | RK4       | 24            | RK4       | _             | I/O      | DIG/ST         |                   |

| RK5      | B19           | RK5       | 27            | RK5       | _             | I/O      | DIG/ST         |                   |

| RK6      | A24           | RK6       | 25            | RK6       | _             | I/O      | DIG/ST         |                   |

| RK7      | B20           | RK7       | 28            | RK7       | _             | I/O      | DIG/ST         |                   |

| RK8      | B21           | _         | _             | RK8       | _             | I/O      | DIG/ST         |                   |

| RK9      | A26           | _         | _             | RK9       | _             | I/O      | DIG/ST         |                   |

| RK10     | B22           | _         | _             | RK10      | _             | I/O      | DIG/ST         |                   |

| RK11     | A27           | _         | _             | RK11      | _             | I/O      | DIG/ST         |                   |

| RK12     | A6            | RK12      | 15            | RK12      | _             | I/O      | DIG/ST         |                   |

| RK13     | A5            | RK13      | 16            | RK13      | _             | I/O      | DIG/ST         |                   |

| RK14     | B4            | RK14      | 17            | RK14      | _             | I/O      | DIG/ST         |                   |

| PK15     | A58           | PK15      | 54            | PK15      | _             | I        | DIG/ST         |                   |

Legend: DIG = Digital input ST = Schmitt Trigger input with CMOS levels O = Output I = Input

TABLE 2-7: TIMER1 THROUGH TIMER7 AND RTCC PINOUT DESCRIPTION

| PIC32                 | /IZ W1                       | WFI32E01/WFI32E03 |               | WFI32E02/WFI32E04 |               |          | D. effer       |                             |  |

|-----------------------|------------------------------|-------------------|---------------|-------------------|---------------|----------|----------------|-----------------------------|--|

| Pin Name              | Pin<br>Number                | Pin Name          | Pin<br>Number | Pin Name          | Pin<br>Number | Pin Type | Buffer<br>Type | Description                 |  |

| Timer1 through Timer7 |                              |                   |               |                   |               |          |                |                             |  |

| T1CK                  | PPS                          | T1CK              | PPS           | T1CK              | PPS           | I        | ST             | Timer1 External Clock Input |  |

| T2CK                  | PPS                          | T2CK              | PPS           | T2CK              | PPS           | I        | ST             | Timer2 External Clock Input |  |

| T3CK                  | PPS                          | T3CK              | PPS           | T3CK              | PPS           | I        | ST             | Timer3 External Clock Input |  |

| T4CK                  | PPS                          | T4CK              | PPS           | T4CK              | PPS           | I        | ST             | Timer4 External Clock Input |  |

| T5CK                  | PPS                          | T5CK              | PPS           | T5CK              | PPS           | I        | ST             | Timer5 External Clock Input |  |

| T6CK                  | PPS                          | T6CK              | PPS           | T6CK              | PPS           | I        | ST             | Timer6 External Clock Input |  |

| T7CK                  | PPS                          | T7CK              | PPS           | T7CK              | PPS           | I        | ST             | Timer7 External Clock Input |  |

| Real-Time             | Real-Time Clock and Calendar |                   |               |                   |               |          |                |                             |  |

| RTCC                  | B49                          | RTCC              | 52            | RTCC              | 52            | 0        | _              | RTCC Output Clock           |  |

**Legend:** ST = Schmitt Trigger input with CMOS levels

O = Output I = Input

PPS = Peripheral Pin Select

TABLE 2-8: UART1 (DEDICATED) PINOUT DESCRIPTION

|                   | -                                             | ,                 |               | ,                 | _             | _        |        |                                                         |  |  |  |

|-------------------|-----------------------------------------------|-------------------|---------------|-------------------|---------------|----------|--------|---------------------------------------------------------|--|--|--|

| PIC32N            | /IZ W1                                        | WFI32E01/WFI32E03 |               | WFI32E02/WFI32E04 |               |          | Buffer |                                                         |  |  |  |

| Pin Name          | Pin<br>Number                                 | Pin Name          | Pin<br>Number | Pin Name          | Pin<br>Number | Pin Type | Туре   | Description                                             |  |  |  |

| Universal A       | Universal Asynchronous Receiver Transmitter 1 |                   |               |                   |               |          |        |                                                         |  |  |  |

| U1CTSn            | B16                                           | _                 | _             | U1CTSn            | B19           | I        | ST     | UART1 Clear to Send (CTS) Input                         |  |  |  |

| U1RTSn/<br>U1BCLK | A21                                           | _                 | _             | U1RTSn/<br>U1BCLK | B21           | 0        | DIG    | UART1 Request to Send (RTS) Output/<br>UART1 Baud Clock |  |  |  |

| U1RX              | B17                                           | U1RX              | 30            | U1RX              | B20           | I        | ST     | UART1 Receive                                           |  |  |  |

| U1TX              | A22                                           | U1TX              | 29            | U1TX              | B22           | 0        | DIG    | UART1 Transmit                                          |  |  |  |

Legend: DIG = Digital input ST = Schmitt Trigger input with CMOS levels O = Output I = Input

TABLE 2-9: UART1 THROUGH UART3 PINOUT DESCRIPTION

| TABLE 2 0. CARTI TIMOCOTI CARTOT MOOT BECORNI TICK |               |               |               |           |               |          |        |                                      |  |  |  |

|----------------------------------------------------|---------------|---------------|---------------|-----------|---------------|----------|--------|--------------------------------------|--|--|--|

| PIC32M                                             | IZ W1         | WFI32E01/     | WFI32E03      | WFI32E02/ | WFI32E04      |          | Buffer |                                      |  |  |  |

| Pin Name                                           | Pin<br>Number | Pin Name      | Pin<br>Number | Pin Name  | Pin<br>Number | Pin Type | Туре   | Description                          |  |  |  |

| Universal Asynchronous Receiver Transmitter 1      |               |               |               |           |               |          |        |                                      |  |  |  |

| U1CTSn                                             | PPS           | U1CTSn        | PPS           | U1CTSn    | PPS           | I        | ST     | UART1 CTS Input                      |  |  |  |

| U1RTSn/<br>U1BCLK                                  | PPS           | U1RTSn        | PPS           | U1RTSn    | PPS           | 0        | DIG    | UART1 RTS Output/UART1 Baud<br>Clock |  |  |  |

| U1RX                                               | PPS           | U1RX          | PPS           | U1RX      | PPS           | I        | ST     | UART1 Receive                        |  |  |  |

| U1TX                                               | PPS           | U1TX          | PPS           | U1TX      | PPS           | 0        | DIG    | UART1 Transmit                       |  |  |  |

| Universal As                                       | ynchronou     | s Receiver Tr | ansmitter 2   | 2         |               |          |        |                                      |  |  |  |

| U2CTSn                                             | PPS           | U2CTSn        | PPS           | U2CTSn    | PPS           | I        | ST     | UART2 CTS Input                      |  |  |  |

| U2RTSn/<br>U2BCLK                                  | PPS           | U2RTSn        | PPS           | U2RTSn    | PPS           | 0        | DIG    | UART2 RTS Output/UART2 Baud Clock    |  |  |  |

| U2RX                                               | PPS           | U2RX          | PPS           | U2RX      | PPS           | I        | ST     | UART2 Receive                        |  |  |  |

| U2TX                                               | PPS           | U2TX          | PPS           | U2TX      | PPS           | 0        | DIG    | UART2 Transmit                       |  |  |  |

| Universal Asynchronous Receiver Transmitter 3      |               |               |               |           |               |          |        |                                      |  |  |  |

| U3CTSn                                             | PPS           | U3CTSn        | PPS           | U3CTSn    | PPS           | I        | ST     | UART3 CTS Input                      |  |  |  |

**Legend:** DIG = Digital input ST = Schmitt Trigger input with CMOS levels O = Output I = Input

PPS = Peripheral Pin Select

TABLE 2-9: UART1 THROUGH UART3 PINOUT DESCRIPTION (CONTINUED)

| PIC32M            | IZ W1         | WFI32E01/WFI32E03 |               | WFI32E02/WFI32E04 |               |          | Buffer |                                      |  |

|-------------------|---------------|-------------------|---------------|-------------------|---------------|----------|--------|--------------------------------------|--|

| Pin Name          | Pin<br>Number | Pin Name          | Pin<br>Number | Pin Name          | Pin<br>Number | Pin Type | Туре   | Description                          |  |

| U3RTSn/<br>U3BCLK | PPS           | U3RTSn            | PPS           | U3RTSn            | PPS           | 0        | DIG    | UART3 RTS Output/UART3 Baud<br>Clock |  |

| U3RX              | PPS           | U3RX              | PPS           | U3RX              | PPS           | I        | ST     | UART3 Receive                        |  |

| U3TX              | PPS           | U3TX              | PPS           | U3TX              | PPS           | 0        | DIG    | UART3 Transmit                       |  |

Legend: DIG = Digital input

ST = Schmitt Trigger input with CMOS levels

O = Output

I = Input

PPS = Peripheral Pin Select

TABLE 2-10: SPI1 (DEDICATED) PINOUT DESCRIPTION

| PIC32N       | /IZ W1                        | WFI32E01/WFI32E03 |               | WFI32E02/WFI32E04 |               |          | Buffer |                                      |  |  |  |

|--------------|-------------------------------|-------------------|---------------|-------------------|---------------|----------|--------|--------------------------------------|--|--|--|

| Pin Name     | Pin<br>Number                 | Pin Name          | Pin<br>Number | Pin Name          | Pin<br>Number | Pin Type | Туре   | Description                          |  |  |  |

| Serial Perip | Serial Peripheral Interface 1 |                   |               |                   |               |          |        |                                      |  |  |  |

|              |                               |                   |               |                   |               |          |        | SPI1 Synchronous Serial Clock        |  |  |  |

| SCK1         | B11                           | SCK1              | 21            | SCK1              | A20           | I/O      | DIG/ST | Input/Output                         |  |  |  |

| SDI1         | A13                           | SDI1              | 19            | SDI1              | A18           | I        | ST     | SPI1 Data In                         |  |  |  |

| SDO1         | B12                           | SDO1              | 23            | SDO1              | A21           | 0        | DIG    | SPI1 Data Out                        |  |  |  |

|              |                               |                   |               |                   |               |          |        | SPI1 Client Select/Chip Select/Frame |  |  |  |

| SS1/CS1      | A14                           | SS1/CS1           | 20            | SS1/CS1           | A19           | I/O      | DIG/ST | Sync (active-low)                    |  |  |  |

Legend:

DIG = Digital input

ST = Schmitt Trigger input with CMOS levels

O = Output

I = Input

# TABLE 2-11: SPI1 AND SPI 2 PINOUT DESCRIPTION

| PIC32I                        | VIZ W1        | WFI32E01 | WFI32E01/WFI32E03 |          | WFI32E02/WFI32E04 |          | Duffer         |                                                           |  |  |

|-------------------------------|---------------|----------|-------------------|----------|-------------------|----------|----------------|-----------------------------------------------------------|--|--|

| Pin Name                      | Pin<br>Number | Pin Name | Pin<br>Number     | Pin Name | Pin<br>Number     | Pin Type | Buffer<br>Type | Description                                               |  |  |

| Serial Peripheral Interface 1 |               |          |                   |          |                   |          |                |                                                           |  |  |

|                               |               |          |                   |          |                   |          |                | SPI1 Synchronous Serial Clock Input/                      |  |  |

| SCK1                          | B11           | SCK1     | 21                | SCK1     | A20               | I/O      | DIG/ST         | Output                                                    |  |  |

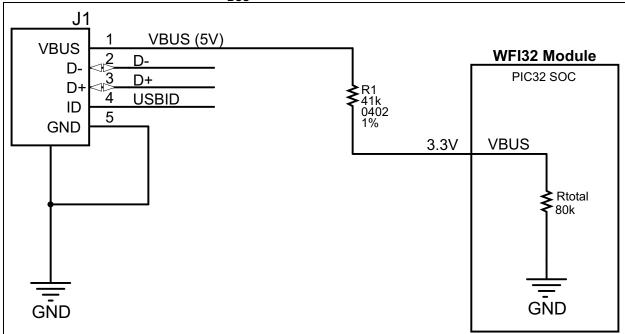

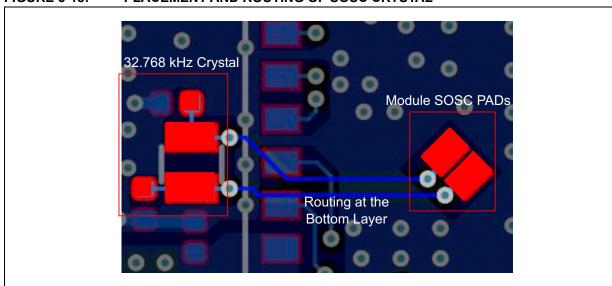

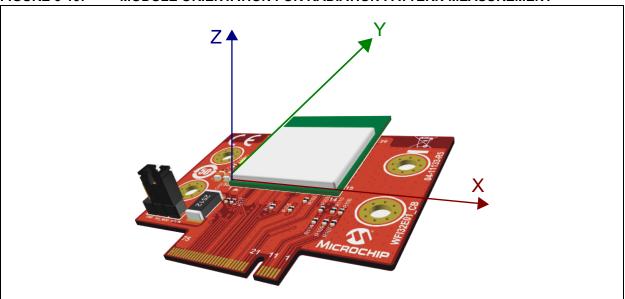

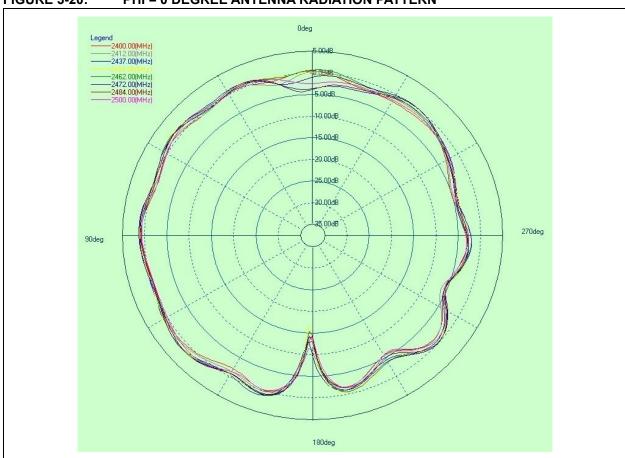

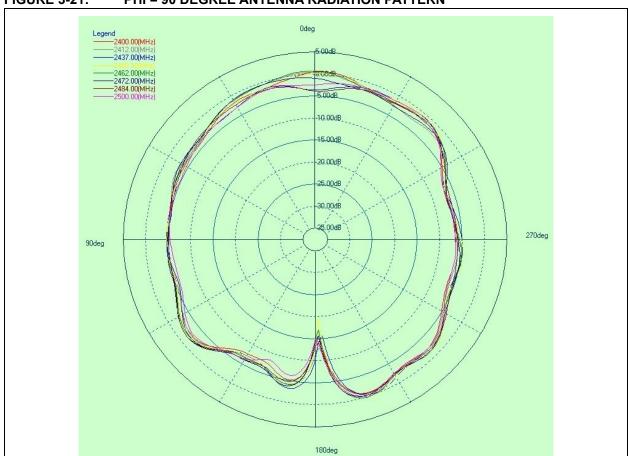

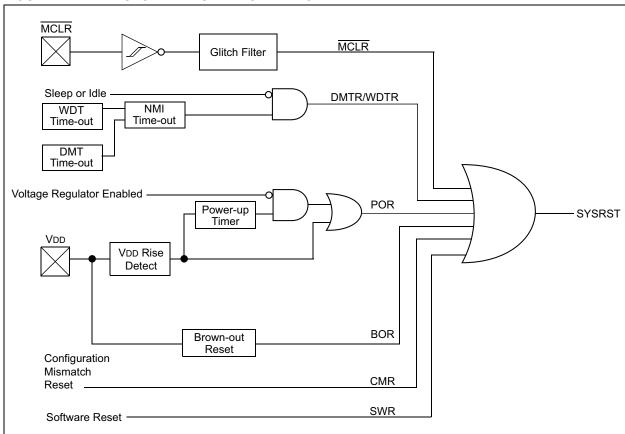

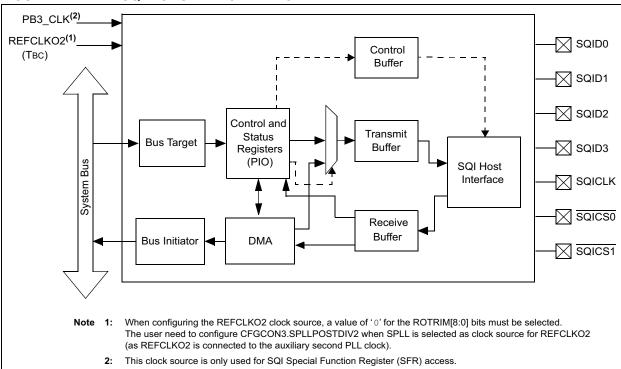

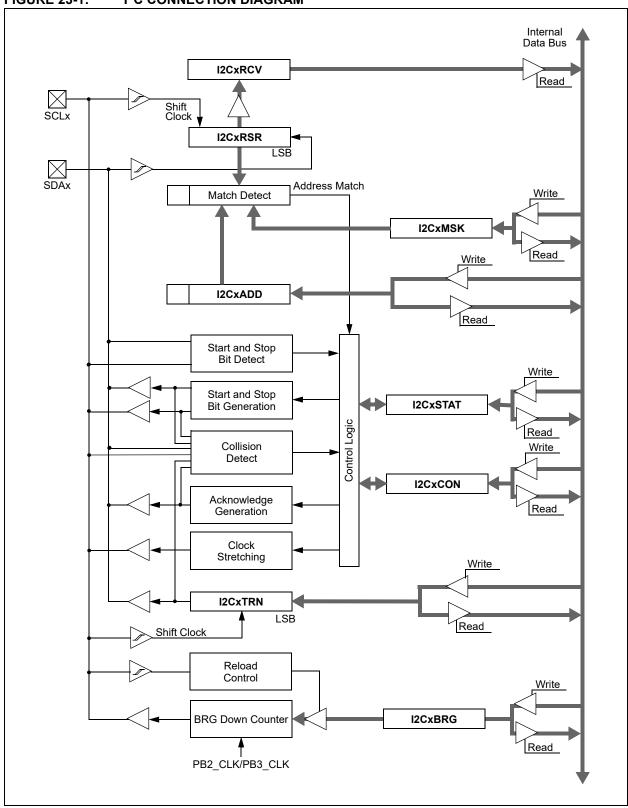

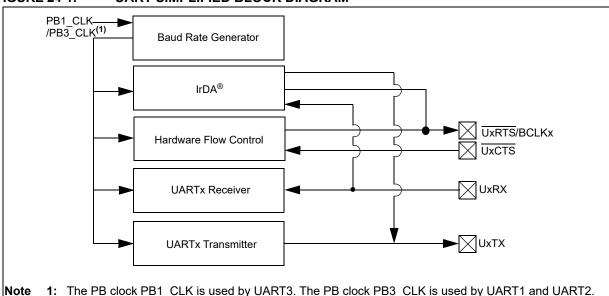

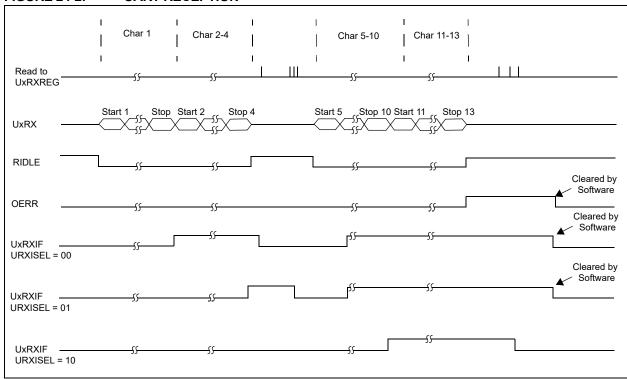

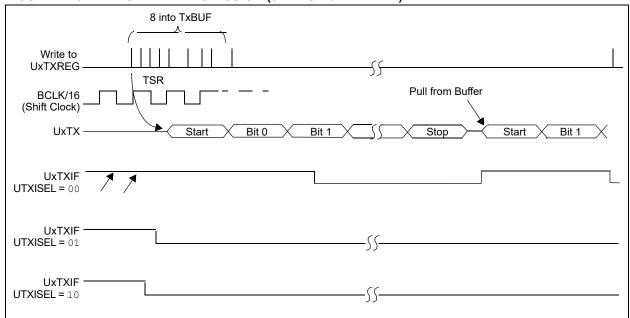

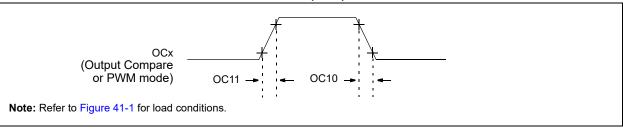

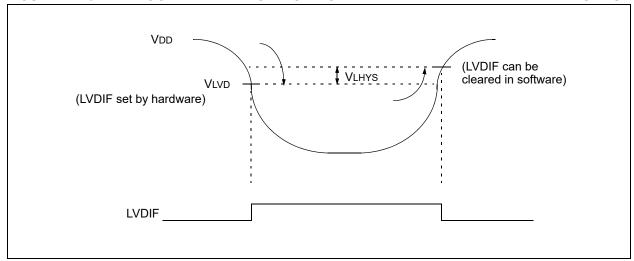

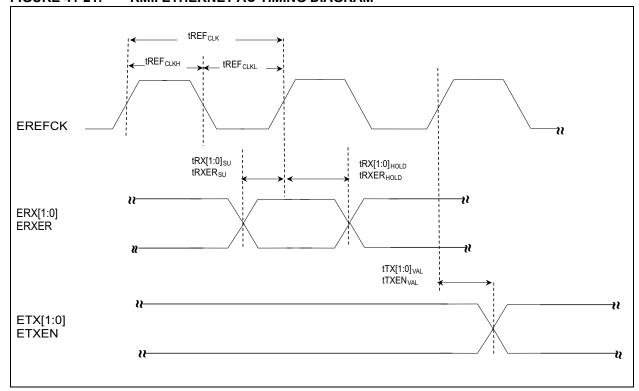

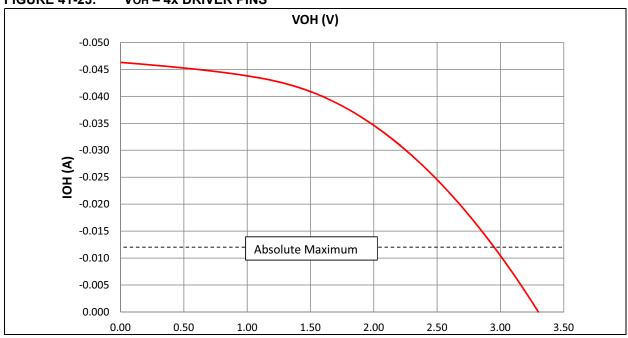

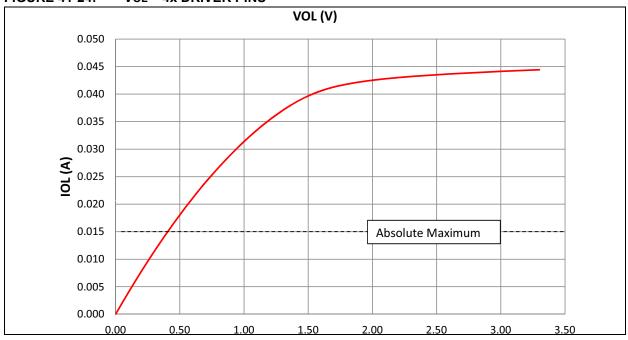

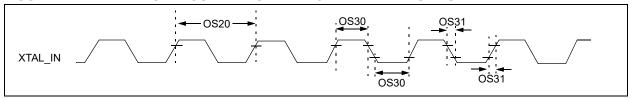

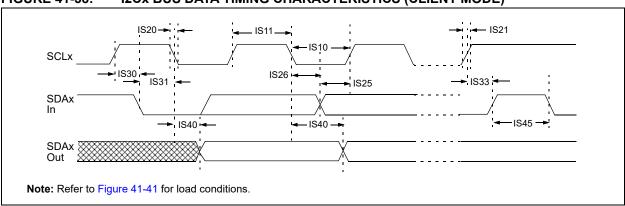

| SDI1                          | PPS           | SDI1     | PPS               | SDI1     | PPS               | I        | ST             | SPI1 Data In                                              |  |  |