# PIC24FJ256GA705 FAMILY

# 16-Bit General Purpose Microcontrollers with 256-Kbyte Flash and 16-Kbyte RAM in Low Pin Count Packages

#### **High-Performance CPU**

- Modified Harvard Architecture

- Up to 16 MIPS Operation @ 32 MHz

- 8 MHz Fast RC Internal Oscillator:

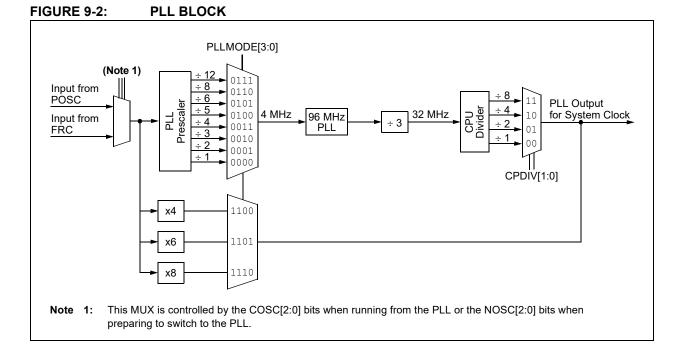

- 96 MHz PLL option

- Multiple clock divide options

- Fast start-up

- 17-Bit x 17-Bit Single-Cycle Hardware Fractional/Integer Multiplier

- 32-Bit by 16-Bit Hardware Divider

- 16-Bit x 16-Bit Working Register Array

- · C Compiler Optimized Instruction Set Architecture

- Two Address Generation Units for Separate Read and Write Addressing of Data Memory

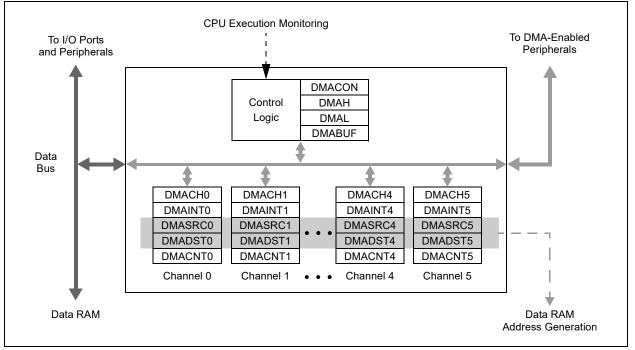

- Six-Channel DMA Controller

### **Analog Features**

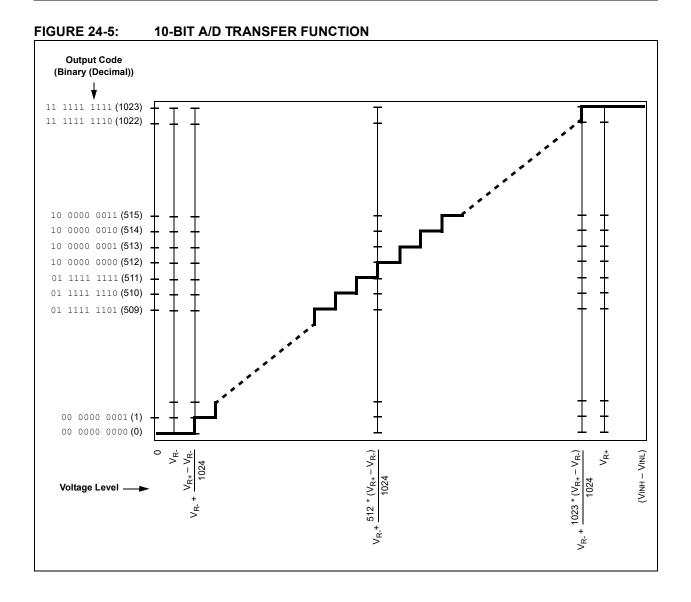

- Up to 14-Channel, Software-Selectable, 10/12-Bit Analog-to-Digital Converter:

- 12-bit, 200K samples/second conversion rate (single Sample-and-Hold)

- Sleep mode operation

- Charge pump for operating at lower AVDD

- Band gap reference input feature

- Windowed threshold compare feature

- Auto-scan feature

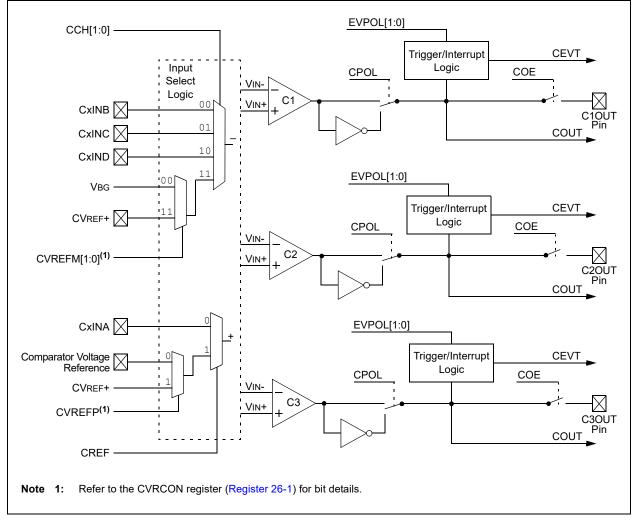

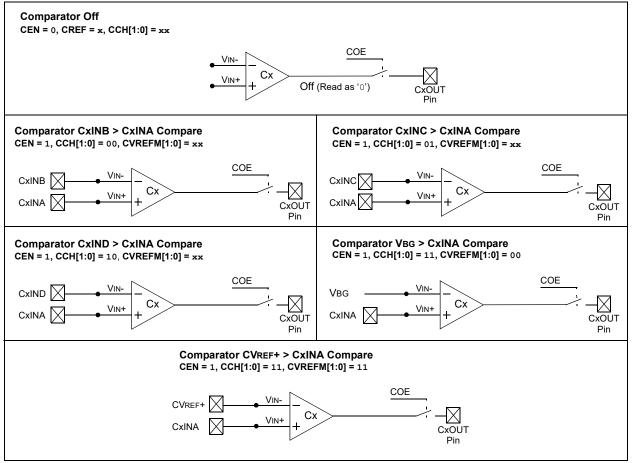

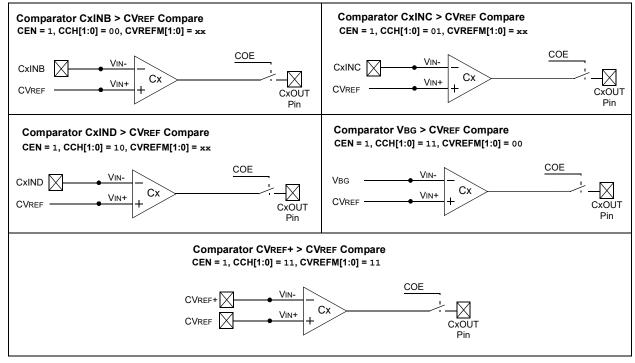

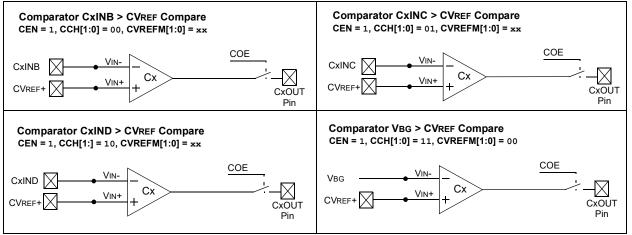

- · Three Analog Comparators with Input Multiplexing:

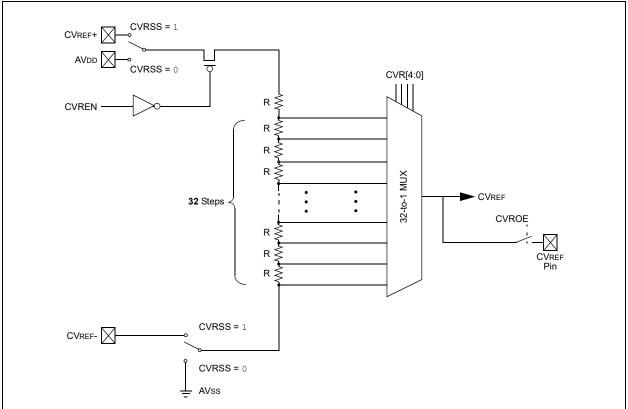

- Programmable reference voltage for comparators

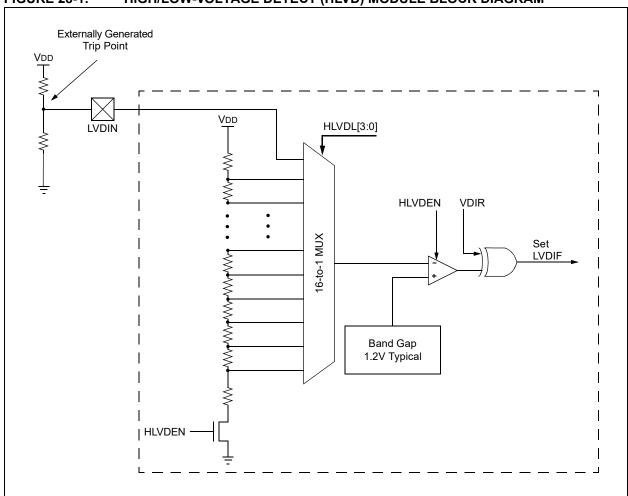

- LVD Interrupt Above/Below Programmable

VLVD Level

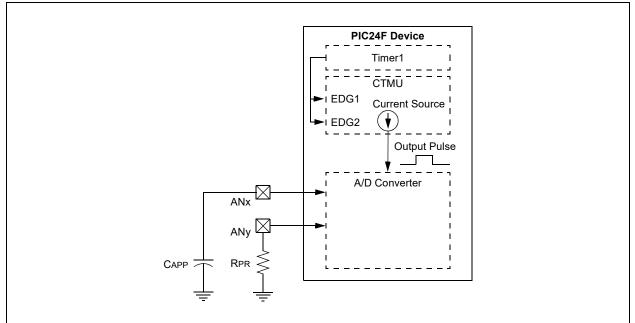

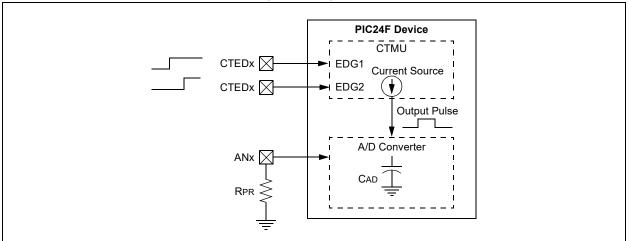

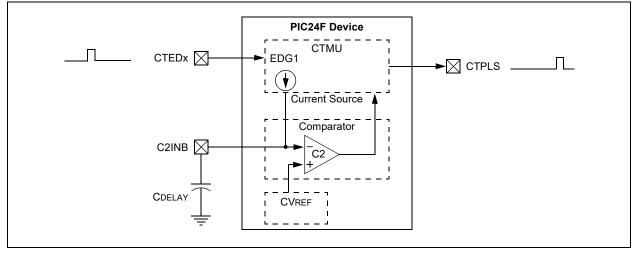

- Charge Time Measurement Unit (CTMU):

- Allows measurement of capacitance and time

- Operational in Sleep

#### **Low-Power Features**

- Sleep and Idle modes Selectively Shut Down Peripherals and/or Core for Substantial Power Reduction and Fast Wake-up

- Doze mode allows CPU to Run at a Lower Clock Speed than Peripherals

- Alternate Clock modes allow On-the-Fly Switching to a Lower Clock Speed for Selective Power Reduction

### **Special Microcontroller Features**

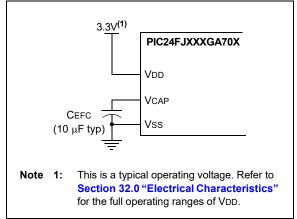

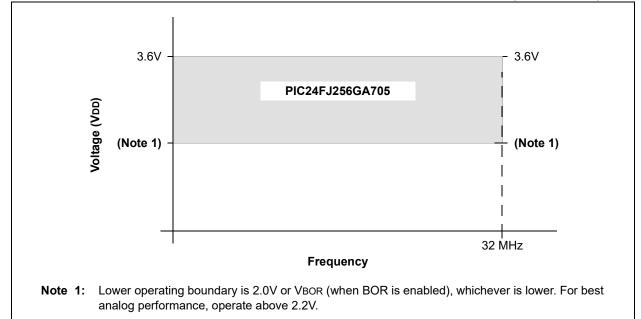

- Supply Voltage Range of 2.0V to 3.6V

- · Dual Voltage Regulators:

- 1.8V core regulator

- 1.2V regulator for Retention Sleep mode

- Operating Ambient Temperature Range of -40°C to +125°C

- ECC Flash Memory (256 Kbytes):

- Single Error Correction (SEC)

- Double Error Detection (DED)

- 10,000 erase/write cycle endurance, typical

- Data retention: 20 years minimum

- Self-programmable under software control

- 16-Kbyte SRAM

- · Programmable Reference Clock Output

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and In-Circuit Emulation (ICE) via 2 Pins

- JTAG Boundary Scan Support

- Fail-Safe Clock Monitor Operation:

- Detects clock failure and switches to on-chip, Low-Power RC (LPRC) Oscillator

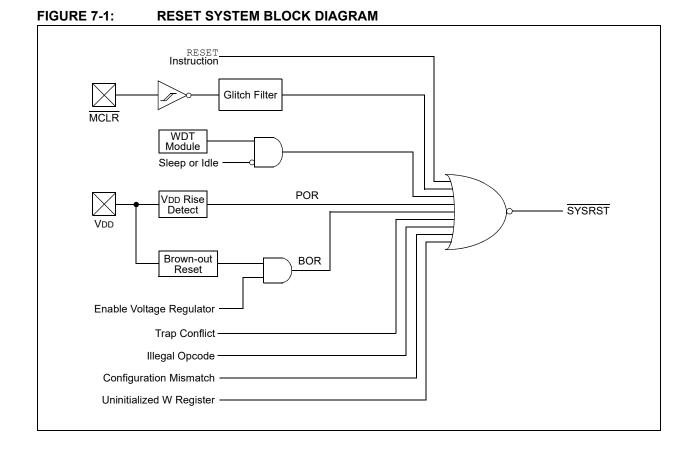

- Power-on Reset (POR), Brown-out Reset (BOR) and Oscillator Start-up Timer (OST)

- Programmable Low-Voltage Detect (LVD)

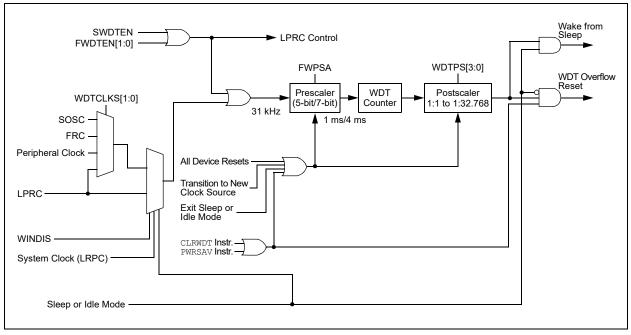

- Flexible Watchdog Timer (WDT) with its Own RC Oscillator for Reliable Operation

#### **Qualification and Class B Support**

- AEC-Q100 REVG (Grade 1 -40°C to +125°C)

- Class B Safety Library, IEC 60730

# **Peripheral Features**

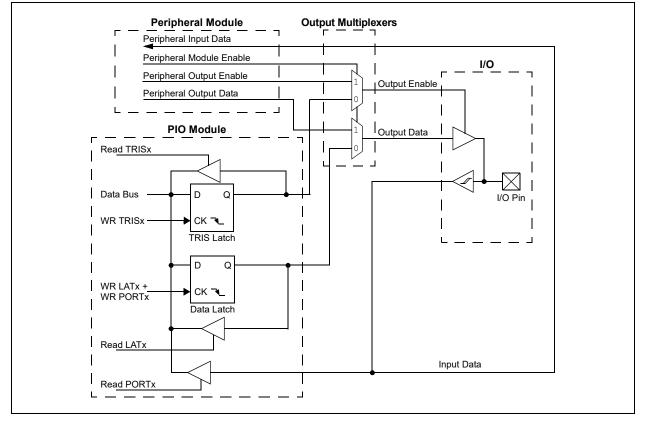

- High-Current Sink/Source 18 mA/18 mA on All I/O Pins

- Independent, Low-Power 32 kHz Timer Oscillator

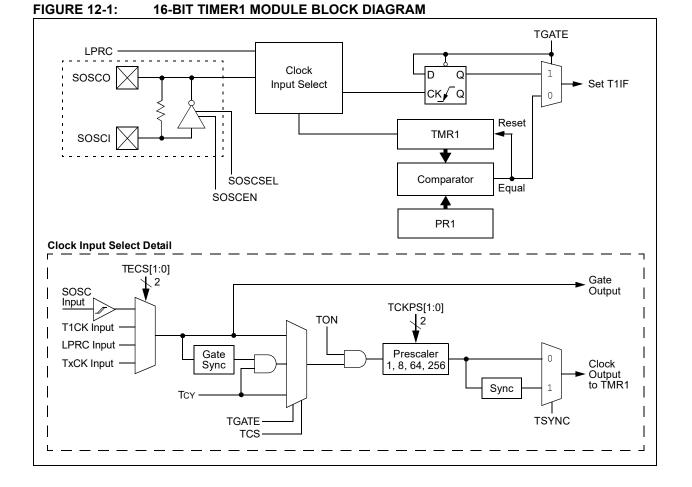

- Timer1: 16-Bit Timer/Counter with External Crystal Oscillator; Timer1 can Provide an A/D Trigger

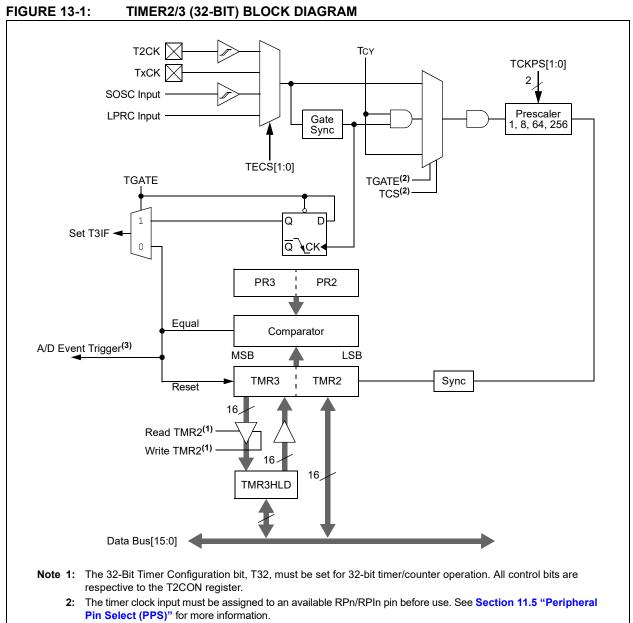

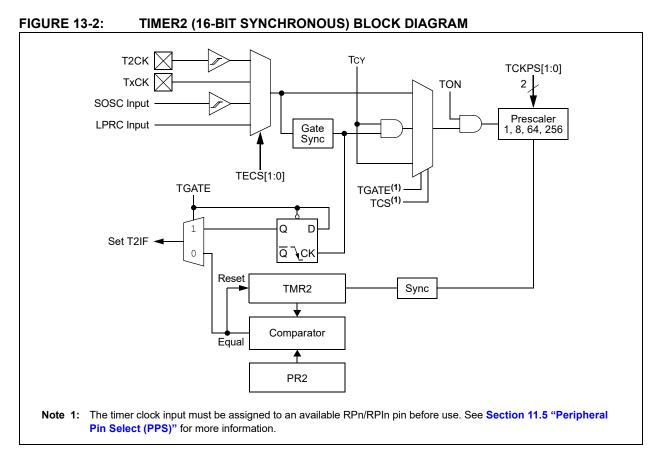

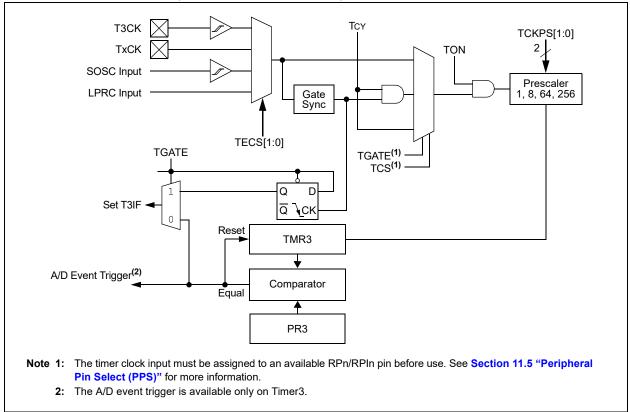

- Timer2,3: 16-Bit Timer/Counter, can Create 32-Bit Timer; Timer3 can Provide an A/D Trigger

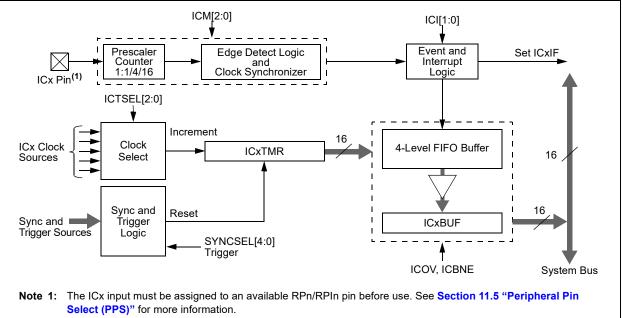

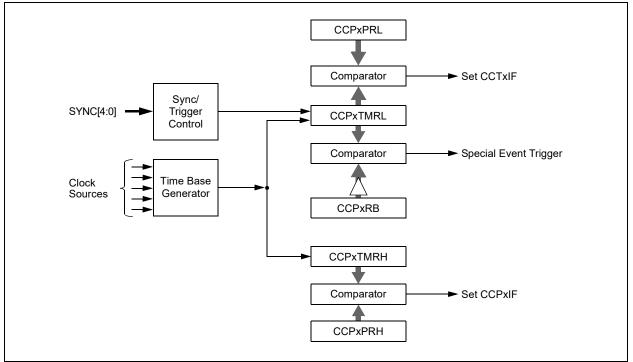

- Three Input Capture modules, Each with a 16-Bit Timer

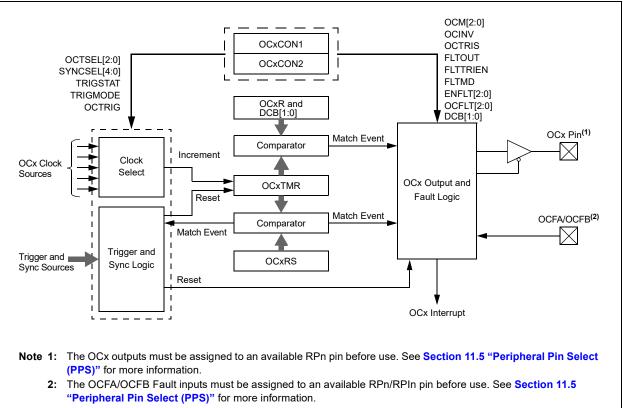

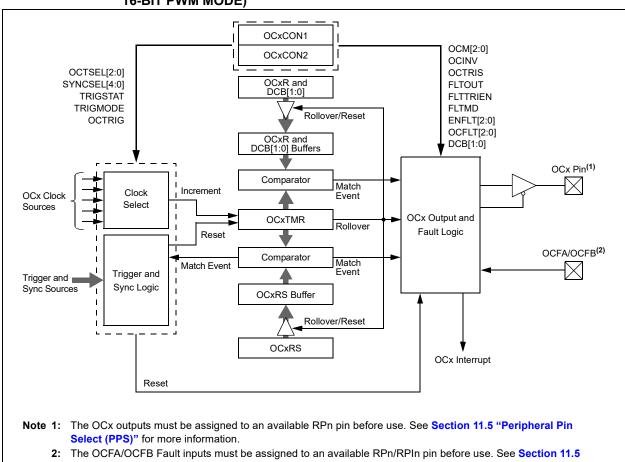

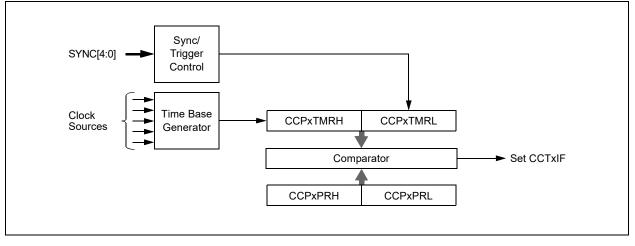

- Three Output Compare/PWM modules, Each with a 16-Bit Timer

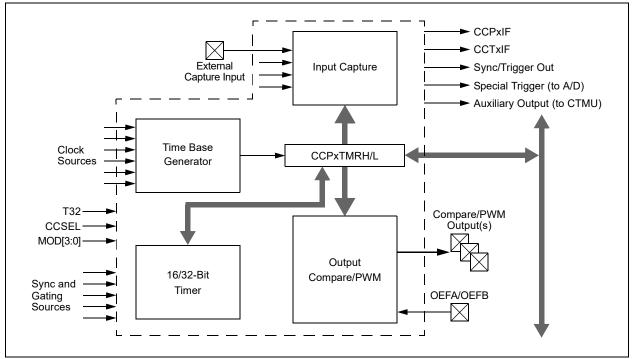

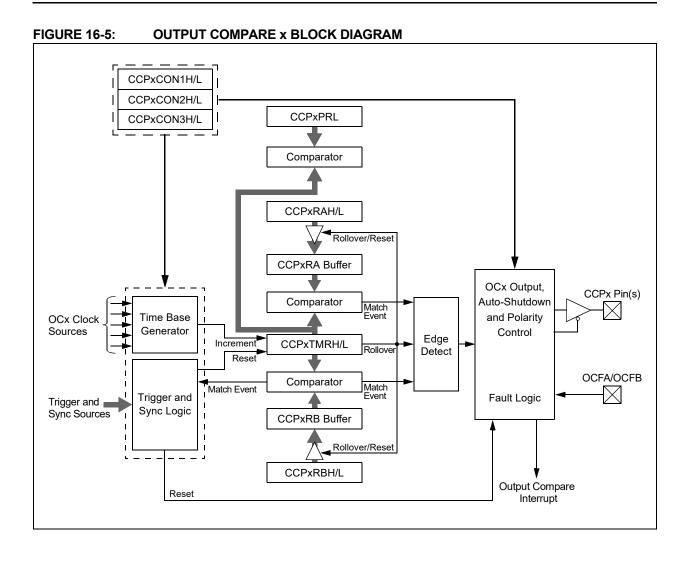

- Four MCCP modules, Each with a Dedicated 16/32-Bit Timer:

- One 6-output MCCP module

- Three 2-output MCCP modules

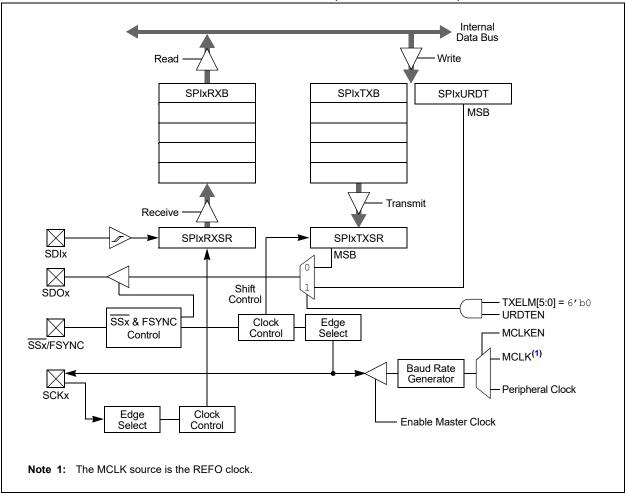

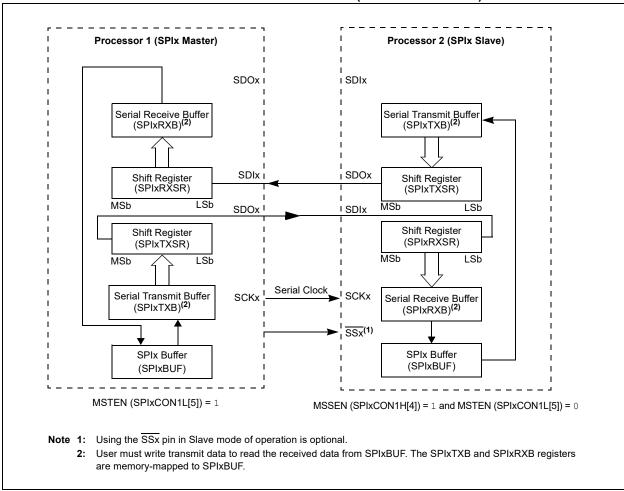

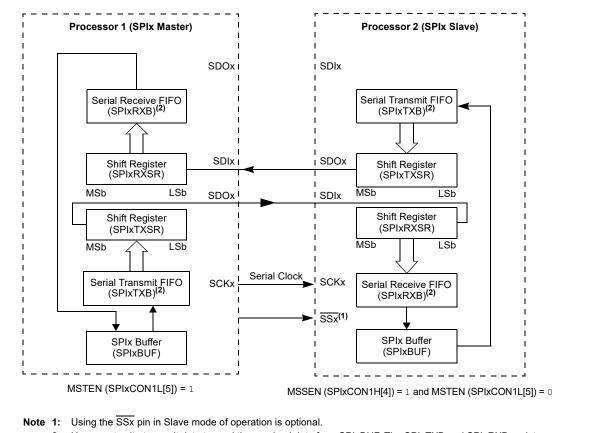

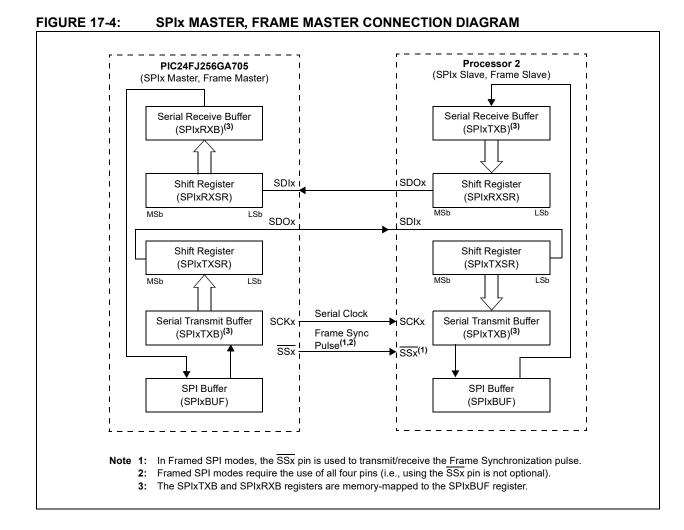

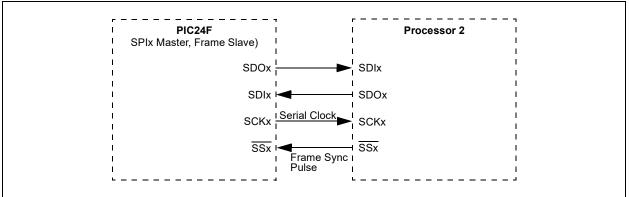

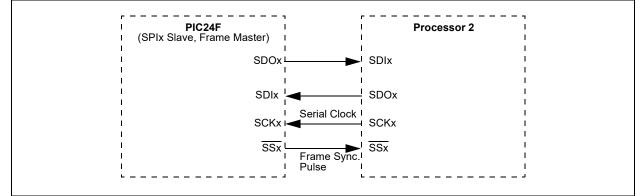

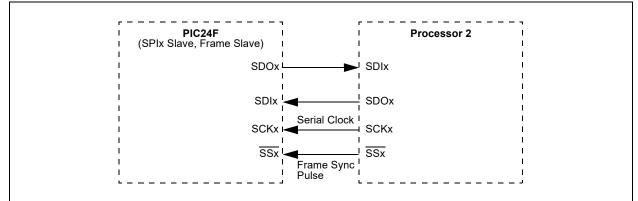

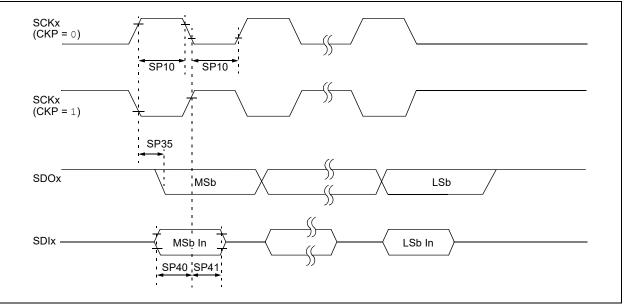

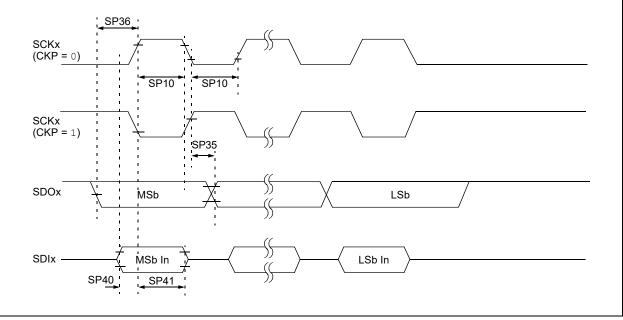

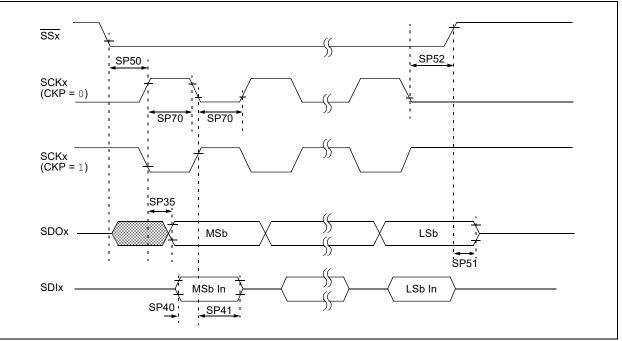

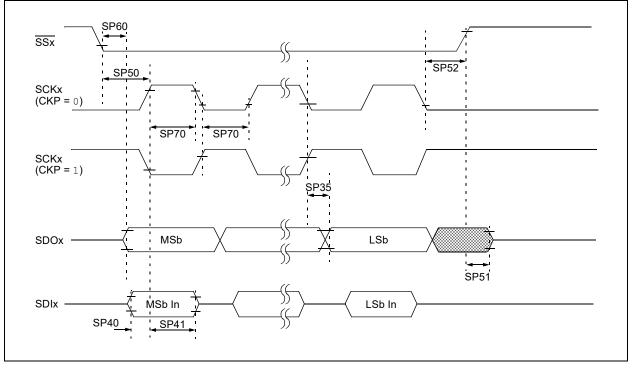

- Three Variable Widths, Synchronous Peripheral Interface (SPI) Ports on All Devices; Three Operation modes:

- Three-wire SPI (supports all four SPI modes)

- 8 by 16-bit or 8 by 8-bit FIFO

- I<sup>2</sup>S mode

#### TABLE 1: PIC24FJ256GA705 FAMILY DEVICES

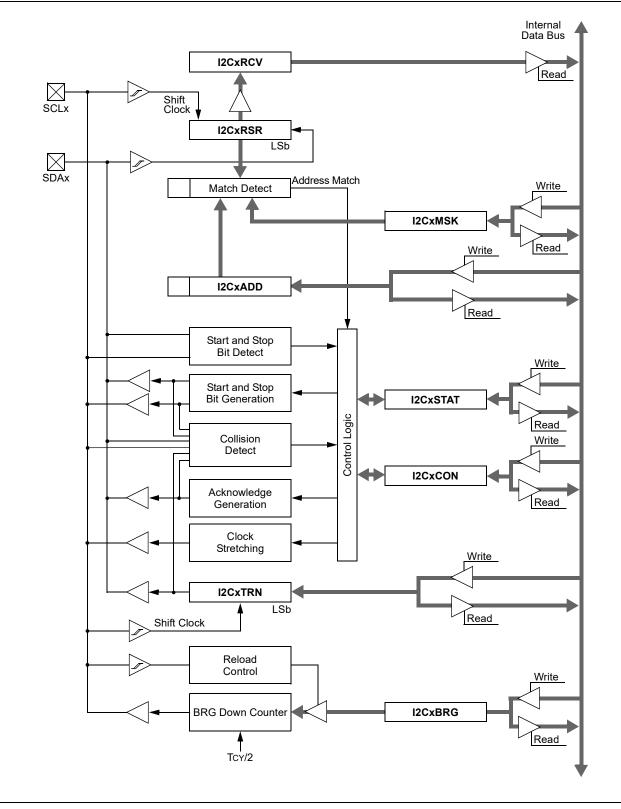

- Two I<sup>2</sup>C Masters and Slaves w/Address Masking, and IPMI Support

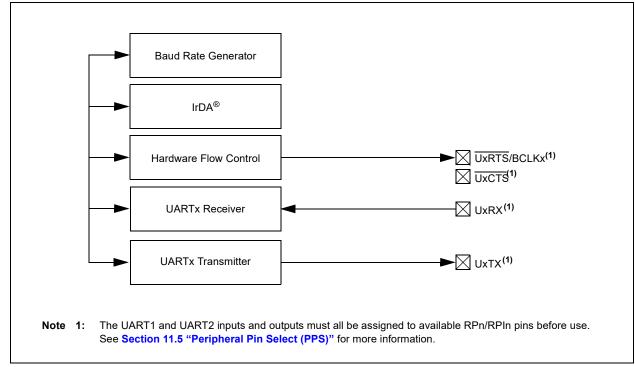

- Two UART modules:

- LIN/J2602 bus support (auto-wake-up, Auto-Baud Detect (ABD), Break character support)

- RS-232 and RS-485 support

- IrDA<sup>®</sup> mode (hardware encoder/decoder functions)

- · Five External Interrupt Pins

- Parallel Master Port/Enhanced Parallel Slave Port (PMP/EPSP), 8-Bit Data with External Programmable Control (polarity and protocol)

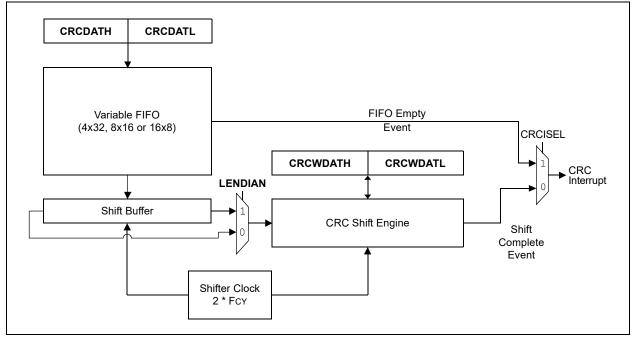

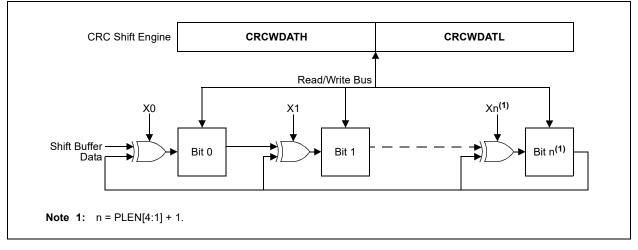

- Enhanced CRC module

- Reference Clock Output with Programmable

Divider

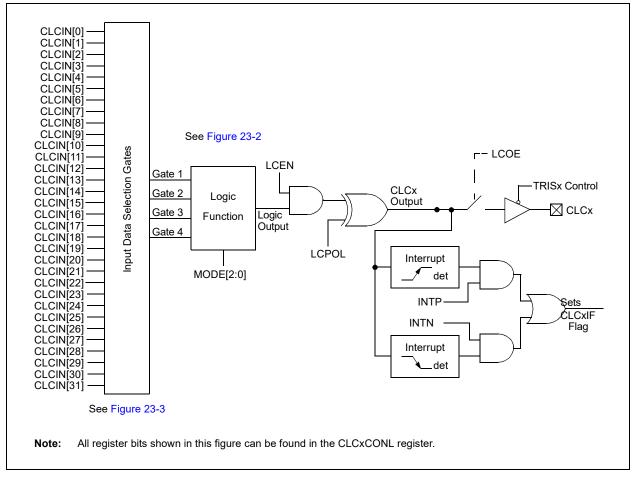

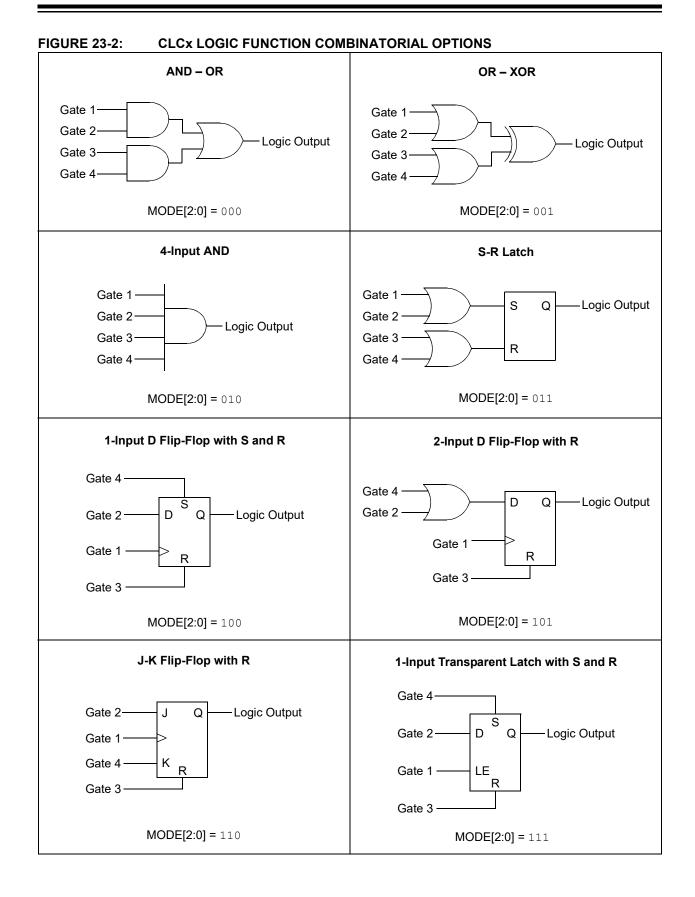

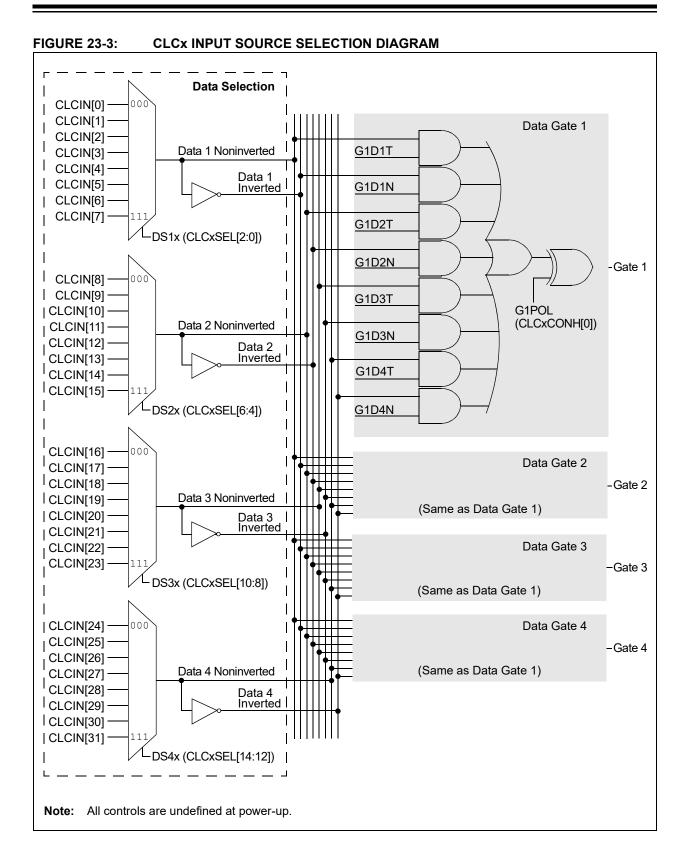

- Two Configurable Logic Cell (CLC) Blocks:

- Two inputs and one output, all mappable to peripherals or I/O pins

- AND/OR/XOR logic and D/JK flip-flop functions

- Peripheral Pin Select (PPS) with Independent I/O Mapping of Many Peripherals

|                 | Men                | nory            |      |      |              |                        |             |     |                        |           | Peri          | pher             | als                |                   |               |                          |     |      |      |

|-----------------|--------------------|-----------------|------|------|--------------|------------------------|-------------|-----|------------------------|-----------|---------------|------------------|--------------------|-------------------|---------------|--------------------------|-----|------|------|

| Device          | Program<br>(bytes) | SRAM<br>(bytes) | Pins | Old9 | DMA Channels | 10/12-Bit A/D Channels | Comparators | CRC | MCCP 6-Output/2-Output | IC/OC/PWM | 16-Bit Timers | I <sup>2</sup> C | Variable Width SPI | BULIN-USART/Irda® | CTMU Channels | EPMP (Address/Data Line) | CLC | RTCC | JTAG |

| PIC24FJ64GA705  | 64K                | 16K             | 48   | 40   | 6            | 14                     | 3           | Yes | 1/3                    | 3/3       | 3             | 2                | 3                  | 2                 | 13            | 10/8                     | 2   | Yes  | Yes  |

| PIC24FJ128GA705 | 128K               | 16K             | 48   | 40   | 6            | 14                     | 3           | Yes | 1/3                    | 3/3       | 3             | 2                | 3                  | 2                 | 13            | 10/8                     | 2   | Yes  | Yes  |

| PIC24FJ256GA705 | 256K               | 16K             | 48   | 40   | 6            | 14                     | 3           | Yes | 1/3                    | 3/3       | 3             | 2                | 3                  | 2                 | 13            | 10/8                     | 2   | Yes  | Yes  |

| PIC24FJ64GA704  | 64K                | 16K             | 44   | 36   | 6            | 14                     | 3           | Yes | 1/3                    | 3/3       | 3             | 2                | 3                  | 2                 | 13            | 10/8                     | 2   | Yes  | Yes  |

| PIC24FJ128GA704 | 128K               | 16K             | 44   | 36   | 6            | 14                     | 3           | Yes | 1/3                    | 3/3       | 3             | 2                | 3                  | 2                 | 13            | 10/8                     | 2   | Yes  | Yes  |

| PIC24FJ256GA704 | 256K               | 16K             | 44   | 36   | 6            | 14                     | 3           | Yes | 1/3                    | 3/3       | 3             | 2                | 3                  | 2                 | 13            | 10/8                     | 2   | Yes  | Yes  |

| PIC24FJ64GA702  | 64K                | 16K             | 28   | 22   | 6            | 10                     | 3           | Yes | 1/3                    | 3/3       | 3             | 2                | 3                  | 2                 | 12            | No                       | 2   | Yes  | Yes  |

| PIC24FJ128GA702 | 128K               | 16K             | 28   | 22   | 6            | 10                     | 3           | Yes | 1/3                    | 3/3       | 3             | 2                | 3                  | 2                 | 12            | No                       | 2   | Yes  | Yes  |

| PIC24FJ256GA702 | 256K               | 16K             | 28   | 22   | 6            | 10                     | 3           | Yes | 1/3                    | 3/3       | 3             | 2                | 3                  | 2                 | 12            | No                       | 2   | Yes  | Yes  |

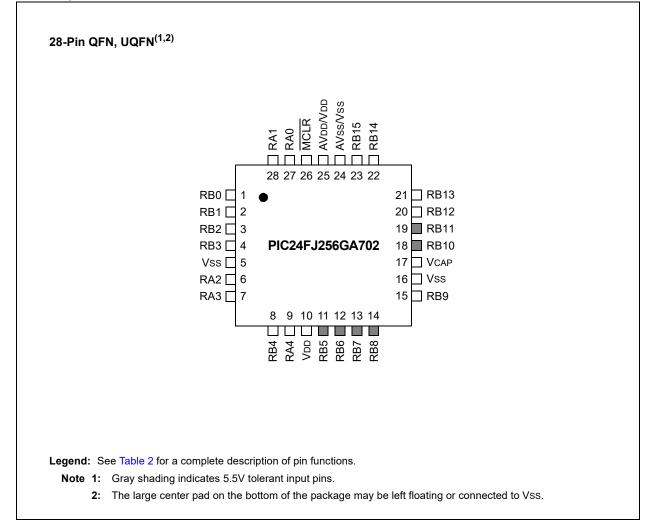

### Pin Diagrams (PIC24FJ256GA702 Devices)

#### TABLE 2: COMPLETE PIN FUNCTION DESCRIPTIONS (PIC24FJ256GA702 QFN, UQFN)

| Pin | Function                                    | Pin | Function                                            |

|-----|---------------------------------------------|-----|-----------------------------------------------------|

| 1   | PGD1/AN2/CTCMP/C2INB/ <b>RP0</b> /RB0       | 15  | TDO/C1INC/C2INC/C3INC/TMPRN/RP9/SDA1/T1CK/CTED4/RB9 |

| 2   | PGC1/AN1-/AN3/C2INA/ <b>RP1</b> /CTED12/RB1 | 16  | Vss                                                 |

| 3   | AN4/C1INB/RP2/SDA2/CTED13/RB2               | 17  | VCAP                                                |

| 4   | AN5/C1INA/RP3/SCL2/CTED8/RB3                | 18  | PGD2/TDI/ <b>RP10</b> /OCM1C/CTED11/RB10            |

| 5   | Vss                                         | 19  | PGC2/TMS/REFI1/RP11/CTED9/RB11                      |

| 6   | OSCI/CLKI/C1IND/RA2                         | 20  | AN8/LVDIN/ <b>RP12</b> /RB12                        |

| 7   | OSCO/CLKO/C2IND/RA3                         | 21  | AN7/C1INC/ <b>RP13</b> /OCM1D/CTPLS/RB13            |

| 8   | SOSCI/ <b>RP4</b> /RB4                      | 22  | CVREF/AN6/C3INB/ <b>RP14</b> /CTED5/RB14            |

| 9   | SOSCO/PWRLCLK/RA4                           | 23  | AN9/C3INA/ <b>RP15</b> /CTED6/RB15                  |

| 10  | VDD                                         | 24  | AVss/Vss                                            |

| 11  | PGD3/ <b>RP5</b> /ASDA1/OCM1E/RB5           | 25  | AVDD/VDD                                            |

| 12  | PGC3/ <b>RP6</b> /ASCL1/OCM1F/RB6           | 26  | MCLR                                                |

| 13  | RP7/OCM1A/CTED3/INT0/RB7                    | 27  | VREF+/CVREF+/AN0/C3INC/RP26/CTED1/RA0               |

| 14  | TCK/RP8/SCL1/OCM1B/CTED10/RB8               | 28  | VREF-/CVREF-/AN1/C3IND/RP27/CTED2/RA1               |

Legend: RPn represents remappable pins for Peripheral Pin Select (PPS) functions.

# Pin Diagrams (PIC24FJ256GA702 Devices)

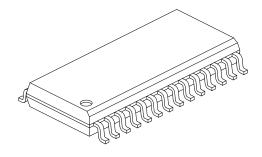

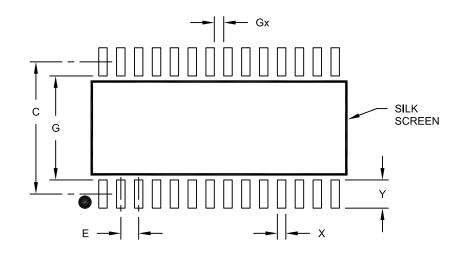

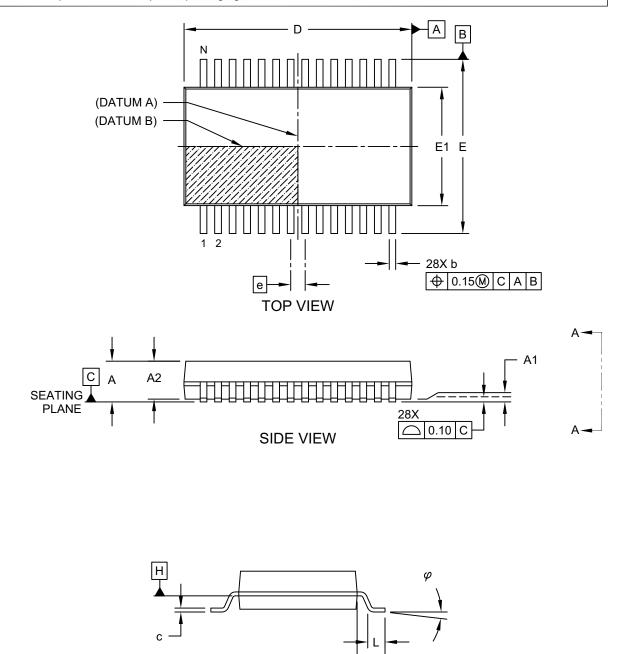

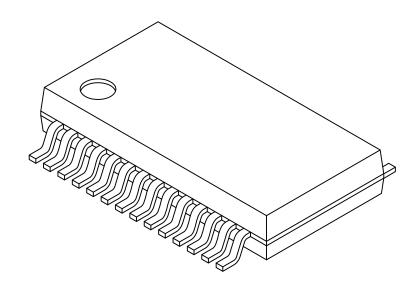

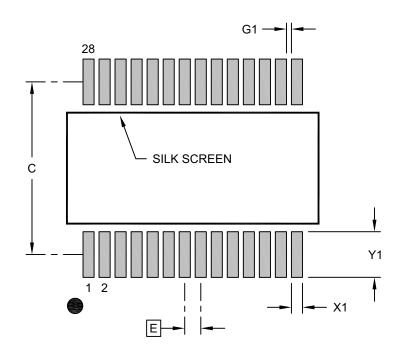

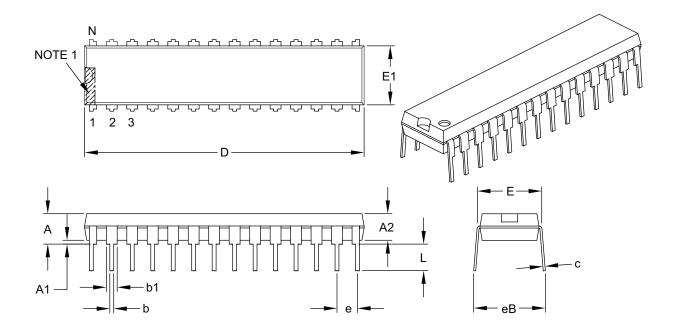

28-Pin SOIC, SSOP, SPDIP

**Legend:** See Table 3 for a complete description of pin functions. **Note:** Gray shading indicates 5.5V tolerant input pins.

#### TABLE 3: COMPLETE PIN FUNCTION DESCRIPTIONS (PIC24FJ256GA702 SOIC, SSOP, SPDIP)

| Pin | Function                                       | Pin | Function                                            |

|-----|------------------------------------------------|-----|-----------------------------------------------------|

| 1   | MCLR                                           | 15  | PGC3/ <b>RP6</b> /ASCL1/OCM1F/RB6                   |

| 2   | VREF+/CVREF+/AN0/C3INC/RP26/CTED1/RA0          | 16  | RP7/OCM1A/CTED3/INT0/RB7                            |

| 3   | VREF-/CVREF-/AN1/C3IND/ <b>RP27</b> /CTED2/RA1 | 17  | TCK/RP8/SCL1/OCM1B/CTED10/RB8                       |

| 4   | PGD1/AN2/CTCMP/C2INB/ <b>RP0</b> /RB0          | 18  | TDO/C1INC/C2INC/C3INC/TMPRN/RP9/SDA1/T1CK/CTED4/RB9 |

| 5   | PGC1/AN1-/AN3/C2INA/ <b>RP1</b> /CTED12/RB1    | 19  | Vss                                                 |

| 6   | AN4/C1INB/ <b>RP2</b> /SDA2/CTED13/RB2         | 20  | VCAP                                                |

| 7   | AN5/C1INA/RP3/SCL2/CTED8/RB3                   | 21  | PGD2/TDI/ <b>RP10</b> /OCM1C/CTED11/RB10            |

| 8   | Vss                                            | 22  | PGC2/TMS/REFI1/RP11/CTED9/RB11                      |

| 9   | OSCI/CLKI/C1IND/RA2                            | 23  | AN8/LVDIN/ <b>RP12</b> /RB12                        |

| 10  | OSCO/CLKO/C2IND/RA3                            | 24  | AN7/C1INC/RP13/OCM1D/CTPLS/RB13                     |

| 11  | SOSCI/ <b>RP4</b> /RB4                         | 25  | CVREF/AN6/C3INB/RP14/CTED5/RB14                     |

| 12  | SOSCO/PWRLCLK/RA4                              | 26  | AN9/C3INA/ <b>RP15</b> /CTED6/RB15                  |

| 13  | VDD                                            | 27  | AVss/Vss                                            |

| 14  | PGD3/ <b>RP5</b> /ASDA1/OCM1E/RB5              | 28  | AVdd/Vdd                                            |

Legend: RPn represents remappable pins for Peripheral Pin Select (PPS) functions.

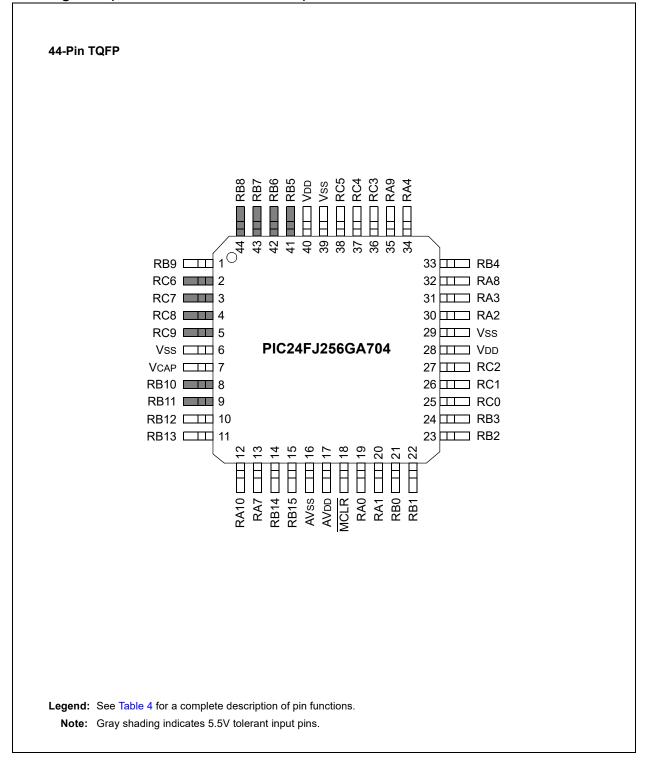

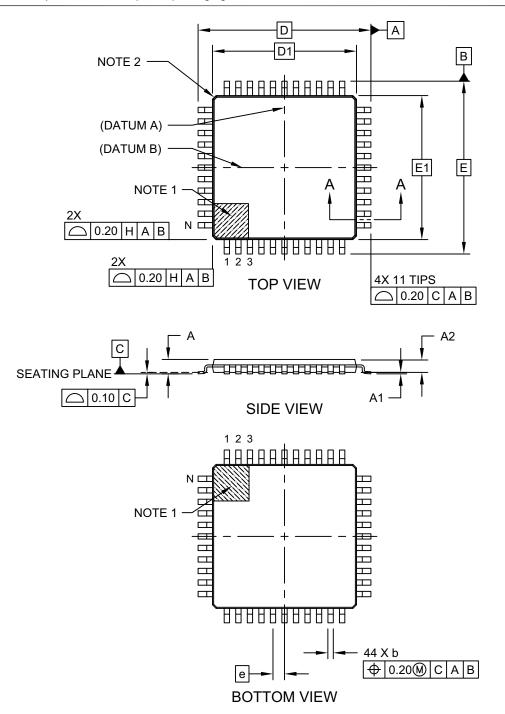

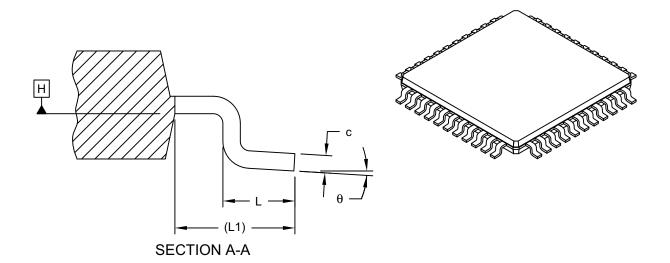

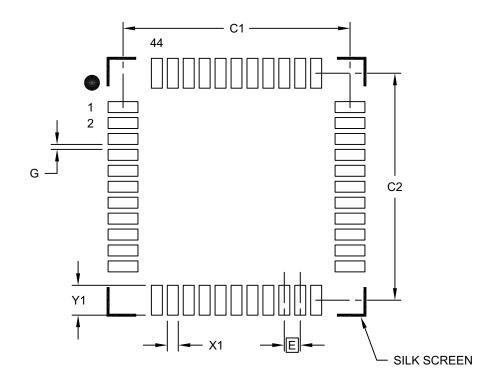

#### Pin Diagrams (PIC24FJ256GA704 Devices)

| Pin | Function                                             | Pin | Function                               |

|-----|------------------------------------------------------|-----|----------------------------------------|

| 1   | C1INC/C2INC/C3INC/TMPRN/RP9/SDA1/T1CK/CTED4/PMD3/RB9 | 23  | AN4/C1INB/ <b>RP2</b> /SDA2/CTED13/RB2 |

| 2   | RP22/PMA1/PMALH/RC6                                  | 24  | AN5/C1INA/ <b>RP3</b> /SCL2/CTED8/RB3  |

| 3   | RP23/PMA0/PMALL/RC7                                  | 25  | AN10/ <b>RP16</b> /PMBE1/RC0           |

| 4   | RP24/PMA5/RC8                                        | 26  | AN11/RP17/PMA15/PMCS2/RC1              |

| 5   | RP25/CTED7/PMA6/RC9                                  | 27  | AN12/ <b>RP18</b> /PMACK1/RC2          |

| 6   | Vss                                                  | 28  | Vdd                                    |

| 7   | VCAP                                                 | 29  | Vss                                    |

| 8   | PGD2/RP10/OCM1C/CTED11/PMD2/RB10                     | 30  | OSCI/CLKI/C1IND/RA2                    |

| 9   | PGC2/REFI1/RP11/CTED9/PMD1/RB11                      | 31  | OSCO/CLKO/C2IND/RA3                    |

| 10  | AN8/LVDIN/ <b>RP12</b> /PMD0/RB12                    | 32  | TDO/PMA8/RA8                           |

| 11  | AN7/C1INC/ <b>RP13</b> /OCM1D/CTPLS/PMRD/PMWR/RB13   | 33  | SOSCI/ <b>RP4</b> /RB4                 |

| 12  | TMS/ <b>RP28</b> /PMA2/PMALU/RA10                    | 34  | SOSCO/PWRLCLK/RA4                      |

| 13  | TCK/PMA7/RA7                                         | 35  | TDI/PMA9/RA9                           |

| 14  | CVREF/AN6/C3INB/RP14/CTED5/PMWR/PMENB/RB14           | 36  | AN13/ <b>RP19</b> /PMBE0/RC3           |

| 15  | AN9/C3INA/ <b>RP15</b> /CTED6/PMA14/PMCS/PMCS1/RB15  | 37  | RP20/PMA4/RC4                          |

| 16  | AVss                                                 | 38  | RP21/PMA3/RC5                          |

| 17  | AVDD                                                 | 39  | Vss                                    |

| 18  | MCLR                                                 | 40  | Vdd                                    |

| 19  | VREF+/CVREF+/AN0/C3INC/RP26/CTED1/RA0                | 41  | PGD3/ <b>RP5</b> /ASDA1/OCM1E/PMD7/RB5 |

| 20  | VREF-/CVREF-/AN1/C3IND/ <b>RP27</b> /CTED2/RA1       | 42  | PGC3/ <b>RP6</b> /ASCL1/OCM1F/PMD6/RB6 |

| 21  | PGD1/AN2/CTCMP/C2INB/ <b>RP0</b> /RB0                | 43  | RP7/OCM1A/CTED3/PMD5/INT0/RB7          |

| 22  | PGC1/AN1-/AN3/C2INA/ <b>RP1</b> /CTED12/RB1          | 44  | RP8/SCL1/OCM1B/CTED10/PMD4/RB8         |

# TABLE 4: COMPLETE PIN FUNCTION DESCRIPTIONS (PIC24FJ256GA704 TQFP)

Legend: RPn represents remappable pins for Peripheral Pin Select (PPS) functions.

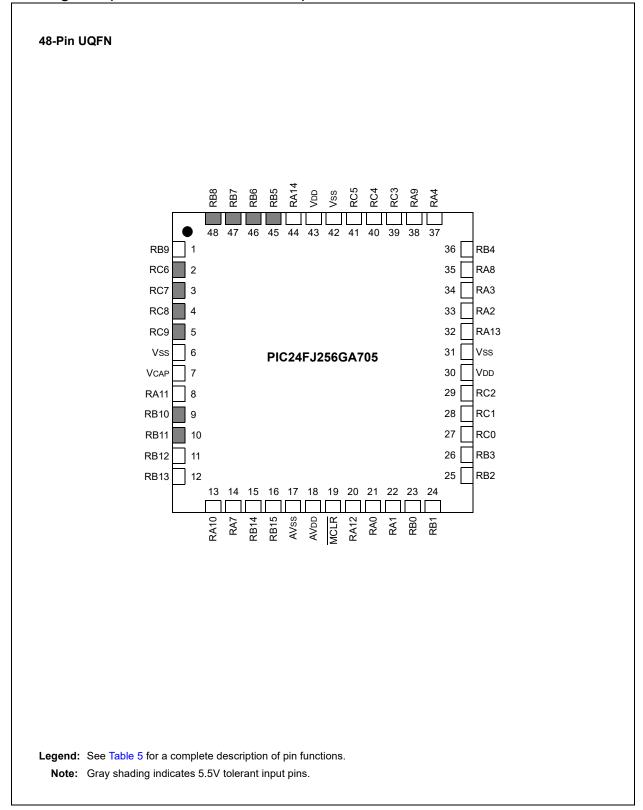

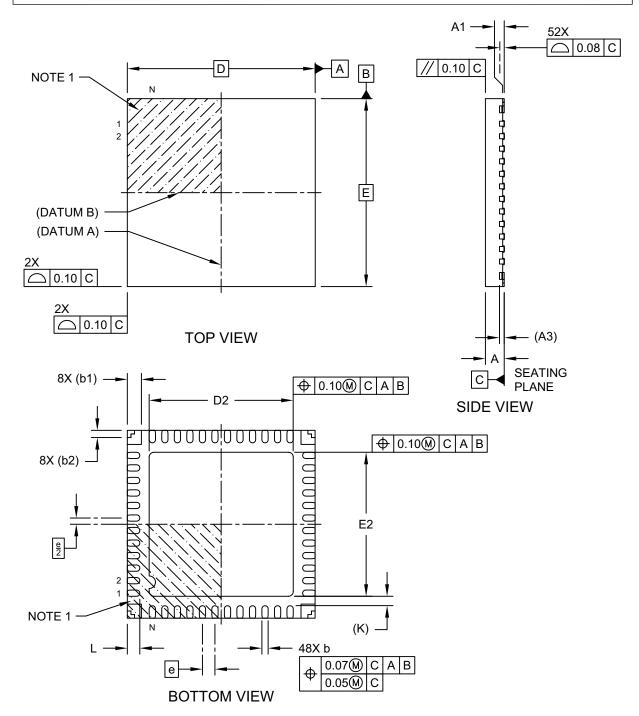

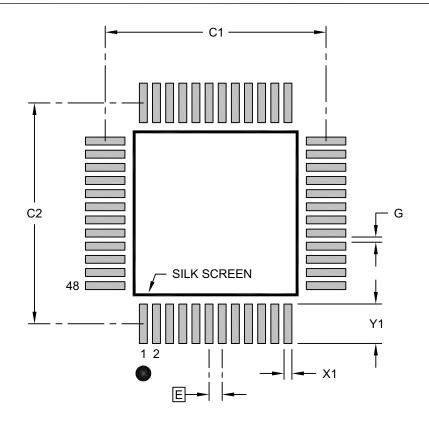

#### Pin Diagrams (PIC24FJ256GA705 Devices)

| Pin | Function                                             | Pin | Function                               |

|-----|------------------------------------------------------|-----|----------------------------------------|

| 1   | C1INC/C2INC/C3INC/TMPRN/RP9/SDA1/T1CK/CTED4/PMD3/RB9 | 25  | AN4/C1INB/ <b>RP2</b> /SDA2/CTED13/RB2 |

| 2   | RP22/PMA1/PMALH/RC6                                  | 26  | AN5/C1INA/RP3/SCL2/CTED8/RB3           |

| 3   | RP23/PMA0/PMALL/RC7                                  | 27  | AN10/ <b>RP16</b> /PMBE1/RC0           |

| 4   | RP24/PMA5/RC8                                        | 28  | AN11/ <b>RP17</b> /PMA15/PMCS2/RC1     |

| 5   | RP25/CTED7/PMA6/RC9                                  | 29  | AN12/RP18/PMACK1/RC2                   |

| 6   | Vss                                                  | 30  | Vdd                                    |

| 7   | VCAP                                                 | 31  | Vss                                    |

| 8   | RPI29/RA11                                           | 32  | RPI31/RA13                             |

| 9   | PGD2/RP10/OCM1C/CTED11/PMD2/RB10                     | 33  | OSCI/CLKI/C1IND/RA2                    |

| 10  | PGC2/REFI1/RP11/CTED9/PMD1/RB11                      | 34  | OSCO/CLKO/C2IND/RA3                    |

| 11  | AN8/LVDIN/RP12/PMD0/RB12                             | 35  | TDO/PMA8/RA8                           |

| 12  | AN7/C1INC/ <b>RP13</b> /OCM1D/CTPLS/PMRD/PMWR/RB13   | 36  | SOSCI/ <b>RP4</b> /RB4                 |

| 13  | TMS/RP28/PMA2/PMALU/RA10                             | 37  | SOSCO/PWRLCLK/RA4                      |

| 14  | TCK/PMA7/RA7                                         | 38  | TDI/PMA9/RA9                           |

| 15  | CVREF/AN6/C3INB/RP14/CTED5/PMWR/PMENB/RB14           | 39  | AN13/ <b>RP19</b> /PMBE0/RC3           |

| 16  | AN9/C3INA/RP15/CTED6/PMA14/PMCS/PMCS1/RB15           | 40  | RP20/PMA4/RC4                          |

| 17  | AVss                                                 | 41  | RP21/PMA3/RC5                          |

| 18  | AVdd                                                 | 42  | Vss                                    |

| 19  | MCLR                                                 | 43  | VDD                                    |

| 20  | RPI30/RA12                                           | 44  | RPI32/RA14                             |

| 21  | VREF+/CVREF+/AN0/C3INC/RP26/CTED1/RA0                | 45  | PGD3/ <b>RP5</b> /ASDA1/OCM1E/PMD7/RB5 |

| 22  | VREF-/CVREF-/AN1/C3IND/RP27/CTED2/RA1                | 46  | PGC3/ <b>RP6</b> /ASCL1/OCM1F/PMD6/RB6 |

| 23  | PGD1/AN2/CTCMP/C2INB/ <b>RP0</b> /RB0                | 47  | RP7/OCM1A/CTED3/PMD5/INT0/RB7          |

| 24  | PGC1/AN1-/AN3/C2INA/ <b>RP1</b> /CTED12/RB1          | 48  | RP8/SCL1/OCM1B/CTED10/PMD4/RB8         |

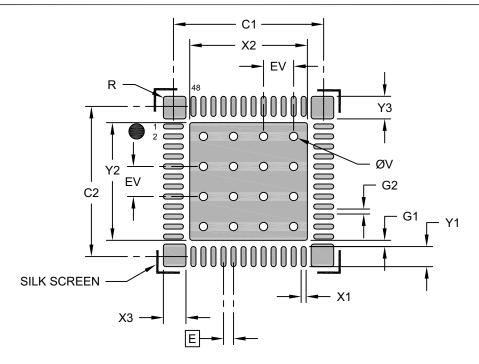

# TABLE 5: COMPLETE PIN FUNCTION DESCRIPTIONS (PIC24FJ256GA705 UQFN)

Legend: RPn and RPIn represent remappable pins for Peripheral Pin Select (PPS) functions.

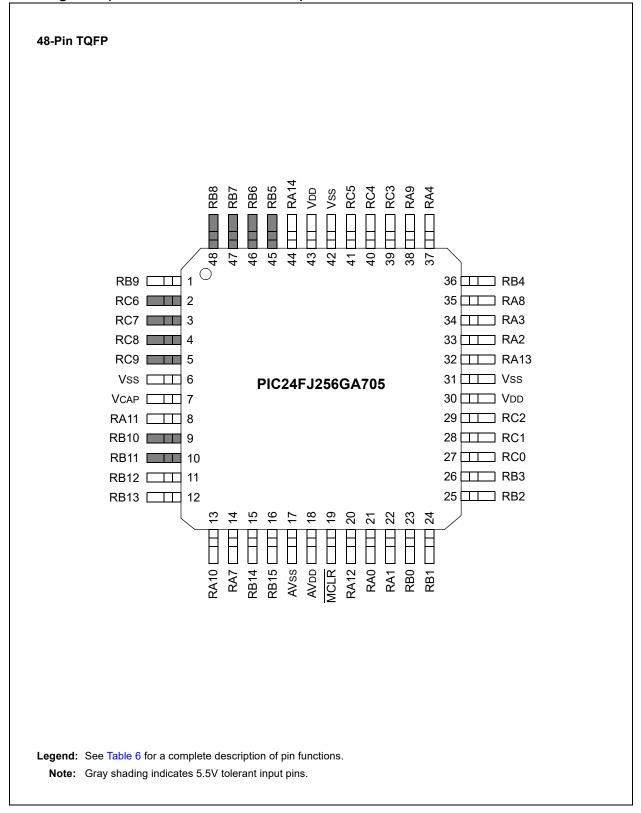

## Pin Diagrams (PIC24FJ256GA705 Devices)

| Pin | Function                                             | Pin | Function                               |

|-----|------------------------------------------------------|-----|----------------------------------------|

| 1   | C1INC/C2INC/C3INC/TMPRN/RP9/SDA1/T1CK/CTED4/PMD3/RB9 | 25  | AN4/C1INB/ <b>RP2</b> /SDA2/CTED13/RB2 |

| 2   | RP22/PMA1/PMALH/RC6                                  | 26  | AN5/C1INA/RP3/SCL2/CTED8/RB3           |

| 3   | RP23/PMA0/PMALL/RC7                                  | 27  | AN10/ <b>RP16</b> /PMBE1/RC0           |

| 4   | RP24/PMA5/RC8                                        | 28  | AN11/ <b>RP17</b> /PMA15/PMCS2/RC1     |

| 5   | RP25/CTED7/PMA6/RC9                                  | 29  | AN12/ <b>RP18</b> /PMACK1/RC2          |

| 6   | Vss                                                  | 30  | VDD                                    |

| 7   | VCAP                                                 | 31  | Vss                                    |

| 8   | RPI29/RA11                                           | 32  | RPI31/RA13                             |

| 9   | PGD2/ <b>RP10</b> /OCM1C/CTED11/PMD2/RB10            | 33  | OSCI/CLKI/C1IND/RA2                    |

| 10  | PGC2/REFI1/RP11/CTED9/PMD1/RB11                      | 34  | OSCO/CLKO/C2IND/RA3                    |

| 11  | AN8/LVDIN/ <b>RP12</b> /PMD0//RB12                   | 35  | TDO/PMA8/RA8                           |

| 12  | AN7/C1INC/ <b>RP13</b> /OCM1D/CTPLS/PMRD/PMWR/RB13   | 36  | SOSCI/ <b>RP4</b> /RB4                 |

| 13  | TMS/RP28/PMA2/PMALU/RA10                             | 37  | SOSCO/PWRLCLK/RA4                      |

| 14  | TCK/PMA7/RA7                                         | 38  | TDI/PMA9/RA9                           |

| 15  | CVREF/AN6/C3INB/RP14/CTED5/PMWR/PMENB/RB14           | 39  | AN13/ <b>RP19</b> /PMBE0/RC3           |

| 16  | AN9/C3INA/RP15/CTED6/PMA14/PMCS/PMCS1/RB15           | 40  | RP20/PMA4/RC4                          |

| 17  | AVss                                                 | 41  | RP21/PMA3/RC5                          |

| 18  | AVdd                                                 | 42  | Vss                                    |

| 19  | MCLR                                                 | 43  | VDD                                    |

| 20  | RPI30/RA12                                           | 44  | <b>RPI32</b> /RA14                     |

| 21  | VREF+/CVREF+/AN0/C3INC/RP26/CTED1/RA0                | 45  | PGD3/ <b>RP5</b> /ASDA1/OCM1E/PMD7/RB5 |

| 22  | VREF-/CVREF-/AN1/C3IND/ <b>RP27</b> /CTED2/RA1       | 46  | PGC3/ <b>RP6</b> /ASCL1/OCM1F/PMD6/RB6 |

| 23  | PGD1/AN2/CTCMP/C2INB/ <b>RP0</b> /RB0                | 47  | RP7/OCM1A/CTED3/PMD5/INT0/RB7          |

| 24  | PGC1/AN1-/AN3/C2INA/ <b>RP1</b> /CTED12/RB1          | 48  | RP8/SCL1/OCM1B/CTED10/PMD4/RB8         |

# TABLE 6: COMPLETE PIN FUNCTION DESCRIPTIONS (PIC24FJ256GA705 TQFP)

Legend: RPn and RPIn represent remappable pins for Peripheral Pin Select (PPS) functions.

# **Table of Contents**

| 1.0   | Device Overview                                             |     |

|-------|-------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-Bit Microcontrollers |     |

| 3.0   | CPU                                                         |     |

| 4.0   | Memory Organization                                         |     |

| 5.0   | Direct Memory Access Controller (DMA)                       |     |

| 6.0   | Flash Program Memory                                        |     |

| 7.0   | Resets                                                      |     |

| 8.0   | Interrupt Controller                                        |     |

| 9.0   | Oscillator Configuration                                    |     |

| 10.0  | Power-Saving Features                                       | 113 |

| 11.0  | I/O Ports                                                   |     |

| 12.0  | Timer1                                                      | 159 |

| 13.0  | Timer2/3                                                    |     |

| 14.0  | Input Capture with Dedicated Timers                         |     |

| 15.0  |                                                             | 173 |

| 16.0  | Capture/Compare/PWM/Timer Modules (MCCP)                    | 183 |

| 17.0  |                                                             |     |

| 18.0  | $\mathbf{J}$                                                |     |

| 19.0  | Universal Asynchronous Receiver Transmitter (UART)          |     |

| 20.0  | Enhanced Parallel Master Port (EPMP)                        |     |

| 21.0  | Real-Time Clock and Calendar (RTCC) with Timestamp          |     |

| 22.0  | 32-Bit Programmable Cyclic Redundancy Check (CRC) Generator |     |

|       | Configurable Logic Cell (CLC) Generator                     |     |

| 24.0  | 12-Bit A/D Converter with Threshold Detect                  |     |

| 25.0  | Triple Comparator Module                                    |     |

|       | Comparator Voltage Reference                                |     |

| 27.0  | Charge Time Measurement Unit (CTMU)                         |     |

| 28.0  |                                                             |     |

| 29.0  | Special Features                                            |     |

| 30.0  | Development Support                                         |     |

| 31.0  |                                                             |     |

| 32.0  |                                                             |     |

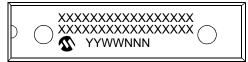

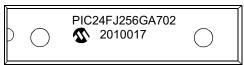

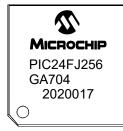

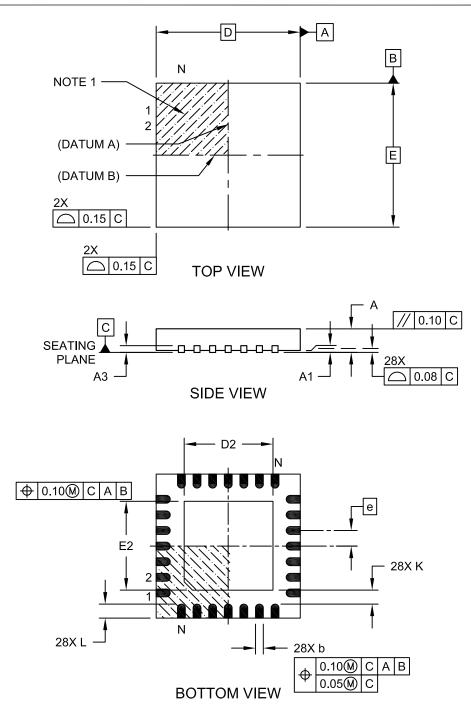

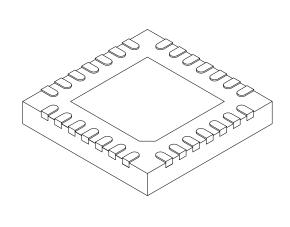

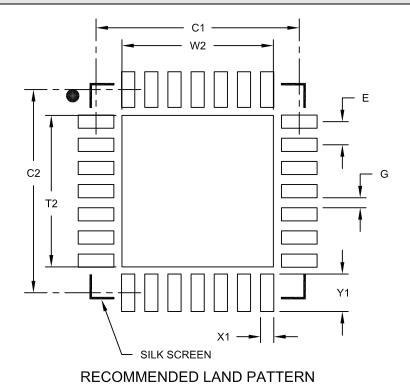

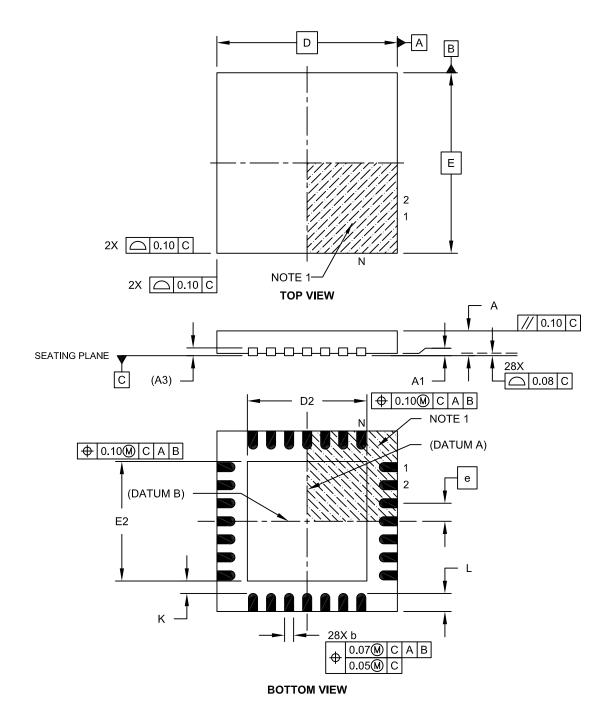

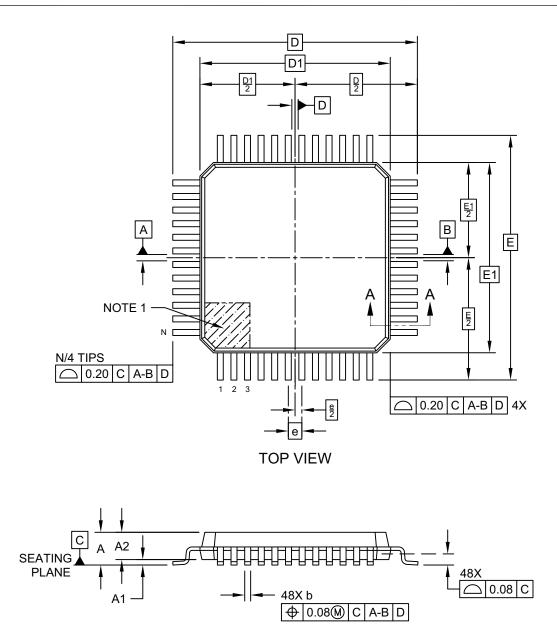

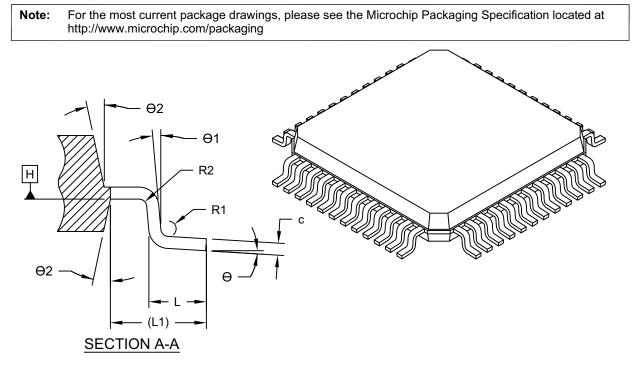

|       | Packaging Information                                       |     |

| Appe  | endix A: Revision History                                   | 411 |

| Index | Χ                                                           | 413 |

|       | Microchip Website                                           |     |

|       | omer Change Notification Service                            |     |

|       | omer Support                                                |     |

| Prod  | luct Identification System                                  |     |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

#### **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPIC33/PIC24 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the PIC24FJ256GA705 product page of the Microchip website (www.microchip.com) or select a family reference manual section from the following list.

> In addition to parameters, features and other documentation, the resulting page provides links to the related family reference manual sections.

- "CPU with Extended Data Space (EDS)" (DS39732)

- "Direct Memory Access Controller (DMA)" (DS30009742)

- "PIC24F Flash Program Memory" (DS30009715)

- "Data Memory with Extended Data Space (EDS)" (DS39733)

- "Reset" (DS39712)

- "Interrupts" (DS70000600)

- "Oscillator" (DS39700)

- "Power-Saving Features with Deep Sleep" (DS39727)

- "I/O Ports with Peripheral Pin Select (PPS)" (DS30009711)

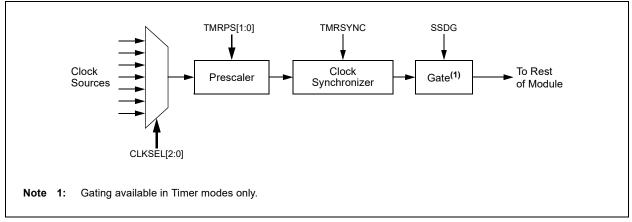

- "Timers" (DS39704)

- "Input Capture with Dedicated Timer" (DS70000352)

- "Output Compare with Dedicated Timer" (DS70005159)

- "Capture/Compare/PWM/Timer (MCCP and SCCP)" (DS30003035)

- "Serial Peripheral Interface (SPI) with Audio Codec Support" (DS70005136)

- "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS70000195)

- "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582)

- "Enhanced Parallel Master Port (EPMP)" (DS39730)

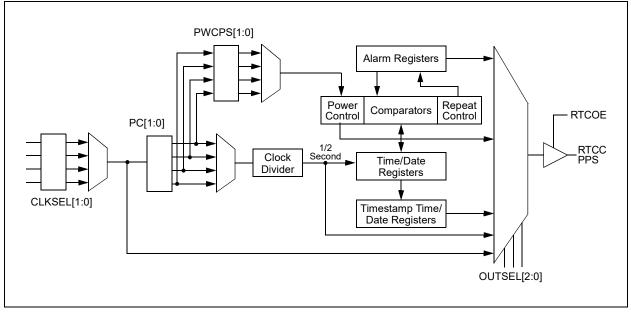

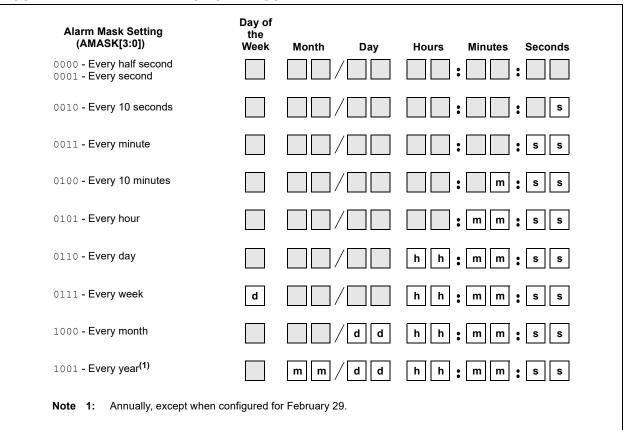

- "RTCC with Timestamp" (DS70005193)

- "32-Bit Programmable Cyclic Redundancy Check (CRC)" (DS30009729)

- "Configurable Logic Cell (CLC)" (DS70005298)

- "12-Bit A/D Converter with Threshold Detect" (DS39739)

- "Scalable Comparator Module" (DS39734)

- "Dual Comparator Module" (DS39710)

- "Charge Time Measurement Unit (CTMU) and CTMU Operation with Threshold Detect" (DS30009743)

- "High-Level Integration with Programmable High/Low-Voltage Detect (HLVD)" (DS39725)

- "Watchdog Timer (WDT)" (DS39697)

- "CodeGuard™ Intermediate Security" (DS70005182)

- "High-Level Device Integration" (DS39719)

- "Programming and Diagnostics" (DS39716)

- "Comparator Voltage Reference Module" (DS39709)

NOTES:

# 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC24FJ64GA705 PIC24FJ256GA704

- PIC24FJ128GA705 PIC24FJ64GA702

- PIC24FJ256GA705 PIC24FJ128GA702

- PIC24FJ256GA702

- PIC24FJ64GA704PIC24FJ128GA704

The PIC24FJ256GA705 family introduces large Flash and SRAM memory in smaller package sizes. This is a 16-bit microcontroller family with a broad peripheral feature set and enhanced computational performance. This family also offers a new migration option for those high-performance applications which may be outgrowing their 8-bit platforms, but do not require the numerical processing power of a Digital Signal Processor (DSP).

Table 1-3 lists the functions of the various pins shown in the pinout diagrams.

# 1.1 Core Features

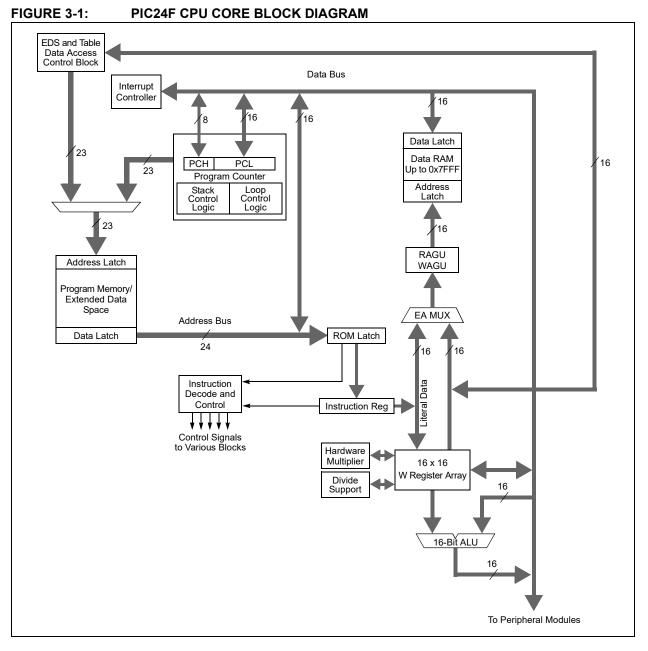

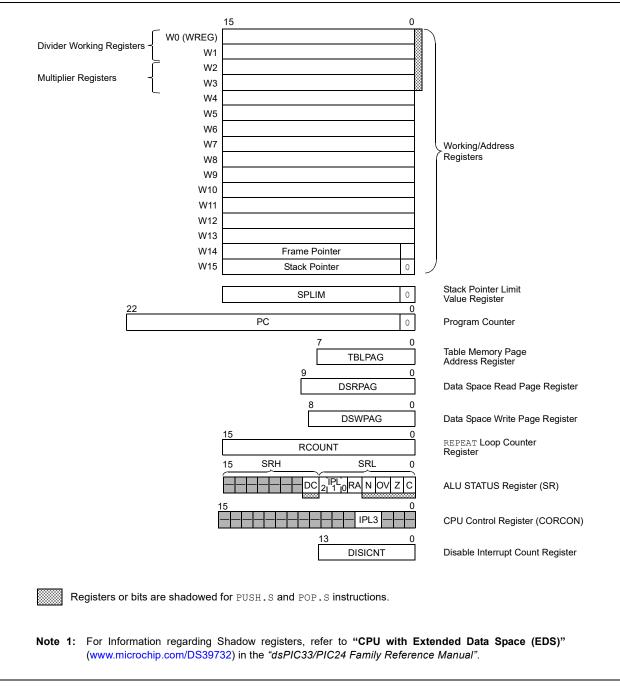

#### 1.1.1 16-BIT ARCHITECTURE

Central to all PIC24F devices is the 16-bit modified Harvard architecture, first introduced with Microchip's dsPIC<sup>®</sup> Digital Signal Controllers (DSCs). The PIC24F CPU core offers a wide range of enhancements, such as:

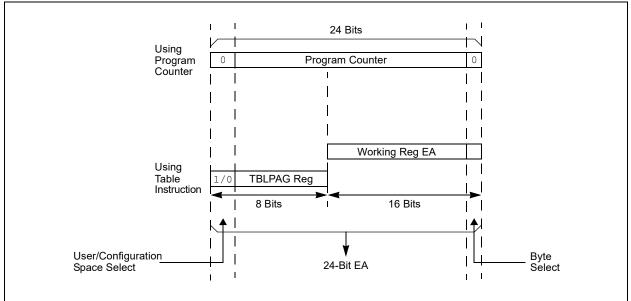

- 16-bit data and 24-bit address paths with the ability to move information between data and memory spaces

- Linear addressing of up to 12 Mbytes (program space) and 32 Kbytes (data)

- A 16-element Working register array with built-in software stack support

- A 17 x 17 hardware multiplier with support for integer math

- Hardware support for 32 by 16-bit division

- An instruction set that supports multiple addressing modes and is optimized for high-level languages, such as 'C'

- Operational performance up to 16 MIPS

#### 1.1.2 POWER-SAVING TECHNOLOGY

The PIC24FJ256GA705 family of devices includes Retention Sleep, a low-power mode with essential circuits being powered from a separate low-voltage regulator.

This new low-power mode also supports the continuous operation of the low-power, on-chip Real-Time Clock/ Calendar (RTCC), making it possible for an application to keep time while the device is otherwise asleep. Aside from this new feature, PIC24FJ256GA705 family devices also include all of the legacy power-saving features of previous PIC24F microcontrollers, such as:

- On-the-Fly Clock Switching, allowing the selection of a lower power clock during run time

- Doze Mode Operation, for maintaining peripheral clock speed while slowing the CPU clock

- Instruction-Based Power-Saving Modes, for quick invocation of the Idle and Sleep modes

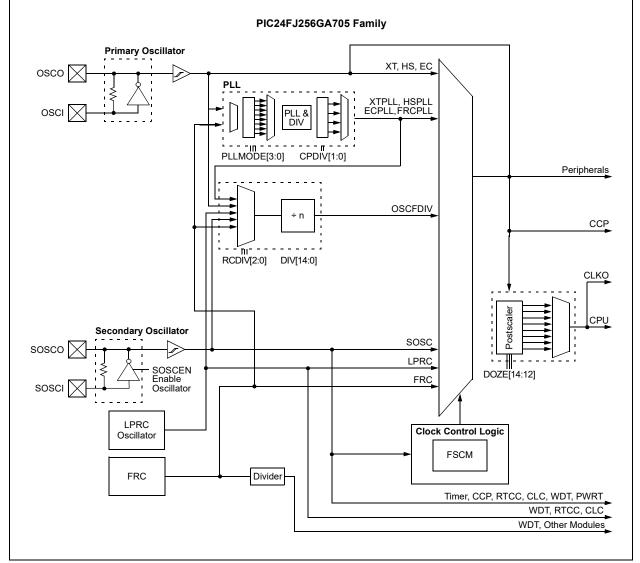

# 1.1.3 OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC24FJ256GA705 family offer six different oscillator options, allowing users a range of choices in developing application hardware. These include:

- · Two Crystal modes

- External Clock (EC) mode

- A Phase-Locked Loop (PLL) frequency multiplier, which allows processor speeds up to 32 MHz

- An internal Fast RC Oscillator (FRC), a nominal 8 MHz output with multiple frequency divider options

- A separate internal Low-Power RC Oscillator (LPRC), 31 kHz nominal for low-power, timing-insensitive applications.

The internal oscillator block also provides a stable reference source for the Fail-Safe Clock Monitor (FSCM). This option constantly monitors the main clock source against a reference signal provided by the internal oscillator and enables the controller to switch to the internal oscillator, allowing for continued low-speed operation or a safe application shutdown.

#### 1.1.4 EASY MIGRATION

Regardless of the memory size, all devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve. The consistent pinout scheme used throughout the entire family also aids in migrating from one device to the next larger device.

The PIC24F family is pin-compatible with devices in the dsPIC33 family, and shares some compatibility with the pinout schema for PIC18 and dsPIC30. This extends the ability of applications to grow from the relatively simple, to the powerful and complex, yet still selecting a Microchip device.

# 1.2 DMA Controller

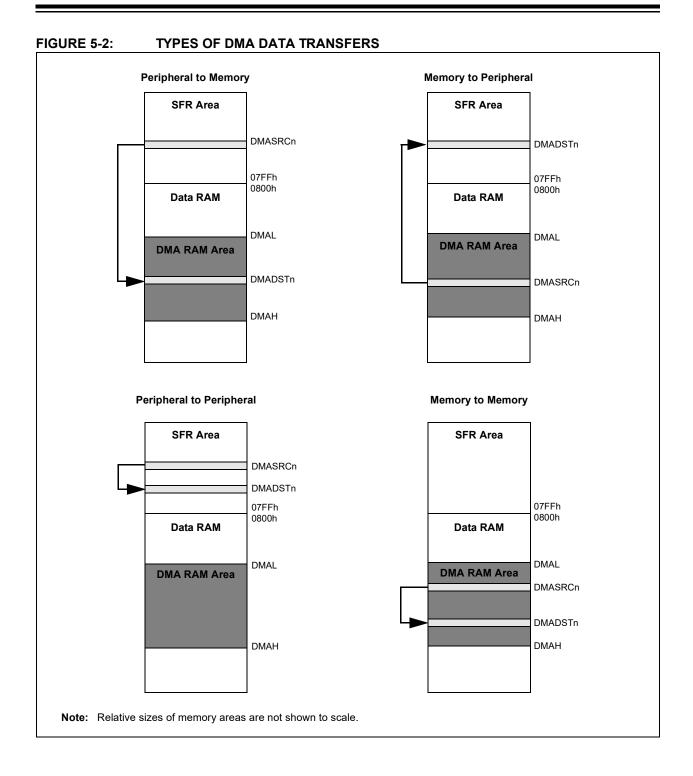

PIC24FJ256GA705 family devices have a Direct Memory Access (DMA) Controller. This module acts in concert with the CPU, allowing data to move between data memory and peripherals without the intervention of the CPU, increasing data throughput and decreasing execution time overhead. Six independently programmable channels make it possible to service multiple peripherals at virtually the same time, with each channel peripheral performing a different operation. Many types of data transfer operations are supported.

# 1.3 Other Special Features

- Peripheral Pin Select: The Peripheral Pin Select (PPS) feature allows most digital peripherals to be mapped over a fixed set of digital I/O pins. Users may independently map the input and/or output of any one of the many digital peripherals to any one of the I/O pins.

- **Configurable Logic Cell:** The Configurable Logic Cell (CLC) module allows the user to specify combinations of signals as inputs to a logic function and to use the logic output to control other peripherals or I/O pins.

- **Timing Modules:** The PIC24FJ256GA705 family provides three independent, general purpose, 16-bit timers (two of which can be combined into a 32-bit timer). The devices also include four multiple output advanced Capture/Compare/PWM/Timer peripherals, and three independent legacy Input Capture and three independent legacy Output Compare modules.

- **Communications:** The PIC24FJ256GA705 family incorporates a range of serial communication peripherals to handle a range of application requirements. There are two independent I<sup>2</sup>C modules that support both Master and Slave modes of operation. Devices also have, through the PPS feature, two independent UARTs with built-in IrDA<sup>®</sup> encoders/decoders and three SPI modules.

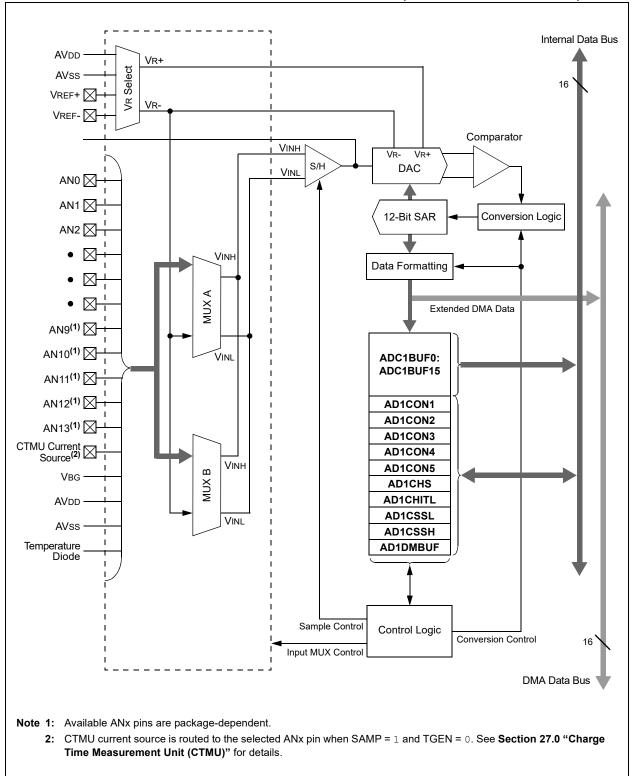

- Analog Features: All members of the PIC24FJ256GA705 family include a 12-bit A/D Converter (A/D) module and a triple comparator module. The A/D module incorporates a range of new features that allow the converter to assess and make decisions on incoming data, reducing CPU overhead for routine A/D conversions. The comparator module includes three analog comparators that are configurable for a wide range of operations.

- CTMU Interface: In addition to their other analog features, members of the PIC24FJ256GA705 family include the CTMU interface module. This provides a convenient method for precision time measurement and pulse generation, and can serve as an interface for capacitive sensors.

- Enhanced Parallel Master/Parallel Slave Port: This module allows rapid and transparent access to the microcontroller data bus, and enables the CPU to directly address external data memory. The parallel port can function in Master or Slave mode, accommodating data widths of four or eight bits and address widths of up to ten bits in Master modes.

- Real-Time Clock and Calendar (RTCC): This module implements a full-featured clock and calendar with alarm functions in hardware, freeing up timer resources and program memory space for use of the core application.

# 1.4 Details on Individual Family Members

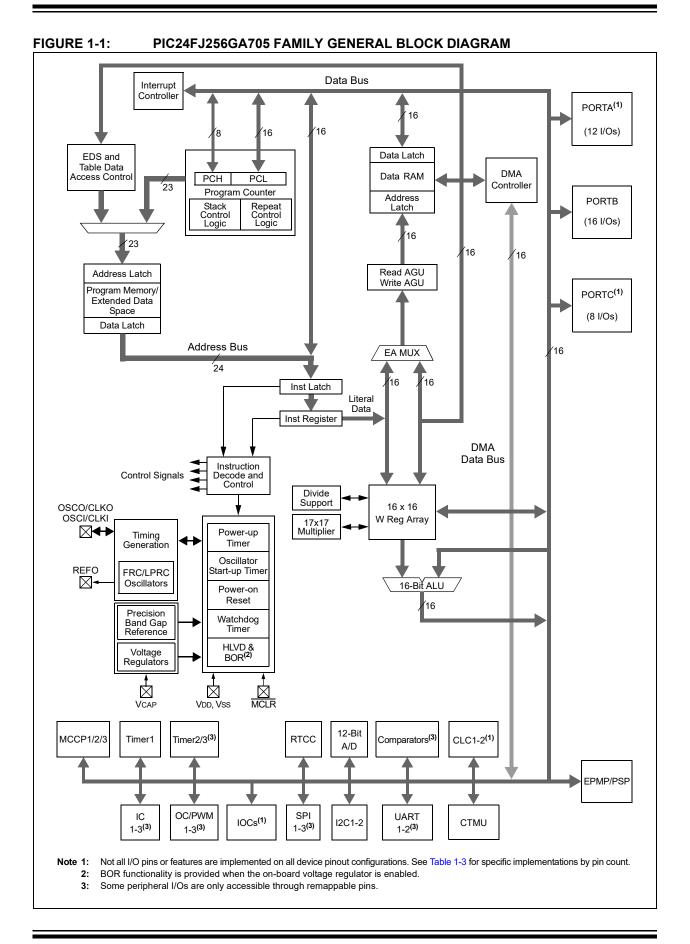

Devices in the PIC24FJ256GA705 family are available in 28-pin, 44-pin and 48-pin packages. The general block diagram for all devices is shown in Figure 1-1.

The devices are differentiated from each other in five ways:

- Flash program memory (64 Kbytes for PIC24FJ64GA70X devices, 128 Kbytes for PIC24FJ128GA70X devices, 256 Kbytes for PIC24FJ256GA70X devices).

- 2. Available I/O pins and ports (22 pins on two ports for 28-pin devices, and 36 and 40 pins on three ports for 44-pin/48-pin devices).

- 3. Enhanced Parallel Master Port (EPMP) is only available on 44-pin/48-pin devices.

- 4. Analog input channels (10 channels for 28-pin devices and 14 channels for 44-pin/48-pin devices).

- 5. CTMU input channels (12 channels for 28-pin devices and 13 channels for 44-pin/48-pin devices)

All other features for devices in this family are identical. These are summarized in Table 1-1 and Table 1-2.

A list of the pin features available on the PIC24FJ256GA705 family devices, sorted by function, is shown in Table 1-3. Note that this table shows the pin location of individual peripheral features and not how they are multiplexed on the same pin. This information is provided in the pinout diagrams in the beginning of this data sheet. Multiplexed features are sorted by the priority given to a feature, with the highest priority peripheral being listed first.

| Features                                                               | PIC24FJ64GA702                                                                                                                                                        | PIC24FJ256GA702             |        |  |  |  |  |  |

|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------|--|--|--|--|--|

| Operating Frequency                                                    | DC – 32 MHz                                                                                                                                                           |                             |        |  |  |  |  |  |

| Program Memory (bytes)                                                 | 64K                                                                                                                                                                   | 128K                        | 256K   |  |  |  |  |  |

| Program Memory<br>(instruction words, 24 bits)                         | 22,528                                                                                                                                                                | 45,056                      | 88,064 |  |  |  |  |  |

| Data Memory (bytes)                                                    |                                                                                                                                                                       | 16K                         | ·      |  |  |  |  |  |

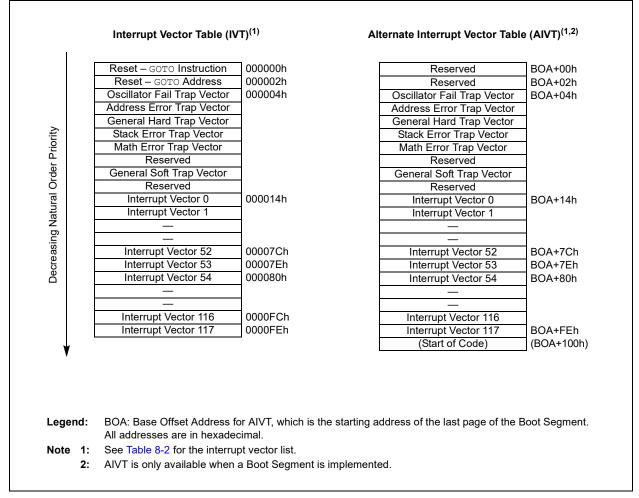

| Interrupt Sources<br>(soft vectors/NMI traps)                          |                                                                                                                                                                       | 124                         |        |  |  |  |  |  |

| I/O Ports                                                              |                                                                                                                                                                       | Ports A, B                  |        |  |  |  |  |  |

| Total I/O Pins                                                         |                                                                                                                                                                       | 22                          |        |  |  |  |  |  |

| Remappable Pins                                                        |                                                                                                                                                                       | 18 (18 I/Os, 0 inputs only) |        |  |  |  |  |  |

| DMA                                                                    |                                                                                                                                                                       | 1 6-channel                 |        |  |  |  |  |  |

| 16-Bit Timers                                                          |                                                                                                                                                                       | 3 <sup>(1)</sup>            |        |  |  |  |  |  |

| Real-Time Clock and Calendar<br>(RTCC)                                 |                                                                                                                                                                       | Yes                         |        |  |  |  |  |  |

| Cyclic Redundancy Check (CRC)                                          |                                                                                                                                                                       | Yes                         |        |  |  |  |  |  |

| Input Capture Channels                                                 | 3(1)                                                                                                                                                                  |                             |        |  |  |  |  |  |

| Output Compare/PWM Channels                                            | 3(1)                                                                                                                                                                  |                             |        |  |  |  |  |  |

| Input Change Notification Interrupt                                    | 21 (remappable pins)                                                                                                                                                  |                             |        |  |  |  |  |  |

| Serial Communications:                                                 |                                                                                                                                                                       |                             |        |  |  |  |  |  |

| UART                                                                   | 2 <sup>(1)</sup>                                                                                                                                                      |                             |        |  |  |  |  |  |

| SPI (three-wire/four-wire)                                             |                                                                                                                                                                       | 3 <sup>(1)</sup>            |        |  |  |  |  |  |

| I <sup>2</sup> C                                                       |                                                                                                                                                                       | 2                           |        |  |  |  |  |  |

| Configurable Logic Cell (CLC)                                          |                                                                                                                                                                       | 2 <sup>(1)</sup>            |        |  |  |  |  |  |

| Parallel Communications<br>(EPMP/PSP)                                  | No                                                                                                                                                                    |                             |        |  |  |  |  |  |

| Capture/Compare/PWM/Timer                                              | 4 Multiple CCPs                                                                                                                                                       |                             |        |  |  |  |  |  |

| Modules                                                                | 1 (6-output), 3 (2-output)                                                                                                                                            |                             |        |  |  |  |  |  |

| JTAG Boundary Scan                                                     | Yes                                                                                                                                                                   |                             |        |  |  |  |  |  |

| 10/12-Bit Analog-to-Digital Converter<br>(A/D) Module (input channels) | 10                                                                                                                                                                    |                             |        |  |  |  |  |  |

| Analog Comparators                                                     | 3                                                                                                                                                                     |                             |        |  |  |  |  |  |

| CTMU Interface                                                         |                                                                                                                                                                       | Yes                         |        |  |  |  |  |  |

| Universal Serial Bus Controller                                        | No                                                                                                                                                                    |                             |        |  |  |  |  |  |

| Resets (and Delays)                                                    | <u>Core</u> POR, VDD POR, BOR, RESET Instruction,<br>MCLR, WDT, Illegal Opcode, REPEAT Instruction,<br>Hardware Traps, Configuration Word Mismatch<br>(OST, PLL Lock) |                             |        |  |  |  |  |  |

| Instruction Set                                                        | 76 Base Instructions, Multiple Addressing Mode Variations                                                                                                             |                             |        |  |  |  |  |  |

| Packages                                                               | 28-Pin QFN, UQFN, SOIC, SSOP and SPDIP <sup>(2)</sup>                                                                                                                 |                             |        |  |  |  |  |  |

#### TABLE 1-1: DEVICE FEATURES FOR THE PIC24FJXXXGA702: 28-PIN DEVICES

**Note 1:** Some peripherals are accessible through remappable pins.

2: 28-Pin SPDIP is available only in the highest Flash variant.

| Features                                                               | PIC24FJ64GA70X                                            | PIC24FJ128GA70X                                                                                                                                                | PIC24FJ256GA70X |  |  |  |  |  |

|------------------------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|--|

| Operating Frequency                                                    | DC – 32 MHz                                               |                                                                                                                                                                |                 |  |  |  |  |  |

| Program Memory (bytes)                                                 | 64K                                                       | 128K                                                                                                                                                           | 256K            |  |  |  |  |  |

| Program Memory<br>(instruction words, 24 bits)                         | 22,528                                                    | 45,056                                                                                                                                                         | 88,064          |  |  |  |  |  |

| Data Memory (bytes)                                                    |                                                           | 16K                                                                                                                                                            |                 |  |  |  |  |  |

| Interrupt Sources<br>(soft vectors/NMI traps)                          |                                                           | 124                                                                                                                                                            |                 |  |  |  |  |  |

| I/O Ports                                                              |                                                           | Ports A, B, C                                                                                                                                                  |                 |  |  |  |  |  |

| Total I/O Pins:                                                        |                                                           |                                                                                                                                                                |                 |  |  |  |  |  |

| 44-pin                                                                 | 35                                                        | 35                                                                                                                                                             | 35              |  |  |  |  |  |

| 48-pin                                                                 | 39                                                        | 39                                                                                                                                                             | 39              |  |  |  |  |  |

| Remappable Pins:                                                       |                                                           |                                                                                                                                                                |                 |  |  |  |  |  |

| 44-pin                                                                 |                                                           | 29 (29 I/Os, 0 inputs only)                                                                                                                                    |                 |  |  |  |  |  |

| 48-pin                                                                 |                                                           | 33 (29 I/Os, 4 inputs only)                                                                                                                                    |                 |  |  |  |  |  |

| DMA (6-channel)                                                        |                                                           | 1                                                                                                                                                              |                 |  |  |  |  |  |

| 16-Bit Timers                                                          |                                                           | 3(1)                                                                                                                                                           |                 |  |  |  |  |  |

| Real-Time Clock and Calendar<br>(RTCC)                                 | Yes                                                       |                                                                                                                                                                |                 |  |  |  |  |  |

| Cyclic Redundancy Check (CRC)                                          | Yes                                                       |                                                                                                                                                                |                 |  |  |  |  |  |

| Input Capture Channels                                                 | 3 <sup>(1)</sup>                                          |                                                                                                                                                                |                 |  |  |  |  |  |

| Output Compare/PWM Channels                                            |                                                           | 3 <sup>(1)</sup>                                                                                                                                               |                 |  |  |  |  |  |

| Input Change Notification Interrupt                                    |                                                           | 25 (remappable pins)                                                                                                                                           |                 |  |  |  |  |  |

| Serial Communications:                                                 |                                                           |                                                                                                                                                                |                 |  |  |  |  |  |

| UART                                                                   |                                                           | 2 <sup>(1)</sup>                                                                                                                                               |                 |  |  |  |  |  |

| SPI (three-wire/four-wire)                                             |                                                           |                                                                                                                                                                |                 |  |  |  |  |  |

| l <sup>2</sup> C                                                       | 2                                                         |                                                                                                                                                                |                 |  |  |  |  |  |

| Configurable Logic Cell (CLC)                                          | 2 <sup>(1)</sup>                                          |                                                                                                                                                                |                 |  |  |  |  |  |

| Parallel Communications<br>(EPMP/PSP)                                  | Yes                                                       |                                                                                                                                                                |                 |  |  |  |  |  |

| Capture/Compare/PWM/Timer<br>Modules (MCCP)                            | 4 Modules<br>1 (6-output), 3 (2-output)                   |                                                                                                                                                                |                 |  |  |  |  |  |

| JTAG Boundary Scan                                                     | Yes                                                       |                                                                                                                                                                |                 |  |  |  |  |  |

| 10/12-Bit Analog-to-Digital Converter<br>(A/D) Module (input channels) |                                                           | 14                                                                                                                                                             |                 |  |  |  |  |  |

| Analog Comparators                                                     |                                                           | 3                                                                                                                                                              |                 |  |  |  |  |  |

| CTMU Interface                                                         |                                                           | Yes                                                                                                                                                            |                 |  |  |  |  |  |

| Universal Serial Bus Controller                                        | No                                                        |                                                                                                                                                                |                 |  |  |  |  |  |

| Resets (and delays)                                                    | MCLR, W                                                   | Core POR, VDD POR, BOR, RESET Instruction,<br>MCLR, WDT, Illegal Opcode, REPEAT Instruction,<br>Hardware Traps, Configuration Word Mismatch<br>(OST, PLL Lock) |                 |  |  |  |  |  |

| Instruction Set                                                        | 76 Base Instructions, Multiple Addressing Mode Variations |                                                                                                                                                                |                 |  |  |  |  |  |

| Packages                                                               |                                                           | in TQFP, 48-Pin TQFP and L                                                                                                                                     |                 |  |  |  |  |  |

**Note 1:** Some peripherals are accessible through remappable pins.

| Dia             | 1                           | Pin Number/G        | rid Locato     | r                   |     | Input  |                                      |  |

|-----------------|-----------------------------|---------------------|----------------|---------------------|-----|--------|--------------------------------------|--|

| Pin<br>Function | 28-Pin SOIC,<br>SSOP, SPDIP | 28-Pin QFN,<br>UQFN | 44-Pin<br>TQFP | 48-Pin<br>UQFN/TQFP | I/O | Buffer | Description                          |  |

| AN0             | 2                           | 27                  | 19             | 21                  | Ι   | ANA    | A/D Analog Inputs                    |  |

| AN1             | 3                           | 28                  | 20             | 22                  | I   | ANA    |                                      |  |

| AN2             | 4                           | 1                   | 21             | 23                  | I   | ANA    |                                      |  |

| AN3             | 5                           | 2                   | 22             | 24                  | I   | ANA    |                                      |  |

| AN4             | 6                           | 3                   | 23             | 25                  | I   | ANA    |                                      |  |

| AN5             | 7                           | 4                   | 24             | 26                  | I   | ANA    |                                      |  |

| AN6             | 25                          | 22                  | 14             | 15                  | I   | ANA    | ]                                    |  |

| AN7             | 24                          | 21                  | 11             | 12                  | I   | ANA    |                                      |  |

| AN8             | 23                          | 20                  | 10             | 11                  | Ι   | ANA    |                                      |  |

| AN9             | 26                          | 23                  | 15             | 16                  | I   | ANA    |                                      |  |

| AN10            | _                           | —                   | 25             | 27                  | I   | ANA    | 1                                    |  |

| AN11            | _                           | _                   | 26             | 28                  | I   | ANA    |                                      |  |

| AN12            |                             | —                   | 27             | 29                  | I   | ANA    |                                      |  |

| AN13            | _                           | _                   | 36             | 39                  | I   | ANA    | ]                                    |  |

| AVDD            | 28                          | 25                  | 17             | 18                  | Р   | _      | Positive Supply for Analog modules   |  |

| AVss            | 27                          | 24                  | 16             | 17                  | Р   | _      | Ground Reference for Analog modules  |  |

| C1INA           | 7                           | 4                   | 24             | 26                  | I   | ANA    | Comparator 1 Input A                 |  |

| C1INB           | 6                           | 3                   | 23             | 25                  | I   | ANA    | Comparator 1 Input B                 |  |

| C1INC           | 18, 24                      | 15, 21              | 1, 11          | 1, 12               | I   | ANA    | Comparator 1 Input C                 |  |

| C1IND           | 9                           | 6                   | 30             | 33                  | Ι   | ANA    | Comparator 1 Input D                 |  |

| C2INA           | 5                           | 2                   | 22             | 24                  | I   | ANA    | Comparator 2 Input A                 |  |

| C2INB           | 4                           | 1                   | 21             | 23                  | I   | ANA    | Comparator 2 Input B                 |  |

| C2INC           | 18                          | 15                  | 1              | 1                   | I   | ANA    | Comparator 2 Input C                 |  |

| C2IND           | 10                          | 7                   | 31             | 34                  | I   | ANA    | Comparator 2 Input D                 |  |

| C3INA           | 26                          | 23                  | 15             | 16                  | I   | ANA    | Comparator 3 Input A                 |  |

| C3INB           | 25                          | 22                  | 14             | 15                  | I   | ANA    | Comparator 3 Input B                 |  |

| C3INC           | 2, 18                       | 15, 27              | 1, 19          | 1, 21               | I   | ANA    | Comparator 3 Input C                 |  |

| C3IND           | 3                           | 28                  | 20             | 22                  | I   | ANA    | Comparator 3 Input D                 |  |

| CLKI            | 9                           | 6                   | 30             | 33                  | _   | —      | Main Clock Input Connection          |  |

| CLKO            | 10                          | 7                   | 31             | 34                  | 0   | DIG    | System Clock Output                  |  |

| CTCMP           | 4                           | 1                   | 21             | 23                  | 0   | ANA    | CTMU Comparator 2 Input (Pulse mode) |  |

### TABLE 1-3: PIC24FJ256GA705 FAMILY PINOUT DESCRIPTIONS

Legend: TTL = TTL input buffer ANA = Analog level input/output DIG = Digital input/output

ST = Schmitt Trigger input buffer

$I^2C = I^2C/SMBus$  input buffer

| Dim             | F                           | Pin Number/G        | rid Locator    |                     | I/O | Immunt          |                                           |

|-----------------|-----------------------------|---------------------|----------------|---------------------|-----|-----------------|-------------------------------------------|

| Pin<br>Function | 28-Pin SOIC,<br>SSOP, SPDIP | 28-Pin QFN,<br>UQFN | 44-Pin<br>TQFP | 48-Pin<br>UQFN/TQFP |     | Input<br>Buffer | Description                               |

| CTED1           | 2                           | 27                  | 19             | 21                  | Ι   | ST              | CTMU External Edge Inputs                 |

| CTED2           | 3                           | 28                  | 20             | 22                  | -   | ST              |                                           |

| CTED3           | 16                          | 13                  | 43             | 47                  | Ι   | ST              |                                           |

| CTED4           | 18                          | 15                  | 1              | 1                   | Ι   | ST              |                                           |

| CTED5           | 25                          | 22                  | 14             | 15                  | Ι   | ST              |                                           |

| CTED6           | 26                          | 23                  | 15             | 16                  | Ι   | ST              |                                           |

| CTED7           | —                           | _                   | 5              | 5                   | Ι   | ST              |                                           |

| CTED8           | 7                           | 4                   | 24             | 26                  | Ι   | ST              |                                           |

| CTED9           | 22                          | 19                  | 9              | 10                  | Ι   | ST              |                                           |

| CTED10          | 17                          | 14                  | 44             | 48                  | Ι   | ST              |                                           |

| CTED11          | 21                          | 18                  | 8              | 9                   | Ι   | ST              |                                           |

| CTED12          | 5                           | 2                   | 22             | 24                  | Ι   | ST              |                                           |

| CTED13          | 6                           | 3                   | 23             | 25                  | Ι   | ST              |                                           |

| CTPLS           | 24                          | 21                  | 11             | 12                  | 0   | DIG             | CTMU Pulse Output                         |

| CVREF           | 25                          | 22                  | 14             | 15                  | 0   | ANA             | Comparator Voltage Reference Output       |

| CVREF+          | 2                           | 27                  | 19             | 21                  | Ι   | ANA             | Comparator Voltage Reference (high) Input |

| CVREF-          | 3                           | 28                  | 20             | 22                  | Ι   | ANA             | Comparator Voltage Reference (low) Input  |

| INT0            | 16                          | 13                  | 43             | 47                  | Ι   | ST              | External Interrupt Input 0                |

| IOCA0           | 2                           | 27                  | 19             | 21                  | Ι   | ST              | PORTA Interrupt-on-Change                 |

| IOCA1           | 3                           | 28                  | 20             | 22                  | Ι   | ST              |                                           |

| IOCA2           | 9                           | 6                   | 30             | 33                  | Ι   | ST              |                                           |

| IOCA3           | 10                          | 7                   | 31             | 34                  | Ι   | ST              |                                           |

| IOCA4           | 12                          | 9                   | 34             | 37                  | Ι   | ST              |                                           |

| IOCA7           | —                           | _                   | 13             | 14                  | Ι   | ST              |                                           |

| IOCA8           | —                           | _                   | 32             | 35                  | Ι   | ST              | ]                                         |

| IOCA9           | _                           | _                   | 35             | 38                  | Ι   | ST              | ]                                         |

| IOCA10          | _                           | _                   | 12             | 13                  | Ι   | ST              | ]                                         |

| IOCA11          | _                           | _                   | _              | 8                   | Ι   | ST              | ]                                         |

| IOCA12          | _                           | _                   |                | 20                  | Ι   | ST              | ]                                         |

| IOCA13          | _                           | _                   | _              | 32                  | I   | ST              | ]                                         |

| IOCA14          | _                           | —                   | _              | 44                  | I   | ST              | 1                                         |

Legend: TTL = TTL input buffer ANA = Analog level input/output DIG = Digital input/output ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMBus$  input buffer

| Dim             | F                           | Pin Number/G        | rid Locator    |                     |     |                 |                                                                               |

|-----------------|-----------------------------|---------------------|----------------|---------------------|-----|-----------------|-------------------------------------------------------------------------------|

| Pin<br>Function | 28-Pin SOIC,<br>SSOP, SPDIP | 28-Pin QFN,<br>UQFN | 44-Pin<br>TQFP | 48-Pin<br>UQFN/TQFP | I/O | Input<br>Buffer | Description                                                                   |

| IOCB0           | 4                           | 1                   | 21             | 23                  | I   | ST              | PORTB Interrupt-on-Change                                                     |

| IOCB1           | 5                           | 2                   | 22             | 24                  | -   | ST              |                                                                               |

| IOCB2           | 6                           | 3                   | 23             | 25                  | I   | ST              |                                                                               |

| IOCB3           | 7                           | 4                   | 24             | 26                  | I   | ST              |                                                                               |

| IOCB4           | 11                          | 8                   | 33             | 36                  | -   | ST              |                                                                               |

| IOCB5           | 14                          | 11                  | 41             | 45                  | I   | ST              |                                                                               |

| IOCB6           | 15                          | 12                  | 42             | 46                  | I   | ST              |                                                                               |

| IOCB7           | 16                          | 13                  | 43             | 47                  | I   | ST              |                                                                               |

| IOCB8           | 17                          | 14                  | 44             | 48                  | I   | ST              |                                                                               |

| IOCB9           | 18                          | 15                  | 1              | 1                   |     | ST              |                                                                               |

| IOCB10          | 21                          | 18                  | 8              | 9                   | I   | ST              |                                                                               |

| IOCB11          | 22                          | 19                  | 9              | 10                  | I   | ST              |                                                                               |

| IOCB12          | 23                          | 20                  | 10             | 11                  |     | ST              |                                                                               |

| IOCB13          | 24                          | 21                  | 11             | 12                  | I   | ST              |                                                                               |

| IOCB14          | 25                          | 22                  | 14             | 15                  | I   | ST              |                                                                               |

| IOCB15          | 26                          | 23                  | 15             | 16                  | I   | ST              |                                                                               |

| IOCC1           | _                           | _                   | 26             | 28                  | I   | ST              | PORTC Interrupt-on-Change                                                     |

| IOCC2           | _                           | _                   | 27             | 29                  | Ι   | ST              |                                                                               |

| IOCC3           | _                           | —                   | 36             | 39                  |     | ST              |                                                                               |

| IOCC4           | _                           | _                   | 37             | 40                  | -   | ST              |                                                                               |

| IOCC5           | _                           | _                   | 38             | 41                  | I   | ST              |                                                                               |

| IOCC6           | _                           | —                   | 2              | 2                   |     | ST              |                                                                               |

| IOCC7           | _                           | _                   | 3              | 3                   | -   | ST              |                                                                               |

| IOCC8           | _                           | _                   | 4              | 4                   | I   | ST              |                                                                               |

| IOCC9           | _                           | _                   | 5              | 5                   | I   | ST              |                                                                               |