# **Front-End PD Interface Controller**

### Product Overview

The PD70210, PD70210A, and PD70210AL devices are advanced PD interface controllers (front-end IC) for powered devices in PoE applications. They support IEEE<sup>®</sup> 802.3af, IEEE 802at, HDBaseT, and general 2-pair or 4-pair configurations.

The PD70210, PD70210A, and PD70210AL devices have an advanced classification block that supports 2, 3, 4, and 6 event classification. These devices also identify the four pairs of cable that receives power and generates appropriate flags by using the SUPP\_Sx pins. The IC features an internal bleeder for rapidly discharging the input capacitor of the DC–DC converter to ensure fast re-detection and port power-up on sudden removal and re-insertion of the Ethernet cable into RJ45.

### Features

The following are the features of PD70210, PD70210A, and PD70210AL devices.

- Supports IEEE 802.3af/at, HDBaseT, and other 2-pair or 4-pair configurations

- PD detection and programmable classification

- 2, 3, 4, and 6 event classification

- Integrated 0.3 Ω isolating (series-pass) FET

- In-rush current limiting

- Wall adapter priority support (PD70210A and PD70210AL only)

- Less than 5 µA offset current during detection

- DFN-16/QFN-38 package

- Power Good Flag (PD70210 only)

UPoE

x x

Х

х

х

The following table lists the Microchip PD products offerings.

| ···· · · · · · · · · · · · · · · · · · |                 |                     |                 |                 |                  |  |  |  |  |  |

|----------------------------------------|-----------------|---------------------|-----------------|-----------------|------------------|--|--|--|--|--|

| Part                                   | Туре            | Package             | IEEE<br>802.3af | IEEE<br>802.3at | HDBaseT<br>(PoH) |  |  |  |  |  |

| PD70100                                | Front-end       | 3 mm × 4 mm 12L DFN | x               |                 | —                |  |  |  |  |  |

| PD70101                                | Front-end + PWM | 5 mm × 5 mm 32L QFN | x               | —               | —                |  |  |  |  |  |

| PD70200                                | Front-end       | 3 mm × 4 mm 12L DFN | x               | x               | —                |  |  |  |  |  |

| PD70201                                | Front-end + PWM | 5 mm × 5 mm 32L QFN | x               | x               | —                |  |  |  |  |  |

| PD70210                                | Front-end       | 4 mm × 5 mm 16L DFN | x               | x               | x                |  |  |  |  |  |

| PD70210A                               | Front-end       | 4 mm × 5 mm 16L DFN | x               | x               | x                |  |  |  |  |  |

5 mm × 7 mm 38L QFN

6 mm × 6 mm 36L QFN

6 mm × 8 mm 40L QFN

Х

х

х

Х

х

х

х

х

х

#### Table 1. Microchip Powered Device Products Offerings

# Applications

PD70210AL

PD70211

PD70224

The following are the applications of PD70210, PD70210A, and PD70210AL devices.

• Single HDBaseT or double up to 95 W

Front-end

Front-end + PWM

Ideal diode bridge

- IEEE 802.3af and IEEE 802.3at

- Indoor and outdoor PoE

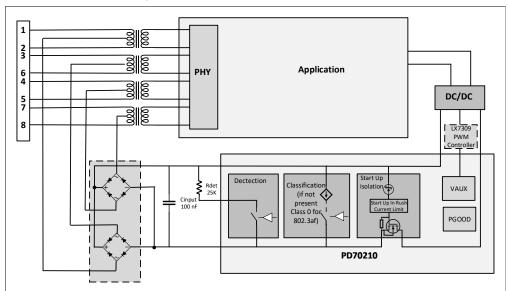

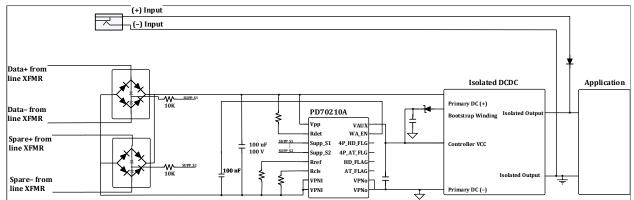

The following figure shows a typical PD70210 application.

Figure 1. Basic PD70210 Block Diagram

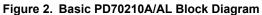

The following figure shows a typical PD70210A/AL application.

Microchip offers complete reference design packages and Evaluation Boards (EVBs). For access to these design packages, device datasheets, or application notes, consult local Microchip Client Engagement Manager or visit Microchip website. For technical support, consult local Embedded Solutions Engineers or go to Microchip Support. For help in designing the DC-DC portion of circuit try MPLAB Analog Designer (MAD) tool.

# **Table of Contents**

| Pro  | duct Overview                          | 1  |

|------|----------------------------------------|----|

| Fea  | itures                                 | 1  |

| Арр  | plications                             | 2  |

| 1.   | Functional Descriptions                | 5  |

|      | 1.1. Application Information           | 6  |

|      | 1.2. Wall Adapter Mode (PD70210A/AL)   | 6  |

|      | 1.3. Flags                             | 9  |

| 2.   | Electrical Specifications              | 10 |

|      | 2.1. Absolute Maximum Ratings          | 13 |

|      | 2.2. Operating Conditions              | 14 |

|      | 2.3. Thermal Properties                | 14 |

| 3.   | Pin Descriptions                       |    |

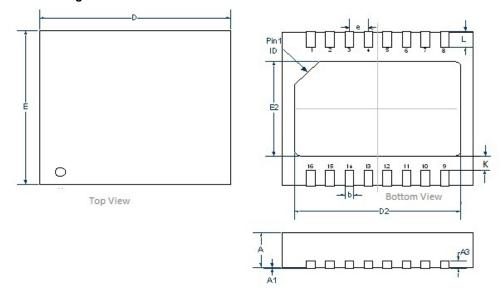

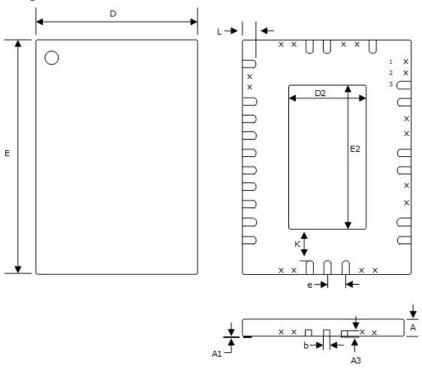

| 4.   | Package Information                    |    |

|      | 4.1. 16-Pin Plastic DFN, 5 mm × 4 mm   |    |

|      | 4.2. 38-Pin Plastic QFN, 5 mm × 7 mm   |    |

|      | 4.3. Thermal Protection                |    |

| 5.   | Ordering Information                   |    |

| 6.   | Reference Documents                    |    |

| 7.   | Revision History                       |    |

| The  | Microchip Website                      | 27 |

| Pro  | duct Change Notification Service       | 27 |

| Cus  | stomer Support                         |    |

| Mic  | rochip Devices Code Protection Feature | 27 |

| Leg  | al Notice                              |    |

| Trac | demarks                                |    |

| Qua  | ality Management System                | 29 |

| Woi  | rldwide Sales and Service              |    |

# 1. Functional Descriptions

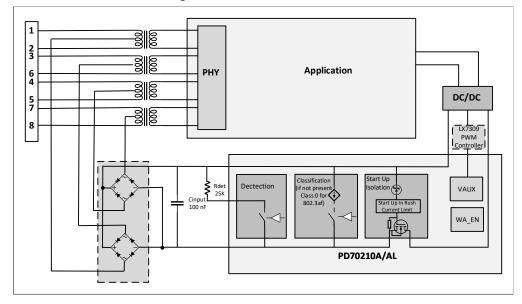

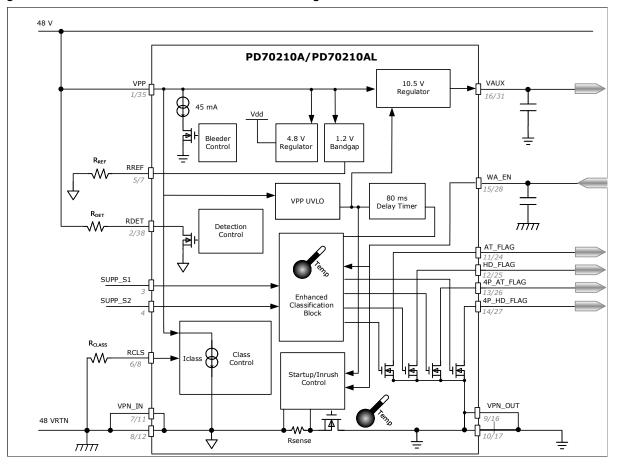

The following figure shows the functional blocks of the PD70210 device.

Figure 1-1. PD70210 Functional Block Diagram

**Functional Descriptions**

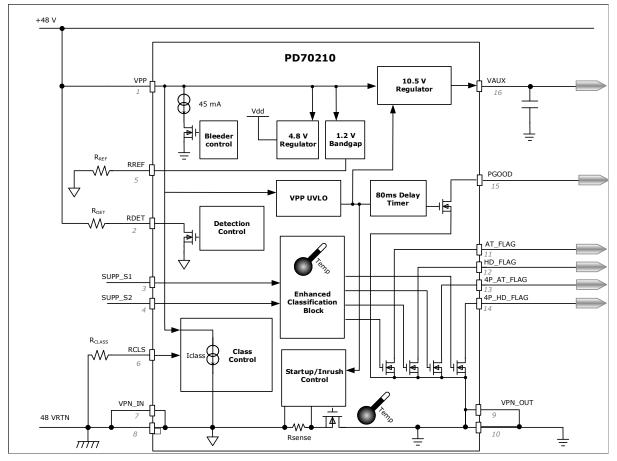

The following figure shows the functional blocks of the PD70210A/PD70210AL devices.

Figure 1-2. PD70210A/PD70210AL Functional Block Diagram

#### 1.1 Application Information

This section describes the PD70210/A/AL application.

For latest recommendations, contact Microchip and/or see AN3468 Designing a Type 1/2 802.3 or HDBaseT Type 3 Powered Device Front-End Using PD702x0 and PD701x0 ICs.

### 1.2 Wall Adapter Mode (PD70210A/AL)

PD70210A and PD70210AL supports wall adapter functionality. By setting the WA\_EN pin high, it gives priority to the wall adapter jack to supply the load.

The WA\_EN pin is used while connecting a wall-adapter voltage between VPP and VPN\_OUT by OR-ing diode. When WA\_EN (the wall adapter enable pin) is held low (referenced to VPN\_IN), the front-end works as a normal PD. When WA\_EN is raised high (referenced to VPN\_IN), the following three internal operations are forced.

- The isolation FET is turned off.

- All output flags (AT\_FLAG, HD\_FLAG, 4P\_AT\_FLAG, and 4P\_HD\_FLAG) are activated (low state).

- Vaux output voltage is turned on.

While activating the WA\_EN pin, the wall adapter supplies input voltage for the DC–DC converter. The WA\_EN at a high state disables the detection and classification modes.

#### **Functional Descriptions**

#### 1.2.1 Peripheral Devices

The following is the list of PD70210/A/AL peripheral devices.

- Place 47 nF to 100 nF/100 V capacitor between the device's VPP and VPNI pins and close to the device.

- Place a 58 V TVS between device VPP and VPN\_IN pins for protection against voltage transients. For complete surge protection, see AN3410 Design for PD System Surge Immunity PD701xx and PD702xx Application Note.

- If 4-pair flags are used, place a 10 KΩ resistor on SUPP\_S1 and SUPP\_S2 lines between the diode bridge and PD70210/A device.

- When WA\_EN is used, place 100 nF to 1  $\mu$ F/10 V capacitor between WA\_EN and the VPN\_IN pin, close to the PD70210/A device.

- When it is not used, connect the WA\_EN to the VPN\_IN pin.

- Place 4.7 μF/25 V capacitor between Vaux pin and VPN\_OUT.

#### 1.2.2 Operation with an External DC Source

PD applications using PD70210A IC operates with an external power source (DC wall adapter). The two cases of providing power with an external source is detailed in the following sections.

#### 1.2.2.1 External Power Input Connected to Application Supply Rails

In this application, the external source is connected to the application's low-voltage supply rails. The external source voltage level depends on DC–DC output characteristics.

#### Figure 1-3. External Power Input to Supply Rails

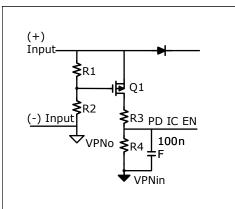

#### 1.2.2.2 External Power Input Connected to PD70210A Output

In this application, the external source is connected to the PD device's output connection for the application (VPP to VPN<sub>OUT</sub>). The external source voltage level depends on the DC–DC input requirements.

#### (+) Input Q1 (-) Input Data+ from line XFMR Isolated DCDC Application 10 K arv DC (+) Data- from PD70210A solated Out Ŷ Bootstrap Windin line XFMR Vpp VAUX WA EN Spare+ fron Supp\_S1 4P\_HD\_FLG 100 nF 100 V Controller VCC line XFMR SUPP S 4P\_AT\_FLG upp\_S2 HD\_FLAG ₩ 101 100 nF Rcls AT FLAG Isolated Output Spare- from VPNI VPN 1 line XFMR /PNI VPN Primary DC (-) Ŧ

#### Figure 1-4. External Power Input to PD70210A Output

When an external adapter is connected, the PD70210A WA\_EN pin is used for disabling the isolation switch and PSE input power. The WA\_EN pin resistors divider depends on the WA\_EN threshold of the PD70210A.

# PD70210/PD70210A/PD70210AL Functional Descriptions

The following figure shows a detailed view of the resistors to be selected in an external adapter connection.

#### Figure 1-5. External Power Input Resistors Dividers

R1 and R2 sets a threshold for Pfet Q1 enable to detect an external adapter. It must be set to a lower threshold than PD70210A disable levels. R3 and R4 sets the PD70210A disable threshold. Therefore, in 36 V–57 V external adapter, the disable settings are selected as follows:

- Pfet enable threshold = 30 V.

- R1 and R2 setting must be the value of Q1 VGS < 20 V at the maximum voltage condition of the external adapter.

- When the external adapter voltage is more than 30 V, Q1 is more than its VGS<sub>TH</sub> value.

$$VGS = Vext\_adapter \times \frac{R1}{R1 + R2}$$

• R1 is selected as 2 KΩ.

$$R2 = R1 \times \frac{Vext\_adapter - VGS}{VGS}$$

- Using R1 = 2 K $\Omega$ , Vext\_adapter = 30 V, and VGS = maximum VGS<sub>TH</sub> = 3.5 V, provides the R2 value as 15 K $\Omega$ .

- R3 and R4 are set to the range of few K $\Omega$  to tens of K $\Omega$  using the following equation.

$$PD70210A_Wa_en = Vext_adapter_PD70210A \times \frac{R4}{(R3+R4)}$$

• Using R3 = 15 K $\Omega$ , Vext\_adapter = 33.7 V, and PD70210A\_WA\_EN = 2.4 V as turn-off minimum threshold from the datasheet, solving the equation gives the valid resistor values for an adapter of 36 V and above. The values are: R3 = 15 K $\Omega$  and R4 = 1.15 K $\Omega$ .

For more information and various adapter connection methods, see AN3472 Implementing AUX Power in PoE Application Note.

### 1.3 Flags

The following truth table lists the flags status.

| Table 1-1. | Truth | Table <sup>•</sup> | for | Status | of Flags |

|------------|-------|--------------------|-----|--------|----------|

|------------|-------|--------------------|-----|--------|----------|

| Number of<br>Fingers "N"<br>(N-Event<br>Classification) | SUPP_S1     | SUPP_S2             | AT_FLAG | HD_FLAG | 4P_AT_FLAG | 4P_HD_FLAG |  |  |

|---------------------------------------------------------|-------------|---------------------|---------|---------|------------|------------|--|--|

| 1                                                       | Х           | Х                   | Hi Z    | Hi Z    | Hi Z       | Hi Z       |  |  |

| 2                                                       | Н           | L                   | 0 V     | Hi Z    | Hi Z       | Hi Z       |  |  |

| 2                                                       | L           | Н                   | 0 V     | Hi Z    | Hi Z       | Hi Z       |  |  |

| 2                                                       | Н           | Н                   | 0 V     | Hi Z    | 0 V        | Hi Z       |  |  |

| 3                                                       | L           | Н                   | 0 V     | 0 V     | Hi Z       | Hi Z       |  |  |

| 3                                                       | Н           | L                   | 0 V     | 0 V     | Hi Z       | Hi Z       |  |  |

| 3                                                       | Н           | Н                   | 0 V     | 0 V     | 0 V        | Hi Z       |  |  |

| 4                                                       | Х           | Х                   | 0 V     | 0 V     | 0 V        | Hi Z       |  |  |

| 5                                                       | Reserved fo | Reserved for future |         |         |            |            |  |  |

| 6                                                       | Х           | Х                   | 0 V     | 0 V     | 0 V        | Hi Z       |  |  |

**Note:** A flag's state is set only once at port turn on, while VPP-VPNin voltage crosses UVLO<sub>ON</sub>. If SUPP\_S1 and SUPP\_S2 pins are changing after port turn on, the flags do not change accordingly.

# 2. Electrical Specifications

Unless otherwise specified under conditions, the minimum and maximum ratings stated apply over the entire specified operating rating of the device. Typical values are obtained either by design or by production testing at 25 °C ambient. Voltages are with respect to IC ground (VPN\_IN).

#### Table 2-1. Input Voltage

| Symbol          | Parameter                                    | Conditions | Typical | Maximum | Unit |

|-----------------|----------------------------------------------|------------|---------|---------|------|

| I <sub>IN</sub> | IC input current with I <sub>CLASS</sub> off | VPP = 55 V | 1       | 3       | mA   |

### Table 2-2. Detection Phase

| Symbol                  | Parameter                                                          | Conditions                                        | Minimum | Typical | Maximum | Unit |

|-------------------------|--------------------------------------------------------------------|---------------------------------------------------|---------|---------|---------|------|

| V <sub>DET</sub>        | Detection range                                                    | —                                                 | 1.1     | —       | 10.1    | V    |

| R <sub>DET_TH</sub>     | R <sub>DET</sub> disconnect threshold                              | —                                                 | 10.1    | —       | 12.8    | V    |

| R <sub>DS_DET_ON</sub>  | On-resistance of<br>internal FET<br>during detection               | _                                                 | _       | _       | 50      | Ω    |

| R <sub>DS_DET_OFF</sub> | Off-resistance of<br>internal FET<br>after detection               | —                                                 | 2       | —       | —       | ΜΩ   |

| I <sub>OFFSET_DET</sub> | Input offset<br>current                                            | 1.1 V ≤ VPP ≤<br>10.1 V<br>T <sub>J</sub> ≤ 85 °C |         |         | 5       | μΑ   |

| V <sub>R_DET_ON</sub>   | R <sub>DET</sub><br>reconnection<br>threshold when<br>VPP goes low | -                                                 | 2.8     | 3.0     | 4.85    | V    |

#### Table 2-3. Classification Phase

| Symbol                  | Parameter                                         | Conditions | Minimum | Typical | Maximum | Unit |

|-------------------------|---------------------------------------------------|------------|---------|---------|---------|------|

| V <sub>CLS_ON</sub>     | Classification<br>sink turn-on<br>threshold       |            | 11.4    |         | 13.7    | V    |

| V <sub>CLS_OFF</sub>    | Classification<br>sink turn-off<br>threshold      | —          | 20.9    | —       | 23.9    | V    |

| V <sub>HYS_CLS_ON</sub> | Hysteresis of<br>V <sub>CLS_ON</sub><br>threshold |            |         | 1       |         | V    |

| V <sub>MARK_TH</sub>    | Mark detection<br>threshold<br>(VPP falling)      | —          | 10.1    | —       | 11.4    | V    |

| I <sub>MARK</sub>       | Current sink in<br>mark event<br>region           |            | 0.25    |         | 4       | mA   |

### **Electrical Specifications**

| continu                 | continued                         |                                                  |         |         |         |      |  |  |  |  |

|-------------------------|-----------------------------------|--------------------------------------------------|---------|---------|---------|------|--|--|--|--|

| Symbol                  | Parameter                         | Conditions                                       | Minimum | Typical | Maximum | Unit |  |  |  |  |

| I <sub>CLASS_CLIM</sub> | Current limit of<br>class current | —                                                | 50      | 68      | 80      | mA   |  |  |  |  |

| I <sub>CLASS</sub>      | Classification current sink       | R <sub>CLASS</sub> = not<br>present (Class<br>0) |         |         | 3       | mA   |  |  |  |  |

|                         |                                   | $R_{CLASS} = 133$<br>$\Omega$ (Class 1)          | 9.5     | 10.5    | 11.5    |      |  |  |  |  |

|                         |                                   | R <sub>CLASS</sub> = 69.8<br>Ω (Class 2)         | 17.5    | 18.5    | 19.5    | -    |  |  |  |  |

|                         |                                   | $R_{CLASS} = 45.3$ 26.5 28.0 29.5 Ω (Class 3)    | 29.5    |         |         |      |  |  |  |  |

|                         |                                   | $R_{CLASS} = 30.9$<br>$\Omega$ (Class 4)         | 38.0    | 40.0    | 42.0    |      |  |  |  |  |

#### Table 2-4. Isolation FET

| Symbol                   | Parameter                                    | Conditions                                                                                                   | Minimum | Typical | Maximum | Unit |

|--------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------|---------|---------|------|

| R <sub>DSON</sub>        | On resistance                                | Total<br>resistance<br>between<br>VPN_IN to<br>VPN_OUT;<br>$I_{LOAD} < 600$<br>mA, -40 °C <<br>$T_A < 85$ °C |         | 0.22    | 0.3     | Ω    |

| I <sub>CLIM_INRUSH</sub> | Inrush current<br>limit                      | —                                                                                                            | 105     | 240     | 325     | mA   |

| OCP                      | Overcurrent protection                       |                                                                                                              | 2.2     |         |         | A    |

| I <sub>LOAD</sub>        | Continuous<br>operation<br>load <sup>1</sup> | —                                                                                                            | —       | —       | 2       | A    |

**Note:** 1. Actual maximum load is subjected to the application environment conditions, such as ambient temperatures, air flow, mutual heating by other components, and so on.

#### Table 2-5. Undervoltage Lockout

| Symbol              | Parameter                                                 | Minimum | Maximum | Unit |

|---------------------|-----------------------------------------------------------|---------|---------|------|

| UVLO <sub>ON</sub>  | Threshold that marks start of inrush phase                | 36      | 42      | V    |

| UVLO <sub>OFF</sub> | Threshold where<br>pass-FET turns off as<br>VPP collapses | 30.5    | 34.5    | V    |

### **Electrical Specifications**

| Symbol               | Parameter                       | Conditions                                          | Minimum    | Maximum | Unit     |

|----------------------|---------------------------------|-----------------------------------------------------|------------|---------|----------|

| I <sub>CAP_DIS</sub> | Discharge current<br>(PD70210)  | 12 V ≤ VPP ≤ 30<br>V<br>7 V ≤ VPP ≤ 12 V            | 22.8<br>10 | 60      | mA<br>mA |

| I <sub>CAP_DIS</sub> | Discharge current<br>(PD70210A) | 7 V ≤ VPP ≤ 30 V                                    | 22.8       | 60      | mA       |

| timer <sub>dis</sub> | Discharge timer                 | Time for which<br>discharge circuit<br>is activated | 430        |         | ms       |

#### Table 2-6. DC–DC Input Cap Discharger

### Table 2-7. References, Rails, and Logic

| Symbol                 | Parameter                                                               | Conditions                                                                         | Minimum | Typical | Maximum | Unit |

|------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------|---------|---------|------|

| V <sub>AUX</sub>       | Auxiliary<br>voltage                                                    | 0 mA < I <sub>AUX</sub> <<br>4 mA                                                  | 9.8     | 10.5    | 12.0    | V    |

| I <sub>AUX_CLIM</sub>  | Auxiliary current limit                                                 | —                                                                                  | 10      | —       | 32      | mA   |

| V <sub>REF</sub>       | Bias current<br>reference<br>voltage                                    | —                                                                                  | 1.17    | 1.2     | 1.23    | V    |

| V <sub>FLAG_LO</sub>   | Low level flag                                                          | For AT_FLAG,<br>HD_FLAG,<br>4P_AT_FLAG,<br>4P_HD_FLAG,<br>I <sub>FLAG</sub> = 3 mA |         |         | 0.4     | V    |

| V <sub>PGOOD_LO</sub>  | Power good,<br>active low<br>voltage                                    | I <sub>PGOOD</sub> = 3 mA<br>PD70210 only                                          | _       | _       | 0.4     | V    |

| t <sub>FLAG</sub>      | Delay timer<br>between start<br>of inrush and<br>flags declared         | For AT_FLAG,<br>HD_FLAG,<br>4P_AT_FLAG,<br>4P_HD_FLAG                              | 80      | -       | -       | ms   |

| t <sub>PGOOD</sub>     | Delay timer<br>between start<br>of inrush and<br>power good<br>declared | PD70210 only                                                                       | 80      | —       | —       | ms   |

| IFLAG_max              | Flag current<br>driving<br>capability                                   | For AT_FLAG,<br>HD_FLAG,<br>4P_AT_FLAG,<br>4P_HD_FLAG                              | 5       |         | _       | mA   |

| I <sub>PGOOD_max</sub> | Power good<br>current<br>capability                                     | PD70210 only                                                                       | 5       | _       | —       | mA   |

### **Electrical Specifications**

| continued            |                                      |                            |         |         |         |      |

|----------------------|--------------------------------------|----------------------------|---------|---------|---------|------|

| Symbol               | Parameter                            | Conditions                 | Minimum | Typical | Maximum | Unit |

| V <sub>SUPP_HI</sub> | SUPP_Sx high<br>voltage<br>threshold | For SUPP_S1<br>and SUPP_S2 | 25      | —       | 35      | V    |

#### Table 2-8. Wall Adapter Enable Pin

| Symbol          | Parameter        | Conditions                  | Minimum | Maximum | Unit |

|-----------------|------------------|-----------------------------|---------|---------|------|

| V <sub>IH</sub> | Input high logic | PD70210A,<br>PD70210AL only | 2.4     |         | V    |

| V <sub>IL</sub> | Input low logic  | PD70210A,<br>PD70210AL only |         | 0.8     | V    |

#### 2.1 Absolute Maximum Ratings

Performance is not guaranteed over this entire range. These are maximum stress ratings only. Exceeding these ratings cause immediate damage or negatively impact long-term operating reliability. Voltages are with respect to IC ground (VPN\_IN), unless otherwise specified.

#### Table 2-9. Absolute Maximum Ratings

| Parameter                                                                   |                              | Minimum | Maximum                | Units |

|-----------------------------------------------------------------------------|------------------------------|---------|------------------------|-------|

| VPP, RDET                                                                   |                              | -0.3    | 74                     | V     |

| PGOOD, AT_FLAG, HD_FLAG,<br>4P_AT_FLAG, 4P_HD_FLAG referenced to<br>VPN_OUT |                              | -0.3    | 20                     | V     |

| SUPP_S1, SUPP_S2                                                            |                              | 0       | V <sub>VPP</sub> + 1.5 | V     |

| RREF, RCLS, WA_EN                                                           |                              | -0.3    | 5                      | V     |

| Junction temperature                                                        |                              | -40     | 150                    | °C    |

| Lead soldering temper                                                       | ature (40 s, reflow)         |         | 260                    | °C    |

| Storage temperature, I                                                      | MSL3                         | -65     | 150                    | °C    |

| ESD rating                                                                  | HBM (PD70210)                | —       | ±1.5                   | kV    |

|                                                                             | HBM (PD70210A/<br>PD70210AL) | _       | ±1.25                  | kV    |

|                                                                             | MM                           | —       | ±100                   | V     |

|                                                                             | CDM                          | _       | ±500                   | V     |

### **Electrical Specifications**

### 2.2 Operating Conditions

Performance is guaranteed over this range as described in other electrical characteristics tables. Voltages are with respect to IC ground (VPN\_IN).

#### Table 2-10. Operating Conditions

| Conditions                       | Minimum | Maximum | Units |

|----------------------------------|---------|---------|-------|

| VPP                              | 0       | 57      | V     |

| Ambient temperature <sup>1</sup> | -40     | 85      | °C    |

| Detection range                  | 1.1     | 10.1    | V     |

| Mark event range                 | 4.9     | 10.1    | V     |

| Class event range                | 13.7    | 20.9    | V     |

**Note:** 1. Corresponding maximum operating junction temperature is 125 °C.

#### 2.3 Thermal Properties

The following table shows the thermal properties of the device.

#### Table 2-11. Thermal Properties

| Thermal Resistance | Typical | Units |

|--------------------|---------|-------|

| θ <sub>JA</sub>    | 31      | °C/W  |

| θ <sub>JP</sub>    | 3       | °C/W  |

| θ <sub>JC</sub>    | 4       | °C/W  |

**Note:**  $\theta_{JX}$  numbers assume no forced airflow. Junction temperature is calculated using  $T_J = T_A + (P_D \times \theta_{JA})$ .  $\theta_{JA}$  is a function of the PCB construction. The stated number is for a four-layer board in accordance with JESD-51 (JEDEC<sup>®</sup>).

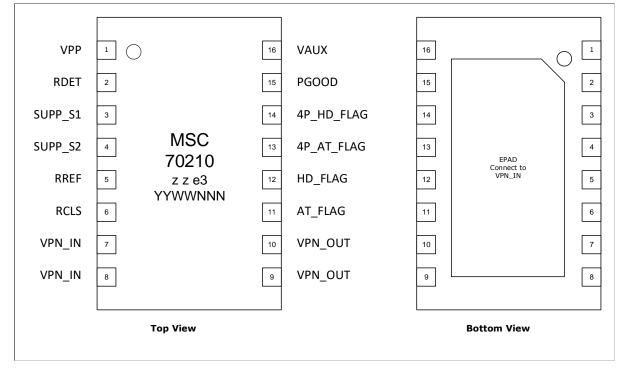

# 3. Pin Descriptions

This section provides the pin information for the PD70210/PD70210A/PD7021AL devices.

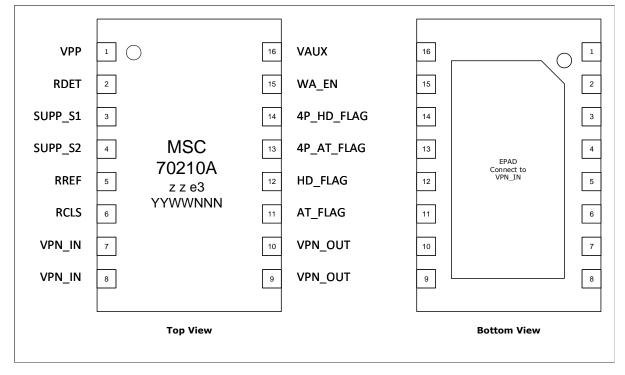

The following figures show the device pin diagrams (top and bottom views).

#### Figure 3-1. PD70210 Pinout

Figure 3-2. PD70210A Pinout

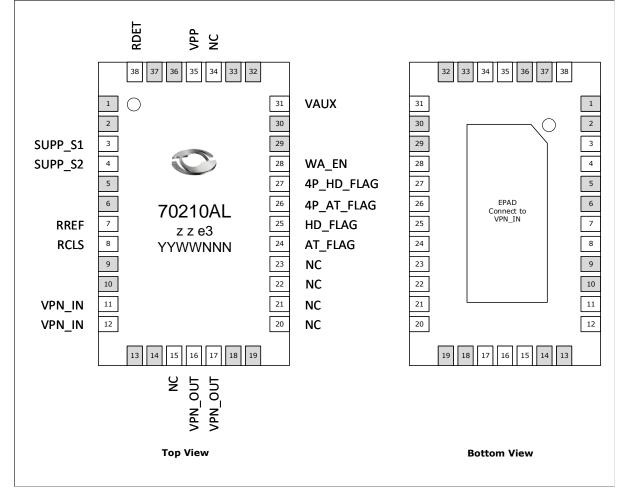

### **Pin Descriptions**

#### Figure 3-3. PD70210AL Pinout

Note: Shaded pins do not exist.

The following table lists the pin descriptions for the PD70210/PD70210A devices.

Table 3-1. PD70210/PD70210A Pin Descriptions

| Pin<br>Number | Pin Name<br>(PD70210A) | Pin Name<br>(PD70210) | Description                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | VPP                    | VPP                   | Upper rail of the incoming PSE voltage rail from the positive terminal of the two OR-ed bridge rectifiers. The corresponding lower PoE rail is VPN_IN.                                                                                                                                                                                                                                               |

| 2             | RDET                   | RDET                  | Internally connects to VPN_IN during detection phase and disengages after it is over. A 25 K $\Omega$ (or 24.9 K $\Omega$ ) 1 % resistor is connected between this pin and VPP.                                                                                                                                                                                                                      |

| 3             | SUPP_S1                | SUPP_S1               | Input pin for sensing the voltage on the diode bridge connected to the data pairs. This pin, along with the SUPP_S2 pin, can be used to distinguish between 2-pair and 4-pair operation for PSEs that operate in 4-pairs but do not generate the classification procedure on both pairs, but one pair only. Signal is referenced to VPN_IN. Place a 10 K $\Omega$ resistor in the input of this pin. |

# **Pin Descriptions**

| contii        | continued              |                       |                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|---------------|------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin<br>Number | Pin Name<br>(PD70210A) | Pin Name<br>(PD70210) | Description                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 4             | SUPP_S2                | SUPP_S2               | Input pin for sensing the voltage on the diode bridge connected to the data pairs. This pin, along with the SUPP_S1 pin, can be used to distinguish between 2-pair and 4-pair operation for PSEs that operate in 4-pairs but do not generate the classification procedure on both pairs, but one pair only. Signal is referenced to VPN_IN. Place a 10 K $\Omega$ resistor in the input of this pin.              |  |

| 5             | RREF                   | RREF                  | Bias current resistor. A 60.4 K $\Omega$ 1 % resistor is connected between RREF and IC ground (VPN_IN).                                                                                                                                                                                                                                                                                                           |  |

| 6             | RCLS                   | RCLS                  | Sets the class of the PD. Connect R <sub>CLASS</sub> (programming resistor) between this pin and IC ground (VPN_IN). Allowed values are 133 $\Omega$ , 69.8 $\Omega$ , 45.3 $\Omega$ , and 30.9 $\Omega$ for Class 1, 2, 3, and 4, respectively. If RCLASS is not present, the PD will draw up to 3 mA during classification, indicating Class 0 (default type 1) to the PSE. Signal is referenced to VPN_IN.     |  |

| 7,8           | VPN_IN                 | VPN_IN                | Lower rail of the incoming PSE voltage rail, from the negative terminal of the two OR-ed bridge rectifiers. The corresponding upper PoE rail is VPP.                                                                                                                                                                                                                                                              |  |

| 9,10          | VPN_OUT                | VPN_OUT               | In effect, the switched ground for establishing continuity to<br>the PWM section after successful detection, classification,<br>and power-up. It is connected to the power ground and<br>PWM controller IC's ground plane of the DC–DC<br>converter section.                                                                                                                                                      |  |

| 11            | AT_FLAG                | AT_FLAG               | Open drain output. This pin gets actively pulled low when<br>a type 2 PD-PSE mutually identifies each other through<br>classification. In PD70210A, there is a minimum 80 ms<br>delay from the moment that the input capacitor is fully<br>charged to this signal activity. In PD70210, this flag<br>asserts once inrush current is ended. Signal is referenced<br>to VPN_OUT.                                    |  |

| 12            | HD_FLAG                | HD_FLAG               | Open drain output. This pin gets actively pulled low when<br>a 2-pair HDBaseT PD-PSE mutually identifies each other<br>through classification. In PD70210A, there is a minimum<br>80 ms delay from the moment that the input capacitor is<br>fully charged to this signal activity. In PD70210, this flag<br>asserts once inrush current is ended. Signal is referenced<br>to VPN_OUT.                            |  |

| 13            | 4P_AT_FLAG             | 4P_AT_FLAG            | Open drain output. This pin gets actively pulled low when<br>a 4-pair version of a (non-standard) type 2 PD-PSE<br>mutually identifies each other through classification. In<br>PD70210A, there is a minimum 80 ms delay from the<br>moment that the input capacitor is fully charged to this<br>signal activity. In PD70210, this flag asserts once inrush<br>current is ended. Signal is referenced to VPN_OUT. |  |

### **Pin Descriptions**

| contii        | nued                   |                       |                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>Number | Pin Name<br>(PD70210A) | Pin Name<br>(PD70210) | Description                                                                                                                                                                                                                                                                                                                                                                            |

| 14            | 4P_HD_FLAG             | 4P_HD_FLAG            | Open drain output. This pin gets actively pulled low when<br>a 4-pair HDBaseT PD-PSE mutually identifies each other<br>through classification. In PD70210A, there is a minimum<br>80 ms delay from the moment that the input capacitor is<br>fully charged to this signal activity. In PD70210, this flag<br>asserts once inrush current is ended. Signal is referenced<br>to VPN_OUT. |

| 15            | WA_EN                  |                       | While this input is low (referenced to VPN_IN), the chip works according to internal flow diagram. When this input is high, it enables the wall adapter feature. Place from 100 nF/10 V to 1 $\mu$ F/10 V capacitor from WA_EN to VPN_IN pins, close to the device. When WA_EN is not used, connect it to VPN_IN. For more information, see Figure 1-3.                                |

|               |                        | PGOOD                 | Open drain output. Power good output signal from the front-end stage. This pin gets actively pulled low when power-on occurs. There is a minimum 80 ms delay from the moment VPort exceeds UVLO (~36 V) to this PGOOD signal being driven low as per the IEEE standard, to allow the PSE to increase its current limit after power-up is completed. Signal is referenced to VPN_OUT.   |

| 16            | VAUX                   | VAUX                  | Auxiliary voltage rail. This can be used to provide a few mA of startup current for the PWM controller (typically, 10.5 V). Signal is referenced to VPN_OUT and is activated once the front-end power-up sequence ends. DC-DC must not start up until Vaux is active.                                                                                                                  |

|               | EPAD                   | EPAD                  | Connected on PCB plane to VPN_IN.                                                                                                                                                                                                                                                                                                                                                      |

The following table lists the pin descriptions for the PD70210AL device.

#### Table 3-2. PD70210AL Pin Descriptions

| Pin Number | Pin Name | Description                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2       | NA       |                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3          | SUPP_S1  | Input pin for sensing the voltage on the diode bridge connected to the data pairs. This pin, along with the SUPP_S2 pin, can be used to distinguish between 2-pair and 4-pair operation for PSEs that operate in 4-pairs but do not generate the classification procedure on both pairs, but one pair only. Signal is referenced to VPN_IN. Place a 10 K $\Omega$ resistor in the input of this pin. |

| 4          | SUPP_S2  | Input pin for sensing the voltage on the diode bridge connected to the data pairs. This pin, along with the SUPP_S1 pin, can be used to distinguish between 2-pair and 4-pair operation for PSEs that operate in 4-pairs but do not generate the classification procedure on both pairs, but one pair only. Signal is referenced to VPN_IN. Place a 10 K $\Omega$ resistor in the input of this pin. |

| 5,6        | NA       |                                                                                                                                                                                                                                                                                                                                                                                                      |

# **Pin Descriptions**

| Pin Number         Pin Name         Description           7         RREF         Bias current resistor. A 60.4 K0 1% resistor is connected between RREF<br>and IC ground (VPN_IN).           8         RCLS         Sets the class of the PD. Connect R <sub>CLASS</sub> (programming resistor) between<br>this pin and IC ground (VPN_IN). Allowed values are 133.0, 693.0, 453.<br>0, and 30.9 Ω for Class.1, 2.3, and 4, respectively.1 RCLASS is not<br>present, the PD will draw up to 3 mA during classification, indicating Class 0<br>(default type 1) to the PSE. Signal is referenced to VPN_IN.           9, 10         NA         Lower rail of the incoming PSE voltage rail, from the negative terminal of<br>the two OR-ed bridge rectifiers. The corresponding upper PoE rail is VPP.           13, 14         NA         In effect, the switched ground for establishing continuity to the PWM section<br>after successful detection, classification, and power-up. It is connected to<br>the power ground and PWM controller IC's ground plane of the DC-DC<br>converter section.           18, 19         NA           20, 21, 22, 23         NC         No connect.           24         AT_FLAG         Open drain output. This pin gets actively pulled low when a type 2 PD-PSE<br>isignal activity. Signal is referenced to VPN_OUT.           25         HD_FLAG         Open drain output. This pin gets actively pulled low when a 2-pair HDBaseT<br>PD-PSE mutually identifies each other through classification. There is a<br>minimum 80 ms delay from the moment that the input capacitor is fully<br>charged to this signal activity. Signal is referenced to VPN_OUT.           26         4P_AT_FLAG                                                                                                            | continued      |            |                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| and IC ground (VPN_IN).       8     RCLS     Sets the class of the PD. Connect R <sub>CLASS</sub> (programming resistry) between the pD wind (VPN_IN). Allowed values are 133 0, 69.8 0, 45.3 0, and 30 0 for Class 1, 2, 3, and 4, respectively. If RCLASS is not present, the PD will draw up to 3 mA during classification, indicating Class 0 (default type 1) to the PSE. Signal is referenced to VPN_IN.       9, 10     NA       11, 12     VPN_IN     Lower rail of the incoming PSE voltage rail, from the negative terminal of the WO OR-ed bridge rectifiers. The corresponding upper POE rail is VPP.       13, 14     NA       15     NC     No connect.       16, 17     VPN_OUT     In effect, the switched ground for establishing continuity to the PVM sector on the power ground and PVM controller IC's ground plane of the DC-DC converter section.       18, 19     NA       20, 21, 22, 23     NC     No connect.       24     AT_FLAG     Open drain output. This pin gets actively pulled low when a type 2 PD-PSE mutually identifies each other through classification. There is a minimum 80 ms delay from the moment that the input capacitor is fully charged to this signal activity. Signal is referenced to VPN_OUT.       25     HD_FLAG     Open drain output. This pin gets actively pulled low when a 2-pair HDBaseT PD-PSE mutually identifies each other through classification. There is a minimum 80 ms delay from the moment that the input capacitor is fully charged to this signal activity. Signal is referenced to VPN_OUT.       26     4P_AT_FLAG     Open drain output. This pin gets actively pulled low when a 4-pair HDBaseT PD-PSE m                                                                                                                                                        | Pin Number     | Pin Name   | Description                                                                                                                                                                                                                                                  |

| this pin and 1C ground (VPN_IN). Allowed values are 133, 069.8 0, 45.3         0, and 30.9 G for Class 1.2, 3. and 4, respectively. If RCLASS is not present, the PD will draw up to 3 mA during classification, indicating Class 0 (default type 1) to the PSE. Signal is referenced to VPN_IN.         9, 10       NA         11, 12       VPN_IN         Lower rail of the incoming PSE voltage rail, from the negative terminal of the two OR-ed bridge rectifiers. The corresponding upper PoE rail is VPP.         13, 14       NA         15       NC       No connect.         16, 17       VPN_OUT       In effect, the switched ground for establishing continuity to the PVM section the power ground and PVM controller IC's ground plane of the DC-DC converter section.         18, 19       NA         20, 21, 22, 23       NC       No connect.         24       AT_FLAG       Open drain output. This pin gets actively pulled low when a type 2 PD-PSE mutually identifies each other through classification. There is a minimum 80 ms delay from the moment that the input capacitor is fully charged to this signal activity. Signal is referenced to VPN_OUT.         25       HD_FLAG       Open drain output. This pin gets actively pulled low when a 4-pair version of a (non-standard) type 2 PD-PSE mutually identifies each other through classification. There is a minimum 80 ms delay from the moment that the input capacitor is fully charged to this signal activity. Signal is referenced to VPN_OUT.         26       4P_AT_FLAG       Open drain output. This pin gets actively pu                                                                                                                                                                                                                           | 7              | RREF       |                                                                                                                                                                                                                                                              |

| 11, 12       VPN_IN       Lower rail of the incoming PSE voltage rail, from the negative terminal of the two OR-ed bridge rectifiers. The corresponding upper PoE rail is VPP.         13, 14       NA         15       NC       No connect.         16, 17       VPN_OUT       In effect, the switched ground for establishing continuity to the PWM section after successful detection, classification, and power-up. It is connected to the power ground and PWM controller IC's ground plane of the DC-DC converter section.         18, 19       NA         20, 21, 22, 23       NC       No connect.         24       AT_FLAG       Open drain output. This pin gets actively pulled low when a type 2 PD-PSE mutually identifies each other through classification. There is a minimum 80 ms delay from the moment that the input capacitor is fully charged to this signal activity. Signal is referenced to VPN_OUT.         25       HD_FLAG       Open drain output. This pin gets actively pulled low when a 2-pair HDBaseT PD-PSE mutually identifies each other through classification. There is a minimum 80 ms delay from the moment that the input capacitor is fully charged to this signal activity. Signal is referenced to VPN_OUT.         26       4P_AT_FLAG       Open drain output. This pin gets actively pulled low when a 4-pair HDBaseT PD-PSE mutually identifies each other through classification is fully charged to this signal activity. Signal is referenced to VPN_OUT.         27       4P_AT_FLAG       Open drain output. This pin gets actively pulled low when a 4-pair HDBaseT PD-PSE mutually identifies each other through classifica                                                                                                                                                               | 8              | RCLS       | this pin and IC ground (VPN_IN). Allowed values are 133 $\Omega$ , 69.8 $\Omega$ , 45.3 $\Omega$ , and 30.9 $\Omega$ for Class 1, 2, 3, and 4, respectively. If RCLASS is not present, the PD will draw up to 3 mA during classification, indicating Class 0 |

| InstructionThe two OR-ed bridge rectifiers. The corresponding upper PoE rail is VPP.13, 14NA15NCNo connect.16, 17VPN_OUTIn effect, the switched ground for establishing continuity to the PWM section<br>after successful detection, classification, and power-up. It is connected to<br>the power ground and PVM controller IC's ground plane of the DC-DC<br>converter section.18, 19NA20, 21, 22, 23NCNo connect.24AT_FLAGOpen drain output. This pin gets actively pulled low when a type 2 PD-PSE<br>mutually identifies each other through classification. There is a minimum 80<br>ms delay from the moment that the input capacitor is fully charged to this<br>signal activity. Signal is referenced to VPN_OUT.25HD_FLAGOpen drain output. This pin gets actively pulled low when a 2-pair HDBaseT<br>PD-PSE mutually identifies each other through classification. There is a<br>minimum 80 ms delay from the moment that the input capacitor is fully<br>charged to this signal activity. Signal is referenced to VPN_OUT.264P_AT_FLAGOpen drain output. This pin gets actively pulled low when a 4-pair version of<br>a (non-standard) type 2 PD-PSE mutually identifies each other through classification. There is a<br>minimum 80 ms delay from the moment that the input capacitor is fully<br>charged to this signal activity. Signal is referenced to<br>VPN_OUT.274P_AT_FLAGOpen drain output. This pin gets actively pulled low when a 4-pair version of<br>a (non-standard) type 2 PD-PSE mutually identifies each other through classification. There is a<br>minimum 80 ms delay from the moment that the<br>input capacitor is fully charged to this signal activity. Signal is referenced to<br>VPN_OUT.274P_                                                                                                           | 9, 10          | NA         |                                                                                                                                                                                                                                                              |

| 15         NC         No connect.           16, 17         VPN_OUT         In effect, the switched ground for establishing continuity to the PWM section after successful detection, classification, and power-up. It is connected to the power ground and PWM controller IC's ground plane of the DC-DC converter section.           18, 19         NA           20, 21, 22, 23         NC         No connect.           24         AT_FLAG         Open drain output. This pin gets actively pulled low when a type 2 PD-PSE mutually identifies each other through classification. There is a minimum 80 ms delay from the moment that the input capacitor is fully charged to this signal activity. Signal is referenced to VPN_OUT.           25         HD_FLAG         Open drain output. This pin gets actively pulled low when a 2-pair HDBaseT PD-PSE mutually identifies each other through classification. There is a minimum 80 ms delay from the moment that the input capacitor is fully charged to this signal activity. Signal is referenced to VPN_OUT.           26         4P_AT_FLAG         Open drain output. This pin gets actively pulled low when a 4-pair version of a (non-standard) type 2 PD-PSE mutually identifies each other through classification. There is a minimum 80 ms delay from the moment that the input capacitor is fully charged to this signal activity. Signal is referenced to VPN_OUT.           27         4P_AT_FLAG         Open drain output. This pin gets actively pulled low when a 4-pair Version of a (non-standard) type 2 PD-PSE mutually identifies each other through classification. There is a minimum 80 ms delay from the moment that the input capacitor is fully charged to this signal activity. Sig                                                                        | 11, 12         | VPN_IN     |                                                                                                                                                                                                                                                              |

| 16, 17       VPN_OUT       In effect, the switched ground for establishing continuity to the PWM section after successful detection, classification, and power-up. It is connected to the power ground and PVMM controller IC's ground plane of the DC-DC converter section.         18, 19       NA         20, 21, 22, 23       NC       No connect.         24       AT_FLAG       Open drain output. This pin gets actively pulled low when a type 2 PD-PSE mutually identifies each other through classification. There is a minimum 80 ms delay from the moment that the input capacitor is fully charged to this signal activity. Signal is referenced to VPN_OUT.         25       HD_FLAG       Open drain output. This pin gets actively pulled low when a 2-pair HDBaseT PD-PSE mutually identifies each other through classification. There is a minimum 80 ms delay from the moment that the input capacitor is fully charged to this signal activity. Signal is referenced to VPN_OUT.         26       4P_AT_FLAG       Open drain output. This pin gets actively pulled low when a 4-pair version of a (non-standard) type 2 PD-PSE mutually identifies each other through classification. There is a minimum 80 ms delay from the moment that the input capacitor is fully charged to this signal activity. Signal is referenced to VPN_OUT.         27       4P_AT_FLAG       Open drain output. This pin gets actively pulled low when a 4-pair VPN_OUT.         28       WA_EN       While this input is low (referenced to VPN_IN), the chip works according to internal flow diagram. When this signal activity. Signal is referenced to VPN_OUT.         28       WA_EN       While this input                                                                                                                             | 13, 14         | NA         |                                                                                                                                                                                                                                                              |

| after successful detection, classification, and power-up. It is connected to<br>the power ground and PWM controller IC's ground plane of the DC-DC<br>converter section.18, 19NA20, 21, 22, 23NCNo connect.24AT_FLAGOpen drain output. This pin gets actively pulled low when a type 2 PD-PSE<br>mutually identifies each other through classification. There is a minimum 80<br>ms delay from the moment that the input capacitor is fully charged to this<br>signal activity. Signal is referenced to VPN_OUT.25HD_FLAGOpen drain output. This pin gets actively pulled low when a 2-pair HDBaseT<br>PD-PSE mutually identifies each other through classification. There is a<br>minimum 80 ms delay from the moment that the input capacitor is fully<br>charged to this signal activity. Signal is referenced to VPN_OUT.264P_AT_FLAGOpen drain output. This pin gets actively pulled low when a 4-pair version of<br>a (non-standard) type 2 PD-PSE mutually identifies each other through<br>classification. There is a minimum 80 ms delay from the moment that the<br>input capacitor is fully<br>charged to this signal activity. Signal is referenced to<br>VPN_OUT.274P_HD_FLAGOpen drain output. This pin gets actively pulled low when a 4-pair HDBaseT<br>PD-PSE mutually identifies each other through classification. There is a<br>minimum 80 ms delay from the moment that the input capacitor is fully<br>charged to this signal activity. Signal is referenced to VPN_OUT.28WA_ENWhile this input is low (referenced to VPN_IN), the chip works according to<br>internal flow diagram. When this input is high, tenables the wall adapter<br>feature. Place from 100 nF/10 V to 1 µF/10 V capacitor from WA_EN to<br>VPN_IN pins, close to the device. When WA_EN is not used, connect it to<br>VPN_IN. For more in           | 15             | NC         | No connect.                                                                                                                                                                                                                                                  |

| 20, 21, 22, 23NCNo connect.24AT_FLAGOpen drain output. This pin gets actively pulled low when a type 2 PD-PSE<br>mutually identifies each other through classification. There is a minimum 80<br>ms delay from the moment that the input capacitor is fully charged to this<br>signal activity. Signal is referenced to VPN_OUT.25HD_FLAGOpen drain output. This pin gets actively pulled low when a 2-pair HDBaseT<br>PD-PSE mutually identifies each other through classification. There is a<br>minimum 80 ms delay from the moment that the input capacitor is fully<br>charged to this signal activity. Signal is referenced to VPN_OUT.264P_AT_FLAGOpen drain output. This pin gets actively pulled low when a 4-pair version of<br>a (non-standard) type 2 PD-PSE mutually identifies each other through<br>classification. There is a minimum 80 ms delay from the moment that the<br>input capacitor is fully<br>charged to this signal activity. Signal is referenced to<br>VPN_OUT.274P_HD_FLAGOpen drain output. This pin gets actively pulled low when a 4-pair HDBaseT<br>PD-PSE mutually identifies each other through<br>classification. There is a minimum 80 ms delay from the moment that the<br>input capacitor is fully<br>charged to this signal activity. Signal is referenced to<br>VPN_OUT.28WA_ENWhile this input is low (referenced to VPN_N). The chip works according to<br>internal flow diagram. When this input is high, it enables the wall adapter<br>feature. Place from 100 nF/10 V to 1 µF/10 V capacitor from WA_EN to<br>VPN_N. N. For more information, see Figure 1-3.29,30NA31VAUXAuxiliary voltage rail. This is used to provide a few mA of startup current for<br>the PVM controller (typically, 10.5 V). Signal is referenced to VPN_OUT<br>and is activated once the front-end                     | 16, 17         | VPN_OUT    | after successful detection, classification, and power-up. It is connected to the power ground and PWM controller IC's ground plane of the DC–DC                                                                                                              |

| 24       AT_FLAG       Open drain output. This pin gets actively pulled low when a type 2 PD-PSE mutually identifies each other through classification. There is a minimum 80 ms delay from the moment that the input capacitor is fully charged to this signal activity. Signal is referenced to VPN_OUT.         25       HD_FLAG       Open drain output. This pin gets actively pulled low when a 2-pair HDBaseT PD-PSE mutually identifies each other through classification. There is a minimum 80 ms delay from the moment that the input capacitor is fully charged to this signal activity. Signal is referenced to VPN_OUT.         26       4P_AT_FLAG       Open drain output. This pin gets actively pulled low when a 4-pair version of a (non-standard) type 2 PD-PSE mutually identifies each other through classification. There is a minimum 80 ms delay from the moment that the input capacitor is fully charged to this signal activity. Signal is referenced to VPN_OUT.         27       4P_HD_FLAG       Open drain output. This pin gets actively pulled low when a 4-pair version of a (non-standard) type 2 PD-PSE mutually identifies each other through classification. There is a minimum 80 ms delay from the moment that the input capacitor is fully charged to this signal activity. Signal is referenced to VPN_OUT.         27       4P_HD_FLAG       Open drain output. This pin gets actively pulled low when a 4-pair HDBaseT PD-PSE mutually identifies each other through classification. There is a minimum 80 ms delay from the moment that the input capacitor is fully charged to this signal activity. Signal is referenced to VPN_OUT.         28       WA_EN       While this input is low (referenced to VPN_IN), the chip works according to internal flow diagram. When this input is high, it | 18, 19         | NA         |                                                                                                                                                                                                                                                              |

| Imitually identifies each other through classification. There is a minimum 80<br>ms delay from the moment that the input capacitor is fully charged to this<br>signal activity. Signal is referenced to VPN_OUT.25HD_FLAGOpen drain output. This pin gets actively pulled low when a 2-pair HDBaseT<br>PD-PSE mutually identifies each other through classification. There is a<br>minimum 80 ms delay from the moment that the input capacitor is fully<br>charged to this signal activity. Signal is referenced to VPN_OUT.264P_AT_FLAGOpen drain output. This pin gets actively pulled low when a 4-pair version of<br>a (non-standard) type 2 PD-PSE mutually identifies each other through<br>classification. There is a minimum 80 ms delay from the moment that the<br>input capacitor is fully charged to this signal activity. Signal is referenced to<br>VPN_OUT.274P_HD_FLAGOpen drain output. This pin gets actively pulled low when a 4-pair HDBaseT<br>PD-PSE mutually identifies each other through classification. There is a<br>minimum 80 ms delay from the moment that the input capacitor is fully<br>charged to this signal activity. Signal is referenced to<br>VPN_OUT.28WA_ENWhile this input is low (referenced to VPN_IN), the chip works according to<br>internal flow diagram. When this input is high, it enables the wall adapter<br>feature. Place from 100 nF/10 V to 1 µF/10 V capacitor from WA_EN to<br>VPN_IN. For more information, see Figure 1-3.29,30NAMa31VAUXAuxiliary voltage rail. This is used to provide a few mA of startup current for<br>the PWM controller (typically, 10.5 V). Signal is referenced to VPN_OUT<br>and is activated once the front-end power-up sequence ends. DC-DC<br>should not start up until Vaux is active.                                                               | 20, 21, 22, 23 | NC         | No connect.                                                                                                                                                                                                                                                  |

| PD-PSE mutually identifies each other through classification. There is a<br>minimum 80 ms delay from the moment that the input capacitor is fully<br>charged to this signal activity. Signal is referenced to VPN_OUT.264P_AT_FLAGOpen drain output. This pin gets actively pulled low when a 4-pair version of<br>a (non-standard) type 2 PD-PSE mutually identifies each other through<br>classification. There is a minimum 80 ms delay from the moment that the<br>input capacitor is fully charged to this signal activity. Signal is referenced to<br>VPN_OUT.274P_HD_FLAGOpen drain output. This pin gets actively pulled low when a 4-pair HDBaseT<br>PD-PSE mutually identifies each other through classification. There is a<br>minimum 80 ms delay from the moment that the input capacitor is fully<br>charged to this signal activity. Signal is referenced to<br>VPN_OUT.28WA_ENWhile this input is low (referenced to VPN_IN), the chip works according to<br>internal flow diagram. When this input is high, it enables the wall adapter<br>feature. Place from 100 nF/10 V to 1 µF/10 V capacitor from WA_EN to<br>VPN_IN. For more information, see Figure 1-3.29,30NA31VAUXAuxiliary voltage rail. This is used to provide a few mA of startup current for<br>the PWM controller (typically, 10.5 V). Signal is referenced to VPN_OUT<br>and is activated once the front-end power-up sequence ends. DC-DC<br>should not start up until Vaux is active.                                                                                                                                                                                                                                                                                                                                                                        | 24             | AT_FLAG    | mutually identifies each other through classification. There is a minimum 80 ms delay from the moment that the input capacitor is fully charged to this                                                                                                      |

| a (non-standard) type 2 PD-PSE mutually identifies each other through<br>classification. There is a minimum 80 ms delay from the moment that the<br>input capacitor is fully charged to this signal activity. Signal is referenced to<br>VPN_OUT.274P_HD_FLAGOpen drain output. This pin gets actively pulled low when a 4-pair HDBaseT<br>PD-PSE mutually identifies each other through classification. There is a<br>minimum 80 ms delay from the moment that the input capacitor is fully<br>charged to this signal activity. Signal is referenced to<br>VPN_OUT.28WA_ENWhile this input is low (referenced to VPN_IN), the chip works according to<br>internal flow diagram. When this input is high, it enables the wall adapter<br>feature. Place from 100 nF/10 V to 1 µF/10 V capacitor from WA_EN to<br>VPN_IN pins, close to the device. When WA_EN is not used, connect it to<br>VPN_IN_EN more information, see Figure 1-3.29,30NA31VAUXAuxiliary voltage rail. This is used to provide a few mA of startup current for<br>the PWM controller (typically, 10.5 V). Signal is referenced to VPN_OUT<br>and is activated once the front-end power-up sequence ends. DC-DC<br>should not start up until Vaux is active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25             | HD_FLAG    | PD-PSE mutually identifies each other through classification. There is a minimum 80 ms delay from the moment that the input capacitor is fully                                                                                                               |

| PD-PSE mutually identifies each other through classification. There is a<br>minimum 80 ms delay from the moment that the input capacitor is fully<br>charged to this signal activity. Signal is referenced to VPN_OUT.28WA_ENWhile this input is low (referenced to VPN_IN), the chip works according to<br>internal flow diagram. When this input is high, it enables the wall adapter<br>feature. Place from 100 nF/10 V to 1 µF/10 V capacitor from WA_EN to<br>VPN_IN pins, close to the device. When WA_EN is not used, connect it to<br>VPN_IN. For more information, see Figure 1-3.29,30NA31VAUXAuxiliary voltage rail. This is used to provide a few mA of startup current for<br>the PWM controller (typically, 10.5 V). Signal is referenced to VPN_OUT<br>and is activated once the front-end power-up sequence ends. DC-DC<br>should not start up until Vaux is active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 26             | 4P_AT_FLAG | a (non-standard) type 2 PD-PSE mutually identifies each other through classification. There is a minimum 80 ms delay from the moment that the input capacitor is fully charged to this signal activity. Signal is referenced to                              |

| internal flow diagram. When this input is high, it enables the wall adapter<br>feature. Place from 100 nF/10 V to 1 µF/10 V capacitor from WA_EN to<br>VPN_IN pins, close to the device. When WA_EN is not used, connect it to<br>VPN_IN. For more information, see Figure 1-3.29,30NA31VAUXAuxiliary voltage rail. This is used to provide a few mA of startup current for<br>the PWM controller (typically, 10.5 V). Signal is referenced to VPN_OUT<br>and is activated once the front-end power-up sequence ends. DC-DC<br>should not start up until Vaux is active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27             | 4P_HD_FLAG | PD-PSE mutually identifies each other through classification. There is a minimum 80 ms delay from the moment that the input capacitor is fully                                                                                                               |

| 31VAUXAuxiliary voltage rail. This is used to provide a few mA of startup current for<br>the PWM controller (typically, 10.5 V). Signal is referenced to VPN_OUT<br>and is activated once the front-end power-up sequence ends. DC-DC<br>should not start up until Vaux is active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28             | WA_EN      | internal flow diagram. When this input is high, it enables the wall adapter feature. Place from 100 nF/10 V to 1 $\mu$ F/10 V capacitor from WA_EN to VPN_IN pins, close to the device. When WA_EN is not used, connect it to                                |