# PD69208M and PD69200 Datasheet 8-Port PSE PoE Manager and PSE PoE Controller

September 2019

# **Contents**

| 1 | Revis | sion History                                    | 1    |

|---|-------|-------------------------------------------------|------|

|   | 1.1   | Revision 6.0                                    | 1    |

|   | 1.2   | Revision 5.0                                    | 1    |

|   | 1.3   | Revision 4.0                                    | 1    |

|   | 1.4   | Revision 3.0                                    | 2    |

|   | 1.5   | Revision 2.0                                    | 2    |

|   | 1.6   | Revision 1.2                                    | 2    |

|   | 1.7   | Revision 1.1                                    | 2    |

|   | 1.8   | Revision 1.0                                    | 2    |

| 2 | Over  | view                                            | 3    |

|   | 2.1   | Features                                        | 4    |

|   | 2.2   | Applications                                    | 4    |

|   | 2.3   | Typical PoE Application                         | 5    |

| 3 | Func  | tional Descriptions                             | 6    |

|   | 3.1   | Digital Block Module                            | 6    |

|   | 3.2   | PD Detection Generator                          | 6    |

|   | 3.3   | Classification Generator                        | 6    |

|   | 3.4   | Current Limiter                                 | 7    |

|   | 3.5   | Main Power MOSFET                               | 7    |

|   | 3.6   | Analog to Digital Converter                     | 7    |

|   | 3.7   | Power on Reset                                  | 7    |

|   | 3.8   | Voltage Regulator                               | 7    |

|   | 3.9   | Clock                                           | 7    |

|   | 3.10  | SPI Communication                               | 8    |

|   | 3.11  | PD69208M SPI Addressing                         | 8    |

|   | 3.12  | Broadcast                                       | 8    |

|   | 3.13  | SPI Timing                                      | 9    |

|   | 3.14  | PD69200 I2C Address Selection                   | . 10 |

| 4 | Elect | rical Specifications                            | 11   |

|   | 4.1   | PD69200 Electrical Characteristics and Features | . 11 |

|   | 4.2   | PD69208M Electrical Characteristics             |      |

|   | 4     | I.2.1 Electrical Characteristics                |      |

|   | 4     | I.2.2 Detection                                 |      |

|   | 4     | 1.2.3 Classification                            |      |

|   | 4     | I.2.4 Port Real Time Protection                 | . 14 |

|   | 4     | 1.2.5 Port Current Monitoring                   | . 15 |

|                                                                                                                                                | 4.2.6    | 5 Port Voltage Monitoring                                  | 15         |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------|------------|

|                                                                                                                                                | 4.2.7    | 7 Main Voltage Monitoring                                  | 15         |

|                                                                                                                                                | 4.2.8    | B Temperature Monitoring                                   | 16         |

|                                                                                                                                                | 4.2.9    | Digital Interface                                          | 16         |

|                                                                                                                                                | 4.2.1    | LO Immunity                                                | 16         |

|                                                                                                                                                | 4.3 Ab   | solute Maximum Ratings                                     | 17         |

| 5                                                                                                                                              | Pin Desc | criptions                                                  | 18         |

| J                                                                                                                                              |          | n Configuration and Pinout                                 |            |

|                                                                                                                                                |          | 69200 and PD69208M Pin Descriptions                        |            |

|                                                                                                                                                | 5.2.1    | ·                                                          |            |

|                                                                                                                                                | 5.2.2    | PD69208M Pin Descriptions                                  | 23         |

|                                                                                                                                                | 5.3 Re   | commended PCB Layouts                                      | 25         |

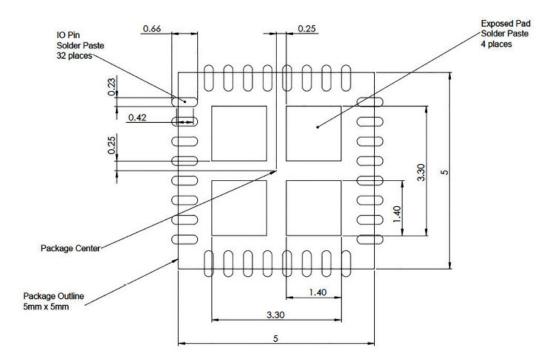

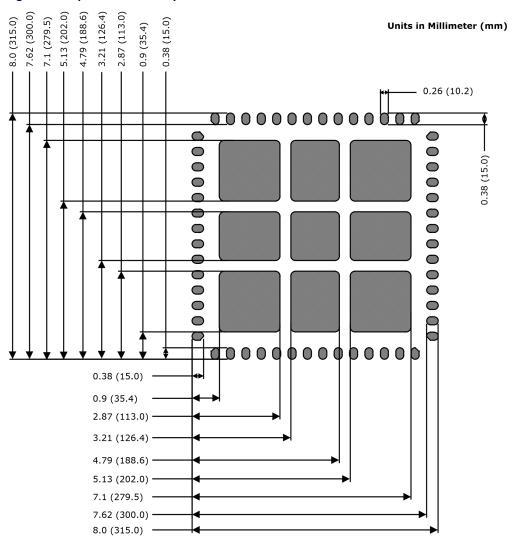

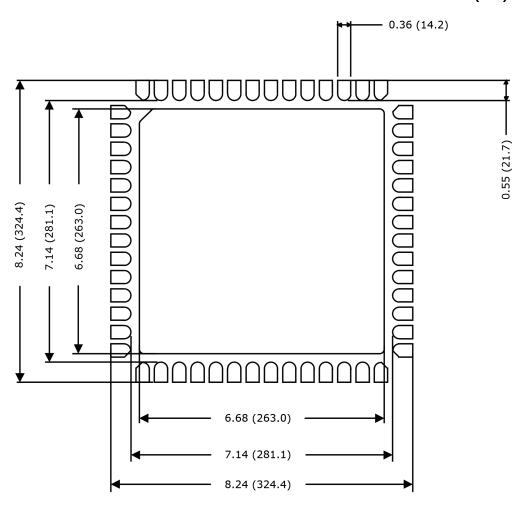

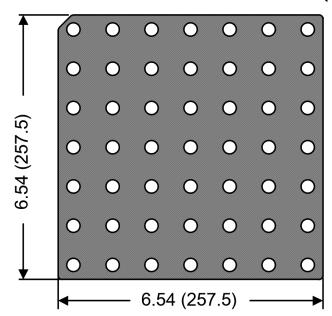

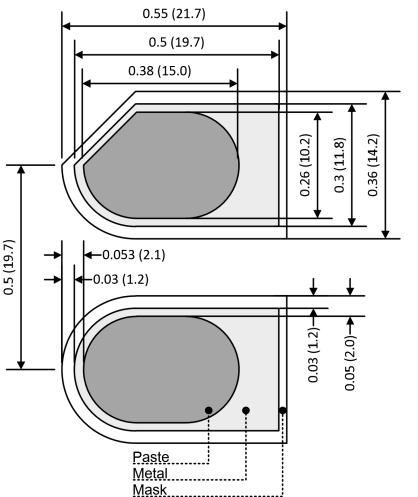

| 4 4 4 4 4 4 3 5 Pin D 5.1 5.2 5 5 5 5 6 Packa 6.1 6.2 6.3 6 6.4 7 Appli 7.1 7.2 7.3 7.4 7.5 7.6 7.7 7.8 7.9 7.10 7.11 7.12 7.13 7.14 7.15 7.16 | 5.3.1    | PD69200 Recommended PCB Layout for 32-Pin QFN 5 mm x 5 mm  | 25         |

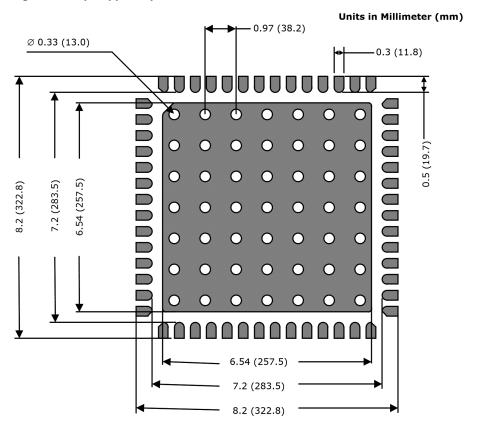

|                                                                                                                                                | 5.3.2    | PD69208M Recommended PCB Layout for 56-Pin QFN 8 mm x 8 mm | 27         |

| 6                                                                                                                                              | Package  | Specification                                              | 32         |

| Ŭ                                                                                                                                              | _        | ermal Specifications                                       |            |

|                                                                                                                                                |          | commended Solder Reflow                                    |            |

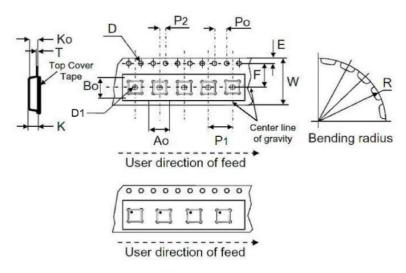

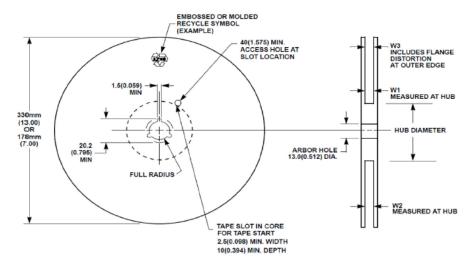

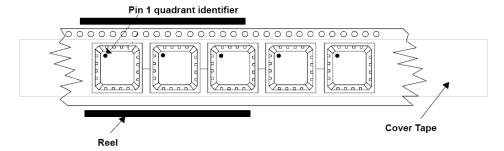

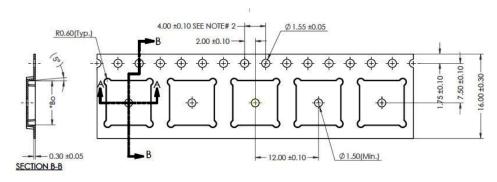

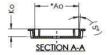

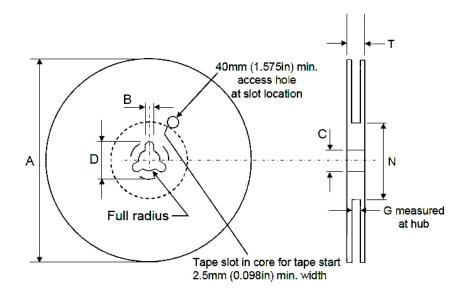

|                                                                                                                                                | 6.3 Ta   | pe and Reel                                                | 36         |

|                                                                                                                                                | 6.3.1    | PD69200 Tape and Reel Specification                        | 36         |

|                                                                                                                                                | 6.3.2    | PD69208M Tape and Reel Specification                       | 37         |

|                                                                                                                                                | 6.4 Re   | ference Documents                                          | 40         |

| 7                                                                                                                                              | Annlicat | ion Information                                            | <i>1</i> 1 |

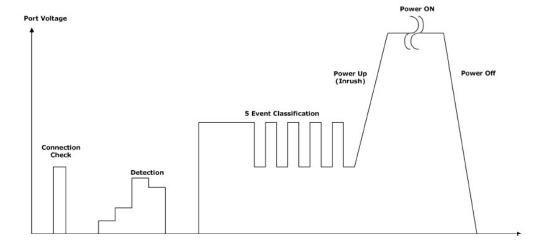

| •                                                                                                                                              |          | Detection                                                  |            |

|                                                                                                                                                |          | gacy (Reduced Capacitor) Detection                         |            |

|                                                                                                                                                | •        | assification                                               |            |

|                                                                                                                                                |          | rt Start-Up                                                |            |

|                                                                                                                                                |          | rer-Load Detection and Port Shut Down                      |            |

|                                                                                                                                                |          | sconnect Detection                                         |            |

|                                                                                                                                                |          | Thermal Monitoring                                         |            |

|                                                                                                                                                |          | ver-Temperature Protection                                 |            |

|                                                                                                                                                |          | MAIN Out of Range Protection                               |            |

|                                                                                                                                                |          | -Pair and 4-Pair Ports                                     |            |

|                                                                                                                                                |          | ower Management                                            |            |

|                                                                                                                                                |          | ort Power Limit                                            |            |

|                                                                                                                                                |          | eset Pin                                                   |            |

|                                                                                                                                                |          | ystem OK Indication                                        |            |

|                                                                                                                                                |          | nterrupt Pin                                               |            |

|                                                                                                                                                |          | ort Matrix Control                                         |            |

|                                                                                                                                                |          | ower Good Interrupt                                        |            |

|                                                                                                                                                |          | ED Stream                                                  |            |

|                                                                                                                                                |          |                                                            |            |

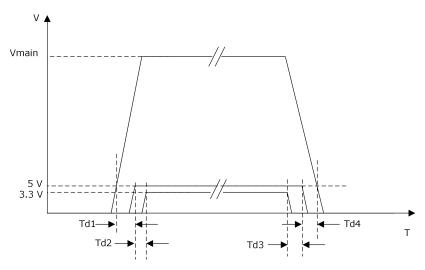

|   | 7.19  | Power Sequencing | 5  |

|---|-------|------------------|----|

| 8 | Order | ing Information4 | .6 |

# 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

## 1.1 Revision 6.0

Revision 6.0 of this document was published in September 2019. The following is a summary of the changes.

- Features (see page 4) list was updated.

- Typical PoE Application (see page 5) figure and note were updated.

- Fast PoE and Perpetual PoE were added to PD69200 Features Description (see page 11) table.

- Max accuracy value was updated in PD69208M Main Voltage Monitoring (see page 15) table.

- PD69208M Pin Diagram (see page 19), PD69200 Top-Layer Copper PCB Layout (see page 25), and PD69200 Top-Layer Solder Paste and Vias PCB Layout for Thermal Pad Array (see page 26) figures were updated.

- Typical Θ<sub>IB</sub> value was updated in PD69208M Thermal Specifications (see page 34) table.

- Typical IEEE802.3bt Port PoE Voltage Diagram (see page 42) was updated.

- Ordering Information (see page 46) was updated.

## 1.2 **Revision 5.0**

Revision 5.0 of this document was published in November 2018. The following was a summary of the changes.

- Updated the Features and Applications details.

- Port real time protection details are updated for IPORT, ILIM, ICUT, IUDL, PPWR, and TMPS.

- Port current monitoring information is updated for accuracy.

- Main voltage information is updated for accuracy.

- The PD69200 pin diagram is updated.

- The Top-Layer Pin Geometry measurement is updated.

- The PD692000 Thermal Specifications table is added.

- The company name Freescale is replaced with NXP across the document.

- Updated Figures 8 12.

- Added table footnotes for D, VVVV, and SS.

## 1.3 **Revision 4.0**

Revision 4.0 of this document was published in February 2018. The following was a summary of the changes.

- Preliminary designation was removed.

- Thermal specifications were updated.

- The tape specification was updated.

- Tape mechanical data was added.

- Ordering part numbers were updated.

#### 1.4 Revision 3.0

Revision 3.0 of this document was published in November 2017. The following was a summary of the changes.

- Maximum storage temperature value is no longer preliminary.

- The link to stencil and via plug recommendations was updated.

- Application information was updated.

- Maximum slew rate requirement of 100 mS was added.

- Manufacturing and ordering part number information was updated.

- Updated revision 2.0 history to include entry for the redefinition of quiescent current in terms of port threshold.

## 1.5 **Revision 2.0**

Revision 2.0 of this document was published in September 2017. The following was a summary of the changes.

- Updated the recommended PCB layout for better manufacturability.

- Redefined guiescent current in terms of port threshold.

- Added the PD69208M Manufacturing and Ordering Part Numbers table.

- Added a note about I<sup>2</sup>C communication configuration.

- Added table footnotes for ESD (HBM and CDM).

- Updated the main voltage monitoring table for accuracy data.

- Updated the Peak Classification Temperature (TP).

- Updated the description for pin 24 for PD69200.

- Updated the description for pin 19 for PD69208M.

- Updated the thermal specifications table.

- Changed the notation from VPORT\_NEGX to VPORT.

- Added a footnote for Absolute Storage Temperature in the table.

- Updated the accuracy values in the Port Current Monitoring table.

- Updated the Rsig\_Low and Rsig\_High values in the Detection table.

- Updated the LSB value in the Temperature Monitoring table.

- Updated the values for D11, D12, D15, D16, and D17 in the SPI Timing Diagram Description table.

## 1.6 **Revision 1.2**

Revision 1.2 of this document was published in August 2016. The following was a summary of the changes.

- According to PCN155881, qualification of UTAC Thailand assembly for PD6920X. Parts from UTAC will be identified by different marking that was added.

- Match 802.3af ILIM and Inrush levels to IEEE standard levels.

- Match 802.3at ILIM low level to IEEE standard levels.

## **1.7** Revision **1.1**

Revision 1.1 of this document was published in July 2016. The following was a summary of the changes.

- Updated the feature's list. Changed MSL1 of PD69208 to MSL3.

- Updated ordering information. Changed MSL1 of PD69208 to MSL3.

## 1.8 Revision 1.0

Revision 1.0 of this document was published in December 2015. This was the first publication.

## 2 Overview

Microsemi's PD69208M Power over Ethernet (PoE) manager IC integrates power, analog, and state-of-the-art logic into a single 56-pin, plastic QFN package. The device is used in Ethernet switches and Midspans to allow network devices to share power and data over the same cable. The PD69208M device is an 8-port, mixed-signal, and high-voltage PoE driver. Together with the PD69200 external MCU, it performs as a PSE system. Microsemi's PoE controller, PD69200, is a cost-effective, pre-programmed MCU designed to implement enhanced mode.

PD69208M/PD69200 chip-set supports PoE Powered Device (PD) detection, power-up, and protection according to IEEE standards, as well as legacy/pre-standard PD detection. It provides PD real-time protection through the following mechanisms: overload, under-load, over-voltage, over-temperature, and short-circuit, and enables operation in a standalone mode. It also executes all real-time functions as specified in IEEE802.3at and IEEE802.3bt Class 3.

PD69208M supports supply voltages between 32 V and 57 V without additional power supply sources. A system that powers over four pairs can be implemented by combining two ports of PD69208M, enabling an extra feature for a simple and low-cost, high-power PD device. Ongoing monitoring of system parameters for the host software is available via communication. Internal thermal protection is implemented in the chip. PD69208M is a low-power dissipation device that uses internal MOSFETs and internal  $100 \text{ m}\Omega$  sense resistors.

PD69200 features an ESPI bus for all PD69208M. It is developed based on NXP Kinetis\_L family, MKL15Z128VFM4, that is embedded with the ARM Cortex™-M0+ core. It also uses I²C or UART interface to the host CPU, and is designed to support software field upgradable through the communication interface.

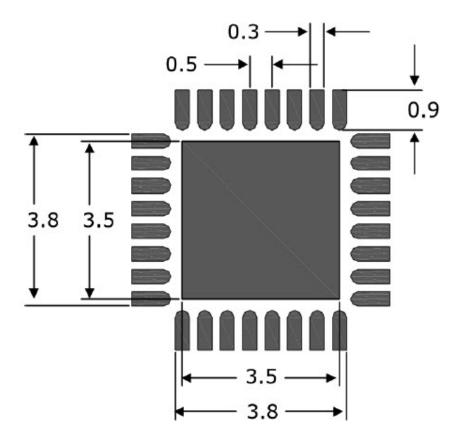

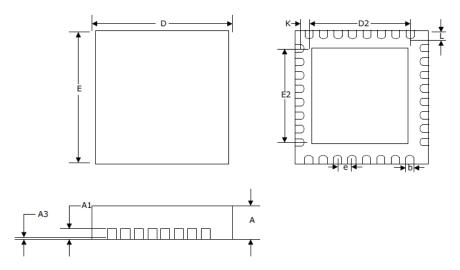

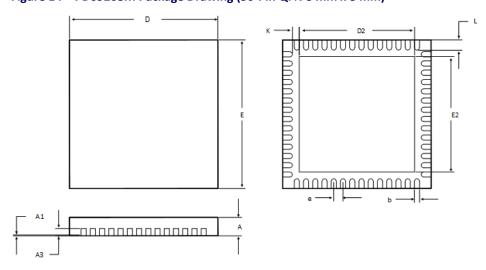

PD69208M is available in a 56-pin, 8 mm  $\times$  8 mm QFN package. PD69200 is available in 32-pin, 5 mm  $\times$  5 mm QFN package.

## 2.1 Features

- 8 independent channels

- Complies with IEEE802.3af-2003, IEEE802.3at-2009 (including two-event classification), and IEEE802.3bt

- Supports Fast PoE

- Supports Perpetual PoE

- Drives 2-pair power ports or 4-pair ports

- Supports pre-standard PD detection

- Single DC voltage input (32 V to 57 V)

- Built-in 3.3 V and 5 V regulators

- Input voltage out of range protection

- Wide ambient temperature range: –40 °C to 85 °C

- On-chip over-temperature thermal protection and monitoring

- Low-power dissipation (0.1  $\Omega$  sense resistor and 0.2  $\Omega$  MOSFET Rdson per channel)

- Includes Reset command pin

- 4× direct address configuration pins

- Continuous port monitoring and system data

- Configurable load current setting

- Configurable PSE AT/AF/BT-Type3 modes

- Power soft start mechanism

- Voltage monitoring/protection

- Internal power on reset

- Emergency power management supporting four configurable power bank I/Os

- Advance System Power Management algorithm supports up to 96 physical ports

- Can be cascaded to up to 12 PoE devices (96 ports)

- Supports both UART and I<sup>2</sup>C interfaces to host CPU

- Backwards compatible with Microsemi communication protocol used at prior generations

- LED stream support

- System OK indication

- Software download via I<sup>2</sup>C or UART

- Detailed port status

- Programmable threshold temperature alarm limit

- Interrupt out pin for system and port events

- Forced port power ON function

- Port power limit setting

- Port matrix and priority

- Automatic PoE device type detection

- MSL3, RoHS compliant

# 2.2 Applications

- Power over Ethernet (all IEEE compliant 2-pair modes)

- Supports 4-pair and IEEE802.3bt PSE Type 3

- Switches/Routers/Midspans

- Industrial automation

- PoE for LED lighting

# 2.3 Typical PoE Application

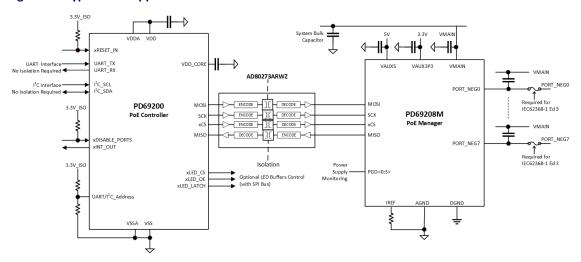

The following figure illustrates the typical PoE application of PD69208M and PD69200 devices.

Figure 1 • Typical PoE Application

**Note:** For complete reference design, see Microsemi AN211 Designing an IEEE 802.3af/802.3at/802.3bt-Compliant PD69208 48-Port PoE System (Document Number: PD-000300282).

Fuses per port are not required for use in circuits with a total power level of up to 3 kW. This is because PD69208 is a UL 2367 (category QVRQ2) recognized component and fulfills limited power source (LPS) requirements of the latest editions of IEC60950-1 and EN60950-1. However, IEC62368-1 Ed 3 (released in October 2018 and becomes effective December 2020) requires per-port fuses for a system power supply greater than 250 W.

# **3** Functional Descriptions

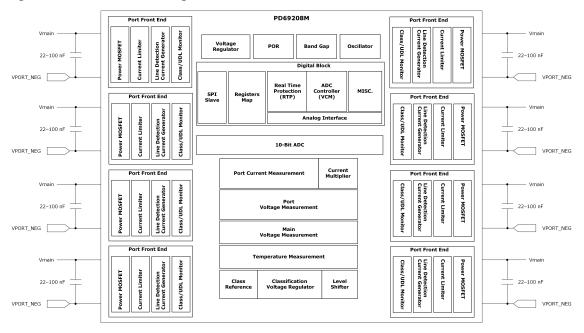

The following illustration shows the functional blocks of PD69208M.

Figure 2 • PD69208M Block Diagram

The following sections describe the functional blocks of PD69208M.

# 3.1 Digital Block Module

The logic main control block includes digital timing mechanisms and state machines synchronizing and activating PoE functions according to PD69200 control commands, such as:

- Real Time Protection (RTP)

- Start Up Macro (DVDT)

- Load Signature Detection (RES DET)

- Classification Macro (CLASS)

- Voltage and Current Monitoring (VCM)

- ADC Interfacing

- Direct Digital Signals with Analog Block

- SPI Communication Block

- Registers

## 3.2 PD Detection Generator

Upon request from PD69200 to main control module, the PD detection generator generates four different voltage levels to ensure a robust AF/AT/BT PD detection functionality.

## 3.3 Classification Generator

Upon request from PD69200 to main control module, the state machine applies a regulated class event and mark event voltage to ports, as required by IEEE standards.

## 3.4 Current Limiter

This circuit continuously monitors the current of powered ports and limits the current to a pre-defined value set by AF/AT. When the current value exceeds this specific value, the system starts measuring the elapsed timing. If this interval is greater than a preset threshold, the port is disconnected.

## 3.5 Main Power MOSFET

Main power switching FET is used to control PoE current into the load.

## 3.6 Analog to Digital Converter

A 10-bit analog to digital converter (ADC) is used to convert analog signals into digital registers for the logic control module.

#### 3.7 Power on Reset

Power on reset (PoR) monitors the internal 3.3 V and 5 V DC levels. If this voltage drops down below the specified threshold limit, a reset signal is generated and PD69208M is reset.

## 3.8 Voltage Regulator

The voltage regulator generates 3.3 V and 5 V for internal circuitry. These voltages are derived from V<sub>MAIN</sub> supply. Connect the following to use the internal voltage regulator:

- VAUX5 to DRV\_VAUX5

- VAUX3P3 to VAUX3P3 INT

The following three options reduce PD69208M power dissipation by regulating the voltage outside the chip:

- Use an external NPN transistor to regulate the 5 V. In this setup, the configuration of regulator pins should be as follows:

- DRV VAUX5 is connected to NPN BASE

- VAUX5 is connected to NPN EMITTER (Connect Collector to VMAIN)

- Vaux3p3 is connected to Vaux3p3\_int

- Supply PD69208M with an external 5 V regulator. In this setup, regulator pins configuration should be as follows:

- VAUX3P3 is connected to VAUX3P3\_INT

- DRV\_VAUX5 is not connected (left open)

- VAUX5 is connected to external 5 V

- Supply PD69208M with an external 3.3 V regulator. In this setup, regulator pins configuration should be as follows:

- VAUX5 is connected to DRV\_VAUX5

- VAUX3P3 INT is not connected (left open)

- VAUX3P3 is connected to external 3.3 V

These options can be implemented simultaneously to reduce PD69208M power dissipation.

## 3.9 Clock

PD69208M clock (CLK) is an internal 8 MHz clock oscillator.

## 3.10 SPI Communication

PD69208M uses SPI communication in SPI slave mode to communicate with the PD69200 MCU. Each PD69208M has an address determined by ADDR0-ADDR3 pins. The PD69200 can support up to 12 ICs. The actual frequency between PD69200 and PD69208M ICs is 1 MHz.

The following table lists the SPI communication packet structure.

Table 1 • SPI Communication: Packet Structure

| Control Byte Selects PD69208M<br>According to the Address | R/W Bit   | Internal<br>Register Address | Number of Words<br>(Only in Read Access) | Data Written to IC (in Write Access) Read from IC (in Read Access) |

|-----------------------------------------------------------|-----------|------------------------------|------------------------------------------|--------------------------------------------------------------------|

| 8 bits                                                    | R(0)/W(1) | 8 bits                       | 8 bits                                   | 16 bits                                                            |

## 3.11 PD69208M SPI Addressing

PD69208M operates in 8-bit address and 16-bit data. It responds to SPI transaction if the first SPI byte (IC address byte bits[7:1]) complies with the following:

Table 2 • SPI Addressing

| 3 Bits (Bit 7:5) | 4 Bits (Bit 4:1)  | 1 Bit (Bit 0) |

|------------------|-------------------|---------------|

| 000              | Address Input Pin | Read/Write    |

## 3.12 Broadcast

- A broadcast command is intended to instruct all connected PD69208M ICs to perform a specific operation

- The broadcast command is a write command with the standard packet structure. In case of a broadcast read operation, the read data is not valid and the read operation has no impact.

Table 3 • Broadcast

| 3 Bits (Bit 7:5) | 4 Bits (Bit 4:1) | 1 Bit (Bit 0) |

|------------------|------------------|---------------|

| 001              | 0000             | Write         |

# 3.13 SPI Timing

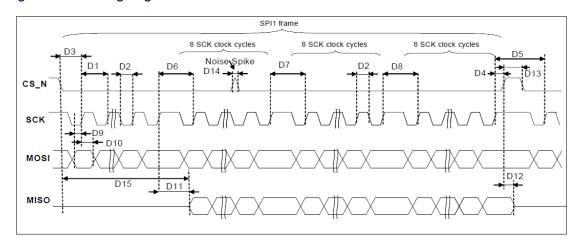

Figure 3 • SPI Timing Diagram

**Table 4 • SPI Timing Diagram Description**

| Name | Min Delay   | Max Delay     | Description                                                                     |

|------|-------------|---------------|---------------------------------------------------------------------------------|

| D1   | 910 ns      |               | SPI clock period                                                                |

| D2   | 45%         | 55%           | SPI duty cycle                                                                  |

| D3   | 340 ns      |               | SPI_CS setup to SPI clock positive edge (delay after SPI_CS active signal)      |

| D4   | 340 ns      |               | SPI_CS hold to SPI clock positive edge (delay before SPI_CS inactive signal)    |

| D5   | 2 SPI clock |               | Delay between the last SCK in eSPI1 frame and first SCK at adjacent eSPI1 frame |

|      | cycles      |               |                                                                                 |

| D6   | 1 SPI clock |               | Between byte 0 (IC address) and byte 1 (address)                                |

|      | cycles      |               |                                                                                 |

| D7   | 1 SPI clock |               | Between byte 1 (address) and byte 2 (data)                                      |

|      | cycles      |               |                                                                                 |

| D8   | 1 SPI clock |               | Between byte 2 (MS data byte) and byte 3 (LS data byte)                         |

|      | cycles      |               |                                                                                 |

| D9   | 340 ns      |               | MOSI setup time                                                                 |

| D10  | 340 ns      |               | MOSI hold time                                                                  |

| D11  |             | 700 ns        | MISO tri-state to valid data from clock positive edge                           |

| D12  |             | 700 ns        | MISO valid data to tri-state from SPI_CS positive edge                          |

| D13  | 1 SPI clock |               | SPI_CS width (Delay eSPI1 frame to adjacent eSPI1 frame)                        |

|      | cycles      |               |                                                                                 |

| D14  |             | 60 ns         | Filtered glitch width                                                           |

| D15  |             | D3 + D11 + 24 | MISO tri-state from SPI_CS negative edge to valid data                          |

|      |             | SPI clock     |                                                                                 |

|      |             | cycles        |                                                                                 |

| D16  | 200 ns      |               | MISO setup to SCK positive edge                                                 |

| D17  | 200 ns      |               | MISO hold to SCK positive edge                                                  |

## 3.14 PD69200 I2C Address Selection

The I<sup>2</sup>C interface between the host CPU and a specific PD69200 requires setting the PD69200 address. This is done by applying a specific voltage level to pin #22 (I2C\_ADDR\_MEAS), as listed in the following table.

Table 5 • I2C Address Selection

| I2C_ADDR Voltage Level | I <sup>2</sup> C Address (Hexadecimal) |

|------------------------|----------------------------------------|

| 0.00 to 0.21 VDC       | UART                                   |

| 0.21 to 0.41 VDC       | 0x4                                    |

| 0.41 to 0.62 VDC       | 0x8                                    |

| 0.62 to 0.83 VDC       | 0xC                                    |

| 0.83 to 1.03 VDC       | 0x10                                   |

| 1.03 to 1.24 VDC       | 0x14                                   |

| 1.24 to 1.44 VDC       | 0x18                                   |

| 1.44 to 1.65 VDC       | 0x1C                                   |

| 1.65 to 1.86 VDC       | 0x20                                   |

| 1.86 to 2.06 VDC       | 0x24                                   |

| 2.06 to 2.27 VDC       | 0x28                                   |

| 2.27 to 2.48 VDC       | 0x2C                                   |

| 2.48 to 2.68 VDC       | 0x30                                   |

| 2.68 to 2.89 VDC       | 0x34                                   |

| 2.89 to 3.09 VDC       | 0x38                                   |

| 3.09 to 3.30 VDC       | 0x3C                                   |

## UART communications configuration:

• Bits per second: 19,200 bps

Data bits: 8Parity: NoneStop bits: 1

• Flow control: None

I<sup>2</sup>C communication configuration:

Address: 7 bits

Host should support clock stretchTransaction: 15 bytes or 1 byte

# 4 Electrical Specifications

The following sections describe the electrical characteristics of PD69208M and PD69200 devices.

## 4.1 PD69200 Electrical Characteristics and Features

In this application, PD69200 consumption is ~20 mA.

- Manufacturer: NXP

- Manufacturer part number: MKL15Z128VFM4

- Maximum pull-ups consumption based on PD69200 application is 2 mA. See the hardware application note (Catalog Number: PD69208\_AN\_211).

Table 6 • PD69200 Features Description

| Features                                                               | Description                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Supports up to 12 PoE<br>devices: 96 physical ports<br>(48 logical)    | Up to 12 PoE devices can be cascaded, fitting into a 96-physical-port PoE system that uses one PoE controller (PD69200). PD69200 can support up to 48 logical ports. A logical port can be built from 2× physical ports or 1× physical port.                                                                                     |

| Power management                                                       | The system supports three power management modes: Class (LLDP), Dynamic, and Static.                                                                                                                                                                                                                                             |

| Threshold configuration                                                | Over-voltage and under-voltage thresholds can be configured for disconnection purposes.                                                                                                                                                                                                                                          |

| Fast PoE                                                               | Ability of a system to quickly boot and power-up ports without loading EEPROM firmware.                                                                                                                                                                                                                                          |

| Perpetual PoE                                                          | Ability of a PoE system to maintain PoE power while switch host firmware is being loaded.                                                                                                                                                                                                                                        |

| High-power ports, 2-pair or 4-pair                                     | PoE devices can be configured (both hardware and software) to enable higher current through ports (up to ~627 mA) or double power at the RJ in case of 4 pairs.                                                                                                                                                                  |

| Communication                                                          | Supports both I <sup>2</sup> C and UART interfaces with host CPU.                                                                                                                                                                                                                                                                |

| Legacy (reduced capacitance) detection                                 | Enables detection and powering of pre-standard devices (PDs) up to 30 uF.                                                                                                                                                                                                                                                        |

| LED stream                                                             | Provides a direct SPI interface to an external LED stream circuitry. Enables designers to implement a simple LED circuit that does not require a software code. LED stream clock frequency is 1 MHz.                                                                                                                             |

| System OK indication                                                   | Provides a digital output pin to host. System validity indication, when system OK pin state is low. This output behavior is controlled by software mask register settings (Mask 0×28). The mask default settings is 0, meaning that this pin indicates valid software and V <sub>MAIN</sub> is in range. This pin is active low. |

|                                                                        | For more information, see the Serial Communication Protocol User Guide document (Catalog Number: PD69200_UG_COMM_PROT).                                                                                                                                                                                                          |

| System and port measurements                                           | Measurements of the following parameters: Current (mA), Power Consumption (W), V <sub>MAIN</sub> (V), Port Voltage (V), and PD Class (0–4).                                                                                                                                                                                      |

| Detailed port status                                                   | Port statuses are received from PoE managers. Statuses such as port on and port off due to disconnection or due to overload.                                                                                                                                                                                                     |

| Interrupt pin                                                          | Interrupt out from PoE controller (PD69200) indicating events such as: port on, port off, port fault, PoE device fault, voltage out of range, and more. For a full list of interrupt events, see the Serial Communication Protocol User Guide document (Catalog Number: PD69200_UG_COMM_PROT).                                   |

| Port power limit                                                       | Configurable port power limit; when a port exceeds the limit, it is automatically disconnected.                                                                                                                                                                                                                                  |

| Port matrix control                                                    | Enables layout designers to connect all physical ports to logical ports as required.                                                                                                                                                                                                                                             |

| "Power Good" interrupt<br>from power supply directly<br>to POE drivers | For systems comprising more than a single power supply, when one power supply fails, a fast port disconnection mechanism is executed to maintain operation and prevent collapse of other power supplies.                                                                                                                         |

## 4.2 PD69208M Electrical Characteristics

Unless otherwise specified under conditions, the Min and Max ratings stated in the following table apply to the entire specified operating ratings of the device. Typ values stated are either by design or by production testing at 25 °C ambient.

## 4.2.1 Electrical Characteristics

**Table 7 • Electrical Characteristics**

| Symbol              | Parameter                                  | Conditions                                                           | Min   | Тур   | Max   | Units |

|---------------------|--------------------------------------------|----------------------------------------------------------------------|-------|-------|-------|-------|

| VMAIN               | Main supply voltage                        | Supports Full IEEE802.3 AF and AT functionality                      | 32    |       | 57    | V     |

| VPORT               | Port output                                | Vmain — Vport_negx                                                   | 0     |       | 57    | V     |

| V <sub>тн</sub>     | POR threshold                              | Internal or External 3.3 V supply                                    |       | 8     |       | V     |

| Imain               |                                            | Main power supply current at operating mode.V <sub>MAIN</sub> = 55 V |       | 14    |       | mA    |

| V <sub>AUX5</sub>   | 5 V output voltage                         | V <sub>AUX5</sub> —AGND                                              | 4.5   | 5     | 5.5   | V     |

| V <sub>AUX3P3</sub> | 3.3 V output voltage                       | Vauxapa—AGND                                                         | 3     | 3.3   | 3.6   | V     |

| <b>І</b> АИХЗРЗ     | 3.3 V output current                       | Without external NPN                                                 |       |       | 5     | mA    |

|                     | for application use                        | With external NPN transistor on V <sub>AUX5</sub>                    |       |       | 30    | mA    |

| Vaux3p3_in          | 3.3 V input voltage                        | Vaux3p3-AGND                                                         | 3     | 3.3   | 3.6   | V     |

| DV <sub>DD</sub>    | Digital 3.3 V input<br>voltage             | DV <sub>DD</sub> -DGND                                               | 3     | 3.3   | 3.6   | V     |

| PORTP               | Power-on reset DVDD trip point             | DV <sub>DD</sub> -DGND                                               | 2.575 | 2.775 | 2.975 | V     |

| PORHYS              | Power-on reset DV <sub>DD</sub> hysteresis | POR <sub>TP</sub> -DGND                                              | 0.2   | 0.25  | 0.3   | V     |

| Rch_on              | Total channel resistance                   | Rds_on + Rsense + Rbonding                                           |       | 0.34  |       | Ω     |

## 4.2.2 Detection

Table 8 • PD69208M Detection

| Symbol    | Parameter                                   | Conditions                                                                               | Min  | Тур | Max | Units |

|-----------|---------------------------------------------|------------------------------------------------------------------------------------------|------|-----|-----|-------|

| Voc       | Pre-detection voltage, open circuit voltage | V <sub>MAIN</sub> – V <sub>PORT_NEGx</sub> , open port                                   |      |     | 7.8 | V     |

| Vvalid    | Detection voltage                           | $V_{MAIN} - V_{PORT\_NEGx_y}$ for IEEE802.3 compliant signature resistance (RsIG < 33 K) |      |     | 9.3 | V     |

| İsc       | Short circuit current                       | Vmain - Vport_negx = 0 V                                                                 |      | 388 | 408 | μΑ    |

| Rsig_Low  | Minimum valid detection resistance          |                                                                                          | 15   |     | 19  | ΚΩ    |

| Rsig_High | Maximum valid detection resistance          |                                                                                          | 26.5 |     | 33  | ΚΩ    |

# 4.2.3 Classification

Table 9 • PD69208M Classification

| Symbol     | Parameter                      | Conditions                                                                     | Min  | Тур | Max  | Units |

|------------|--------------------------------|--------------------------------------------------------------------------------|------|-----|------|-------|

| VCLASS     | Class event output voltage     | V <sub>MAIN</sub> − V <sub>PORT_NEGx</sub> ; 0 mA ≤ I <sub>PORT</sub> ≤ 50 mA  | 15.5 | 18  | 20.5 | V     |

| Vmark      | Mark event output voltage      | V <sub>MAIN</sub> − V <sub>PORT_NEGx</sub> ; 0.1 mA ≤ I <sub>PORT</sub> ≤ 5 mA | 7    | 8.5 | 10   | V     |

| Iclass_lim | Class event current limitation | V <sub>MAIN</sub> - V <sub>PORT_NEGx</sub> = 0 V                               | 51   | 70  | 100  | mA    |

| IMARK_LIM  | Mark event current limitation  | V <sub>MAIN</sub> - V <sub>PORT_NEGx</sub> = 0 V                               | 51   | 70  | 100  | mA    |

|            | Classification current         | Class 0                                                                        | 0    |     | 5    | mA    |

|            | thresholds                     | Class 1                                                                        | 8    |     | 13   | mA    |

|            |                                | Class 2                                                                        | 16   |     | 21   | mA    |

|            |                                | Class 3                                                                        | 25   |     | 31   | mA    |

|            |                                | Class 4                                                                        | 35   |     | 45   | mA    |

|            |                                | Class error                                                                    | 51   |     | 100  | mA    |

## 4.2.4 Port Real Time Protection

Table 10 • PD69208M Port Real Time Protection

| Symbol           | Parameter                                            | Conditions                                                                                                   | Min | Тур | Max | Unit |

|------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Trise            | Turn on rise time                                    | From 10% to 90% of the voltage difference at the VPORT_NEGX in POWER_ON state from the beginning of POWER_UP | 15  |     |     | μs   |

| linrush          | Output current in POWER_UP state                     | Cload ≤ 180 μF¹                                                                                              | 400 | 425 | 450 | mA   |

| Tinrush          | Inrush time                                          |                                                                                                              |     |     | 65  | ms   |

| IPORT            | Output operating current                             | 802.3af                                                                                                      | 10  |     | 360 | mA   |

|                  |                                                      | 802.3at                                                                                                      | 10  |     | 620 | mA   |

|                  |                                                      | 802.3bt class 5                                                                                              | 10  |     | 560 | mA   |

|                  |                                                      | 802.3bt class 6                                                                                              | 10  |     | 692 | mA   |

| Ісит             | Overload current                                     | 802.3af                                                                                                      |     | 375 |     | mA   |

|                  |                                                      | 802.3at                                                                                                      |     | 645 |     | mA   |

|                  |                                                      | 802.3bt class 5                                                                                              |     | 589 |     | mA   |

|                  |                                                      | 802.3bt class 6                                                                                              |     | 709 |     | mA   |

| Тсит             | Overload time limit                                  |                                                                                                              | 62  | 64  | 66  | ms   |

| Інм              | Port current limit                                   | 802.3af                                                                                                      | 400 | 425 | 450 | mA   |

|                  |                                                      | 802.3bt class 1–3                                                                                            | 670 | 720 | 770 | mA   |

|                  |                                                      | 802.3at, 802.3bt class 4–6                                                                                   | 790 | 850 | 892 | mA   |

| Тим              | Port current limit time                              | Vmain – Vport_negx < 30 V                                                                                    | 1   | 2   | 3   | ms   |

| P <sub>PWR</sub> | Port power accuracy                                  | > 90 W                                                                                                       |     |     | 2   | %    |

| ludl             | DC disconnect                                        | 2 Pairs                                                                                                      | 6   | 7.5 | 9   | mA   |

|                  | Under-load current                                   | 4 Pairs (for each pair-set)                                                                                  | 2   | 2.5 | 3   | mA   |

| Тмро             | PD maintain power<br>signature dropout<br>time limit | 322 324                                                                                                      |     | 324 | 326 | ms   |

| Тмрѕ             | PD maintain power                                    | 802.3bt PSE type 1, 2                                                                                        | 46  | 48  | 50  | ms   |

|                  | Signature time for validity                          | 802.3bt PSE type 3, 4                                                                                        | 3   | 4   | 5   | ms   |

| Toff             | Turn off time                                        | From V <sub>MAIN</sub> to 2.8 V                                                                              |     |     | 500 | ms   |

<sup>1.</sup> Can be overridden by communication command.

## 4.2.5 Port Current Monitoring

Table 11 • PD69208M Port Current Monitoring

| Symbol             | Conditions                          | Тур    | Max | Units |

|--------------------|-------------------------------------|--------|-----|-------|

| Resolution         | Reported as 14 bits                 | 10     |     | Bits  |

| LSB                |                                     | 122.07 |     | μΑ    |

| Measurement period |                                     | 16     |     | ms    |

| Accuracy           | 50 mA < I <sub>PORT</sub> < 150 mA  |        | 9   | %     |

|                    | 150 mA < I <sub>PORT</sub> < 350 mA |        | 4.5 | %     |

|                    | 350 mA < I <sub>PORT</sub> < 600 mA |        | 3.5 | %     |

|                    | IPORT > 600 mA                      |        | 3.0 | %     |

# 4.2.6 Port Voltage Monitoring

**Table 12 • Port Voltage Monitoring**

| Symbol             | Тур  | Max | Units |

|--------------------|------|-----|-------|

| Resolution         | 10   |     | Bits  |

| LSB                | 58.6 |     | mV    |

| Measurement period | 3    |     | ms    |

| Accuracy           |      | 3.3 | %     |

# 4.2.7 Main Voltage Monitoring

Table 13 • PD69208M Main Voltage Monitoring

| Conditions                                   | Тур                                                                | Max                                                                                   | Units                                                                                        |

|----------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|                                              | 10                                                                 |                                                                                       | Bits                                                                                         |

|                                              | 58.6                                                               |                                                                                       | mV                                                                                           |

|                                              | 3                                                                  |                                                                                       | ms                                                                                           |

| 42 V < V <sub>MAIN</sub> < 50 V              |                                                                    | 2.1                                                                                   | %                                                                                            |

| 50 V < V <sub>MAIN</sub> < 57 V              |                                                                    | 1.5                                                                                   | %                                                                                            |

| 50 V < V <sub>MAIN</sub> < 57 V <sup>1</sup> |                                                                    | 0.6                                                                                   | %                                                                                            |

|                                              | 42 V < V <sub>MAIN</sub> < 50 V<br>50 V < V <sub>MAIN</sub> < 57 V | 10<br>58.6<br>3<br>42 V < V <sub>MAIN</sub> < 50 V<br>50 V < V <sub>MAIN</sub> < 57 V | 10<br>58.6<br>3<br>42 V < V <sub>MAIN</sub> < 50 V<br>50 V < V <sub>MAIN</sub> < 57 V<br>1.5 |

1. 0-70 °C

## 4.2.8 Temperature Monitoring

Table 14 • PD69208M Temperature Monitoring

| Symbol             | Conditions                          | Min | Тур    | Max | Units |

|--------------------|-------------------------------------|-----|--------|-----|-------|

| Resolution         |                                     |     | 8      |     | Bits  |

| LSB                | Temperature = (DATA x 1.9384) – 273 |     | 1.9384 |     | °C    |

| Measurement period |                                     |     | 3      |     | ms    |

| Accuracy           |                                     | -3  |        | 3   | °C    |

# 4.2.9 Digital Interface

Table 15 • PD69208M Digital Interface

| Symbol | Parameter                      | Conditions                                        | Min | Тур | Max | Units |

|--------|--------------------------------|---------------------------------------------------|-----|-----|-----|-------|

| ViH    | Input logic high voltage       | RESET_N, MOSI, MISO, SCK, CS_N, PGD[03], ADDR[03] | 2.2 |     |     | V     |

| VIL    | Input logic low voltage        | RESET_N, MOSI, MISO, SCK, CS_N, PGD[03], ADDR[03] |     |     | 0.8 | V     |

| Hyst   | Input logic hysteresis voltage | RESET_N, MOSI, MISO, SCK, CS_N, PGD[03], ADDR[03] | 0.4 | 0.6 | 0.8 | V     |

| Іін    | Input logic high current       | RESET_N, MOSI, MISO, SCK, CS_N, PGD[03], ADDR[03] | -10 |     | 10  | μА    |

| lı.    | Input logic low current        | RESET_N, MOSI, MISO, SCK, CS_N, PGD[03], ADDR[03] | -10 |     | 10  | μА    |

| Vон    | Output logic high voltage      | RESET_N, MOSI, MISO, SCK, CS_N, PGD[03], ADDR[03] | 2.4 |     |     | V     |

|        |                                | I <sub>OH</sub> = −1 mA                           |     |     |     |       |

| Vol    | Output logic low voltage       | RESET_N, MOSI, MISO, SCK, CS_N, PGD[03], ADDR[03] |     |     | 0.4 | V     |

|        |                                | I <sub>OH</sub> = 1 mA                            |     |     |     |       |

## **4.2.10** Immunity

Table 16 • PD69208M Immunity

| Symbol | Parameter                    | Conditions       | Min | Тур | Max | Units |

|--------|------------------------------|------------------|-----|-----|-----|-------|

| ESD    | ESD rating                   | HBM <sup>1</sup> |     |     |     |       |

|        |                              | CDM <sup>2</sup> |     |     |     |       |

| Surge  | Lightning surge <sup>3</sup> | EN61000 4-5      | -1  |     | 1   | KV    |

- 1. ESD HBM complies with JESD22 Class 2 standard.

- 2. ESD CDM complies with JESD22 Class 1 standard.

- 3. System-level common mode 10/700  $\mu S$  according to IEC61000-4-5.

# 4.3 Absolute Maximum Ratings

PoE performance is not guaranteed when exceeding the recommended rating. Exposure to any stress in the range between the recommended rating, as listed in the following table, and the absolute maximum rating should be limited to a short time. Exceeding these ratings may impact long-term operating reliability.

**Table 17 • Absolute Maximum Ratings**

| Parameters                                                              | Min         | Max                             | Units |

|-------------------------------------------------------------------------|-------------|---------------------------------|-------|

| Supply input voltage (V <sub>MAIN</sub> ) <sup>1, 2</sup>               | -0.3        | 72                              | V     |

| PORT_NEG[0.7] pins                                                      | -0.3        | V <sub>MAIN</sub> + 0.5         | V     |

| V <sub>AUX5</sub>                                                       | -0.3        | 6                               | V     |

| VAUX3P3, DVDD                                                           | -0.3        | 4                               | V     |

| Digital pins: MISO, MOSI, SCK, CS_N, ADDR[3:0], PGD[3:0], RESET_N, TRIM | -0.3        | D <sub>VDD</sub> + 0.3 and <4.0 | V     |

| Junction temperature                                                    |             | 150                             | °C    |

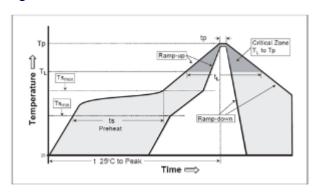

| Lead soldering temperature (40 s, reflow)                               |             | 260                             | °C    |

| Storage temperature                                                     | <b>-</b> 65 | 150                             | °C    |

- 1. Power Sequence Requirement: V<sub>MAIN</sub> > V<sub>AUX5</sub> > V<sub>AUX3P3</sub> = T<sub>RIM</sub>, D<sub>VDD</sub>.

- 2. PD69208M EPAD is connected by copper plane on PCB to AGND. AGND is ground for IC.

**Note**: DRV\_VAUX5 and IREF are output pins and should not apply voltage or current. DRV\_VAUX5 can be left open when not used.

# **5** Pin Descriptions

The PD69200 device has 32 pins and PD69208M device has 56 pins, which are described in this section.

## 5.1 Pin Configuration and Pinout

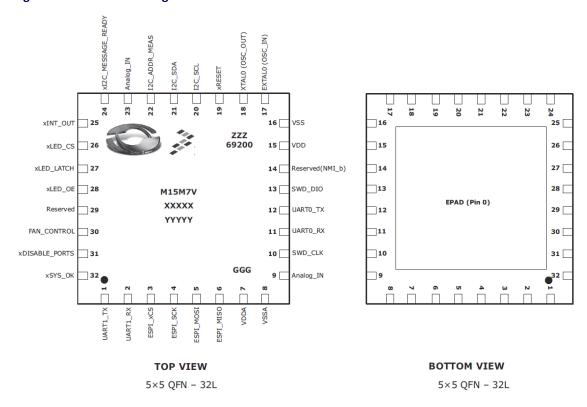

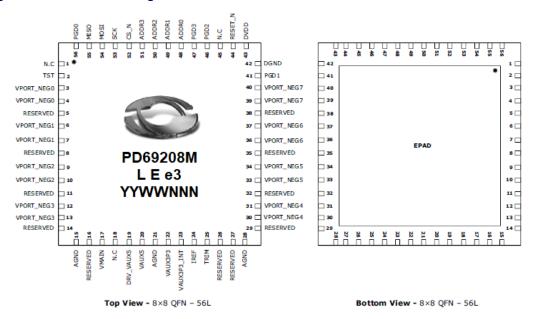

The following figures represent the top and bottom view of PD69200 and PD69208M devices.

Figure 4 • PD69200 Pin Diagram

Note: The marking position of PD69200 may change subject to NXP practice.

**Note:** For definitions about markings in the PD69200 pinout diagram, see the Ordering Information (see page 46) table.

Figure 5 • PD69208M Pin Diagram

**Note**: For definitions about markings in the PD69208M pinout diagram, see the Ordering Information (see page 46) table.

# 5.2 PD69200 and PD69208M Pin Descriptions

The following sections describe the functional pin descriptions of PD69200 and PD69208M devices.

## 5.2.1 PD69200 Pin Descriptions

The following table lists the functional pin descriptions of the PD69200 device.

Table 18 • PD69200 Pin Description

| Number | Designation                  | Туре       | Description                                                                                                                                                                              |

|--------|------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | EPAD                         | Thermal    | Isolated Thermal PAD, recommended to tie to GND.                                                                                                                                         |

| 1      | UART1_TX¹                    | OUT        | Reserved UART.                                                                                                                                                                           |

| 2      | UART1_RX¹                    | IN         | Reserved UART.                                                                                                                                                                           |

| 3      | ESPI_xCS                     | OUT        | ESPI Bus to PoE Manager. SPI chip select (Active Low). CS is asserted during all SPI frame.                                                                                              |

| 4      | ESPI_SCK                     | OUT        | ESPI Bus to PoE Manager. SPI clock output to PD6920x, and LED stream clock output, set to 1 MHz.                                                                                         |

| 5      | ESPI_MOSI                    | OUT        | SPI packets are transmitted on this line.                                                                                                                                                |

| 6      | ESPI_MISO                    | IN         | ESPI Bus to PoE Manager. SPI Master In Slave Out. SPI packets are received on this line.                                                                                                 |

| 7      | VDDA                         | Supply     | Main Supply 3.3 V.                                                                                                                                                                       |

| 8      | VSSA                         | GND        | Analog ground.                                                                                                                                                                           |

| 9      | Analog_IN                    | Analog_IN  | Analog input. Should be connected to 3.3 V.                                                                                                                                              |

| 10     | SWD_CLK                      | DEBUG      | Serial Debug Data Bus Clock.                                                                                                                                                             |

| 11     | UARTO_RX <sup>1</sup>        | IN         | UART receive from host. 15-byte protocol commands are received on this line. The baud rate is set to 19,200 bps.  For more information, see the Serial Communication Protocol User Guide |

|        |                              |            | (Catalog Number: PD69200_UG_COMM_PROT).                                                                                                                                                  |

| 12     | UARTO_TX¹                    | OUT        | UART transmit to host. 15-byte protocol reply/telemetry are transmitted on this line. The baud rate is set to 19,200 bps.                                                                |

|        |                              |            | For more information, see the Serial Communication Protocol User Guide (Catalog Number: PD69200_UG_COMM_PROT).                                                                           |

| 13     | SWD_DIO                      | DEBUG      | Serial Debug Data Bus.                                                                                                                                                                   |

| 14     | Reserved (NMI_b)             | IRQ_Input  | Spare, an external pull-up must be connected.                                                                                                                                            |

| 15     | VDD                          | Supply     | Main Supply 3.3 V.                                                                                                                                                                       |

| 16     | VSS                          | GND        | Digital ground.                                                                                                                                                                          |

| 17     | EXTALO (OSC_IN) <sup>2</sup> | Oscillator | Oscillator input - Reserved.                                                                                                                                                             |

| 18     | XTAL0 (OSC_OUT) <sup>2</sup> | Oscillator | Oscillator output - Reserved.                                                                                                                                                            |

|        |                              |            |                                                                                                                                                                                          |

| Number | Designation                     | Type      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|---------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19     | xRESET <sup>(3,4)</sup>         | IN/OUT    | Host Reset input (Active Low). The shortest reset pulse from the host that is required for the PD69200 application is 150 $\mu$ s. PD69200 can generate self-reset. In this case, the xRESET pin is driven low by the PD69200 for about 100 $\mu$ s. It is recommended to connect this pin to a host open drain output with 10 K $\Omega$ pull-up. An 47 nF filter capacitor should be connected between this pin to GND, close to the PD69200 device. If this pin is connected to a push/pull driver, a serial resistor of 1.5 K $\Omega$ must be connected instead of the pull-up. The required shortest reset pulse in this case is 300 $\mu$ s. |

|        |                                 |           | Application Note (Catalog Number: PD69208_AN_211).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 20     | I2CO_SCL <sup>4</sup>           | IN/OUT    | I <sup>2</sup> C clock from the host master. Speed is limited to 400 KHz and clock stretching functionality must be implemented in the host master. If PD69200 is busy, it holds the clock line.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 21     | I2CO_SDA <sup>4</sup>           | IN/OUT    | $\ensuremath{\text{I}^2\text{C}}$ bidirectional data. 15-byte protocol messages are transmitted on this line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        |                                 |           | For more information, see the Serial Communication Protocol User Guide document (Catalog Number: PD69200_UG_COMM_PROT).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 22     | I2C_ADDR_MEAS                   | Analog_IN | I <sup>2</sup> C address of PD69200. Analog input to determine I <sup>2</sup> C address or UART operation. See I <sup>2</sup> C address selection in table I2C Address Selection (see page 10).                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 23     | Analog_IN                       | Analog_IN | Reserved analog input. connect to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 24     | xI2C_MESSAGE_READY <sup>3</sup> | OUT       | I <sup>2</sup> C message ready for read by the host. PD69200 asserts this line low when it has an answer to the host. Therefore, the host can poll this line and initiate I2C read cycle only when the message is ready. This pin is active low.  After the host reads the data from PD69200, this pin is asserted to high.                                                                                                                                                                                                                                                                                                                         |

| 25     | xINT_OUT <sup>(3, 4)</sup>      | OUT       | Interrupt output indication. This line is asserted low when a preconfigured event is in progress. The host configures the event that should generate an interrupt through 15 bytes protocol. When this event occurs, the xINT_OUT pin is asserted. This pin is active low.                                                                                                                                                                                                                                                                                                                                                                          |

| 26     | xLED_CS <sup>3</sup>            | OUT       | Chip select signal for LED stream. This pin is active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 27     | xLED_LATCH <sup>3</sup>         | OUT       | Latch signal for LED stream. This pin is active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 28     | xLED_OE <sup>3</sup>            | OUT       | Output enable signal for LED stream. This pin is active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |