# PD69104B1 4-Port PoE Manager Datasheet

## Product Overview

Microchip's PD69104B1 Power over Ethernet (PoE) Manager enables network devices to share power and data over a single cable. PD69104B1 PoE-Manager chip is employed by both Ethernet switches and midspans. The device integrates power, analog circuitry, and state-of-the-art control logic into a single 48-pin plastic Quad Flat No-leads (QFN) package.

PD69104B1 device is a 4-port, mixed-signal, high-voltage PoE Manager. PD69104B1 supports the following modes of operation.

- Extended Auto mode—A stand-alone mode in which the PD69104B1 detects IEEE<sup>®</sup> 802.3AF-2003 compliant Powered Devices (PDs) and IEEE 802.3AT-2009 high-power devices, ensuring safe power feeding and disconnection of ports based on a power management algorithm while employing a minimum of external components.

- Semi Auto mode—Allows the host to control which devices are powered and which are not, as well as communicate with PD69104B1 and configuring it.

PD69104B1 executes all real-time functions as specified in IEEE 802.3AF-2003 (AF) and IEEE 802.3AT high-power (AT) standards. This includes load detection, AF and AT classifications. In addition, the PD69104B1 device features Multiple Classification Attempts (MCA) port status monitoring.

PD69104B1 supports detection of legacy/pre-standard PD devices. It also provides PD real-time protection through the following mechanisms: overload, under-load, over-voltage, over-temperature, and short-circuit. PD69104B1 supports supply voltages between 44V and 57V, with no need for additional power supply sources, and has built-in thermal protection.

PD69104B1 is a low-power device that uses internal MOSFETs and external  $0.36\Omega$  sense resistors, and is available in a 48-lead, 8 mm × 8 mm QFN package.

### Features

The following features are included in PD69104B1:

- Supports IEEE 802.3AF and IEEE 802.3AT, including two-event classifications

- · Extended auto and semi auto

- Supports pre-standard PD detection

- Supports Cisco device detection

- Single DC voltage input (44 V to 57 V)

- Wide temperature range: -10 °C to 85 °C (PD69104B1F: -40 °C to 85 °C)

- Low-power dissipation (0.36  $\Omega$  sense resistor)

- Drives independent 4/2-pairs power port

- Supports Extended PoE Protocol and Register Map

- Includes two selectable communication modes (IC and UART). Consult Microchip before beginning a design based on UART.

- Includes Reset command pin integrated with an RPD/MRPD mechanism

- · Continuously monitoring port and system data

- Parameter setting using input pins

- Parameters setting from external serial EEPROM device

- Built-in dynamic power management and emergency power management mechanisms with 3x power supply power-good pins

- Power soft start mechanism

- On-chip thermal protection

- On-chip continual thermal monitoring

- Voltage/current and temperature monitoring/protection

- Built-in 3.3V and 5V regulators

- Internal power on Reset

- MSL 3

- · RoHS compliant

## **Typical Application**

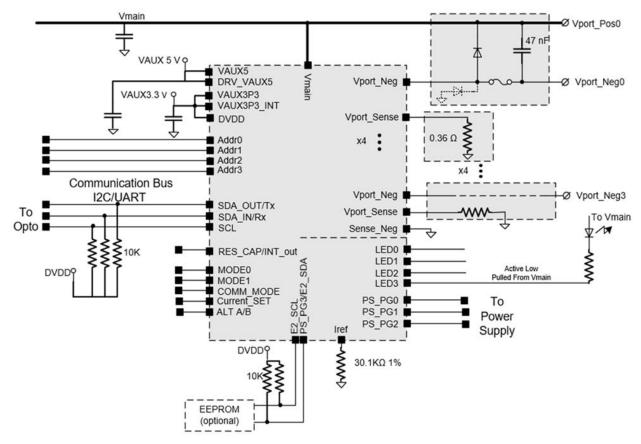

The following figure shows a typical application with a simple plug-and-play PoE solution for a single Ethernet port, switch, or hub.

Plug the positive (POS) and negative (NEG) signals into the RJ45 switch jack.

#### Figure 1. Typical Application

**Note:** Fuses per port are not required for use in circuits with total power level of up to 3 kW, as the PD69104B1 designed to fulfill Limited Power Source (LPS) requirements per the latest editions of IEC60950-1 and EN60950-1. For more information on detailed schematics of application and layout recommendations, contact Microchip.

## **Table of Contents**

| Pro | duct O                    | verview                                                                        | 1    |

|-----|---------------------------|--------------------------------------------------------------------------------|------|

|     | 1.                        | Features                                                                       | 1    |

|     | 2.                        | Typical Application                                                            | 2    |

| 1.  | Funct                     | ional Descriptions                                                             | 5    |

|     | 1.1.                      | Internal Block Diagram                                                         |      |

|     | 1.1.                      | Logic Main Control Module                                                      |      |

|     | 1.2.<br>1.3.              | Line Detection Generator                                                       |      |

|     | 1.3.<br>1.4.              | Classification Generator                                                       |      |

|     | 1. <del>4</del> .<br>1.5. | Current Limiter                                                                |      |

|     | 1.5.<br>1.6.              | Main MOSFET                                                                    |      |

|     | 1.0.<br>1.7.              |                                                                                |      |

|     | 1.7.                      | IC and Port Parameters Monitoring                                              |      |

|     | 1.o.<br>1.9.              | Power-on Reset (PoR)                                                           |      |

|     |                           | Voltage Regulator                                                              |      |

|     |                           | Clock (CLK)<br>I <sup>2</sup> C Address Selection                              |      |

|     |                           | Mode of Operation                                                              |      |

|     |                           |                                                                                |      |

|     |                           | IC Communication Functional Description                                        |      |

|     |                           | I <sup>2</sup> C High-Level Layer<br>UART Communication Functional Description |      |

|     |                           |                                                                                |      |

| 2.  | Electr                    | ical Specifications                                                            | . 14 |

|     | 2.1.                      | Electrical Characteristics                                                     |      |

|     | 2.2.                      | Dynamic Characteristics                                                        | 16   |

|     | 2.3.                      | Absolute Maximum Ratings                                                       | 17   |

| 3.  | Pin D                     | escriptions                                                                    | . 19 |

| 4.  | Packa                     | age Information                                                                | . 24 |

|     | 4.1.                      | Package Outline Drawing                                                        | 24   |

|     | 4.2.                      | Thermal Specifications                                                         |      |

|     | 4.3.                      | RoHS and Solder Reflow Information                                             |      |

|     | 4.4.                      | Tape and Reel Packaging Information                                            |      |

| 5.  | oilaaA                    | cation Information                                                             | 29   |

|     | 5.1.                      | Line Detection                                                                 |      |

|     | 5.2.                      | Legacy (Cap) Detection                                                         |      |

|     | 5.3.                      | Classification                                                                 |      |

|     | 5.4.                      | Port Startup                                                                   |      |

|     | 5.5.                      | Over-Load Detection and Port Shut Down                                         |      |

|     | 5.6.                      | Disconnect Detection                                                           |      |

|     | 5.0.<br>5.7.              | Over-Temperature Protection                                                    |      |

|     | 5.8.                      | V <sub>MAIN</sub> Out of Range Protection                                      |      |

|     | 5.9.                      | Serial EEPROM Load Mechanism                                                   |      |

|     |                           | Reset Mechanism                                                                |      |

|     |                           |                                                                                |      |

| 6.  | Order                     | ing Information                                                                | . 35 |

| 7. Revision History                       | 36   |

|-------------------------------------------|------|

| The Microchip Website                     | . 37 |

| Product Change Notification Service       | .37  |

| Customer Support                          | 37   |

| Microchip Devices Code Protection Feature | . 37 |

| Legal Notice                              | 37   |

| Trademarks                                | 38   |

| Quality Management System                 | 39   |

| Worldwide Sales and Service               | .40  |

## 1. Functional Descriptions

The following sections describe the functions of the PD69104B1 device.

## 1.1 Internal Block Diagram

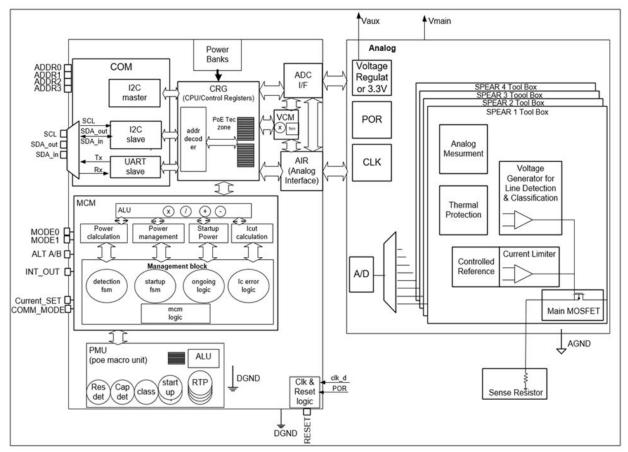

The following illustration shows the internal block diagram for the PD69104B1 device.

#### Figure 1-1. Internal Block Diagram

## 1.2 Logic Main Control Module

The logic main control block includes the digital timing mechanisms and the state machines, synchronizing and activating the following PoE functions.

- Real-Time Protection (RTP)

- Start-up macro (DVDT)

- Load-signature detection (RES DET)

- Classification macro (CLASS)

- Voltage and current monitoring registers (VMC)

- ADC interfacing

- Direct digital signals with analog block

### 1.3 Line Detection Generator

When a request is made from the main control module, the line detection generator creates four different voltage levels. This ensures robust AF/AT line detection functionality.

### 1.4 Classification Generator

When a request is made from the main control module, the state machine applies regulated class event and mark event voltages to the ports, as required by the IEEE standard.

### 1.5 Current Limiter

This circuit continuously monitors the current of the powered ports and limits it to a specific value, according to predefined limits set using the Current\_Set pin. In case the current exceeds this specific level, the system starts measuring the elapsed time. If this period is longer than the preset threshold, the port is disconnected.

## 1.6 Main MOSFET

Main power switching FET is used for controlling the PoE current that streams into the load.

## 1.7 IC and Port Parameters Monitoring

A 10-bit analog-to-digital converter is used for converting analog signals into digital registers.

- IC main voltage monitoring—The chip main voltage is sampled every 1 mS. Each measurement is an average

of four consecutive ADC measurements and stored in the relevant register. The main voltage measurement

resolution is 5.835 mV/count ±5 %.

- IC thermal monitoring—The PD69104B1 contains a thermal sensor that is sampled to register every 1 mS so the PD69104B1 die temperature can be monitored at all time.

- Port current/voltage monitoring—After the ports start to deliver the power the current/voltage is sampled every 1 mS on each port. Each measurement is an average of four consecutive ADC measurements and stored in the relevant register. Current measurement resolution is 122.07 µA/count ±5% and voltage measurement resolution is 5.835 mV/count ±5% (see the PD69104B1 User Guide register map document for more details).

## 1.8 Power-on Reset (PoR)

This element monitors the internal 3.3  $V_{DC}$  levels. If this voltage drops below specific thresholds, a Reset signal is generated and the PD69104B1 is reset.

## 1.9 Voltage Regulator

The voltage regulator generates 3.3  $V_{DC}$  and 5  $V_{DC}$  for the internal circuitry. These voltages are derived from the  $V_{MAIN}$  supply.

## 1.10 Clock (CLK)

This is an internal 8 MHz CLK oscillator.

## 1.11 I<sup>2</sup>C Address Selection

The following table lists the  $I^2C$  address selection for the PD69104B1 device.

#### Table 1-1. I<sup>2</sup>C Address Selection

| CONST<br>Bits | ADDR3<br>Client 1 Bit | ADDR2<br>Client 0 Bit | ADDR1<br>ID1 Bit | ADDR0<br>ID0 Bit | IC/UART Address |

|---------------|-----------------------|-----------------------|------------------|------------------|-----------------|

| 010           | 0                     | 0                     | 0                | 0                | 010000b         |

| 010           | 0                     | 0                     | 0                | 1                | 0100001b        |

| 010           | 0                     | 0                     | 1                | 0                | 0100010b        |

| 010           | 0                     | 0                     | 1                | 1                | 0100011b        |

| 010           | 0                     | 1                     | 0                | 0                | 0100100b        |

| 010           | 0                     | 1                     | 0                | 1                | 0100101b        |

| 010           | 0                     | 1                     | 1                | 0                | 0100110b        |

| 010           | 0                     | 1                     | 1                | 1                | 0100111b        |

| 010           | 1                     | 0                     | 0                | 0                | 0101000b        |

| 010           | 1                     | 0                     | 0                | 1                | 0101001b        |

| 010           | 1                     | 0                     | 1                | 0                | 0101010b        |

| 010           | 1                     | 0                     | 1                | 1                | 0101011b        |

| 010           | 1                     | 1                     | 0                | 0                | 0101100b        |

| 010           | 1                     | 1                     | 0                | 1                | 0101101b        |

| 010           | 1                     | 1                     | 1                | 0                | 0101110b        |

| 010           | 1                     | 1                     | 1                | 1                | 0101111b        |

#### Notes:

- Address 0000000b is the global address in Extended mode operation IC (MODE<1:0>='00').

- Address 0110000b is the global address in Semi-Auto mode operations (MODE<1:0>='01' or '11').

- All clients respond to the global address.

- Avoid global read transactions.

- Address 0001100b is used for extended PoE address (alert response address) in Semi-Auto mode operations.

- When reading from this alert response address, only clients that assert the Int\_out pin will send bytes that consist of their own addresses.

## 1.12 Mode of Operation

The following table lists the modes of operation for the PD69104B1 device.

#### Table 1-2. Mode of Operation

| Mode<br>1 | Mode<br>0 | Mode                  | Comm to the IC                    | Functionality                                                                                                         |

|-----------|-----------|-----------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| 0         | 0         | Extended Auto<br>mode | IC or UART (see<br>COMM_MODE pin) | Fully autonomous operation without a need<br>for host controller (MCU). This mode supports<br>extended registers map. |

|           |           |                       |                                   | Default operation—with no interrupt function<br>(interrupt can be enabled by communication<br>command).               |

| 0         | 1         | Semi-Auto mode        | IC or UART (see<br>COMM_MODE pin) | Host should manage the ports.                                                                                         |

Note: Consult Microchip before beginning a design based on UART.

## 1.13 IC Communication Functional Description

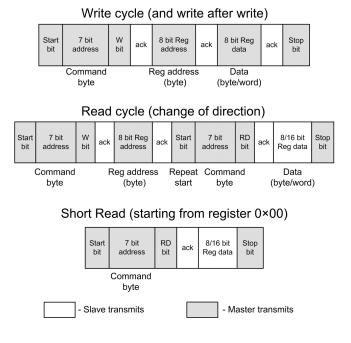

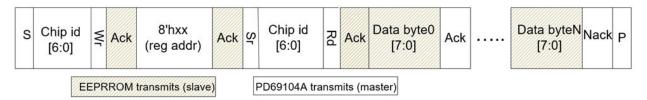

The following figure shows the IC communication format of the data write/read access for the PD69104B1 device.

#### Figure 1-2. Packet Structure

#### 1.13.1 Address Phase

This phase is common to both read and write accesses.

- Both accesses (read and write) begin with a Start indication.

- The address of the client is following the Start indication. In case of a miss match, the client ignores the rest of the access and waits for the Stop indication to close the current access. However, in case the client address matches, the next bit indicates the type of the access (read or write).

- The matched client acknowledges the first byte.

• The following byte is the internal register address. The client should acknowledge the byte.

#### 1.13.2 Data Phase

In this phase, the read and write accesses behave differently.

- Write Access

- Byte of write data is transmitted to the client; the client acknowledges it.

- A Stop indication from the host closes the current access.

- Read Access

- Another command byte is received, comprised of the client address and the real command type (in this case, read). The client acknowledges the byte.

- At this stage, the host is ready to continue the communication and to sample the read data; hence, the read data must be ready on the next rise of the clock pulse.

- A byte of data is transmitted to the host; the host acknowledges it.

### 1.14 I<sup>2</sup>C High-Level Layer

The following figure shows the supported I<sup>2</sup>C high-level packet structure.

#### Figure 1-3. High-Level Packet Structure

#### 1.14.1 Byte/Word Read/Write Transaction

- The first byte is the control byte that consists of the chip address and a read/write operation indication.

- The second byte is the internal chip's address register.

- The following bytes/words are data bytes. For a read operation, they are read from the client, and for a a write operation, they are written to the client.

#### 1.14.2 Successive Read/Write Transaction

- The host can continue sending bytes that the clients write, or continue receiving data from a client during the address phase.

- The client will continue to send/receive data bytes from/to the host until a stop bit is asserted by the host.

- Each byte received by the client (or each byte to be read from the registers) is received from the next register address (each byte address is increased by 1).

#### 1.14.3 Read Byte Transaction

The client supports a send byte transaction.

- The host begins with a start bit. The following byte consists of the chip address and a read bit.

- If the chip address is correct, the client acknowledges the byte and immediately (at the next sck phase) sends a data byte from a constant address (addr 7'h00).

- A send byte transaction continues with successive read transactions (address 1, address 2, and so on) until the host asserts a stop bit.

#### 1.14.4 Broadcast Support

All clients answer a general address sent by the host. For Semi-Auto modes, the general address is 7'h30, and for of Extended Auto mode, the general address is 7'h0. The broadcast is for host writing only; read access is ignored in a broadcast transaction.

#### 1.14.5 Timeout Mechanism

The IC has an internal counter of 14 ms. The counter resets each time the SCL rises or falls. If the SCL is "stuck" for 14 ms, the IC returns to Idle state and transaction is ignored (the timeout mechanism is active between the start bit and the stop bit).

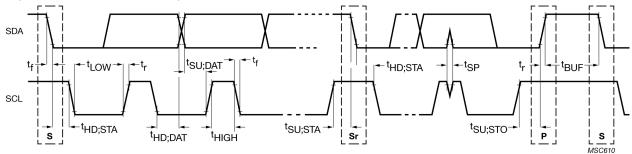

#### 1.14.6 I<sup>2</sup>C Timing Constraints

The following table lists the characteristics of the SDA and SCL bus lines for F/A-mode I<sup>2</sup>C-bus.

Table 1-3. Characteristics of the SDA and SCL Bus Lines for F/A-Mode I<sup>2</sup>C-Bus

|                                                                                                      |                     | Standard M          | ode               | Fast Mode                           | Fast Mode        |      |  |

|------------------------------------------------------------------------------------------------------|---------------------|---------------------|-------------------|-------------------------------------|------------------|------|--|

| Parameter                                                                                            | Symbol              | Min                 | Max               | Min                                 | Мах              | Unit |  |

| SCL clock frequency                                                                                  | f <sub>SCL</sub>    | 0                   | 100               | 0                                   | 400              | kHz  |  |

| Hold time (repeated)<br>Start condition. After this<br>period, the first clock<br>pulse is generated | t <sub>HD;STA</sub> | 4.0                 | -                 | 0.6                                 | -                | μs   |  |

| Low period of the SCL clock                                                                          | t <sub>LOW</sub>    | 4.7                 | _                 | 1.3                                 | -                | μs   |  |

| High period of the SCL clock                                                                         | t <sub>HIGH</sub>   | 4.0                 | -                 | 0.6                                 | -                | μs   |  |

| Set-up time for a repeated Start condition                                                           | t <sub>SU;STA</sub> | 4.7                 | -                 | 0.6                                 | -                | μs   |  |

| Data hold time:                                                                                      | t <sub>HD;DAT</sub> |                     |                   |                                     |                  |      |  |

| CBUS compatible hosts                                                                                |                     | 5.0                 | -                 | -                                   | -                | μs   |  |

| I <sup>2</sup> C-bus devices                                                                         |                     | 0 <sup>1</sup>      | 3.34 <sup>2</sup> | 0 <sup>1</sup>                      | 0.9 <sup>2</sup> | μs   |  |

| Data set-up time                                                                                     | t <sub>SU;STA</sub> | 250                 | -                 | 100 <sup>3</sup>                    |                  | ns   |  |

| Rise time of both SDA and SCL signals                                                                | t <sub>r</sub>      | -                   | 1000              | 20 + 0.1C <sub>b</sub> <sup>4</sup> | 300              | ns   |  |

| Fall time of both SDA and SCL signals                                                                | t <sub>f</sub>      | -                   | 300               | 20 + 0.1C <sub>b</sub> <sup>4</sup> | 300              | ns   |  |

| Set-up time for Stop condition                                                                       | t <sub>SU;STO</sub> | 4.0                 | -                 | 0.6                                 | -                | μs   |  |

| Bus free time between a Stop and Start condition                                                     | t <sub>BUF</sub>    | 4.7                 | -                 | 1.3                                 | -                | μs   |  |

| Capacitive load for each bus line                                                                    | C <sub>b</sub>      | -                   | 400               | -                                   | 400              | pF   |  |

| Noise margin at<br>the low level for<br>each connected device<br>(including hysteresis)              | V <sub>nL</sub>     | 0.1 V <sub>DD</sub> | -                 | 0.1 V <sub>DD</sub>                 | -                | V    |  |

| Noise margin at<br>the high level for<br>each connected device<br>(including hysteresis)             | V <sub>nH</sub>     | 0.2 V <sub>DD</sub> | -                 | 0.2 V <sub>DD</sub>                 | -                | V    |  |

#### Notes:

- A device must internally provide a hold time of at least 300 ns for the SDA signal (refers to the V<sub>IHmin</sub> of the SCL signal) to bridge the undefined region of the falling edge of the SCL.

- 2. The maximum t<sub>HD:DAT</sub> has to be met only if the device does not stretch the low period (t<sub>LOW</sub>) of the SCL signal.

- 3. A fast mode I<sup>2</sup>C bus device can be used in a standard mode I<sup>2</sup>C bus system, but the requirement t<sub>SU;DAT</sub> <sup>3</sup> 250 ns must then be met. This is in case the device does not stretch the LOW period of the SCL signal.

- If the device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line tr max + t<sub>SU;DAT</sub> = 1000 ns + 250 ns = 1250 ns (according to the Standard-mode I<sup>2</sup>C-bus specification) before the SCL line can be released.

**Note:** All values refer to  $V_{IHmin}$  and  $V_{ILmax}$  levels. For more information, see Electrical Characteristics section.

The following figure shows the definition of timing for F/S-mode devices on the I<sup>2</sup>C-bus.

#### Figure 1-4. Definition of Timing for F/S-mode Devices on the I<sup>2</sup>C-bus

## 1.15 UART Communication Functional Description

The UART is supported by the PD69104B1 platform to allow communication between PD69104B1 IC's and an external host. The PD69104B1 platform supports UART only as a client. The following is a list of features for the UART communication mode. Consult Microchip before beginning a design on the UART interface.

- Client mode

- Supports 4,800 to 115,200 Baud rate, auto-learning mechanism

- Supports 8-bit address

- Supports 8-bit data access

- Supports general broadcast transmission

- 8N1

- 8-bits data

- No parity

- 1 stop bit

- Frame transaction—header, payload, and suffix

- Timeout mechanism (time-out for frame and per byte)

- No successive read/write—one transaction per register (read/write)

- · Half-duplex implementation-Rx starts after Tx ends

- · A filter for glitches cancelling on the Rx pin

#### 1.15.1 The Physical Layer

The UART protocol has two data lines; the Rx, from where PD69104B1 receives its data, and the Tx, where data is transmitted. UART is a byte protocol in which every byte starts with a start bit and ends with a stop bit.

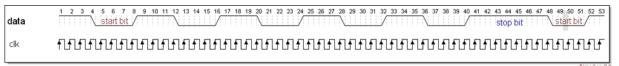

The following figure shows the UART read/write frame.

#### Figure 1-5. UART Read/Write Frame

The data is sent in a constant frame in order to be synchronized.

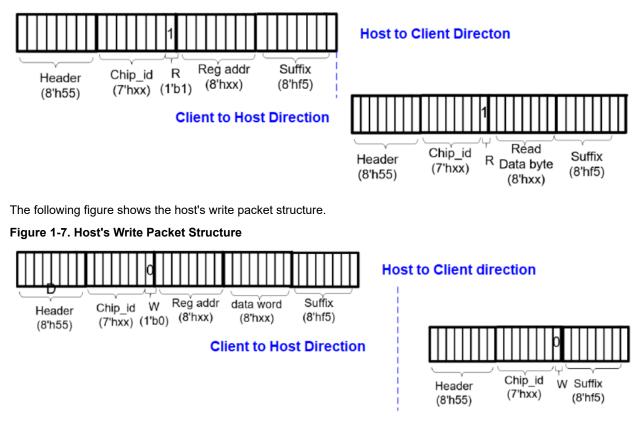

The following figure shows the host's read packet structure.

#### Figure 1-6. Host's Read Packet Structure

#### 1.15.2 Broadcast Support

All clients answer a general address sent by the host. The general address is 7'h0.

Broadcast is for host writing only—read accesses are ignored in a broadcast transaction.

#### 1.15.3 Auto Baud Rate Learning

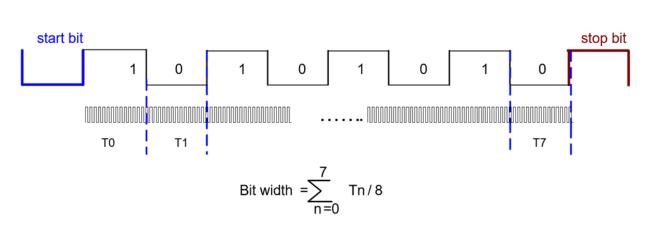

PD69104B1 has a self-learning baud rate mechanism that allows synchronizing all PD69104B1 clients to the host's "real" baud rate and thus working with a higher baud rate.

The first byte received by the client is 8'hAA. At the rising or falling edge of each bit, an 8 MHz counter starts counting the bit width (in a 125 ns resolution). The average width of the 8 header bits is the actual bits rate. By using this mechanism, PD69104B1 clients can be synchronized with the host and set back data at that rate. The header is a preamble bit that facilitates synchronization.

The following figure shows the header bit width.

#### Figure 1-8. Header Bit Width

Header bit (8'hAA)

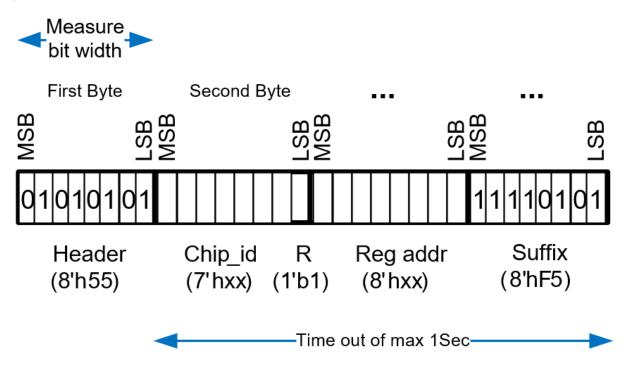

#### 1.15.4 Timeout Mechanisms

The UART protocol has a frame time-out mechanism. This mechanism has the following two purposes.

- Distinguishing between the frame's suffix of 8'f5 and a payload byte with the same value. The mechanism identifies a frame suffix only when it arrives as 2 bytes in a read access or as 4-bytes in a write access; otherwise it is treated as a data byte.

- Preventing UART communication from getting stuck. A 1-second time-out counter is activated beginning with a start frame (the end of header byte) till a suffix arrival. If a suffix byte does not arrive within that time the transaction is ignored and the client moves into an Idle state.

The following figure shows the time-out mechanism.

#### Figure 1-9. Timeout Mechanism

## 2. Electrical Specifications

The following sections describe the electrical specifications of the PD69104B1 device.

## 2.1 Electrical Characteristics

The following minimum and maximum ratings apply over the entire specified operating ratings of the device, unless otherwise specified under conditions.

#### Table 2-1. Power Supply

| Symbol              | Parameter                              | Test Conditions/Comment                                                                 | Min  | Тур | Max  | Units           |

|---------------------|----------------------------------------|-----------------------------------------------------------------------------------------|------|-----|------|-----------------|

| V <sub>MAIN</sub>   | Input voltage                          | Supports full IEEE 802.3 functionality                                                  | 44   | 55  | 57   | V <sub>DC</sub> |

| I <sub>MAIN</sub>   | Power supply current at operating mode | V <sub>MAIN</sub> = 55V                                                                 |      | 10  |      | mA              |

| V <sub>AUX5</sub>   | 5V output voltage                      | -                                                                                       | 4.5  | 5   | 5.5  | $V_{DC}$        |

| V <sub>AUX3P3</sub> | 3.3V output voltage                    | -                                                                                       | 2.97 | 3.3 | 3.63 | V <sub>DC</sub> |

| -                   | 3 3\/ output current                   | Without external NPN                                                                    |      |     | 5    | mA              |

|                     | 3.3V output current                    | With external NPN transistor on $V_{\text{AUX5}}$                                       |      |     | 30   | mA              |

| _                   | 3.3V input voltage                     | REG_EN_N pin= 3.3V<br>(internal register is disabled) V <sub>AUX3P3_INT</sub><br>pin=5V | 3    | 3.3 | 3.6  | V <sub>DC</sub> |

#### Table 2-2. PoR

| Symbol | Parameter  | Test Conditions/Comment | Min   | Тур   | Max   | Units           |

|--------|------------|-------------------------|-------|-------|-------|-----------------|

| -      | Threshold  | -                       | 2.575 | 2.775 | 2.975 | V <sub>DC</sub> |

| -      | Hysteresis | -                       | 0.2   | 0.25  | 0.3   | V <sub>DC</sub> |

| -      | Delay      | -                       | 10    | 50    | 100   | μS              |

#### Table 2-3. Digital I/O

| Symbol          | Parameter                  | Test Conditions/Comment     | Min | Тур | Max | Units           |

|-----------------|----------------------------|-----------------------------|-----|-----|-----|-----------------|

| V <sub>IH</sub> | Input logic high threshold | -                           | 2   |     |     | V <sub>DC</sub> |

| V <sub>IL</sub> | Input logic low threshold  | -                           |     |     | 0.8 | V <sub>DC</sub> |

| -               | Input hysteresis voltage   | -                           | 0.4 | 0.6 | 0.8 | V <sub>DC</sub> |

| IIH             | Input high current         | -                           | -10 |     | 10  | μA              |

| IIL             | Input low current          | -                           | -10 |     | 10  | μA              |

| V <sub>OH</sub> | Output high voltage        | For I <sub>OH</sub> = –1 mA | 2.4 |     |     | V <sub>DC</sub> |

| V <sub>OL</sub> | Output low voltage         | I <sub>OH</sub> = 1 mA      |     |     | 0.4 | $V_{DC}$        |

#### Table 2-4. PoE Load Currents

| Symbol          | Parameter                         | Test Conditions/Comment                                                                   | Min | Тур | Мах  | Units |

|-----------------|-----------------------------------|-------------------------------------------------------------------------------------------|-----|-----|------|-------|

| AT_LIM_LOW      | AT Limit mode                     | Tested with sense resistance= 0.366 $\Omega$                                              | 706 | 722 | 767  | mA    |

|                 |                                   | $(R_{sense} + traces = 0.36 \Omega + 6 mΩ = 0.366 \Omega)$<br>connected at port sense pin | 847 | 874 | 919  | mA    |

|                 |                                   |                                                                                           | 537 |     | 1200 | mA    |

| AT_LIM_HIGH     | AF Limit mode                     |                                                                                           | 410 | 425 | 448  | mA    |

| AT configurable | PoE technology<br>high-power port |                                                                                           | 808 | 850 | 892  | mA    |

#### Table 2-5. Main Power Switching FET

| Symbol            | Parameter                             | Test Conditions/Comment | Min | Тур | Max | Units |

|-------------------|---------------------------------------|-------------------------|-----|-----|-----|-------|

| R <sub>dson</sub> | ON resistance                         | -                       | -   | 0.3 | -   | Ω     |

| -                 | Internal thermal protection threshold | -                       | _   | 200 | _   | °C    |

#### Table 2-6. Line Detection

| Symbol | Parameter | Test Conditions/Comment          | Min | Тур | Max  | Units |

|--------|-----------|----------------------------------|-----|-----|------|-------|

| -      | Range     | According to IEEE 802.3 standard | 19  | -   | 26.5 | kΩ    |

#### Table 2-7. Classification

| Symb | ol Parameter               | Test Conditions/Comment                                                   | Min  | Тур | Max  | Units           |

|------|----------------------------|---------------------------------------------------------------------------|------|-----|------|-----------------|

| -    | Class event output voltage | Measured between $V_{\text{MAIN}}$ and $V_{\text{PORT}\_\text{NEG}}$ pins | 16.5 | 18  | 19.5 | V <sub>DC</sub> |

| _    | Mark event output voltage  | Measured between $V_{MAIN}$ and $V_{PORT\_NEG}$ pins                      | 7.5  | 8.5 | 9.5  | V <sub>DC</sub> |

#### Table 2-8. LED 0 to 3, MAX\_LED Drivers

| Symbol                                             | Parameter    | Test Conditions/Comment                                                   | Min | Тур | Max | Units |

|----------------------------------------------------|--------------|---------------------------------------------------------------------------|-----|-----|-----|-------|

| $I_{\text{sink}}$ (from $V_{\text{MAIN}}$ to AGND) | Current sink | Measured between $V_{\text{MAIN}}$ and $V_{\text{PORT}\_\text{NEG}}$ pins | -   | 3   | 5   | mA    |

#### Table 2-9. Three States Analog Input Pins (Current Set, Comm\_Mode)

| Symbol | Parameter                | Test Conditions/Comment | Min                     | Тур | Мах                     | Units           |

|--------|--------------------------|-------------------------|-------------------------|-----|-------------------------|-----------------|

| -      | High-level input voltage | -                       | 80% V <sub>AUX3P3</sub> | -   | -                       | V <sub>DC</sub> |

| _      | Open                     | Not connected           | 40% V <sub>AUX3P3</sub> | -   | 60% V <sub>AUX3P3</sub> | V <sub>DC</sub> |

| -      | Low-level input voltage  | -                       | -                       | -   | 20% V <sub>AUX3P3</sub> | V <sub>DC</sub> |

#### 2.1.1 Typical Power Dissipation Information

- R<sub>sense</sub> Power Dissipation: 0.36  $\Omega \times I_{port}^{2}$

- $R_{ds_{ON}}$  Power Dissipation: 0.3  $\Omega \times I_{port}^{2}$

- P<sub>port\_AF</sub> = 15.4W ==> Port Power Dissipation at R<sub>sense</sub>= 37 mW (320 mA)

- Port Power Dissipation at R<sub>ds\_ON</sub> = 31 mW (320 mA)

- P<sub>port AT</sub> = 30W ==> Port Power Dissipation at R<sub>sense</sub>= 130 mW (600 mA)

- Port Power Dissipation at R<sub>ds ON</sub> = 108 mW (600 mA)

#### Using Internal 3.3V regulator

- Typical PD69104B1 self power dissipation (including internal regulations) = 0.5 W (50V)

- Typical PD69104B1 at 4 × Port AF application power dissipation = 0.5W + 4 x 31 mW + 4 × 37 mW = 0.77W

- Typical PD69104B1 at 4 × Port AT application power dissipation = 0.5W + 4 x 108 mW + 4 × 130 mW = 1.45W

#### Using External 3.3V regulator

- Typical PD69104B1 self power dissipation (external 3.3V source) = 0.25W (50V)

- Typical PD69104B1 at 4 × Port AF application power dissipation = 0.25W + 4 x 31 mW + 4 × 37 mW = 0.52W

- Typical PD69104B1 at 4 × Port AT application power dissipation = 0.25W + 4 x 108 mW + 4 × 130 mW = 1.2W

### 2.2 Dynamic Characteristics

PD69104B1 utilizes three current level thresholds (I<sub>min</sub>, I<sub>cut</sub>, I<sub>lim</sub>) and three timers (T<sub>min</sub>, T<sub>cut</sub>, T<sub>lim</sub>).

- Loads that consume I<sub>lim</sub> current for more than T<sub>lim</sub> are labeled as "short circuit state" and are shutdown.

- Loads that dissipate more than I<sub>cut</sub> for longer than T<sub>cut</sub> are labeled as "overloads" and are shutdown.

- If output power is below I<sub>min</sub> for more than T<sub>min</sub>, the PD is labeled as "no-load" and is shutdown.

Automatic recovery from overload and no-load conditions is attempted every T<sub>OVLREC</sub> period (typically 1 second). Output power is limited to I<sub>lim</sub>, which is the maximum peak current allowed at the port.

The following table lists the operational mode parameters.

| Symbol                                                                      | Parameter                                                                                             | Conditions                                                                 | Min  | Тур | Max | Unit |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------|-----|-----|------|

| T <sub>UDLREC</sub>                                                         | Automatic recovery<br>from no-load<br>shutdown                                                        | Measured from port shutdown point (can be – modified through control port) |      | 1   | -   | S    |

| -                                                                           | Cutoff timers<br>accuracy                                                                             | Typical accuracy of T <sub>cut</sub> –                                     |      | 2   | -   | ms   |

| I <sub>Inrsh</sub>                                                          | $I_{\text{Inrsh}}$ Inrush current For t= 50 ms, $C_{\text{load}}$ = 180 µF maximum 4                  |                                                                            | 400  |     | 450 | mA   |

| I <sub>port</sub>                                                           | Output current operating range                                                                        | Continuous operation after startup period                                  |      | -   | 725 | mA   |

| P <sub>port</sub>                                                           | Dort Output power available, operating range Continuous operation after startup period at port output |                                                                            | 0.57 | -   | 36  | W    |

| I <sub>min1</sub>                                                           | Off-mode current                                                                                      | Must disconnect where T is greater than $T_{\text{UVL}}$                   | 0    | -   | 5   | mA   |

|                                                                             |                                                                                                       | May or may not disconnect where T is greater than $T_{UVL}$                | 5    | 7.5 | 10  | mA   |

| I <sub>min2</sub> PD power<br>maintenance<br>request drop-out<br>time limit |                                                                                                       | Buffer period to handle transitions                                        | 300  | -   | 400 | ms   |

| T <sub>PMDO</sub>                                                           | Overload time limit                                                                                   | -                                                                          | 50   | -   | 75  | ms   |

#### **Table 2-10. Operational Mode Parameters**

| co                | continued                                                                                                                        |                                      |    |     |     |      |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----|-----|-----|------|--|--|

| Symbol Parameter  |                                                                                                                                  | Conditions I                         |    | Тур | Max | Unit |  |  |

| T <sub>OVL</sub>  | DVLTurn-on rise timeFrom 10% to 90% of Vport(specified for PD load consisting of 100 μF<br>capacitor parallel to 200 Ω resistor) |                                      | 15 | _   | _   | μs   |  |  |

| T <sub>rise</sub> | ise Turn-off time From V <sub>port</sub> to 2.8 V <sub>DC</sub>                                                                  |                                      | -  | _   | 500 | ms   |  |  |

| T <sub>off</sub>  | Time maintain power signature                                                                                                    | DC modulation time for DC disconnect | -  | 49  | -   | ms   |  |  |

The following table lists the IEEE 802.3AT mode parameters.

#### Table 2-11. IEEE 802.3AT Mode Parameters

| Symbol                                                                      | Parameter                                                                                                                                       | Conditions                                                               | Min  | Тур | Max | Unit |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------|-----|-----|------|

| T <sub>UDLREC</sub>                                                         | Automatic<br>recovery from no-<br>load shutdown                                                                                                 | Measured from port shutdown point (can be modified through control port) | -    | 1   | -   | S    |

| -                                                                           | Cutoff timers<br>accuracy                                                                                                                       | Typical accuracy of T <sub>cut</sub>                                     | -    | 2   | -   | ms   |

| I <sub>Inrsh</sub>                                                          | Inrush current                                                                                                                                  | For t= 50 ms, C <sub>load</sub> = 180 µF maximum                         | 400  | -   | 450 | mA   |

| I <sub>port</sub>                                                           | Output current operating range                                                                                                                  | Continuous operation after startup period 10                             |      | -   | 725 | mA   |

| P <sub>port</sub>                                                           | P <sub>port</sub> Output power<br>available,<br>operating range Continuous operation after startup period at<br>port output                     |                                                                          | 0.57 | -   | 36  | W    |

| I <sub>min1</sub>                                                           | Off-mode current                                                                                                                                | Must disconnect where T is greater than $\mathrm{T}_{\mathrm{UVL}}$      | 0    | -   | 5   | mA   |

|                                                                             |                                                                                                                                                 | May or may not disconnect where T is greater than $T_{UVL}$              | 5    | 7.5 | 10  | mA   |

| I <sub>min2</sub> PD power<br>maintenance<br>request drop-out<br>time limit |                                                                                                                                                 | Buffer period to handle transitions                                      | 300  | -   | 400 | ms   |

| T <sub>PMDO</sub>                                                           | Overload time limit                                                                                                                             | -                                                                        | 50   | -   | 75  | ms   |

| T <sub>OVL</sub>                                                            | Torn-on rise time         From 10% to 90% of V <sub>port</sub> (Specified for PD load consisting of 100 μF capacitor parallel to 200W resistor) |                                                                          | 15   | -   | -   | μs   |

| T <sub>rise</sub>                                                           | Turn-off time                                                                                                                                   | From $V_{port}$ to 2.8 $V_{DC}$                                          | -    | -   | 500 | ms   |

| T <sub>off</sub>                                                            | Time maintain power signature DC modulation time for DC disconnect                                                                              |                                                                          | -    | 49  | -   | ms   |

## 2.3 Absolute Maximum Ratings

The following table lists the absolute maximum ratings for the PD69104B1 device.

| Parameter                                      | Absolute Maximum Rating                    |

|------------------------------------------------|--------------------------------------------|

| Supply input voltage (V <sub>MAIN</sub> )      | –0.3 $V_{DC}$ to 74 $V_{DC}$               |

| Port_Neg [07] pins                             | –0.3 $V_{DC}$ to 74 $V_{DC}$               |

| LED pins                                       | –0.3 V <sub>DC</sub> to 74 V <sub>DC</sub> |

| Port_Sense[07] pins                            | –0.3 $V_{DC}$ to 3.6 $V_{DC}$              |

| QGND, GND pins                                 | –0.3 $V_{DC}$ to 0.3 $V_{DC}$              |

| V <sub>AUX5</sub> , DRV_VAUX5                  | –0.3 $V_{DC}$ to 5.5 $V_{DC}$              |

| All other pins                                 | –0.3 $V_{DC}$ to 3.6 $V_{DC}$              |

| PD69104B1 operating ambient temperature range  | –10 °C to 85 °C                            |

| PD69104B1F operating ambient temperature range | –40 °C to 85 °C                            |

| Maximum operating junction temperature         | 160 °C                                     |

| ESD protection at all I/O pins                 | JESD22 Class 1C HBM (±2 KV)                |

| Storage temperature range                      | –65 °C to 150 °C                           |

#### Table 2-12. Absolute Maximum Ratings

**Note:** Exceeding these ratings can cause damage to the device. All voltages are with respect to ground. Currents are marked positive when flowing into specified terminals and marked negative when flowing out of specified terminals.

## 3. Pin Descriptions

The PD69104B1 device has 48-pins, which are described in this section.

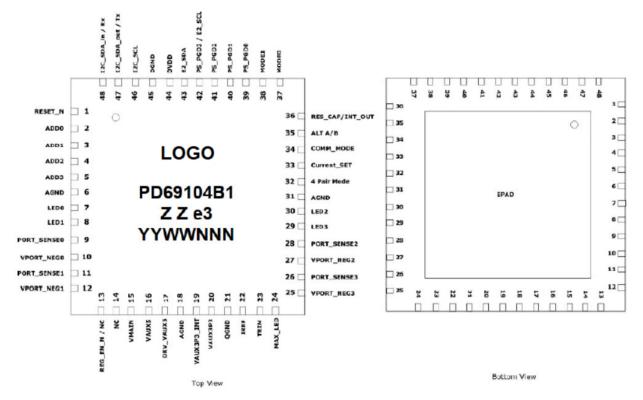

The following figure shows the top view of the PD69104B1 pin configuration and pinout.

#### Figure 3-1. PD69104B1 Pin Configuration and Pinout

**Note:** RoHS/Pb-free 100 % matte tin finish. PD69104B1 for -10 °C to 85 °C operating ambient temperature range. The following table lists the functional pin descriptions for the PD69104B1 device.

| Pin | Pin Name             | Pin Type      | Description                                                                                                                                                        |

|-----|----------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | PAD                  | Analog GND    | Exposed PAD: connect to analog ground (AGND). A decent ground plane should be deployed around this pin whenever possible (see PD69104B1 Layout Design Guidelines). |

| 1   | RESET_N <sup>1</sup> | Digital input | Reset input: active low (0 = reset) This pin is also used for RPD/MRPD function.                                                                                   |

| 2   | ADDR0                | Digital input | Address bus for setting the address of the chip. See Table 1-1. I <sup>2</sup> C Address Selection.                                                                |

| 3   | ADDR1                | Digital input | Address bus for setting the address of the chip. See Table 1-1. I <sup>2</sup> C Address Selection.                                                                |

| 4   | ADDR2                | Digital input | Address bus for setting the address of the chip. See Table 1-1. I <sup>2</sup> C Address Selection.                                                                |

| 5   | ADDR3                | Digital input | Address bus for setting the address of the chip. See Table 1-1. I <sup>2</sup> C Address Selection.                                                                |

#### Table 3-1. Pin Descriptions

# PD69104B1 Pin Descriptions

| continued |             |                   |                                                                                                                                                                                                           |  |  |  |  |

|-----------|-------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin       | Pin Name    | Pin Type          | Description                                                                                                                                                                                               |  |  |  |  |

| 6         | AGND        | Power             | Analog ground                                                                                                                                                                                             |  |  |  |  |

| 7         | LED 0       | Open drain output | Port 0 LED indication: active low (0 = LED ON). See Table 5-1. LED Indications.                                                                                                                           |  |  |  |  |

| 8         | LED 1       | Open drain output | Port 1 LED indication: active low (0 = LED ON). See Table 5-1. LED Indications.                                                                                                                           |  |  |  |  |

| 9         | PORT_SENSE0 | Analog input      | Sense resistor port input (connected to 0.36 $\Omega$ , 1% resistor to QGND with ~6 m $\Omega$ trace for measurements accuracy).                                                                          |  |  |  |  |

| 10        | VPORT_NEG0  | Analog I/O        | Negative port output                                                                                                                                                                                      |  |  |  |  |

| 11        | PORT_SENSE1 | Analog input      | Sense resistor port input (connected to 0.36 $\Omega$ , 1% resistor to QGND with ~6 m $\Omega$ trace for measurements accuracy).                                                                          |  |  |  |  |

| 12        | VPORT_NEG1  | Analog I/O        | Negative port output                                                                                                                                                                                      |  |  |  |  |

| 13        | REG_EN_N/NC | Analog I/O        | An input pin that enables control of the 3.3 V <sub>DC</sub> internal regulator. Disables internal 3.3 V <sub>DC</sub> regulator in case external 3.3 V <sub>DC</sub> is used to supply the chip.         |  |  |  |  |

|           |             |                   | If connected to GND or unconnected, internal regulator is enabled. If connected to 3.3 $V_{\text{DC}},$ internal regulator is disabled.                                                                   |  |  |  |  |

| 14        | NC          | Analog I/O        | A test pin used only during production. Keep unconnected.                                                                                                                                                 |  |  |  |  |

| 15        | VMAIN       | Power             | Supplies voltage for the internal analog circuitry. A 1 $\mu$ F (or higher) low ESR bypass capacitor, connected to AGND, should be placed as close as possible to this pin through low resistance traces. |  |  |  |  |

| 16        | VAUX5       | Power             | Regulated 5 $V_{DC}$ output voltage source, needs to be connected to a filtering capacitor of 4.7 $\mu$ F or higher.                                                                                      |  |  |  |  |

|           |             |                   | If an external NPN is used to regulate the voltage, connect this pin to the emitter (the collector should be connected to $V_{\rm MAIN}).$                                                                |  |  |  |  |

| 17        | DRV_VAUX5   | Power             | Driven outputs for 5 $V_{DC}$ external regulations. In case internal regulation is used, connect to pin 16.                                                                                               |  |  |  |  |

|           |             |                   | In case an external NPN is used to regulate the voltage, connect this pin to the base.                                                                                                                    |  |  |  |  |

| 18        | AGND        | Power             | Analog ground                                                                                                                                                                                             |  |  |  |  |

| 19        | VAUX3P3_INT | Power             | In case internal 3.3 $V_{DC}$ regulator is used, connected to $V_{AUX3P3}$ (pin 20).                                                                                                                      |  |  |  |  |

|           |             |                   | In case external 3.3 $V_{DC}$ regulator is used, connect to $V_{AUX5}$ (pin 16).                                                                                                                          |  |  |  |  |

| 20        | VAUX3P3     | Power             | Regulated 3.3 $V_{DC}$ output voltage source. A 4.7 $\mu F$ or higher filtering capacitor must be connected between this pin and AGND.                                                                    |  |  |  |  |

|           |             |                   | When an external 3.3 $V_{DC}$ regulator is used, connect it to this pin to supply the chip.                                                                                                               |  |  |  |  |

# PD69104B1 Pin Descriptions

| con | tinued       |                   |                                                                                                                                                                                                                                                                                                                                        |

|-----|--------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin | Pin Name     | Pin Type          | Description                                                                                                                                                                                                                                                                                                                            |

| 21  | QGND         | Power             | Quiet analog ground                                                                                                                                                                                                                                                                                                                    |

| 22  | IREF         | Analog input      | A reference resistor pin. A 30.1 k $\Omega$ , 1% resistor should be connected between this pin and QGND.                                                                                                                                                                                                                               |

| 23  | TRIM         | Test input        | Trimming input for IC production. Should be connected to $V_{\text{AUX3P3}}.$                                                                                                                                                                                                                                                          |

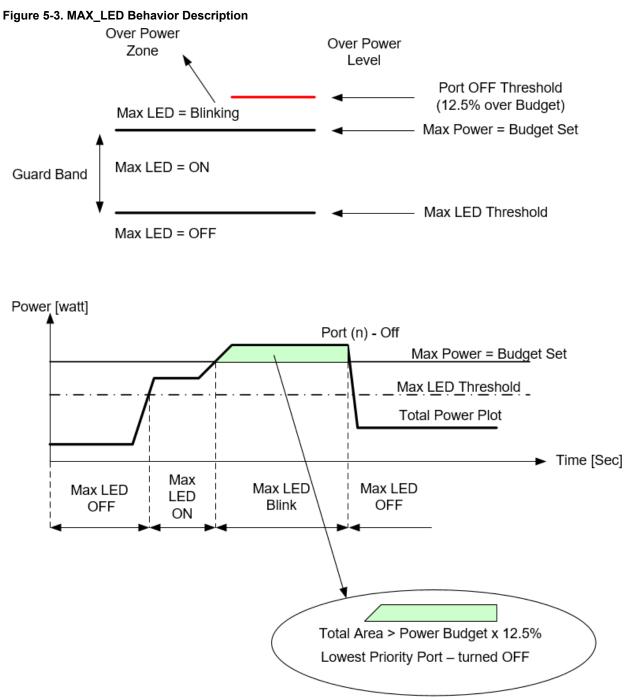

| 24  | MAX_LED      | Open drain output | Maximum LED analog output. Indicates the device has exceeded maximum power budget. See Table 5-1. LED Indications.                                                                                                                                                                                                                     |

| 25  | VPORT_NEG3   | Analog I/O        | Negative port output                                                                                                                                                                                                                                                                                                                   |

| 26  | PORT_SENSE3  | Analog input      | Sense resistor port input (connected to 0.36 $\Omega$ , 1% resistor to QGND with ~6 m $\Omega$ trace for measurements accuracy).                                                                                                                                                                                                       |

| 27  | VPORT_NEG2   | Analog I/O        | Negative port output                                                                                                                                                                                                                                                                                                                   |

| 28  | PORT_SENSE2  | Analog input      | Sense resistor port input (connected to 0.36 $\Omega$ , 1% resistor to QGND with ~6 m $\Omega$ trace for measurements accuracy).                                                                                                                                                                                                       |

| 29  | LED 3        | Open drain output | Port 3 LED indication: active low (0 = LED ON). See Table 5-1. LED Indications.                                                                                                                                                                                                                                                        |

| 30  | LED 2        | Open drain output | Port 2 LED indication: active low (0 = LED ON). See Table 5-1. LED Indications.                                                                                                                                                                                                                                                        |

| 31  | AGND         | Power             | Analog ground                                                                                                                                                                                                                                                                                                                          |

| 32  | 4 pairs mode | Analog input      | <ul> <li>2-state input pin. Select 4-Pairs Mode:</li> <li>0 (GND): 4 ports of 2 pairs</li> <li>1 (VCC): 2 ports of 4 pairs</li> </ul>                                                                                                                                                                                                  |

| 33  | Current_SET  | Analog input      | <ul> <li>3-state input pin, used for selecting output current and AF/AT mode:</li> <li>0 (AGND): AF mode</li> <li>"open" (N.C): Low AT mode 600 mA</li> <li>1 (V<sub>DD</sub>): High AT mode 720 mA</li> </ul>                                                                                                                         |

| 34  | COMM_MODE    | Analog input      | <ul> <li>3-state input pin communication. The following options are available:</li> <li>0 (AGND): UART active</li> <li>"open" (N.C): E2PROM connected and I<sup>2</sup>C active if connected. In this case, within 2PROM Register 0x7E (SYS_CFG) bit 5 (i2c_en) should be set to 1.</li> <li>1 (V<sub>DD</sub>): I2C active</li> </ul> |

| 35  | ALT A/B      | Digital input     | <ul> <li>User input pin, used for setting the chip working mode:</li> <li>GND: ALT B mode = Midspan mode (midsp [1:4] bits = 1)</li> <li>DVDD: ALT A mode = Endspan mode (midsp [1:4] bits = 0)</li> </ul>                                                                                                                             |

| co  | ontinued    |                             |                                                                                                                  |

|-----|-------------|-----------------------------|------------------------------------------------------------------------------------------------------------------|

| Pin | Pin Name    | Pin Type                    | Description                                                                                                      |

| 36  | INT_OUT     | Digital I/O (open<br>drain) | In MCHP Extended Auto mode: User input pin. Used for setting the chip legacy detection mode:                     |

|     |             |                             | <ul> <li>1 (V<sub>DD</sub>): IEEE 802.3af compliant resistor detection<br/>only</li> </ul>                       |

|     |             |                             | <ul> <li>0 (GND): IEEE 802.3 AF/AT Detection and Legacy<br/>(non-standard) line detection</li> </ul>             |

|     |             |                             | In Semi-Auto mode: Interrupt out pin. Indicates an interruption event has occurred.                              |

|     |             |                             | An external $10k\Omega$ pull-up resistor should be connected between this pin and DVDD.                          |

| 37  | Mode0       | Digital input               | Used for IC operational mode selection. See Table 1-2.<br>Mode of Operation.                                     |

| 38  | Mode1       | Digital input               | Used for IC operational mode selection. See Table 1-2.<br>Mode of Operation.                                     |

| 39  | PS_PGD0     | Digital input               | Power supply power good 0; power budget set pin for fast power control. See Table 5-2. Power Budget.             |

| 40  | PS_PGD1     | Digital input               | Power supply power good 1; power budget set pin for fast power control. See Table 5-2. Power Budget.             |

| 41  | PS_PGD2     | Digital input               | Power supply power good 2; power budget set pin for fast power control. See Table 5-2. Power Budget.             |

| 42  | PS_PGD3 /   | Digital I/O (open           | Power supply power good 3;                                                                                       |

|     | E2_SCL      | drain)                      | Power budget set pin—for initial configuration (refer to COMM MODE PIN)                                          |

|     |             |                             | E2_SCL: I <sup>2</sup> C Clock Out to EEPROM                                                                     |

|     |             |                             | When working with EPROM, an external $10k\Omega$ pull-up resistor should be connected between this pin and DVDD. |

| 43  | E2_SDA      | Digital I/O (open<br>drain) | EEPROM I <sup>2</sup> C data I/O pin. Used for power-up configuration in stand-alone systems.                    |

|     |             |                             | An external 10K pull-up resistor should be connected between this pin and DVDD.                                  |

| 44  | DVDD        | Power                       | Digital 3.3 V <sub>DC</sub> power input                                                                          |

| 45  | DGND        | Power                       | Digital GND                                                                                                      |

| 46  | I2C_SCL     | Digital input               | I <sup>2</sup> C bus, serial clock input                                                                         |

|     |             |                             | An external $10k\Omega$ pull-up resistor should be connected between this pin and DVDD.                          |

| 47  | I2C_SDA_out | Digital I/O (open           | I <sup>2</sup> C bus, data output/UART Tx output                                                                 |

|     |             | drain)                      | An external $10k\Omega$ pull-up resistor should be connected between this pin and DVDD.                          |

| continued |            |                             |                                                                                                                                       |  |  |  |  |  |

|-----------|------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin       | Pin Name   | Pin Type                    | Description                                                                                                                           |  |  |  |  |  |

| 48        | I2C_SDA_in | Digital I/O (open<br>drain) | I <sup>2</sup> C bus, data input/UART Rx input<br>An external 10kΩ pull-up resistor should be connected<br>between this pin and DVDD. |  |  |  |  |  |

**Note:** The PD69104B1 pin should be free of large capacitance in order to prevent RPD and MRPD pulses distortion. 0 = connect to DGND and 1 = connect to DVDD.

## 4. Package Information

The following sections describe the package information for the PD69104B1 device.

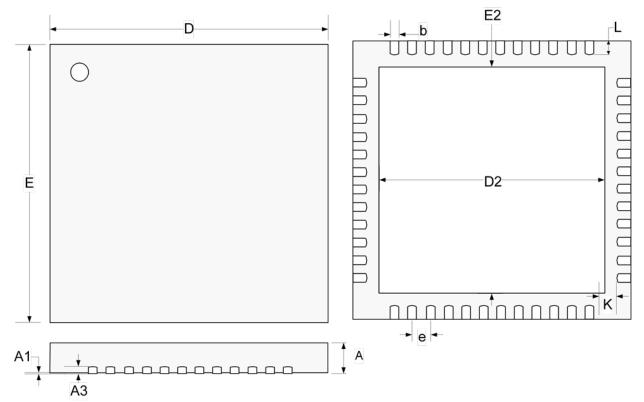

## 4.1 Package Outline Drawing

The following illustration shows the package outline drawing for the PD69104B1 device.

### Figure 4-1. Package Outline Drawing

The following table lists the dimensions and measurements of the PD69104B1 device.

Table 4-1. Dimensions and Measurements

|     | Millimeters |              | Inches    |       |  |

|-----|-------------|--------------|-----------|-------|--|

| Dim | Min         | Max          | Min       | Мах   |  |

| А   | 0.80        | 1.00         | 0.031     | 0.039 |  |

| A1  | 0.00        | 0.05         | 0         | 0.002 |  |

| A3  | 0.20 ref    | 1            | 0.008 ref |       |  |

| К   | 0.20 min    |              | 0.008 min |       |  |

| е   | 0.50 BSC    | 3SC 0.02 BSC |           |       |  |

| L   | 0.30        | 0.50         | 0.012     | 0.02  |  |

| b   | 0.18        | 0.30         | 0.007     | 0.012 |  |

| co  | ontinued    |      |           |       |

|-----|-------------|------|-----------|-------|

|     | Millimeters |      | Inches    |       |

| Dim | Min         | Max  | Min       | Мах   |

| D2  | 6.35        | 6.60 | 0.250     | 0.260 |

| E2  | 6.35        | 6.60 | 0.250     | 0.260 |

| D   | 8.00 BSC    |      | 0.315 BSC |       |

| E   | 8.00 BSC    |      | 0.315 BSC |       |

**Note:** Dimensions do not include protrusions; these should not exceed 0.155 mm (0.006") on any side. The lead dimension shall not include solder coverage.

## 4.2 Thermal Specifications

Thermal resistance-junction to ambient is 25 °C/W.

Thermal resistance-junction to case is 4 °C/W.

**Note:** All of the above assume no ambient airflow. Junction temperature calculation:  $T_J = T_A + (P_D \times \theta_{JA})$ . The  $\theta_{JA}$  numbers are guidelines for the thermal performance of the device/PC-board system.

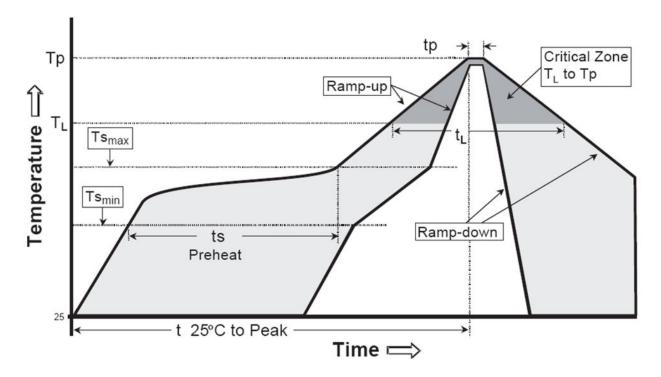

## 4.3 RoHS and Solder Reflow Information

The following lists the recommended RoHS and solder reflow information for the PD69104B1 device.

- RoHS 6/6

- Pb-free 100 % matte tin finish

- Package peak temperature for solder reflow (40 seconds maximum exposure)—260 °C (0 ° C, -5 °C)

Note: Exceeding these ratings can cause damage to the device.

The following table lists the reflow profiles.

#### Table 4-2. Classification Reflow Profiles

| Profile Feature                                                                                                                           | Pb-Free Assembly                           |

|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Average ramp-up rate (TS <sub>max</sub> to Tp)                                                                                            | 3 °C/second max                            |

| Preheat<br>Temperature min (TS <sub>min</sub> )<br>Temperature max (TS <sub>max</sub> )<br>Time (ts <sub>min</sub> to ts <sub>max</sub> ) | 150 °C<br>200 °C<br>60 seconds–180 seconds |

| Time maintained Temperature $(T_L)$ Time $(t_L)$                                                                                          | 217 °C<br>60 seconds–150 seconds           |

| Peak classification temperature $(T_P)$                                                                                                   | 240 °C–255 °C                              |

| Time within 5 °C of actual peak temperature (tp)                                                                                          | 20 seconds-40 seconds                      |

| Ramp-down rate                                                                                                                            | 6 °C/second max                            |

| continued                      |                   |

|--------------------------------|-------------------|

| Profile Feature                | Pb-Free Assembly  |

| Time 25 °C to peak temperature | 8 minutes maximum |

Note: All temperatures refer to topside of the package, measured on the package body surface.

The following figure shows the classification reflow profiles.

Figure 4-2. Classification Reflow Profiles

## 4.4 Tape and Reel Packaging Information

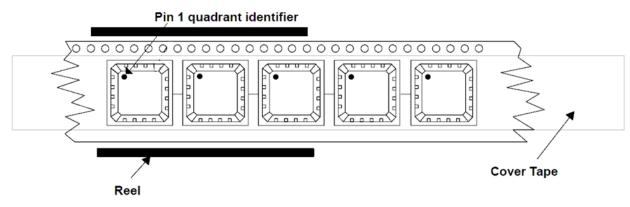

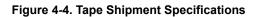

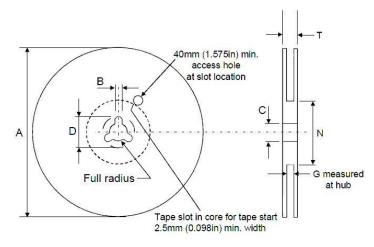

The following figure shows the Pin 1 Orientation.

The following figure shows the tape and reel shipment specifications.

The following table lists the tape mechanical data.

#### Table 4-3. Tape Mechanical Data

| Dimensions | Millimeters |

|------------|-------------|

| Ao         | 8.35 ±0.10  |

| Во         | 8.35 ±0.10  |

| Ко         | 1.40 ±0.10  |

| К1         | N/A         |

| Pitch      | 12.00 ±0.10 |

| Width      | 16.00 ±0.30 |

The following figure shows the reel specifications.

#### Figure 4-5. Reel Specifications

The following table lists the reel mechanical data. The base quantity are 2000 pcs.

| Dimension | Millimeters     | Inch               |

|-----------|-----------------|--------------------|

| Tape size | 16.00 ±0.3      | 0.630 ±0.012       |

| A max     | 330             | 13                 |

| B max     | 1.5             | 0.059              |

| С         | 13.0 ±0.20      | 0.512 ±0.008       |

| D min     | 20.2            | 0.795              |

| N min     | 50              | 1.968              |

| G         | 16.4 + 2.0/-0.0 | 0.645 + 0.079/_0.0 |

| T max     | 29              | 1.142              |

#### Table 4-4. Reel Mechanical Data

## 5. Application Information

PD69104B1 meets IEEE 802.3af and IEEE 802.3at functionality standards, as well as legacy (capacitor) and Cisco PDs detection standards. It also supports additional protections such as short circuit, and dV/dT protection upon port startup.

## 5.1 Line Detection

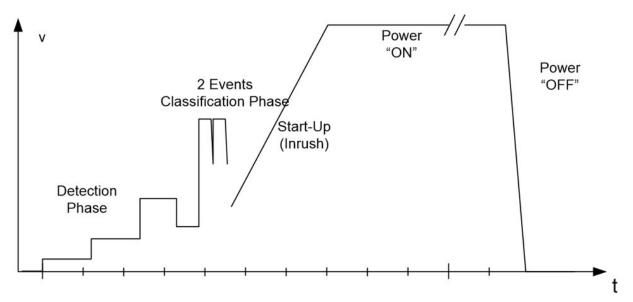

The line detection feature detects a valid AF or AT load, as specified in the IEEE 802.3 standard. The resistance value should range from 19 k $\Omega$  to 26.5 k $\Omega$ . Line detection is based on four different voltage levels generated over the PD (the load), as shown in the following figure.

#### Figure 5-1. Typical PoE Voltage vs. Time Diagram

The first two levels (low voltage level < 3 V) are for detecting if load up to 200 k $\Omega$  is connected to the PSE; preventing from applying high voltages on the PSE when there is no load, and eliminating potential risk to the DTE. If the first detection passes, next two levels of resistor detection are applied. If the PoE detects a valid resistor signature value, the detection is passed. Otherwise, the detection fails and moves to IDLE.

## 5.2 Legacy (Cap) Detection