# **MIC2584**

## **Dual-Channel Hot Swap Controller/Sequencer**

## Features

- 1.0V to 13.2V Supply Voltage Operation

- Surge Voltage Protection Up to 20V

- Current Regulation Limits Inrush Current Regardless of Load Capacitance

- Programmable Inrush Current Limiting

- Electronic Circuit Breaker

- Dual Level Overcurrent Fault Sensing Eliminates False Tripping

- Fast Response to Short Circuit Conditions (<1 µs)</li>

- Undervoltage Output Monitoring

- · Undervoltage Lockout Protection

- · FAULT Status Output

- Power On Reset Output

## Applications

- RAID Systems

- Network Servers

- Base Stations

- Network Switches

- Hot Board Insertion

## **General Description**

The MIC2584 is a dual-channel positive voltage hot swap controller designed to facilitate the safe insertion of boards into live system backplanes. The MIC2584 is available in a 16-lead TSSOP package. Using a few external discrete components and by controlling the gate drives of external N-Channel MOSFET devices, the MIC2584 provides inrush current limiting and output voltage slew rate control in harsh, critical power supply environments. In combination, the device's many features provide a simplified, robust solution for many network applications meeting protection requirements of multiple voltage logic systems.

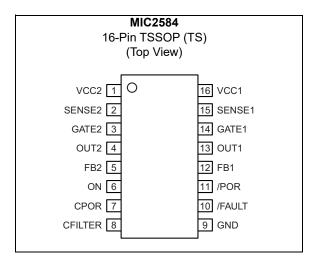

## Package Type

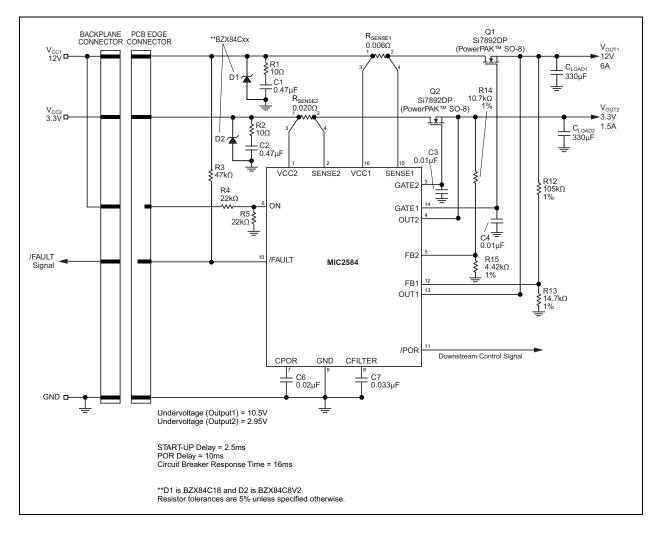

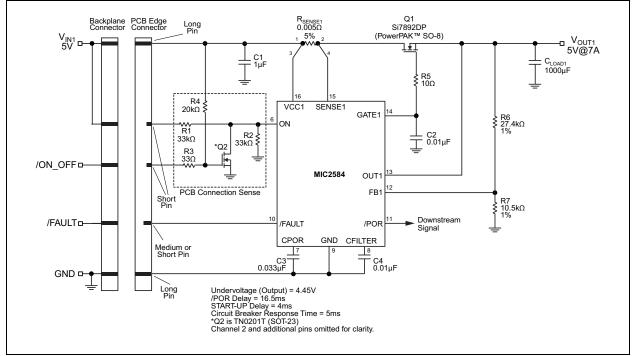

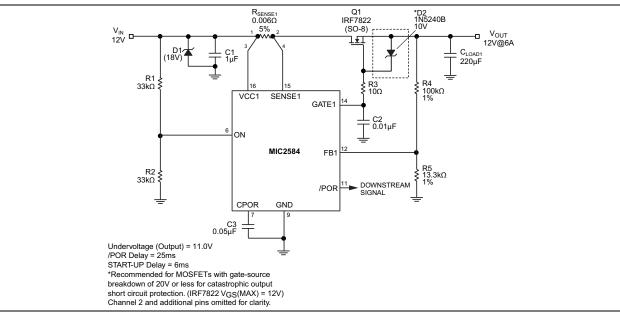

## **Typical Application Circuit**

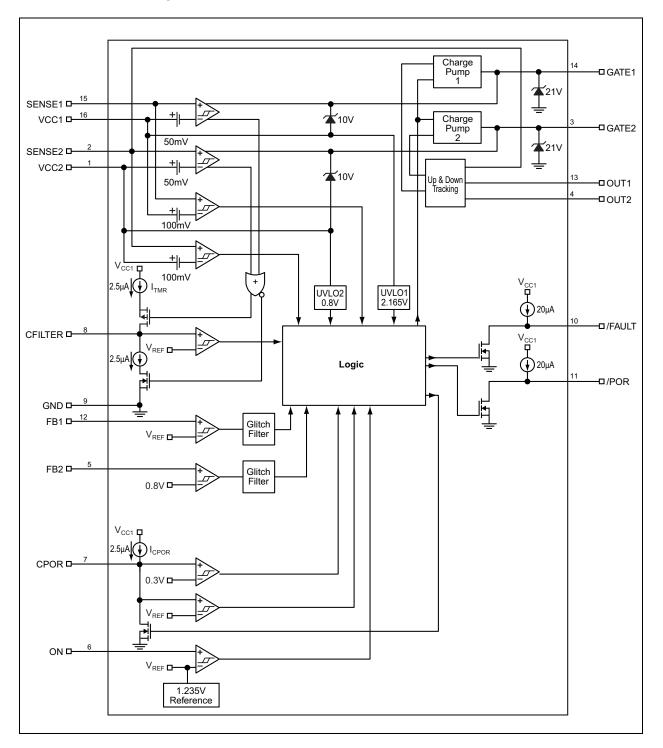

## **Functional Block Diagram**

## 1.0 ELECTRICAL CHARACTERISTICS

## Absolute Maximum Ratings †

| Supply Voltage (V <sub>CC1</sub> /V <sub>CC2</sub> )     | 0.3V to V <sub>CC1/2</sub><br>-0.3V to +15V<br>-0.3V to +25V |

|----------------------------------------------------------|--------------------------------------------------------------|

| ESD Rating (Note 1)<br>Human Body Model<br>Machine Model | 1500V                                                        |

## **Operating Ratings ‡**

| Supply Voltage (V <sub>CC1</sub> ) | +2.3V to +13.2V |

|------------------------------------|-----------------|

| Supply Voltage (V <sub>CC2</sub> ) | +1.0V to +13.2V |

**† Notice:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not intended. Exposure to maximum rating conditions for extended periods may affect device reliability. Specifications are for packaged product only.

**‡ Notice:** The device is not guaranteed to function outside its operating ratings.

Note 1: Devices are ESD sensitive. Handling precautions are recommended.

## **ELECTRICAL CHARACTERISTICS**

**Electrical Characteristics:**  $2.3V \le V_{CC1} \le 13.2V$ ,  $1.0V \le V_{CC2} \le 13.2V$ ,  $T_A = +25^{\circ}C$  unless otherwise noted. **Bold** values indicate  $-40^{\circ}C \le T_A \le +85^{\circ}C$ . (Note 1)

| Parameter                                           | Symbol                | Min.  | Тур.  | Max.  | Units | Conditions                                                                        |

|-----------------------------------------------------|-----------------------|-------|-------|-------|-------|-----------------------------------------------------------------------------------|

| Supply Voltage                                      | V <sub>CC1</sub>      | 2.3   | _     | 13.2  | V     | —                                                                                 |

| Supply Current                                      | I <sub>CC1</sub>      | _     | 1.7   | 3     | mA    | —                                                                                 |

| Supply Voltage                                      | V <sub>CC2</sub>      | 1.0   | —     | 13.2  | V     | $V_{CC2} \le V_{CC1}$                                                             |

| Supply Current                                      | I <sub>CC2</sub>      | —     | 0.05  | 0.15  | mA    | —                                                                                 |

| V <sub>CC1</sub> Undervoltage Lockout<br>Threshold  | V <sub>UV1</sub>      | 2.050 | 2.165 | 2.275 | V     | _                                                                                 |

| V <sub>CC1</sub> Undervoltage Lockout<br>Hysteresis | V <sub>UV1HYS</sub>   | _     | 200   | _     | mV    | _                                                                                 |

| V <sub>CC2</sub> Undervoltage Lockout<br>Threshold  | V <sub>UV2</sub>      | 0.7   | 0.8   | 0.9   | V     | _                                                                                 |

| V <sub>CC2</sub> Undervoltage Lockout<br>Hysteresis | V <sub>UV2HYS</sub>   |       | 30    | _     | mV    | _                                                                                 |

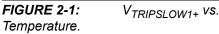

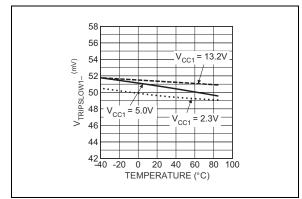

| Slow Trip Overcurrent<br>Threshold                  | V <sub>TRIPSLOW</sub> | 42.5  | 50    | 57.5  | mV    | V <sub>CCx</sub> – V <sub>SENSEx</sub> , V <sub>CC1</sub> = V <sub>CC2</sub> = 5V |

| Slow Trip Overcurrent<br>Hysteresis                 | V <sub>TRIPHYS</sub>  |       | 2.5   | _     | mV    | _                                                                                 |

|                                                     |                       | 90    | 100   | 110   | mV    | $V_{CC1} = V_{CC2} = 5V$ , J option                                               |

| Fast Trip Overcurrent<br>Threshold                  | V <sub>TRIPFAST</sub> | _     | 150   | _     | mV    | $V_{CC1} = V_{CC2} = 5V$ , K option                                               |

|                                                     |                       | _     | 200   |       | mV    | $V_{CC1} = V_{CC2} = 5V$ , L option                                               |

| External Gate Drive                                 | N.                    | 6     | 8     | 10    | V     | $V_{GATEx} - V_{CCx}$<br>( $V_{CC1}$ or $V_{CC2} > 5V$ )                          |

| (GATE1 and GATE2)                                   | V <sub>GATE</sub>     | 3.5   | 4.5   | 8     | V     | $V_{GATEx} - V_{CCx}$<br>( $V_{CC1}$ or $V_{CC2} < 5V$ )                          |

## **ELECTRICAL CHARACTERISTICS (CONTINUED)**

**Electrical Characteristics:**  $2.3V \le V_{CC1} \le 13.2V$ ,  $1.0V \le V_{CC2} \le 13.2V$ ,  $T_A = +25^{\circ}C$  unless otherwise noted. **Bold** values indicate  $-40^{\circ}C \le T_A \le +85^{\circ}C$ . (Note 1)

| Values indicate $-40^{\circ}C \le T_A \le$<br><b>Parameter</b> | Symbol               | Min.  | Тур.  | Max.  | Units | Conditions                                                                                                           |

|----------------------------------------------------------------|----------------------|-------|-------|-------|-------|----------------------------------------------------------------------------------------------------------------------|

| GATE Pin Pull-Up Current                                       | I <sub>GATE</sub>    | -25   | -14   | -8    | μA    | Start cycle                                                                                                          |

|                                                                |                      |       | 50    |       | mA    | /FAULT asserted                                                                                                      |

| GATE Pin Sink Current                                          | IGATEOFF             | 30    | 45    | 70    | μA    | Turn off (ON deasserted)                                                                                             |

| Overcurrent Timer Pin                                          |                      | -3.5  | -2.5  | -1.5  | μA    | V <sub>CCx</sub> – V <sub>SENSEx</sub> = 50 mV                                                                       |

| Charge Current                                                 | I <sub>TMR</sub>     | 1.5   | 2.5   | 3.5   | μA    | $V_{CCx} - V_{SENSEx} = 25 \text{ mV}$                                                                               |

| Overcurrent Timer Pin<br>Threshold                             | V <sub>TMR</sub>     | 1.190 | 1.235 | 1.290 | V     |                                                                                                                      |

| Power-on Reset Current                                         |                      | -3.5  | -2.5  | -1.5  |       | V <sub>CC1</sub> = 5V, C <sub>POR</sub> = 0.5V<br>Charge Current                                                     |

| Power-on Reset Current                                         | ICPOR                |       | 2.5   |       | μA    | V <sub>CC1</sub> = 5V, C <sub>POR</sub> = 0.5V<br>Sink Current                                                       |

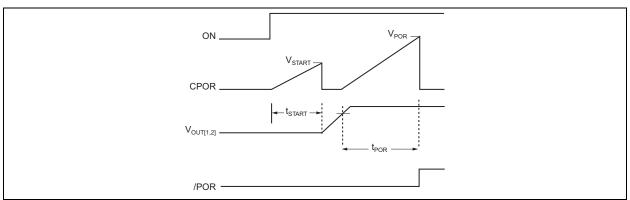

| Power-on Reset Delay<br>Threshold                              | V <sub>POR</sub>     | 1.190 | 1.235 | 1.290 | V     | Start-up cycle                                                                                                       |

| Power-On Reset Delay<br>Threshold Hysteresis                   | V <sub>PORHYS</sub>  |       | 25    |       | mV    | _                                                                                                                    |

| Start-Up Threshold                                             | V <sub>START</sub>   | 0.25  | 0.30  | 0.35  | V     | Start-up cycle                                                                                                       |

| FB1 Threshold                                                  | V <sub>FB1</sub>     | 1.190 | 1.235 | 1.290 | V     | —                                                                                                                    |

| FB1 Threshold Hysteresis                                       | V <sub>FB1HYS</sub>  |       | 25    |       | mV    | —                                                                                                                    |

| FB2 Threshold                                                  | V <sub>FB2</sub>     | 0.75  | 0.80  | 0.85  | V     | —                                                                                                                    |

| FB2 Threshold Hysteresis                                       | V <sub>FB2HYS</sub>  |       | 25    |       | mV    | —                                                                                                                    |

| ON Pin Input Threshold                                         | V <sub>ON</sub>      | 1.190 | 1.235 | 1.290 | V     | —                                                                                                                    |

| ON Pin Hysteresis                                              | V <sub>ONHYS</sub>   | _     | 25    | _     | mV    | —                                                                                                                    |

| ON Pin Input Current                                           | I <sub>ON</sub>      |       | 0.1   | 0.5   | μA    | $V_{ON} = V_{CCx}$                                                                                                   |

| /FAULT, /POR Output Low<br>Voltage                             | V <sub>OL</sub>      |       |       | 0.4   | V     | I <sub>OUT</sub> = 1.6 mA, V <sub>CC1</sub> = 5V                                                                     |

| /FAULT, /POR Active<br>Output Pull-Up Current                  | I <sub>PULLUP</sub>  | 7     | 12    | 22    | μΑ    | ON asserted, V <sub>FB1</sub> > 1.25V, V <sub>FB2</sub> ><br>0.8V, /POR = V <sub>CC1</sub> – 1V                      |

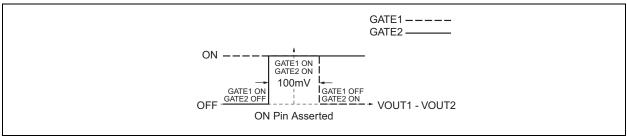

| GATE1 and GATE2<br>ON/OFF Voltage Window                       | V <sub>GATEWIN</sub> | _     | 100   | 250   | mV    | See Timing Diagrams, (Figure 1-2)                                                                                    |

| AC Parameters                                                  |                      |       |       |       |       |                                                                                                                      |

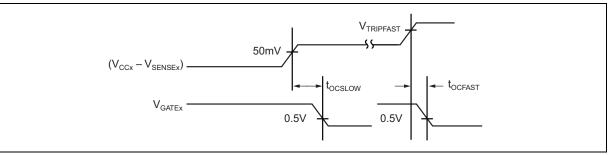

| Fast Overcurrent Sense to<br>GATE Low Trip Time                | t <sub>OCFAST</sub>  | _     | 1     | _     | μs    | $V_{CCx} - V_{SENSEx} = 100 \text{ mV},$<br>$C_{GATE} = 10 \text{ nF}, \text{ See Timing Diagrams},$<br>(Figure 1-3) |

| Slow Overcurrent Sense to<br>GATE Low Trip Time                | t <sub>OCSLOW</sub>  | _     | 20    | _     | μs    | V <sub>CCx</sub> – V <sub>SENSEx</sub> = 50 mV, C <sub>FILTER</sub> = 0                                              |

Note 1: Specification for packaged product only.

## **TEMPERATURE SPECIFICATIONS (Note 1)**

|                                  | •              |      | •    |      |       |                    |

|----------------------------------|----------------|------|------|------|-------|--------------------|

| Parameters                       | Sym.           | Min. | Тур. | Max. | Units | Conditions         |

| Temperature Ranges               |                |      |      |      |       |                    |

| Maximum Junction Temperature     | TJ             | _    | _    | 125  | °C    | Internally Limited |

| Operating Temperature Range      | T <sub>A</sub> | -40  | —    | +85  | °C    | —                  |

| Package Thermal Resistances      |                |      |      |      |       |                    |

| Thermal Resistance 16-Lead TSSOP | $\theta_{JA}$  | _    | 99.1 | —    | °C/W  | —                  |

|                                  |                |      |      |      |       |                    |

**Note 1:** The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junction temperature and the thermal resistance from junction to air (i.e., T<sub>A</sub>, T<sub>J</sub>, θ<sub>JA</sub>).

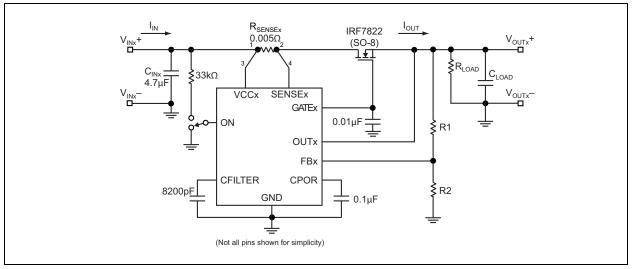

## **Test Circuit**

FIGURE 1-1: MIC2584 Test Circuit.

## **Timing Diagrams**

FIGURE 1-2: Gate Voltage Window.

FIGURE 1-3: Current Limit Response.

FIGURE 1-4: Start-Up Cycle Timing.

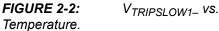

#### 2.0 TYPICAL PERFORMANCE CURVES

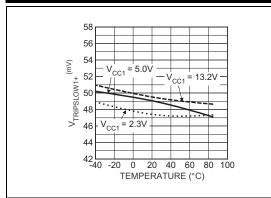

Note: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

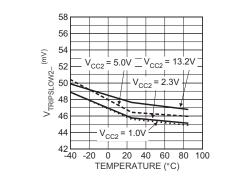

Temperature.

V<sub>TRIPSLOW2</sub>\_ vs.

FIGURE 2-5: Temperature.

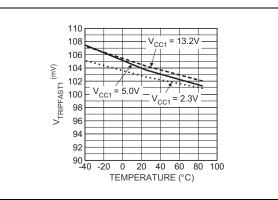

V<sub>TRIPFAST1</sub> vs.

FIGURE 2-6: Temperature.

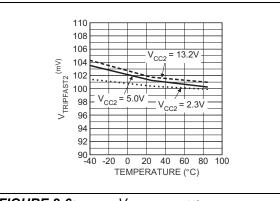

V<sub>TRIPFAST2</sub> vs.

FIGURE 2-7:

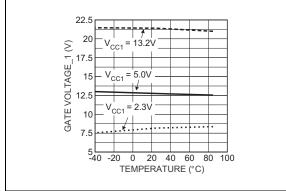

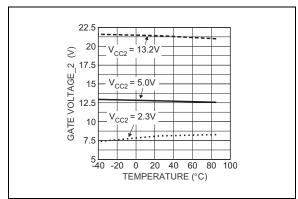

V<sub>GATE1</sub> vs. Temperature.

FIGURE 2-8:

V<sub>GATE2</sub> vs. Temperature.

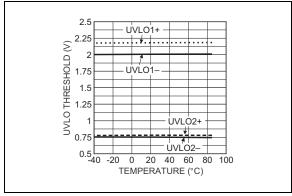

FIGURE 2-9: Temperature.

UVLO1 and UVLO2 vs.

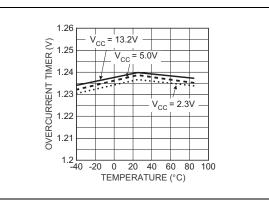

FIGURE 2-10: Overcurrent Timer Threshold vs. Temperature.

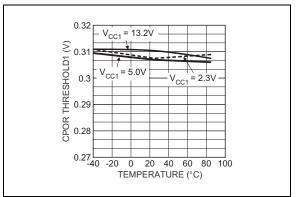

FIGURE 2-11: CPOR Threshold1 (Start-Up) vs. Temperature.

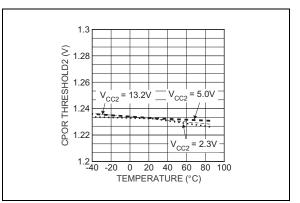

FIGURE 2-12: Temperature.

CPOR Threshold2 vs.

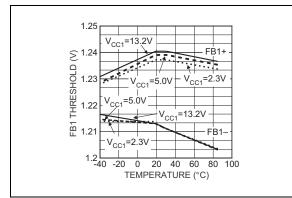

FIGURE 2-13: FB1 Threshold vs. Temperature.

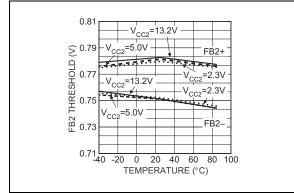

FIGURE 2-14: FB2 Threshold vs. Temperature.

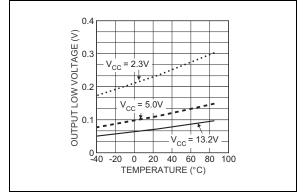

Output Low Voltage vs.

FIGURE 2-15: Temperature.

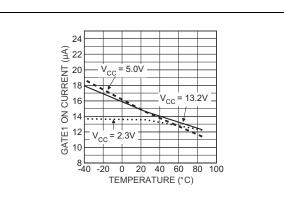

*FIGURE 2-16:* GATE1 On Current vs. Temperature.

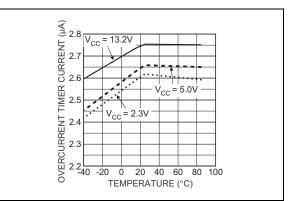

FIGURE 2-17: Overcurrent Timer Discharge Current vs. Temperature.

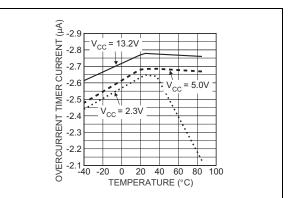

FIGURE 2-18: Overcurrent Timer Charge Current vs. Temperature.

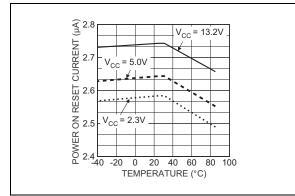

**FIGURE 2-19:** Power On Reset Current vs. Temperature.

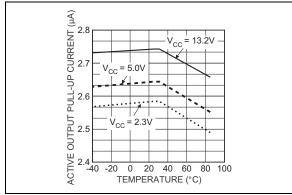

*FIGURE 2-20:* Active Output Pull-Up Current vs. Temperature.

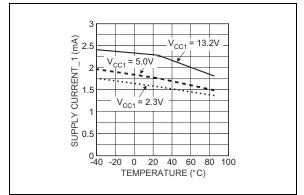

FIGURE 2-21:Supply Current\_1 vs.Temperature.

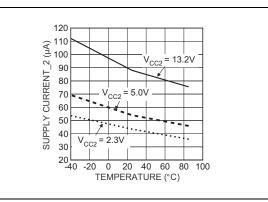

FIGURE 2-22: Supply Current\_2 vs. Temperature.

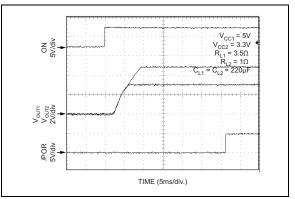

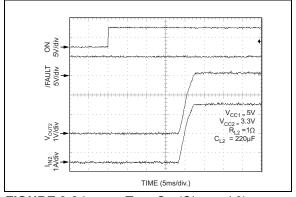

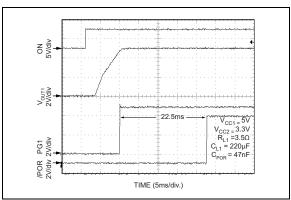

FIGURE 2-23: Turn-On (No Delay).

FIGURE 2-24: Turn-On (Channel 2).

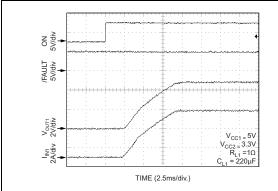

FIGURE 2-25:

Turn-On (Channel 1).

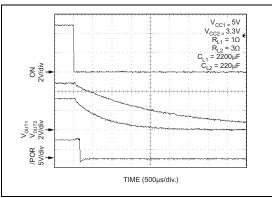

FIGURE 2-26: T

Insert).

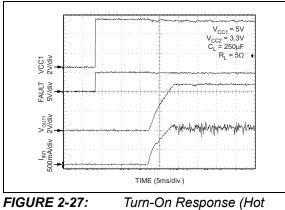

FIGURE 2-28: Power-on Reset Response.

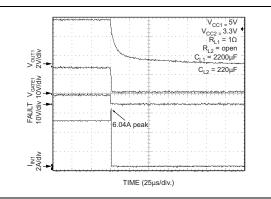

FIGURE 2-29:

Short-Circuit Response.

## 3.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 3-1.

| TABLE 3-1. |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Number | Pin<br>Name       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 1          | VCC2              | Positive Supply (Input), Channel 2: The GATE2 pin is held low by an internal undervoltage lockout circuit until $V_{CC1}$ and $V_{CC2}$ exceed their respective undervoltage lockout threshold of 2.165V and 0.8V. This input must be in the range of 1.0V to 13.2V and be less than or equal to $V_{CC1}$ . This input is protected up to 20V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 2, 15      | SENSE2,<br>SENSE1 | Circuit Breaker Sense (Inputs): A resistor between this pin and VCC1 and VCC2 sets the current limit threshold for each channel. Whenever the voltage across either sense resistor exceeds the slow trip current limit threshold ( $V_{TRIPSLOW}$ ), the GATE voltage is adjusted to ensure a constant load current. If $V_{TRIPSLOW}$ (50 mV) is exceeded for longer than time period $t_{OCSLOW}$ , then the circuit breaker is tripped and both GATE outputs are immediately pulled low. If the voltage across either sense resistor exceeds the fast trip circuit breaker threshold, $V_{TRIPFAST}$ , at any point due to fast, high amplitude power supply faults, then both GATE outputs are immediately brought low without delay. To disable the circuit breaker for either channel, the SENSE and VCC pins can be tied together. The default $V_{TRIPFAST}$ for either device is 100 mV. Other fast trip thresholds are available: 150 mV, 200 mV, or OFF ( $V_{TRIPFAST}$ disabled). Please contact factory for availability of other options. |  |  |  |  |

| 3, 14      | GATE2,<br>GATE1   | Gate Drive (Outputs): Connect each output to the gates of external N-Channel MOSFETs. When ON is asserted, a 14 $\mu$ A current source is activated and begins to charge the gate of the N-Channel MOSFET connected to this pin. An internal clamp ensures that no more than 10V is applied between the GATE and Source when VCC1 or VCC2 is above 5V. When the circuit breaker trips or when an input undervoltage lockout condition is detected, the GATE1 and GATE2 pins are immediately brought low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 4, 13      | OUT2, OUT1        | Output Voltage Monitor (Inputs): For output tracking, connect these pins to their respective output to sense the output voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 5, 12      | FB2, FB1          | Power Good Threshold Input (Undervoltage Detect): FB1 and FB2 are internally compared to 1.235V and 0.80V references with 25 mV of hysteresis, respectively. External resistive divider networks may be used to set the voltage at these pins. If either FB input momentarily goes below its threshold, then /POR is activated for one timing cycle, $t_{POR}$ , indicating an output undervoltage condition. The /POR signal deasserts one timing cycle after the FB pin exceeds its power good threshold by 25 mV. A 5 $\mu$ s filter on these pins prevents glitches from inadvertently activating the /POR signal.                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 6          | ON                | Enable (Input): Active-High. The ON pin, an input to a Schmitt-triggered comparator used to enable/disable the controller, is compared to a 1.235V reference with 25 mV of hysteresis. When a logic high is applied to the ON pin ( $V_{ON} > 1.235V$ ), a start-up sequence begins when the GATE1 and GATE2 pins begin ramping up towards their final operating voltage. When the ON pin receives a logic low signal ( $V_{ON} < 1.21V$ ), the GATE pins are grounded and /FAULT remains high if both inputs are above their respective UVLO thresholds. The ON pin must be low for at least 20 µs in order to initiate a start-up sequence. Additionally, toggling the ON pin LOW to HIGH resets the circuit breaker.                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

TABLE 3-1:PIN FUNCTION TABLE

## TABLE 3-1: PIN FUNCTION TABLE (CONTINUED)

| Pin Number | Pin<br>Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7          | CPOR        | Power-on Reset Timer (Input): A capacitor connected between this pin and ground sets the start-up delay ( $t_{START}$ ) and the power-on reset interval ( $t_{POR}$ ). Once the lagging supply rises above its UVLO threshold and ON asserts, the capacitor connected to CPOR begins to charge. When the voltage at CPOR crosses 0.3V, the start-up threshold ( $V_{START}$ ), a start cycle is initiated as the GATE outputs begin to ramp while capacitor CPOR is immediately discharged to ground. When the voltage at the lagging FB pin rises above its threshold ( $V_{FB}$ ), capacitor CPOR begins to charge again. When the voltage at CPOR rises above the power-on reset delay threshold ( $V_{POR}$ ) of 1.235V, the timer resets by pulling CPOR to ground and /POR is deasserted. If CPOR = 0, then $t_{START}$ defaults to 20 µs. |

| 8          | CFILTER     | Current Limit Response Timer (Input): A capacitor connected to this pin defines the period of time, $t_{OCSLOW}$ , in which an overcurrent event must last to signal a fault condition and trip the circuit breaker. When an overcurrent condition occurs, a 2.5 µA current source begins to charge this capacitor. If the voltage at this pin reaches 1.235V, the circuit breaker is tripped, both GATE pins immediately shut off, and /FAULT is asserted. If $C_{FILTER} = 0$ , then $t_{OCSLOW}$ defaults to 20 µs.                                                                                                                                                                                                                                                                                                                           |

| 9          | GND         | Ground: Tie to analog ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10         | /FAULT      | Circuit Breaker Fault Status (Output): Active-Low, weak pull-up to VCC1 or open-drain. Asserted when the circuit breaker is tripped due to an overcurrent, undervoltage lockout event.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 11         | /POR        | Power-on Reset (Output): Active-Low, weak pull-up to VCC1 or open drain. This pin remains asserted during start-up until a time period ( $t_{POR}$ ) after the lagging FB pin threshold ( $V_{FB1}$ or $V_{FB2}$ ) is exceeded. The timing capacitor CPOR determines $t_{POR}$ . When the output voltage monitored at either FB pin falls below $V_{FB}$ , /POR is asserted for a minimum of one timing cycle ( $t_{POR}$ ).                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 16         | VCC1        | Positive Supply (Input), Channel 1: This input is the main supply to the internal circuitry and must be in the range of 2.3V to 13.2V. The GATE1 pin is held low by an internal undervoltage lockout circuit until $V_{CC1}$ and $V_{CC2}$ exceed their respective undervoltage lockout threshold of 2.165V and 0.8V. This input is protected up to 20V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

## 4.0 FUNCTIONAL DESCRIPTION

## 4.1 Hot Swap Insertion

When circuit boards are inserted into live system backplanes and supply voltages, high inrush currents can result due to the charging of bulk capacitance that resides across the supply pins of the circuit board. This inrush current, although transient in nature, may be high enough to cause permanent damage to on-board components or may cause the system's supply voltages to go out of regulation during the transient period, which may result in system failures. The MIC2584 acts as a controller for external N-channel MOSFET devices in which the gate drive is controlled to provide inrush current limiting and output voltage slew rate control during hot swap insertions.

## 4.2 Power Supply

$V_{CC1}$  is the main supply input to the MIC2584 controller with a voltage range of 2.3V to 13.2V. The  $V_{CC2}$  supply input ranges from 1.0V to 13.2V and must be less than or equal to  $V_{CC1}$  for operation. Both inputs can withstand transient spikes up to 20V. In order to ensure stability of the supplies, a minimum 1  $\mu$ F capacitor from each  $V_{CC}$  to ground is recommended. Alternatively, a low pass filter, shown in the Typical Application Circuit, can be used to eliminate high frequency oscillations as well as help suppress transient spikes.

Also, due to the existence of undetermined parasitic inductance in the absence of bulk capacitance, placing a Zener diode at each  $V_{CC}$  of the controller to ground in order to provide external supply transient protection is strongly recommended. See the Typical Application Circuit.

## 4.3 Start-Up Cycle

## 4.3.1 SUPPLY CONTACT DELAY

During a hot insert of a PC board into a backplane or when the main supply (V<sub>CC1</sub>) is powered up from a cold start, as the voltage at the ON pin rises above its threshold (1.235V typical), the MIC2584 first checks that both supply voltages are above their respective UVLO thresholds. If so, then the device is enabled and an internal 2.5  $\mu$ A current source begins charging the capacitor CPOR to 0.3V to initiate a start-up sequence. Once the start-up delay (t<sub>START</sub>) elapses, the CPOR pin is pulled immediately to ground and a separate 14  $\mu$ A current source begins charging each GATE output to drive the external MOSFET that switches V<sub>IN</sub> to V<sub>OUT</sub>. The programmed contact start-up delay is calculated using Equation 4-1:

#### **EQUATION 4-1:**

$$t_{START} = C_{POR} \times \frac{V_{START}}{I_{CPOR}} \cong 0.12 \times C_{POR}(\mu F)$$

Where:

| Start-up delay timer threshold (V <sub>START</sub> ) = | 0.3V   |

|--------------------------------------------------------|--------|

| Power-on Reset timer current (I <sub>CPOR</sub> ) =    | 2.5 µA |

See Table 4-2 for some typical supply contact start-up delays using several standard value capacitors. As each GATE voltage continues ramping toward its final value ( $V_{CC} + V_{GS}$ ) at a defined slew rate (See the Load Capacitance Dominated Start-Up and GATE Capacitance Dominated Start-Up sections), a second CPOR timing cycle begins if: /FAULT is high and CFILTER is low (i.e., not an overvoltage, undervoltage lockout, or overcurrent state).

This second timing cycle ( $t_{POR}$ ) begins when the lagging voltage exceeds its FB pin threshold ( $V_{FB}$ ). See Figure 1-4 in the Timing Diagrams section. When the power supply is already present (i.e., not a "hot swapping" condition) and the MIC2584 device is enabled by applying a logic high signal at the ON pin, the GATE outputs begin ramping immediately as the first CPOR timing cycle is bypassed. Active current regulation is employed to limit the inrush current transient response during start-up by regulating the load current at the programmed current limit value (See the Current Limiting and Dual-Level Circuit Breaker section). Equation 4-2 is used to determine the nominal current limit value:

## **EQUATION 4-2:**

$$I_{LIM} = \frac{V_{TRIPSLOW}}{R_{SENSE}} = \frac{50mV}{R_{SENSE}}$$

Where:

V<sub>TRIPSLOW</sub> = The current limit slow trip threshold.

R<sub>SENSE</sub> = The selected value that sets the desired current limit.

There are two basic start-up modes for the MIC2584: Start-up dominated by load capacitance and start-up dominated by total gate capacitance. The magnitude of the inrush current delivered to the load will determine the dominant mode. If the inrush current is greater than the programmed current limit ( $I_{LIM}$ ), then load capacitance is dominant. Otherwise, gate capacitance is dominant. The expected inrush current may be calculated using Equation 4-3:

#### **EQUATION 4-3:**

$$INRUSH = I_{GATE} \times \frac{C_{LOAD}}{C_{GATE}} \cong 14 \mu A \times \frac{C_{LOAD}}{C_{GATE}}$$

Where:

$I_{GATE}$  = GATE pin pull-up current  $C_{LOAD}$  = The total GATE capacitance

C<sub>GATE</sub> = Total GATE capacitance (The C<sub>ISS</sub> of the external MOSFET and any external capacitor connected from the MIC2584 GATE pin to ground.)

#### 4.3.2 LOAD CAPACITANCE DOMINATED START-UP

In this case, the load capacitance ( $C_{LOAD}$ ) is large enough to cause the inrush current to exceed the programmed current limit but is less than the fast-trip threshold (or the fast-trip threshold is disabled, 'M' option). During start-up under this condition, the load current is regulated at the programmed current limit value ( $I_{LIM}$ ) and held constant until the output voltage rises to its final value. The output slew rate and equivalent GATE voltage slew rate is computed by Equation 4-4:

## **EQUATION 4-4:**

$$dV_{OUT}/dt = \frac{I_{LIM}}{C_{LOAD}}$$

Where:

I<sub>LIM</sub> = The programmed current limit value.

Consequently, the value of  $C_{FILTER}$  must be selected to ensure that the overcurrent response time,  $t_{OCSLOW}$ , exceeds the time needed for the output to reach its final value. For example, given a MOSFET with an input capacitance  $C_{ISS} = C_{GATE} = 2000 \text{ pF}$ ,  $C_{LOAD}$  is 1000 µF, and  $I_{LIM}$  is set to 5A with a 12V input, then the load capacitance dominates as determined by the calculated INRUSH >  $I_{LIM}$ . Therefore, the output voltage slew rate determined from Equation 4-5 is:

#### **EQUATION 4-5:**

$$dV_{OUT}/dt = \frac{5A}{100\mu F} = 5 \times \frac{V}{ms}$$

The resulting  $t_{OCSLOW}$  needed to achieve a 12V output is approximately 2.5 ms. See the Power-on Reset, Overcurrent Timer, and Sequenced Output Delays section to calculate  $t_{OCSLOW}$ .

#### 4.3.3 GATE CAPACITANCE DOMINATED START-UP

In this case, the value of the load capacitance relative to the GATE capacitance is small enough such that during start-up the output current never exceeds the current limit threshold as determined by Equation 4-3. The minimum value of  $C_{GATE}$  that will ensure that the current limit is never exceeded is given by Equation 4-6:

#### **EQUATION 4-6:**

$$C_{GATE(MIN)} = \frac{I_{GATE}}{I_{LIMIT}} \times C_{LOAD}$$

Where:

$C_{GATE}$  = The summation of the MOSFET input capacitance ( $C_{ISS}$ ) specification and the value of the capacitor connected to the GATE pin of the MIC2584 (and MOSFET) to ground.

Once  $C_{GATE}$  is determined, use Equation 4-7 to determine the output slew rate  $dV_{OUT}/dt$  for gate capacitance dominated start-up:

## **EQUATION 4-7:**

$$dV_{OUT}/dt = \frac{I_{GATE}}{C_{GATE}}$$

Table 4-1 depicts the output slew rate for various values of  $C_{GATE}$ .

#### TABLE 4-1: OUTPUT SLEW RATE SELECTION FOR GATE CAPACITANCE DOMINATED START-UP

| I <sub>GATE</sub> = | <sup>=</sup> 14 μA    |

|---------------------|-----------------------|

| C <sub>GATE</sub>   | dV <sub>OUT</sub> /dt |

| 0.001 µF            | 14V/ms                |

| 0.01 µF             | 1.4V/ms               |

| 0.1 µF              | 0.14V/ms              |

| 1 µF                | 0.014V/ms             |

## 4.4 Current Limiting and Dual-Level Circuit Breaker

Many applications will require that the inrush and steady state supply current be limited at a specific value in order to protect critical components within the system. Connecting a sense resistor between the VCC and SENSE pins of each channel sets the nominal current limit value for each channel of the MIC2584 and the current limit is calculated using Equation 4-2.

The MIC2584 also features a dual-level circuit breaker triggered via 50 mV and 100 mV current limit thresholds sensed across the VCC and SENSE pins. The first level of the circuit breaker functions as follows. For the MIC2584, once the voltage sensed across these two pins exceeds 50 mV on either channel, the overcurrent timer, its duration set by capacitor C<sub>FILTER</sub>, starts to ramp the voltage at CFILTER using a 2.5 µA constant current source. If the voltage at CFILTER reaches the overcurrent timer threshold ( $V_{TMR}$ ) of 1.235V, then CFILTER immediately returns to ground as the circuit breaker trips and both GATE outputs are immediately shut down. For the second level, if the voltage sensed across VCC and SENSE of either channel exceeds 100 mV (-J option) at any time, the circuit breaker trips and both GATE outputs shut down immediately, bypassing the overcurrent timer period. To disable current limit and circuit breaker operation, tie each channel's SENSE and VCC pins together and the CFILTER pin to ground.

## 4.5 Output Undervoltage Detection

The MIC2584 employ output undervoltage detection by monitoring the output voltage through a resistive divider connected at the FB pins. During turn on, while the voltage at either FB pin is below its threshold (V<sub>FB</sub>), the /POR pin is asserted low. Once both FB pin voltages cross their respective threshold (V<sub>FB</sub>), a 2.5  $\mu$ A current source charges capacitor C<sub>POR</sub>. Once the CPOR pin voltage reaches 1.235V, the time period t<sub>POR</sub> elapses as pin CPOR is pulled to ground and the /POR pin goes HIGH. If the voltage at either FB drops below V<sub>FB</sub> for more than 10  $\mu$ s, the /POR pin resets for at least one timing cycle defined by t<sub>POR</sub> (See Application Information for an example).

## 4.6 Power-on Reset, Overcurrent Timer, and Sequenced Output Delays

The Power-on Reset delay,  $t_{POR}$ , is the time period for the /POR pin to go HIGH once the lagging voltage exceeds the power good threshold (V<sub>FB</sub>) monitored at the FB pin. A capacitor connected to CPOR sets the interval and is determined by using Equation 4-8 with V<sub>POR</sub> substituted for V<sub>START</sub>. The resulting equation becomes:

## **EQUATION 4-8:**

$$t_{POR} = C_{POR} \times \frac{V_{POR}}{I_{CPOR}} \cong 0.5 \times C_{POR}(\mu F)$$

Where:

| V <sub>POR</sub> (Power-on Reset threshold) = | 1.235V |

|-----------------------------------------------|--------|

| I <sub>CPOR</sub> (Timer current) =           | 2.5 µA |

For the MIC2584, a capacitor connected to CFILTER is used to set the timer that activates the circuit breaker during overcurrent conditions. When the voltage across either sense resistor exceeds the slow trip current limit threshold of 50 mV, the overcurrent timer begins to charge for a period,  $t_{OCSLOW}$ , determined by C<sub>FILTER</sub>. If  $t_{OCSLOW}$  elapses, then the circuit breaker is activated and both GATE outputs are immediately pulled to ground. The following equation is used to determine the overcurrent timer period,  $t_{OCSLOW}$ .

## **EQUATION 4-9:**

$$t_{OCSLOW} = C_{FILTER} \times \frac{V_{TMR}}{I_{TMR}} \cong 0.5 \times C_{FILTER}(\mu F)$$

Where:

The overcurrent timer threshold ( $V_{TMR}$ ) = 1.235V The overcurrent timer current ( $I_{TMR}$ ) = 2.5  $\mu$ A

If no capacitor for CFILTER is used, then  $t_{OCSLOW}$  defaults to 20  $\mu$ s.

Table 4-2 and Table 4-3 provide a quick reference for several timer calculations using selected standard value capacitors.

## 4.7 Undervoltage Lockout

Internal circuitry keeps both GATE output charge pumps off until  $V_{CC1}$  and  $V_{CC2}$  exceed 2.165V and 0.8V, respectively.

#### TABLE 4-2: SELECTED POWER-ON RESET AND START-UP DELAYS

| C <sub>POR</sub> | t <sub>start</sub> | t <sub>POR</sub> |

|------------------|--------------------|------------------|

| 0.01 µF          | 1.2 ms             | 5 ms             |

| 0.033 µF         | 4 ms               | 16.5 ms          |

| 0.05 µF          | 6 ms               | 25 ms            |

| 0.1 µ µF         | 12 ms              | 50 ms            |

| 0.33 µF          | 40 ms              | 165 ms           |

| 0.47 µF          | 56 ms              | 235 ms           |

| 1 µF             | 120 ms             | 500 ms           |

# TABLE 4-3:SELECTED OVERCURRENTTIMER DELAYS

| C <sub>FILTER</sub> | toscLow |

|---------------------|---------|

| 220 pF              | 110 µs  |

| 680 pF              | 340 µs  |

| 1000 pF             | 500 μs  |

| 3300 pF             | 1.6 ms  |

| 0.01 µF             | 5 ms    |

| 0.047 µF            | 23.5 ms |

| 0.1 µF              | 50 ms   |

| 0.33 µF             | 165 ms  |

## 5.0 APPLICATION INFORMATION

## 5.1 Output Tracking and Sequencing

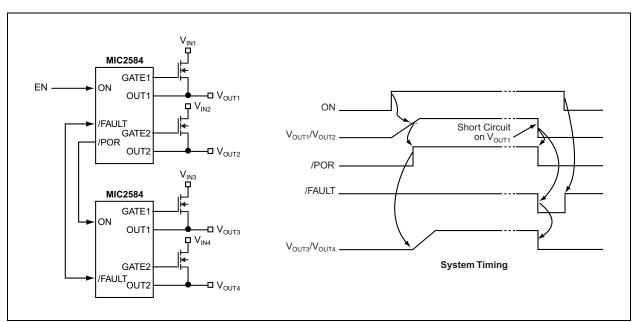

The MIC2584 can be used in systems that support more than two supplies. Figure 5-1 illustrates the generic use of two separate controllers configured to support four independent supply rails with an associated output timing response. The /POR output of the first controller is used to enable the second controller. As configured, a fault condition on either  $V_{OUT1}$  or  $V_{OUT2}$  will result in all channels being shut down. For systems with multiple power sequencing requirements, the controllers' output tracking and sequencing features can be implemented in order to meet the system's timing demands.

FIGURE 5-1:

Supporting More Than Two Supplies.

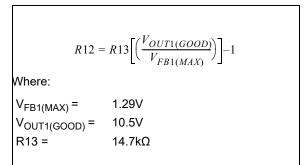

## 5.2 Output Undervoltage Detection

For output undervoltage detection, the first consideration is to establish the output voltage level that indicates "power is good." For this example, the output value for which a 12V supply will signal "good" is 10.5V. Next, consider the tolerances of the input supply and FB threshold (V<sub>FB</sub>). For this example, given a 12V ±5% supply for Channel 1, the resulting output voltage may be as low as 11.4V and as high as 12.6V. Additionally, the FB1 threshold has ±50 mV tolerance and may be as low as 1.19V and as high as 1.29V. Thus, to determine the values of the resistive divider network (R12 and R13) at the FB1 pin, shown in Typical Application Circuit, use the following iterative design procedure.

Choose R13 so as to limit the current through the divider to approximately 100  $\mu A$  or less.

#### **EQUATION 5-1:**

$$R13 \cong \frac{V_{FB1(MAX)}}{100 \mu A} \cong \frac{1.29 V}{100 \mu A} \cong 12.9 k\Omega$$

Where:

R13 = 14.7 kO +1%

Next, determine R12 using the output "good" voltage of 10.5V and Equation 5-2:

#### **EQUATION 5-2:**

$$V_{OUT1(GOOD)} = V_{FB1(MAX)} \left[ \frac{(R12 + R13)}{R13} \right]$$

Using some basic algebra and simplifying Equation 5-2 to isolate R12, yields:

## **EQUATION 5-3:**

Substituting these values into Equation 5-3 now yields R12 = 104.95 k $\Omega$ . A standard 105 k $\Omega$  ±1% is selected. Now, consider the 11.4V minimum output voltage, the lower tolerance for R13 and higher tolerance for R12, 14.55 k $\Omega$  and 106.05 k $\Omega$ , respectively. With only 11.4V available, the voltage sensed at the FB1 pin exceeds V<sub>FB1(MAX)</sub>, thus the /POR signal will transition from LOW to HIGH indicating "power is good" given the worse case tolerances of this example. A similar approach should be used for Channel 2

## 5.3 PCB Connection Sense

There are several configuration options for the MIC2584's ON pin to detect if the PCB has been fully seated in the backplane before initiating a start-up cycle. In Typical Application Circuit, the MIC2584 is mounted on the PCB with a resistive divider network connected to the ON pin. R4 is connected to a short pin on the PCB edge connector. Until the connectors mate, the ON pin is held low which keeps the GATE output charge pump off. Once the connectors mate, the resistor network is pulled up to the input supply, 12V in this example, and the ON pin voltage exceeds its threshold (V<sub>ON</sub>) of 1.235V and the MIC2584 initiates a start-up cycle. In Figure 5-2, the connection sense consisting of a discrete logic-level MOSFET and a few resistors allows for interrupt control from the processor or other signal controller to shut off the output of the MIC2584. R4 pulls the GATE of Q2 to V<sub>IN</sub> and the ON pin is held low until the connectors are fully mated. Once the connectors fully mate, a logic LOW at the /ON OFF signal turns Q2 off and allows the ON pin to pull up above its threshold and initiate a start-up cycle. Applying a logic HIGH at the /ON OFF signal will turn Q2 on and short the ON pin of the MIC2584 to ground, which turns off the GATE output charge pump.

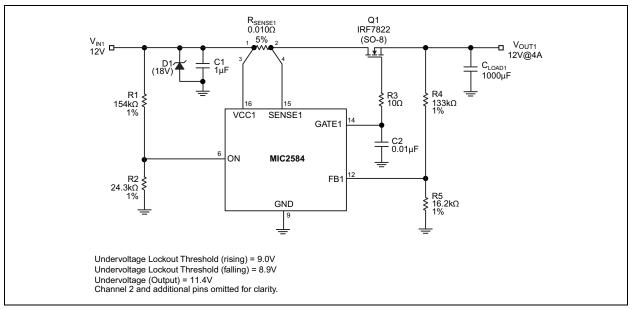

## 5.4 Higher UVLO Setting

Once a PCB is inserted into a backplane (power supply), the internal UVLO circuit of the MIC2584 holds the GATE output charge pump off until V<sub>CC1</sub> exceeds 2.165V and V<sub>CC2</sub> exceeds 0.8V. If V<sub>CC1</sub> falls below 1.935V or V<sub>CC2</sub> falls below 0.77V, the UVLO circuit pulls the GATE output to ground and clears the overvoltage and/or current limit faults. For a higher UVLO threshold, the circuit in Figure 5-3 can be used to delay the output MOSFET from switching on until the desired input voltage is achieved. The circuit allows the charge pumps to remain off until V<sub>IN1</sub> exceeds

$(1 + R1/R2) \times 1.235V$ , provided that V<sub>CC2</sub> has exceeded its threshold. Both GATE drive outputs will be shut down when V<sub>IN1</sub> falls below  $(1 + R1/R2) \times 1.21V$ .

In Figure 5-3, the rising UVLO threshold is set at approximately 9.0V and the falling UVLO threshold is established as 8.9V. The circuit consists of an external resistor divider at the ON pin that keeps both GATE output charge pumps off until the voltage at the ON pin exceeds its threshold ( $V_{ON}$ ) and after the start- up timer elapses.

FIGURE 5-2:

PCB Connection Sense with ON/OFF Control.

Higher UVLO Setting.

## 5.5 Sense Resistor Selection

The MIC2584 uses a low value sense resistor to measure the current flowing through the MOSFET switch (and therefore the load). This sense resistor is nominally set at 50 mV/I<sub>LOAD(CONT)</sub>. To accommodate worst case tolerances for both the sense resistor (allow  $\pm 3\%$  over time and temperature for a resistor with  $\pm 1\%$

initial tolerance) and still supply the maximum required steady-state load current, a slightly more detailed calculation must be used.

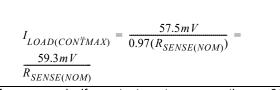

The current limit threshold voltage (i.e., the "trip point") for the MIC2584 may be as low as 42.5 mV, which would equate to a sense resistor value of 42.5 mV/I<sub>LOAD(CONT)</sub>. Carrying the numbers through for the case where the value of the sense resistor is 3% high yields:

## **EQUATION 5-4:**

$$R_{SENSE(MAX)} = \frac{42.5mV}{(1.03)(I_{LOAD(CONT)})} = \frac{41.3mV}{I_{LOAD(CONT)}}$$

Once the value of  $R_{SENSE}$  has been chosen in this manner, it is good practice to check the maximum  $I_{LOAD(CONT)}$  which the circuit may let through in the case of tolerance build-up in the opposite direction. Here, the worst case maximum current is found using a 57.5 mV trip voltage and a sense resistor that is 3% low in value. The resulting equation is:

#### **EQUATION 5-5:**

As an example, if an output must carry a continuous 6A without nuisance trips occurring, Equation 5-4 yields:

## **EQUATION 5-6:**

$$R_{SENSE(MAX)} = \frac{41.3mV}{6A} = 6.88m\Omega$$

The next lowest standard value is  $6 \text{ m}\Omega$ , and the other set of tolerance extremes for the output in guestion.

## **EQUATION 5-7:**

$$I_{LOAD(CONTMAX)} = \frac{59.3mV}{6.0m\Omega} = 9.88A$$

Knowing this final data, we can determine the necessary wattage of the sense resistor using  $P = I^2 R$ , where I will be  $I_{LOAD(CONTMAX)}$ , and R will be (0.97)( $R_{SENSE(NOM)}$ ). These numbers yield the following:

#### **EQUATION 5-8:**

$$P_{MAX} = (9.88A)^2 \times (5.82m\Omega) = 0.568W$$

In this example, a 1W sense resistor is sufficient.

#### 5.6 MOSFET Selection

Selecting the proper external MOSFET for use with the MIC2584 involves three straightforward tasks:

- Choose a MOSFET that meets minimum voltage requirements.

- Select a device to handle the maximum continuous current (steady-state thermal issues).

- Verify the selected part's ability to withstand any peak currents (transient thermal issues).

## 5.7 MOSFET Voltage Requirements

The first voltage requirement for the MOSFET is easily stated: the drain-source breakdown voltage of the MOSFET must be greater than  $V_{IN(MAX)}$ . For instance, a 12V input may reason ably be expected to see high frequency transients as high as 18V. Therefore, the drain-source breakdown voltage of the MOSFET must be at least 19V. For ample safety margin and standard availability, the closest minimum value will be 20V.

The second breakdown voltage criterion that must be met is a bit subtler than simple drain source breakdown voltage, but is not hard to meet. In MIC2584 applications, the gate of the external MOSFET is driven up to approximately 20V by the internal output MOSFET (again, assuming 12V operation). At the same time, if the output of the external MOSFET (its source) is suddenly subjected to a short, the gate source voltage will go to (20V - 0V) = 20V. This means that the external MOSFET must be chosen to have a gate-source breakdown voltage of 20V or more, which is an available standard maximum value. However, if operation is above 12V, the 20V gate source maximum will likely be exceeded. As a result, an external Zener diode clamp should be used to prevent breakdown of the external MOSFET when operating at voltages above 10V. A Zener diode with 10V rating is recommended as shown in Figure 5-4. At the present time, most power MOSFETs with a 20V gate-source voltage rating have a 30V drain source break down rating or higher. As a general tip, choose surface mount devices with a drain source rating of 30V as a starting point.

Finally, the external gate drive of the MIC2584 requires a low voltage logic level MOSFET when operating at voltages lower than 3V. There are 2.5V logic level MOSFETs available.

## 5.8 MOSFET Steady State Thermal Issues

The selection of a MOSFET to meet the maximum continuous current is a fairly straightforward exercise. First, the following steps have to be taken:

- The value of I<sub>LOAD(CONTMAX)</sub> for the output in question (see Sense Resistor Selection).

- The manufacturer's data sheet for the candidate MOSFET.

- The maximum ambient temperature in which the device will be required to operate.

- Any information that can be acquired about the heat sinking available to the device (e.g., through the ground plane/power plane).

The data sheet will almost always give a value of on resistance given for the MOSFET at a gate source voltage of 4.5V, and another value at a gate source voltage of 10V. As a first approximation, add the two values together and divide by two to get the on resistance of the part with 8V of enhancement. Call this value RON. Because a heavily enhanced MOSFET acts as an ohmic (resistive) device, almost all that's required to determine steady state power dissipation is to calculate I<sup>2</sup>R. The one addendum to this is that MOSFETs have a slight increase in RON with increasing die temperature. A good approximation for this value is 0.5% increase in R<sub>ON</sub> per °C rise in junction temperature above the point at which RON was initially specified by the manufacturer. For instance, if the selected MOSFET has a calculated  $R_{ON}$  of 10  $m\Omega$ at T<sub>.I</sub> = 25°C, and the actual junction temperature ends up at 110°C, a good first cut at the operating value for R<sub>ON</sub> would be:

## **EQUATION 5-9:**

$$R_{\Omega N} \cong 10m\Omega[1 + (110 - 25)(0.005)] \cong 14.3m\Omega$$

The final step is to make sure that the heat sinking available to the MOSFET is capable of dissipating at least as much power (rated in °C/W) as that with which the MOSFET's performance was specified by the manufacturer. Here are a few practical tips:

- The heat from a surface mount device such as an SO-8 MOSFET flows almost entirely out of the drain leads. If the drain leads can be soldered down to one square inch or more, the copper will act as the heat sink for the part. This copper must be on the same layer of the board as the MOSFET drain.

- Even a few LFM (linear feet per minute) of air will cool a MOSFET down substantially. If possible,

position the MOSFET(s) near the inlet of a power supply's fan, or the outlet of a processor's cooling fan.

• The best test of a surface mount MOSFET for an application (assuming the above tips show it to be a likely fit) is an empirical one. Check the MOSFET's temperature in the actual layout of the expected final circuit, at full operating current. The use of a thermocouple on the drain leads, or infrared pyrometer on the package, will then give a reasonable idea of the device's junction temperature.

## 5.9 MOSFET Transient Thermal Issues

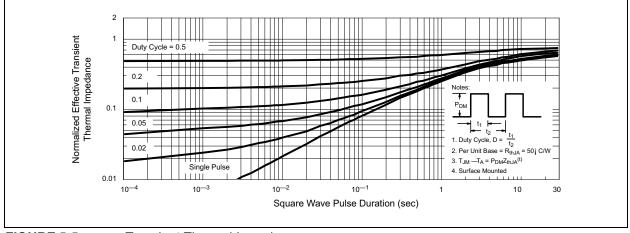

Having chosen a MOSFET that will withstand the imposed voltage stresses, and the worst case continuous I<sup>2</sup>R power dissipation which it will see, it remains only to verify the MOSFET's ability to handle short term overload power dissipation without overheating. A MOSFET can handle a much higher pulsed power without damage than its continuous dissipation ratings would imply. The reason for this is that, like everything else, thermal devices (silicon die, lead frames, etc.) have thermal inertia.

In terms related directly to the specification and use of power MOSFETs, this is known as "transient thermal impedance," or  $Z_{\theta(JA)}$ . Almost all power MOSFET data sheets give a Transient Thermal Impedance Curve. For example, take the following case:  $V_{IN} = 12V$ ,  $t_{OCSLOW}$  has been set to 100 ms  $I_{LOAD(CONT.MAX)}$  is 1.2A, the slow-trip threshold is 50 mV nominal, and the fast trip threshold is 100 mV. If the output is accidentally connected to a 6 $\Omega$  load, the output current from the MOSFET will be regulated to 1.2A for 100 ms ( $t_{OCSLOW}$ ) before the part trips. During that time, the dissipation in the MOSFET is given by:

## EQUATION 5-10:

$$P = E \times IE_{MOSEET} = [12V - (1.2A)(6\Omega)] = 4.8V$$

$$P_{MOSFET} = (4.8V \times 1.2A) = 5.76W for 100 ms$$

At first glance, it would appear that a really hefty MOSFET is required to withstand this sort of fault condition. This is where the transient thermal impedance curves become very useful. Figure 5-5 shows the curve for the Vishay (Siliconix) Si4410DY, a commonly used SO-8 power MOSFET.

Taking the simplest case first, we'll assume that once a fault event such as the one in question occurs, it will be a long time, 10 minutes or more, before the fault is isolated and the channel is reset. In such a case, we

can approximate this as a "single pulse" event, that is to say, there's no significant duty cycle. Then, reading up from the X-axis at the point where "Square Wave Pulse Duration" is equal to 0.1sec (= 100 ms), we see that the  $Z_{\theta(JA)}$  of this MOSFET to a highly infrequent event of this duration is only 8% of its continuous  $R_{\theta(JA)}$ .

This particular part is specified as having an  $R_{\theta(JA)}$  of 50°C/W for intervals of 10 seconds or less. Assume  $T_A$  = 55°C maximum, 1 square inch of copper at the drain leads, no airflow.

Recalling from the previous approximation hint, the part has an  $R_{ON}$  of (0.0335/2) = 17 m $\Omega$  at 25°C.

Assume it has been carrying just about 1.2A for some time.

When performing this calculation, be sure to use the highest anticipated ambient temperature ( $T_{A(MAX)}$ ) in which the MOSFET will be operating as the starting temperature, and find the operating junction temperature increase ( $\Delta T_J$ ) from that point. Then, as shown next, the final junction temperature is found by adding  $T_{A(MAX)}$  and  $\Delta T_J$ . Because this is no a closed form equation, getting a close approximation may take one or two iterations, but it's not a hard calculation to perform, and tends to converge quickly.

Then the starting (steady state)  $T_J$  is:

## EQUATION 5-11:

$$\begin{split} T_{J} &\cong T_{A(MAX)} + \Delta T_{J} &\cong T_{A(MAX)} + \\ [R_{ON} + (T_{A(MAX)} - T_{A})(0.005/(^{\circ}C))(R_{ON})] \times \\ I^{2} &\times R_{\theta(JA)} \\ \\ T_{J} &\cong 55^{\circ}C + [17m\Omega + (55^{\circ}C - 25^{\circ}C)(0.005) \\ (17m\Omega)] \times (1.2A)^{2} \times (50^{\circ}C/W) \\ \\ T_{J} &\cong (55^{\circ}C + (0.02815W)(50^{\circ}C/W) \cong 54.6^{\circ}C \end{split}$$

Iterate the calculation once to see if this value is within a few percent of the expected final value.For this iteration, we will start with  $T_J$  equal to the already calculated value of 54.6°C.

#### **EQUATION 5-12:**

$$T_{J} \cong T_{A} + [17m\Omega + (56.4^{\circ}C - 25^{\circ}C)(0.005) \\ (17m\Omega)] \times (1.2A)^{2} \times (50^{\circ}C/W)$$

$$T_I \cong (55^{\circ}C + (0.02832W)(50^{\circ}C/W) \cong 56.42^{\circ}C$$

FIGURE 5-4:

Zener Clamped MOSFET Gate.

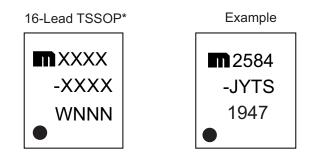

## 6.0 PACKAGING INFORMATION

## 6.1 Package Marking Information

| Legend: | <ul> <li>XX Product code or customer-specific information<br/>Year code (last digit of calendar year)<br/>YY Year code (last 2 digits of calendar year)</li> <li>WW Week code (week of January 1 is week '01')</li> <li>NN Alphanumeric traceability code</li> <li>Pb-free JEDEC<sup>®</sup> designator for Matte Tin (Sn)<br/>This package is Pb-free. The Pb-free JEDEC designator (€3)<br/>can be found on the outer packaging for this package.</li> <li>A, ▼ Pin one index is identified by a dot, delta up, or delta down (triangle nark).</li> </ul> |  |  |  |  |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| t<br>t  | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information. Package may or may not include<br>the corporate logo.<br>Underbar (_) and/or Overbar ( <sup>-</sup> ) symbol may not be to scale.                                                                                                                                                                                                             |  |  |  |  |  |

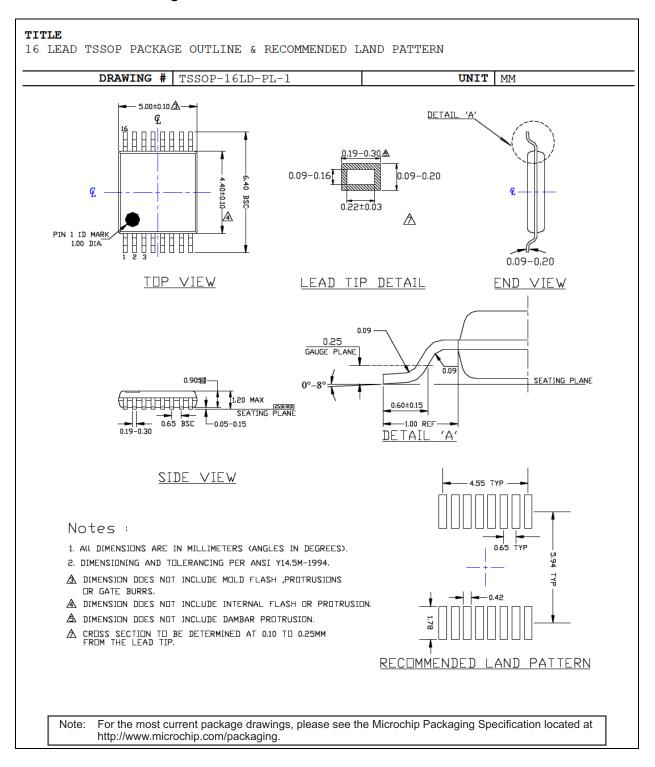

#### 16-Lead TSSOP Package Outline and Recommended Land Pattern

NOTES:

## APPENDIX A: REVISION HISTORY

## **Revision A (March 2023)**

- Converted Micrel document MIC2584 to Microchip data sheet DS20006617A.

- Minor text changes throughout.

- All reference to the EOL MIC2585 removed.

NOTES:

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, contact your local Microchip representative or sales office.

| PART NO.                       | _X                      | X                                           | XX          | -XX        | Example             | es:                                               |                                                                                                                                                                                                           |

|--------------------------------|-------------------------|---------------------------------------------|-------------|------------|---------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device I                       | Te                      | Junction<br>emperature<br>Range             | Package     | Media Type | a) MIC25            | 584-JYTS:                                         | Dual-Channel Hot-Swap Controller/<br>Sequencer, 100 mV Fast Circuit<br>Breaker Threshold, Output Latched<br>Off, -40°C to +85°C Temperature<br>Range, RoHS Compliant, 16-Lead<br>TSSOP Package, 94/Tube   |

| Device:<br>Feature:            | Fast Trip<br>J =<br>K = | Sequencer<br>Threshold<br>100 mV<br>150 mV* |             | Controller | b) MIC25            | 584-JYTS-TR:                                      | Dual-Channel Hot-Swap Controller/<br>Sequencer, 100 mV Fast Circuit<br>Breaker Threshold, Output Latched<br>Off, –40°C to +85°C Temperature<br>Range, RoHS Compliant, 16-Lead<br>TSSOP Package, 2500/Reel |

| Junction<br>Temperature Range: | L =<br>M =<br>Y =       | 200 mV*<br>Off*<br>–40°C to +85             | °C, RoHs Co | ompliant   | a) MIC2584-KYTS:    |                                                   | Dual-Channel Hot-Swap Controller/<br>Sequencer, 150 mV Fast Circuit<br>Breaker Threshold, Output Latched<br>Off, -40°C to +85°C Temperature<br>Range, RoHS Compliant, 16-Lead<br>TSSOP Package, 94/Tube   |

| Package:<br>Media Type:        | TS =<br>Blank =<br>TR = | 16-Lead TSS<br>94/Tube<br>2,500/Reel        | OP          |            | b) MIC2584-KYTS-TR: |                                                   | Dual-Channel Hot-Swap Controller/<br>Sequencer, 150 mV Fast Circuit<br>Breaker Threshold, Output Latched<br>Off, –40°C to +85°C Temperature<br>Range, RoHS Compliant, 16-Lead<br>TSSOP Package, 2500/Reel |

| *Contact Sales for ava         | ailability.             |                                             |             |            | Note 1:             | part number de<br>ordering purpo<br>package. Chec | identifier only appears in the catalog<br>escription. This identifier is used for<br>uses and is not printed on the device<br>k with your Microchip Sales Office<br>railability with the Tape and Reel    |

NOTES:

#### Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not

mean that we are guaranteeing the product is "unbreakable" Code protection is constantly evolving. Microchip is committed to

continuously improving the code protection features of our products.

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at https:// www.microchip.com/en-us/support/design-help/client-supportservices.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WAR-RANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDI-RECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSE-QUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### Trademarks

The Microchip name and logo, the Microchip logo, Adaptec, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet- Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, TrueTime, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, Clockstudio, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, GridTime, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, IntelliMOS, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, KoD, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, Trusted Time, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

$\ensuremath{\textcircled{\text{C}}}$  2023, Microchip Technology Incorporated and its subsidiaries.

All Rights Reserved.

ISBN: 978-1-6683-2251-2

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

## **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

China - Beijing Tel: 86-10-8569-7000 China - Chengdu

Tel: 86-28-8665-5511 China - Chongqing Tel: 86-23-8980-9588

China - Dongguan Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

China - Nanjing Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

China - Shanghai Tel: 86-21-3326-8000

China - Shenyang Tel: 86-24-2334-2829

China - Shenzhen Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

**China - Wuhan** Tel: 86-27-5980-5300

China - Xian Tel: 86-29-8833-7252

China - Xiamen Tel: 86-592-2388138 China - Zhuhai

Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631 India - Pune

Tel: 91-20-4121-0141 Japan - Osaka

Tel: 81-6-6152-7160

Japan - Tokyo Tel: 81-3-6880- 3770 Korea - Daegu

Tel: 82-53-744-4301 Korea - Seoul

Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

Singapore Tel: 65-6334-8870

Taiwan - Hsin Chu

Tel: 886-3-577-8366 Taiwan - Kaohsiung Tel: 886-7-213-7830

Taiwan - Taipei Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

siung Israel - Ra'anana Tel: 972-9-744-7705

> **Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

**EUROPE**

Austria - Wels

Tel: 43-7242-2244-39

Tel: 45-4485-5910

Fax: 45-4485-2829

Tel: 358-9-4520-820

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79

Germany - Garching

Tel: 49-2129-3766400

Germany - Heilbronn

Germany - Karlsruhe

Tel: 49-7131-72400

Tel: 49-721-625370

Germany - Munich

Tel: 49-89-627-144-0

Fax: 49-89-627-144-44

Germany - Rosenheim

Tel: 49-8031-354-560

Tel: 49-8931-9700

Germany - Haan

Finland - Espoo

France - Paris

Fax: 43-7242-2244-393

**Denmark - Copenhagen**

Italy - Padova Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7288-4388

Poland - Warsaw Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Gothenberg Tel: 46-31-704-60-40

**Sweden - Stockholm** Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Microchip:

MIC2584-JYTS MIC2584-JYTS-TR