# Keyboard and Embedded Controller for Notebook PC

# **Operating Conditions**

- Operating Voltages: 3.3 V and 1.8 V

- Operating Temperature Range: -40 °C to 85 °C

#### **Low Power Modes**

- Chip is designed to always operate in Lowest Power state during Normal Operation

- Supports all 5 ACPI Power States for PC platforms

- Supports 2 Chip-level Sleep Modes: Light Sleep and Heavy Sleep

- Low Standby Current in Sleep Modes

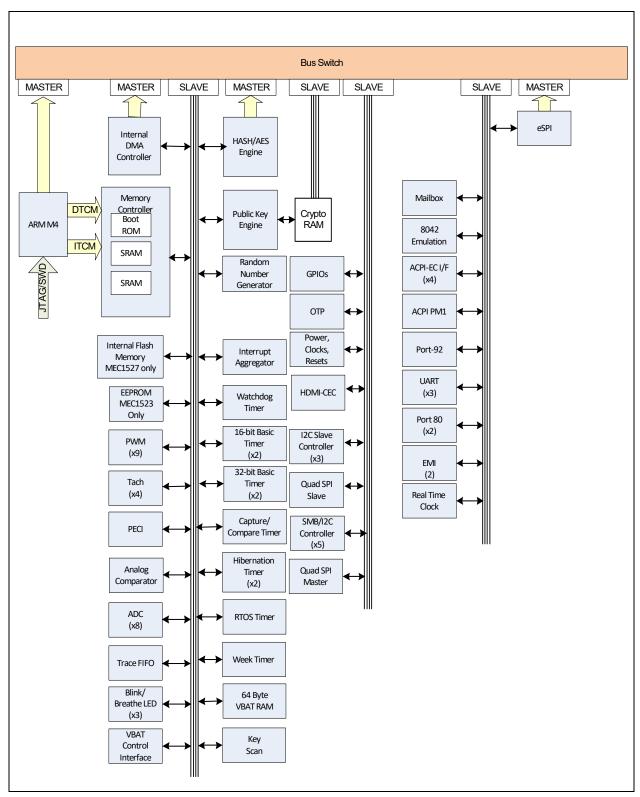

### ARM® Cortex-M4 Embedded Processor

- · Programmable clock frequency up to 48 MHz

- · Fixed point processor

- · Single 4GByte Addressing Space

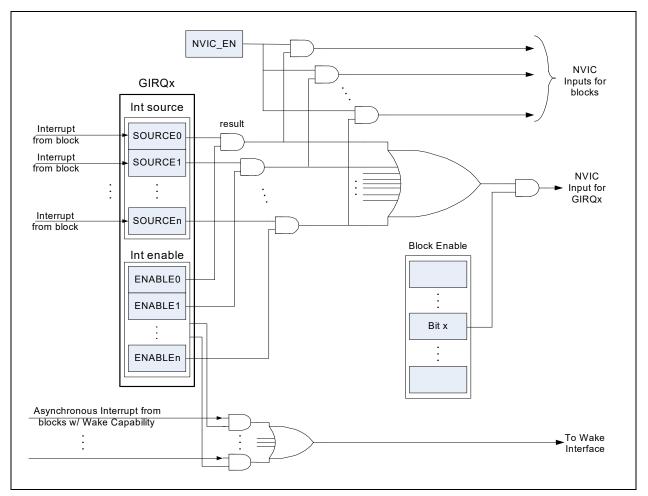

- Nested Vectored Interrupt Controller (NVIC)

- Maskable Interrupt Controller

- Maskable hardware wake up events

- 8 Levels of priority, individually assignable by vector

- EC Interrupt Aggregator expands number of Interrupt sources supported or reduces number of vectors needed

- Complete ARM<sup>®</sup> Standard debug support

- JTAG-Based DAP port, comprised of SWJ-DP and AHB-AP debugger access functions

### **Memory Components**

- 256 KB Code/Data SRAM

- 224 KB optimized for code performance

- 32 KB optimized for data performance

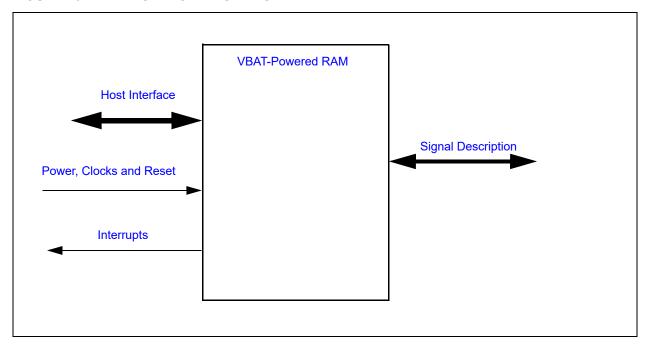

- 64 Bytes Battery Powered Storage SRAM

- 4K bits OTP

- In circuit programmable

- ROM

- Contains Boot ROM

- Contains Runtime APIs for built-in functions

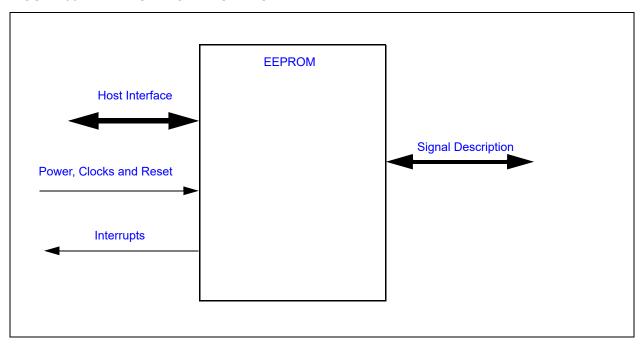

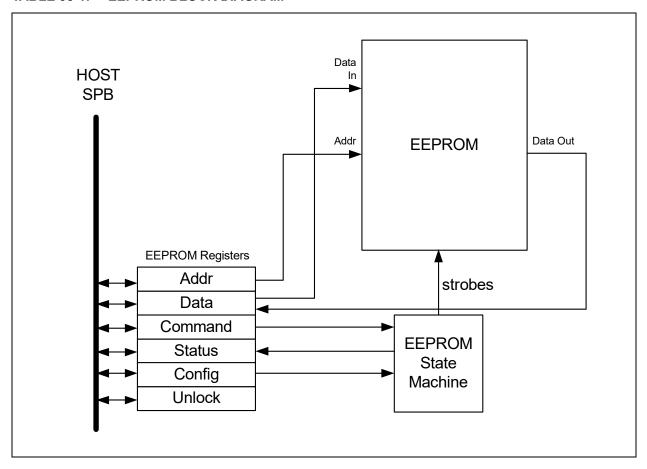

- 2K byte Internal EEPROM (MEC1523 Only)

- 4Mbit in-chip SPI Serial Flash (MEC1527 only)

- SST25PF040C

- SPI Master controller

- Supports Mode 0 and mode 3

- · 24MHz

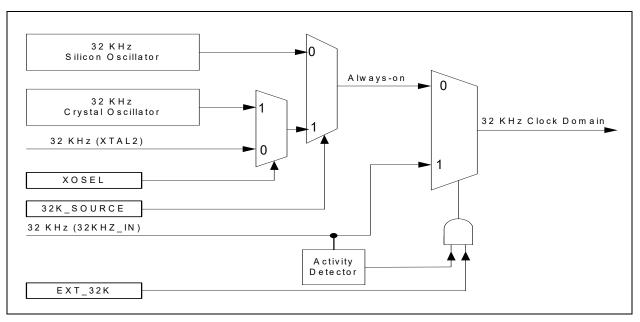

#### Clocks

- 48 MHz Internal PLL

- · 32 kHz Clock Sources

- Internal 32 kHz silicon oscillator

- External 32 kHz crystal (XTAL) source

- External single-ended 32 kHz clock source

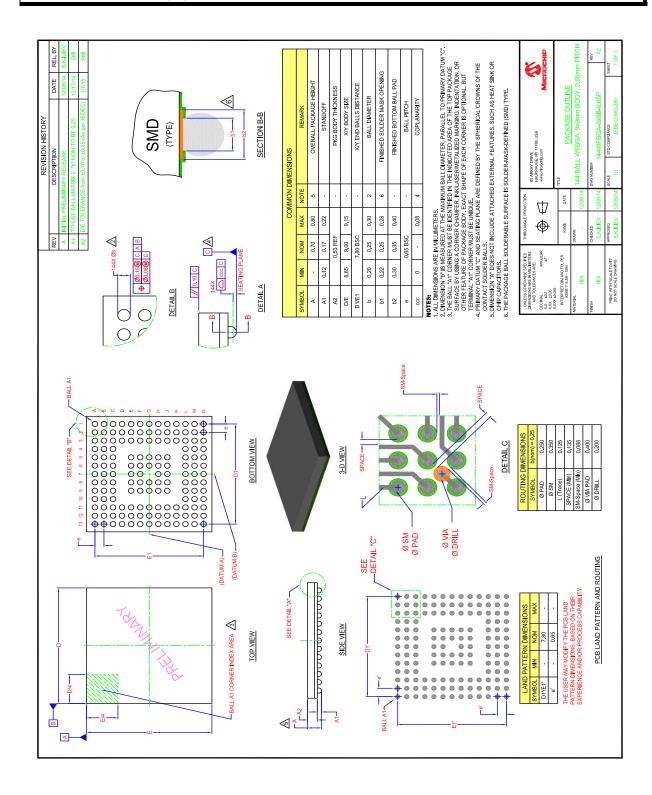

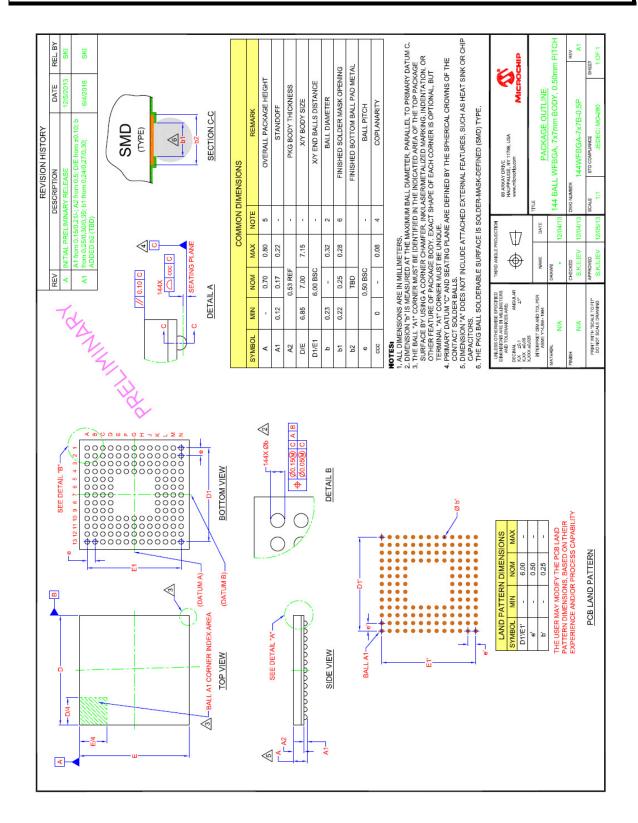

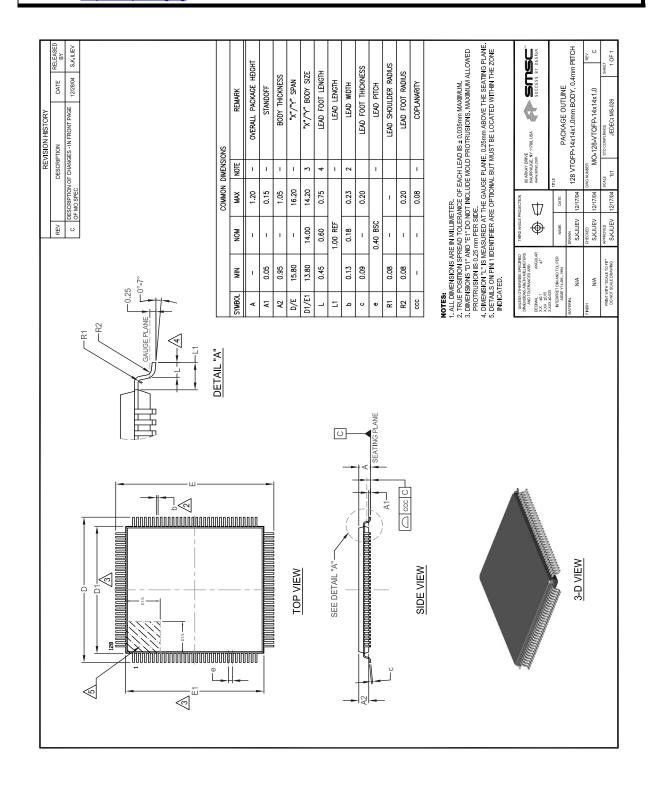

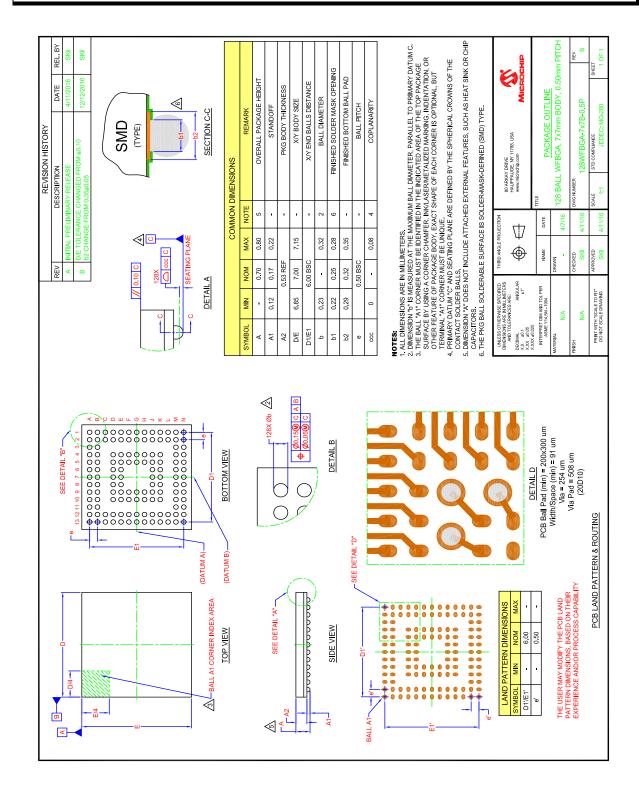

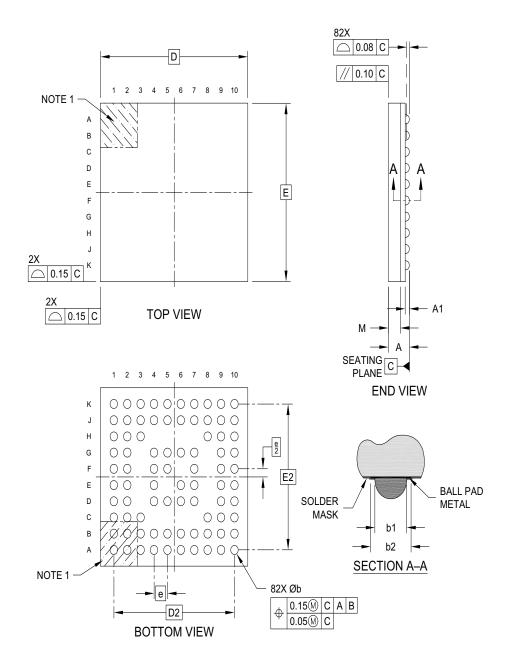

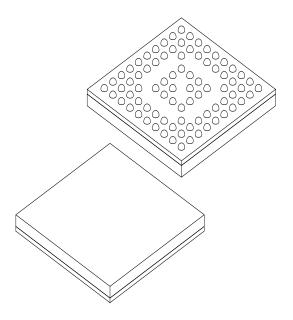

# **Package Options**

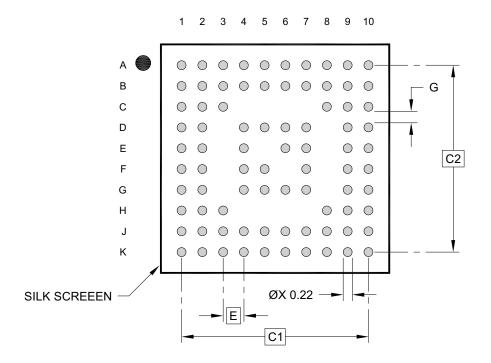

- 144 pin WFBGA

- 128 pin VTQFP

- 128 pin WFBGA

# **Security Features**

- · Boot ROM Secure Boot Loader

- Hardware Root of Trust (RoT) using Secure Boot and Immutable Code using ECDSA p-384 and SHA-384

- Supports 2 Code Images in external SPI Flash (Primary and Fall back image)

- Supports Full EC firmware redundancy over Two Flash components

- Authenticates SPI Flash image before loading

- Support AES-256 Encrypted SPI Flash images

- Key Revocation

- Roll back protection up to 128 Revisions

- · Hardware Accelerators:

- Multi purpose AES Crypto Engine:

- Support for 128-bit 256-bit key length

- Supports Battery Authentication applications

- Digital Signature Algorithm Support

- Support for ECDSA and EC\_KCDSA

- Cryptographic Hash Engine

- Support for SHA-1, SHA-256 to SHA-512

- Public Key Crypto Engine

- Hardware support for RSA and Elliptic Curve asymmetric public key algorithms

- RSA keys length of 1024 to 4096 bits

- ECC Prime Field keys up to 571 bits

- ECC Binary Field keys up to 571 bits

- Microcoded support for standard public key algorithms

- OTP for storing Keys and IDs

- Lockable on 32 B boundaries to prevent read access or write access

- True Random Number Generator

- 1 kbit FIFO

- JTAG Disabled by default

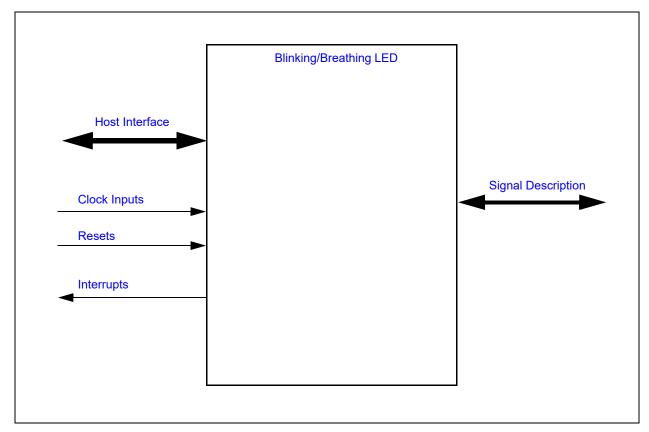

## System Host interface

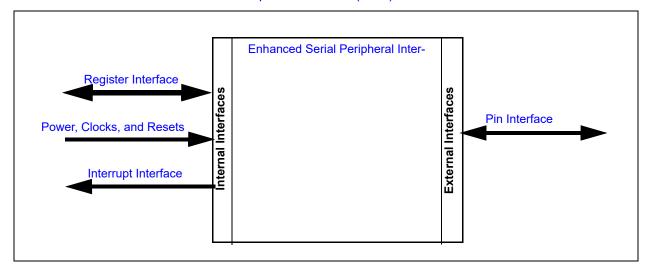

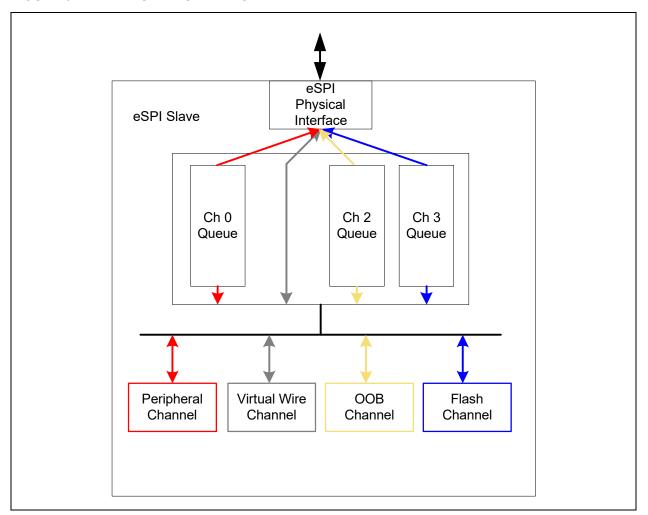

- Enhanced Serial Peripheral Interface (eSPI)

- Intel eSPI Specification compliant

- eSPI Interface Base Spec, Intel Doc. #327432-004, Rev. 1.0.MEC152x

- eSPI Compatibility Spec, Intel Doc. #562633, Rev. 0.6

- Support for Master Attached Flash Sharing (MAFS)

- Support for Slave Attached Flash Sharing (SAFS)

- Supports all four channels:

- Peripheral Channel

- Virtual Wires Channel

- Out-of-Band (OOB) Tunneled Message Channel

- Run-time Flash Access Channel

- Supports EC Bus Master to Host Memory

- Supports up to 66 MHz maximum operating frequency

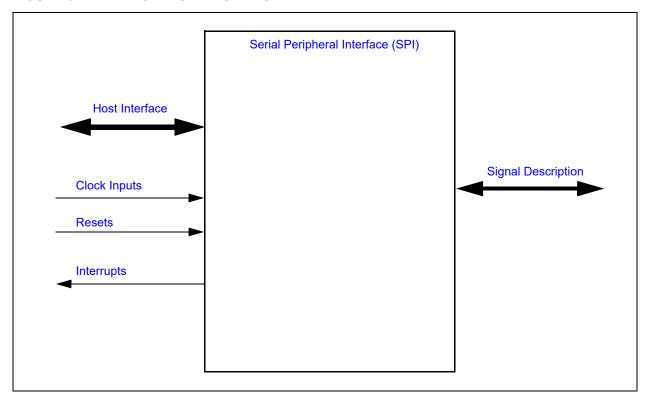

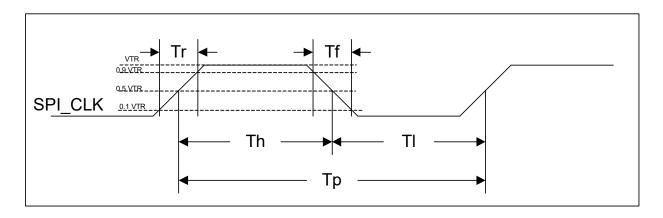

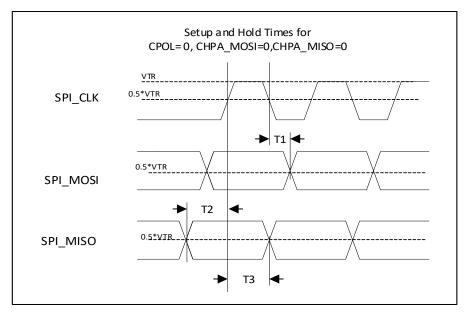

- One Serial Peripheral Interface (SPI) Slave

- Quad SPI (half-duplex) or Single wire (full duplex) support

- Mode 0 and Mode3 operation

- Programmable wait time for response delay

- · System to EC Message Interface

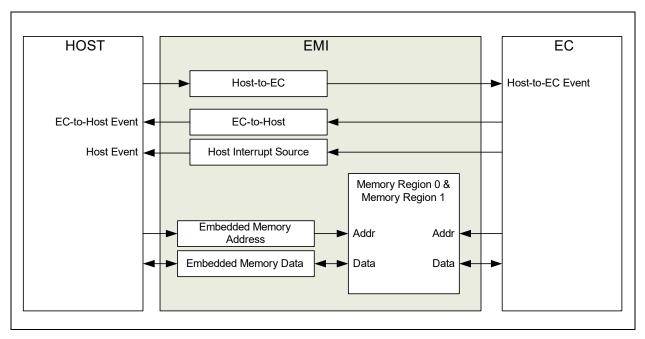

- Two Embedded Memory Interfaces

- Provides Two Windows to On-Chip SRAM for Host Access

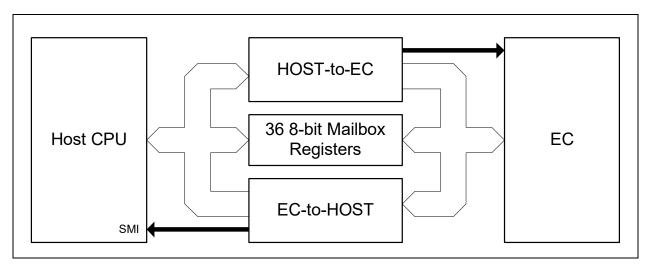

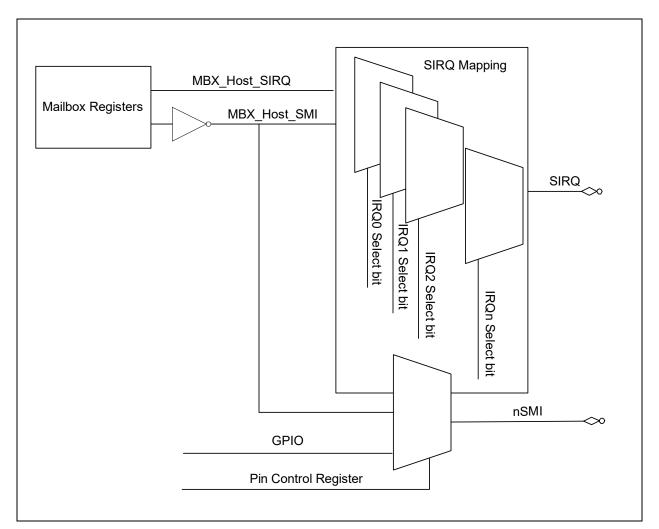

- Two Register Mailbox Command Interface

- Mailbox Registers Interface

- Thirty-two 8-bit registers

- Two Register Mailbox Command Interfaces

- Two Register SMI Source Interfaces

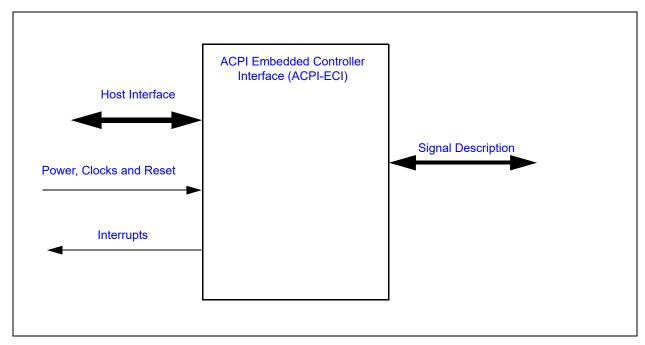

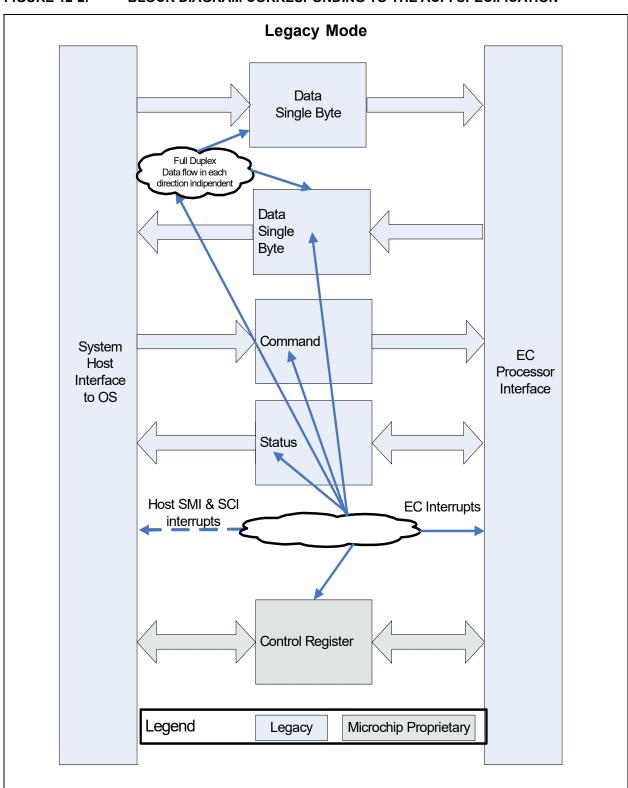

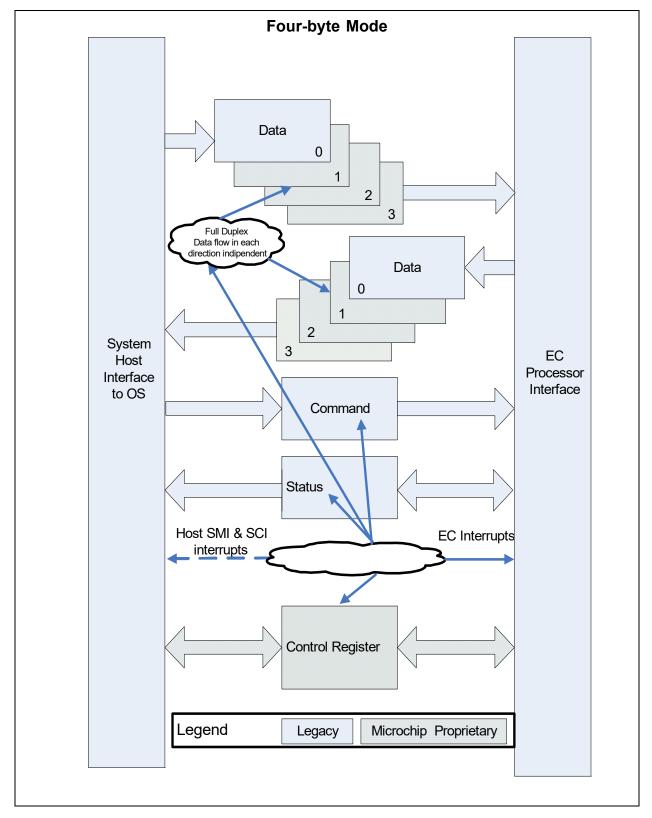

- Five ACPI Embedded Controller Interfaces

- Four EC Interfaces

- One Power Management Interface

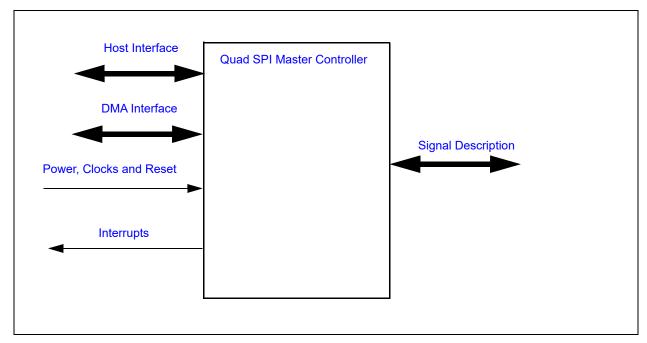

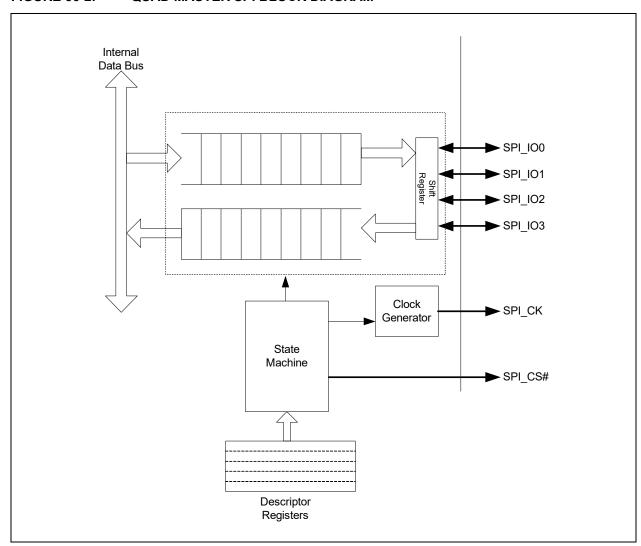

- One Serial Peripheral Interface (SPI) Master Controller

- Dual and Quad I/O Support

- Flexible Clock Rates

- Support for 1.8V and 3.3V slave devices

- SPI Burst Capable

- SPI Controller Operates with Internal DMA Controller with CRC Generation

- Mappable to the following ports (only 1 port active at a time)

- 1 shared SPI Interface

- 1 Private SPI interface

- 1 General Purpose SPI interface

- 1 In-Chip SPI (MEC1527 Only)

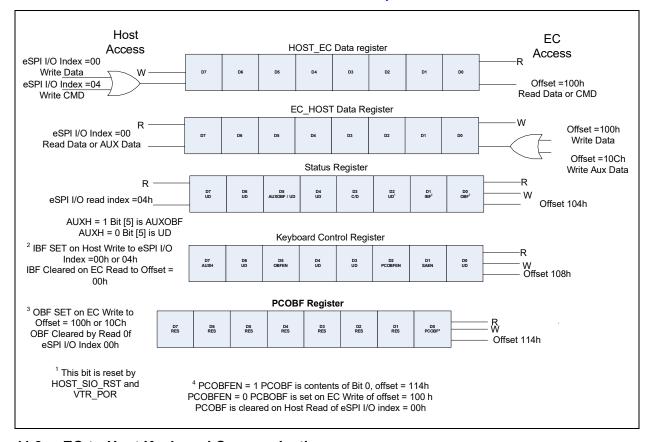

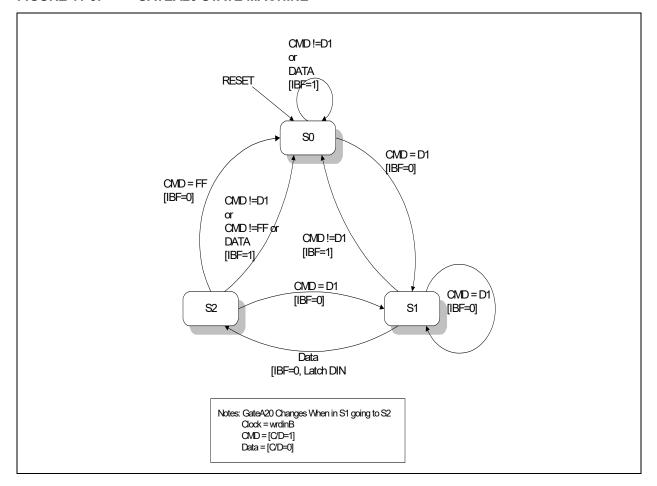

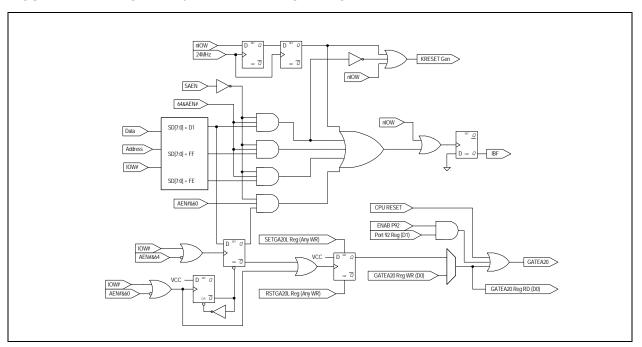

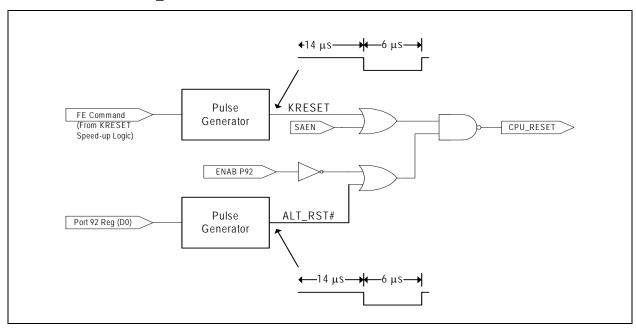

- · 8042 Emulated Keyboard Controller

- 8042 Style Host Interface

- Port 92 Legacy A20M Support

- Fast GATEA20 & Fast CPU\_RESET

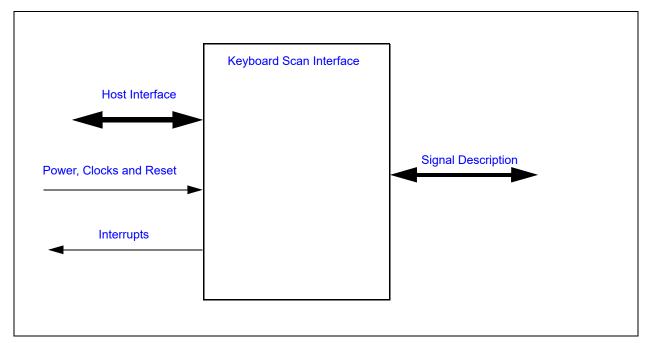

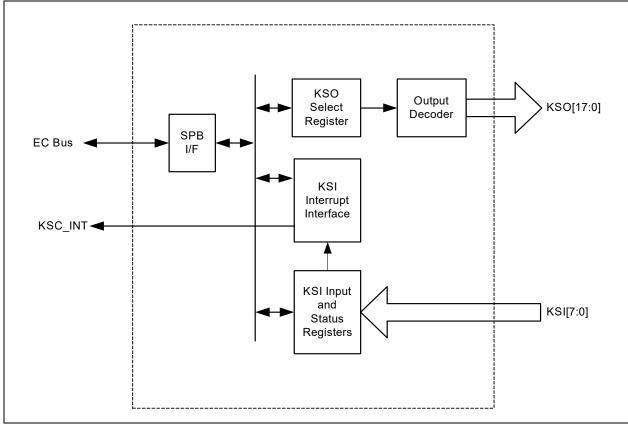

- 18 x 8 Interrupt Capable Multiplexed Keyboard Scan Matrix

- Optional Push-Pull Drive for Fast Signal Switching

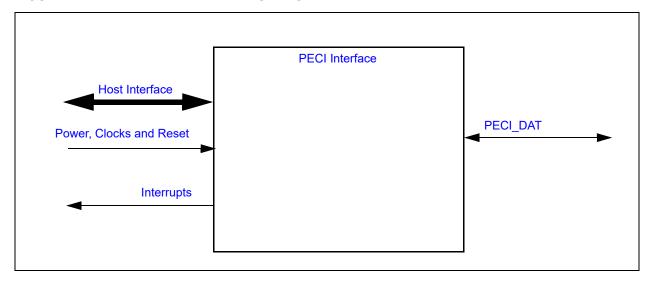

- · PECI Interface 3.1

- Support Intel's low voltage PECI

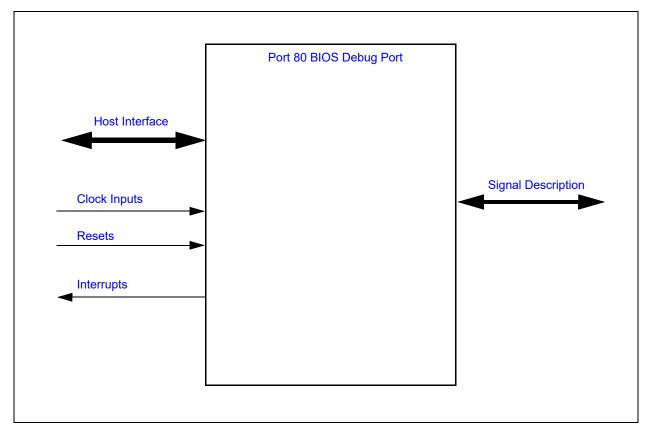

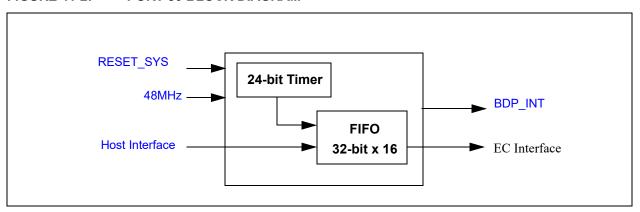

- · Port 80 BIOS Debug Port

- Two Ports, Assignable to Any eSPI IO Address

- 24-bit Timestamp with Adjustable Timebase

- 16-Entry FIFO

# **Peripheral Features**

- · Internal DMA Controller

- Hardware or Firmware Flow Control

- Firmware Initiated Memory-to-Memory transfers

- Hardware CRC-32 Generator on Channel 0

- 12-Hardware DMA Channels support five SMBus Master/Slave Controllers and One SPI Controller

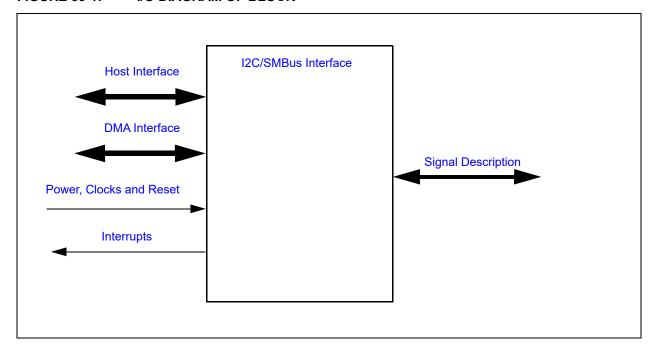

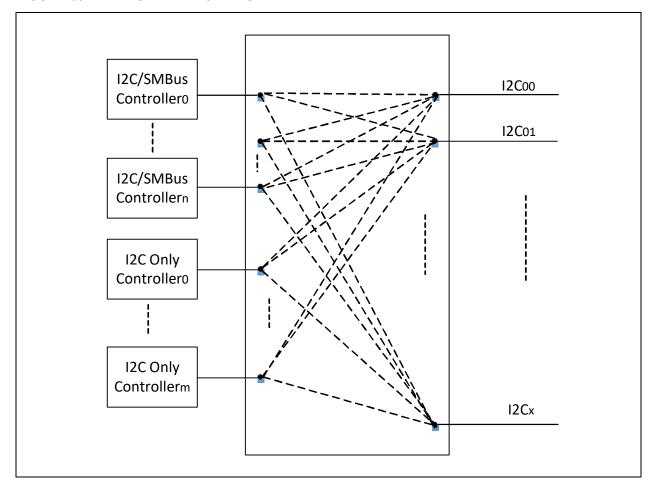

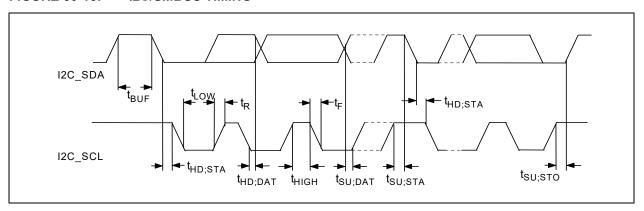

- I2C/SMBus Controllers

- 5 I2C/SMBus controllers

- 3 I2C only controllers without the Network layer

- Up to 16 Configurable I2C ports

- Full Crossbar switch allows any port to be connected to any controller

- Supports Promiscuous mode of operation

- Fully Operational on Standby Power

- Multi-Master Capable

- Supports Clock Stretching

- Programmable Bus Speeds

- 1 MHz Capable

- Supports DMA Network Layer

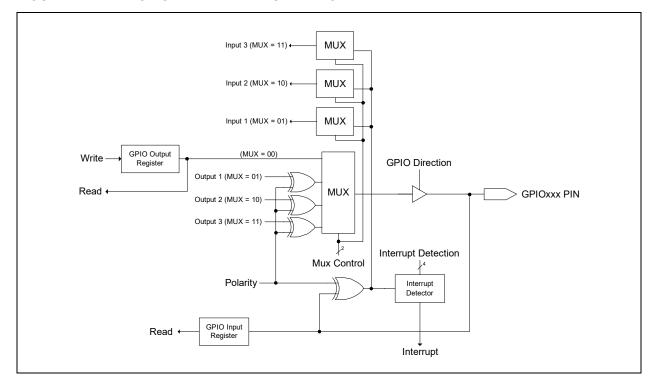

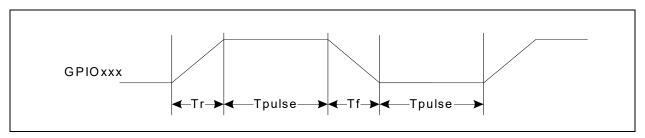

- · General Purpose I/O Pins

- Inputs:

- Asynchronous rising and falling edge wakeup detection Interrupt High or Low Level

- Outputs:

- Push Pull or Open Drain output

- Programmable power well emulation

- Pull up or pull down resistor control

- Automatically disabling pull-up resistors when output driven low

- Automatically disabling pull-down resistors when output driven high

- Programmable drive strength

- Two separate1.8V/3.3V configurable IO regions

- Group or individual control of GPIO data

- Glitch protection and Under-Voltage Protection on all GPIO pins

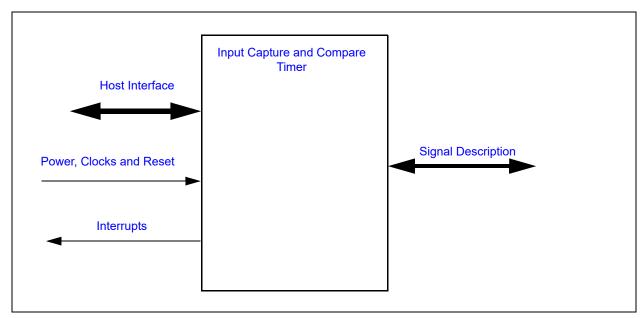

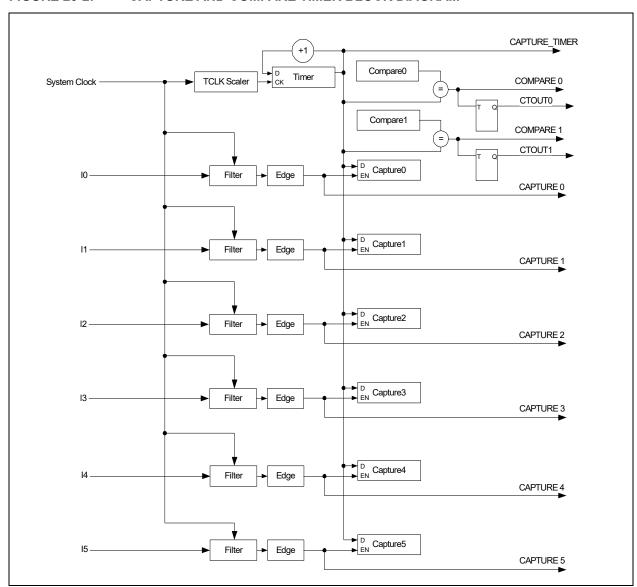

- · Input Capture and Compare timer

- Six 32-bit Capture Registers

- 16Input Pins (ICTx)

- Full Crossbar switch allows any port to be connected to any controller

- 32-bit Free-running timer

- Two 32-bit Compare Registers

- Capture, Compare and Overflow Interrupts

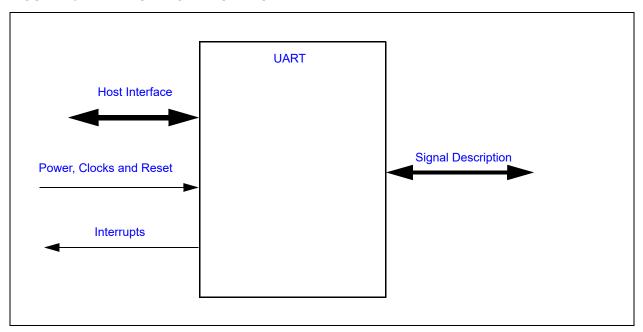

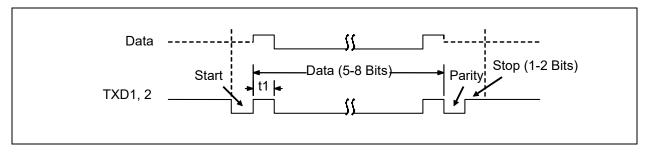

- Universal Asynchronous Receiver Transmitter (UART)

- Three High Speed NS16C550A Compatible UARTs with Send/Receive 16-Byte FIFOs

- UART1 Configurable 2-pin/4-pin/8-pin

- UART2 Configurable 2-pin/4-pin

- UART3 Configurable 2-pin/4-pin/8-pin

- Programmable Main Power or Standby Power Functionality

- Standard Baud Rates to 115.2 Kbps, Custom Baud Rates to 1.5 Mbps

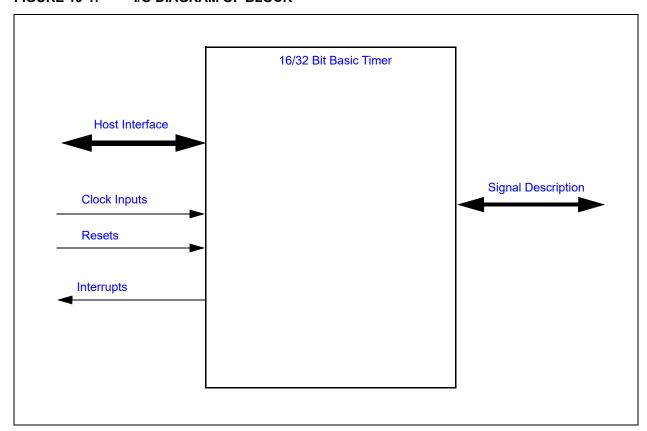

- · Programmable Timer Interface

- Two16-bit Auto-reloading Timer Instances

- 16 bit Pre-Scale divider

- Halt and Reload control

- Auto Reload

- Two 32-bit Auto-reloading Timer Instances

- 16 bit Pre-Scale divider

- Halt and Reload control

- Auto Reload

- Three Operating Modes per Instance: Timer (Reload or Free-Running) or One-shot.

- Event Mode is not supported

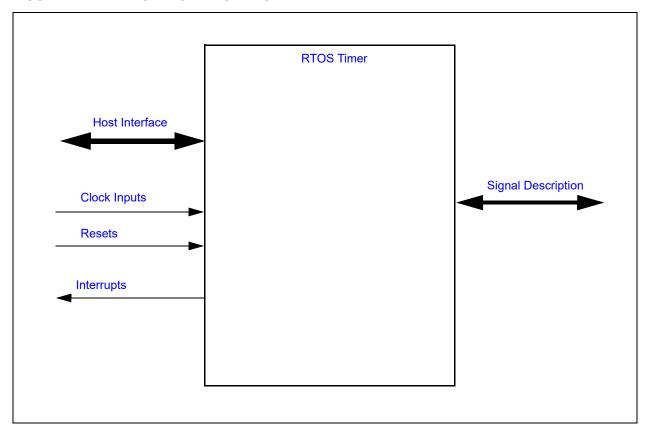

- · 32-bit RTOS Timer

- Runs Off 32kHz Clock Source

- Continues Counting in all the Chip Sleep States regardless of Processor Sleep State

- Counter is Halted when Embedded Controller is Halted (e.g., JTAG debugger active, break points)

- Generates wake-capable interrupt event

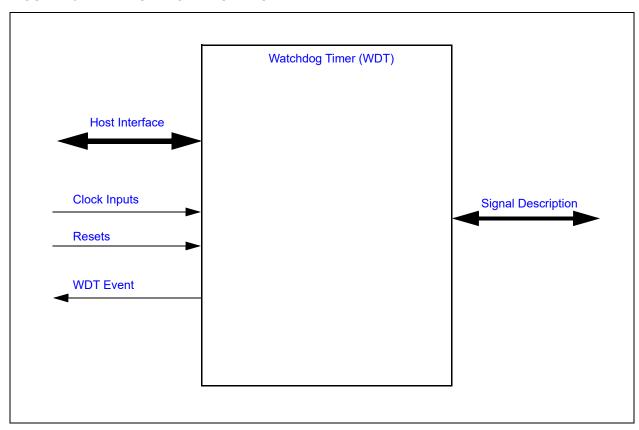

- Watch Dog Timer (WDT)

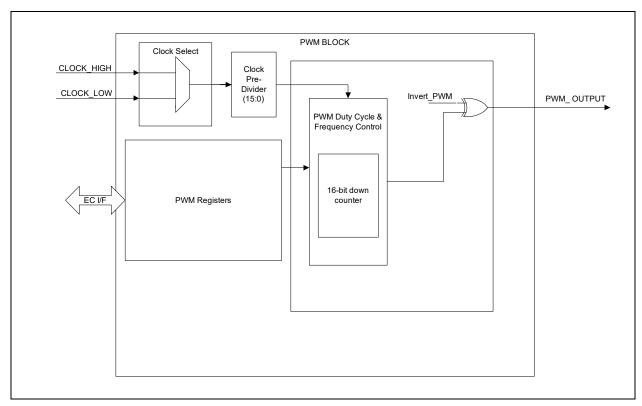

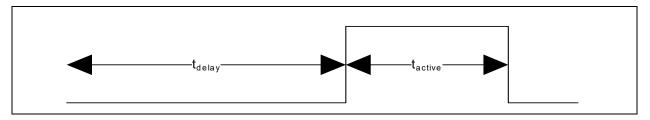

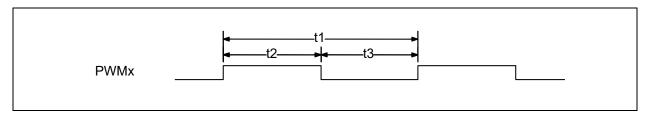

- 9 Programmable Pulse Width Modulator (PWM) outputs

- Multiple Clock Rates

- 16-Bit ON & 16-Bit OFF Counters

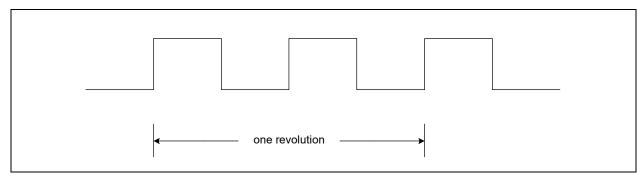

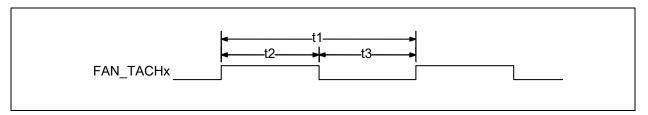

- 4 Fan Tachometer Inputs

- 16 Bit Resolution

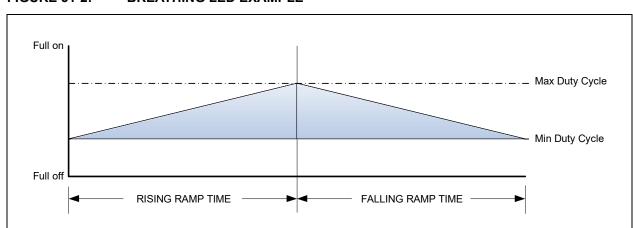

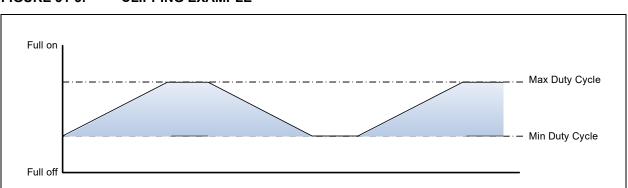

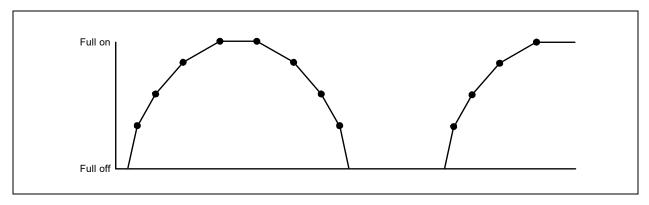

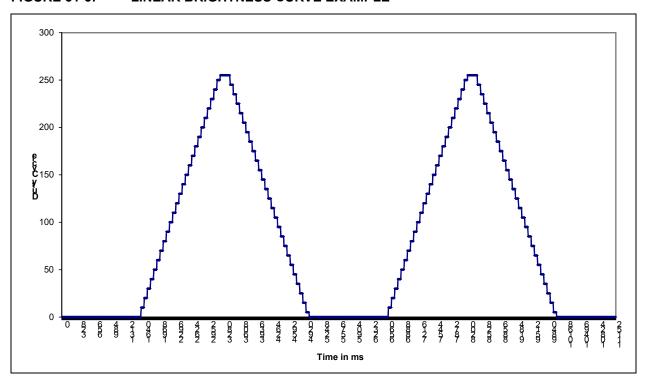

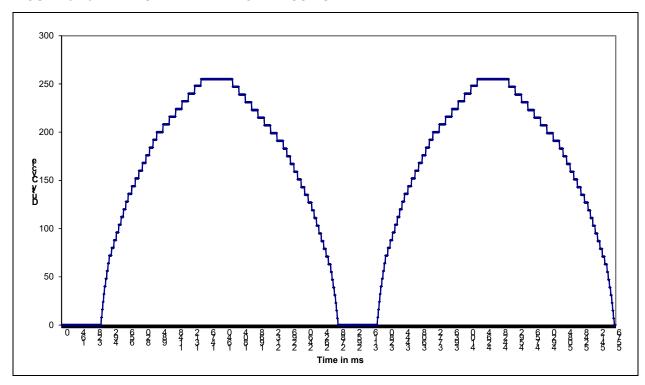

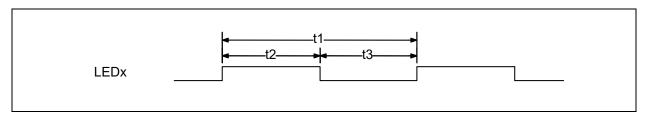

- · Breathing LED Interface

- Three Blinking/Breathing LEDs

- Programmable Blink Rates

- Piecewise Linear Breathing LED Output Controller

- Provides for programmable rise and fall waveforms

- Operational in EC Sleep States

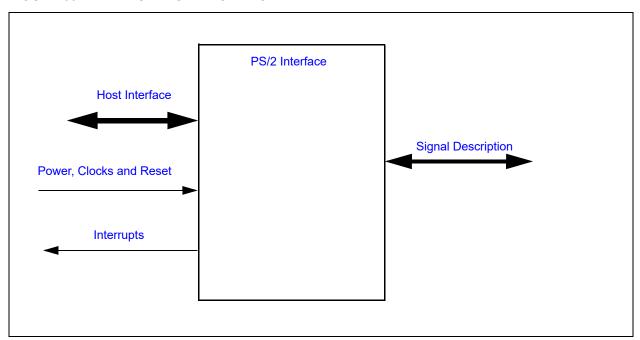

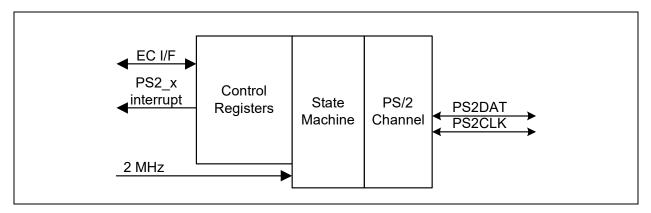

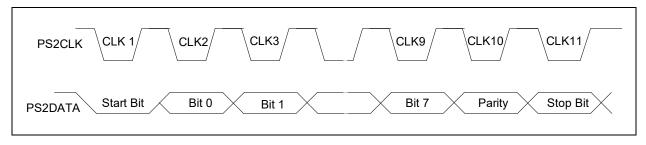

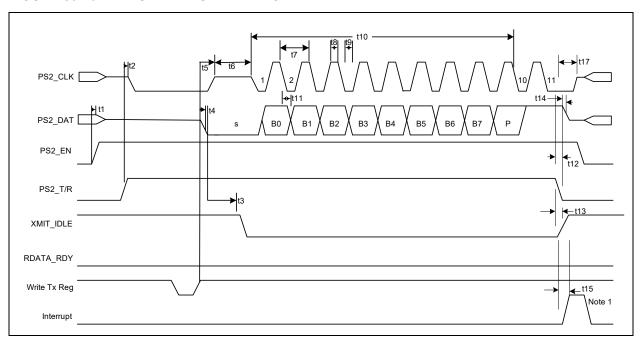

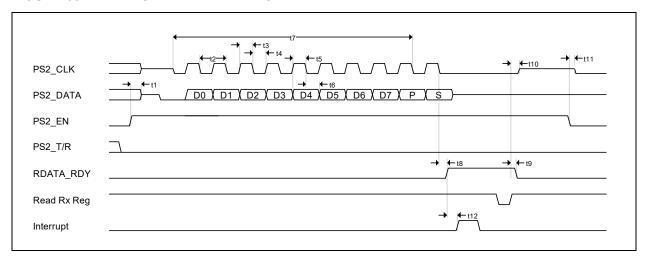

- PS2 Controller

- Two PS2 controllers

- Three PS2 ports

- All three ports are 5 volt tolerant

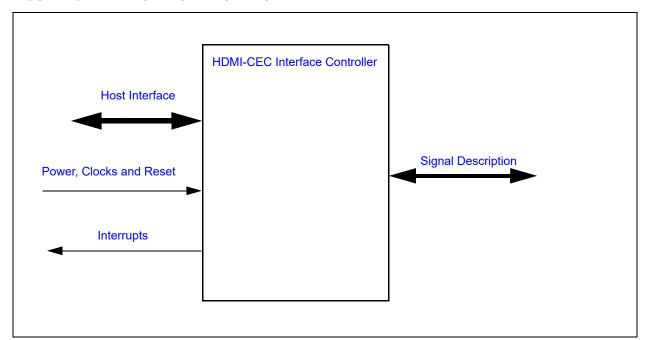

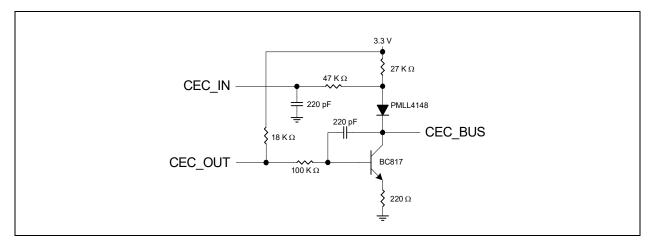

- HDMI-CEC

- One instance of HDMI Consumer Electronics Control (CEC) Bus Controller

- Master/Slave

- Handles signaling and encoding of the CEC data

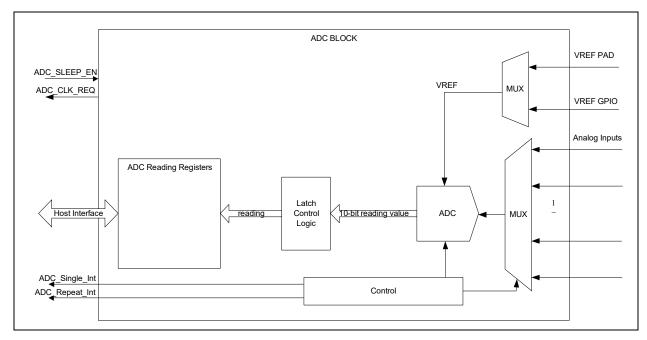

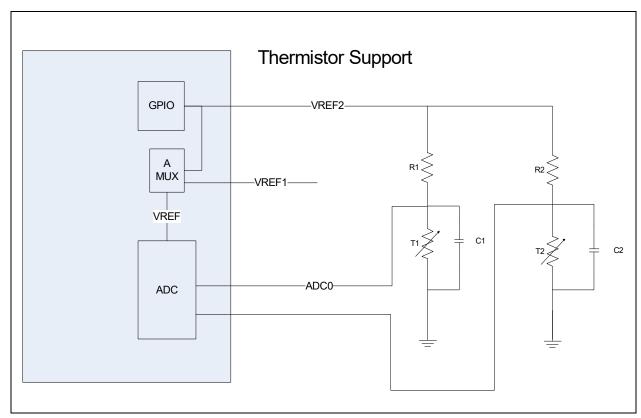

## **Analog Features**

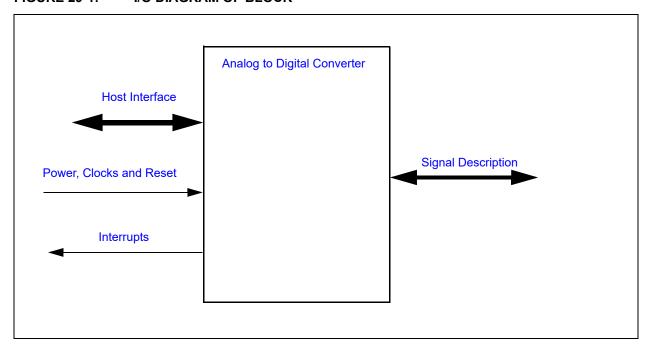

- · ADC Interface

- 10-bit or 12-bit readings supported

- ADC Conversion time 500nS/channel

- 8 Channels

- External voltage reference

- Supports thermistor temperature readings

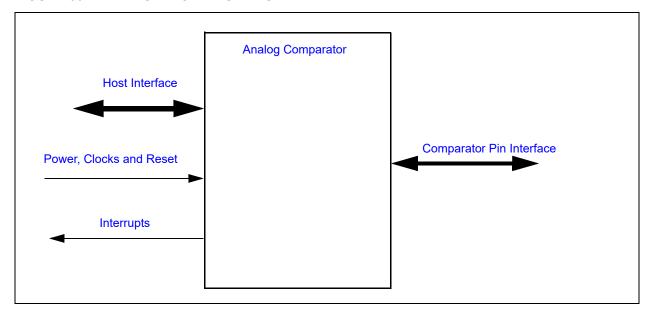

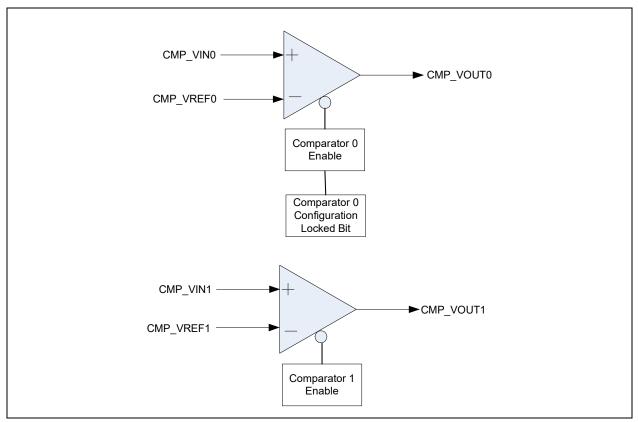

- · Two Analog Comparators

- May be used for Hardware Shutdown

- Detection of voltage limit event

- Detection of Thermistor Over-Temp Event

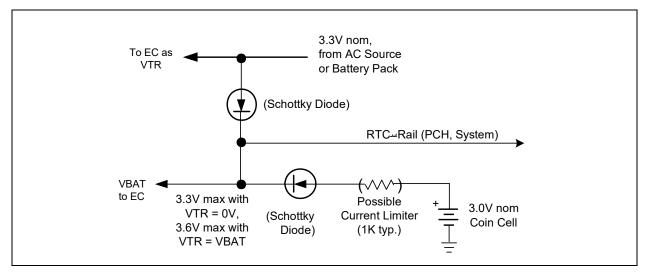

### **Battery Powered Peripherals**

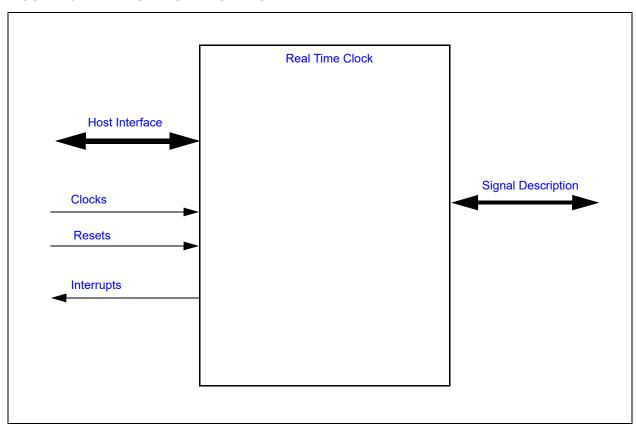

- Real Time Clock (RTC)

- VBAT Powered

- 32KHz Crystal Oscillator or External singleended 32 kHz clock source

- Time-of-Day and Calendar Registers

- Programmable Alarms

- Supports Leap Year and Daylight Savings Time

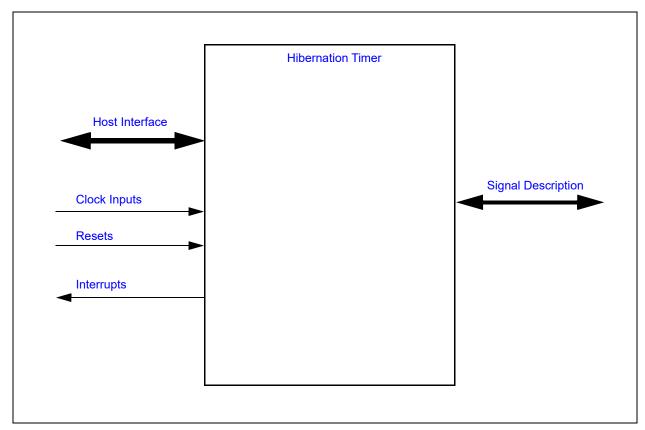

- · Hibernation Timer Interface

- Two 32.768 KHz Driven Timers

- Programmable Wake-up from 0.5ms to 128 Minutes

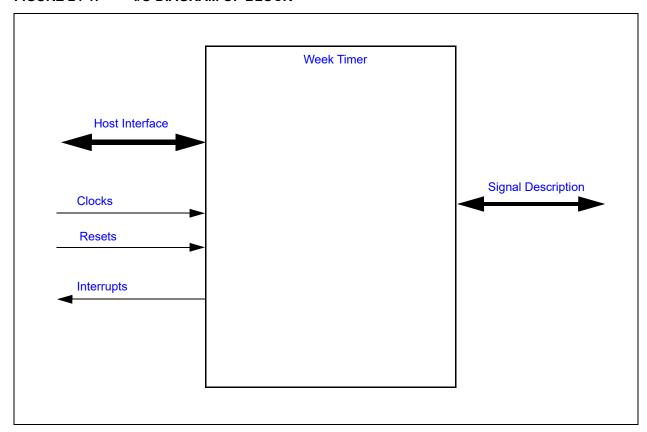

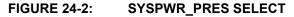

- · Week Timer

- System Power Present Input Pin

- Week Alarm Event only generated when System Power is Available

- Power-up Event

- Week Alarm Interrupt with 1 Second to 8.5 Year Time-out

- Sub-Week Alarm Interrupt with 0.50 Seconds

- 72.67 hours time-out

- 1 Second and Sub-second Interrupts

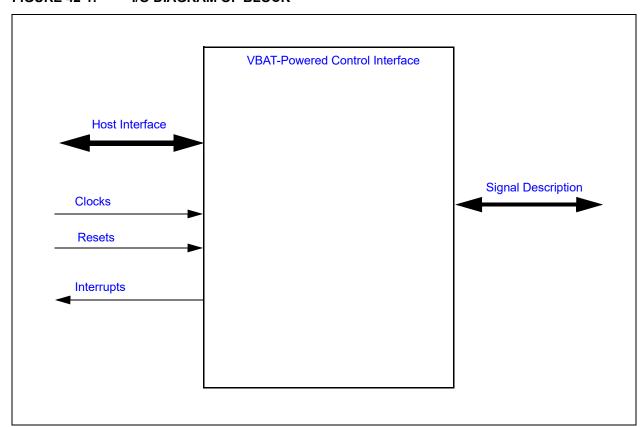

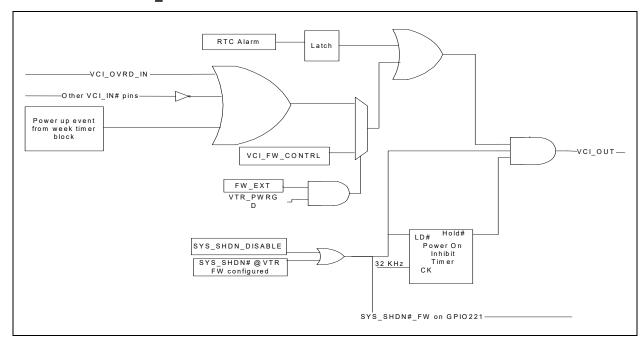

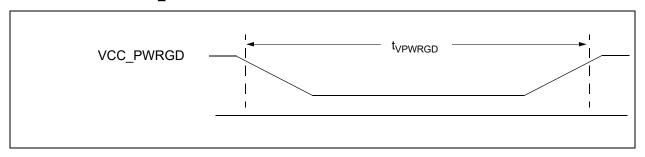

- VBAT-Powered Control Interface (VCI)

- 4 Active-low VCI Inputs

- 1 Active-high VCI Output Pin

- System Power Present Detection for gating RTC wake eventsd

- · Optional filter and latching

- Battery- powered General purpose Output (BGPO)

# **Debug Features**

- 2-pin Serial Wire Debug (SWD) interface

- · 4-Pin JTAG interface for Boundary Scan

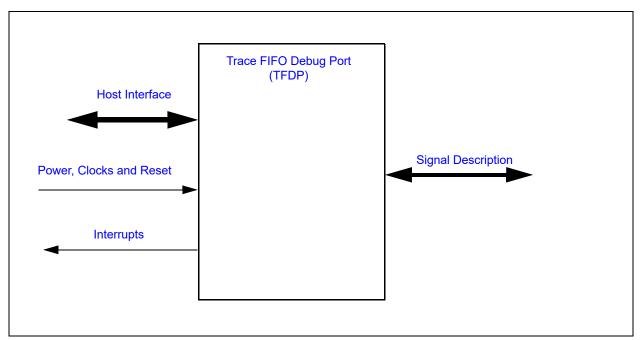

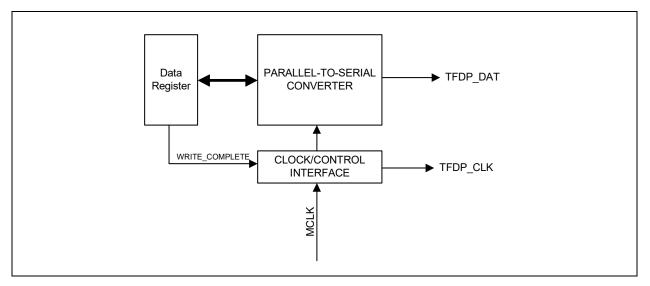

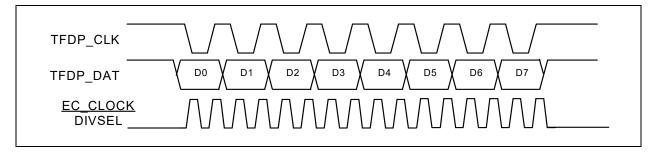

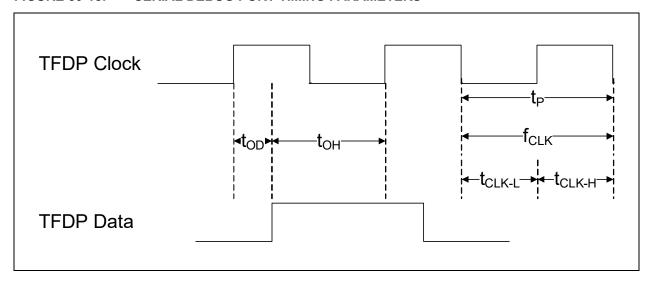

- Trace FIFO Debug Port (TFDP)

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# **Table Of Contents**

| 1.0 General Description                            |     |

|----------------------------------------------------|-----|

| 2.0 Pin Configuration                              | 15  |

| 3.0 Device Inventory                               |     |

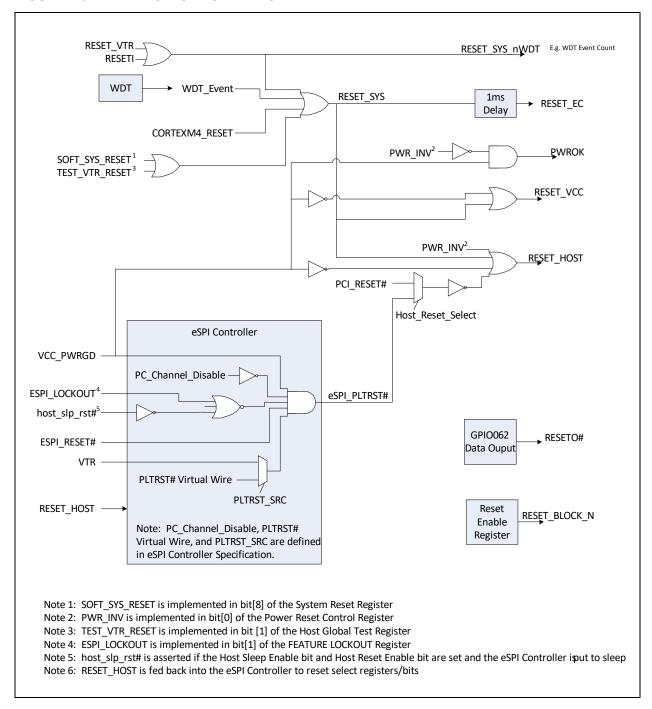

| 4.0 Power, Clocks, and Resets                      |     |

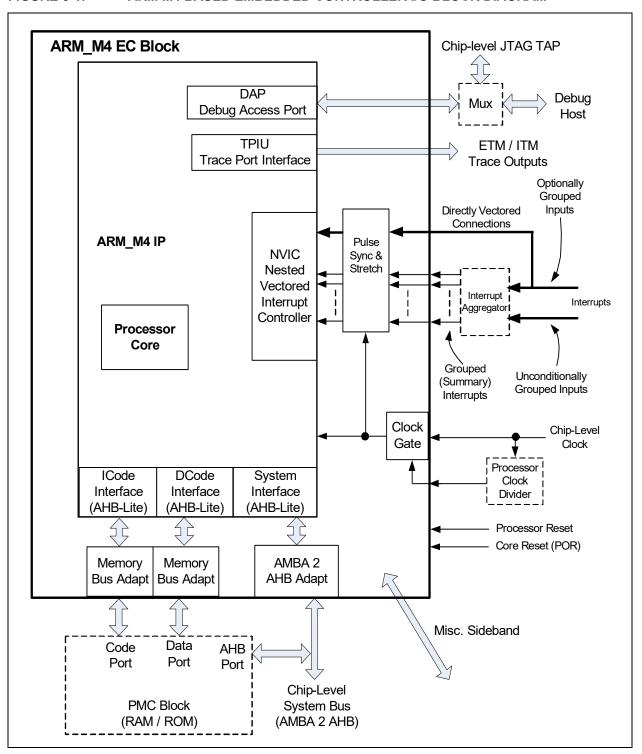

| 5.0 ARM M4 Based Embedded Controller               |     |

| 6.0 RAM and ROM                                    |     |

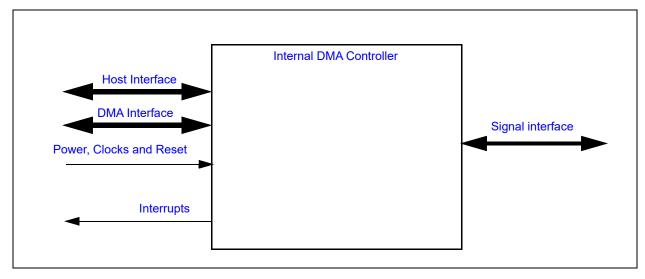

| 7.0 Internal DMA Controller                        | 137 |

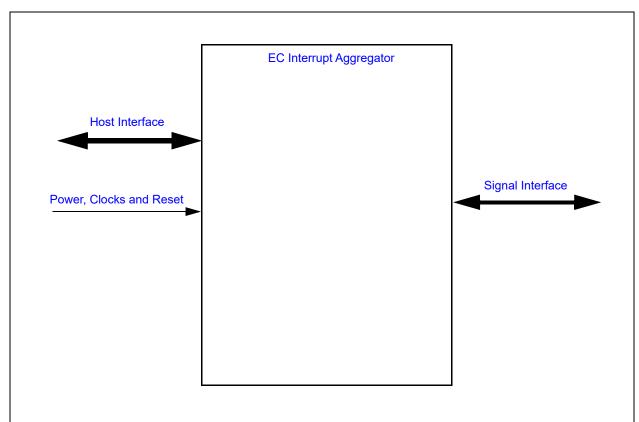

| 8.0 EC Interrupt Aggregator                        |     |

| 9.0 Enhanced Serial Peripheral Interface (eSPI)    |     |

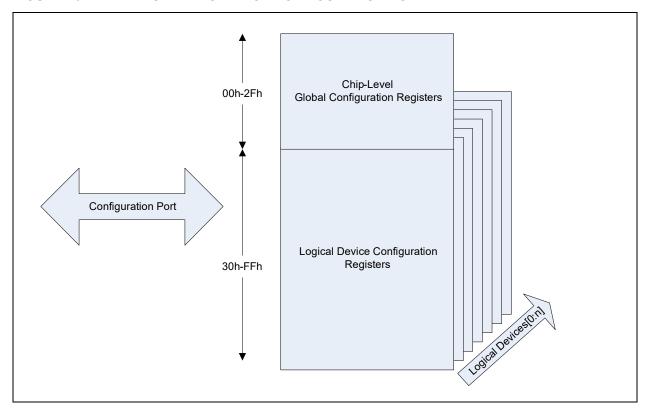

| 10.0 Chip Configuration                            | 174 |

| 11.0 8042 Emulated Keyboard Controller             |     |

| 12.0 ACPI Embedded Controller Interface (ACPI-ECI) | 194 |

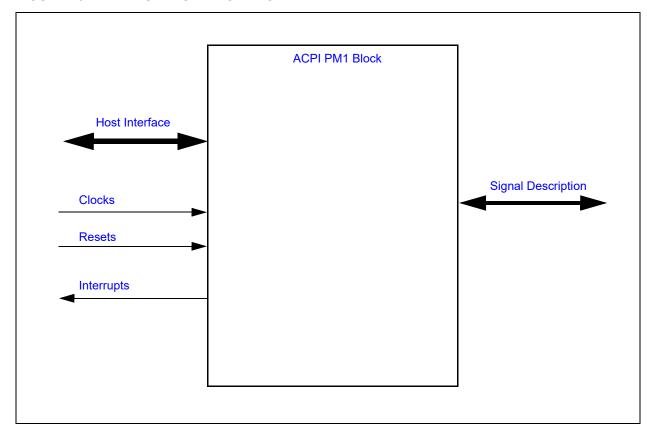

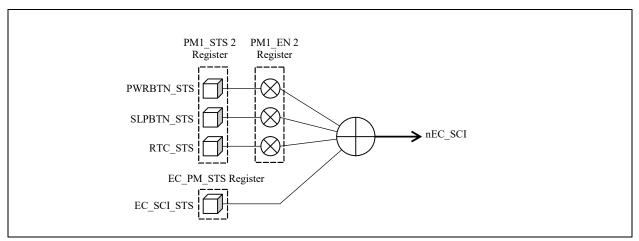

| 13.0 ACPI PM1 Block                                | 211 |

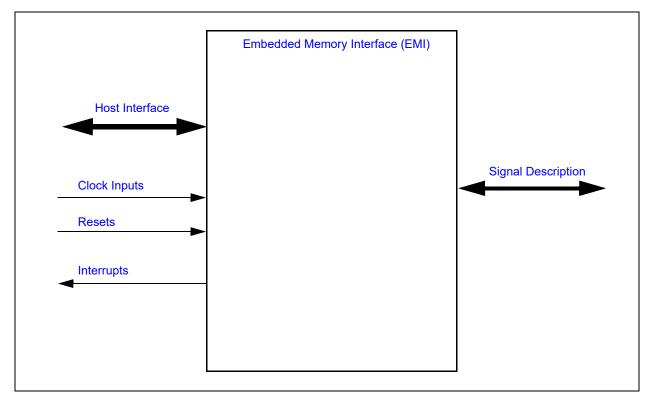

| 14.0 Embedded Memory Interface (EMI)               | 218 |

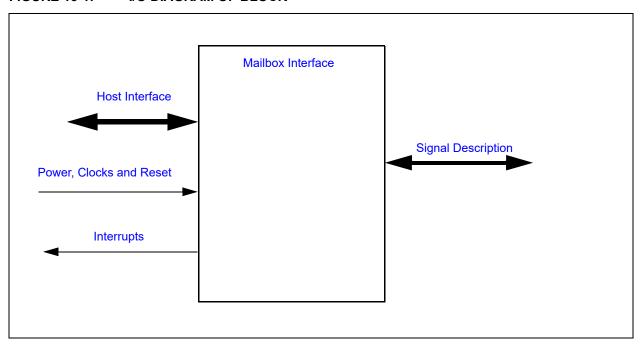

| 15.0 Mailbox Interface                             |     |

| 16.0 UART                                          | 240 |

| 17.0 GPIO Interface                                |     |

| 18.0 Watchdog Timer (WDT)                          |     |

| 19.0 16/32 Bit Basic Timer                         |     |

| 20.0 Input Capture and Compare Timer               |     |

| 21.0 Hibernation Timer                             |     |

| 22.0 RTOS Timer                                    |     |

| 23.0 Real Time Clock                               |     |

| 24.0 Week Timer                                    |     |

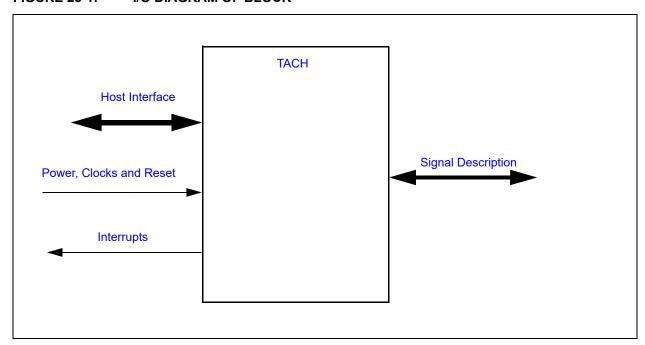

| 25.0 TACH                                          |     |

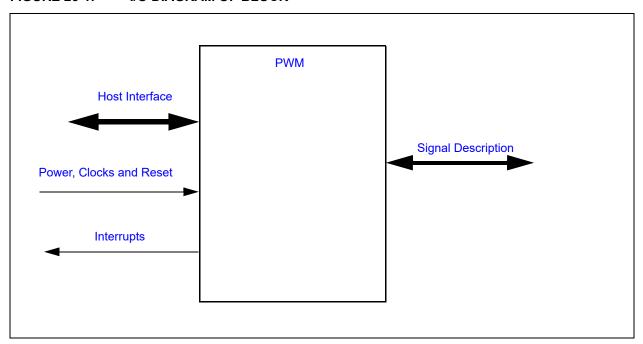

| 26.0 PWM                                           |     |

| 27.0 PECI Interface                                |     |

| 28.0 HDMI-CEC Interface Controller                 |     |

| 29.0 Analog to Digital Converter                   |     |

| 30.0 Analog Comparator                             |     |

| 31.0 Blinking/Breathing LED                        |     |

| 32.0 Keyboard Scan Interface                       |     |

| 33.0 I2C/SMBus Interface                           |     |

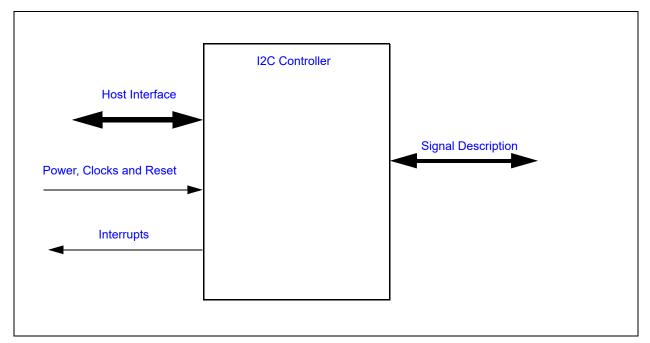

| 34.0 I2C Controller                                |     |

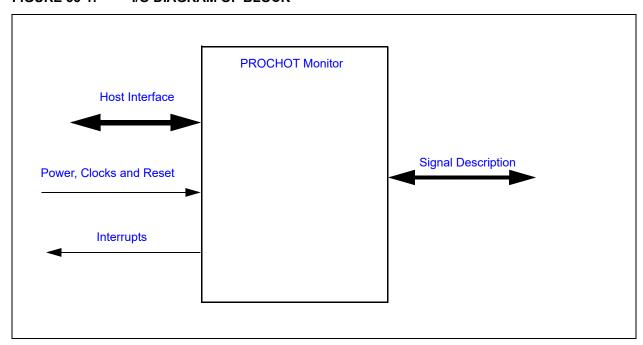

| 35.0 PROCHOT Monitor                               |     |

| 36.0 Quad SPI Master Controller                    |     |

| 37.0 Serial Peripheral Interface (SPI) Slave       |     |

| 38.0 EEPROM                                        |     |

| 39.0 PS/2 Interface                                |     |

| 40.0 Trace FIFO Debug Port (TFDP)                  |     |

| 41.0 Port 80 BIOS Debug Port                       |     |

| 42.0 VBAT-Powered Control Interface                |     |

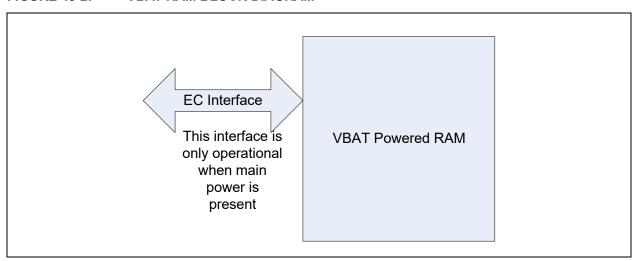

| 43.0 VBAT-Powered RAM                              |     |

| 44.0 VBAT Register Bank                            |     |

| 45.0 EC Subsystem Registers                        |     |

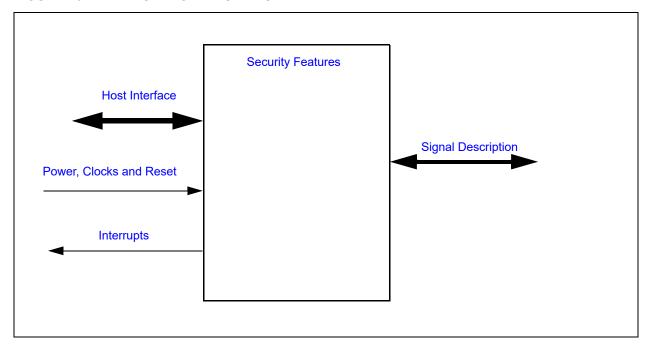

| 46.0 Security Features                             |     |

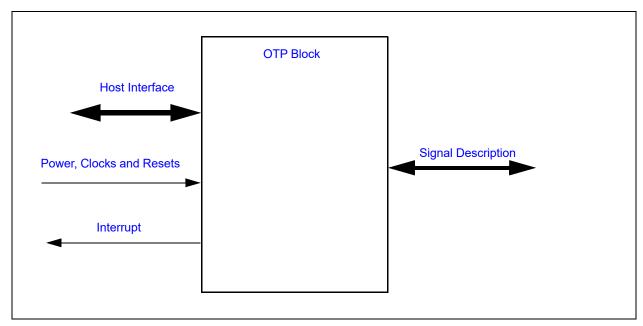

| 47.0 OTP Block                                     |     |

| 48.0 Test Mechanisms                               |     |

| 49.0 Electrical Specifications                     |     |

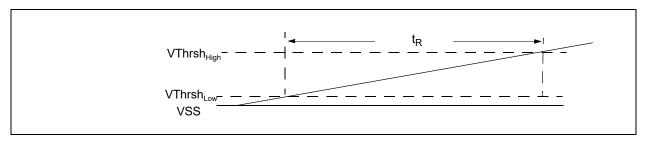

| 50.0 Timing Diagrams                               |     |

| 51.0 Packaging Information                         |     |

| Appendix A: Data Sheet Revision History            |     |

| The Microchip Web Site                             |     |

| Customer Change Notification Service               |     |

| Customer Support                                   |     |

| Product Identification System                      | 573 |

|                                                    |     |

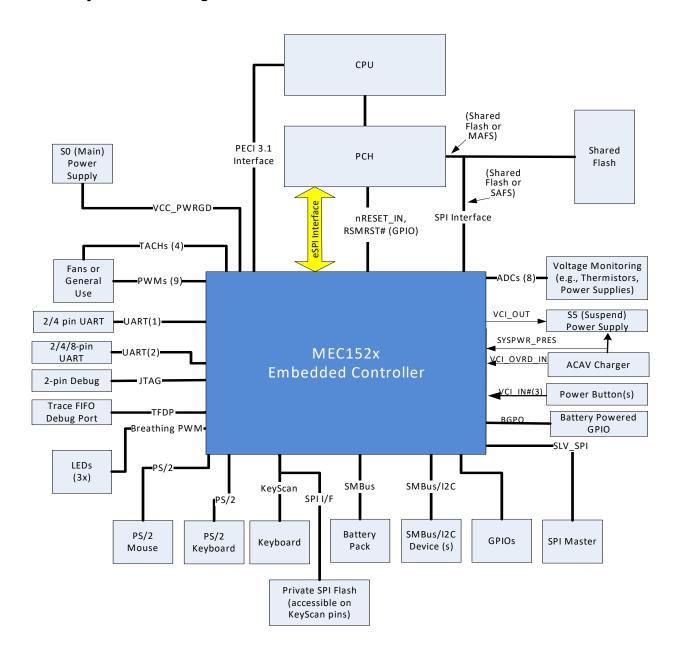

## 1.0 GENERAL DESCRIPTION

The MEC152x is a family of low power integrated embedded controllers designed for notebook applications. The MEC152x is a highly-configurable, mixed-signal, advanced I/O controller architecture. It contains a 32-bit ARM® Cortex-M4 processor core with closely-coupled memory for optimal code execution and data access. An internal ROM, embedded in the design, is used to store the power on/boot sequence and APIs available during run time. When VTR\_CORE is applied to the device, the secure boot loader API is used to download the custom firmware image from the system's shared SPI Flash device, thereby allowing system designers to customize the device's behavior.

The MEC152x device is directly powered by a minimum of two separate suspend supply planes (VBAT and VTR) and senses a third runtime power plane (VCC) to provide "instant on" and system power management functions. The MEC152x has two banks of I/O pins that are able to operate at either 3.3 V or 1.8 V. Operating at 1.8V allows the MEC152x to interface with the latest platform controller hubs and will lower the overall power consumed by the device, Whereas 3.3V allows this device to be integrated into legacy platforms that require 3.3V operation.

The MEC152x host interface is the Intel® Enhanced Serial Peripheral Interface (eSPI). The eSPI Interface is a 1.8V interface that operates in single, double and quad I/O modes. The eSPI Interface supports all four eSPI channels: Peripheral Channel, Virtual Wires Channel, OOB Message Channel, and Run-time Flash Access Channel. The eSPI hardware Flash Access Channel is used by the Boot ROM to support Master Attached Flash Sharing (MAFS). In addition, the MEC152x has specially designed hardware to support Slave Attached Flash Sharing (SAFS). The eSPI SAFS Bridge imposes Region-Based Protection and Locking security feature, which limits access to certain regions of the flash to specific masters. There may be one or more masters (e.g., BIOS, ME, etc) that will access the SAF via the eSPI interface. The ARM® Cortex-M4 processor is also considered a master, which will also have its access limited to EC only regions of SPI Flash as determined by the customer firmware application.

The MEC152x secure boot loader authenticates and optionally decrypts the SPI Flash OEM boot image using the AES-256, ECDSA, SHA-384 cryptographic hardware accelerators. The MEC152x hardware accelerators support 128-bit and 256-bit AES encryption, ECDSA and EC\_KCDSA signing algorithms, 1024-bits to 4096-bits RSA and Elliptic asymmetric public key algorithms, and a True Random Number Generator (TRNG). Runtime APIs are provided in the ROM for customer application code to use the cryptographic hardware. Additionally, the device offers lockable OTP storage for private keys and IDs.

The MEC152x is designed to be incorporated into low power PC architecture designs and supports ACPI sleep states (S0-S5). During normal operation, the hardware always operates in the lowest power state for a given configuration. The chip power management logic offers two low power states: light sleep and heavy sleep. These features can be used to support S0 Connected Standby state and the lower ACPI S3-S5 system sleep states. In connected standby, any eSPI command will wake the device and be processed. When the chip is sleeping, it has many wake events that can be configured to return the device to normal operation. Some examples of supported wake events are PS2 wake events, RTC, Week Alarm, Hibernation Timer, or any GPIO pin.

The MEC152x offers a software development system interface that includes a Trace FIFO Debug port, a host accessible serial debug port with a 16C550A register interface, a Port 80 BIOS Debug Port, and a 2-pin Serial Wire Debug (SWD) interface. Also included is a 4-wire JTAG interface used for Boundary Scan testing.

# 1.1 Family Features

TABLE 1-1: MEC152X FEATURE LIST BY PACKAGE

| Features | MEC1523<br>144<br>WFBGA                           | MEC1521<br>144<br>WFBGA | MEC1527<br>144<br>WFBGA | MEC1521<br>128<br>VTQFP/<br>WFBGA | MEC1527<br>128<br>WFBGA | MEC1521<br>82<br>WFBGA |

|----------|---------------------------------------------------|-------------------------|-------------------------|-----------------------------------|-------------------------|------------------------|

| Package  | MEC1523<br>H-B0-<br>I/SZ,<br>MEC1523<br>H-B0-I/3Y |                         | MEC1527<br>H-B0-I/SZ    |                                   | MEC1521<br>H-B0-I/TF    | MEC1521H-<br>B0-I/2MW  |

TABLE 1-1: MEC152X FEATURE LIST BY PACKAGE (CONTINUED)

|                                                |                         |                         | -                       | FACKAG                            | · ·                     | <del>, ,</del> , , , , , , , , , , , , , , , , , |

|------------------------------------------------|-------------------------|-------------------------|-------------------------|-----------------------------------|-------------------------|--------------------------------------------------|

| Features                                       | MEC1523<br>144<br>WFBGA | MEC1521<br>144<br>WFBGA | MEC1527<br>144<br>WFBGA | MEC1521<br>128<br>VTQFP/<br>WFBGA | MEC1527<br>128<br>WFBGA | MEC1521<br>82<br>WFBGA                           |

| Device ID                                      | 0023_B4<br>xxh          | 0023_34<br>xxh          | 0023_74<br>xxh          | 0023_33<br>xxh                    | 0023_73<br>xxh          | 0023_35xxh                                       |

| Boundary<br>Scan JTAG ID                       | 0223244<br>5h           | 0223244<br>5h           | 0223244<br>5h           | 0223244<br>5h                     | 0223244<br>5h           | 02232445h                                        |

| Total SRAM<br>Options                          | 256KB                   | 256KB                   | 256KB                   | 256KB                             | 256KB                   | 256KB                                            |

| Code/Data<br>Options<br>(Primary Use)          | 224KB/32<br>KB          | 224KB/32<br>KB          | 224KB/32<br>KB          | 224KB/32<br>KB                    | 224KB/32<br>KB          | 224KB/32KB                                       |

| Battery Backed<br>SRAM                         | 64 bytes                | 64 bytes                | 64 bytes                | 64 bytes                          | 64 bytes                | 64 bytes                                         |

| Internal SPI<br>Flash                          | 0                       | 0                       | 512kB                   | 0                                 | 512kB                   | 0                                                |

| EEPROM                                         | 2KB                     | No                      | No                      | No                                | No                      | No                                               |

| eSPI Host<br>Interface                         | Yes                     | Yes                     | Yes                     | Yes                               | Yes                     | Yes                                              |

| eSPI SAF<br>Interface                          | Yes                     | Yes                     | Yes                     | Yes                               | Yes                     | Yes                                              |

| SPI Slave                                      | Yes                     | Yes                     | Yes                     | Yes                               | Yes                     | Yes                                              |

| 8042 Emu-<br>lated Key-<br>board<br>Controller | Yes                     | Yes                     | Yes                     | Yes                               | Yes                     | No                                               |

| Embedded<br>Memory Inter-<br>face (EMI)        | 2                       | 2                       | 2                       | 2                                 | 2                       | 2                                                |

| Mailbox Regis-<br>ter Interface                | 1                       | 1                       | 1                       | 1                                 | 1                       | 1                                                |

| ACPI Embed-<br>ded Memory<br>Controller        | 4                       | 4                       | 4                       | 4                                 | 4                       | 4                                                |

| ACPI PM1<br>Block Interface                    | 1                       | 1                       | 1                       | 1                                 | 1                       | 1                                                |

| Trace FIFO<br>Debug Port                       | Yes                     | Yes                     | Yes                     | Yes                               | Yes                     | Yes                                              |

| Internal DMA<br>Channels                       | 12                      | 12                      | 12                      | 12                                | 12                      | 12                                               |

| 32-bit Basic<br>Timer                          | 2                       | 2                       | 2                       | 2                                 | 2                       | 2                                                |

| 16-bit Basic<br>Timer                          | 2                       | 2                       | 2                       | 2                                 | 2                       | 2                                                |

| Capture Timer<br>Reg                           | 6                       | 6                       | 6                       | 6                                 | 6                       | 6                                                |

| ICT Channels                                   | 16                      | 16                      | 16                      | 13                                | 13                      | 10                                               |

| Compare<br>Timer                               | 2                       | 2                       | 2                       | 2                                 | 2                       | 2                                                |

TABLE 1-1: MEC152X FEATURE LIST BY PACKAGE (CONTINUED)

| IADLE 1-1.                         | 10120102                      | ,                             | <u> </u>                      | PACKAGE (CONTINUED)               |                               |                          |  |

|------------------------------------|-------------------------------|-------------------------------|-------------------------------|-----------------------------------|-------------------------------|--------------------------|--|

| Features                           | MEC1523<br>144<br>WFBGA       | MEC1521<br>144<br>WFBGA       | MEC1527<br>144<br>WFBGA       | MEC1521<br>128<br>VTQFP/<br>WFBGA | MEC1527<br>128<br>WFBGA       | MEC1521<br>82<br>WFBGA   |  |

| Watchdog<br>Timer (WDT)            | 1                             | 1                             | 1                             | 1                                 | 1                             | 1                        |  |

| Hibernation<br>Timer               | 2                             | 2                             | 2                             | 2                                 | 2                             | 2                        |  |

| Week Timer                         | 1                             | 1                             | 1                             | 1                                 | 1                             | 1                        |  |

| Sub Week<br>Timer                  | 1                             | 1                             | 1                             | 1                                 | 1                             | 1                        |  |

| RTC                                | 1                             | 1                             | 1                             | 1                                 | 1                             | 1                        |  |

| RTOS Timer                         | 1                             | 1                             | 1                             | 1                                 | 1                             | 1                        |  |

| Keyboard<br>Matrix Scan<br>Support | Yes                           | Yes                           | Yes                           | Yes                               | Yes                           | No                       |  |

| Port 80 BIOS<br>Debug Port         | 2                             | 2                             | 2                             | 2                                 | 2                             | 2                        |  |

| SMBus 2.0<br>Host Control-<br>lers | 5                             | 5                             | 5                             | 5                                 | 5                             | 5                        |  |

| I2C Host Con-<br>trollers          | 3                             | 3                             | 3                             | 3                                 | 3                             | 3                        |  |

| SMBus/I2C<br>Ports                 | 16                            | 16                            | 16                            | 15                                | 15                            | 9                        |  |

| QMSPI Controller                   | 1 control-<br>ler/<br>3 ports | 1 control-<br>ler/<br>3 ports | 1 control-<br>ler/<br>3 ports | 1 control-<br>ler/<br>2 ports     | 1 control-<br>ler/<br>2 ports | 1 controller/<br>1port   |  |

| GP SPI port                        | Yes - 4<br>pin                | Yes -4 pin                    | Yes -4 pin                    | No                                | No                            | No                       |  |

| PVT SPI port                       | Yes - 4<br>pin                | Yes -4 pin                    | Yes -4 pin                    | Yes - 4<br>pin                    | Yes - 4<br>pin                | No                       |  |

| SHD SPI port                       | Yes - 4<br>pin                | Yes -4 pin                    | Yes -4 pin                    | Yes - 4<br>pin                    | Yes - 4<br>pin                | Yes - 4 pin              |  |

| ADC Channels                       | 8                             | 8                             | 8                             | 8                                 | 8                             | 6                        |  |

| Vref 2 ADC                         | Yes                           | Yes                           | Yes                           | No                                | No                            | No                       |  |

| PWMs                               | 9                             | 9                             | 9                             | 9                                 | 9                             | 9                        |  |

| TACHs                              | 4                             | 4                             | 4                             | 4                                 | 4                             | 4                        |  |

| PECI 3.1 Inter-<br>face            | Yes                           | Yes                           | Yes                           | Yes                               | Yes                           | Yes                      |  |

| PS/2 Device<br>Interface           | 2 control-<br>ler/<br>3 ports | 2 control-<br>ler/<br>3 ports | 2 control-<br>ler/<br>3 ports | 2 control-<br>ler/<br>3 ports     | 2 control-<br>ler/<br>3 ports | 1 controller/<br>2 ports |  |

| Blink-<br>ing/Breathing<br>LED     | 3                             | 3                             | 3                             | 3                                 | 3                             | 1                        |  |

TABLE 1-1: MEC152X FEATURE LIST BY PACKAGE (CONTINUED)

|                                                                            | 201022                                                        | , ., .,                                                       |                                                               | PACKAGE (CONTINUED)                                   |                                                       |                              |  |

|----------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|------------------------------|--|

| Features                                                                   | MEC1523<br>144<br>WFBGA                                       | MEC1521<br>144<br>WFBGA                                       | MEC1527<br>144<br>WFBGA                                       | MEC1521<br>128<br>VTQFP/<br>WFBGA                     | MEC1527<br>128<br>WFBGA                               | MEC1521<br>82<br>WFBGA       |  |

| UARTs                                                                      | 3<br>UART0:                                                   | 3<br>UART0:                                                   | 3<br>UART0:                                                   | 3<br>UART0:                                           | 3<br>UART0:                                           | 3<br>UART0: 2-pin            |  |

|                                                                            | 2/4/8-pin<br>UART1:<br>2/4/8-pin<br>UART2:<br>1/2/4/8-<br>pin | 2/4/8-pin<br>UART1:<br>2/4/8-pin<br>UART2:<br>1/2/4/8-<br>pin | 2/4/8-pin<br>UART1:<br>2/4/8-pin<br>UART2:<br>1/2/4/8-<br>pin | 2/4/8-pin<br>UART1:<br>2/4-pin<br>UART2:<br>2/4/8-pin | 2/4/8-pin<br>UART1:<br>2/4-pin<br>UART2:<br>2/4/8-pin | UART1: 2-pin<br>UART2: 2-pin |  |

| Customer OTP                                                               | 4K bits                                                       | 4K bits                                                       | 4K bits                                                       | 4K bits                                               | 4K bits                                               | 4K bits                      |  |

| Analog Com-<br>parator                                                     | 2                                                             | 2                                                             | 2                                                             | 2                                                     | 2                                                     | 0                            |  |

| HDMI CEC                                                                   | Yes                                                           | Yes                                                           | Yes                                                           | No                                                    | No                                                    | No                           |  |

| JTAG                                                                       | 4pin /2pin                                                    | 4pin /2pin                                                    | 4pin /2pin                                                    | 4pin /2pin                                            | 4pin /2pin                                            | 4pin /2pin                   |  |

| GPIOs                                                                      | 128                                                           | 128                                                           | 128                                                           | 108                                                   | 108                                                   | 66                           |  |

| Over voltage<br>Protected<br>Pads                                          | 17                                                            | 17                                                            | 17                                                            | 15                                                    | 15                                                    | 15                           |  |

| GPTP                                                                       | 3                                                             | 3                                                             | 3                                                             | 3                                                     | 3                                                     | 0                            |  |

| Battery-Pow-<br>ered General<br>Purpose Out-<br>put (BGPO)                 | 3                                                             | 3                                                             | 3                                                             | 1                                                     | 1                                                     | 2                            |  |

| Active Low<br>VBAT-Pow-<br>ered Control<br>Interface<br>(VCI_IN#)          | 4                                                             | 4                                                             | 4                                                             | 3                                                     | 3                                                     | 2                            |  |

| VBAT-Pow-<br>ered Control<br>Interface<br>(VCI_OUT)                        | 1                                                             | 1                                                             | 1                                                             | 1                                                     | 1                                                     | 1                            |  |

| Active High<br>VBAT-Pow-<br>ered Control<br>Interface<br>(VCI_OVRD_I<br>N) | 0                                                             | 1                                                             | 1                                                             | 1                                                     | 1                                                     | 1                            |  |

| 2 pin parallel<br>XTAL oscillator                                          | No                                                            | Yes                                                           | Yes                                                           | Yes                                                   | Yes                                                   | No                           |  |

| Single ended<br>external<br>32KHz clock<br>input                           | Yes                                                           | Yes                                                           | Yes                                                           | Yes                                                   | Yes                                                   | Yes                          |  |

| PROCHOT_IN                                                                 | Yes                                                           | Yes                                                           | Yes                                                           | No                                                    | No                                                    | No                           |  |

| AES Hard-<br>ware Support                                                  | 128-256<br>bit                                                | 128-256<br>bit                                                | 128-256<br>bit                                                | 128-256<br>bit                                        | 128-256<br>bit                                        | 128-256 bit                  |  |

| SHA Hashing<br>Support                                                     | SHA-1 to<br>SHA-512                                           | SHA-1 to<br>SHA-512                                           | SHA-1 to<br>SHA-512                                           | SHA-1 to<br>SHA-512                                   | SHA-1 to<br>SHA-512                                   | SHA-1 to<br>SHA-512          |  |

TABLE 1-1: MEC152X FEATURE LIST BY PACKAGE (CONTINUED)

| IABLE 1-1:                                                      | MEC152X FEATURE LIST BY PACKAGE (CONTINUED) |                                   |                                   |                                   |                                   |                             |  |  |

|-----------------------------------------------------------------|---------------------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------|--|--|

| Features                                                        | MEC1523<br>144<br>WFBGA                     | MEC1521<br>144<br>WFBGA           | MEC1527<br>144<br>WFBGA           | MEC1521<br>128<br>VTQFP/<br>WFBGA | MEC1527<br>128<br>WFBGA           | MEC1521<br>82<br>WFBGA      |  |  |

| Public Key<br>Cryptography<br>Support                           | RSA: 4K<br>bit<br>ECC: 571<br>bits          | RSA: 4K<br>bit<br>ECC: 640<br>bit | RSA: 4K<br>bit<br>ECC: 640<br>bit | RSA: 4K<br>bit<br>ECC: 640<br>bit | RSA: 4K<br>bit<br>ECC: 640<br>bit | RSA: 4K bit<br>ECC: 640 bit |  |  |

| True Random<br>Number Gen-<br>erator (1K bits)                  | Yes                                         | Yes                               | Yes                               | Yes                               | Yes                               | Yes                         |  |  |

| Root of Trust                                                   | Yes                                         | Yes                               | Yes                               | Yes                               | Yes                               | Yes                         |  |  |

| Secure Boot                                                     | Yes                                         | Yes                               | Yes                               | Yes                               | Yes                               | Yes                         |  |  |

| Immutable<br>Code                                               | Yes                                         | Yes                               | Yes                               | Yes                               | Yes                               | Yes                         |  |  |

| Optional OTP S (Note 1)                                         | electable Fe                                | eatures                           |                                   |                                   |                                   |                             |  |  |

| DSW Power<br>OK                                                 | Yes                                         | Yes                               | Yes                               | Yes                               | Yes                               | Yes                         |  |  |

| EEPROM Lock                                                     | Yes                                         | No                                | No                                | No                                | No                                | No                          |  |  |

| Comparator<br>Strap Option                                      | Yes                                         | Yes                               | Yes                               | Yes                               | Yes                               | No                          |  |  |

| QA Testing                                                      | Yes                                         | Yes                               | Yes                               | Yes                               | Yes                               | Yes                         |  |  |

| JTAG Disable                                                    | Yes                                         | Yes                               | Yes                               | Yes                               | Yes                               | Yes                         |  |  |

| Authentication                                                  | Yes                                         | Yes                               | Yes                               | Yes                               | Yes                               | Yes                         |  |  |

| Encrypt ECDH<br>Private Key<br>(Bytes 0-31)                     | Yes                                         | Yes                               | Yes                               | Yes                               | Yes                               | Yes                         |  |  |

| AES Encryp-<br>tion Mandatory                                   | Yes                                         | Yes                               | Yes                               | Yes                               | Yes                               | Yes                         |  |  |

| OTP Write<br>Lock - [0]<br>ECDH Private<br>Key                  | Yes                                         | Yes                               | Yes                               | Yes                               | Yes                               | Yes                         |  |  |

| OTP Write<br>Lock - [4]<br>Authentication<br>Key - Public<br>Qx | Yes                                         | Yes                               | Yes                               | Yes                               | Yes                               | Yes                         |  |  |

| OTP Write<br>Lock - [5]<br>Authentication<br>Key - Public<br>Qy | Yes                                         | Yes                               | Yes                               | Yes                               | Yes                               | Yes                         |  |  |

| OTP Write<br>Lock - [6]<br>ECDH Public<br>Key 2, Public<br>Rx   | Yes                                         | Yes                               | Yes                               | Yes                               | Yes                               | Yes                         |  |  |

TABLE 1-1: MEC152X FEATURE LIST BY PACKAGE (CONTINUED)

| Features                                                      | MEC1523<br>144<br>WFBGA | MEC1521<br>144<br>WFBGA | MEC1527<br>144<br>WFBGA | MEC1521<br>128<br>VTQFP/<br>WFBGA | MEC1527<br>128<br>WFBGA | MEC1521<br>82<br>WFBGA |

|---------------------------------------------------------------|-------------------------|-------------------------|-------------------------|-----------------------------------|-------------------------|------------------------|

| OTP Write<br>Lock - [7]<br>ECDH Public<br>Key 2, Public<br>Ry | Yes                     | Yes                     | Yes                     | Yes                               | Yes                     | Yes                    |

| TAG0 SPI<br>Flash Base<br>Address                             | Yes                     | Yes                     | Yes                     | Yes                               | Yes                     | Yes                    |

Note 1: Please refer to Boot ROM document for below set of optional OTP selectable feature.

# 1.2 Boot ROM

Following the release of the RESET\_EC signal, the processor will start executing code in the Boot ROM. The Boot ROM executes the SPI Flash Loader, which downloads User Code from SPI Flash and stores it in the internal Code RAM. Refer to MEC152x Boot ROM document for further details.

# 1.3 System Block Diagram

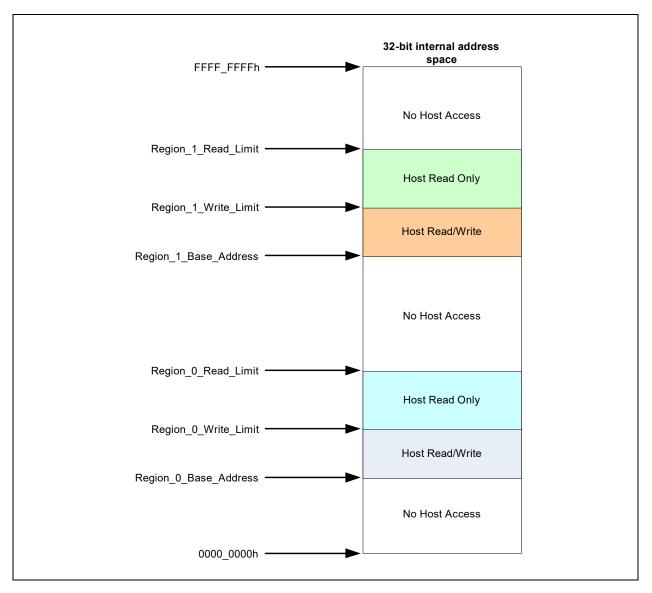

# 1.4 MEC152x Internal Address Spaces

The Internal Embedded Controller can access any register in the EC Address Space or Host Address Space. The eSPI Host Controllers can directly access peripheral registers in the Host Address Space. If the I<sup>2</sup>C interface is used as the Host Interface, access to all the IP Peripherals is dependent on EC firmware.

**Note:** The eSPI Host Controllers also have access to the SRAM data space via the SRAM Memory BAR, which is not illustrated below.

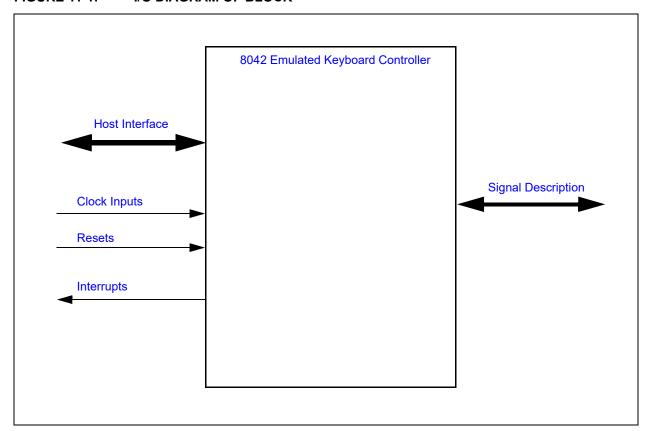

FIGURE 1-1: BLOCK DIAGRAM

## 2.0 PIN CONFIGURATION

# 2.1 Description

The Pin Configuration chapter includes Pin List, Pin Multiplexing.

# 2.2 Terminology and Symbols for Pins/Buffers

### 2.2.1 BUFFER TERMINOLOGY

| Term   | Definition                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| #      | The '#' sign at the end of a signal name indicates an active-low signal                                                                                                                                    |  |  |  |  |  |  |  |

| n      | The lowercase 'n' preceding a signal name indicates an active-low signal                                                                                                                                   |  |  |  |  |  |  |  |

| PWR    | Power                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|        | Programmable as Input, Output, Open Drain Output, Bi-directional or Bi-directional with Open Drain Output. Configurable drive strength from 2ma to12ma.                                                    |  |  |  |  |  |  |  |

| PIO    | <b>Note:</b> All GPIOs have programmable drive strength options of 2ma, 4ma, 8ma and 12ma. GPIO pin drive strength is determined by the Pin Control Register Defaults field in the Pin Control Register 2. |  |  |  |  |  |  |  |

| In     | l Type Input Buffer.                                                                                                                                                                                       |  |  |  |  |  |  |  |

| O2     | O-2 mA Type Buffer.                                                                                                                                                                                        |  |  |  |  |  |  |  |

| PECI   | PECI Input/Output. These pins operate at the processor voltage level (VREF_VTT)                                                                                                                            |  |  |  |  |  |  |  |

| SB-TSI | SB-TSI Input/Output. These pins operate at the processor voltage level (VREF_VTT)                                                                                                                          |  |  |  |  |  |  |  |

#### 2.2.2 PIN NAMING CONVENTIONS

- Pin Name is composed of the multiplexed options separated by '/'. E.g., GPIOxxxx/SignalA/SignalB.

- The first signal shown in a pin name is the default signal. E.g., GPIOxxxx/SignalA/SignalB means the GPIO is the default signal.

- Parenthesis '()' are used to list aliases or alternate functionality for a single mux option. For example, GPIO062(RESETO#) has only a single mux option, GPIO062, but the signal GPIO062 can also be used or interpreted as RESETO#.

- Square brackets '[]' are used to indicate there is a Strap Option on a pin. This is always shown as the last signal on the Pin Name.

- Signal Names appended with a numeric value indicates the Instance Number. E.g., PWM0, PWM1, etc. indicates that PWM0 is the PWM output for PWM Instance 0, PWM1 is the PWM output for PWM Instance 1, etc. The instance number may be omitted if there in only one instance of the IP block implemented.

#### 2.3 Pin List

TABLE 2-1: MEC152X PIN MAP

| MEC1521H-<br>B0-I/2MW | MEC1521H-<br>B0-I/Z2 | MEC1521H-<br>B0-I/TF and<br>MEC1527H-<br>B0-I/TF |    | MEC1523H-<br>B0-I/3Y | MEC1523H-<br>B0-I/SZ | Pin Name                                        |

|-----------------------|----------------------|--------------------------------------------------|----|----------------------|----------------------|-------------------------------------------------|

|                       |                      |                                                  |    |                      |                      |                                                 |

|                       | 128                  | D4                                               | C3 | B2                   | C3                   | SYSPWR_PRES &<br>VCI_IN3#/GPIO000/I2C11_SD<br>A |

|                       | 119                  | F4                                               | A7 | B6                   | B6                   | GPIO062(RESETO#)/I2C11_S<br>CL                  |

| B2                    | 1                    | B2                                               | D3 | D3                   | D3                   | GPIO033/TACH3                                   |

|                       |                      |                                                  | A6 | A5                   | A4                   | GPIO022/GPSPI_IO3                               |

TABLE 2-1: MEC152X PIN MAP (CONTINUED)

| ., .,                 | -1. WILC 132X FIN WAF |                                                  | (OOITTINOL  | , D <sub>1</sub>     |                      |                                                   |

|-----------------------|-----------------------|--------------------------------------------------|-------------|----------------------|----------------------|---------------------------------------------------|

| MEC1521H-<br>B0-I/2MW | MEC1521H-<br>B0-l/Z2  | MEC1521H-<br>B0-I/TF and<br>MEC1527H-<br>B0-I/TF | B0-I/SZ and | MEC1523H-<br>B0-I/3Y | MEC1523H-<br>B0-I/SZ | Pin Name                                          |

|                       |                       |                                                  | C6          | C6                   | C6                   | GPIO023/GPSPI CLK                                 |

|                       |                       |                                                  | A5          | B5                   | B5                   | GPIO024/GPSPI_CS#/I2C07_<br>SCL_ALT               |

| В3                    | 2                     | A1                                               | B2          | B1                   | B2                   | GPIO221/32KHz_OUT/SYS-<br>_SHDN#                  |

| A2                    | 3                     | C2                                               | E3          | C2                   | E3                   | nRESET_IN                                         |

| A1                    | 4                     | B1                                               | A1          | C1                   | A1                   | GPIO057/VCC_P-<br>WRGD/GPSPI_CLK_ALT              |

| C3                    | 5                     | D2                                               | F3          | E3                   | F3                   | GPIO106/PWROK                                     |

|                       | 6                     | C1                                               | C2          | D1                   | C2                   | GPIO226                                           |

| C9                    | 97                    | A10                                              | C12         | B11                  | A13                  | GPIO060/KBRST/TST<br>CLK_OUT/UART1_DCD#           |

| B9                    | 102                   | B9                                               | E9          | D9                   | E9                   | GPIO051/ICT1_TACH1                                |

| B10                   | 103                   | A9                                               | A13         | C10                  | A12                  | GPIO050/ICT0_TACH0                                |

| G1                    | 20                    | J1                                               | J1          | H2                   | J1                   | GPIO200/ADC00/TRACEDAT0                           |

| E1                    | 21                    | J2                                               | G3          | H4                   | G3                   | GPIO201/ADC01/TRACEDAT1                           |

| G2                    | 22                    | K1                                               | K1          | J3                   | K1                   | GPIO202/ADC02/TRACEDAT2                           |

| H2                    | 23                    | K2                                               | J2          | J2                   | J2                   | GPIO203/ADC03/TRACEDAT3                           |

| F1                    | 24                    | J4                                               | H3          | H3                   | H3                   | GPIO204/ADC04                                     |

| H1                    | 25                    | L1                                               | K2          | K1                   | K2                   | GPIO205/ADC05                                     |

|                       | 26                    | L2                                               | L2          | K2                   | L2                   | GPIO206/ADC06                                     |

|                       | 27                    | K4                                               | M2          | L4                   | M2                   | GPIO207/ADC07[CMP_STRA<br>P]                      |

|                       | 30                    | K5                                               | N1          | L3                   | N1                   | GPIO064/PCI_RESET#                                |

|                       |                       |                                                  | H1          | J1                   | H1                   | GPIO067/VREF2_ADC                                 |

| J2                    | 31                    | M2                                               | K3          | L1                   | K3                   | GPIO066/ESPI_CS#/I2C13_S<br>DA                    |

| J1                    | 29                    | M1                                               | J3          | K3                   | J3                   | GPIO061/ESPI_RE-<br>SET#/PWM7_ALT/nEC_SCI_A<br>LT |

| K1                    | 32                    | N1                                               | L3          | M1                   | L3                   | GPIO065/ESPI_CL-<br>KI2C13_SCL/ICT5_ALT           |

| J3                    | 33                    | N2                                               | L4          | N1                   | L4                   | GPIO070/ESPI_IO0/I2C14_SD<br>A                    |

| J4                    | 35                    | M3                                               | N3          | N3                   | N3                   | GPIO071/ESPI_IO1/I2C14_SC<br>L                    |

| K2                    | 36                    | N3                                               | M3          | N2                   | M3                   | GPIO072/ESPI_IO2/I2C01_S-<br>DA_ALT               |

| K3                    | 38                    | M4                                               | L5          | M2                   | L5                   | GPIO073/ESPI_IO3/I2C01_S-<br>CL_ALT               |

|                       |                       |                                                  | M1          | L2                   | M1                   | GPIO100/nEC_SCI_ALT2/ICT 6                        |

| H3                    | 39                    | K6                                               | J6          | L5                   | J6                   | GPIO011/nSMI_ALT/PWM4/IC<br>T7                    |

TABLE 2-1: MEC152X PIN MAP (CONTINUED)

| MEC1521H-<br>B0-I/2MW | MEC1521H-<br>B0-I/Z2 | MEC1521H-<br>B0-I/TF and<br>MEC1527H-<br>B0-I/TF | _   | MEC1523H-<br>B0-I/3Y | MEC1523H-<br>B0-I/SZ | Pin Name                                          |

|-----------------------|----------------------|--------------------------------------------------|-----|----------------------|----------------------|---------------------------------------------------|

| J5                    | 40                   | N4                                               | M4  | M3                   | M4                   | GPIO063/ESPI_ALERT#/PWM<br>6_ALT/ICT8             |

|                       |                      |                                                  | J8  | K8                   | J8                   | GPIO222/PROCHOT_IN#                               |

| K4                    | 41                   | N5                                               | N4  | N4                   | N4                   | GPIO224/GPTP_IN0/SHD_IO1                          |

| K5                    | 42                   | N6                                               | M5  | M4                   | M5                   | GPIO016/GPT-<br>P_IN1/SHD_IO3/ICT3(DSW_P<br>WROK) |

| J6                    | 43                   | M5                                               | L6  | M5                   | L6                   | GPIO227/SHD_IO2[PWRG-<br>D_STRAP]                 |

| K6                    | 44                   | N7                                               | N5  | N5                   | N5                   | GPIO223/SHD_IO0                                   |

| J7                    | 45                   | M6                                               | N6  | N7                   | N6                   | GPIO055(RSMRST#)/PWM2/S<br>HD_CS0#[BSS_STRAP]     |

| K7                    | 46                   | M7                                               | M6  | N6                   | M6                   | GPIO056/PWM3/SHD_CLK                              |

| K9                    | 47                   | K7                                               | N2  | M6                   | N2                   | GPIO012/I2C07_SDA/SLV_SP<br>I_IO2                 |

| H8                    | 48                   | K8                                               | J7  | L6                   | J7                   | GPIO013/I2C07_SCL/SLV_SPI<br>_IO3                 |

| K8                    | 50                   | K9                                               | N7  | K6                   | N7                   | GPIO130/I2C01_SDA/SLV_SP<br>I_IO0                 |

| K10                   | 51                   | H10                                              | M7  | M7                   | M7                   | GPIO131/I2C01_SCL/SLV_SPI<br>_CS#                 |

|                       | 57                   | N10                                              | L9  | M9                   | L9                   | GPIO020/KSI1                                      |

|                       | 58                   | M10                                              | J9  | L8                   | J9                   | GPIO021/KSI2                                      |

| J10                   | 52                   | K10                                              | N8  | K7                   | N8                   | GPIO052/ICT2_TACH2                                |

| J8                    | 53                   | N8                                               | L7  | N10                  | L7                   | GPIO002/PWM5/SHD_CS1#                             |

| J9                    | 54                   | M8                                               | M8  | M8                   | M8                   | GPIO014/PWM6/SLV_SPI_IO2<br>/GPTP_IN2             |

| H9                    |                      |                                                  | M9  | N9                   | M9                   | GPIO015/PWM7/ICT10                                |

|                       | 59                   | M11                                              | N10 | M10                  | N10                  | GPIO151/ICT4/KSO15                                |

|                       | 16                   | G4                                               | L1  | G2                   | L1                   | GPIO152/KSO14/I2C07_S-<br>DA_ALT                  |

|                       | 60                   | N11                                              | N11 | M12                  | N11                  | GPIO017/KSI0/UART0_DCD#                           |

|                       | 61                   | M12                                              | M10 | M11                  | M10                  | GPIO040/GPT-<br>P_OUT2/KSO00/UART1_CTS<br>#       |

|                       | 62                   | N12                                              | N12 | N13                  | N12                  | GPIO032/KSI7/GPT-<br>P_OUT0/UART0_RI#             |

|                       | 63                   | M13                                              | L10 | N11                  | L10                  | GPIO031/KSI6/GPTP_OUT1                            |

|                       | 98                   | D10                                              | B12 | B12                  | C11                  | GPIO132/I2C06_SDA/KSO16                           |

|                       | 99                   | B10                                              | C13 | C11                  | B13                  | GPIO140/I2C06_SCL/ICT5/KS<br>O17                  |

|                       | 72                   | H12                                              | L13 | K11                  | J13                  | GPIO115/PS2_DAT0A                                 |

|                       |                      |                                                  | D2  | D4                   | D2                   | GPIO025/nEMI_INT/UART<br>CLK/UART1_RI#            |

|                       | 64                   | N13                                              | N13 | L11                  | M12                  | GPIO026/KSI3/UART0_DTR#/I<br>2C12_SDA             |

TABLE 2-1: MEC152X PIN MAP (CONTINUED)

| IADLL 2-1.            | WIEG 132X FIN WAF    |                                                  | (OONTHIOL | , D <sub>1</sub>     |                      |                                          |

|-----------------------|----------------------|--------------------------------------------------|-----------|----------------------|----------------------|------------------------------------------|

| MEC1521H-<br>B0-I/2MW | MEC1521H-<br>B0-I/Z2 | MEC1521H-<br>B0-I/TF and<br>MEC1527H-<br>B0-I/TF |           | MEC1523H-<br>B0-I/3Y | MEC1523H-<br>B0-I/SZ | Pin Name                                 |

| F7                    | 55                   | N9                                               | L8        | L7                   | L8                   | GPIO053/PWM0/SLV_SPI_M-<br>STR_INT       |

| G7                    | 56                   | M9                                               | N9        | N8                   | N9                   | GPIO054/PWM1/SLV_SPI_S-CLK               |

|                       | 65                   | L13                                              | M11       | N12                  | M13                  | GPIO027/KSI4/UART0_DSR#/<br>I2C12_SCL    |

|                       | 66                   | L12                                              | L11       | L9                   | L12                  | GPIO030/KSI5/I2C10_SDA                   |

|                       | 67                   | K12                                              | K11       | K9                   | K11                  | GPIO107/nSMI/KSO04/I2C10_<br>SCL         |

|                       | 68                   | K13                                              | M12       | L12                  | L13                  | GPIO120/KSO07/UART1_DTR<br>#             |

|                       | 69                   | H13                                              | L12       | K10                  | K13                  | GPIO112/KSO05                            |

|                       | 70                   | J13                                              | M13       | K12                  | K12                  | GPIO113/KSO06/ICT9                       |

|                       | 71                   | J12                                              | J11       | L10                  | J11                  | GPIO114/PS2<br>CLK0A/nEC_SCI             |

| H10                   | 74                   | G13                                              | K12       | H13                  | H11                  | GPIO042/PECI_DAT/SB-TSI<br>DAT           |

| G10                   | 75                   | F13                                              | H9        | H10                  | H9                   | GPIO043/SB-TSI_CLK                       |

| G9                    | 76                   | J10                                              | H11       | G13                  | G11                  | GPIO044/VREF_VTT                         |

|                       |                      |                                                  | H13       | J13                  | H13                  | GPIO034/GPSPI_IO2                        |

|                       |                      |                                                  | B6        | A6                   | A3                   | GPIO036                                  |

|                       |                      |                                                  | E7        | A4                   | E7                   | GPIO240                                  |

| C2                    |                      |                                                  | E1        | E2                   | E1                   | GPIO035/PWM8/CTOUT1/ICT 15               |

| F9                    | 78                   | G10                                              | J12       | H11                  | H12                  | GPIO170/UART1_TX/CEC_O<br>UT[JTAG_STRAP] |

|                       |                      |                                                  | B11       | B13                  | B10                  | GPIO171/UART1_RX/CEC_IN                  |

| E7                    | 79                   | E13                                              | K13       | J11                  | J12                  | JTAG_RST#                                |

| F10                   | 80                   | G12                                              | J13       | J12                  | G12                  | GPIO104/UART0_TX/TFDP<br>CLK[VTR2_STRAP] |

| D7                    | 81                   | F12                                              | H12       | F13                  | G13                  | GPIO105/UART0_RX/TFDP<br>DATA/TRACECLK   |

|                       | 82                   | F9                                               | G13       | H12                  | F13                  | GPIO046/KSO02/ICT11                      |

|                       | 83                   | F10                                              | G9        | E11                  | G9                   | GPIO047/KSO03/PWM3_ALT/I<br>CT13         |

|                       | 84                   | C13                                              | G12       | G12                  | F12                  | GPIO121/PVT_IO0/KSO08                    |

|                       | 85                   | E12                                              | G11       | G10                  | F11                  | GPIO122/PVT_IO1/KSO09                    |

|                       | 86                   | D12                                              | F12       | F11                  | E12                  | GPIO123/PVT_IO2/KSO10                    |

|                       | 87                   | D13                                              | F11       | G11                  | E11                  | GPIO126/PVT_IO3/KSO13                    |

|                       | 17                   | H1                                               | G2        | H1                   | G2                   | GPIO124/PVT_CS#/KSO11/IC<br>T12          |

|                       | 88                   | C12                                              | E11       | F12                  | E13                  | GPIO125/PVT_CLK/KSO12                    |

|                       | 89                   | E10                                              | F9        | D10                  | F9                   | GPIO175/CMP<br>VOUT1/PWM8_ALT            |

|                       | 91                   | A12                                              | F13       | E13                  | D12                  | GPIO127/A20M/UART1_RTS#                  |

TABLE 2-1: MEC152X PIN MAP (CONTINUED)

| IABLE 2-1.            | 10120102             | ZA PIN WAP                                       | (001111100  | <u> </u>             |                      |                                                   |

|-----------------------|----------------------|--------------------------------------------------|-------------|----------------------|----------------------|---------------------------------------------------|

| MEC1521H-<br>B0-I/2MW | MEC1521H-<br>B0-I/Z2 | MEC1521H-<br>B0-I/TF and<br>MEC1527H-<br>B0-I/TF | B0-I/SZ and | MEC1523H-<br>B0-I/3Y | MEC1523H-<br>B0-I/SZ | Pin Name                                          |

| E10                   | 92                   | A13                                              | D11         | E12                  | D11                  | GPIO156/LED0                                      |

|                       | 100                  | D9                                               | B13         | A11                  | C10                  | GPIO157/LED1                                      |

|                       | 101                  | E9                                               | A12         | C12                  | B11                  | GPIO153/LED2                                      |

| E9                    | 93                   | A11                                              | E12         | D12                  | D13                  | GPIO007/I2C03_SDA/PS2<br>CLK0B                    |

| D10                   | 94                   | B13                                              | E13         | D11                  | C13                  | GPIO010/I2C03_SCL/PS2<br>DAT0B                    |

| D9                    | 95                   | B11                                              | D13         | D13                  | B12                  | GPIO154/I2C02_SDA/PS2<br>CLK1B                    |

| C10                   | 96                   | B12                                              | D12         | C13                  | C12                  | GPIO155/I2C02_SCL/PS2<br>DAT1B                    |

|                       | 10                   | E2                                               | E2          | F2                   | E2                   | GPIO246/CTOUT1_ALT/CMP_<br>VREF0                  |

|                       |                      |                                                  | C9          | C9                   | C9                   | GPIO245/Single-<br>WireUART/GPSPI_IO0             |

| D2                    | 13                   | G2                                               | F1          | F4                   | F1                   | GPIO244/UART<br>CLK_ALT/nEMI_INT_ALT/CMP<br>_VIN1 |

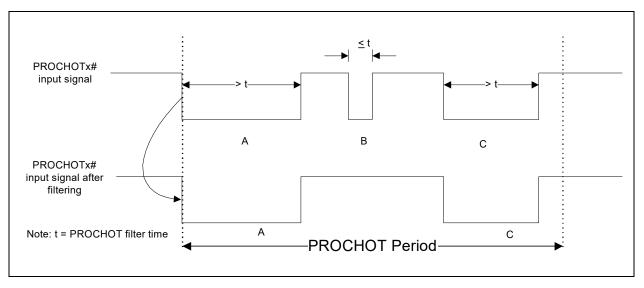

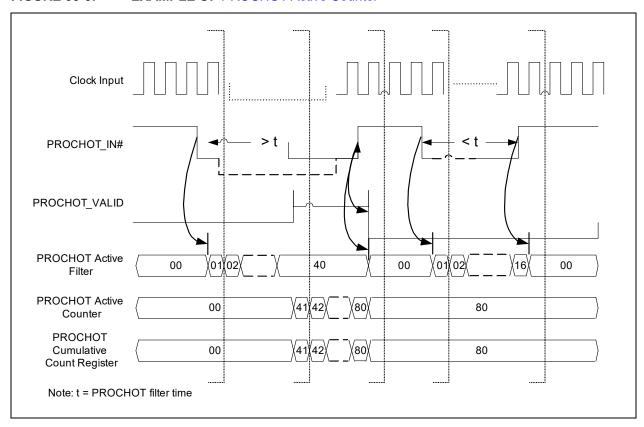

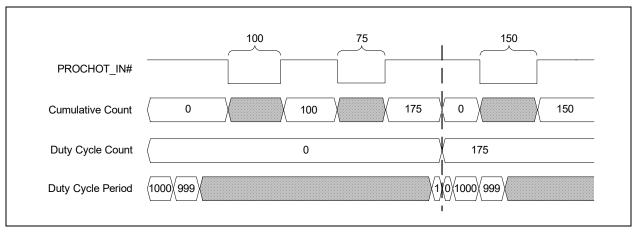

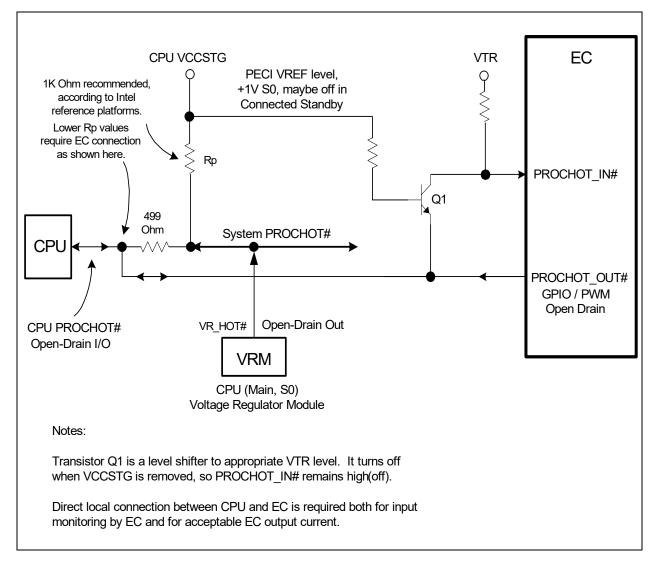

|                       |                      |                                                  | C11         | A10                  | A9                   | GPIO243/GPSPI_IO1                                 |