# High-Performance, High-Accuracy PMIC for PIC64GX MPU Family

**MICROCHIP**

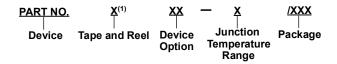

MCP164GX1000

# **General Description**

The MCP164GX1000 is a custom-designed Power Management Integrated Circuit (PMIC) specifically developed as a high-performance, small-footprint power companion for the Microchip 64-bit RISC-V® Quad-Core Microprocessor PIC64GX1000.

Making use of the on-board embedded EEPROM for default power-up configuration, the device is preprogrammed with the necessary configuration required by the PIC64GX1000. It is available in two memory architecture options: DDR4 (MCP164GX1000AB) and LPDDR4 (MCP164GX1000AA).

These options alleviate the production effort, simplifying the integration task of the PMIC into the design. The MCP164GX1000 also offers flexibility, allowing users to reprogram the IC, in-field or in-circuit, with any desired configuration using the integrated  $I^2C$  bus, which supports clock rates up to 3.4 MHz. As a safety mechanism, the integrated EEPROM has protection against accidental write operations.

The MCP164GX1000 supports commercial and industrial applications.

The MCP164GX1000 integrates 13 power channels distributed as eight parallelable 1.5A Buck regulators, four 300 mA LDOs, and one low-input/low-output voltage LDO Controller using an external MOSFET.

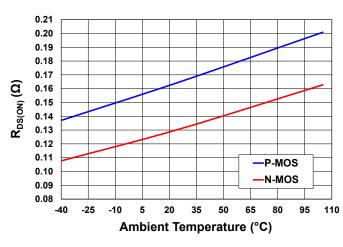

The eight 1.5A Buck regulators can be operated either independently or in parallel to support higher currents, in groups of up to four. The paralleling technique relies on the matching of the power switches' resistances and does not require the complication of an additional current-sharing loop. Part count and solution footprint are also reduced since all paralleled channels share the same inductor, while the required magnetic volume is the same as equivalent multi-phase architectures.

As a result of the pin arrangement, paralleling up to four channels allows for a total of 6A output current with the recommended layout.

The switching frequency of the Buck channels defaults to 2 MHz, and the switching phases can also be programmed. Furthermore, the switching frequency can be synchronized to an external clock within the 3-5 MHz range. The frequency synchronization technique can achieve zero phase error (after synchronization) between the incoming synchronization clock and the Buck converters' turn-on switching, such that the timing of the switching events can be accurately established.

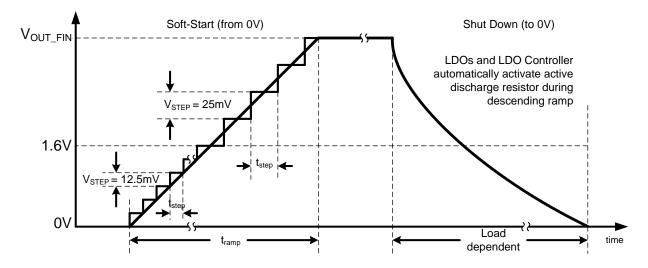

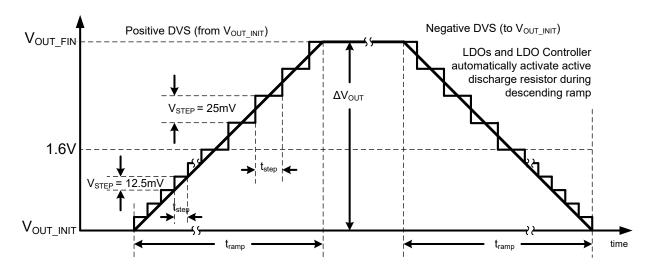

The buck output voltage setting spans from 0.6V to 1.6V in 12.5 mV increments and from 1.6V to 3.8V in 25 mV increments and can be as accurate as  $\pm 0.8\%$  (V<sub>FB</sub>  $\geq$  1V) over temperature. Feedback resistors are internal, thus improving total accuracy (due to superior matching in integrated form) and further reducing part count and solution space.

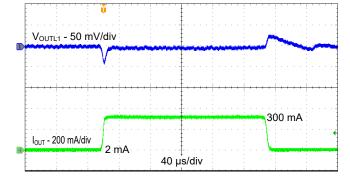

The four 300 mA high-accuracy (±1% overtemperature), high-PSRR LDOs can also be cascaded (in groups of two) to the output of a DC-DC channel, thus improving overall conversion efficiency. LDOs are typically dedicated to sensitive analog loads, such as PLL supply rails.

LDOs' output voltages are also programmable from 0.6V to 1.6V in 12.5 mV increments and from 1.6V to 3.8V in 25 mV increments.

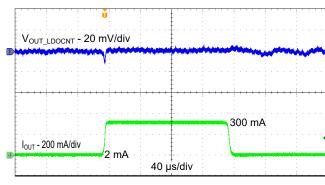

The MCP164GX1000 additionally integrates one low-input/low-output high-accuracy LDO Controller, using a small, inexpensive external N-channel MOSFET as a pass device. This solution is intended to provide a clean supply voltage to SERDES lanes. It can do so while maintaining high PSRR, low noise, fast load transient performance, and also achieving scalability for different applications.

Data Sheet 20007007A - 1

The LDO Controller typically post-regulates the output of one (or more, if paralleled) Buck channels to a slightly lower regulated voltage. Protection features are provided by the upstream Buck stage. The output voltage of the LDO Controller is programmable from 0.6V to 1.6V in 12.5 mV increments.

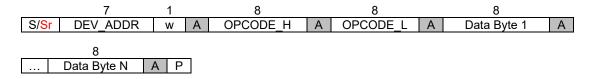

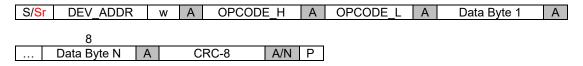

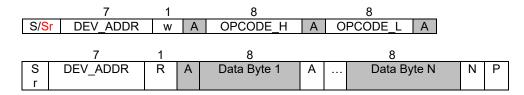

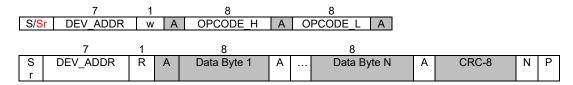

The programming and communication interface is I<sup>2</sup>C (High-Speed mode i.e. up to 3.4 MHz) with optional support of Packet Error Checking (PEC). An open-drain interrupt pin (nINTO) allows signaling of anomalies to the host MPU.

Although the MCP164GX1000 comes preconfigured, the default power-up voltage values, as well as all the sequencing among power channels, associated delays, and many other settings, can be modified by the user using the embedded EEPROM memory. This allows any differences from typical application use cases can be addressed without the need for dedicated product variants from the factory. This step may be done during prototyping and also at board manufacturing, taking a negligible amount of time in the production flow. Nevertheless, preprogrammed customized parts can be ordered from Microchip to support large-volume applications.

The MCP164GX1000 features two different reset outputs:

- nRSTO\_A: The nRSTO\_A signal is deasserted (with a user-programmable delay) after all enabled channels have reached their regulation voltage. The nRSTO\_A signal is meant to flag to a system supervisor (e.g. housekeeping MCU) that the whole application has started correctly.

- nRSTO\_P: The nRSTO\_P signal is deasserted (with a user-programmable delay) after a user-defined subset of all enabled channels have reached their regulation voltage. The nRSTO\_P signal is meant to drive the DEVRST\_N input of PolarFire® FPGAs/SoCs.

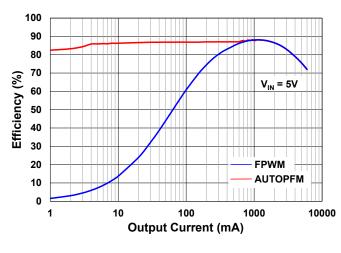

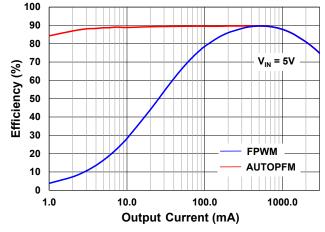

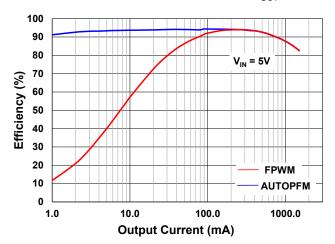

The MCP164GX1000 power management settings allow for the implementation of low-power modes commanded by a GPIO pin (MODE input of the MCP164GX1000). Any channel can also be selectively and permanently set in AutoPFM or FPWM, or even turned on/off based on the MODE input.

A programmable, windowed Watchdog Timer with uncommitted open-drain output (nWDO) is also available.

The MCP164GX1000 is available in a 64-pin, 8 x 8 mm VQFN package with an operating junction temperature range from  $-40^{\circ}$ C to  $+105^{\circ}$ C.

#### **Features**

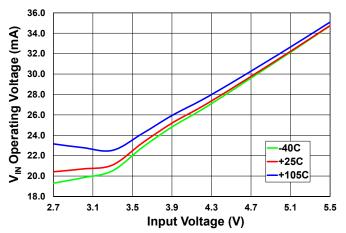

- Input Voltage: 2.7V to 5.5V

- Eight 1.5A Buck DC-DC Channels

- Four 300 mA High-Accuracy LDOs

- One High-Accuracy, High-PSRR LDO Controller Using External N-Channel MOSFET (SERDES Lanes Supply)

- ±0.8% Output Voltage Accuracy for Bucks (VDD), for V<sub>FB</sub> ≥ 1V

- -1.5%/+1% Output Voltage Accuracy for the LDO Controller, for V<sub>FBLC</sub> ≥ 0.9V

- ±1% Output Voltage Accuracy for LDOs, for V<sub>FBI</sub> ≥ 1.8V

- Directly Parallelable Buck Channels Power Stages Up to 4 for a Combined Current Capability Up to 6A

- Tight R<sub>DS(ON)</sub> Matching of Parallelable Channels for Good Current Sharing

- Minimum Number of Inductors: Paralleled Buck Channels Share the Same Inductor

- Programmable Output Voltage for all Buck and LDO Channels 0.6V to 3.8V No External Feedback Resistors Required

- 100% Duty Cycle Capability of Buck Channels

- LDO Controller Output Voltage 0.6V to 1.6V/12.5 mV Steps

- Reference Ground (REFGND) Can be Remotely Routed to the Load Ground (Pseudo Remote Sensing)

- Low-Noise Forced-PWM and Light-load High-Efficiency Mode Available (Pin-Selectable or Bit Control)

- External Synchronization of Switching Frequency, with Accurate Switching-Events Time Positioning

- Selectable Phase (0°, 90°, 180° or 270°) for Buck Channels

- Global RESET (nRSTO\_A) with Programmable Deassertion Delay

- User-Defined RESET (nRSTO\_P) with Programmable Deassertion Delay Ideal for PolarFire FPGA DEVRST\_N Interfacing

- 3.4 MHz I<sup>2</sup>C Interface

- In-Circuit Programmable: On-Board Embedded EEPROM for Default Power-Up Configuration Programming

- EEPROM Write Password Protection

- Dedicated VDD Supply Pin for EEPROM and Interface Allows Programming Without Powering Up the Application

- Reconfigurable During Run Time

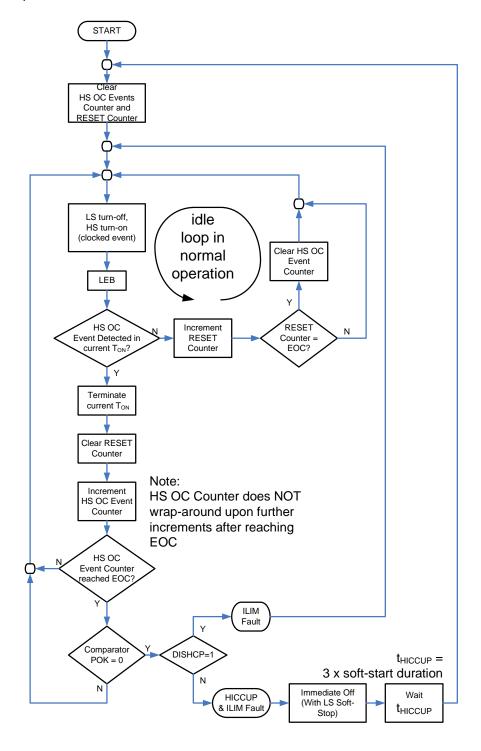

- Hiccup Mode Current Limit for Buck Channels (Can Be Disabled)

- Programmable Thermal Early Warning and Thermal Shutdown Protection

- nINTO Pin (Interrupt Flag) With Selectable Interrupt Masking for Each Channel

- 64-Pin VQFN Package, 8 x 8 mm

- -40°C to +105°C Junction Temperature Range

# **Applications**

Microchip 64-bit RISC-V® Quad-Core Microprocessor PIC64GX1000

# **Typical Application**

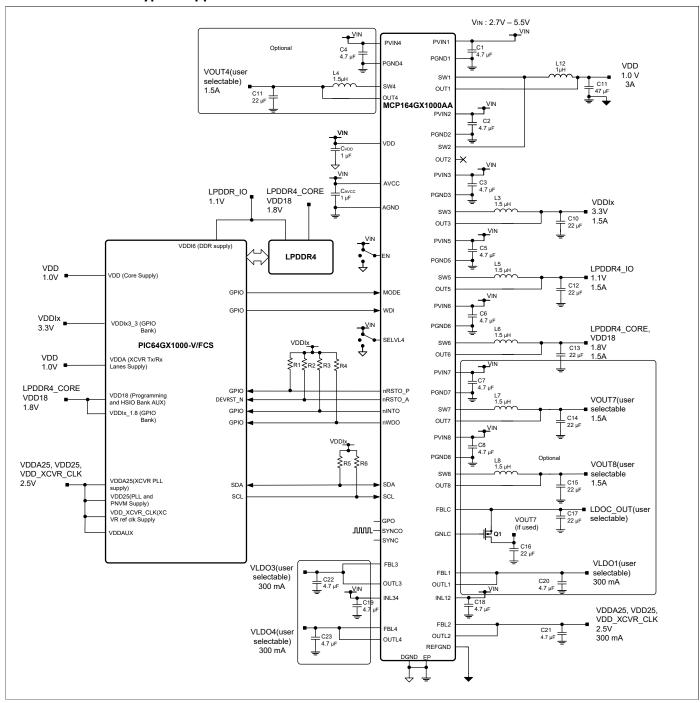

# MCP164GX1000AA Typical Application

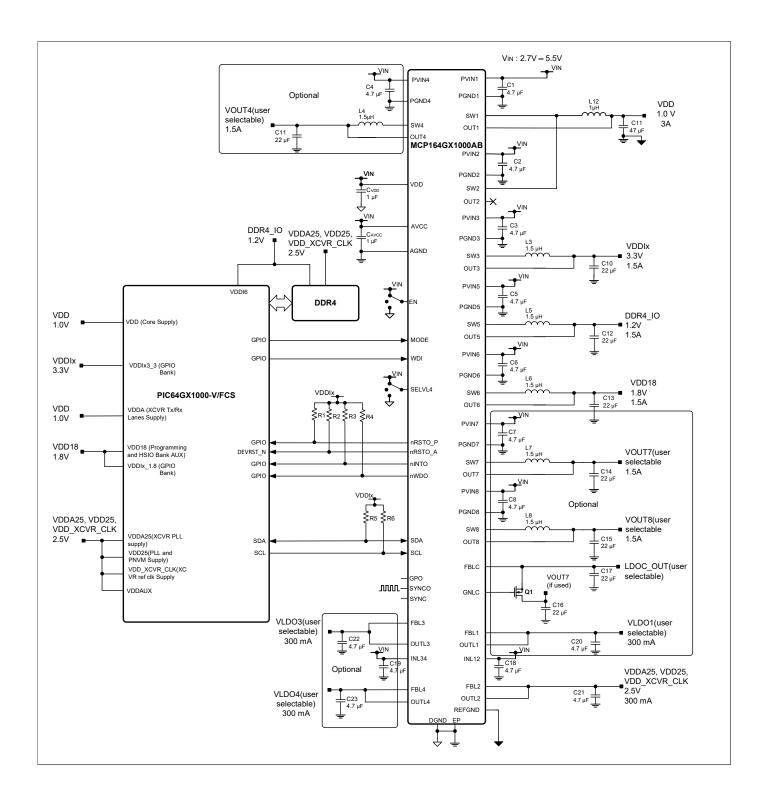

## MCP164GX1000AB Typical Application

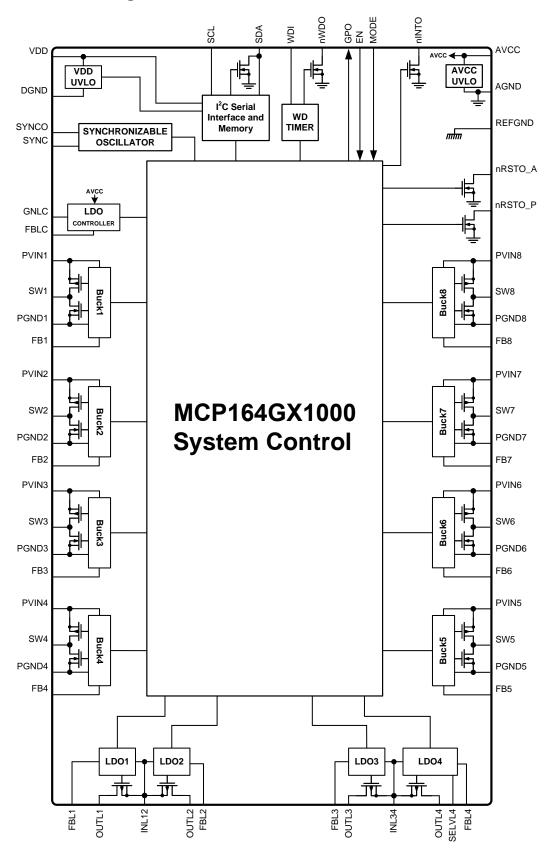

# **Functional Block Diagram**

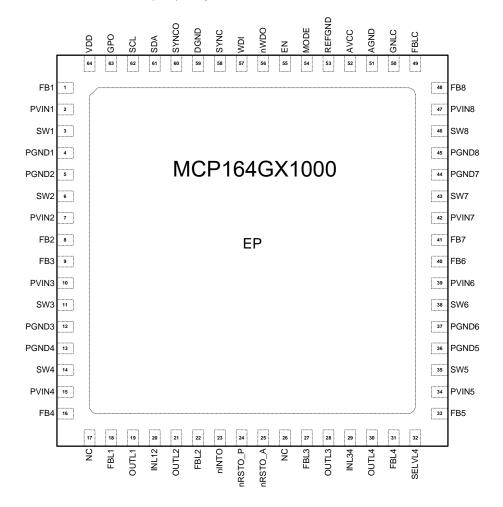

# 1. Pin Description

| Pin Number | Pin Name | Description                                                                                                                                                                                                                                                                                                      |

|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | FB1      | Buck1 Feedback. Connect to VOUT1 for output sensing for Buck Channel 1. Buck1 is always a main channel.                                                                                                                                                                                                          |

| 2          | PVIN1    | Power Input Voltage of Buck Channel 1.                                                                                                                                                                                                                                                                           |

| 3          | SW1      | Switch Node of Buck Channel 1. Internal power MOSFET switches and external inductor connection.                                                                                                                                                                                                                  |

| 4          | PGND1    | Power Ground of Buck Channel 1.                                                                                                                                                                                                                                                                                  |

| 5          | PGND2    | Power Ground of Buck Channel 2.                                                                                                                                                                                                                                                                                  |

| 6          | SW2      | Switch Node of Buck Channel 2. Internal power MOSFET switches and external inductor connection.                                                                                                                                                                                                                  |

| 7          | PVIN2    | Power Input Voltage of Buck Channel 2.                                                                                                                                                                                                                                                                           |

| 8          | FB2      | Buck2 Feedback. Connect to VOUT2 for output sensing of Buck Channel 2 in main operation. Connect to PVIN2, ground or leave floating when Buck2 is defined as replica and paralleled to Buck1.                                                                                                                    |

| 9          | FB3      | Buck3 Feedback. Connect to VOUT3 for output sensing of Buck Channel 3 in main operation. Connect to PVIN3, ground or leave floating when Buck3 is defined as replica and paralleled to Buck2.                                                                                                                    |

| 10         | PVIN3    | Power Input Voltage of Buck Channel 3.                                                                                                                                                                                                                                                                           |

| 11         | SW3      | Switch Node of Buck Channel 3. Internal power MOSFET switches and external inductor connection.                                                                                                                                                                                                                  |

| 12         | PGND3    | Power Ground of Buck Channel 3.                                                                                                                                                                                                                                                                                  |

| 13         | PGND4    | Power Ground of Buck Channel 4.                                                                                                                                                                                                                                                                                  |

| 14         | SW4      | Switch Node of Buck Channel 4. Internal power MOSFET switches and external inductor connection.                                                                                                                                                                                                                  |

| 15         | PVIN4    | Power Input Voltage of Buck Channel 4.                                                                                                                                                                                                                                                                           |

| 16         | FB4      | Buck4 Feedback. Connect to VOUT4 for output sensing of Buck Channel 4 in main operation. Connect to PVIN4, ground or leave floating when Buck4 is defined as replica and paralleled to Buck3.                                                                                                                    |

| 17         | NC       | Not Connected. Leave floating.                                                                                                                                                                                                                                                                                   |

| 18         | FBL1     | LDO1 Feedback. Connect to the point of regulation of the load of LDO1, fed by pin OUTL1.                                                                                                                                                                                                                         |

| 19         | OUTL1    | LDO1 Output. Decouple OUTL1 to ground with a 2.2 µF (minimum) ceramic capacitor.                                                                                                                                                                                                                                 |

| 20         | INL12    | Input Voltage for LDO1 and LDO2. Decouple INL12 to ground with a 2.2 $\mu\text{F}$ (minimum) ceramic capacitor.                                                                                                                                                                                                  |

| 21         | OUTL2    | LDO2 Output. Decouple OUTL2 to ground with a 2.2 µF (minimum) ceramic capacitor.                                                                                                                                                                                                                                 |

| 22         | FBL2     | LDO2 Feedback. Connect to the point of regulation of the load of LDO2, fed by pin OUTL2.                                                                                                                                                                                                                         |

| 23         | nINTO    | Interrupt Output (open-drain).                                                                                                                                                                                                                                                                                   |

| 24         | nRSTO_P  | Programmable Reset Open-drain Output. nRSTO_P will be deasserted (high-Z), with a default or user-defined delay, after a user-defined subset of all enabled regulators (which are part of the start-up sequence) have reached their POK thresholds. Typically interfaced to the DEVRST_N pin of PolarFire FPGAs. |

| 25         | nRSTO_A  | Global Reset Open-drain Output (default). nRSTO_A will be deasserted (high-Z), with a default or user-defined delay, after all enabled regulators (which are part of the start-up sequence) have reached their POK thresholds.                                                                                   |

| 26         | NC       | Not Connected. Leave floating.                                                                                                                                                                                                                                                                                   |

| 27         | FBL3     | LDO3 Feedback. Connect to the point of regulation of the load of LDO3, fed by pin OUTL3.                                                                                                                                                                                                                         |

| 28         | OUTL3    | LDO3 Output. Decouple OUTL3 to ground with a 2.2 µF (minimum) ceramic capacitor.                                                                                                                                                                                                                                 |

| 29         | INL34    | Input Voltage for LDO3 and LDO4. Decouple INL34 to ground with a 2.2 $\mu\text{F}$ (minimum) ceramic capacitor.                                                                                                                                                                                                  |

| 30         | OUTL4    | LDO4 Output. Decouple OUTL4 to ground with a 2.2 µF (minimum) ceramic capacitor.                                                                                                                                                                                                                                 |

| n Description | (continued) |                                                                                                                                                                                                                                     |

|---------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| in Number     | Pin Name    | Description                                                                                                                                                                                                                         |

| 31            | FBL4        | LDO4 Feedback. Connect to the point of regulation of the load of LDO4, fed by pin OUTL4.                                                                                                                                            |

| 32            | SELVL4      | LDO4 Voltage Selection Pin. If configured appropriately, this pin selects between 1.8V and 3.3V on LDO4. Used for dual-voltage SD Card support. <b>Do not leave floating.</b>                                                       |

| 33            | FB5         | Buck5 Feedback. Connect to VOUT5 for output sensing of Buck Channel 5. Buck5 is always a main channel.                                                                                                                              |

| 34            | PVIN5       | Power Input Voltage of Buck Channel 5.                                                                                                                                                                                              |

| 35            | SW5         | Switch Node of Buck Channel 5. Internal power MOSFET switches and external inductor connection.                                                                                                                                     |

| 36            | PGND5       | Power Ground of Buck Channel 5.                                                                                                                                                                                                     |

| 37            | PGND6       | Power Ground of Buck Channel 6.                                                                                                                                                                                                     |

| 38            | SW6         | Switch Node of Buck Channel 6. Internal power MOSFET switches and external inductor connection.                                                                                                                                     |

| 39            | PVIN6       | Power Input Voltage of Buck Channel 6.                                                                                                                                                                                              |

| 40            | FB6         | Buck6 Feedback. Connect to VOUT6 for output sensing of Buck Channel 6 in main operation. Connect to PVIN6, ground or leave floating when Buck6 is defined as replica and paralleled to Buck5.                                       |

| 41            | FB7         | Buck7 Feedback. Connect to VOUT7 for output sensing of Buck Channel 7 in main operation. Connect to PVIN7, ground or leave floating when Buck7 is defined as replica and paralleled to Buck6.                                       |

| 42            | PVIN7       | Power Input Voltage of Buck Channel 7.                                                                                                                                                                                              |

| 43            | SW7         | Switch Node of Buck Channel 7. Internal power MOSFET switches and external inductor connection.                                                                                                                                     |

| 44            | PGND7       | Power Ground of Buck Channel 7.                                                                                                                                                                                                     |

| 45            | PGND8       | Power Ground of Buck Channel 8.                                                                                                                                                                                                     |

| 46            | SW8         | Switch Node of Buck Channel 8. Internal power MOSFET switches and external inductor connection.                                                                                                                                     |

| 47            | PVIN8       | Power Input Voltage of Buck Channel 8.                                                                                                                                                                                              |

| 48            | FB8         | Buck8 Feedback. Connect to VOUT8 for output sensing of Buck Channel 8 in main operation. Connect to PVIN8, ground or leave floating when Buck8 is defined as replica and paralleled to Buck7.                                       |

| 49            | FBLC        | LDO Controller Feedback. Connect to the point of regulation of the load, which is connected to the source of the external N-channel MOSFET. The typical load of the LDO Controller will be the SERDES lanes core rail of the FPGA.  |

| 50            | GNLC        | LDO Controller Gate. Connect to the gate of the external N-channel MOSFET.                                                                                                                                                          |

| 51            | AGND        | Analog Ground for control section. AGND is also the return for the LDO Controller.                                                                                                                                                  |

| 52            | AVCC        | Analog Supply Voltage for control section (2.7V to 5.5V). Locally decouple pin AVCC to pins AGND and REFGND with a 1 $\mu$ F (minimum) ceramic capacitor. AVCC is also the supply voltage for the gate drive of the LDO Controller. |

| 53            | REFGND      | Reference Ground. All reference voltages are returned to this pin. For best regulation accuracy, route REFGND free from any parasitic voltage drops up to the grounding point of the load.                                          |

| 54            | MODE        | Buck channels high-efficiency light-load mode selection pin. Drive this pin HIGH to force FPWM operation. Leave floating or connect to ground to enable AutoPFM. MODE is internally pulled down through a 100 k $\Omega$ resistor.  |

| 55            | EN          | Enable input. Set EN to HIGH to turn on the power channels. Set LOW to turn power channels off.                                                                                                                                     |

| 56            | nWDO        | Watchdog Output (open drain).                                                                                                                                                                                                       |

| 57            | WDI         | Watchdog Input.                                                                                                                                                                                                                     |

| Pin Description | (continued) |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Number      | Pin Name    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 58              | SYNC        | External Synchronization pin. A reference clock frequency can be provided externally to the SYNC pin, resulting in the switching frequency of the Buck regulators being ½ of the SYNC frequency. Feeding SYNC with an external clock will also cause the Buck channels to operate in CCM mode (aka FPWM), regardless of the MODE selection pin (unless masked by configuration). SYNC is internally pulled down to DGND through a 100 k $\Omega$ resistor. |

| 59              | DGND        | Digital Ground. Return for I <sup>2</sup> C interface.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 60              | SYNCO       | Programmable SYNChronization Output pin. When enabled, this pin provides a square wave which can be used to synchronize other DC-DC converters in the system.                                                                                                                                                                                                                                                                                              |

| 61              | SDA         | I <sup>2</sup> C Interface Serial Data.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 62              | SCL         | I <sup>2</sup> C Interface Serial Clock.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 63              | GPO         | General Purpose Output.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 64              | VDD         | Digital Supply Voltage for EEPROM memory, I $^2$ C interface, and volatile registers. VDD can be applied independently from all other supply rails. Decouple VDD to DGND with a 1 $\mu$ F (minimum) ceramic capacitor.                                                                                                                                                                                                                                     |

| _               | EP          | Exposed Pad. Connect to a ground plane with vias to ensure good thermal properties.                                                                                                                                                                                                                                                                                                                                                                        |

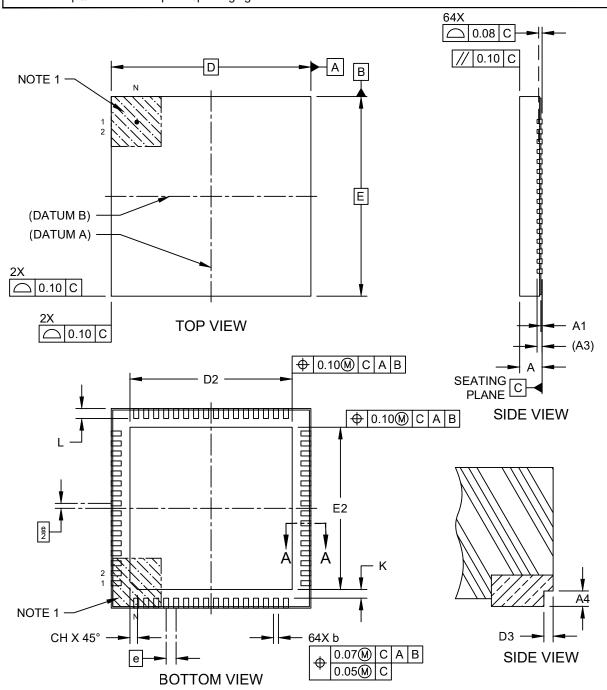

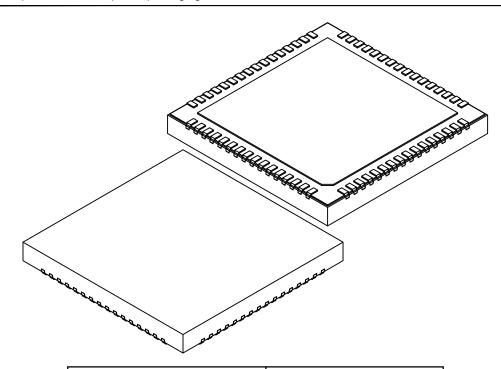

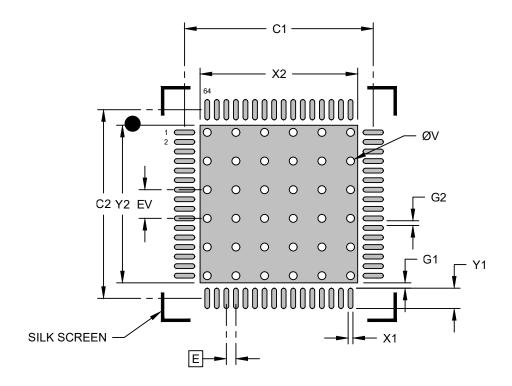

# 1.1. Package Type

Figure 1-1. 64-Lead 8x8x0.9 mm VQFN (KCX) - Top View

# 2. Functional Description

## 2.1. Buck Channels and Related External Components

The MCP164GX1000 integrates eight parallelable 1.5A Buck regulators that can be operated in parallel. These Buck regulators can function independently or be paralleled in groups of up to four to support higher currents. The paralleling technique relies on the matching of the power switches' resistances and does not require the complication of an additional current sharing loop. Part count and solution footprint are also reduced since all paralleled channels share the same inductor, while the required magnetic volume is the same as equivalent multi-phase architectures. As a result of the pin arrangement, paralleling up to four channels allows for a total of 6A output current with the recommended layout.

The MCP164GX1000 Buck channels are based on a peak-current-mode control architecture and have internal frequency compensation for the voltage regulation loop. The slope compensation is optimized for inductors in the 1  $\mu$ H to 2.2  $\mu$ H range. A minimum output capacitor of 22  $\mu$ F is required for stable operation. Output capacitance can be increased if necessary; however, the maximum output capacitance value should be limited to avoid engaging Hiccup mode overcurrent protection during the initial soft-start ramp and during DVS operation.

The recommended input decoupling capacitance on each Buck channel is 4.7  $\mu$ F.

The Buck channels can operate either in Forced PWM mode (Continuous Inductor Current mode), where the inductor current is allowed to go negative, or in Automatic PFM mode, where the inductor current is not allowed to go negative through Zero-Current Detection (ZCD) and diode emulation of the low-side MOSFET.

The switching frequency in Forced PWM mode is nominally 2 MHz and can be displaced through  $I^2C$  by  $\pm 16.5\%$  to prevent interference with other sensitive system blocks.

For the MCP164GX1000, parallel operation is constrained to Buck channels placed on the same side of the device. Buck channels placed on opposite sides cannot be connected in parallel. Therefore, the two separate parallel groups are Buck1-to-Buck4 and Buck5-to-Buck8. Buck1 and Buck5 are always either independent or MAIN.

# 2.2. LDO Channels with Forced Bypass Mode and Related External Components

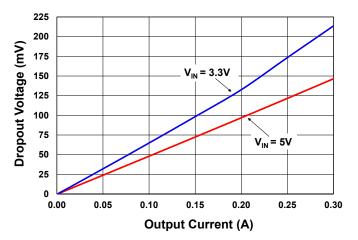

The MCP164GX1000 integrates four 300 mA high-accuracy ( $\pm 1\%$  over temperature, for V<sub>FB</sub>  $\geq 1.8$ V), high-PSRR LDOs. The LDOs can also be cascaded (in groups of two) to the output of a DC-DC channel, thus improving overall conversion efficiency. LDOs are typically dedicated to sensitive analog loads such as PLL supply rails.

The LDOs' output voltages are also programmable from 0.6V to 1.6V in 12.5 mV increments and from 1.6V to 3.8V in 25 mV increments.

#### 2.2.1. LDO Mode Operation

The MCP164GX1000 LDOs are designed for operation with low-ESR ceramic output capacitors of 2.2  $\mu$ F (minimum value) for loads up to 150 mA, and of 4.7  $\mu$ F (minimum value) for loads up to 300 mA. The total output capacitance should not exceed 20  $\mu$ F.

The LDOs can be used with an input voltage (INL) less than or equal to the voltage at pin AVCC. As such, they can operate as post-regulators cascaded to a buck output, if its output voltage is programmed above 2.7V.

#### 2.2.2. Forced Bypass Mode Operation

The forced bypass operation of LDOs can change the functionality of the LDOs into four additional software-controlled load switches. Forced Bypass mode is enabled by setting bit FBYPM (default is '0' = normal LDO mode).

When the FBYPM is set, the LDO is programmed to deliver a 5.25V output voltage to the load (the LDO will always operate in dropout). However, if for any reason the input voltage INLxx overshoots above 5.25V, the output of the LDO will try to regulate at 5.25V, thus protecting the load from overvoltage.

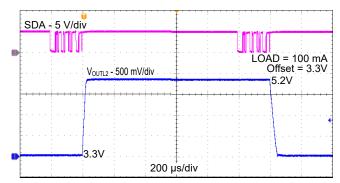

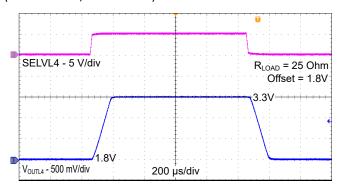

## 2.2.3. LDO4 with External Voltage Selection (SELVL4 Pin)

LDO4 features a dedicated pin (SELVL4) to control its output voltage between 1.8V and 3.3V. This is done to implement support for dual-voltage SD Cards.

#### The SELVL4 can be changed on-the-fly during run time.

LDO4 with External Voltage Selection (SELVL4 Pin) summarizes the mode of operation of LDO4 depending on the configuration bits ENSELVL4, POLSELV/FBYPM, and SELVL4 pin logic level.

Table 2-1. LDO4 Functionality vs. NVM ENSELVL4, POLSELV/FBYPM, SELVL4.

| NVM_ENSELVL4 | POLSELV/FBYPM | SELVL4 Pin | VOUT LDO4          | SELVL4S Status Bit |

|--------------|---------------|------------|--------------------|--------------------|

| 0            | 0             | Don't care | From VSET[7:0]     | 0                  |

| 0            | 1             | Don't care | Forced Bypass mode | 0                  |

| 1            | 0             | 0          | 3.3V               | 0                  |

| 1            | 0             | 1          | 1.8V               | 1                  |

| 1            | 1             | 0          | 1.8V               | 0                  |

| 1            | 1             | 1          | 3.3V               | 1                  |

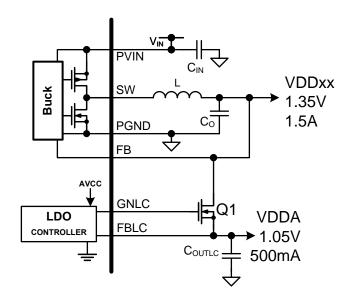

## 2.3. LDO Controller and Related External Components

The LDO Controller is intended to drive an external N-channel MOSFET (Q1 in the figure below). There is no charge pump for gate overdrive, and the turn-on of the external MOSFET is based only on its gate threshold voltage and the available supply voltage (AVCC).

The LDO Controller output voltage (sensed at FBLC) is programmable from 0.6V to 1.6V in 12.5 mV increments.

Figure 2-1. LDO Controller Concept

The drain of the external MOSFET Q1 is connected to the output of one of the Buck channels. This can either be a dedicated or a shared output. In the first case, the output voltage of the front-end Buck can be optimized for the best efficiency and performance. In the second case, efficiency

optimization may not be possible, and the user must ensure that the LDO Controller output rail sequencing is compatible with the shared Buck output (i.e. the LDO Controller is turned on after the shared Buck output and turned off before the shared Buck output or at least at the same time).

Possible external MOSFETs Q1 for the LDO Controller are listed in the LDO Controller External MOSFET Selection chapter.

Overload protection for the LDO Controller channel is supported by the Buck channel, which powers the input of the LDO Controller (external MOSFET drain). The LDO Controller does not have any autonomous overcurrent protection.

For safety and robustness against short-circuits on the LDO Controller output, the Hiccup mode protection of the Buck feeding the LDO Controller should never be disabled; otherwise, excessive power dissipation across the external MOSFET may result.

The MCP164GX1000 LDO Controller is designed for operation with low-ESR ceramic output capacitors of 4.7  $\mu$ F (minimum value) for loads up to 300 mA, and 22  $\mu$ F (minimum value) for loads up to 1.5A. The total output capacitance should not exceed 120  $\mu$ F.

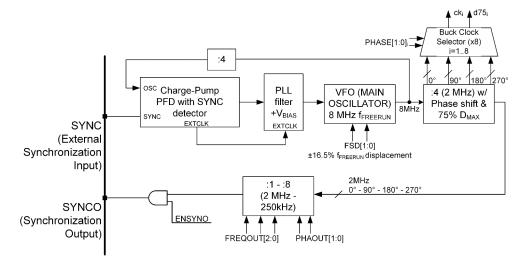

## 2.4. Main Oscillator with External Synchronization

The MCP164GX1000 dedicated synchronizable oscillator generates the switching frequencies and phases for all DC-DC channels.

In free-running mode, the oscillator frequency is nominally 8 MHz (supporting selectable 4-phase operation of the Bucks). Each Buck runs at 2 MHz, and its turn-on switching can be programmed to 0°, 90°, 180° or 270° phase-shift.

The oscillator always starts on its own free-running frequency. In the absence of external frequency synchronization fed at SYNC, FSD[1:0] bits may shift the oscillator free-running frequency as soon as the volatile registers become operational. Until then, FSD[1:0] = 00.

The oscillator can be externally synchronized to an external clock fed at pin SYNC. This clock will typically be generated by a GPIO of the FPGA/MPU or the housekeeping MCU and could also be spread-spectrum modulated.

As soon as the SYNC signal is detected, the oscillator frequency is locked to the SYNC frequency. Therefore, the external synchronization used in the MCP164GX1000 falls into the category of PLL-based techniques.

When the SYNC signal disappears, the PLL filter is slowly reset, and the controlling voltage for the oscillator frequency seamlessly decays towards the free-running value.

# 2.5. Control Signals and Power States

#### 2.5.1. Interfacing Signals

The MCP164GX1000 is interfaced to the system supervisor by means of  $I^2C$  interface pins. The  $I^2C$  interface supporting the High-Speed mode (Hs-mode) data transfer with a bit rate up to 3.4 Mbit/s, as described in the official  $I^2C$  standard, with optional support of Packet Error Checking (PEC). The  $I^2C$  interface is always accessible, even in the OFF state, as long as the VDD pin is powered and above its UVLO Threshold. AVCC UVLO is irrelevant to  $I^2C$  interface operation. Further details about the  $I^2C$  interface of the MCP164GX1000 are given in the  $I^2C$  Interface Description section.

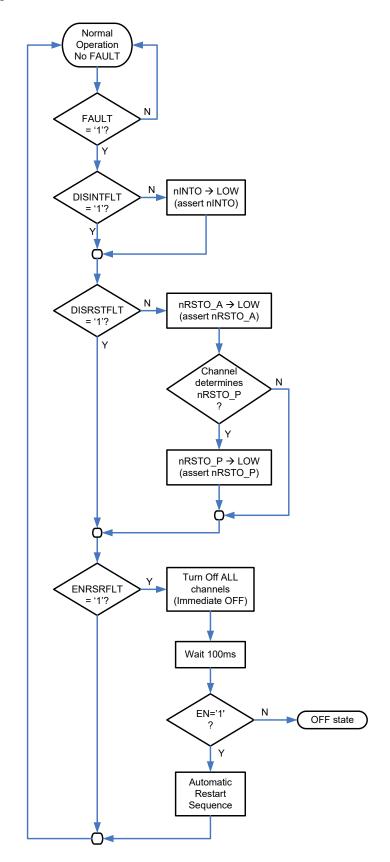

#### 2.5.2. nRSTO A, nRSTO P, nINTO

The MCP164GX1000 features two different reset outputs:

nRSTO\_A: The nRSTO\_A signal is deasserted (with a user-programmable delay) after all enabled channels have reached their regulation voltage. The nRSTO\_A signal is meant to flag to a system supervisor (e.g. housekeeping MCU) that the whole application has been correctly started.

• nRSTO\_P: The nRSTO\_P signal is deasserted (with a user-programmable delay) after a user-defined subset of all enabled channels have reached their regulation voltage. The nRSTO\_P signal is meant to drive the DEVRST N input of PolarFire FPGAs/SoCs.

The nINTO pin is an active-low, open-drain interrupt output pin. The nINTO pin goes low every time a fault is detected, and the corresponding interrupt masking bit is cleared, thus signaling any anomalies to either the FPGA/FPGA SoC or to a host MCU/MPU.

The interrupt is maskable for each channel.

#### 2.5.3. GPO Output

The MCP164GX1000 also provides a general-purpose output pin, which can be used in two ways depending on its NVM\_ENABLE bit setting:

- 1. **NVM\_ENABLE = 1:** GPO is used as an auxiliary command for an external power stage during turn-on/off sequences.

- In this mode, GPO will be asserted during the start-up sequence and deasserted during the turn-off sequence in a similar way as other power channels.

- In any case, GPO does NOT influence the assertion/deassertion of nRSTO\_A/nRSTO\_P.

- The assertion polarity (asserted level = HIGH or LOW) can be controlled by the GPOPOL bit. Therefore, it is possible to have the GPO pin starting HIGH or LOW at the beginning of the start-up sequence and to have GPO toggle to the opposite level during start-up (if ENABLE = 1).

- If ENABLE = 1, during the turn-off sequence, the GPO will toggle at the deassertion level at the time programmed by its OFFDLY[5:0] bits.

- In this mode, it is recommended NOT to change ENABLE and/or GPOPOL in the volatile shadow registers during run time, or to restore them to their default values prior to initiating a turn-off sequence.

- 2. **NVM\_ENABLE = 0:** GPO is only activated by the user during run time i.e. after the start-up sequence, through interface commands that overwrite the ENABLE and/or the GPOPOL bits.

The user is responsible for ensuring that ENABLE = 0 at the beginning and during the turn-off sequence to avoid unwanted potential toggling of GPO at the programmed OFFDLY[5:0].

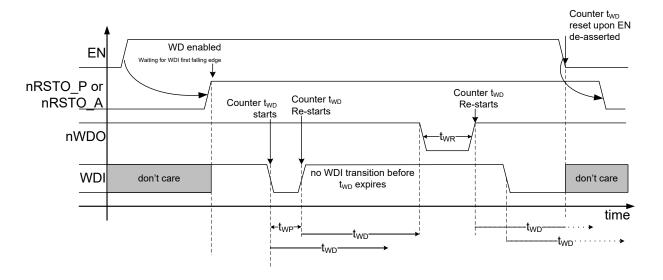

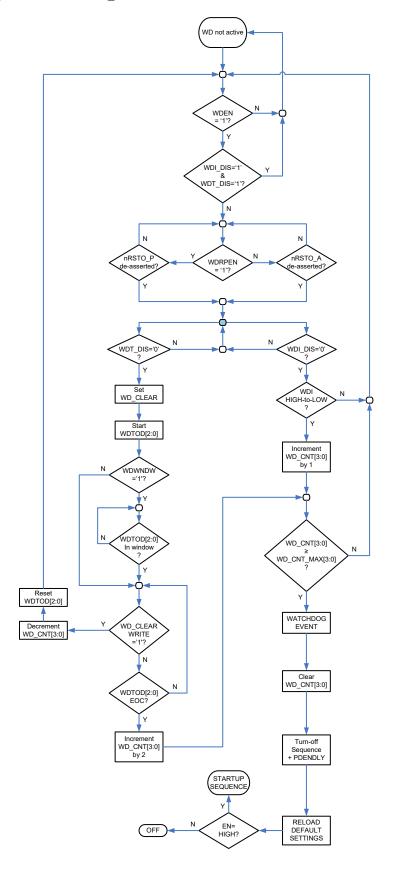

#### 2.5.4. Programmable Watchdog Timer and WDI, nWDO Pins

The Watchdog Timer (WDT) functionality can be chosen as a basic GPIO-cleared WDI/nWDO Watchdog Timer (NVM\_WDMODE = 0, EEPROM only bit) or a more complex, interface-cleared internal WDT with WDI transitions count and hardware reset and restart (NVM WDMODE = 1).

Before the watchdog can run, the NVM\_WDEN/WDEN bit must be set. This applies to both modes of operation.

The need for two different modes arises because:

- For **NVM\_WDMODE** = 0, it is assumed that the host does NOT have an embedded watchdog, or the embedded watchdog is redundant. In this case, the WDI pin is driven by a host GPIO which is toggled intentionally by software. In this scenario, the transition of WDI is a sign of system good health (software is running and periodically toggling WDI). The lack of WDI transition within the programmed time window is a symptom of the software being stuck.

- For **NVM\_WDMODE** = 1, it is assumed that the host has already an embedded watchdog which can assert a software reset. In this case, WDI will be toggled because of a host watchdog reset assertion. Therefore, in this scenario, the transition of WDI means that the software is NOT running properly. If WDI is repeatedly triggered, this is a sign of a malfunction that cannot be recovered by only resetting the software, and therefore, a full hardware reset is invoked.

Additional information regarding Watchdog Timer modes can be found in WDI/nWDO Watchdog Timer Modes.

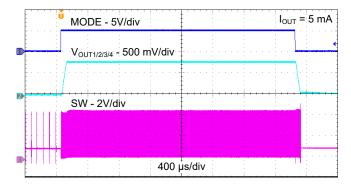

#### 2.5.5. MODE Pin and Low-Power/Standby Mode Control

The MODE pin is typically used to switch the MCP164GX1000 between a high-performance mode (Forced PWM) and a low-power mode (AutoPFM).

As a note of caution, when the MODE pin/bit is changed, the output voltage of the regulator may also change (dictated by the VSET0/VSET1 values). Each VSET register corresponds to an imposed mode of operation (VSET0 = AutoPFM, VSET1 = FPWM).

The MODE pin features programmable polarity, which is defined by an EEPROM bit (NVM\_INVMODEP, Inversion of MODE Pin). The MODE pin polarity is defined by the hardware configuration and therefore it is only allocated in EEPROM.

It is possible to override the external MODE pin command for every regulator. This is done by setting the MODEPMSK bit. When MODEPMSK is '0', the MODE pin (external command) will have an effect on the corresponding regulator. If MODEPMSK = 1, the external MODE command is disabled and the operation of the regulator will be determined by bit MODEB bit.

This way, it is possible to force some regulators to always operate in a certain mode, regardless of the MODE pin, and/or assign their mode control to software commands only, such that it is possible to activate or suspend external MODE control during run time.

The control interdependencies of the MODE pin are outlined in the following table:

Table 2-2. MODE Pin Configuration

| MODE Pin   | INVMODEP bit | MODEPMSK bit | MODEB      | Output Voltage Determined by: | Operation Mode |

|------------|--------------|--------------|------------|-------------------------------|----------------|

| LOW        | 0            | 0            | Irrelevant | VSET0[7:0]                    | AutoPFM        |

| LOW        | 1            | 0            | Irrelevant | VSET1[7:0]                    | FPWM           |

| HIGH       | 0            | 0            | Irrelevant | VSET1[7:0]                    | FPWM           |

| HIGH       | 1            | 0            | Irrelevant | VSET0[7:0]                    | AutoPFM        |

| Irrelevant | Irrelevant   | 1            | 0          | VSET0[7:0]                    | AutoPFM        |

| Irrelevant | Irrelevant   | 1            | 1          | VSET1[7:0]                    | FPWM           |

The MODE pin also allows the user to disable desired regulators using DISMODE0 and DISMODE1 bits. By doing so, the power consumption can be further decreased. Please note that when regulators are disabled using the MODE pin, no sequencing or active discharge will be activated, but the start up of the disabled regulators will be achieved as described by the corresponding ONSR bits.

#### 2.5.6. Power States Definitions

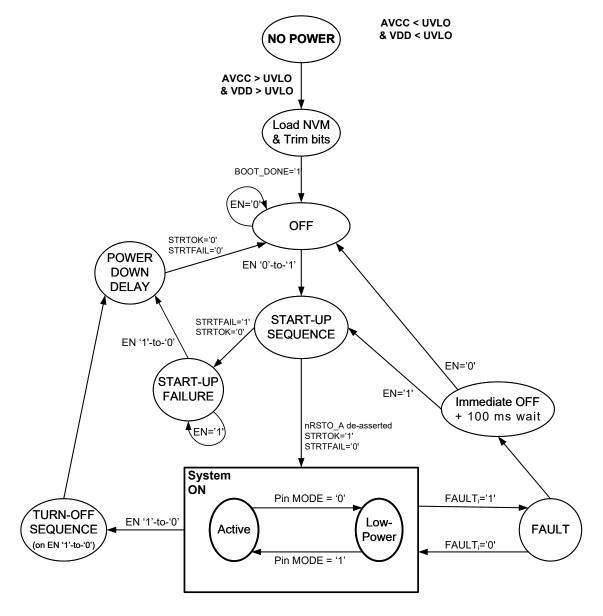

Figure 2-2. Finite State Machine (FSM) States Diagram for MCP164GX1000

The process by which the MCP164GX1000 exits the OFF state and enters the other possible power states is defined as the Power-Up Sequence, which is described in the relevant Power-Up/Power-Down Sequences and Timings section.

# 2.6. Power-Up/Power-Down Sequences and Timings

#### 2.6.1. Typical Power-up Sequence and Timing

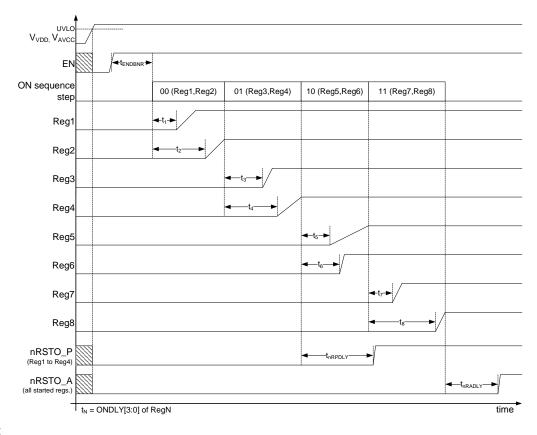

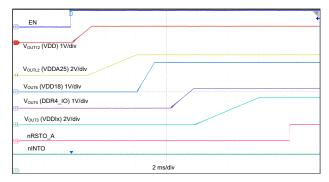

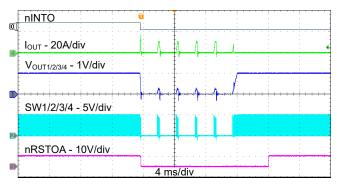

Figure 2-3. Turn-On Sequence Timing Diagram Example

#### Where:

- $t_1$  to  $t_8$  are programmable turn-on delays within each sequence step and configured by the ONDLY[3:0] bits

- t<sub>ENDBNR</sub> defines the debounce time for the L-to-H (rising) edge (or initial H status upon AVCC and VDD UVLO release) and is configured by the ENDBNR[2:0] bits

- t<sub>nRPDLY</sub> represents the deassertion delays for nRSTO\_P and is programmed through the nRPDLY[3:0] bits

- t<sub>nRADLY</sub> represents the deassertion delays for nRSTO\_A and is programmed through the nRADLY[3:0] bits

For the MCP164GX1000, a turn-on (start-up) sequence is typically initiated by EN going HIGH (L-to-H transition).

If EN is connected to VIN and VIN is ramped up, crossing the AVCC and VDD UVLO thresholds, the turn-on sequence will be started.

EN pin transitions (or initial H status upon AVCC and VDD UVLO release) are always deglitched in the analog domain (typically 5-10  $\mu$ s).

Furthermore, the EN pin transitions (or initial H status upon AVCC and VDD UVLO release) are debounced digitally by an internal programmable timer.

The timing diagram above exemplifies the turn-on sequence.

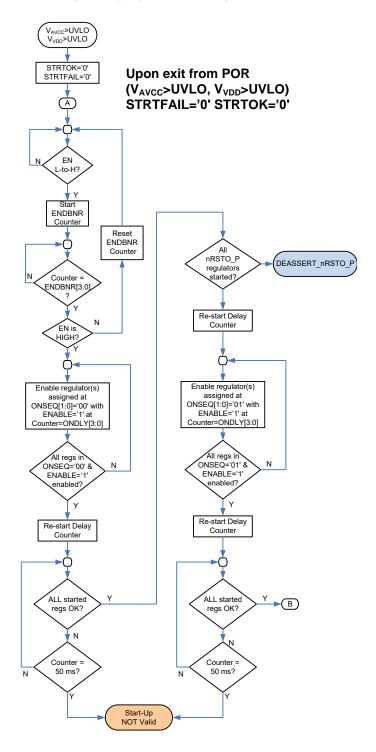

## 2.6.2. Power-Up Sequence Programming and Flowchart

Figure 2-4. Start-Up Flowchart, Part 1 (ONSEQ[1:0] = '00' and '01')

B nRSTO\_P nRSTO\_P nRSTO\_P DEASSERT\_nRSTO\_F DEASSERT\_nRSTO\_P DEASSERT\_nRSTO\_P regulator started? regulator started? started? N N N tart nRADLY[3:0] Re-start Delay Re-start Delay counter (nRSTO\_A Counter assertion delay) ŏ Enable regulator(s) Enable regulator(s) assigned at

ONSEQ[1:0]='10' with

ENABLE='1' at

Counter=ONDLY[3:0] assigned at

ONSEQ[1:0]='11' with

ENABLE='1' at

Counter=ONDLY[3:0] nRADL expired? All regs in ONSEQ='10' & ENABLE='1' All regs in ONSEQ='11' 8 ENABLE='1' ALL started regs OK? enabled? enabled? Υ Re-start Delay Re-start Delay Counter Counter HIGH? Set STRTOK='1' De-assert nRSTO\_A ALL started regs OK? regs OK? START-UP COMPLETED N N 50 ms? 50 ms? EN H-to-L? NOT Valid ENDBNF Shutdown ALL Reset ENDBNF ENDBNF started regulators (Immediate OFF) DEASSERT\_nRSTO\_P Counter ALL started Counter Assert nRSTO P nRSTO\_P regs OK? ENDBNF[3:0] Start nRPDLY[3:0] Counter = assertion delay) ENDBNF[3:0] Assert nINTO, set STRTFAIL='1 EN is Ò LOW? De-assert nRSTO\_P Reset nRPDLY counte EN is STRTOK← '0' nRPDL counter EN is LOW? De-assert nINTO, STRTFAIL←'0' TURN-OFF SEQUENCE (A)

Figure 2-5. Start-Up Flowchart, Part 2 (ONSEQ[1:0] = 10 and '11' – nRSTO\_P and nRSTO\_A Deassertion)

The MCP164GX1000 supports four different sequence steps and sixteen different delays within each sequence.

This allows for up to  $4 \times 16 = 64$  possible different power channel activation instances.

If a given first output voltage must be fully established before a second output voltage is started, then they should be assigned to different turn-on sequence steps.

Sequence steps are defined by the ONSEQ[1:0] bits. See Table 2-11 for the Turn-on Sequence Step Assignment Bit value.

The next sequence step can be initiated only after ALL power channels assigned to the current sequence step are properly established.

It is recommended to assign power supply rails that have sequencing and relative voltage level requirements - such as the VDD1 and VDD2/VDDQ supply rails of LPDDR2/3/4 memories - to different sequence steps. This ensures that any possible failure of the first channel during start-up will also prevent the subsequent channel from attempting start-up, and the turn-on sequence will be aborted without violating the LPDDRx power supplies ramping specified by JEDEC standards.

This is especially important when the first channel (powering VDD1) can be exposed to unpredictable loading in the system (despite it not being recommended to use the LPDDRx VDD1 rail for other purposes).

If different channels are assigned to the same sequence step, their start-up times within the sequence step are purely determined by the turn-on delay (ONDLY[3:0] bits), i.e., the first channel being fully established does NOT condition the start-up of the second channel.

At the conclusion of each sequence step, the proper power-on of ALL regulators previously started is checked. If ALL regulators (including those started in any previous sequence step) have been properly powered-up (POK or bypass POK goes HIGH), then the sequence can continue to the next step.

If ANY of the previously started regulators (including those started in any previous sequence step) have failed to power-up properly (i.e., POK/bypass POK is LOW) after 50 ms since the start of the last regulator in the current sequence step, then the turn-on sequence is immediately aborted, all regulators are shut down through Immediate OFF, nRSTO\_P is asserted (if previously deasserted), nINTO output will be asserted and the STRTFAIL bit will be set.

After the failure of the start-up sequence, even if EN is still HIGH, no further start-up attempts will be made. The MCP164GX1000 expects the host (housekeeping MCU) to detect the failure of the start-up sequence because of the nINTO assertion and STRTFAIL bit readout, and to set EN = LOW. If EN is set LOW for the duration determined by ENDBNF[2:0] bits, then nINTO is deasserted and the STRTFAIL bit cleared. Then the turn-on sequencer can accept another EN LOW-to-HIGH transition.

If EN was connected directly to VIN, power cycling (AVCC and VDD must both fall below the UVLO lower threshold and come back above the UVLO upper threshold) will be the only way to initiate another start-up sequence. This will also reset all status bits (e.g., STRTFAIL) and deassert nINTO.

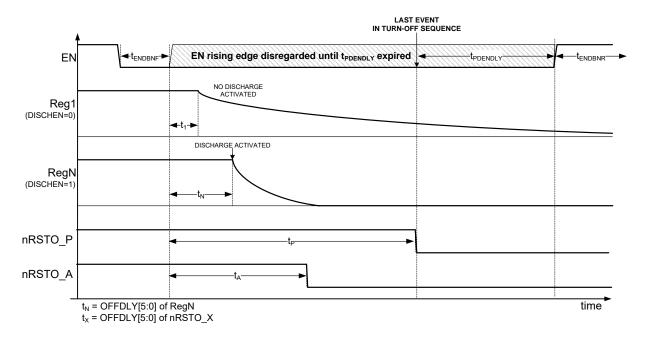

## 2.6.3. Typical Power-Down Sequence and Timing Diagram

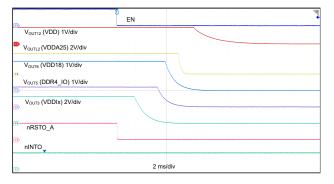

#### **Turn-Off Sequencer**

The MCP164GX1000 also supports turn-off sequencing and Immediate OFF.

Unlike turn-on, there are no turn-off sequence steps. All channels are turned off (upon deassertion of EN and debouncing) based solely on their OFFDLY[5:0] bits. The OFFDLY[5:0] delay marks the beginning of the Immediate OFF.

The turn-off sequence is concluded when the last regulator has been turned off through Immediate OFF or the nRSTO\_P/\_A signals have both been asserted, whichever comes later.

At that point, the PDENDLY[2:0] delay (Power-Down Enable Delay) is started.

During the execution of the turn-off sequence, and for a programmable delay set by the PDENDLY[2:0] bits, the EN pin is masked, and any LOW-to-HIGH transition will be ignored until the PDENDLY[2:0] delay has expired.

If EN is detected HIGH at the end of PDENDLY, it will be interpreted as a LOW-to-HIGH transition just after the expiration of PDENDLY, and another start-up sequence will be initiated after validating the EN LOW-to-HIGH through the ENDBNR debounce timer.

#### nRSTO P/nRSTO A

Assertion at Turn-Off nRSTO\_A and nRSTO\_P can be programmed to be asserted at a specific time during the turn-off sequence.

The table Turn-Off Sequence Step Delay Bits OFFDLY[5:0] also applies to the nRSTO\_A/\_P assertion.

The choice of the nRSTO\_A/P OFFDLY[5:0] bits is entirely up to the user. If OFFDLY[5:0] = 000000, then nRSTO\_A/nRSTO\_P will be asserted LOW as soon as EN has experienced a valid HIGH-to-LOW transition (i.e., after ENDBNF delay) during run time.

The STRTOK bit does not have a corresponding OFFDLY[5:0] and will be cleared with no delay when the turn-off sequence is initiated.

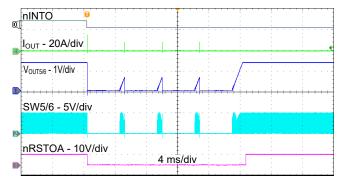

#### **Turn-off Sequence Timing Diagram**

The timing diagram below exemplifies the turn-off sequence. Reg1 to RegN are generic regulators (Buck1-Buck8, LDO1-LDO4, LDO Controller).

All OFF delays (programmed by the OFFDLY[5:0] bits of each regulator and nRSTO\_P/\_A) are counted starting from the same time instant (t<sub>ENDBNF</sub> after the EN HIGH-to-LOW edge, which marks the beginning of the turn-off sequence).

In the example below, the last event in the turn-off sequence is the Immediate OFF of **RegN**.

Additional information about OFFDLY[5:0] can be found in Turn-Off Sequence Step Delay Bits OFFDLY[5:0].

Since the beginning of the turn-off sequence and for the Power-Down Enable Delay t<sub>PDENDLY</sub> (programmed through the PDENDLY[2:0] bits) after the last event in the turn-off sequence, the EN LOW-to-HIGH transition is not recognized.

Additional information about PDENDLY[2:0] can be found in Power-Down Delay Programming PDENDLY[2:0].

Figure 2-6. Turn-OFF Sequence Example Timing Diagram

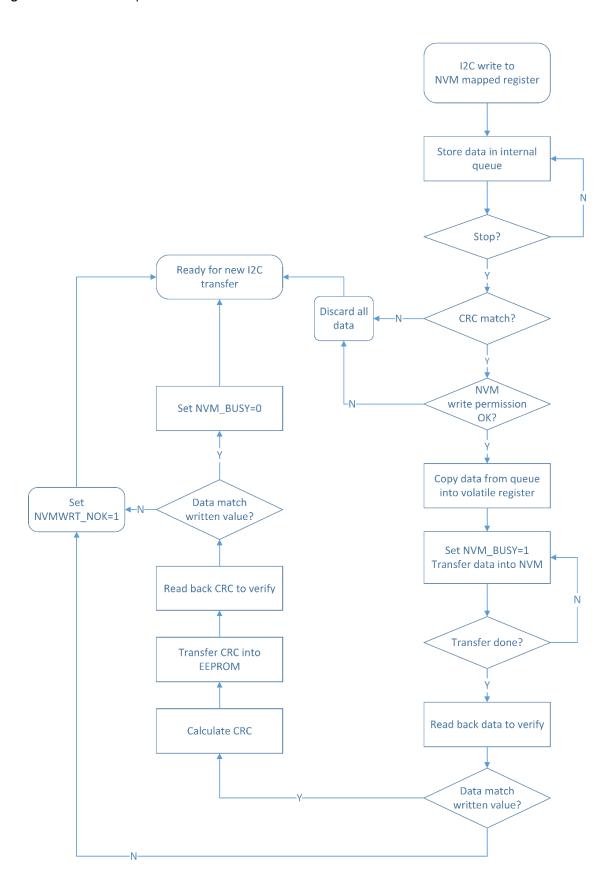

## 2.7. Configuration Bits, Register Definitions and Maps

The position of the configuration bits in the global register maps is described in I<sup>2</sup>C Registers Maps and Bit Definitions.

#### 2.7.1. VSET[7:0] Codes Definition

For the MCP164GX1000, the entire output voltage range is covered with only one type of Buck converter. For this reason, the output voltage range is divided into two sub-ranges featuring different resolution (12.5 mV and 25 mV steps). One full byte, VSET[7:0], is allocated for output voltage coding, as illustrated in the following table. For the VSET0 and VSET1 registers, if the value is programmed between '00000000' to '00110000', the output voltage is clamped at 0.6V. From the value of '11011000' to '111111111', the output voltage is clamped at 3.8V.

Two VSET[7:0] bytes are available for each regulator:

- VSET0[7:0]: voltage setting when mode = 0

- VSET1[7:0]: voltage setting when mode = 1

If VSET0[7:0] is different from the VSET1[7:0] setting, the voltage will change from one level to the other upon MODE bit or pin change (DVS).

Table 2-3 also applies to LDOs' output voltage coding.

For the LDO Controller, the output voltage range is limited to 0.6V to 1.6V with 12.5 mV resolution.

**Table 2-3.** Voltage Codes Definition Bits VSET[7:0]

| VSET[4:0] | VSET[7:5] |        |        |       |       |       |

|-----------|-----------|--------|--------|-------|-------|-------|

|           | 001       | 010    | 011    | 100   | 101   | 110   |

| 00000     | 0.6       | 0.8    | 1.2    | 1.6   | 2.4   | 3.2   |

| 00001     | 0.6       | 0.8125 | 1.2125 | 1.625 | 2.425 | 3.225 |

| 00010     | 0.6       | 0.825  | 1.225  | 1.65  | 2.45  | 3.25  |

| 00011     | 0.6       | 0.8375 | 1.2375 | 1.675 | 2.475 | 3.275 |

| 00100     | 0.6       | 0.85   | 1.25   | 1.7   | 2.5   | 3.3   |

| 00101     | 0.6       | 0.8625 | 1.2625 | 1.725 | 2.525 | 3.325 |

| 00110     | 0.6       | 0.875  | 1.275  | 1.75  | 2.55  | 3.35  |

| 00111     | 0.6       | 0.8875 | 1.2875 | 1.775 | 2.575 | 3.375 |

| 01000     | 0.6       | 0.9    | 1.3    | 1.8   | 2.6   | 3.4   |

| 01001     | 0.6       | 0.9125 | 1.3125 | 1.825 | 2.625 | 3.425 |

| 01010     | 0.6       | 0.925  | 1.325  | 1.85  | 2.65  | 3.45  |

| 01011     | 0.6       | 0.9375 | 1.3375 | 1.875 | 2.675 | 3.475 |

| 01100     | 0.6       | 0.95   | 1.35   | 1.9   | 2.7   | 3.5   |

| 01101     | 0.6       | 0.9625 | 1.3625 | 1.925 | 2.725 | 3.525 |

| 01110     | 0.6       | 0.975  | 1.375  | 1.95  | 2.75  | 3.55  |

| 01111     | 0.6       | 0.9875 | 1.3875 | 1.975 | 2.775 | 3.575 |

| 10000     | 0.6       | 1      | 1.4    | 2     | 2.8   | 3.6   |

| 10001     | 0.6125    | 1.0125 | 1.4125 | 2.025 | 2.825 | 3.625 |

| 10010     | 0.625     | 1.025  | 1.425  | 2.05  | 2.85  | 3.65  |

| 10011     | 0.6375    | 1.0375 | 1.4375 | 2.075 | 2.875 | 3.675 |

| 10100     | 0.65      | 1.05   | 1.45   | 2.1   | 2.9   | 3.7   |

| 10101     | 0.6625    | 1.0625 | 1.4625 | 2.125 | 2.925 | 3.725 |

| 10110     | 0.675     | 1.075  | 1.475  | 2.15  | 2.95  | 3.75  |

| 10111     | 0.6875    | 1.0875 | 1.4875 | 2.175 | 2.975 | 3.775 |

| 11000     | 0.7       | 1.1    | 1.5    | 2.2   | 3     | 3.8   |

Table 2-3. Voltage Codes Definition Bits VSET[7:0] (continued)

| VSET[4:0] | VSET[7:5] |        |        |       |       |     |

|-----------|-----------|--------|--------|-------|-------|-----|

|           | 001       | 010    | 011    | 100   | 101   | 110 |

| 11001     | 0.7125    | 1.1125 | 1.5125 | 2.225 | 3.025 | 3.8 |

| 11010     | 0.725     | 1.125  | 1.525  | 2.25  | 3.05  | 3.8 |

| 11011     | 0.7375    | 1.1375 | 1.5375 | 2.275 | 3.075 | 3.8 |

| 11100     | 0.75      | 1.15   | 1.55   | 2.3   | 3.1   | 3.8 |

| 11101     | 0.7625    | 1.1625 | 1.5625 | 2.325 | 3.125 | 3.8 |

| 11110     | 0.775     | 1.175  | 1.575  | 2.35  | 3.15  | 3.8 |

| 11111     | 0.7875    | 1.1875 | 1.5875 | 2.375 | 3.175 | 3.8 |

Note 1: Truncated to 0.6V.

2: User accessible, 12.5 mV resolution (LDO Controller limited to 1.600V).

3: User accessible, 25 mV resolution.

4: Truncated to 3.800V.

Table 2-4. Power Channels Default Output Voltage Value and State

|                   | Value(V) <sup>(1)</sup>                                                                                   | Factory Default State <sup>(2)</sup>                                                                                                                                                                                                                                                              |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MCP164            | GX1000AA                                                                                                  | •                                                                                                                                                                                                                                                                                                 |  |  |  |

| VDD (Core Supply) | 1.0                                                                                                       | On                                                                                                                                                                                                                                                                                                |  |  |  |

| VDDIx             | 3.3                                                                                                       | On                                                                                                                                                                                                                                                                                                |  |  |  |

| LPDDR4_IO         | 1.1                                                                                                       | On                                                                                                                                                                                                                                                                                                |  |  |  |

| LPDDR4_CORE       | 1.8                                                                                                       | On                                                                                                                                                                                                                                                                                                |  |  |  |

| VDDA25            | 2.5                                                                                                       | On                                                                                                                                                                                                                                                                                                |  |  |  |

| MCP164GX1000AB    |                                                                                                           |                                                                                                                                                                                                                                                                                                   |  |  |  |

| VDD(Core Supply)  | 1.0                                                                                                       | On                                                                                                                                                                                                                                                                                                |  |  |  |

| VDDIx             | 3.3                                                                                                       | On                                                                                                                                                                                                                                                                                                |  |  |  |

| DDR4_IO           | 1.2                                                                                                       | On                                                                                                                                                                                                                                                                                                |  |  |  |

| VDD18             | 1.8                                                                                                       | On                                                                                                                                                                                                                                                                                                |  |  |  |

| VDDA25            | 2.5                                                                                                       | On                                                                                                                                                                                                                                                                                                |  |  |  |

|                   | VDD (Core Supply)  VDDIX  LPDDR4_IO  LPDDR4_CORE  VDDA25  MCP164  VDD(Core Supply)  VDDIX  DDR4_IO  VDD18 | MCP164GX1000AA         VDD (Core Supply)       1.0         VDDIX       3.3         LPDDR4_IO       1.1         LPDDR4_CORE       1.8         VDDA25       2.5         MCP164GX1000AB         VDD(Core Supply)       1.0         VDDIX       3.3         DDR4_IO       1.2         VDD18       1.8 |  |  |  |

#### Notes:

- 1. The default voltage value is programmed identically in both VSET0 and VSET1 registers. MCP164GX1000 PMIC channels will generate the same output voltage regardless of the MODE pin state.

- 2. MCP164GX1000 PMIC remaining channels (BUCK4, BUCK7, BUCK8, LDO1, LDO3, LDO4, LDOC) are programmed to the OFF state by default on power-up.

#### 2.7.2. Switching (Oscillator) Frequency Displacement Programming Bits

The frequency displacement acts on the main oscillator. The switching frequencies of all regulators and all timings are shifted accordingly.

The switching frequency can be adjusted by programing the FSD[1:0] bits. Possible values are presented in Table 2-5.

Table 2-5. Switching Frequency Displacement Bits FSD[1:0]

| FSD[1:0] | Frequency Displacement |

|----------|------------------------|

| 00       | 0%                     |

| 01       | 0%                     |

| 10       | -16.50%                |

|          | • • • • • • • • • • • • • • • • • • • • |

|----------|-----------------------------------------|

| FSD[1:0] | Frequency Displacement                  |

| 11       | +16.50%                                 |

#### 2.7.3. Switching (Oscillator) Phase Displacement Programming Bits

The phase displacement acts on the selected buck regulator, shifting the switching event accordingly.

The switching (oscillator) phase can be adjusted by changing the value of the PHASE[1:0] bits. Possible values are presented in Table 2-6.

**Table 2-6.** Buck Clock Phase Displacement Bits PHASE[1:0]

| PHASE[1:0] | Phase Displacement |

|------------|--------------------|

| 00         | 0°                 |

| 01         | 90°                |

| 10         | 180°               |

| 11         | 270°               |

#### 2.7.4. SYNCO Frequency vs. FREQOUT[2:0] Bits

When an external sync signal is applied, the frequency of the main oscillator can still be adjusted by modifying the value of the FREQOUT[2:0 bits]. Possible values are presented in Table 2-7.

If the ENSYNO bit = 1, the SYNCO pin will output a sub-multiple of the Buck switching frequency (nominally 2 MHz) as follows:

Table 2-7. SYNCO Frequency vs FREQOUT

| FREQOUT[2:0] | Division Factor | SYNCO     | FREQOUT[2:0] Division Factor |    | SYNCO Frequency |

|--------------|-----------------|-----------|------------------------------|----|-----------------|

|              |                 | Frequency |                              |    |                 |

| 000          | :1              | 2 MHz     | 100                          | :5 | 400 kHz         |

| 001          | :2              | 1 MHz     | 101                          | :6 | 333 kHz         |

| 010          | :3              | 667 kHz   | 110                          | :8 | 250 kHz         |

|              |                 |           |                              | :7 | 286 kHz         |

| 011          | :4              | 500 kHz   | 111                          | :8 | 250 kHz         |

#### 2.7.5. SYNCO Output Phase Displacement Bits PHAOUT[1:0]

When an external sync signal is applied, the phase of the main oscillator can still be adjusted by modifying the value of the PHAOUT[1:0] bits. Possible values are presented in Table 2-8.

Table 2-8. Phase Displacement Bits PHAOUT

| PHAOUT[1:0] | Phase Displacement |

|-------------|--------------------|

| 00          | 0°                 |

| 01          | 90°                |

| 10          | 180°               |

| 11          | 270°               |

#### 2.7.6. nRSTO P / nRSTO A Deassertion Delays Bits nRPDLY[3:0] and nRADLY[3:0]

The deassertion delays for the pins nRSTO\_P/nRSTO\_A can be adjusted by modifying the value of the nRPDLY[3:0] and nRADLY[3:0] bits. Possible values are presented in Table 2-9.

Table 2-9. nRSTO\_A/nRSTO\_P Deassertion Delay Bits

| nRPDLY[3:0] | nRSTO_P Deassertion Delay<br>(ms) | nRADLY[3:0] | nRSTO_A Deassertion Delay<br>(ms) |

|-------------|-----------------------------------|-------------|-----------------------------------|

| 0000        | 0                                 | 0000        | 0                                 |

| 0001        | 0.25                              | 0001        | 0.25                              |

| 0010        | 0.5                               | 0010        | 0.5                               |

| 0011        | 0.75                              | 0011        | 0.75                              |

| 0100        | 1                                 | 0100        | 1                                 |

| 0101        | 1.5                               | 0101        | 1.5                               |

| 0110        | 2                                 | 0110        | 2                                 |

| 0111        | 3                                 | 0111        | 3                                 |

| 1000        | 4                                 | 1000        | 4                                 |

| 1001        | 5                                 | 1001        | 5                                 |

| 1010        | 6                                 | 1010        | 6                                 |

| 1011        | 8                                 | 1011        | 8                                 |

| 1100        | 16                                | 1100        | 16                                |

| 1101        | 32                                | 1101        | 32                                |

| 1110        | 64                                | 1110        | 64                                |

| 1111        | 128                               | 1111        | 128                               |

## 2.7.7. EN Transitions Debouncing Delays Bits ENDBNR[2:0] and ENDBNF[2:0]

The ENDBNR[2:0] bits define the debounce time for the LOW-to-HIGH (rising) edge (or initial HIGH status upon AVCC and VDD UVLO release), and the ENDBNF[2:0] bits define the debounce time for the HIGH-to-LOW (falling) edge. Possible values are presented in Table 2-10.

Table 2-10. EN Debouncing Delay Bits

| ENDBNR[2:0] | Delay (ms) | ENDBNF[2:0] | Delay (ms) |

|-------------|------------|-------------|------------|

| 000         | 0          | 000         | 0          |

| 001         | 0.5        | 001         | 0.5        |

| 010         | 1          | 010         | 1          |

| 011         | 2          | 011         | 2          |

| 100         | 4          | 100         | 4          |

| 101         | 8          | 101         | 8          |

| 110         | 16         | 110         | 16         |

| 111         | 32         | 111         | 32         |

#### 2.7.8. Turn-On Sequence Step Assignment Bits ONSEQ[1:0]

Sequence steps are defined by the ONSEQ[1:0] bits. Possible values are presented in Table 2-11.

Table 2-11. Turn-On Sequence Steps ONSEQ

| ONSEQ[1:0] | Turn-On Sequence Step |

|------------|-----------------------|

| 00         | 1                     |

| 01         | 2                     |

| 10         | 3                     |

| 11         | 4                     |

#### 2.7.9. Turn-On Sequence Step Delay Bits ONDLY[3:0]

Turn-on delays within each sequence step are defined by the ONDLY[3:0] bits. Possible values are presented in Table 2-12.

Table 2-12. Turn-On Sequence Delay Bits ONDLY

| ONDLY[3:0] | Delay (ms) | ONDLY[3:0] | Delay (ms) |

|------------|------------|------------|------------|

| 0000       | 0          | 1000       | 6          |

| 0001       | 0.5        | 1001       | 8          |

| 0010       | 1          | 1010       | 10         |

| 0011       | 1.5        | 1011       | 12         |

| 0100       | 2          | 1100       | 14         |

| 0101       | 3          | 1101       | 16         |

| 0110       | 4          | 1110       | 18         |

| 0111       | 5          | 1111       | 20         |

## 2.7.10. Turn-Off Sequence Step Delay Bits OFFDLY[5:0]

All channels are turned off (upon deassertion of EN and debouncing) based only on their OFFDLY[5:0] bits. The OFFDLY[5:0] delay marks the beginning of the Immediate OFF. Possible values are presented in Table 2-13.

Table 2-13. Turn-Off Sequence Delay Bits OFFDLY

| OFFDLY[5:0] | Delay (ms) |

|-------------|------------|-------------|------------|-------------|------------|-------------|------------|

| 000000      | 0          | 010000      | 8          | 100000      | 38         | 110000      | 70         |

| 000001      | 0.2        | 010001      | 9          | 100001      | 40         | 110001      | 72         |

| 000010      | 0.4        | 010010      | 10         | 100010      | 42         | 110010      | 74         |

| 000011      | 0.6        | 010011      | 12         | 100011      | 44         | 110011      | 76         |

| 000100      | 0.8        | 010100      | 14         | 100100      | 46         | 110100      | 78         |

| 000101      | 1          | 010101      | 16         | 100101      | 48         | 110101      | 80         |

| 000110      | 1.5        | 010110      | 18         | 100110      | 50         | 110110      | 82         |

| 000111      | 2          | 010111      | 20         | 100111      | 52         | 110111      | 84         |

| 001000      | 2.5        | 011000      | 22         | 101000      | 54         | 111000      | 86         |

| 001001      | 3          | 011001      | 24         | 101001      | 56         | 111001      | 88         |

| 001010      | 3.5        | 011010      | 26         | 101010      | 58         | 111010      | 90         |

| 001011      | 4          | 011011      | 28         | 101011      | 60         | 111011      | 92         |

| 001100      | 4.5        | 011100      | 30         | 101100      | 62         | 111100      | 94         |

| 001101      | 5          | 011101      | 32         | 101101      | 64         | 111101      | 96         |

| 001110      | 6          | 011110      | 34         | 101110      | 66         | 111110      | 98         |

| 001111      | 7          | 011111      | 36         | 101111      | 68         | 111111      | 100        |

#### 2.7.11. Power-Down Delay Programming PDENDLY[2:0]