Data Sheet April 2019

# *Microsemi. MAX24605, MAX24610* 5- or 10-Output Any-to-Any Clock Multiplier / Jitter Attenuator ICs

# **General Description**

The MAX24605 and MAX24610 are flexible, highperformance clock multiplier and jitter attenuator ICs that include a DPLL and two independent APLLs. When locked to one of two input clock signals, the device performs any-to-any frequency conversion. From any input clock frequency 2kHz to 750MHz the device can produce frequency-locked APLL output frequencies up to 750MHz and as many as 10 output clock signals that are integer divisors of the APLL frequencies. Input jitter can be attenuated by an internal low-bandwidth DPLL. The DPLL also provides glitchless switching between input clocks and numerically controlled oscillator capability. Input switching can be manual or automatic. Using only a low-cost crystal or oscillator, the device can also serve as a frequency synthesizer IC. Output jitter is typically 0.18 to 0.3ps RMS for an APLL-only integer multiply and 0.25 to 0.4ps RMS for APLL-only fractional multiply or DPLL+APLL operation.

# **Applications**

Jitter attenuation, frequency conversion and frequency synthesis applications in a wide variety of equipment types

# **Ordering Information**

| PART         | OUTPUTS | TEMP<br>RANGE | PIN-<br>PACKAGE |

|--------------|---------|---------------|-----------------|

| MAX24605EXG2 | 5       | -40 to +85    | 81-CSBGA        |

| MAX24610EXG2 | 10      | -40 to +85    | 81-CSBGA        |

Suffix 2 denotes a lead(Pb)-free/RoHS-compliant package.

Block Diagram appears on page 6. Register Map appears on page 37.

### Input Clocks

- One Crystal Input

- Two Differential or CMOS/TTL Inputs

- Differential to 750MHz, CMOS/TTL to 160MHz

- Continuous Input Clock Quality Monitoring

- Automatic or Manual Clock Selection

- Glitchless Reference Switching

- Low-Bandwidth DPLL

- Programmable Bandwidth, 4Hz to 400Hz

- Attenuates Input Jitter up to Several UI

- Manual Phase Adjustment

- Two APLLs Plus 5 or 10 Output Clocks

- APLLs Perform High Resolution Fractional-N Clock Multiplication

- ♦ Any Output Frequency from <1Hz to 750MHz

- Each Output Has an Independent Divider

- Output Jitter Typically 0.18 to 0.3ps RMS for APLL-Only Integer Multiply and 0.25 to 0.4ps RMS for Other Modes (12kHz to 20MHz)

- Outputs are CML or 2xCMOS, Can Interface to LVDS, LVPECL, HSTL, SSTL and HCSL

- CMOS Output Voltage from 1.5V to 3.3V

- General Features

- Automatic Self-Configuration at Power-Up from External EEPROM Memory

- Uses External Crystal, Oscillator or Clock Signal As Master Clock

- Internal Compensation for Local Oscillator Frequency Error

- SPI Processor Interface

- 1.8V + 3.3V Operation (5V Tolerant)

- -40 to +85°C Operating Temp. Range

- 10mm x 10mm CSBGA Package

# Features

# Table of Contents

| 1.  | APPLICATION EXAMPLES                                                                                      | . 6 |

|-----|-----------------------------------------------------------------------------------------------------------|-----|

| 2.  | BLOCK DIAGRAM                                                                                             | . 6 |

| 3.  | DETAILED FEATURES                                                                                         | . 6 |

| 3.1 | INPUT BLOCK FEATURES                                                                                      | 6   |

| 3.2 | DPLL FEATURES                                                                                             | . 7 |

| 3.3 | APLL FEATURES                                                                                             | 7   |

| 3.4 | OUTPUT CLOCK FEATURES                                                                                     | . 7 |

| 3.5 | GENERAL FEATURES                                                                                          | 7   |

| 4.  | PIN DESCRIPTIONS                                                                                          | 8   |

| 5.  | FUNCTIONAL DESCRIPTION                                                                                    | .11 |

| 5.1 | Device Identification and Protection                                                                      | .11 |

| 5.2 | TOP-LEVEL CONFIGURATION                                                                                   |     |

| 5.  | 2.1 APLL-Only Mode                                                                                        |     |

| 5.  | 2.2 DPLL+APLL Mode                                                                                        |     |

| 5.3 | LOCAL OSCILLATOR AND MASTER CLOCK CONFIGURATION                                                           | .14 |

| 5.  | 3.1 External Oscillator                                                                                   |     |

|     | 5.3.1.1 Oscillator Characteristics to Minimize Output Jitter                                              | 14  |

|     | 3.2 On-Chip Crystal Oscillator                                                                            |     |

|     | 3.3 Master Clock APLL Configuration                                                                       |     |

| 5.4 |                                                                                                           |     |

| 5.5 | INPUT CLOCK DIVIDER, MONITOR AND SELECTOR                                                                 |     |

|     | 5.1 Input Clock Frequency Dividers, Scaling and Inversion                                                 |     |

| 5.  | 5.2 Input Clock Monitoring                                                                                |     |

|     | 5.5.2.1 Frequency Monitoring                                                                              |     |

|     | <ul><li>5.5.2.2 Activity Monitoring</li><li>5.5.2.3 Selected Reference Fast Activity Monitoring</li></ul> |     |

|     | 5.5.2.4 External Monitoring                                                                               |     |

| 5   | 5.3 Input Clock Priority, Selection and Switching                                                         |     |

| 0.  | 5.5.3.1 Priority Configuration                                                                            |     |

|     | 5.5.3.2 Automatic Selection                                                                               |     |

|     | 5.5.3.3 Forced Selection                                                                                  |     |

|     | 5.5.3.4 Ultra-Fast Reference Switching                                                                    | 21  |

|     | 5.5.3.5 External Reference Switching Mode                                                                 | 21  |

|     | 5.5.3.6 Output Clock Phase Continuity During Reference Switching                                          | 22  |

| 5.6 | DPLL ARCHITECTURE AND CONFIGURATION                                                                       | .22 |

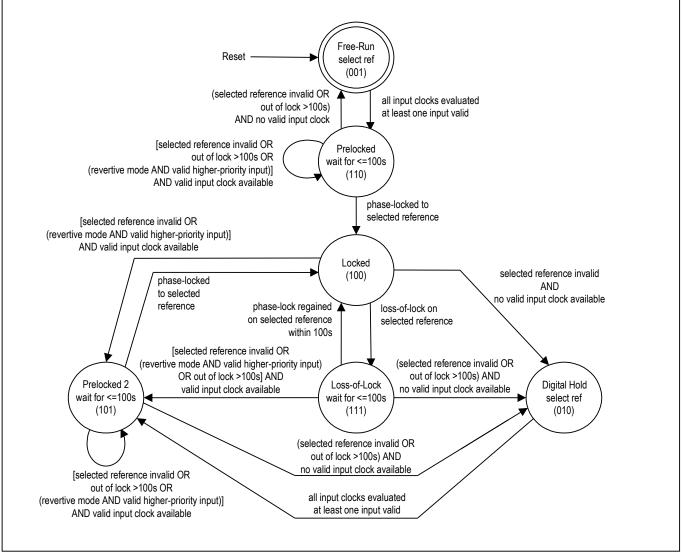

|     | 6.1 DPLL State Machine                                                                                    |     |

|     | 5.6.1.1 Free-Run State                                                                                    |     |

|     | 5.6.1.2 Prelocked State                                                                                   |     |

|     | 5.6.1.3 Locked State                                                                                      |     |

|     |                                                                                                           |     |

|     | 5.6.1.5 Prelocked 2 State                                                                                 |     |

| 5   | 5.6.1.6 Digital Hold State                                                                                |     |

|     | <ul><li>6.2 Bandwidth</li><li>6.3 Damping Factor</li></ul>                                                |     |

|     | 6.4 Phase Detectors                                                                                       |     |

|     | 6.5 Loss of Phase Lock Detection                                                                          |     |

|     | 6.6 Manual Phase Adjustment                                                                               |     |

|     | 6.7 Frequency and Phase Measurement                                                                       |     |

|     | 6.8 Input Wander and Jitter Tolerance                                                                     |     |

|     | 6.9 Jitter and Wander Transfer                                                                            |     |

|     |                                                                                                           |     |

🛇 Microsemi.

|            | .6.10 Output Jitter and Wander                                          |     |

|------------|-------------------------------------------------------------------------|-----|

|            | .6.11 ±160ppm Tracking Range Mode                                       |     |

| 5.7        |                                                                         |     |

| 5.         | 7.1 Input Selection and Frequency                                       |     |

|            | 5.7.1.1         APLL-Only Mode           5.7.1.2         DPLL+APLL Mode |     |

| 5          | 5.7.1.2 DPLL+APLL Mode                                                  |     |

| 5.8        |                                                                         |     |

|            | .8.1 Enable, Signal Format, Voltage and Interfacing                     |     |

|            | 8.2 Frequency Configuration                                             |     |

|            | .8.3 Phase Adjustment                                                   |     |

| 5.9        |                                                                         |     |

| 5.10       |                                                                         |     |

| 5.11       |                                                                         |     |

| 5.12       |                                                                         |     |

| 6.         | REGISTER DESCRIPTIONS                                                   |     |

| -          |                                                                         |     |

| 6.1        |                                                                         |     |

|            | .1.1 Status Bits                                                        |     |

|            | .1.2 Configuration Fields                                               |     |

|            | .1.3 Bank-Switched Registers                                            |     |

|            | 1.4 Multiregister Fields                                                |     |

| 6.2        |                                                                         |     |

| 6.3        |                                                                         |     |

|            | .3.1 Global Registers                                                   |     |

|            | .3.2 GPIO Registers                                                     |     |

|            | .3.3 APLL Registers                                                     |     |

| 6.         | .3.4 Output Clock Registers                                             |     |

| 6.         | .3.5 Input Clock Registers                                              | 57  |

|            | .3.6 DPLL Registers                                                     |     |

| <u>6</u> . | .3.7 DPLL and Input Block Status Registers                              | 88  |

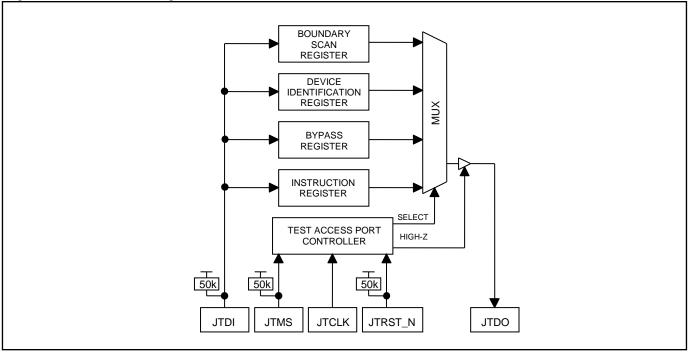

| 7.         | JTAG AND BOUNDARY SCAN                                                  | 92  |

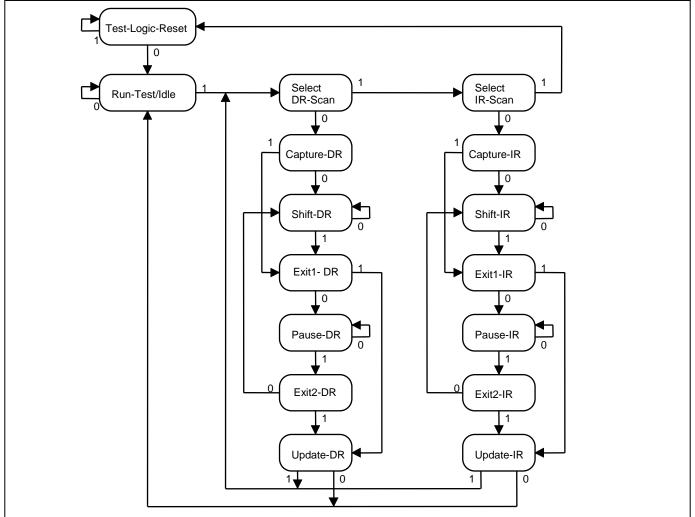

| 7.1        | JTAG DESCRIPTION                                                        | 92  |

| 7.2        |                                                                         |     |

| 7.3        |                                                                         |     |

| 7.4        |                                                                         |     |

|            |                                                                         |     |

| 8.         | ELECTRICAL CHARACTERISTICS                                              | 97  |

| 9.         | PIN ASSIGNMENTS                                                         |     |

| 9.1        |                                                                         |     |

| 9.1        |                                                                         |     |

| -          |                                                                         |     |

| 10.        | PACKAGE AND THERMAL INFORMATION                                         | 111 |

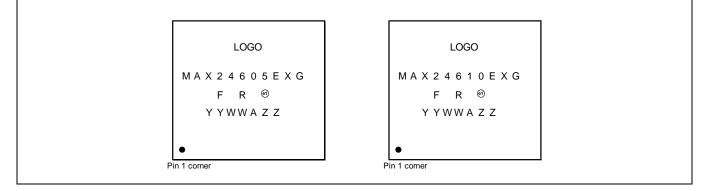

| 10.1       | 1 PACKAGE TOP MARK FORMAT                                               | 111 |

| 10.2       |                                                                         |     |

| 11.        | ACRONYMS AND ABBREVIATIONS                                              | 113 |

| 12.        | DATA SHEET REVISION HISTORY                                             |     |

| 14.        |                                                                         |     |

# List of Figures

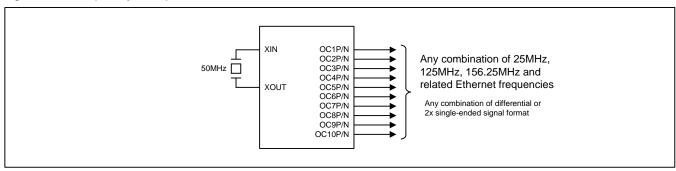

| Figure 1-1. Frequency Multiplication and Fanout of Ethernet Clocks                               | 6   |

|--------------------------------------------------------------------------------------------------|-----|

| Figure 2-1. Block Diagram                                                                        |     |

| Figure 5-1. APLL-Only Mode: Clock Synthesis from a Crystal                                       |     |

| Figure 5-2. APLL-Only Mode: Locked to One of Four Input Clocks                                   | 12  |

| Figure 5-3. DPLL+APLL Mode: Method 1, Master Clock from High-Speed External Oscillator           | 13  |

| Figure 5-4. DPLL+APLL Mode: Method 2a, Master Clock from Crystal Oscillator Multiplied by APLL2  | 13  |

| Figure 5-5. DPLL+APLL Mode: Method 2b, Master Clock from External Oscillator Multiplied by APLL2 | 14  |

| Figure 5-6. Crystal Equivalent Circuit / Crystal and Capacitor Connections                       | 15  |

| Figure 5-7. Input block Diagram                                                                  | 17  |

| Figure 5-8. DPLL Block Diagram                                                                   |     |

| Figure 5-9. DPLL State Transition Diagram                                                        | 23  |

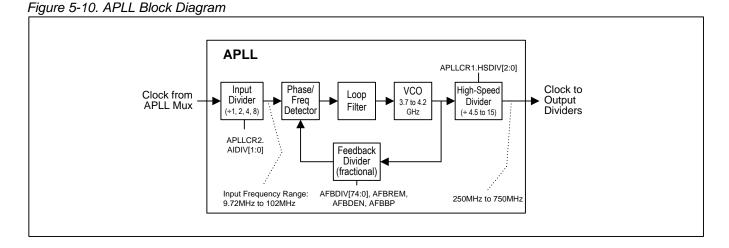

| Figure 5-10. APLL Block Diagram                                                                  | 29  |

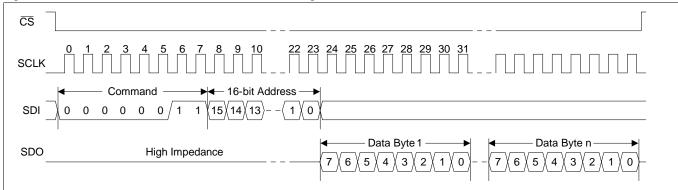

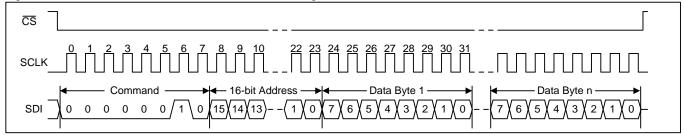

| Figure 5-11. SPI Read Transaction Functional Timing                                              | 33  |

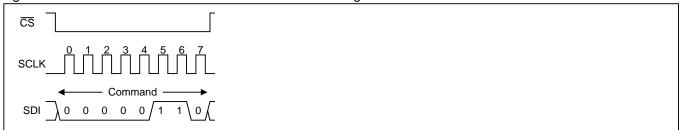

| Figure 5-12. SPI Write Enable Transaction Functional Timing                                      | 33  |

| Figure 5-13. SPI Write Transaction Functional Timing                                             | 33  |

| Figure 7-1. JTAG Block Diagram                                                                   | 92  |

| Figure 7-2. JTAG TAP Controller State Machine                                                    | 94  |

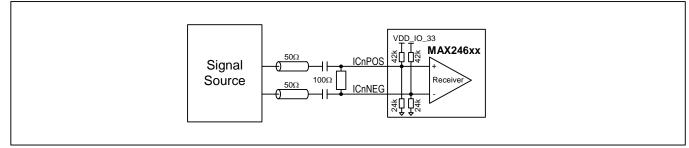

| Figure 8-1. Recommended External Components for Interfacing to Differential Inputs               |     |

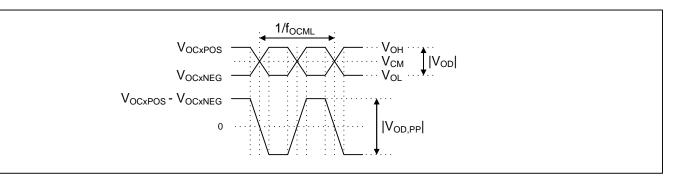

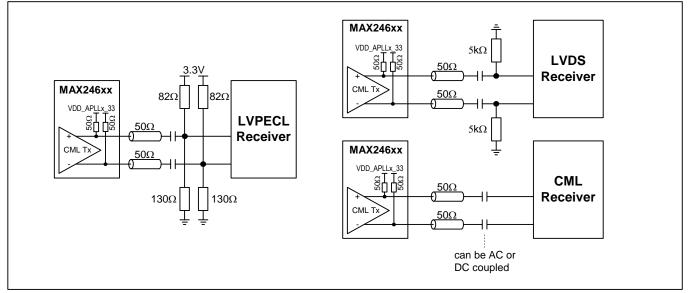

| Figure 8-2. Recommended External Components for Interfacing to CML Outputs                       |     |

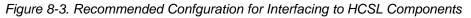

| Figure 8-3. Recommended Confguration for Interfacing to HCSL Components                          | 102 |

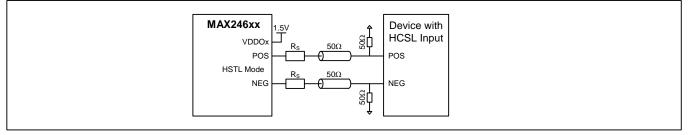

| Figure 8-4. SPI Interface Timing Diagram                                                         |     |

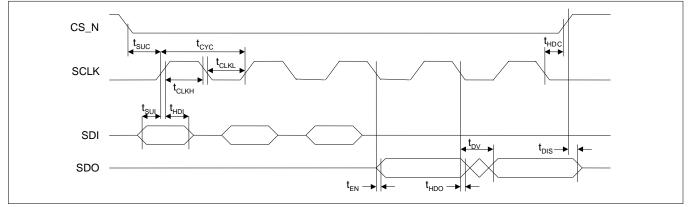

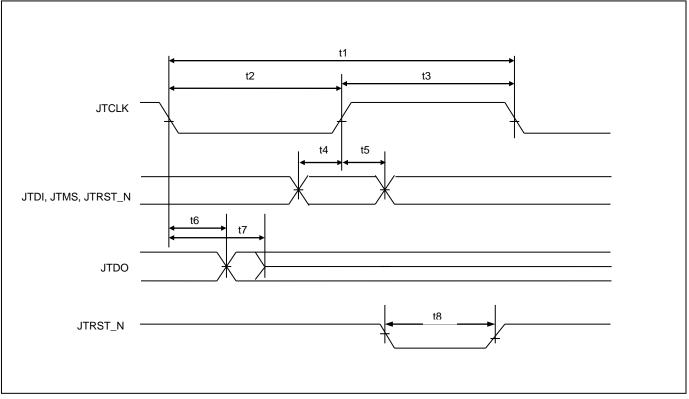

| Figure 8-5. JTAG Timing Diagram                                                                  |     |

| Figure 9-1. MAX24605 Pin Assignment Diagram                                                      | 108 |

| Figure 9-2. MAX24610 Pin Assignment Diagram                                                      |     |

| Figure 10-1. Device Top Mark                                                                     | 111 |

# List of Tables

| Table 4-1. Input Clock Pin Descriptions                                              |      |

|--------------------------------------------------------------------------------------|------|

| Table 4-2. Output Clock Pin Descriptions                                             | 8    |

| Table 4-3. Global Pin Descriptions                                                   | 8    |

| Table 4-4. SPI Interface Pin Descriptions                                            | 9    |

| Table 4-5. External EEPROM SPI Interface Pin Descriptions                            | 9    |

| Table 4-6. JTAG Interface Pin Descriptions                                           | 9    |

| Table 4-7. Power-Supply Pin Descriptions                                             | . 10 |

| Table 5-1. Crystal Selection Parameters                                              | . 15 |

| Table 5-2. Example Master Clock APLL Input Frequencies and Configurations            | . 16 |

| Table 5-3. Input Clock Capabilities                                                  | . 17 |

| Table 5-4. Activity Monitoring, Missing Clock Cycles vs. Frequency                   | . 19 |

| Table 5-5. Default Input Clock Priorities                                            | . 20 |

| Table 5-6. Damping Factors and Peak Jitter/Wander Gain                               | . 25 |

| Table 6-1. Register Map                                                              | . 37 |

| Table 7-1. JTAG Instruction Codes                                                    | . 95 |

| Table 7-2. JTAG ID Code                                                              | . 96 |

| Table 8-1. Recommended DC Operating Conditions                                       | . 97 |

| Table 8-2. Electrical Characteristics: Supply Currents                               | . 97 |

| Table 8-3. Electrical Characteristics: Non-Clock CMOS/TTL Pins                       | . 98 |

| Table 8-4. Electrical Characteristics: Clock Inputs                                  |      |

| Table 8-5. Electrical Characteristics: CML Clock Outputs                             |      |

| Table 8-6. Electrical Characteristics: CMOS and HSTL (Class I) Clock Outputs         | 101  |

| Table 8-7. Electrical Characteristics: Clock Output Timing                           |      |

| Table 8-8. Electrical Characteristics: Jitter Specifications                         | 102  |

| Table 8-9. Electrical Characteristics: Typical Output Jitter Performance, APLL Only  | 103  |

| Table 8-10. Electrical Characteristics: Typical Output Jitter Performance, DPLL+APLL | 103  |

| Table 8-11. Electrical Characteristics: Typical Input-to-Output Clock Delay          |      |

| Table 8-12. Electrical Characteristics: Typical Output-to-Output Clock Delay         | 104  |

| Table 8-13. Electrical Characteristics: SPI Interface Timing                         | 105  |

| Table 8-14. Electrical Characteristics: External EEPROM SPI Interface Timing         | 105  |

| Table 8-15. Electrical Characteristics: JTAG Interface Timing                        | 106  |

| Table 9-1. MAX24605 Pin Assignments Sorted by Signal Name                            | 107  |

| Table 9-2. MAX24610 Pin Assignments Sorted by Signal Name                            | 109  |

| Table 10-1. Package Top Mark Legend                                                  | 111  |

| Table 10-1. CSBGA Package Thermal Properties                                         | 112  |

# 1. Application Examples

Figure 1-1. Frequency Multiplication and Fanout of Ethernet Clocks

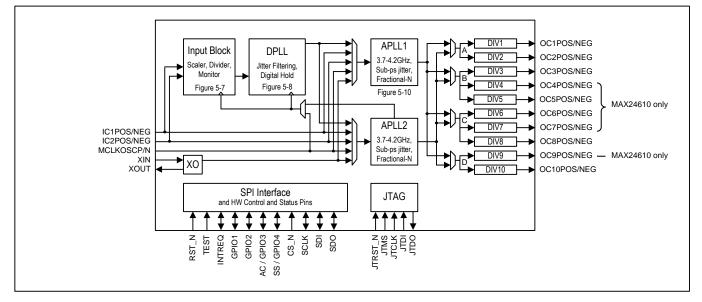

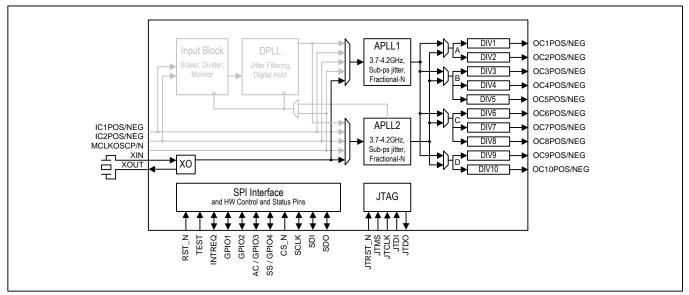

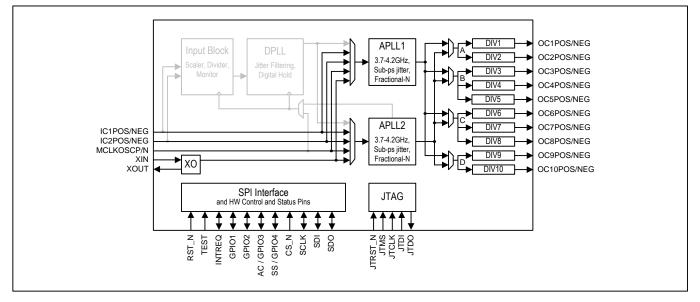

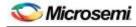

# 2. Block Diagram

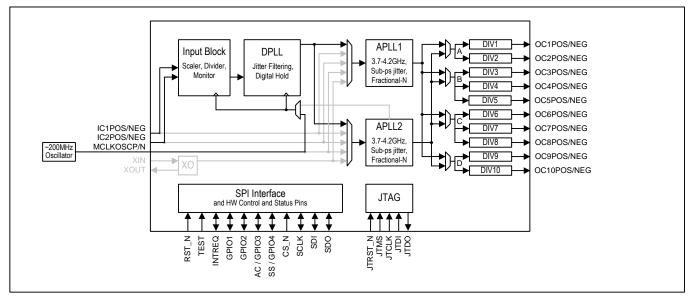

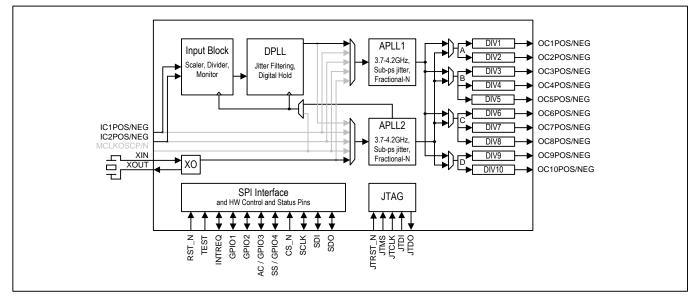

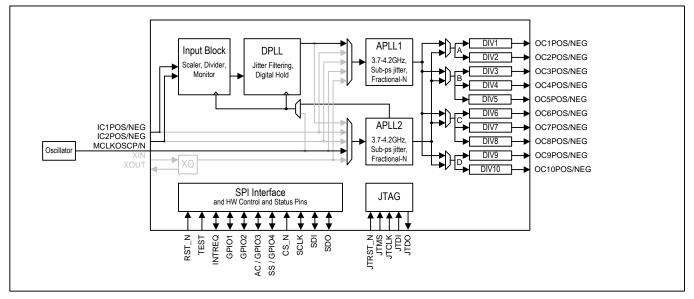

#### Figure 2-1. Block Diagram

# 3. Detailed Features

# 3.1 Input Block Features

- Two input clocks, differential or CMOS/TTL signal format

- Input clocks can be any frequency from 2kHz up to 750MHz

- Per-input fractional scaling (i.e. multiplying by N÷D where N is a 16-bit integer and D is a 32-bit integer and N<D) to undo 64B/66B and FEC scaling (e.g. 64/66, 238/255, 237/255, 236/255)</li>

- All inputs constantly monitored by programmable activity monitors and frequency monitors

- · Fast activity monitor can disqualify the selected reference after a few missing clock cycles

- Frequency measurement with 1.25ppm resolution

- Frequency monitor thresholds with 1.25ppm or 5ppb resolution

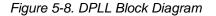

# 3.2 **DPLL Features**

- Very high-resolution DPLL architecture

- Sophisticated state machine automatically transitions between free-run, locked, and digital hold states

- Revertive or nonrevertive reference selection algorithm

- Programmable bandwidth from 4Hz to 400Hz

- Separately configurable acquisition bandwidth and locked bandwidth

- Programmable damping factor to balance lock time with peaking: 1.2, 2.5, 5, 10 or 20

- Multiple phase detectors: phase/frequency and multicycle

- Phase/frequency locking (±360° capture) or nearest-edge phase locking (±180° capture)

- Multicycle phase detection and locking (up to ±8191UI) improves jitter tolerance and lock time

- Output phase adjustment up to ±200ns in 6ps steps with respect to selected input reference

- High-resolution frequency and phase measurement

- Numerically controlled oscillator (NCO) mode allows system software to steer DPLL frequency

# 3.3 APLL Features

- Two independent APLLs simultaneously product two frequency families from the same reference clock or different reference clocks

- Very high-resolution fractional scaling (i.e. non-integer multiplication)

- Output jitter is typically 0.18 to 0.3ps RMS for APLL-only integer multiply and 0.25 to 0.4ps RMS for APLL-only fractional multiply or DPLL+APLL operation (12kHz to 20MHz integration band, for output frequencies >100MHz)

- Bypass mode for each APLL supports system testing and allows device to be used in fanout applications

# 3.4 Output Clock Features

- Ten low-jitter output clocks

- Each output can be one differential output or two CMOS/TTL outputs

- Outputs easily interface with CML, LVDS, LVPECL, HSTL, SSTL, HCSL components

- Each output can be any integer divisor of either APLL output clock

- Can produce clock frequencies for microprocessors, ASICs, FPGAs and other components

- Can produce PCIe-compliant output clocks (PCIe gen. 1, 2 and 3)

- Per-output delay adjustment

- Per-output enable/disable

# 3.5 General Features

- SPI serial microprocessor interface

- Optional automatic self-configuration at power-up from external EEPROM memory

- Four general-purpose I/O pins

- Register set can be write-protected

- Can operate as DPLL+APLL for jitter filtering or as APLL only

- Local oscillator can be nearly any frequency from 10MHz to 750MHz

- Internal compensation for local oscillator frequency error

# 4. Pin Descriptions

| PIN NAME              | <b>TYPE</b> <sup>(1)</sup> | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IC1POS, IC1NEG        | Idiff                      | Input Clocks 1 and 2.<br>Differential or CMOS/TTL signal format. Programmable frequency.<br>Differential: See Table 8-4 for electrical specifications, and see Figure 8-1 for<br>recommended external circuitry for interfacing these differential inputs to LVDS,<br>LVPECL or CML output pins on other devices.<br>CMOS/TTL: Connect the single-ended signal to the POS pin. Connect the NEG pin to a                                                                                                                                                                                                                                                                                                                                                                   |

| IC2POS, IC2NEG        |                            | capacitor $(0.1\mu F \text{ or } 0.01\mu F)$ to VSS_IO. As shown in Figure 8-1, the NEG pin is internally biased to approximately 1.2V. Treat the NEG pin as a sensitive node; minimize stubs; do not connect to anything else including other NEG pins.<br>Unused: The POS and NEG pins can be left floating. Set ICCR1.ICEN=0.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| XIN                   | I                          | <b>Crystal Oscillator Input.</b><br>An on-chip XO circuit is designed to work with an external crystal connected to the XIN and XOUT pins. See section 5.3.2 for crystal characteristics and recommended external components. Alternately, the on-chip XO circuit can be disabled, and XIN can be used as a single-ended input clock pin that can accept a clock signal amplitude from 1.8V to 3.3V.                                                                                                                                                                                                                                                                                                                                                                      |

| хоит                  | 0                          | <b>Crystal Oscillator Output.</b><br>See section 5.3.2 for crystal characteristics and recommended external components.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MCLKOSCP,<br>MCLKOSCN | Idiff                      | <ul> <li>Master Clock Oscillator.</li> <li>These pins can be used to connect the device to a local oscillator (XO, TCXO, OCXO).</li> <li>The oscillator can be any of a range of frequencies. See section 5.3.</li> <li>Differential: See Table 8-4 for electrical specifications, and see Figure 8-1 for recommended external circuitry for interfacing these differential inputs to LVDS, LVPECL or CML output pins on other devices.</li> <li>CMOS/TTL: Connect the single-ended signal to the MCLKOSCP pin. Connect the MCLKOSCN pin to a capacitor (0.1µF or 0.01µF) to VSS_IO. As shown in Figure 8-1, the MCLKOSCN pin is internally biased to approximately 1.2V. Treat MCLKOSCN as a sensitive node; minimize stubs; do not connect to anything else.</li> </ul> |

# Table 4-2. Output Clock Pin Descriptions

| PIN NAME                                                                                                                                                                           | <b>TYPE</b> <sup>(1)</sup> | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OC1POS, OC1NEG<br>OC2POS, OC2NEG<br>OC3POS, OC3NEG<br>OC4POS, OC4NEG<br>OC5POS, OC5NEG<br>OC6POS, OC6NEG<br>OC7POS, OC7NEG<br>OC8POS, OC8NEG<br>OC9POS, OC9NEG<br>OC10POS, OC10NEG | Odiff                      | Differential Output Clocks 1 through 10.<br>CML, HSTL or 1 or 2 CMOS. Programmable frequency.<br>See Table 8-5 and Figure 8-2 for electrical specifications and recommended external<br>circuitry for interfacing to LVDS, LVPECL or CML input pins on other devices.<br>See Table 8-6 for electrical specifications for interfacing to CMOS and HSTL inputs on<br>other devices.<br>See Figure 8-3 for recommended external circuitry for interfacing to HCSL inputs on<br>other devices. |

# Table 4-3. Global Pin Descriptions

| PIN NAME | <b>TYPE</b> <sup>(1)</sup> | PIN DESCRIPTION                                                                                                                                                                                                                    |

|----------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RST_N    | IPU                        | <b>Reset (Active Low).</b> When this global asynchronous reset is pulled low, all internal circuitry is reset to default values. The device is held in reset as long as RST_N is low. RST_N should be held low for at least 100ns. |

| TEST     | I <sub>PD</sub>            | Factory Test Mode Select. Wire this pin to VSS for normal operation.                                                                                                                                                               |

| GPIO1    | I/O <sub>PU</sub>          | General-Purpose I/O Pin 1.<br>GPCR.GPIO1C configures this pin. Its state is indicated in GPSR.GPIO1.                                                                                                                               |

| PIN NAME   | <b>TYPE</b> <sup>(1)</sup> | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO2      | I/O <sub>PD</sub>          | General-Purpose I/O Pin 2.<br>GPCR.GPIO2C configures this pin. Its state is indicated in GPSR.GPIO2.                                                                                                                                                                                                                                                                                                                                                        |

| AC / GPIO3 | I/O <sub>PU</sub>          | Auto Configuration / General-Purpose I/O Pin 3.<br>If this pin is high when RST_N goes high the device automatically configures its<br>registers based on the configuration script stored in external EEPROM memory. See<br>section 5.12. After reset GPCR.GPIO3C configures this pin. Its state is indicated in<br>GPSR.GPIO3.                                                                                                                             |

| SS / GPIO4 | I/O <sub>PD</sub>          | <b>Source Switch / General-Purpose I/O Pin 4.</b><br>When DPLLCR1.EXTSW=1 this pin behaves as SS, the source-switching control input<br>for the input block and DPLL (see section 5.5.3.5). When APLLCR2.EXTSW=1 this pin<br>behaves as SS, the sources-switching control input for one or both APLLs. When<br>DPLLCR1.EXTSW=0 and APLLCR2.EXTSW=0 this pin behaves as GPIO4, it is<br>configured by GPCR.GPIO4C, and its state is indicated in GPSR.GPIO4. |

# Table 4-4. SPI Interface Pin Descriptions

See section 5.9 for functional description and Table 8-13 for timing specifications.

| PIN NAME | <b>TYPE</b> <sup>(1)</sup> | PIN DESCRIPTION                                                                                                                                                                                                               |

|----------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS_N     | I                          | <b>Chip Select.</b> The CS_N, SCLK, SDI and SDO pins together are a SPI slave port through which an external SPI master can communicate with the device. This pin must be asserted (low) to read or write internal registers. |

| SCLK     | I                          | Serial Clock. SCLK is always driven by the SPI bus master.                                                                                                                                                                    |

| SDI      | I                          | Serial Data Input. The SPI bus master transmits data to the device on this pin.                                                                                                                                               |

| SDO      | O <sub>3</sub>             | Serial Data Output. The device transmits data to the SPI bus master on this pin.                                                                                                                                              |

# Table 4-5. External EEPROM SPI Interface Pin Descriptions

See section 5.12 for functional description and Table 8-14 for timing specifications.

| ECS_N | O <sub>3</sub> | <b>External EEPROM Chip Select.</b> The ECS_N, ESCLK, ESDI and ESDO pins together are a SPI master port which can be connected to an external SPI EEPROM device. The device can automatically self-configure from data in the EEPROM at power-up and reset. When the device is reading configuration information from the EEPROM it asserts ECS_N. When the device's SPI master accesses the EEPROM (i.e. when the EESEL bit is set to 1 and CS_N is asserted), ECS_N is a buffered (delayed) version of CS_N. |

|-------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ESCLK | O <sub>3</sub> | <b>External EEPROM Serial Clock.</b> This pin can be connected to the SCLK pin of an external SPI EEPROM. When the device is reading configuration information from the EEPROM it drives a clock signal on ESCLK. When the device's SPI master accesses the EEPROM (i.e. when the <b>EESEL</b> bit is set to 1 and CS_N is asserted), ESCLK is a buffered (delayed) version of SCLK.                                                                                                                           |

| ESDI  | O <sub>3</sub> | <b>External EEPROM Serial Data Input.</b> This pin can be connected to the serial data input pin of an external SPI EEPROM. When the device is reading configuration information from the EEPROM it controls ESDI as needed. When the device's SPI master accesses the EEPROM (i.e. when the EESEL bit is set to 1 and CS_N is asserted), ESDI is a buffered (delayed) version of SDI.                                                                                                                         |

| ESDO  | I              | <b>External EEPROM Serial Data Output.</b> This pin can be connected to the serial data output of the external SPI EEPROM. When the device is reading configuration information from the EEPROM, the data is conveyed on the ESDO pin. When the device's SPI master reads the EEPROM (i.e. when the EESEL bit is set to 1 and CS_N is asserted), the SDO pin is a buffered (delayed) version of ESDO.                                                                                                          |

# Table 4-6. JTAG Interface Pin Descriptions

See Section 7 for functional description and Table 8-15 for timing specifications.

| PIN NAME | TYPE <sup>(1)</sup> | PIN DESCRIPTION                                                                                                                                                                                                   |

|----------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTRST_N  | lpu                 | <b>JTAG Test Reset (Active Low).</b> Asynchronously resets the test access port (TAP) controller. JTRST_N should be held low during device power-up. If not used, JTRST_N can be held low or high after power-up. |

| JTCLK    | Ι                   | <b>JTAG Clock.</b> Shifts data into JTDI on the rising edge and out of JTDO on the falling edge. If not used, JTCLK can be held low or high.                                                                      |

| PIN NAME | <b>TYPE</b> <sup>(1)</sup> | PIN DESCRIPTION                                                                                                                                                                             |  |

|----------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| JTDI     | IPU                        | <b>JTAG Test Data Input.</b> Test instructions and data are clocked in on this pin on the rising edge of JTCLK. If not used, JTDI can be held low or high.                                  |  |

| JTDO     | O <sub>3</sub>             | <b>JTAG Test Data Output.</b> Test instructions and data are clocked out on this pin on the falling edge of JTCLK. If not used, leave floating.                                             |  |

| JTMS     | I <sub>PU</sub>            | <b>JTAG Test Mode Select.</b> Sampled on the rising edge of JTCLK and is used to place the port into the various defined IEEE 1149.1 states. If not used connect to 3.3V or leave floating. |  |

#### **Table 4-7. Power-Supply Pin Descriptions**

| PIN NAME     | <b>TYPE</b> <sup>(1)</sup> | PIN DESCRIPTION                                                       |

|--------------|----------------------------|-----------------------------------------------------------------------|

| VDD_18       | Р                          | Digital I/O Power Supply. 1.8V ±5%.                                   |

| VDD_33       | Р                          | Digital I/O Power Supply. 3.3V ±5%.                                   |

| VDD_APLL1_18 | Р                          | APLL1 Power Supply. 1.8V ±5%. Also supply for IC1 input.              |

| VDD_APLL1_33 | Р                          | APLL1 Power Supply. 3.3V ±5%. Also supply for IC1 input.              |

| VDD_APLL2_18 | Р                          | APLL2 Power Supply. 1.8V ±5%. Also supply for IC2 and MCLKOSC inputs. |

| VDD_APLL2_33 | Р                          | APLL2 Power Supply. 3.3V ±5%. Also supply for IC2 and MCLKOSC inputs. |

| VDD_DIG_18   | Р                          | Core Digital Power Supply. 1.8V ±5%.                                  |

| VDD_OC_18    | Р                          | Output Clock Power Supply. 1.8V ±5%.                                  |

| VDD_XO_18    | Р                          | Crystal Oscillator Power Supply. 1.8V ±5%.                            |

| VDD_XO_33    |                            | Crystal Oscillator Power Supply. 3.3V ±5%.                            |

| VDDO18A      | Р                          | Output Clock Power Supply, Bank A (OC1, OC2). 1.8V ±5%.               |

| VDDO18B      | Р                          | Output Clock Power Supply, Bank B (OC3–OC5). 1.8V ±5%.                |

| VDDO18C      | Р                          | Output Clock Power Supply, Bank C (OC6-OC8). 1.8V ±5%.                |

| VDDO18D      | Р                          | Output Clock Power Supply, Bank D (OC9, OC10). 1.8V ±5%.              |

| VDDOA        | Р                          | Output Clock Power Supply, Bank A (OC1, OC2). 1.5V to 3.3V ±5%.       |

| VDDOB        | Р                          | Output Clock Power Supply, Bank B (OC3–OC5). 1.5V to 3.3V ±5%.        |

| VDDOC        | Р                          | Output Clock Power Supply, Bank C (OC6-OC8). 1.5V to 3.3V ±5%.        |

| VDDOD        | Р                          | Output Clock Power Supply, Bank D (OC9, OC10). 1.5V to 3.3V ±5%.      |

| VSS_APLL1    | Р                          | Return for VDD_APLL1 Supplies.                                        |

| VSS_APLL2    | Р                          | Return for VDD_APLL2 Supplies.                                        |

| VSS_DIG      | Р                          | Core Digital Return.                                                  |

| VSS_OC       | Р                          | Output Clock Return.                                                  |

| VSS_XO       | Р                          | Crystal Oscillator Return.                                            |

| VSSOA        | Р                          | Return for VDDOA Supply.                                              |

| VSSOB        | Р                          | Return for VDDOB Supply.                                              |

| VSSOC        | Р                          | Return for VDDOC Supply.                                              |

| VSSOD        | Р                          | Return for VDDOD Supply.                                              |

| VSUB         | Р                          | Substrate Voltage. Connect to board ground.                           |

Note 1: All pins, except power and analog pins, are CMOS/TTL unless otherwise specified in the pin description.

#### PIN TYPES

#### I = input pin

I<sub>DIFF</sub> = differential input, can be interfaced to LVDS, LVPECL, CML, HSTL or CMOS/TTL signals

$I_{\text{PD}}$  = input pin with internal 50k $\Omega$  pulldown

$I_{PU}$  = input pin with internal 50k $\Omega$  pullup

I/O = input/output pin

$IO_{PD}$  = input/output pin with internal 50k $\Omega$  pulldown

$IO_{PU}$  = input/output pin with internal 50k $\Omega$  pullup

O = output pin

O<sub>3</sub> = output pin that can be tri-stated (i.e., placed in a high-impedance state)

O<sub>DIFF</sub> = differential output, CML format

P = power-supply pin

Note 2: All digital pins, except ICn and OCn, are I/O pins in JTAG mode. ICn and OCn pins do not have JTAG functionality.

# 5. Functional Description

# 5.1 Device Identification and Protection

The 16-bit read-only ID field in the ID1 and ID2 registers is set to 00C3h = 195 decimal. The device revision can be read from the REV register. Contact the factory to interpret this value and determine the latest revision. The register set can be protected from inadvertent writes using the PROT register.

# 5.2 Top-Level Configuration

MAX24605 and MAX24610 have two fundamental modes of operation: APLL-only and DPLL+APLL.

# 5.2.1 APLL-Only Mode

In APLL-only mode, the input block and the DPLL are powered down, and APLL1 and/or APLL2 are available to produce two independent families of output clock frequencies. The input block and the DPLL are powered down by setting MCR1.ICBEN=0 and MCR1.DPLLEN=0, respectively. This reduces chip power consumption as shown in Table 8-2.

The bandwidth of the APLLs is approximately 400kHz and therefore in APLL-only mode the device does not filter jitter. This means that in applications where output signals must have sub-ps jitter, the APLL input signal must have sub-ps jitter. In addition, features of the input block and the DPLL including activity monitoring and frequency monitoring are not available. APLL-only mode is enabled when the APLL input muxes are set to select an input other than the DPLL output (i.e. APLLCR2.APLLMUX=0xx).

APLL-only mode has two usage cases for each APLL. First, the APLLs can be locked to the on-chip crystal oscillator as shown in Figure 5-1. Second, each APLL can be locked to any of the four input clock signals, as shown in Figure 5-2.

Figure 5-1. APLL-Only Mode: Clock Synthesis from a Crystal

#### Figure 5-2. APLL-Only Mode: Locked to One of Four Input Clocks

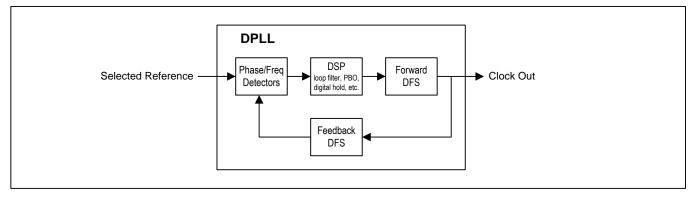

#### 5.2.2 DPLL+APLL Mode

In DPLL+APLL mode, the input block and DPLL are enabled and used. In this mode device power consumption is higher than APLL-only mode, but all input block features are available including activity monitoring, frequency monitoring and automatic reference switching. In addition, all DPLL features are available as well, including bandwidths low enough to filter jitter on the input clock signals.

DPLL+APLL mode is enabled when the APLL1 input mux is set to select the DPLL output (i.e. APLLCR2.APLLMUX=100) and the input block and DPLL are enabled using the enable bits in MCR1.

In this mode the input block and the DPLL must operate from a master clock signal of approximately 200MHz. This master clock signal can be provided using either of two methods.

For method 1, a 190MHz to 208.333MHz local oscillator is connected directly to the MCLKOSCP/N pins, and the MCR3.MCMUX bit is set to 1 to connect this clock signal directly to the input block and the DPLL. This method, shown in Figure 5-3, leaves APLL2 available to be synchronized to the DPLL and allows the device to make two families of output clock frequencies that are both synchronized to the DPLL's selected reference.

For method 2, APLL2 is configured to make the master clock signal from a lower frequency local oscillator connected to the MCLKOSCP/N pins. The APLL2 output frequency must be in the range 380MHz to 416.667MHz or the range 570MHz to 625MHz. APLL2's master clock divider (MCR2.MCDIV) is then configured to divide APLL2's output frequency by 2 or 3 to get a master clock frequency in the range 190MHz to 208.333MHz. The MCR3.MCMUX bit is set to 0 to connect the master clock signal from APLL2 to the input block and the DPLL. The APLL2 output clock frequency can also be provided to any of output banks A, B, C or D where it can be further divided to make output clock signals derived from the local oscillator.

Method 2 has two usage cases, 2a and 2b. For method 2a, APLL2 is locked to the on-chip crystal oscillator as shown in Figure 5-4. This gives the lowest possible cost for the master clock reference, but the DPLL's frequency stability during digital hold is relatively poor due to the use of a non-temperature-compensated crystal. In some applications the DPLL is expected to always be locked to one of the two input clocks and rarely or never enter digital hold. For these applications DPLL stability during digital hold is not a requirement, and deriving the master clock from a crystal is appropriate.

For method 2b, APLL2 is locked to an external oscillator as shown in Figure 5-5. This allows a more stable but more expensive reference for the master clock, such as a high-stability XO, a TCXO or even an OCXO.

Figure 5-4. DPLL+APLL Mode: Method 2a, Master Clock from Crystal Oscillator Multiplied by APLL2

# 5.3 Local Oscillator and Master Clock Configuration

Section 5.2 describes several device configurations that make use of either an external local oscillator (XO, TCXO, OCXO) or the on-chip crystal oscillator connected to an external crystal. Section 5.3.1 describes how to connect an external oscillator and the required characteristics of the oscillator. Section 5.3.2 describes how to connect an external crystal to the on-chip crystal oscillator and the required characteristics of the required characteristics of the crystal. Section 5.3.3 describes how to configure APLL2 to lock to either an external oscillator or the on-chip crystal oscillator and produce a suitable master clock for the input block and the DPLL.

# 5.3.1 External Oscillator

A signal from an external oscillator can be connected to the MCLKOSCP/N pins. The external oscillator can be either differential or single-ended and any frequency from 9.72MHz to 750MHz (but see additional constraint for method 1 in section 5.2.2). See the MCLKOSCP/N pin description in Table 4-1 for additional details. For lowest output jitter, a differential signal is best. To minimize jitter when a single-ended signal is used, the signal must be properly terminated and must have very short trace length. A poorly terminated single-ended signal can greatly increase output jitter, and long single-ended trace lengths are more susceptible to noise. If the oscillator is located more than 2cm away from the device, consider connecting the single-ended oscillator output to an LVDS driver IC (such as MAX9110) and sending a differential clock signal to the device pins.

When the DPLL master clock (see section 5.3.3) is derived from the oscillator signal applied to the MCLKOSCP/N pins, the stability of the DPLL in free-run or digital hold is equivalent to the stability of the oscillator. While many applications can make use of a simple crystal oscillator, some applications may require the stability of a TCXO or an OCXO. Contact Microsemi timing products technical support for recommended oscillator components.

While the stability of the external oscillator can be important, its absolute frequency accuracy is less important because any known frequency inaccuracy of the oscillator can be compensated in the DPLL or in the APLLs. When the device is configured for DPLL+APLL mode, the DPLL's MCFREQ field can be used to compensate for oscillator frequency error. When the device is configured for APLL-only mode, the APLLs' fractional feedback divider values (AFBDIV) can be adjusted by ppb or ppm to compensate for oscillator frequency error.

# 5.3.1.1 Oscillator Characteristics to Minimize Output Jitter

The jitter on output clock signals depends on the phase noise and frequency of the external oscillator. For the device to operate with the lowest possible output jitter, the external oscillator should have the following characteristics:

• Phase Noise: Typical value of -148dBc/Hz or lower at 10kHz offset from the carrier.

• Frequency: The higher the better, all else being equal. Frequencies that are integer divisors of 4000MHz or 4096MHz are excellent choices, including 50MHz and 51.2MHz.

# 5.3.2 On-Chip Crystal Oscillator

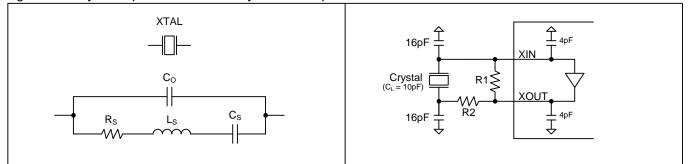

The crystal oscillator is designed to drive a <u>fundamental mode, AT-cut</u> crystal resonator. See <u>Table 5-1</u> for recommended crystal specifications. When a crystal is not connected between XIN and XOUT, the XIN pin can be used as a single-ended input to the APLLs.

To use the crystal oscillator with an external crystal, set MCR2.XIEN=1 to enable the XIN pin logic and set MCR2.XOEN=1 to enable the XOUT pin so the XO can oscillate. To use the XIN pin as a single-ended input, set MCR2.XIEN=1 to enable the XIN pin and set MCR2.XOEN=0 to disable the XOUT pin to minimize power and noise. If the XIN pin is not used, set MCR2.XIEN=0 and MCR2.XOEN=0 to minimize power and noise.

See Figure 5-6 for the crystal equivalent circuit and the recommended external capacitor connections. To achieve a crystal load ( $C_L$ ) of 10pF, an external 16pF is placed in parallel with the 4pF internal capacitance of the XIN pin, and an external 16pF is placed in parallel with the 4pF internal capacitance of the XOUT pin. The crystal then sees a load of 20pF in series with 20pF, which is 10pF total load. Note that the 16pF capacitance values in Figure 5-6 include all capacitance on those nodes. If, for example, PCB trace capacitance between crystal pin and IC pin is 2pF then 14pF capacitors should be used to make 16pF total.

The crystal, traces, and two external capacitors should be placed on the board as close as possible to the XIN and XOUT pins to reduce crosstalk of active signals into the oscillator. Also no active signals should be routed under the crystal circuitry.

Note: Crystals have temperature sensitivies that can cause crystal oscillator frequency changes in response to ambient temperature changes. In applications where significant temperature changes are expected near the crystal, it is recommended that the crystal be covered with a thermal cap, or an external XO, TCXO or OCXO should be used instead.

Figure 5-6. Crystal Equivalent Circuit / Crystal and Capacitor Connections

Note 1: R1=1MΩ. The value of R2 is a function of crystal frequency, loading and maximum power rating. Contact the factory for guidance in choosing the right R2 resistor for a specific crystal.

#### Table 5-1. Crystal Selection Parameters

| PARAMETER                     |              | SYMBOL | MIN | TYP                          | MAX | UNITS |

|-------------------------------|--------------|--------|-----|------------------------------|-----|-------|

| Crystal Oscillation Frequency |              | fosc   | 25  | 25, 50,<br>51.2 <sup>1</sup> | 52  | MHz   |

| Shunt Capacitance             |              | Co     |     | 2                            | 5   | pF    |

| Load Capacitance              |              | CL     |     | 10                           |     | pF    |

| Equivalent Series Resistance  | fosc < 40MHz | Rs     |     |                              | 60  | Ω     |

| (ESR) <sup>2</sup>            | fosc > 40MHz | Rs     |     |                              | 50  | Ω     |

| Maximum Crystal Drive Level   |              |        | 100 |                              |     | μW    |

Note 1: Crystal frequencies of 49.152MHz, 50MHz and 51.2MHz are excellent choices for lowest output jitter.

Note 2: These ESR limits are chosen to constrain crystal drive level to less than 100μW. If the crystal can tolerate a drive level greater than 100μW then proportionally higher ESR is acceptable.

| PARAMETER                                                  | SYMBOL           | MIN | TYP | MAX | UNITS                       |

|------------------------------------------------------------|------------------|-----|-----|-----|-----------------------------|

| Crystal Oscillator Frequency Stability vs. Power<br>Supply | f <sub>FVD</sub> |     | 0.2 | 0.5 | ppm per 10% $\Delta$ in VDD |

Any known frequency inaccuracy of the crystal can be compensated in the DPLL or in the APLLs. When the device is configured for DPLL+APLL mode, the DPLL's MCFREQ field can be used to compensate for crystal frequency error. When the device is configured for APLL-only mode, the APLLs' fractional feedback divider values (AFBDIV) can be adjusted by ppb or ppm to compensate for crystal oscillator frequency error.

# 5.3.3 Master Clock APLL Configuration

This section does not apply for APLL-only mode.

In DPLL+APLL mode method 2 (see section 5.2.2) the main purpose of APLL2 is to provide the required master clock signal (typically 200MHz or 204.8MHz) to the input block and the DPLL. APLL2 accepts a clock signal from either the MCLKOSCP/N pins or from the on-chip crystal oscillator as specified by APLL2's APLLCR2.APLLMUX field. APLL2 can lock to any input clock frequency from 9.72MHz to 102.4MHz. The APLL2's input divider, controlled by APLLCR2.AIDIV, can be used to divide frequencies up to 750MHz down to the 9.72MHz to 102.4MHz range. To minimize output jitter, the APLL2 input frequency should be multiplied by an integer (i.e. APLL2's AFBDIV value should be an integer) to a VCO frequency that can be internally divided by APLL2's high-speed divider (APLLCR1.HSDIV) and then by the master clock divider (MCR2.MCDIV) to get a master clock frequency in the range of 190MHz to 208.333MHz. Higher APLL2 input frequencies give lower output jitter, all else being equal. Several possible APLL2 input clock frequencies are shown in Table 5-2 below along with the corresponding APLL2 register settings and resulting master clock frequencies.

| APLL2                             | Multiplier        |                        |                                  |                               |                           |

|-----------------------------------|-------------------|------------------------|----------------------------------|-------------------------------|---------------------------|

| Input<br>Frequency <sup>2,3</sup> | Value<br>(AFBDIV) | APLL2 VCO<br>Frequency | Divider Value<br>(APLLCR1.HSDIV) | Divider Value<br>(MCR2.MCDIV) | Master Clock<br>Frequency |

| 51.2MHz <sup>1</sup>              | 80                | 4096MHz                | 10                               | 2                             | 204.8MHz                  |

| 50MHz <sup>1</sup>                | 80                | 4000MHz                | 10                               | 2                             | 200MHz                    |

| 40MHz                             | 100               | 4000MHz                | 10                               | 2                             | 200MHz                    |

| 25.6MHz                           | 160               | 4096MHz                | 10                               | 2                             | 204.8MHz                  |

| 25MHz                             | 160               | 4000MHz                | 10                               | 2                             | 200MHz                    |

| 12.8MHz                           | 320               | 4096MHz                | 10                               | 2                             | 204.8MHz                  |

| 10MHz                             | 400               | 4000MHz                | 10                               | 2                             | 200MHz                    |

Table 5-2. Example Master Clock APLL Input Frequencies and Configurations

Note 1: Input frequencies of 98.304MHz, 50MHz and 51.2MHz are excellent choices for lowest output jitter.

Note 2: Many other input frequencies are possible.

Note 3: The APLL2 input frequency range is wider than the crystal oscillator frequency range.

By default the device assumes a master clock frequency of 204.8MHz. When the master clock frequency is different than 204.8MHz, the MCDNOM, MCINOM and MCAC registers must be set correctly for proper operation of the input block and the DPLL.

The APLLs are self-oscillating, and therefore APLL2's output toggles even when the signal on the MCLKOSC pins or the output of the on-chip crystal oscillator is not toggling. This allows the device to continue to operate (although not in a standards-compliant manner) even during a complete oscillator failure. If the input clock to APLL2 is not toggling or is grossly off frequency, the device sets the PLL1LSR.MCFAIL latched status bit. This in turn can cause an interrupt if configured to do so.

The MCLKOSC input must be enabled before use by setting MCR2.MCEN=1. The master clock divider must be enabled before use by setting MCR2.MCDIV to a non-zero value.

# 5.4 Input Signal Format Configuration

Input clocks IC1 and IC2 are enabled by setting MCR2.IC1EN=1 and IC2EN=1, respectively. The power consumed by a differential receiver is shown in Table 8-2. The electrical specifications for these inputs are listed in Table 8-4. Each input clock can be configured to accept nearly any differential signal format by using the proper set of external components (see Table 8-4 and Figure 8-1). To configure these differential inputs to accept single-ended CMOS or TTL signals, connect the single-ended signal to the POS pin, and connect the NEG pin to a capacitor ( $0.1\mu$ F or  $0.01\mu$ F) to VSS\_IO. As shown in Figure 8-1, the NEG pin is internally biased to approximately 1.2V. If a 1.2V bias is unsuitable, an external voltage divider can be used to set a different bias. If an input is not used, both POS and NEG pins can be left floating.

#### Table 5-3. Input Clock Capabilities

| Input Clock | Signal Format | Frequency Range to the Input block (MHz)    | Frequence Range<br>to the APLLs (MHz) |

|-------------|---------------|---------------------------------------------|---------------------------------------|

| IC1         | Diferential   | Differential: 2kHz to 750MHz                | Differential: 9.72MHz to 750MHz       |

| IC2         | CMOS/TTL      | Single-ended: 2kHz to 160MHz <sup>(1)</sup> | Single-ended: 9.72MHz to 160MHz       |

Note 1: See sections 5.5.1 for details on frequency dividers, fractional scaling, and direct-lock frequencies supported by the DPLL.

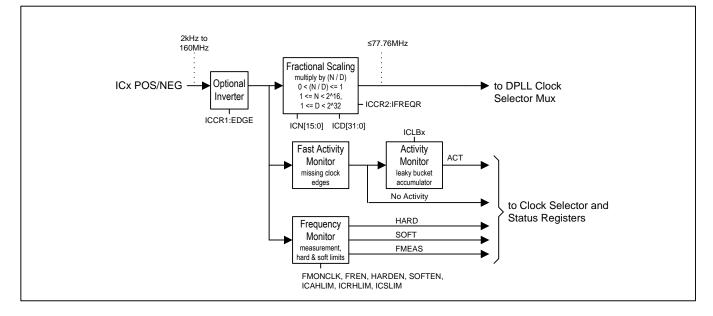

# 5.5 Input Clock Divider, Monitor and Selector

The input block performs the following functions:

- Frequency division (integer or fractional) to a frequency suitable for DPLL locking

- Activity monitoring

- Frequency monitoring

- DPLL input clock selection (automatic or manual)

Figure 5-7 is a detailed block diagram of the input block. This block requires a master clock as described in section 5.2.2. To enable the input block set MCR1.ICBEN=1. To enable APLL2, set APLLSEL=2 and then set APLLCR1.APLLEN=1.

Figure 5-7. Input block Diagram

It is important to note that the input block provides its selector and divider services to the DPLL only. When the device is configured at the top level to connect an input signal to directly to one or both APLLs, the input block is bypassed as shown in the block diagram in Figure 2-1. In this configuration the input block can still be used to monitor the input clock signals for activity and frequency accuracy.

# 5.5.1 Input Clock Frequency Dividers, Scaling and Inversion

The input block tolerates a wide range of duty cycles out to a minimum high time or minimum low time of 3ns or 30% of the clock period, whichever is smaller. The input clock registers are bank-selected by the ICSEL register (see section 6.1.3).

As shown in Figure 5-7, any frequency in the 2kHz to 750MHz range can be accepted by the input block as long as the frequency meets one of the following criteria:

- 1. A DPLL locking frequency listed in the ICCR1.LKFREQ register description

- 2. A frequency that can be divided by an unsigned integer (ICD+1) to produce a DPLL locking frequency listed in ICCR1.LKFREQ

- 3. A frequency that can be multiplied by the ratio of two integers (ICN+1) / (ICD+1) to produce a DPLL locking frequency ≥1MHz listed in ICCR1.LKFREQ

Important notes about the input block:

- ICCR1.POL specifies the edge to which the DPLL will lock (by default, the falling edge).

- The frequency range field ICCR1.IFREQR must be set correctly for the actual frequency of the input clock.

- For fractional scaling, the input clock frequency must be ≥1MHz, and ICN and ICD must be set to meet the requirement 0 < (ICN + 1)/(ICD + 1) ≤ 0.25.</li>

- The frequency out of the scaling block must be a DPLL locking frequency listed in ICCR1.LKFREQ.

- ICN and ICD are set to 0 by default to give no dividing or scaling. This setting is useful for rates that are DPLL locking frequencies (e.g. 1MHz and 25MHz)

# 5.5.2 Input Clock Monitoring

Each input clock (IC1, IC2) is continuously monitored for frequency accuracy and activity. Frequency monitoring is described in section 5.5.2.1, while activity monitoring is described in Sections 5.5.2.2 and 5.5.2.3. Any input clock that has a frequency out-of-band alarm or activity alarm is automatically declared invalid. The valid/invalid state of each input clock is reported in the corresponding real-time status bit in the VALSR1 register. When the valid/invalid state of a clock changes, the corresponding latched status bit is set in the ICLSR1 register, and an interrupt request occurs if the corresponding interrupt enable bit is set in the ICIER1 register. Input clocks marked invalid cannot be automatically selected as the reference for the DPLL.

# 5.5.2.1 Frequency Monitoring

The input block monitors the frequency of each input clock and invalidates any clock whose frequency is outside of specified limits. Measured frequency can be read from the FMEAS field. In addition, three frequency limits can be specified: a soft limit (ICSLIM), a rejection hard limit (ICRHLIM), and an acceptance hard limit (ICAHLIM). When the frequency of an input clock is greater than or equal to the soft limit, the corresponding ISR.SOFT alarm bit is set to 1. The soft limit is only for monitoring; triggering it does not invalidate the clock. When the frequency offset of an input clock is greater than or equal to the rejection hard limit, the corresponding ISR.HARD alarm bit is set to 1, and the clock is marked invalid in the VALSR1 register. When the frequency offset of an input clock is less than the acceptance hard limit, the ISR.HARD alarm bit is cleared to 0. Together, the acceptance hard limit and the rejection hard limit allow hysteresis to be configured as required by Telcordia spec GR-1244-CORE.

Monitoring according to the hard and soft limits is enabled/disabled using the HARDEN and SOFTEN bits in the ICCR2 register. Frequency monitoring is only done on an input clock when the clock does not have an activity alarm.

The frequency monitoring logic determines the nominal (ideal, zero-error) frequency of the input clock from the values in the ICCR1.LKFREQ, ICN, ICD, and ICCR1.IFREQR fields. As must be done in any frequency measurement system, the frequency monitor counts the number of input clock cycles that occur in an interval of time equal to a specific number of reference clock periods. It then compares the actual count to the expected count to determine the fractional frequency offset of the input clock. The reference clock for the frequency monitor can be either the internal master clock (see section 5.3) or the output of the DPLL, depending on the setting of ICCR2.FMONCLK.

Frequency measurement time can be specified in the ICCR3.FMONLEN field. For any input clock there is a relationship among frequency measurement precision, measurement time (duration), and maximum input jitter amplitude as follows:

freq\_meas\_time ≥ max\_p-p\_jitter\_amplitude / ( 0.5 \* freq\_meas\_precision)

When ICCR2.FREN=1 the input block performs gross frequency monitoring and invalidates any clock whose frequency is more than 10,000ppm away from nominal. This function is useful when hard limits are not enabled (ICCR2.HARDEN=0).

# 5.5.2.2 Activity Monitoring

The input block monitors each input clock for activity and proper behavior using a leaky bucket accumulator. A leaky bucket accumulator is similar to an analog integrator: the output amplitude increases in the presence of input events and gradually decays in the absence of events. When events occur infrequently, the accumulator value decays fully between events and no alarm is declared. When events occur close enough together, the accumulator increments faster than it can decay and eventually reaches the alarm threshold. After an alarm has been declared, if events occur infrequently enough, the accumulator can decay faster than it is incremented by new events and eventually reaches the alarm clear threshold. The leaky bucket events come from the fast activity monitor.

The leaky bucket accumulator for each input clock has programmable size, alarm declare threshold, alarm clear threshold, and decay rate, all of which are specified in the ICLB registers.

Activity monitoring is divided into 128ms intervals. The accumulator is incremented once for each 128ms interval in which the input clock is inactive for a few clock cycles (see Table 5-4). Thus the "fill" rate of the bucket is at most 1 unit per 128ms, or approximately 8 units/second. During each period of 1, 2, 4 or 8 intervals (programmable), the accumulator decrements if no irregularities occur. Thus the "leak" rate of the bucket is approximately 8, 4, 2, or 1 units/second. A leak is prevented when a fill event occurs in the same interval.

When the value of an accumulator reaches the alarm threshold (ICLBU register), the corresponding ISR.ACT alarm bit is set to 1, and the clock is marked invalid in the VALSR1 register. When the value of an accumulator reaches the alarm clear threshold (ICLBL register), the activity alarm is cleared by clearing the clock's ACT bit. The accumulator cannot increment past the size of the bucket specified in the ICLBS register. The decay rate of the accumulator is specified in the ICLBD register. The values stored in the leaky bucket configuration registers must have the following relationship at all times: ICLBS  $\geq$  ICLBU > ICLBL. If ICLBS is set to 00h, the leaky bucket count is set to 0, the leaky bucket is disabled, and ISR.ACT alarm bit is set to 0.

When the leaky bucket is empty, the minimum time to declare an activity alarm in seconds is ICLBU / 8. The minimum time to clear an activity alarm in seconds is  $2^{ICLBD} \times (ICLBS - ICLBL) / 8$ . As an example, assume ICLBU = 8, ICLBL = 1, ICLBS = 10, and ICLBD = 0. The minimum time to declare an activity alarm would be 8 / 8 = 1 second. The minimum time to clear the activity alarm would be  $2^{0} \times (10 - 1) / 8 = 1.125$  seconds.

# Table 5-4. Activity Monitoring, Missing Clock Cycles vs. Frequency

| INPUT CLOCK   | NUMBER OF MISSING |

|---------------|-------------------|

| FREQUENCY     | CLOCK CYCLES      |

| <100 MHz      | 2                 |

| 100 – 200 MHz | 4                 |

| 200 – 400 MHz | 8                 |

| >400 MHz      | 16                |

### 5.5.2.3 Selected Reference Fast Activity Monitoring

The input clock that the DPLL is currently locked to is called the selected reference. The quality of the DPLL's selected reference is exceedingly important, since missing cycles and other anomalies on the selected reference can cause unwanted jitter, wander or frequency offset on the output clocks. When anomalies occur on the selected reference they must be detected as soon as possible to give the DPLL opportunity to temporarily disconnect from the reference until the reference is available again. By design, the regular input clock activity monitor (the leaky bucket accumulator described in section 5.5.2.2) is too slow to be suitable for monitoring the selected reference. Instead, the input block provides a fast activity monitor that detects inactivity after a few missing clock cycles (see Table 5-4).

When the fast activity monitor detects a no-activity event, the DPLL immediately enters a temporary digital hold state to isolate itself from the selected reference and sets the SRFAIL bit in PLL1LSR. The setting of the SRFAIL bit can cause an interrupt request if the corresponding enable bit is set in PLL1IER. By setting the appropriate GPIOSS register to xx001011b, a GPIO pin can be configured to follow the state of the SRFAIL status bit. Optionally, a no-activity event can also cause an ultra-fast reference switch (see Section 5.5.3.4). When DPLLCR5.NALOL = 0 (default), the DPLL does not declare loss-of-lock during no-activity events. If the selected reference becomes available again before any alarms are declared by the activity monitor or frequency monitor, then the DPLL continues to track the selected reference using nearest-edge locking ( $\pm 180^{\circ}$ ) to avoid cycle slips. When NALOL = 1, the DPLL declares loss-of-lock during no-activity events. This causes the DPLL state machine to transition to the loss-of-lock state, which sets the STATE bit in PLL1LSR and causes an interrupt request if enabled. If the selected reference becomes available again before available again before any alarms are declared by the activity monitor or frequency monitor, then the DPLL tracks the selected reference using phase/frequency locking ( $\pm 360^{\circ}$ ) until phase lock is reestablished.

#### 5.5.2.4 External Monitoring

Some clock signals come from external components that can monitor the quality of a clock signal or the quality of a signal from which the clock signal is derived. One example is a BITS receiver, which receives a DS1, E1 or 2048kHz synchronization signal and recovers a clock from that signal. A BITS receiver monitors the incoming signal and can declare loss of signal (LOS), loss of frame alignment (LOF) and other defects in the incoming signal. Another example is a synchronous Ethernet PHY, which receives an Ethernet signal and recovers a clock from that signal and can declare loss of lock, loss of codeword alignment and other defects.

When a neighboring component can detect that the incoming signal or the clock recovered from the signal is somehow out of specification, a bad-clock signal from that component can be connected to a GPIO pin on the device. The device can then be configured to squelch the input clock when the bad-clock signal is high by setting ICCR2.GPIOSQ=1 for that input clock. IC1 is squelched when GPIO1 is high. IC2 is squelched when GPIO2 is high.

#### 5.5.3 Input Clock Priority, Selection and Switching

#### 5.5.3.1 Priority Configuration

During normal operation, the selected reference for the DPLL is chosen automatically based on the priority rankings assigned to the input clocks in the input priority register (IPR1). The default input clock priorities are shown in Table 5-5.

Any unused input clock should be given the priority value 0, which disables the clock and marks it as unavailable for selection. Priority 1 is highest while priority 15 is lowest.

# Table 5-5. Default Input Clock Priorities

| INPUT CLOCK | DPLL<br>DEFAULT<br>PRIORITY |

|-------------|-----------------------------|

| IC1         | 1                           |

| IC2         | 2                           |

### 5.5.3.2 Automatic Selection

The reference selection algorithm for the DPLL chooses the <u>highest-priority valid input clock</u> to be the selected reference. The real-time valid/invalid state of each input clock is maintained in the VALSR1 register (see section 5.5.2). The priority of each input clock is set as described in section 5.5.3.1. To select the proper input clock based on these criteria, the selection algorithm maintains a priority table of valid inputs. The top entry in this priority table and the selected reference are displayed in the PTAB1 register.