# KSZ8851-16/32MQL

# Single-Port Ethernet MAC Controller with 8/16-Bit or 32-Bit Non-PCI Interface

## Features

- Integrated MAC and PHY Ethernet Controller Fully Compliant with IEEE 802.3/802.3u Standards

- Designed for High Performance and High Throughput Applications

- Supports 10BASE-T/100BASE-TX

- Supports IEEE 802.3x Full-Duplex Flow Control and Half-Duplex Backpressure Collision Flow Control

- Supports DMA-Slave Burst Data Read and Write Transfers

- Supports IP Header (IPv4)/TCP/UDP/ICMP Checksum Generation and Checking

- Supports IPv6 TCP/UDP/ICMP Checksum Generation and Checking

- Automatic 32-bit CRC Generation and Checking

- Simple SRAM-Like Host Interface Easily Connects to Most Common Embedded MCUs

- Supports Multiple Data Frames for Transmit and Receive without Address Bus and Byte-Enable Signals

- Supports Both Big- and Little-Endian Processors

- Larger Internal Memory with 12K Bytes for RX FIFO and 6K Bytes for TX FIFO. Programmable Low, High, and Overrun Watermark for Flow Control in RX FIFO

- Efficient Architecture Design with Configurable Host Interrupt Schemes to Minimize Host CPU Overhead and Utilization

- Powerful and Flexible Address Filtering Scheme

- Optional to Use External Serial EEPROM Configuration for Both KSZ8851-16MQL and KSZ8851-32MQL

- Single 25 MHz Reference Clock for Both PHY and MAC

## Power Modes, Power Supplies, and Packaging

- Single 3.3V Power Supply with Options for 1.8V, 2.5V, and 3.3V VDD I/O

- Built-In Integrated 3.3V or 2.5V to 1.8V Low Noise Regulator (LDO) for Core and Analog Blocks

- Enhanced Power Management Feature with Energy Detect Mode Ensure Low-Power Dissipation During Device Idle Periods

- Comprehensive LED Indicator Support for Link, Activity and 10/100 Speed (2 LEDs)

- User Programmable

- Low-Power CMOS Design

- Commercial Temperature Range: 0°C to +70°C

- Industrial Temperature Range: –40°C to +85°C

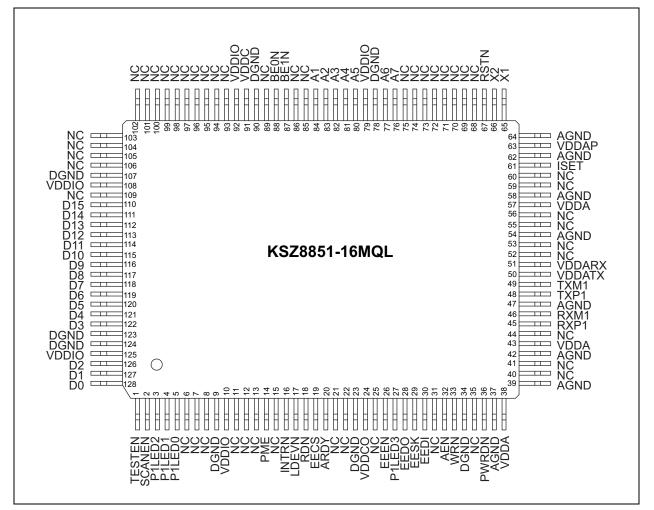

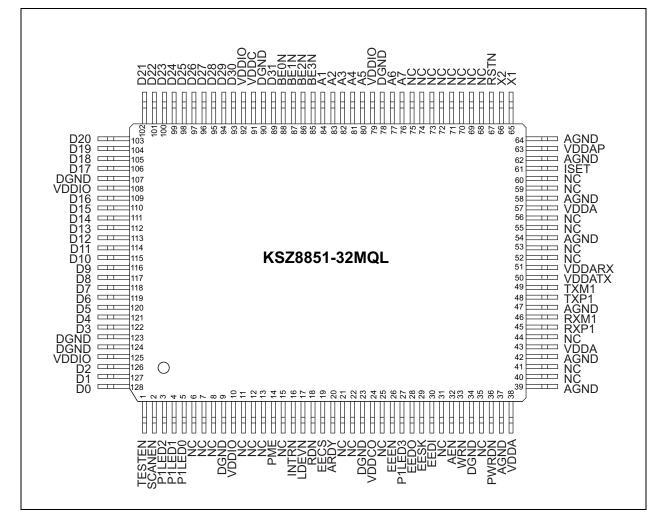

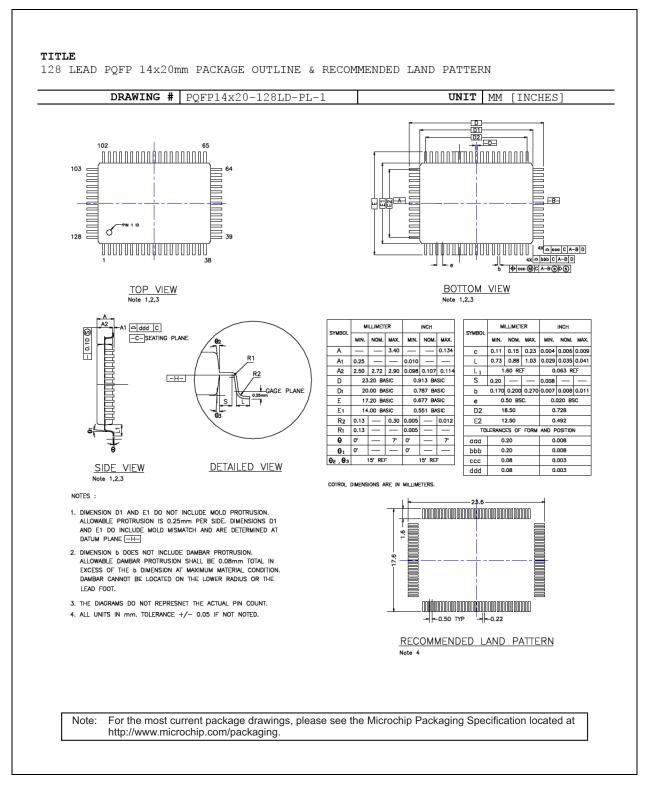

- Flexible Package Options Available in 128-pin PQFP: KSZ8851-16/32MQL or 48-pin LQFP KSZ8851-16MLL

- Pin Compatible with Existing 128-pin KSZ8841-16/ 32MQL and KSZ8842-16/32MQL

#### **Additional Features**

In addition to offering all of the features of a Layer 2 controller, the KSZ8851-16/23MQL offers:

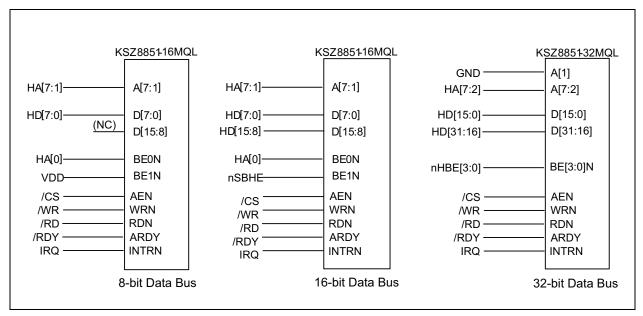

- Flexible 8-bit, 16-bit, and 32-bit Generic Host Processor Interfaces with Same Access Time and Single Bus Timing to Any I/O Registers and RX/TX FIFO Buffers

- Supports Adding Two-Bytes Before Frame Header in Order for IP Frame Content with Double Word Boundary

- LinkMD<sup>®</sup> Cable Diagnostic Capabilities to Determine Cable Length, Diagnose Faulty Cables, and Determine Distance to Fault

- Wake-on-LAN Functionality

Incorporates Magic Packet<sup>™</sup>, Network Link State, and Wake-Up Frame Technology

- HP Auto MDI-X<sup>™</sup> Crossover with Disable/Enable Option

- Ability to Transmit and Receive Frames up to 2000 Bytes

#### **Network Features**

- 10BASE-T and 100BASE-TX Physical Layer Support

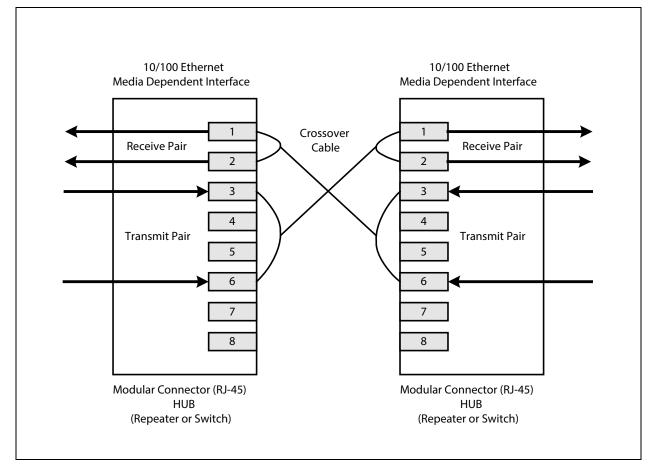

- Auto-Negotiation: 10/100 Mbps Full- and Half-Duplex

- · Adaptive Equalizer

- Baseline Wander Correction

## Applications

- Video/Audio Distribution Systems

- High-End Cable, Satellite, and IP Set-Top Boxes

- · Video over IP and IPTV

- Voice over IP (VoIP) and Analog Telephone Adapters (ATA)

- · Industrial Control in Latency-Critical Applications

- Home Base Station with Ethernet Connection

- Industrial Control Sensor Devices (Temp., Pressure, Levels, and Valves)

- Security, Motion Control, and Surveillance Cameras

#### Markets

- Fast Ethernet

- Embedded Ethernet

- Industrial Ethernet

- · Embedded Systems

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

- To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; <a href="http://www.microchip.com">http://www.microchip.com</a>

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## **Table of Contents**

| 1.0 Introduction                                                         | 4  |

|--------------------------------------------------------------------------|----|

| 2.0 Pin Description and Configuration                                    | 7  |

| 2.0 Pin Description and Configuration         3.0 Functional Description |    |

| 4.0 Register Descriptions                                                |    |

| 5.0 Operational Characteristics                                          | 80 |

| 6.0 Electrical Characteristics                                           | 81 |

| 7.0 Timing Specifications                                                | 83 |

| 8.0 Selection of Isolation Transformers                                  | 88 |

| 9.0 Package Outline                                                      | 89 |

| Appendix A: Data Sheet Revision History                                  |    |

| The Microchip Web Site                                                   |    |

| Customer Change Notification Service                                     |    |

| Customer Support                                                         |    |

| Product Identification System                                            | 92 |

## 1.0 INTRODUCTION

## 1.1 General Terms and Conventions

The following is list of the general terms used throughout this document:

| BIU - Bus Interface Unit                                          | The host interface function that performs code conversion,<br>buffering, and the like required for communications to and<br>from a network.                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BPDU - Bridge Protocol Data Unit                                  | A packet containing ports, addresses, etc. to make sure<br>data being passed through a bridged network arrives at its<br>proper destination.                                                                                                                                                                                                                                                                                                                                                                              |

| CMOS - Complementary Metal Oxide<br>Semiconductor                 | A common semiconductor manufacturing technique in<br>which positive and negative types of transistors are com-<br>bined to form a current gate that in turn forms an effective<br>means of controlling electrical current through a chip.                                                                                                                                                                                                                                                                                 |

| CRC - Cyclic Redundancy Check                                     | A common technique for detecting data transmission errors. CRC for Ethernet is 32 bits long.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Cut-Through Switch                                                | A switch typically processes received packets by reading in<br>the full packet (storing), then processing the packet to<br>determine where it needs to go, then forwarding it. A cut-<br>through switch simply reads in the first bit of an incoming<br>packet and forwards the packet. Cut-through switches do<br>not store the packet.                                                                                                                                                                                  |

| DA - Destination Address                                          | The address to send packets.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DMA - Direct Memory Access                                        | A design in which memory on a chip is controlled inde-<br>pendently of the CPU.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| EEPROM - Electronically Erasable<br>Programmable Read-Only Memory | A design in which memory on a chip can be erased by exposing it to an electrical charge.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| EISA - Extended Industry Standard<br>Architecture                 | A bus architecture designed for PCs using 80x86 processors, or an Intel 80386, 80486 or Pentium microprocessor.<br>EISA buses are 32 bits wide and support multiprocessing.                                                                                                                                                                                                                                                                                                                                               |

| EMI - Electro-Magnetic Interference                               | A naturally occurring phenomena when the electromag-<br>netic field of one device disrupts, impedes or degrades the<br>electromagnetic field of another device by coming into<br>proximity with it. In computer technology, computer devices<br>are susceptible to EMI because electromagnetic fields are<br>a byproduct of passing electricity through a wire. Data lines<br>that have not been properly shielded are susceptible to<br>data corruption by EMI.                                                          |

| FCS - Frame Check Sequence                                        | See CRC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| FID - Frame or Filter ID                                          | Specifies the frame identifier. Alternately is the filter identi-<br>fier.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IGMP - Internet Group Management Protocol                         | The protocol defined by RFC 1112 for IP multicast trans-<br>missions.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| IPG - Inter-Packet Gap                                            | A time delay between successive data packets mandated<br>by the network standard for protocol reasons. In Ethernet,<br>the medium has to be "silent" (i.e., no data transfer) for a<br>short period of time before a node can consider the net-<br>work idle and start to transmit. IPG is used to correct timing<br>differences between a transmitter and receiver. During the<br>IPG, no data is transferred, and information in the gap can<br>be discarded or additions inserted without impact on data<br>integrity. |

| ISI - Inter-Symbol Interface                                      | The disruption of transmitted code caused by adjacent pulses affecting or interfering with each other.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| IOA Inducting Other dend Architecture                | A hus such that was dire that IDM DO WT and DO AT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISA - Industry Standard Architecture<br>Jumbo Packet | A bus architecture used in the IBM PC/XT and PC/AT.<br>A packet larger than the standard Ethernet packet (1500                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                      | bytes). Large packet sizes allow for more efficient use of bandwidth, lower overhead, less processing, etc.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

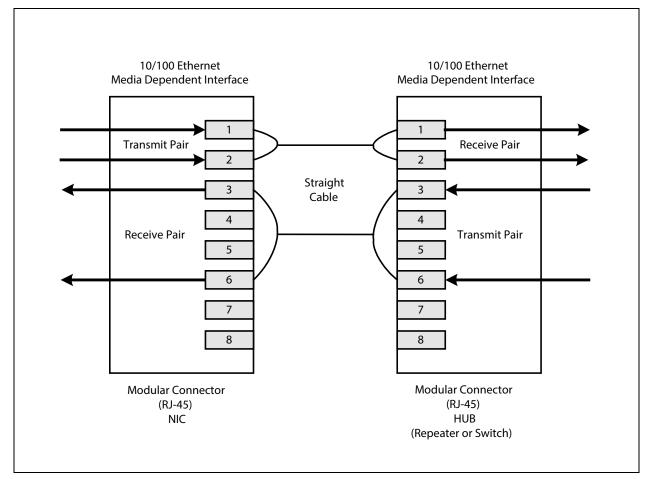

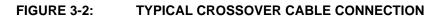

| MDI - Medium Dependent Interface                     | An Ethernet port connection that allows network hubs or<br>switches to connect to other hubs or switches without a<br>null-modem, or crossover, cable. MDI provides the stan-<br>dard interface to a particular media (copper or fiber) and is<br>therefore 'media dependent.'                                                                                                                                                                                                                                                                |

| MDI-X - Medium Dependent Interface<br>Crossover      | An Ethernet port connection that allows networked end sta-<br>tions (i.e., PCs or workstations) to connect to each other<br>using a null-modem, or crossover, cable. For 10/100 full-<br>duplex networks, an end point (such as a computer) and a<br>switch are wired so that each transmitter connects to the<br>far end receiver. When connecting two computers together,<br>a cable that crosses the TX and RX is required to do this.<br>With auto MDI-X, the PHY senses the correct TX and RX<br>roles, eliminating any cable confusion. |

| MIB - Management Information Base                    | The MIB comprises the management portion of network<br>devices. This can include things like monitoring traffic lev-<br>els and faults (statistical), and can also change operating<br>parameters in network nodes (static forwarding<br>addresses).                                                                                                                                                                                                                                                                                          |

| MII - Media Independent Interface                    | The MII accesses PHY registers as defined in the IEEE 802.3 specification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| NIC - Network Interface Card                         | An expansion board inserted into a computer to allow it to<br>be connected to a network. Most NICs are designed for a<br>particular type of network, protocol, and media, although<br>some can serve multiple networks.                                                                                                                                                                                                                                                                                                                       |

| NPVID - Non-Port VLAN ID                             | The port VLAN ID value is used as a VLAN reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PLL - Phase-Locked Loop                              | An electronic circuit that controls an oscillator so that it<br>maintains a constant phase angle (i.e., lock) on the fre-<br>quency of an input, or reference, signal. A PLL ensures<br>that a communication signal is locked on a specific fre-<br>quency and can also be used to generate, modulate, and<br>demodulate a signal and divide a frequency.                                                                                                                                                                                     |

| PME - Power Management Event                         | An occurrence that affects the directing of power to differ-<br>ent components of a system.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| QMU - Queue Management Unit                          | Manages packet traffic between MAC/PHY interface and<br>the system host. The QMU has built-in packet memories<br>for receive and transmit functions called TXQ (Transmit<br>Queue) and RXQ (Receive Queue).                                                                                                                                                                                                                                                                                                                                   |

| SA - Source Address                                  | The address from which information has been sent.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TDR - Time Domain Reflectometry                      | TDR is used to pinpoint flaws and problems in under-<br>ground and aerial wire, cabling, and fiber optics. They send<br>a signal down the conductor and measure the time it takes<br>for the signal—or part of the signal—to return.                                                                                                                                                                                                                                                                                                          |

| UTP - Unshielded Twisted Pair                        | Commonly a cable containing 4 twisted pairs of wires. The wires are twisted in such a manner as to cancel electrical interference generated in each wire, therefore shielding is not required.                                                                                                                                                                                                                                                                                                                                                |

| VLAN - Virtual Local Area Network                    | A configuration of computers that acts as if all computers<br>are connected by the same physical network but which<br>may be located virtually anywhere.                                                                                                                                                                                                                                                                                                                                                                                      |

## 1.2 General Description

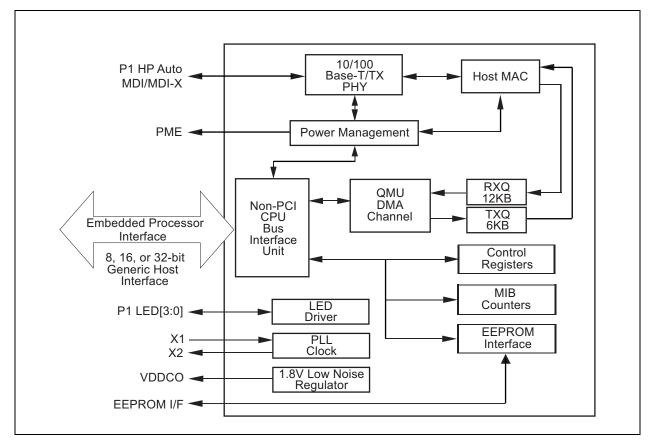

The KSZ8851M-series is a single-port controller chip with a non-PCI CPU interface and is available in 8/16-bit and 32bit bus designs. This data sheet describes the 128-pin PQFP KSZ8851-16/32MQL for applications requiring high-performance from single-port Ethernet Controller with 8/16-bit or 32-bit generic processor interface. The KSZ8851M offers the most cost-effective solution for adding high-throughput Ethernet connectivity to traditional embedded systems.

The KSZ8851M is a single-chip, mixed analog/digital device offering Wake-on-LAN technology for effectively addressing Fast Ethernet applications. It consists of a Fast Ethernet MAC controller, an 8-bit, 16-bit, and 32-bit generic host processor interface and incorporates a unique dynamic memory pointer with 4-byte buffer boundary and a fully usable 18KB for both TX (allocated 6KB) and RX (allocated 12KB) directions in host buffer interface.

The KSZ8851M is designed to be fully compliant with the appropriate IEEE 802.3 standards. An industrial temperaturegrade version of the KSZ8851M, the KSZ8851MQLI, is also available.

Physical signal transmission and reception are enhanced through the use of analog circuitry, making the design more efficient and allowing for lower-power consumption. The KSZ8851M is designed using a low-power CMOS process that features a single 3.3V power supply with options for 1.8V, 2.5V, or 3.3V VDD I/O. The device includes an extensive feature set that offers management information base (MIB) counters and CPU control/data interfaces with single bus timing.

The KSZ8851M includes unique cable diagnostics feature called LinkMD<sup>®</sup>. This feature determines the length of the cabling plant and also ascertains if there is an open or short condition in the cable. Accompanying software enables the cable length and cable conditions to be conveniently displayed. In addition, the KSZ8851M supports Hewlett Packard (HP) Auto-MDIX, thereby eliminating the need to differentiate between straight or crossover cables in applications.

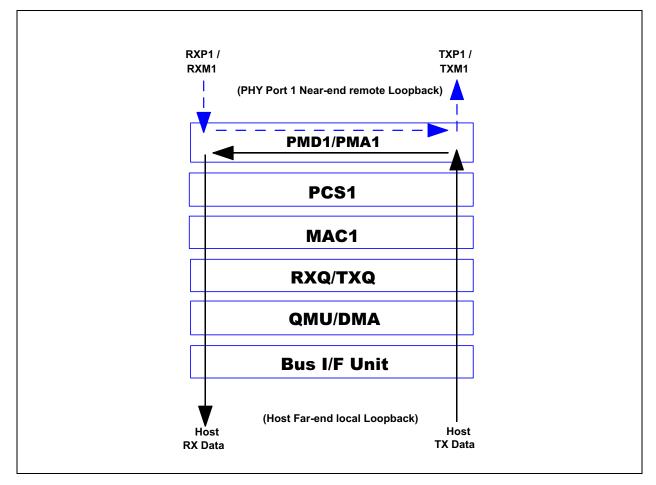

#### FIGURE 1-1: SYSTEM BLOCK DIAGRAM

## 2.0 PIN DESCRIPTION AND CONFIGURATION

#### TABLE 2-1: SIGNALS FOR 16-BIT 128-PIN PQFP

| Pin<br>Number | Pin<br>Name | Type<br>Note<br>2-3 |                                                                                                                                                                                                                                           | Description                                                                                         |                           |

|---------------|-------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------|

| 1             | TEST_EN     | lpd                 | Test Enable<br>For normal operation, op                                                                                                                                                                                                   | Test Enable<br>For normal operation, open or pull-down this pin to ground.                          |                           |

| 2             | SCAN_EN     | lpd                 | Scan Test Scan MUX Ena<br>For normal operation, op                                                                                                                                                                                        | able<br>en or pull-down this pin to g                                                               | round.                    |

|               |             |                     |                                                                                                                                                                                                                                           | ote 2-1) defined as follows:<br>s LOW; LED is OFF when o                                            | utput is HIGH.            |

|               |             |                     |                                                                                                                                                                                                                                           | Chip Global Control Re                                                                              | gister: CGCR bit [15,9]   |

| 3             | P1LED2      | Opu                 | —                                                                                                                                                                                                                                         | [0,0] Default                                                                                       | [0,1]                     |

|               |             |                     | P1LED3 (Note 2-2)                                                                                                                                                                                                                         | _                                                                                                   | _                         |

|               |             |                     | P1LED2                                                                                                                                                                                                                                    | Link/Act                                                                                            | 100Link/Act               |

|               |             |                     | P1LED1                                                                                                                                                                                                                                    | Full-Duplex/Col                                                                                     | 10Link/Act                |

| 4             |             | have 10             | P1LED0                                                                                                                                                                                                                                    | Speed                                                                                               | Full-Duplex               |

| 4             | P1LED1      | lpu/O               |                                                                                                                                                                                                                                           | Reg. CGCF                                                                                           | R bit [15,9]              |

|               |             |                     | _                                                                                                                                                                                                                                         | [1,0]                                                                                               | [1,1]                     |

|               |             |                     | P1LED3 (Note 2-2)                                                                                                                                                                                                                         | Act                                                                                                 | _                         |

|               | P1LED0      |                     | P1LED2                                                                                                                                                                                                                                    | Link                                                                                                | _                         |

|               |             |                     | P1LED1                                                                                                                                                                                                                                    | Full-Duplex/Col                                                                                     | _                         |

| 5             |             | lpu/O               | P1LED0                                                                                                                                                                                                                                    | Speed                                                                                               | _                         |

|               |             |                     | Col = Or<br>Duplex) \$                                                                                                                                                                                                                    | n; Activity = Blink; Link/Act<br>n/Blink; Full-Duplex = On<br>Speed = On (100BASE-T);<br>is Pin 27. | (Full-Duplex); Off (Half- |

| 6             | NC          | _                   | No connect.                                                                                                                                                                                                                               |                                                                                                     |                           |

| 7             | NC          | —                   | No connect.                                                                                                                                                                                                                               |                                                                                                     |                           |

| 8             | NC          | _                   | No connect.                                                                                                                                                                                                                               |                                                                                                     |                           |

| 9             | DGND        | GND                 | Digital ground.                                                                                                                                                                                                                           |                                                                                                     |                           |

| 10            | VDDIO       | Р                   | 3.3V, 2.5V, or 1.8V digital pling capacitors.                                                                                                                                                                                             | V <sub>DDIO</sub> input power supply f                                                              | for IO with well decou-   |

| 11            | NC          | _                   | No connect.                                                                                                                                                                                                                               |                                                                                                     |                           |

| 12            | NC          | —                   | No connect.                                                                                                                                                                                                                               |                                                                                                     |                           |

| 13            | NC          | _                   | No connect.                                                                                                                                                                                                                               |                                                                                                     |                           |

| 14            | PME         | lpu/O               | Power Management Event: It is asserted (low or high depends on polarity set<br>in PMECR register) when one of the wake-on-LAN events is detected by<br>KSZ8851M. The KSZ8851M is requesting the system to wake up from low<br>power mode. |                                                                                                     |                           |

| Pin<br>Number | Pin<br>Name | Type<br>Note<br>2-3 | Description                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------|-------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15            | NC          | -                   | No connect.                                                                                                                                                                                                                                                                                                                                                                                   |

| 16            | INTRN       | Opu                 | Interrupt<br>Active Low signal to host CPU to indicate an interrupt status bit is set.                                                                                                                                                                                                                                                                                                        |

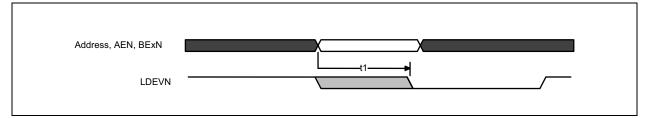

| 17            | LDEVN       | Opu                 | Local Device Not<br>Active Low output signal, asserted when AEN is Low and A7-A1 decode to<br>the KSZ8851M right address register. LDEVN is a combinational decode of<br>the Address and AEN signal.                                                                                                                                                                                          |

| 18            | RDN         | lpu                 | Read Strobe Not<br>Asynchronous read strobe, active low.                                                                                                                                                                                                                                                                                                                                      |

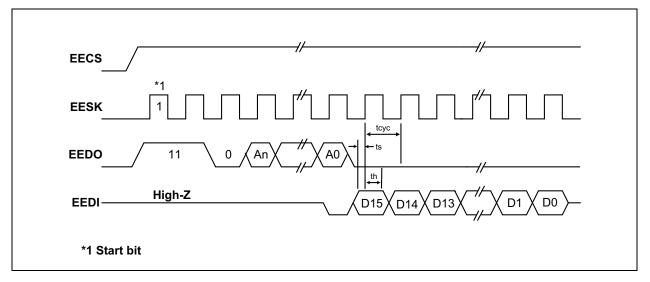

| 19            | EECS        | Opd                 | EEPROM Chip Select<br>This signal is used to select an external EEPROM device.                                                                                                                                                                                                                                                                                                                |

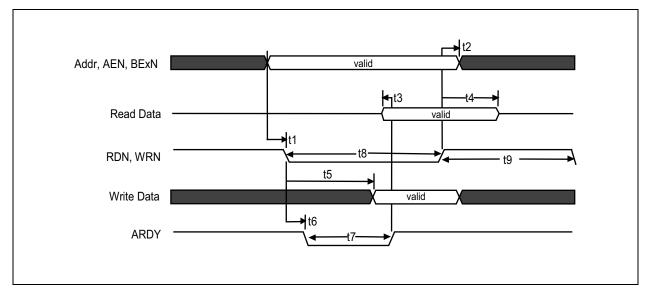

| 20            | ARDY        | Opu                 | Asynchronous Ready ARDY may be used when interfacing asynchronous buses to extend bus access cycles. It is asynchronous to the host CPU or bus clock. This pin need an external 4.7 k $\Omega$ pull-up resistor.                                                                                                                                                                              |

| 21            | NC          | _                   | No connect.                                                                                                                                                                                                                                                                                                                                                                                   |

| 22            | NC          | _                   | No connect.                                                                                                                                                                                                                                                                                                                                                                                   |

| 23            | DGND        | GND                 | Digital IO ground                                                                                                                                                                                                                                                                                                                                                                             |

| 24            | VDDCO       | Р                   | 1.8V regulator output. This 1.8V output pin provides power to pins 38, 43, 57 (VDDA), 63 (VDDAP), and 91 (VDDC) for core $V_{DD}$ supply.<br>If VDD_IO is set for 1.8V then this pin should be left floating, pins 38, 43, 57 (VDDA), 63 (VDDAP), and 91 (VDDC) will be sourced by the external 1.8V supply that is tied to pins 10, 79, 92, 108, and 125 (VDDIO) with appropriate filtering. |

| 25            | NC          | _                   | No connect.                                                                                                                                                                                                                                                                                                                                                                                   |

| 26            | EEEN        | lpd                 | EEPROM Enable<br>EEPROM is enabled and connected when this pin is pull-up.<br>EEPROM is disabled when this pin is pull-down or no connect.                                                                                                                                                                                                                                                    |

| 27            | P1LED3      | Opd                 | Port 1 LED indicator<br>See the description for pins 3, 4, and 5.                                                                                                                                                                                                                                                                                                                             |

| 28            | EEDO        | Opd                 | EEPROM Data Out<br>This pin is connected to DI input of the serial EEPROM.                                                                                                                                                                                                                                                                                                                    |

| 29            | EESK        | lpd/O               | EEPROM Serial Clock: A 4 µs (OBCR[1:0]=11 on-chip bus speed @ 25 MHz)<br>or 800 ns (OBCR[1:0]=00 on-chip bus speed @ 125 MHz) serial output clock<br>cycle to load configuration data from the serial EEPROM.<br>Config Mode: The pull-up/pull-down value is latched as big or little endian<br>mode during power-up/reset. See "Strap-In Options" section for details                        |

## KSZ8851-16/32MQL

| Pin<br>Number | Pin<br>Name | Type<br>Note<br>2-3 | Description                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|-------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30            | EEDI        | lpd                 | EEPROM Data In<br>This pin is connected to DO output of the serial EEPROM when EEEN is pull-<br>up.<br>This pin has to pull-down for 8-bit bus mode or pull-up for 16-bit mode when<br>the EEEN pin is pull-down (without EEPROM).<br>Config Mode: The pull-up/pull-down value is latched as 16- or 8-bit mode<br>during power-up/reset. See "Strap-In Options" section for details. |

| 31            | NC          | _                   | No connect                                                                                                                                                                                                                                                                                                                                                                           |

| 32            | AEN         | lpu                 | Address Enable<br>Address and chip select qualifier for the address decoding and chip enable,<br>active low.                                                                                                                                                                                                                                                                         |

| 33            | WRN         | lpu                 | Write Strobe Not<br>Asynchronous write strobe, active low.                                                                                                                                                                                                                                                                                                                           |

| 34            | DGND        | GND                 | Digital IO ground                                                                                                                                                                                                                                                                                                                                                                    |

| 35            | NC          |                     | No connect.                                                                                                                                                                                                                                                                                                                                                                          |

| 36            | PWRDN       | lpu                 | Full-chip power-down. Active Low (Low = Power down; High or floating = Nor-<br>mal operation). All I/O pins will tri-state during chip power down.                                                                                                                                                                                                                                   |

| 37            | AGND        | GND                 | Analog ground                                                                                                                                                                                                                                                                                                                                                                        |

| 38            | VDDA        | Р                   | 1.8V analog power supply from VDDCO (pin 24) with appropriate filtering. If VDDIO is 1.8V, this pin must be supplied power from the same source as pins 10, 79, 92, 108, and 125 (VDDIO) with appropriate filtering.                                                                                                                                                                 |

| 39            | AGND        | GND                 | Analog ground                                                                                                                                                                                                                                                                                                                                                                        |

| 40            | NC          | _                   | No connect                                                                                                                                                                                                                                                                                                                                                                           |

| 41            | NC          | _                   | No connect                                                                                                                                                                                                                                                                                                                                                                           |

| 42            | AGND        | GND                 | Analog ground                                                                                                                                                                                                                                                                                                                                                                        |

| 43            | VDDA        | Р                   | 1.8V analog power supply from VDDCO (pin 24) with appropriate filtering. If VDDIO is 1.8V, this pin must be supplied power from the same source as pins 10, 79, 92, 108, and 125 (VDDIO) with appropriate filtering.                                                                                                                                                                 |

| 44            | NC          |                     | No connect                                                                                                                                                                                                                                                                                                                                                                           |

| 45            | RXP1        | I/O                 | Port 1 physical receive (MDI) or transmit (MDIX) signal (+ differential)                                                                                                                                                                                                                                                                                                             |

| 46            | RXM1        | I/O                 | Port 1 physical receive (MDI) or transmit (MDIX) signal (– differential)                                                                                                                                                                                                                                                                                                             |

| 47            | AGND        | GND                 | Analog ground                                                                                                                                                                                                                                                                                                                                                                        |

| 48            | TXP1        | I/O                 | Port 1 physical transmit (MDI) or receive (MDIX) signal (+ differential)                                                                                                                                                                                                                                                                                                             |

| 49            | TXM1        | I/O                 | Port 1 physical transmit (MDI) or receive (MDIX) signal (– differential)                                                                                                                                                                                                                                                                                                             |

| 50            | VDDATX      | Р                   | 3.3V analog $V_{DD}$ input power supply with well decoupling capacitors.                                                                                                                                                                                                                                                                                                             |

| 51            | VDDARX      | Р                   | 3.3V analog $V_{DD}$ input power supply with well decoupling capacitors.                                                                                                                                                                                                                                                                                                             |

| 52            | NC          | _                   | No connect                                                                                                                                                                                                                                                                                                                                                                           |

| Pin<br>Number | Pin<br>Name | Type<br>Note<br>2-3 | Description                                                                                                                                                                                                                          |

|---------------|-------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 53            | NC          | _                   | No connect                                                                                                                                                                                                                           |

| 54            | AGND        | GND                 | Analog ground                                                                                                                                                                                                                        |

| 55            | NC          | _                   | No connect                                                                                                                                                                                                                           |

| 56            | NC          | _                   | No connect                                                                                                                                                                                                                           |

| 57            | VDDA        | Р                   | 1.8V analog power supply from VDDCO (pin 24) with appropriate filtering. If VDDIO is 1.8V, this pin must be supplied power from the same source as pins 10, 79, 92, 108, and 125 (VDDIO) with appropriate filtering.                 |

| 58            | AGND        | GND                 | Analog ground                                                                                                                                                                                                                        |

| 59            | NC          | _                   | No connect (internal test only)                                                                                                                                                                                                      |

| 60            | NC          | —                   | No connect (internal test only)                                                                                                                                                                                                      |

| 61            | ISET        | 0                   | Set physical transmits output current. Pull-down this pin with a 3.01 k $\Omega$ 1% resistor to ground.                                                                                                                              |

| 62            | AGND        | GND                 | Analog ground                                                                                                                                                                                                                        |

| 63            | VDDAP       | Р                   | 1.8V analog power supply for PLL from VDDCO (pin 24) with appropriate fil-<br>tering. If VDDIO is 1.8V, this pin must be supplied power from the same<br>source as pins 10, 79, 92, 108, and 125 (VDDIO) with appropriate filtering. |

| 64            | AGND        | GND                 | Analog ground                                                                                                                                                                                                                        |

| 65            | X1          | I                   | 25 MHz crystal or oscillator clock connection.                                                                                                                                                                                       |

| 66            | X2          | 0                   | Pins (X1, X2) connect to a crystal. If an oscillator is used, X1 connects to a 3.3V tolerant oscillator and X2 is a no connect.<br>Note: Clock requirement is ±50 ppm for either crystal or oscillator.                              |

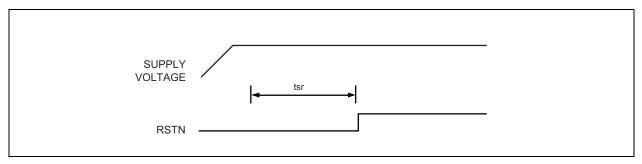

| 67            | RSTN        | lpu                 | Reset Not<br>Hardware reset pin (active low). This reset input is required minimum of 10ms<br>low after stable supply voltage 3.3V.                                                                                                  |

| 68            | NC          | _                   | No connect                                                                                                                                                                                                                           |

| 69            | NC          | -                   | No connect                                                                                                                                                                                                                           |

| 70            | NC          | -                   | No connect                                                                                                                                                                                                                           |

| 71            | NC          | -                   | No connect                                                                                                                                                                                                                           |

| 72            | NC          | —                   | No connect                                                                                                                                                                                                                           |

| 73            | NC          | —                   | No connect                                                                                                                                                                                                                           |

| 74            | NC          | _                   | No connect                                                                                                                                                                                                                           |

| 75            | NC          | _                   | No connect                                                                                                                                                                                                                           |

| 76            | A7          | lpd                 | Address bus bit 7                                                                                                                                                                                                                    |

| 77            | A6          | lpd                 | Address bus bit 6                                                                                                                                                                                                                    |

| 78            | DGND        | GND                 | Digital IO ground                                                                                                                                                                                                                    |

| Pin<br>Number | Pin<br>Name | Type<br>Note<br>2-3 | Description                                                                                                                                                                                                                      |

|---------------|-------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 79            | VDDIO       | Р                   | 3.3V, 2.5V, or 1.8V digital VDDIO input power supply for IO with well decoupling capacitors.                                                                                                                                     |

| 80            | A5          | lpd                 | Address bus bit 5                                                                                                                                                                                                                |

| 81            | A4          | lpd                 | Address bus bit 4                                                                                                                                                                                                                |

| 82            | A3          | lpd                 | Address bus bit 3                                                                                                                                                                                                                |

| 83            | A2          | lpd                 | Address bus bit 2                                                                                                                                                                                                                |

| 84            | A1          | lpd                 | Address bus bit 1                                                                                                                                                                                                                |

| 85            | NC          | _                   | No connect                                                                                                                                                                                                                       |

| 86            | NC          | _                   | No connect                                                                                                                                                                                                                       |

| 87            | BE1N        | lpd                 | Byte Enable 1 Not, Active low for Data byte 1 enable (don't care in 8-bit bus mode).                                                                                                                                             |

| 88            | BE0N        | lpd                 | Byte Enable 0 Not, Active low for Data byte 0 enable.                                                                                                                                                                            |

| 89            | NC          | -                   | No connect                                                                                                                                                                                                                       |

| 90            | DGND        | GND                 | Digital core ground                                                                                                                                                                                                              |

| 91            | VDDC        | Р                   | 1.8V digital core power supply from VDDCO (pin 24) with appropriate filtering.<br>If VDDIO is 1.8V, this pin must be supplied power from the same source as<br>pins 10, 79, 92, 108, and 125 (VDDIO) with appropriate filtering. |

| 92            | VDDIO       | Р                   | 3.3V, 2.5V, or 1.8V digital VDDIO input power supply for IO with well decoupling capacitors.                                                                                                                                     |

| 93            | NC          | _                   | No connect                                                                                                                                                                                                                       |

| 94            | NC          | -                   | No connect                                                                                                                                                                                                                       |

| 95            | NC          | _                   | No connect                                                                                                                                                                                                                       |

| 96            | NC          | -                   | No connect                                                                                                                                                                                                                       |

| 97            | NC          | -                   | No connect                                                                                                                                                                                                                       |

| 98            | NC          | -                   | No connect                                                                                                                                                                                                                       |

| 99            | NC          | _                   | No connect                                                                                                                                                                                                                       |

| 100           | NC          | _                   | No connect                                                                                                                                                                                                                       |

| 101           | NC          | _                   | No connect                                                                                                                                                                                                                       |

| 102           | NC          | _                   | No connect                                                                                                                                                                                                                       |

| 103           | NC          | _                   | No connect                                                                                                                                                                                                                       |

| 104           | NC          | —                   | No connect                                                                                                                                                                                                                       |

| 105           | NC          | _                   | No connect                                                                                                                                                                                                                       |

| 106           | NC          | —                   | No connect                                                                                                                                                                                                                       |

| TABLE 2-1: | SIGNALS FOR 16-BIT | 128-PIN PQFP | (CONTINUED) |

|------------|--------------------|--------------|-------------|

|------------|--------------------|--------------|-------------|

| Pin<br>Number | Pin<br>Name | Type<br>Note<br>2-3 | Description                                                                                  |

|---------------|-------------|---------------------|----------------------------------------------------------------------------------------------|

| 107           | DGND        | GND                 | Digital I/O ground                                                                           |

| 108           | VDDIO       | Р                   | 3.3V, 2.5V, or 1.8V digital VDDIO input power supply for IO with well decoupling capacitors. |

| 109           | NC          | —                   | No connect                                                                                   |

| 110           | D15         | I/O<br>(pd)         | Data bus bit 15                                                                              |

| 111           | D14         | I/O<br>(pd)         | Data bus bit 14                                                                              |

| 112           | D13         | I/O<br>(pd)         | Data bus bit 13                                                                              |

| 113           | D12         | I/O<br>(pd)         | Data bus bit 12                                                                              |

| 114           | D11         | I/O<br>(pd)         | Data bus bit 11                                                                              |

| 115           | D10         | I/O<br>(pd)         | Data bus bit 10                                                                              |

| 116           | D9          | I/O<br>(pd)         | Data bus bit 9                                                                               |

| 117           | D8          | I/O<br>(pd)         | Data bus bit 8                                                                               |

| 118           | D7          | I/O<br>(pd)         | Data bus bit 7                                                                               |

| 119           | D6          | I/O<br>(pd)         | Data bus bit 6                                                                               |

| 120           | D5          | I/O<br>(pd)         | Data bus bit 5                                                                               |

| 121           | D4          | I/O<br>(pd)         | Data bus bit 4                                                                               |

| 122           | D3          | I/O<br>(pd)         | Data bus bit 3                                                                               |

| 123           | DGND        | GND                 | Digital IO ground                                                                            |

| 124           | DGND        | GND                 | Digital core ground                                                                          |

| 125           | VDDIO       | Р                   | 3.3V, 2.5V, or 1.8V digital VDDIO input power supply for IO with well decoupling capacitors. |

| 126           | D2          | I/O<br>(pd)         | Data bus bit 2                                                                               |

| 127           | D1          | I/O<br>(pd)         | Data bus bit 1                                                                               |

| Pin<br>Number | Pin<br>Name                                                                   | Type<br>Note<br>2-3                                                                                      | Description                                                                                                                                                                                                                                                                                  |