# Multi-Channel Low-Voltage Temp Sensors with Shutdown

### EMC1822/23/24/25/43

#### **Features**

- Measures Temperature Rate of Change Calculation with Preemptive Alert(s) Limits

- Up to Four External Temperature Monitors:

- 8-Lead Devices: ±1°C maximum accuracy (-20°C to +105°C T<sub>A</sub>, -40°C to +125°C T<sub>D</sub>)

- ±1.5°C maximum accuracy (-40°C to +125°C  $T_A$ , -40°C to +125°C  $T_D$ )

- 10-Lead Devices: ±1°C maximum accuracy (-20°C to +125°C T<sub>A</sub>, -40°C to +125°C T<sub>D</sub>)

- $-~\pm 1.5^{\circ}\text{C}$  maximum accuracy (-40°C to +125°C  $T_{A},$  -40°C to +125°C  $T_{D})$

- · Internal Temperature Sensor:

- ±1°C maximum accuracy, -40°C to +125°C

- Temperature Sensor Resolution (Internal/External): 0.125°C

- · Resistor Programmable System Shutdown Temperature

- · Configurable Alert Pins

- Operating Voltage: 1.62V to 3.6V

- Temperature Range: -40°C to +125°C

- Other Features: Auto-Beta Compensation, Configurable Ideality Factor, Hottest Diode Compare, Resistance Error Correction

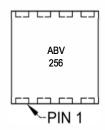

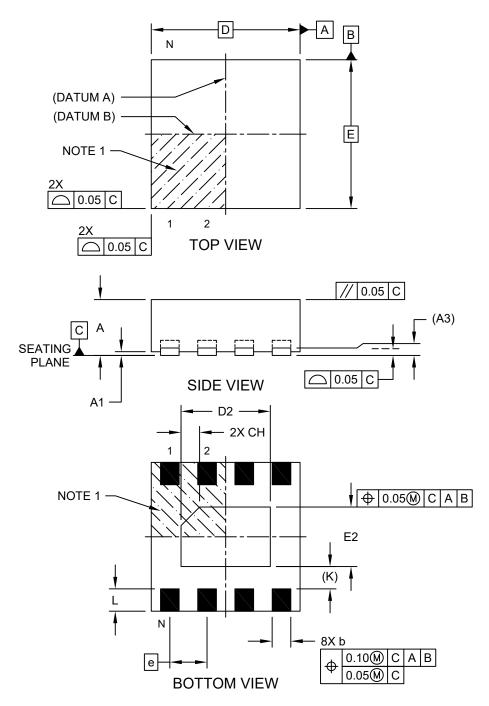

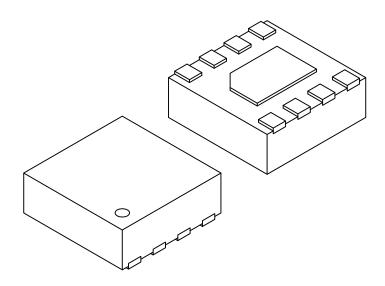

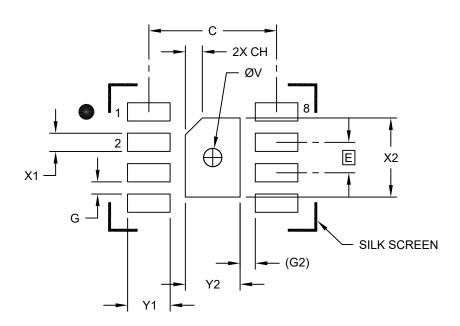

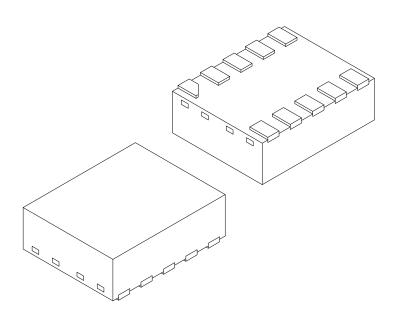

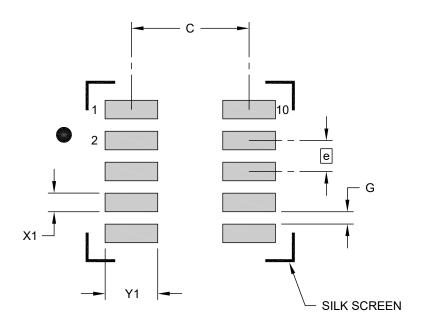

- Available in 8-Lead 2x2 mm WDFN, 10-Lead 2.5x2.0 mm VDFN and 10-Lead MSOP Packages

# **Typical Applications**

- · Temperature Sensitive Storage

- Industrial

- · IoT for Low System Voltage

- · Portable Electronics

- · Handheld Gaming

- Computing

- Food Storage

# **Description**

The EMC1822/23/24/25/43 devices are high-accuracy, two-wire (I<sup>2</sup>C) temperature sensors with resistor programmable system shutdown. The devices monitor up to five temperature channels. Advanced features, such as Resistance Error Correction (REC), Beta Compensation (to support CPU diodes requiring the BJT/Transistor model) and rate of temperature change measurement combine to provide a robust solution for complex environmental monitoring applications.

This device family introduces Rate of Change (ROC) temperature measurement with associated alerts. This provides a preemptive system alert and another protective measurement layer to catch and manage variable system temperatures.

The Resistance Error Correction feature automatically eliminates the temperature error caused by series resistance, allowing for greater flexibility in routing thermal diodes. Beta compensation eliminates temperature errors caused by low, variable beta transistors common in current fine geometry processors. The automatic beta detection feature determines the optimal sensor external diode/transistor settings. This frees up the user from providing unique sensor configurations for each temperature monitoring application. These advanced features plus ±1°C measurement accuracy for both external and internal diode temperatures provide a low-cost, highly flexible and accurate solution for critical temperature monitoring applications.

© 2018-2020 Microchip Technology Inc. Datasheet DS20006048B-page 2

# **Table of Contents**

| Fe  | atures   |                                                | 1  |

|-----|----------|------------------------------------------------|----|

| Тур | oical Ap | oplications                                    | 1  |

| De  | scriptio | n                                              | 2  |

| 1.  | Packa    | age Types                                      | 5  |

| 2.  | Funct    | tional Block Diagram                           | 6  |

| 3.  | Electr   | rical Characteristics                          | 7  |

|     | 3.1.     | Absolute Maximum Ratings                       | 7  |

| 4.  | Typic    | al Operating Curves                            | 11 |

| 5.  | Pin D    | escriptions                                    | 12 |

|     | 5.1.     | Power Supply (V <sub>DD</sub> )                | 13 |

|     | 5.2.     | Diode 1 Pair (DN1/DP1)                         |    |

|     | 5.3.     | System Shutdown                                |    |

|     | 5.4.     | Ground (GND)                                   |    |

|     | 5.5.     | Maskable ALERT (ALERT/THERM2)                  |    |

|     | 5.6.     | SMBus/I <sup>2</sup> C Data (SDA)              |    |

|     | 5.7.     | DP/DP1                                         |    |

|     | 5.8.     | DN/DN1                                         |    |

|     | 5.9.     | DP2                                            |    |

|     |          | DN2                                            |    |

|     |          | Anti-Parallel Diode Pair (DP2/DN3 and DN2/DP3) |    |

|     |          | Anti-Parallel Diode Pair (DP1/DN2 and DN1/DP2) |    |

|     |          | Anti-Parallel Diode Pair (DP3/DN4 and DN3/DP4) |    |

|     |          | SMBus Clock (SCL)                              |    |

|     |          | Exposed Thermal Pad (EP)                       |    |

| 6.  | Detai    | led Description                                | 15 |

| 7.  | Syste    | em Block Diagram                               | 16 |

|     | 7.1.     | Temperature Measurement                        | 16 |

|     | 7.2.     | Temperature Measurement Results and Data       | 16 |

|     | 7.3.     | Limit Registers                                |    |

|     | 7.4.     | Limit Register Interaction                     |    |

|     | 7.5.     | ALERT/THERM2 Output                            |    |

|     | 7.6.     | System Shutdown                                | 19 |

|     | 7.7.     | External Diode Connections                     |    |

|     | 7.8.     | Power States                                   |    |

|     | 7.9.     | Conversion Rates                               |    |

|     | 7.10.    |                                                |    |

|     |          | Digital Filter                                 |    |

|     |          | Beta Compensation                              |    |

|     |          | Resistance Error Correction (REC)              |    |

|     |          | Programmable External Diode Ideality Factor    |    |

|     | -        | ,                                              |    |

|     | 7.15. Diode Faults                        |                                       |    |  |  |  |  |  |  |  |

|-----|-------------------------------------------|---------------------------------------|----|--|--|--|--|--|--|--|

|     | 7.16. Consecutive Alerts                  |                                       |    |  |  |  |  |  |  |  |

|     | 7.17.                                     | "Hottest Of" Comparison               | 28 |  |  |  |  |  |  |  |

|     | 7.18.                                     | Rate of Change                        | 28 |  |  |  |  |  |  |  |

| 8.  | Syste                                     | m Management Bus Protocol             | 31 |  |  |  |  |  |  |  |

|     | 8.1. SMBus Start Bit                      |                                       |    |  |  |  |  |  |  |  |

|     | 8.2.                                      |                                       |    |  |  |  |  |  |  |  |

|     | 8.3.                                      | SMBus Data Bytes                      | 31 |  |  |  |  |  |  |  |

|     | 8.4.                                      | SMBus ACK and NACK Bits               | 31 |  |  |  |  |  |  |  |

|     | 8.5.                                      | SMBus Stop Bit                        | 31 |  |  |  |  |  |  |  |

|     | 8.6.                                      | SMBus Time-out.                       | 31 |  |  |  |  |  |  |  |

|     | 8.7.                                      | SMBus and I <sup>2</sup> C Compliance | 31 |  |  |  |  |  |  |  |

|     | 8.8.                                      | SMBus Protocols                       | 32 |  |  |  |  |  |  |  |

|     | 8.9.                                      | THERM Pin Considerations              | 33 |  |  |  |  |  |  |  |

|     | 8.10.                                     | Register Summary                      | 35 |  |  |  |  |  |  |  |

|     | 8.11.                                     | Data Read Interlock                   | 37 |  |  |  |  |  |  |  |

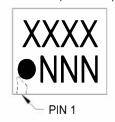

| 9.  | Packa                                     | ging Information                      | 88 |  |  |  |  |  |  |  |

|     | 9.1.                                      | Package Marking Information           | 88 |  |  |  |  |  |  |  |

| 10. | Revisi                                    | on History                            | 95 |  |  |  |  |  |  |  |

| The | Micro                                     | chip Website                          | 06 |  |  |  |  |  |  |  |

|     |                                           |                                       |    |  |  |  |  |  |  |  |

| Pro | duct Cl                                   | nange Notification Service            | 96 |  |  |  |  |  |  |  |

| Cus | tomer                                     | Support                               | 96 |  |  |  |  |  |  |  |

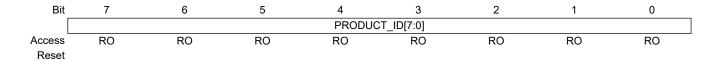

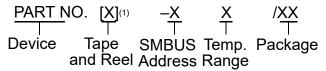

| Pro | duct Id                                   | entification System                   | 97 |  |  |  |  |  |  |  |

| Mic | Microchip Devices Code Protection Feature |                                       |    |  |  |  |  |  |  |  |

| Lea | al Noti                                   | ce                                    | 98 |  |  |  |  |  |  |  |

| Ŭ   |                                           |                                       |    |  |  |  |  |  |  |  |

| Tra | demark                                    | S                                     | 98 |  |  |  |  |  |  |  |

| Qua | Quality Management System                 |                                       |    |  |  |  |  |  |  |  |

| Wo  | Vorldwide Sales and Service 99            |                                       |    |  |  |  |  |  |  |  |

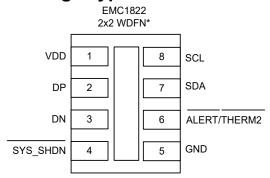

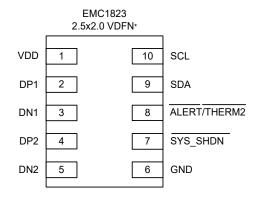

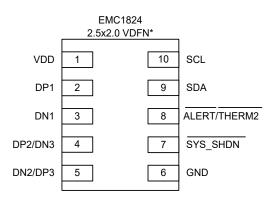

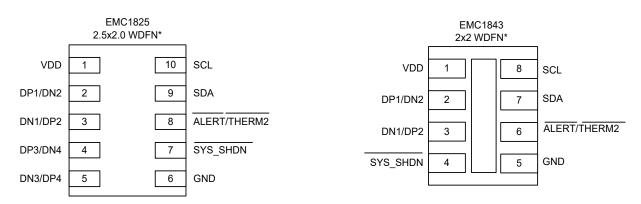

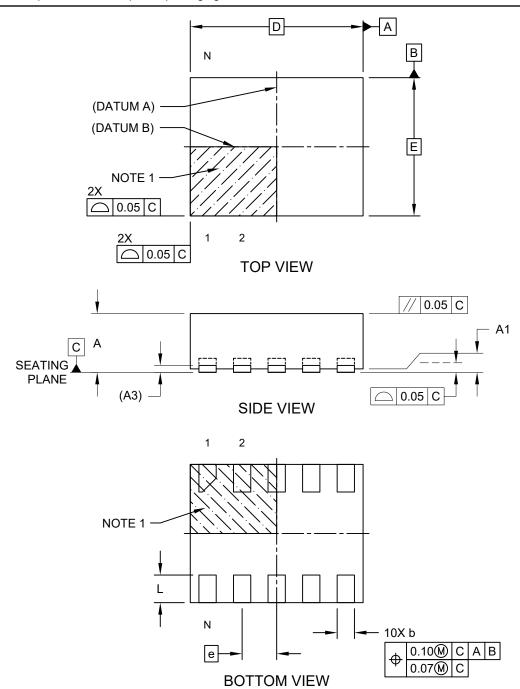

# 1. Package Types

Note: \* Includes Exposed Thermal Pad (EP); see 5. Pin Descriptions

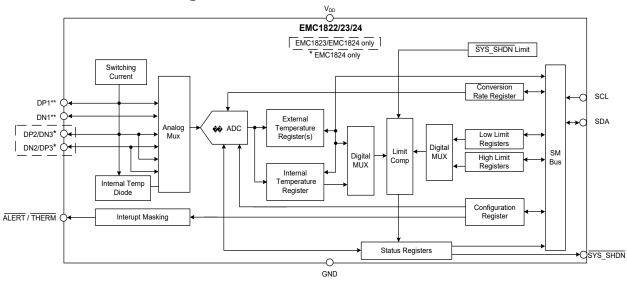

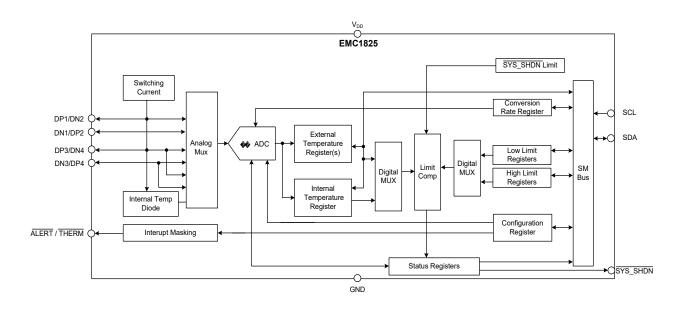

# 2. Functional Block Diagram

### 3. Electrical Characteristics

### 3.1 Absolute Maximum Ratings

$V_{DD}$  4.0V

Voltage at all Input/Output Pins GND – 0.3V to 4.0V

Storage Temperature -65°C to +150°C

Ambient Temperature with Power Applied -40°C to +125°C

Junction Temperature (TJ) +150°C

ESD Protection on All Pins (HBM:MM) (8 kV:400V)

Latch-up Current at Each Pin (+25°C) ±200 mA

**Note:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

Table 3-1. DC Characteristics

Electrical Specifications: Unless otherwise specified, all limits apply for typical values at ambient temperature  $1.62V \le V_{DD} \le +3.6V$  at  $-40^{\circ}C \le T_{A} \le +125^{\circ}C$

| Parameters                        | Sym.                         | Min. | Тур.  | Max. | Units | Conditions                                                                                             |  |  |  |

|-----------------------------------|------------------------------|------|-------|------|-------|--------------------------------------------------------------------------------------------------------|--|--|--|

| Supply Voltage                    | $V_{DD}$                     | 1.62 | _     | 3.6  | V     |                                                                                                        |  |  |  |

| Supply Current                    | I <sub>DD</sub>              | _    | 20    | 80   | μA    | 0.03125 conversion/second, dynamic averaging disabled                                                  |  |  |  |

|                                   |                              | _    | 25    | 164  | μA    | 1 conversion/second, dynamic averaging disabled                                                        |  |  |  |

|                                   |                              | _    | 205   | 432  | μA    | 4 conversions/second, dynamic averaging disabled                                                       |  |  |  |

|                                   |                              | _    | 800   | _    | μA    | > 16 conversions/second, dynamic averaging enabled                                                     |  |  |  |

| Standby Supply Current            | I <sub>DD_OS</sub>           | _    | 15    | 75   | μA    | Device in One-Shot state, no active I <sup>2</sup> C communications, ALERT and THERM pins not asserted |  |  |  |

| Power-on Reset Release<br>Voltage | PORR                         | _    | 1.45  | _    | V     | Rising V <sub>DD</sub>                                                                                 |  |  |  |

| Power-up Timer                    | tPWRT                        | _    | 15    | _    | ms    |                                                                                                        |  |  |  |

| V <sub>DD</sub> Rise Rate         | VDD_RISE                     | 0.05 |       | _    | V/ms  | 0 to 2.75V in ~ 60 ms                                                                                  |  |  |  |

| Internal Temperature Monitor      | Internal Temperature Monitor |      |       |      |       |                                                                                                        |  |  |  |

| Temperature Accuracy              | _                            | _    | ±0.25 | ±1   | °C    |                                                                                                        |  |  |  |

| External Temperature Monitor      |                              |      |       |      |       |                                                                                                        |  |  |  |

**Electrical Characteristics**

| continued                              |                     |                     |                      |                     |       |                                                                             |  |  |

|----------------------------------------|---------------------|---------------------|----------------------|---------------------|-------|-----------------------------------------------------------------------------|--|--|

| Parameters                             | Sym.                | Min.                | Тур.                 | Max.                | Units | Conditions                                                                  |  |  |

| Temperature Accuracy – 8-Lead          | _                   | _                   | ±0.25                | ±1                  | °C    | -20°C < T <sub>A</sub> < 105°C,<br>-40°C < T <sub>D</sub> < +125°C, 2N3904  |  |  |

|                                        |                     | _                   | ±0.25                | ±1.5                | °C    | -40°C < T <sub>A</sub> < +125°C,<br>-40°C < T <sub>D</sub> < +125°C, 2N3904 |  |  |

| Temperature Accuracy – 10-Lead         | _                   | _                   | ±0.25                | ±1                  | °C    | -20°C < T <sub>A</sub> < 125°C,<br>-40°C < T <sub>D</sub> < +125°C, 2N3904  |  |  |

|                                        |                     | _                   | ±0.25                | ±1.5                | °C    | -40°C < T <sub>A</sub> < +125°C,<br>-40°C < T <sub>D</sub> < +125°C, 2N3904 |  |  |

| Temperature Resolution                 | _                   | _                   | 0.125                |                     | °C    |                                                                             |  |  |

| Timing and Capacitive Filter           |                     |                     |                      |                     |       |                                                                             |  |  |

| Time to First<br>Communications        | t <sub>INT_T</sub>  | _                   | 15                   | 20                  | ms    | Time after power-up before ready to begin communications and measurement    |  |  |

| Conversion Time per<br>Channel         | t <sub>CONV</sub>   | _                   | 25                   | _                   | ms    | Default settings                                                            |  |  |

| Time to First Conversion from One-Shot |                     | _                   | 5                    | _                   | ms    |                                                                             |  |  |

| Time to First Conversion from Standby  | t <sub>CONV1</sub>  | _                   | 220                  | _                   | ms    | Default settings                                                            |  |  |

| Capacitive Filter                      | C <sub>FILTER</sub> | _                   | 2.2                  | 2.7                 | nF    | Connected across external diode                                             |  |  |

| ALERT and THERM Pins                   |                     |                     |                      |                     |       |                                                                             |  |  |

| Output Low Voltage                     | V <sub>OL</sub>     | 0.4                 | _                    | _                   | V     | I <sub>SINK</sub> = 8 mA                                                    |  |  |

| Leakage Current                        | I <sub>LEAK</sub>   | _                   | _                    | ±5                  | μA    | ALERT and THERM pins,                                                       |  |  |

|                                        |                     |                     |                      |                     |       | device powered,                                                             |  |  |

|                                        |                     |                     |                      |                     |       | pull-up voltage < 3.6V                                                      |  |  |

| SCL and SDA                            |                     |                     | 1                    |                     |       |                                                                             |  |  |

| Input                                  |                     |                     |                      |                     |       |                                                                             |  |  |

| High-Level Voltage                     | V <sub>IH</sub>     | 0.7 V <sub>DD</sub> | _                    | _                   | V     |                                                                             |  |  |

| Low-Level Voltage                      | V <sub>IL</sub>     | _                   | _                    | 0.3 V <sub>DD</sub> | V     |                                                                             |  |  |

| Input Current                          | I <sub>IN</sub>     | _                   | _                    | ±5                  | μA    | SDA and SCL only                                                            |  |  |

| Output (SDA only)                      |                     |                     |                      |                     |       |                                                                             |  |  |

| Low-Level Voltage                      | V <sub>OL</sub>     | _                   | _                    | 0.4                 | V     | $I_{O}$ = 20 mA, $V_{DD}$ = 1.7V to 3.6V                                    |  |  |

| High-Level Current (leakage)           | I <sub>OH</sub>     | _                   | _                    | 1                   | μA    | V <sub>OH</sub> = V <sub>DD</sub>                                           |  |  |

| Low-Level Current                      | I <sub>OL</sub>     | _                   | _                    | 20                  | mA    | V <sub>OL</sub> = 0.4V, V <sub>DD</sub> = 1.62V to 3.6V                     |  |  |

| Capacitance                            | C <sub>IN</sub>     | _                   | 5                    | _                   | pF    |                                                                             |  |  |

| SDA and SCL Inputs                     |                     |                     |                      |                     |       |                                                                             |  |  |

| Hysteresis                             | V <sub>HYST</sub>   | _                   | 0.05 V <sub>DD</sub> | _                   | V     |                                                                             |  |  |

**Electrical Characteristics**

#### **Table 3-2. Thermal Specifications**

Electrical Characteristics: Unless otherwise specified,  $1.62V \le V_{DD} \le 3.6V$  at  $-40^{\circ}C \le T_{A} \le +125^{\circ}C$

| Parameters                                   | Sym.           | Min. | Тур.  | Max. | Units | Test Conditions                                                       |

|----------------------------------------------|----------------|------|-------|------|-------|-----------------------------------------------------------------------|

| Temperature Ranges                           |                |      |       |      |       |                                                                       |

| Specified Temperature Range                  | T <sub>A</sub> | -40  | _     | +125 | °C    |                                                                       |

| Operating Temperature Range                  | T <sub>A</sub> | -40  | _     | +125 | °C    |                                                                       |

| Storage Temperature Range                    |                | -65  | _     | +125 | °C    |                                                                       |

| Thermal Package Resistances                  |                |      |       |      |       |                                                                       |

| Thermal Resistance, 8-Lead WDFN, 2x2 mm      | $\theta_{JA}$  | _    | 141.3 | _    | °C/W  | JEDEC 2s2p,                                                           |

| Thermal Resistance, 10-Lead VDFN, 2.5x2.0 mm | $\theta_{JA}$  | _    | 78    | _    | °C/W  | board size 76.2 x 114.3 x 1.6 mm,<br>one thermal via, airflow = 0 m/s |

| Thermal Resistance, 10-Lead MSOP, 3x3 mm     | $\theta_{JA}$  |      | 132.2 | _    | °C/W  |                                                                       |

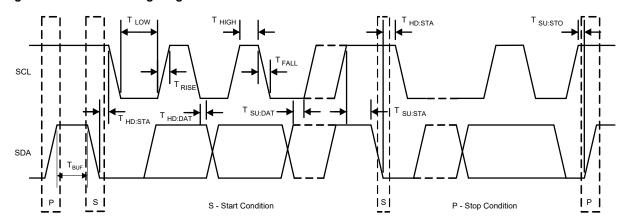

#### Table 3-3. SMBus Module Specifications

Operating Conditions: Unless otherwise indicated, 1.62V  $\leq$  V<sub>DD</sub>  $\leq$  3.6V at -40°C  $\leq$  T<sub>A</sub>  $\leq$  +85°C

| Characteristic              | Sym.                 | Min. | Тур. | Max. | Units | Conditions                          |

|-----------------------------|----------------------|------|------|------|-------|-------------------------------------|

| SMBus Timing                | ,                    |      |      |      |       |                                     |

| Clock Frequency             | f <sub>SMB</sub>     | 10   | _    | 400  | kHz   |                                     |

| Spike Suppression           | t <sub>SP</sub>      | _    | _    | 50   | ns    |                                     |

| Bus Free Time Stop to Start | t <sub>BUF</sub>     | 1.3  | _    | _    | μs    |                                     |

| Hold Time: Start            | t <sub>HD:STA</sub>  | 0.6  | _    | _    | μs    |                                     |

| Setup Time: Start           | t <sub>SU:STA</sub>  | 0.6  | _    | _    | μs    |                                     |

| Setup Time: Stop            | t <sub>SU:STO</sub>  | 0.6  | _    | _    | μs    |                                     |

| Data Hold Time              | t <sub>HD:DAT</sub>  | 0    | _    | _    | μs    | When transmitting to the master     |

| Data Hold Time              | t <sub>HD:DAT</sub>  | 0    | _    | _    | μs    | When receiving from the master      |

| Data Setup Time             | t <sub>SU:DAT</sub>  | 100  | _    | _    | ns    |                                     |

| Clock Low Period            | t <sub>LOW</sub>     | 1.3  | _    | _    | μs    |                                     |

| Clock High Period           | t <sub>HIGH</sub>    | 0.6  | _    | _    | μs    |                                     |

| Clock/Data Fall Time        | t <sub>FALL</sub>    | _    | _    | 300  | ns    | Min = 20 + 0.1 C <sub>LOAD</sub> ns |

| Clock/Data Rise Time        | t <sub>RISE</sub>    | _    | _    | 300  | ns    | Min = 20 + 0.1 C <sub>LOAD</sub> ns |

| Capacitive Load             | C <sub>LOAD</sub>    | _    | _    | 400  | pF    | Per bus line                        |

| Time-out                    | t <sub>TIMEOUT</sub> | 25   | _    | 35   | ms    | Disabled by default                 |

**Electrical Characteristics**

Figure 3-1. SMBus Timing Diagram

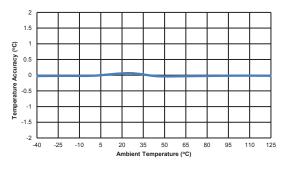

# 4. Typical Operating Curves

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (for example, outside specified power supply range) and therefore outside the warranted range.

Figure 4-1. Internal Temperature Error vs. Ambient Temperature ( $V_{DD}$  = 2.5V,  $T_{D}$  = +25°C, 2N3904)

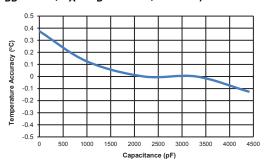

Figure 4-3. Temperature Error vs. Filter Capacitor  $(V_{DD} = 2.5V, T_A = T_D = +25^{\circ}C, 2N3904)$

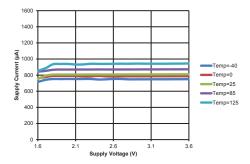

Figure 4-5.  $I_{DD}$  vs.  $V_{DD}$  Across Temperature

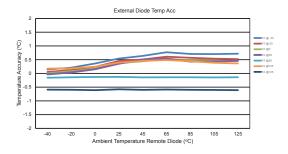

Figure 4-2. Temperature Accuracy vs. Remote Diode Temperature,  $V_{DD} = 1.8V$

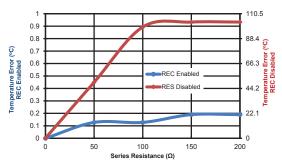

Figure 4-4. Temperature Error vs. Series Resistance ( $T_A = +25^{\circ}C$ ,  $V_{DD} = 1.8V$ )

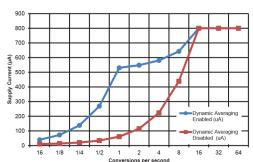

Figure 4-6. Supply Current vs. Conversion Rate  $(T_A = +25^{\circ}C, V_{DD} = 1.8V)$

# 5. Pin Descriptions

The EMC1822/23/24/25/43 has five variants that include features unique to each device. Refer to the table to determine applicability of the pin descriptions.

The description of the pins is listed in the following table.

**Table 5-1. Pin Function Table**

| Pin Name         | EMC1822 | EMC1823 | EMC1824 | EMC1825 | EMC1843      | Pin<br>Type | Description                |

|------------------|---------|---------|---------|---------|--------------|-------------|----------------------------|

| $V_{DD}$         | 1       | 1       | 1       | 1       | 1            | Р           | Power                      |

| GND              | 5       | 6       | 6       | 6       | 5            | Р           | Ground                     |

| ALERT/<br>THERM2 | 6       | 8       | 8       | 8       | 6            | OD          | I <sup>2</sup> C alert pin |

| SYS_SHDN         | 4       | 7       | 7       | 7       | 4            | OD          | System shutdown            |

| SDA              | 7       | 9       | 9       | 9       | 7            | OD          | I <sup>2</sup> C data      |

| SCL              | 8       | 10      | 10      | 10      | 8            | OD          | I <sup>2</sup> C clock     |

| DP1              | 2       | 2       | 2       | _       | _            | Α           | Diode 1 connection         |

| DN1              | 3       | 3       | 3       | _       | _            | Α           | Diode 1 connection         |

| DP2              | _       | 4       | _       | _       | _            | Α           | Diode 2 connection         |

| DN2              | _       | 5       | _       | _       | <del>_</del> | Α           | Diode 2 connection         |

| DP2/DN3          | _       | _       | 4       | _       | _            | А           | Diode 2/3 connection       |

| DN2/DP3          | _       | _       | 5       | _       | _            | А           | Diode 2/3 connection       |

| DP1/DN2          | _       | _       | _       | 2       | 2            | Α           | Diode 1/2 connection       |

| DN1/DP2          | _       | _       | _       | 3       | 3            | Α           | Diode 1/2 connection       |

| DP3/DN4          | _       | _       | _       | 4       | _            | Α           | Diode 3/4 connection       |

| DN3/DP4          | _       | _       | _       | 5       | _            | А           | Diode 3/4 connection       |

**Legend:** P = Power pin; A = Analog pin; OD = Open-Drain pin

### 5.1 Power Supply (V<sub>DD</sub>)

This pin is used to supply power to the device.

### **5.2** Diode 1 Pair (DN1/DP1)

Remote Diode 1 anode (DP1) and cathode (DN1) pins.

### 5.3 System Shutdown

The EMC1822/23/24/25/43 devices contain a hardware configured temperature limit circuit that controls the SYS\_SHDN pin. The threshold temperature is determined by the pull-up resistors on both the SYS\_SHDN and ALERT pins. Note, Standby and One-Shot modes cannot be enabled in device configurations including system shutdown functionality .

The final temperature decode is the responsibility of the digital block. The overall decode is shown in Table 7-3.

The hardware shutdown circuitry measures the External Diode 1 channel and compares it against the hardware thermal shutdown limit. The THERM pin consecutive alert counter (default 4 for the SYS\_SHDN pin) applies to this comparison. If the temperature meets or exceeds the limit for the number of consecutive measurements, the SYS\_SHDN pin is asserted. The SYS\_SHDN pin remains asserted until the temperature drops below the limit minus 10°C. As well, all of the measurement channels (including the External Diode 1 channel) can be configured to assert the SYS\_SHDN pin. If a channel is configured to assert the SYS\_SHDN pin, the temperature on the measured channel must exceed the programmed therm limit value. This is treated in the same way as the THERM output.

### 5.4 Ground (GND)

This pin is used to ground the device.

#### 5.5 Maskable ALERT (ALERT/THERM2)

This pin asserts when a diode temperature exceeds the ALERT threshold. This pin may be masked by register settings.

# 5.6 SMBus/I<sup>2</sup>C Data (SDA)

This is the open-drain, bidirectional data pin for SMBus communication.

#### 5.7 DP/DP1

· DP/DP1: DP and DP1 anode

#### 5.8 DN/DN1

· DN/DN1: DN and DN1 cathode

#### 5.9 DP2

DP2: DP2 anode

**Datasheet**

**Pin Descriptions**

#### 5.10 DN2

· DN2: DN2 cathode

### 5.11 Anti-Parallel Diode Pair (DP2/DN3 and DN2/DP3)

• DP2/DN3: DP2 anode and DN3 cathode

• DN2/DP3: DN2 cathode and DP3 anode

#### 5.12 Anti-Parallel Diode Pair (DP1/DN2 and DN1/DP2)

• DP1/DN2: DP1 anode and DN2 cathode

• DN1/DP2: DN1 cathode and DP2 anode

### 5.13 Anti-Parallel Diode Pair (DP3/DN4 and DN3/DP4)

• DP3/DN4: DP3 anode and DN4 cathode

DN3/DP4: DN3 cathode and DP4 anode

### 5.14 SMBus Clock (SCL)

This is the SMBus/I<sup>2</sup>C input clock pin for SMBus communication.

# 5.15 Exposed Thermal Pad (EP)

There is no internal connection between the Exposed Thermal Pad (EP) and the GND pin. They must be connected to the same electric potential on the Printed Circuit Board (PCB). Grounding is recommended for mechanical support.

**Detailed Description**

# 6. Detailed Description

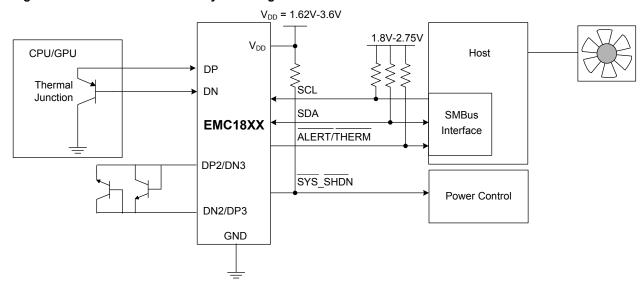

The EMC1822/23/24/25/43 devices monitor one internal diode and up to four externally connected temperature diodes.

Thermal management is performed in cooperation with a host device. This consists of the host reading the temperature data of both the external and internal temperature diodes of the EMC1822/23/24/25/43 and using that data to manage thermal events or to control the speed of one or more fans.

This device family introduces Rate of Change temperature measurement with associated alerts. This provides a preemptive system alert and another protective measurement layer to catch and manage variable system temperatures. Resistance Error Correction automatically eliminates the temperature error caused by series resistance. This feature allows for routing long traces and off-board connections with wires, if desired. Automatic beta compensation eliminates the need for substrate diode and transistor configurations.

The EMC1822/23/24/25/43 family has two levels of monitoring. The first provides a maskable ALERT signal to the host when the measured temperatures exceed user-programmable limits. This allows the EMC1822/23/24/25/43 to be used as an independent thermal watchdog to warn the host of temperature hot spots without direct control by the host. The second level of monitoring provides a nonmaskable interrupt on the THERM pin if the measured temperatures meet or exceed a second programmable limit.

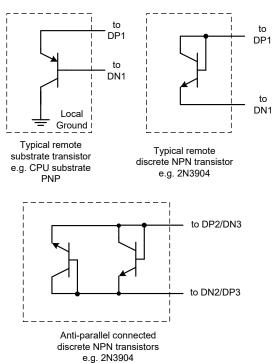

The EMC1822 is a single channel remote temperature sensor, while the EMC1823 is a dual channel remote temperature sensor. The remote channels for this selection of devices can support substrate diodes, discrete diode connected transistors or CPU/GPU thermal diodes.

The EMC1824 supports Anti-Parallel Diode (APD) only on one channel. For the channel that does not support APD functionality, substrate diodes, discrete diode connected transistors or CPU/GPU thermal diodes are supported. For the channel that supports APD, only discrete diode connected transistors may be implemented. However, if APD is disabled on the EMC1824, then the channel that supports APD will be functional with substrate diodes, discrete diode connected transistors and CPU/GPU thermal diodes.

The EMC1825 and EMC1843 support APD on all channels. When APD is enabled, the channels support only diode connected transistors. If APD is disabled, then the channels will support substrate transistors, discrete diode connected transistors and CPU/GPU thermal diodes.

**Note:** Disabling APD functionality to implement substrate diodes on devices that support APD eliminates the benefit of APD (two diodes on one channel).

# 7. System Block Diagram

The figure below shows a system-level block diagram of the EMC1822/23/24/25/43.

Figure 7-1. EMC1822/23/24/25/43 System Diagram

### 7.1 Temperature Measurement

The EMC1822/23/24/25/43 device family can monitor the temperature of up to four externally connected diodes. Each external diode channel is configured with Resistance Error Correction and Beta Compensation based on user settings and system requirements.

The devices contain programmable high, low and therm limits for all measured temperature channels. If the measured temperature goes below the low limit or above the high limit, the  $\overline{\text{ALERT}}$  pin can be asserted (based on user settings). If the measured temperature meets or exceeds the therm limit, the  $\overline{\text{THERM}}$  pin is asserted unconditionally, providing two tiers of temperature detection.

### 7.2 Temperature Measurement Results and Data

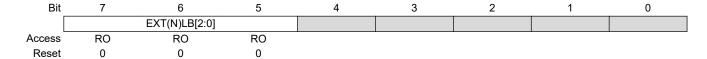

The temperature measurement results are stored in the internal and external temperature registers. These are then compared with the values stored in the High and Low Limit registers. Both external and internal temperature measurements are stored in 11-bit format with the eight Most Significant bits (MSbs) stored in a high-byte register and the three Least Significant bits (LSbs) stored in the three MSB positions of the low-byte register. All other bits of the low-byte register are set to zero.

The EMC1822/23/24/25/43 family has two selectable temperature ranges. The default range is from 0°C to +127°C and the temperature is represented as a binary number able to report a temperature from 0°C to +127.875°C in 0.125°C steps.

The extended range is an extended temperature range, from -64°C to +191°C. The data format is a binary number offset by 64°C. The extended range is used to measure temperature diodes with a large known offset (such as CPU/GPU processor diodes) where the diode temperature plus the offset would be equivalent to a temperature higher than +127°C.

The following table shows the default and extended range formats.

**Table 7-1. Temperature Data Format**

| Temperature (°C) | Default Range 0°C to 127°C | Extended Range<br>-64°C to +191°C |

|------------------|----------------------------|-----------------------------------|

| Diode Fault      | 000 0000 0000              | 000 0000 0000                     |

| -64              | 000 0000 0000              | 000 0000 0000 (Note 1)            |

| -1               | 000 0000 0000              | 001 1111 1000                     |

| 0                | 000 0000 0000 (Note 2)     | 010 0000 0000                     |

| 0.125            | 000 0000 0001              | 010 0000 0001                     |

| 1                | 000 0000 1000              | 010 0000 1000                     |

| 64               | 010 0000 0000              | 100 0000 0000                     |

| 65               | 010 0000 1000              | 100 0000 1000                     |

| 127              | 011 1111 1000              | 101 1111 1000                     |

| 127.875          | 011 1111 1111              | 101 1111 1111                     |

| 128              | 011 1111 1111 (Note 3)     | 110 0000 0000                     |

| 190              | 011 1111 1111              | 111 1111 0000                     |

| 191              | 011 1111 1111              | 111 1111 1000                     |

| ≥ 191.875        | 011 1111 1111              | 111 1111 1111 (Note 4)            |

#### Notes:

- 1. In the extended range, all temperatures below -64°C are reported as -64°C.

- 2. In Default mode, all temperatures below 0°C are reported as 0°C.

- 3. For the default range, all temperatures above +127.875°C are reported as +127.875°C.

- For the extended range, all temperatures above +191.875°C are reported as +191.875°C.

#### 7.3 Limit Registers

The device contains both high and low limits for all temperature channels. If the measured temperature exceeds the high limit, then the corresponding status bit is set and the ALERT pin is asserted. Likewise, if the measured temperature is less than or equal to the low limit, the corresponding status bit is set and the ALERT pin is asserted.

The data format for the limits must match the selected data format for the temperature, so that if the extended temperature range is used, the limits must be programmed in the extended data format.

The Limit registers with multiple addresses are fully accessible at either address.

When the device is in the Standby state, updating the Limit registers will have no effect until the next conversion cycle occurs. This can be initiated via a write to the ONE SHOT Register (Address 0Fh; ONE SHOT) or by clearing the RUN/STANDBY bit (see CONFIG, Address 03h).

### 7.4 Limit Register Interaction

The various Limit registers in the device interact based on both external conditions present on the diode pins, as well as changes in register bits in the I<sup>2</sup>C interface.

#### 7.4.1 High Limit Register

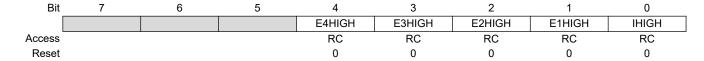

The High Limit Status register contains the status bits that are set when a temperature channel high limit is exceeded. If any of these bits are set, then the HIGH Status bit in the Status register is set. Reading from the High Limit Status register clears all bits. Reading from the register will also clear the HIGH Status bit in the Status register.

System Block Diagram

The ALERT pin will be set if the programmed number of consecutive alert counts has been met and any of these status bits are set.

The status bits remain set until a read is performed unless the ALERT pin is configured as a comparator output (see 7.5.2 ALERT/THERM2 Pin in Therm Mode).

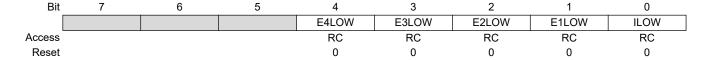

#### 7.4.2 Low Limit Register

The Low Limit Status register contains the status bits that are set when a temperature channel drops below the low limit. If any of these bits are set, then the LOW Status bit in the Status register is set. Reading from the Low Limit Status register clears all bits.

The ALERT pin will be set if the programmed number of consecutive alert counts has been met and any of these status bits are set.

The status bits will remain set until a read is performed, unless the ALERT pin is configured as a comparator output (see 7.5.2 ALERT/THERM2 Pin in Therm Mode).

#### 7.4.3 Therm Limit Register

The Therm Limit registers are used to determine whether a critical thermal event has occurred. If the measured temperature exceeds the therm limit, the THERM pin is asserted. The limit setting must match the chosen data format of the temperature reading registers.

Unlike the ALERT pin, the THERM pin cannot be masked. Additionally, the THERM pin is released once the temperature drops below the corresponding threshold, minus the Therm Hysteresis.

### 7.5 ALERT/THERM2 Output

The ALERT/THERM2 pin is an open-drain output and requires a pull-up resistor to V<sub>DD</sub>, and has two modes of operation: Interrupt mode and Comparator mode. The mode of the ALERT/THERM2 output is selected through the ALERT/THERM2 bit (see CONFIG, Address 03h).

#### 7.5.1 ALERT/THERM2 Pin Interrupt Mode

When configured to operate in Interrupt mode, the ALERT/THERM2 pin asserts low when an out-of-limit measurement (less than or equal to the low limit or greater than the high limit) is detected on any diode or when a Diode Fault is detected. The ALERT/THERM2 pin will remain asserted as long as an out-of-limit condition remains. Once the out-of-limit condition has been removed, the ALERT/THERM2 pin remains asserted until the appropriate status bits are cleared.

The ALERT/THERM2 pin can be masked by setting the MASK\_ALL bit. Once the ALERT/THERM2 pin has been masked, it is deasserted and remains as such until the MASK\_ALL bit is cleared by the user. Any interrupt conditions that occur while the ALERT/THERM2 pin is masked causes the STATUS register to be updated normally. There are also individual channel masks (see 8.11.22 DIODE FAULT MASK.)

The ALERT/THERM2 pin is used as an interrupt signal or as an I<sup>2</sup>C Alert signal that allows an SMBus/I<sup>2</sup>C slave to communicate an error condition to the master. One or more ALERT/THERM2 outputs can be hard-wired together.

#### 7.5.2 ALERT/THERM2 Pin in Therm Mode

When the ALERT/THERM2 pin is configured to operate in Therm mode, it becomes asserted if any of the measured temperatures exceed the respective high limit. The ALERT/THERM2 pin remains asserted until all temperatures drop below the corresponding high limit, minus the Therm Hysteresis value.

When the ALERT/THERM2 pin is asserted in Therm mode, the corresponding High Limit Status bits are set. Reading these bits does not clear them until the ALERT/THERM2 pin is deasserted. Once the ALERT/THERM2 pin is deasserted, the status bits are automatically cleared.

The MASK\_ALL bit does not block the ALERT/THERM2 pin in this mode; however, the individual channel masks prevent the respective channel from asserting the ALERT/THERM2 pin.

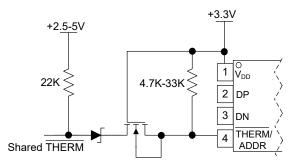

# 7.6 System Shutdown

The EMC1822/23/24/25/43 devices contain a hardware configured temperature limit circuit that controls the  $\overline{SYS\_SHDN}$  pin. The threshold temperature is determined by the pull-up resistors on both the  $\overline{SYS\_SHDN}$  and  $\overline{ALERT}$  pins. Note, Standby and One-shot modes cannot be enabled in device configurations, including system shutdown functionality .

Table 7-2. Pull-Up Resistor Values

| Pull-up Resistor | Bit 2 | Bit 1 | Bit 0 |

|------------------|-------|-------|-------|

| 4.7k             | 0     | 0     | 0     |

| 6.8k             | 0     | 0     | 1     |

| 10k              | 0     | 1     | 0     |

| 15k              | 0     | 1     | 1     |

| 20k 1            |       | 0     | 0     |

| 33k              | 1     | 0     | 1     |

The final temperature decode is the responsibility of the digital block. The overall decode is shown in Table 7-3.

Table 7-3. Temperature Select Encoding

| SYS_S | HDN Pull-up [ | Decode | ALE | RT Pull-up De | Combined<br>Decode<br>(HEX) | Threshold<br>Temperature |      |

|-------|---------------|--------|-----|---------------|-----------------------------|--------------------------|------|

| 2     | 1             | 0      | 2   | 1             | 0                           |                          |      |

| 0     | 0             | 0      | 0   | 0             | 0                           | 00h                      | 77°C |

| 0     | 0             | 0      | 0   | 0             | 1                           | 01h                      | 78°C |

| 0     | 0             | 0      | 0   | 1             | 0                           | 02h                      | 79°C |

| 0     | 0             | 0      | 0   | 1             | 1                           | 03h                      | 80°C |

| 0     | 0             | 0      | 1   | 0             | 0                           | 04h                      | 81°C |

| 0     | 0             | 0      | 1   | 0             | 1                           | 05h                      | 82°C |

| 0     | 0             | 1      | 0   | 0             | 0                           | 08h                      | 83°C |

| 0     | 0             | 1      | 0   | 0             | 1                           | 09h                      | 84°C |

| 0     | 0             | 1      | 0   | 1             | 0                           | 0Ah                      | 85°C |

| 0     | 0             | 1      | 0   | 1             | 1                           | 0Bh                      | 86°C |

| 0     | 0             | 1      | 1   | 0             | 0                           | 0Ch                      | 87°C |

| 0     | 0             | 1      | 1   | 0             | 1                           | 0Dh                      | 88°C |

| 0     | 1             | 0      | 0   | 0             | 0                           | 10h                      | 89°C |

| 0     | 1             | 0      | 0   | 0             | 1                           | 11h                      | 90°C |

| 0     | 1             | 0      | 0   | 1             | 0                           | 12h                      | 91°C |

| 0     | 1             | 0      | 0   | 1             | 1                           | 13h                      | 92°C |

| 0     | 1             | 0      | 1   | 0             | 0                           | 14h                      | 93°C |

| 0     | 1             | 0      | 1   | 0             | 1                           | 15h                      | 94°C |

**System Block Diagram**

| continued |                         |   |   |               |                             |                          |       |  |  |

|-----------|-------------------------|---|---|---------------|-----------------------------|--------------------------|-------|--|--|

| SYS_S     | SYS_SHDN Pull-up Decode |   |   | RT Pull-up De | Combined<br>Decode<br>(HEX) | Threshold<br>Temperature |       |  |  |

| 0         | 1                       | 1 | 0 | 0             | 0                           | 18h                      | 95°C  |  |  |

| 0         | 1                       | 1 | 0 | 0             | 1                           | 19h                      | 96°C  |  |  |

| 0         | 1                       | 1 | 0 | 1             | 0                           | 1Ah                      | 97°C  |  |  |

| 0         | 1                       | 1 | 0 | 1             | 1                           | 1Bh                      | 98°C  |  |  |

| 0         | 1                       | 1 | 1 | 0             | 0                           | 1Ch                      | 99°C  |  |  |

| 0         | 1                       | 1 | 1 | 0             | 1                           | 1Dh                      | 100°C |  |  |

| 1         | 0                       | 0 | 0 | 0             | 0                           | 20h                      | 101°C |  |  |

| 1         | 0                       | 0 | 0 | 0             | 1                           | 21h                      | 102°C |  |  |

| 1         | 0                       | 0 | 0 | 1             | 0                           | 22h                      | 103°C |  |  |

| 1         | 0                       | 0 | 0 | 1             | 1                           | 23h                      | 104°C |  |  |

| 1         | 0                       | 0 | 1 | 0             | 0                           | 24h                      | 105°C |  |  |

| 1         | 0                       | 0 | 1 | 0             | 1                           | 25h                      | 106°C |  |  |

|           | 0                       | 1 | 0 | 0             | 0                           | 28h                      | 107°C |  |  |

| 1         | 0                       | 1 | 0 | 0             | 1                           | 29h                      | 108°C |  |  |

| 1         | 0                       | 1 | 0 | 1             | 0                           | 2Ah                      | 109°C |  |  |

| 1         | 0                       | 1 | 0 | 1             | 1                           | 2Bh                      | 110°C |  |  |

| 1         | 0                       | 1 | 1 | 0             | 0                           | 2Ch                      | 111°C |  |  |

| 1         | 0                       | 1 | 1 | 0             | 1                           | 2Dh                      | 112°C |  |  |

The hardware shutdown circuitry measures the External Diode 1 channel and compares it against the hardware thermal shutdown limit. The THERM pin consecutive alert counter (Default 4 for the SYS\_SHDN pin) applies to this comparison. If the temperature meets or exceeds the limit for the number of consecutive measurements, the SYS\_SHDN pin is asserted. The SYS\_SHDN pin remains asserted until the temperature drops below the limit minus 10°C. As well, all of the measurement channels (including the External Diode 1 channel) can be configured to assert the SYS\_SHDN pin. If a channel is configured to assert the SYS\_SHDN pin, the temperature on the measured channel must exceed the programmed therm limit value. This is treated in the same way as the THERM output. For additional information, see 8.11.17 HARDWARE THERMAL SHUTDOWN LIMIT.

#### 7.7 External Diode Connections

The EMC1822 can be configured to measure a CPU substrate transistor, a discrete 2N3904 thermal diode or a CPU/GPU processor diode. The diodes can be connected as indicated in the figure below.

The EMC1823 can be configured to measure a CPU substrate transistor, a discrete 2N3904 thermal diode or a CPU/GPU processor diode on the External Diode 1 or External Diode 2 channels. For the EMC1824, External Diode 2 and External Diode 3 channels are configured to measure a pair of discrete anti-parallel diodes (shared on pins DP2 and DN2). The supported configurations for the external diode channels are shown in the following figure.

Figure 7-2. Diode Configurations

#### 7.8 Power States

The EMC1822/23/24/25/43 devices have two power states: Active and Standby.

- Active (Run) In this state, the ADC is converting on all temperature channels at the programmed conversion rate. The temperature data is updated at the end of every conversion and the limits are checked. In the Active state, writing to the One-Shot register has no effects.

- Standby (One-Shot) While the device is in Standby, the host can initiate a conversion cycle on demand. After the conversion cycle is complete, the device returns to the Standby state.

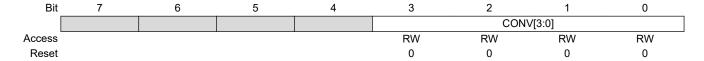

#### 7.9 Conversion Rates

The EMC1822/23/24/25/43 devices may be configured for different conversion rates based on the system requirements. The default conversion rate is four conversions per second. Other available conversion rates are shown in the Conversion Rate table.

Table 7-4. Conversion Rate

|     | CONV< | 3:0> |   |   | Conversions/ Second |

|-----|-------|------|---|---|---------------------|

| HEX | 3     | 2    | 1 | 0 | Conversions/ Second |

| 0h  | 0     | 0    | 0 | 0 | 1/16                |

| 1h  | 0     | 0    | 0 | 1 | 1/8                 |

| 2h  | 0     | 0    | 1 | 0 | 1/4                 |

| 3h  | 0     | 0    | 1 | 1 | 1/2                 |

| 4h  | 0     | 1    | 0 | 0 | 1                   |

| 5h  | 0     | 1    | 0 | 1 | 2                   |

| continued |            |   |   |   |                     |  |  |  |  |

|-----------|------------|---|---|---|---------------------|--|--|--|--|

| CONV<3:0> |            |   |   |   | Conversions/ Second |  |  |  |  |

| HEX       | 3          | 2 | 1 | 0 | Conversions/ Second |  |  |  |  |

| 6h        | 0          | 1 | 1 | 0 | 4 (default)         |  |  |  |  |

| 7h        | 0          | 1 | 1 | 1 | 8                   |  |  |  |  |

| 8h        | 1          | 0 | 0 | 0 | 16                  |  |  |  |  |

| 9h        | 1          | 0 | 0 | 1 | 32                  |  |  |  |  |

| Ah        | 1          | 0 | 1 | 0 | 64                  |  |  |  |  |

| Bh-Fh     | All Others |   |   |   | 1                   |  |  |  |  |

### 7.10 Dynamic Averaging

Dynamic averaging causes the EMC1822/23/24/25/43 devices to measure the external diode channels for an extended time based on the selected conversion rate. This functionality can be disabled for increased power savings at the lower conversion rates. When dynamic averaging is enabled, the devices automatically adjust the sampling and measurement time for the external diode channels. This allows the devices to average 2x to 16x longer than the normal 11-bit operation (nominally 21 ms per channel) while still maintaining the selected conversion rate. The benefits of dynamic averaging are improved noise rejection due to the longer integration time as well as less random variation of the temperature measurement.

When enabled, the dynamic averaging applies when a one-shot command is issued. The devices perform the desired averaging during the one-shot operation according to the selected conversion rate.

When enabled, the dynamic averaging affects the average supply current based on the chosen conversion rate as shown in the following table.

Table 7-5. Supply Current vs. Conversion Rate for EMC1825

|                 | Average Supply          | Current  | Averaging Factor (based on 11-bit operation) |          |  |  |  |  |

|-----------------|-------------------------|----------|----------------------------------------------|----------|--|--|--|--|

| Conversion Rate | Dynamic Averaging State |          |                                              |          |  |  |  |  |

|                 | Enabled (default)       | Disabled | Enabled (default)                            | Disabled |  |  |  |  |

| 1/16s           | 144 μΑ                  | 80 µA    | 16x                                          | 1x       |  |  |  |  |

| 1/8s            | 213 μΑ                  | 86 µA    | 16x                                          | 1x       |  |  |  |  |

| 1/4s            | 351 μΑ                  | 97 μΑ    | 16x                                          | 1x       |  |  |  |  |

| 1/2s            | 627 µA                  | 120 µA   | 16x                                          | 1x       |  |  |  |  |

| 1/s             | 637 µA                  | 164 µA   | 16x                                          | 1x       |  |  |  |  |

| 2/s             | 659 µA                  | 253 μΑ   | 16x                                          | 1x       |  |  |  |  |

| 4/s (default)   | 703 µA                  | 432 µA   | 8x                                           | 1x       |  |  |  |  |

| 8/s             | 790 µA                  | 790 µA   | 4x                                           | 1x       |  |  |  |  |

| 16/s            | 830 μΑ                  | 830 µA   | 2x                                           | 1x       |  |  |  |  |

| 32/s            | 830 μΑ                  | 830 µA   | 1x                                           | 1x       |  |  |  |  |

| 64/s            | 1065 µA                 | 1065 µA  | 0.5x                                         | 0.5x     |  |  |  |  |

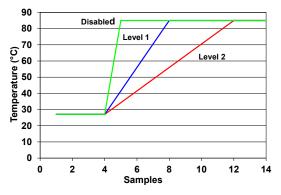

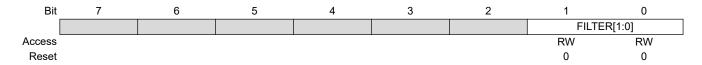

### 7.11 Digital Filter

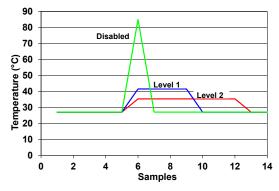

To reduce the effect of noise and temperature spikes on the reported temperature, the external diode channel uses a programmable digital filter. This filter can be configured as Level 1, Level 2 or disabled (default). The typical filter performance is shown in the figures below. The Filter Configuration register controls the digital filter on the External Diode 1 channel.

To reduce complexity, the digital filter only applies to the External Diode Channels 1 and 2. Furthermore, this is only the case when APD is not enabled for a given channel. It applies after the digital block has taken the appropriate 11 bits based on the dynamic averaging.

Table 7-6. Filter Settings

| FILTE | R<1:0> | Averaging          |

|-------|--------|--------------------|

| 1     | 0      | Averaging          |

| 0     | 0      | Disabled (default) |

| 0     | 1      | Level 1 (Note 1)   |

| 1     | 0      | Level 1 (Note 1)   |

| 1     | 1      | Level 2 (Note 2)   |

#### Notes:

- 1. Filtering Level 1 corresponds to 4x attenuation of a temperature spike.

- 2. Filtering Level 2 corresponds to 8x attenuation of a temperature spike.

Figure 7-3. Temperature Filter Step Response

Figure 7-4. Temperature Filter Impulse Response

The filter consists of a running average on the external diode channel. The Level 1 filter is a running average of 4x while the Level 2 filter is a running average of 8x. For the first measurement immediately after power-up, the filter will be filled with the results of the first measurement. After this, the filter is operated normally. Any temperature comparisons are done with the filtered results that are stored in the user register.

**Datasheet**

### 7.12 Beta Compensation

The EMC1822/23/24/25/43 devices are configured to monitor the temperature of basic diodes (for example 2N3904) or CPU thermal diodes. They automatically detect the type of external diode (CPU diode or diode connected transistor) and determine the optimal setting to reduce temperature errors introduced by beta variation. Compensating for this error is also known as implementing the transistor or BJT model for temperature measurement.

For discrete transistors configured with the collector and base shorted together, the beta is generally sufficiently high, such that the percent change in beta variation is very small. For example, a 10% variation in beta for two forced emitter currents with a transistor whose ideal beta is 50 would contribute approximately 0.25°C error at +100°C. However, for substrate transistors where the base-emitter junction is used for temperature measurement and the collector is tied to the substrate, the proportional beta variation will cause large errors. For example, a 10% variation in beta for two forced emitter currents with a transistor whose ideal beta is 0.5, would contribute approximately +8.25°C error at +100°C.

For the EMC1824 and EMC1825 devices, the External Diode Channels 2/3 (EMC1824) and External Diode Channels 3/4 (EMC1825) do not support beta compensation.

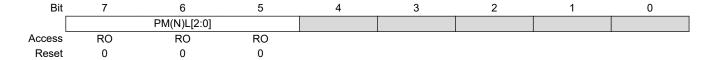

At the beginning of every conversion, the optimal beta compensation factor setting is determined and applied. The BETA(N)[2:0] bits are automatically updated to indicate the current setting. This is the default for EMC1823. This is the default for EMC1824 for External Diode 1 only and it is disabled and cannot be enabled for External Diode 2 or 3. If the auto-detection circuitry is disabled, these bits will determine the beta configuration setting that is used for their respective channels.

It is recommended to be cautious when setting the BETA(N)[2:0] bits when the auto-detection circuitry is disabled. If the beta compensation factor is set at a beta value that is higher than the transistor beta, the circuit may generate measurement errors. When measuring a discrete thermal diode (such as 2N3904) or a CPU diode that functions like a discrete thermal diode (such as a CPU/GPU processor diode), the BETA(N)[2:0] bits should be set to '111b'.

Table 7-7. CPU Beta Values

|   | DI_BET | `A<3:0> |   | Minimum Data |

|---|--------|---------|---|--------------|

| 3 | 2      | 1       | 0 | Minimum Beta |

| 0 | 0      | 0       | 0 | 0.050        |

| 0 | 0      | 0       | 1 | 0.066        |

| 0 | 0      | 1       | 0 | 0.087        |

| 0 | 0      | 1       | 1 | 0.114        |

| 0 | 1      | 0       | 0 | 0.150        |

| 0 | 1      | 0       | 1 | 0.197        |

| 0 | 1      | 1       | 0 | 0.260        |

| 0 | 1      | 1       | 1 | 0.342        |

| 1 | 0      | 0       | 0 | 0.449        |

| 1 | 0      | 0       | 1 | 0.591        |

| 1 | 0      | 1       | 0 | 0.778        |

| 1 | 0      | 1       | 1 | 1.024        |

| 1 | 1      | 0       | 0 | 1.348        |

| 1 | 1      | 0       | 1 | 1.773        |

| 1 | 1      | 1       | 0 | 2.333        |

| 1 | 1      | 1       | 1 | Diode Mode   |

### 7.13 Resistance Error Correction (REC)

Parasitic resistance, in series with the external diodes, limits the accuracy obtainable from temperature measurement devices. The voltage developed across this resistance by the switching diode currents causes the temperature measurement to read higher than the true temperature. Contributors to series resistance are PCB trace resistance, on die (i.e., on the processor) metal resistance, bulk resistance in the base and emitter of the temperature transistor. Typically, the error caused by series resistance is  $+0.7^{\circ}$ C/ $\Omega$ . The EMC1822/23/24/25/43 devices automatically correct up to  $100\Omega$  of series resistance.

### 7.14 Programmable External Diode Ideality Factor

The EMC1822/23/24/25/43 device family is designed for external diodes with an ideality factor of 1.008. Not all external diodes, processor or discrete, will have this exact value. This variation of the ideality factor introduces errors in the temperature measurement which must be corrected for. This correction is typically done using programmable offset registers. Since an ideality factor mismatch introduces an error that is a function of temperature, this correction is only accurate within a small range of temperatures. To provide maximum flexibility to the user, the EMC1822/23/24/25/43 devices provide a 6-bit register for each external diode where the ideality factor of the diode used is programmed to eliminate errors across all temperatures.

When monitoring a substrate transistor or CPU diode and beta compensation is enabled, the ideality factor should not be adjusted. Beta compensation automatically corrects for most ideality errors.

When measuring a 65 nm Intel<sup>®</sup> CPU, the ideality setting should be the default 12h. When measuring a 45 nm Intel CPU, the ideality setting should be 15h.

These registers store the ideality factors that are applied to the external diodes. The following table defines each setting and the corresponding ideality factor. Since beta compensation and Resistance Error Correction automatically correct for most diode ideality errors, it is not recommended that these settings be updated without consulting Microchip Technology.

Table 7-8. Ideality Factor Look-up Table (Diode Model)

| Setting | Factor | Setting | Factor | Setting | Factor |

|---------|--------|---------|--------|---------|--------|

| 08h     | 0.9949 | 18h     | 1.0159 | 28h     | 1.0371 |

| 09h     | 0.9962 | 19h     | 1.0172 | 29h     | 1.0384 |

| 0Ah     | 0.9975 | 1Ah     | 1.0185 | 2Ah     | 1.0397 |

| 0Bh     | 0.9988 | 1Bh     | 1.0200 | 2Bh     | 1.0410 |

| 0Ch     | 1.0001 | 1Ch     | 1.0212 | 2Ch     | 1.0423 |

| 0Dh     | 1.0014 | 1Dh     | 1.0226 | 2Dh     | 1.0436 |

| 0Eh     | 1.0027 | 1Eh     | 1.0239 | 2Eh     | 1.0449 |

| 0Fh     | 1.0040 | 1Fh     | 1.0253 | 2Fh     | 1.0462 |

| 10h     | 1.0053 | 20h     | 1.0267 | 30h     | 1.0475 |

| 11h     | 1.0066 | 21h     | 1.0280 | 31h     | 1.0488 |

| 12h     | 1.0080 | 22h     | 1.0293 | 32h     | 1.0501 |

| 13h     | 1.0093 | 23h     | 1.0306 | 33h     | 1.0514 |

| 14h     | 1.0106 | 24h     | 1.0319 | 34h     | 1.0527 |

| 15h     | 1.0119 | 25h     | 1.0332 | 35h     | 1.0540 |

| 16h     | 1.0133 | 26h     | 1.0345 | 36h     | 1.0553 |

| 17h     | 1.0146 | 27h     | 1.0358 | 37h     | 1.0566 |

System Block Diagram

For CPU substrate transistors that require the BJT transistor model, the ideality factor behaves slightly differently than for discrete diode connected transistors. Refer to the following when using a CPU substrate transistor.

Table 7-9. Substrate Diode Ideality Factor Look-up Table (BJT Model)

| Setting | Factor | Setting | Factor | Setting | Factor |

|---------|--------|---------|--------|---------|--------|

| 08h     | 0.9869 | 18h     | 1.0079 | 28h     | 1.0291 |

| 09h     | 0.9882 | 19h     | 1.0092 | 29h     | 1.0304 |

| 0Ah     | 0.9895 | 1Ah     | 1.0105 | 2Ah     | 1.0317 |

| 0Bh     | 0.9908 | 1Bh     | 1.0120 | 2Bh     | 1.0330 |

| 0Ch     | 0.9921 | 1Ch     | 1.0132 | 2Ch     | 1.0343 |

| 0Dh     | 0.9934 | 1Dh     | 1.0146 | 2Dh     | 1.0356 |

| 0Eh     | 0.9947 | 1Eh     | 1.0159 | 2Eh     | 1.0369 |

| 0Fh     | 0.9960 | 1Fh     | 1.0173 | 2Fh     | 1.0382 |

| 10h     | 0.9973 | 20h     | 1.0187 | 30h     | 1.0395 |

| 11h     | 0.9986 | 21h     | 1.0200 | 31h     | 1.0408 |

| 12h     | 1.0000 | 22h     | 1.0213 | 32h     | 1.0421 |

| 13h     | 1.0013 | 23h     | 1.0226 | 33h     | 1.0434 |

| 14h     | 1.0026 | 24h     | 1.0239 | 34h     | 1.0447 |

| 15h     | 1.0039 | 25h     | 1.0252 | 35h     | 1.0460 |

| 16h     | 1.0053 | 26h     | 1.0265 | 36h     | 1.0473 |

| 17h     | 1.0066 | 27h     | 1.0278 | 37h     | 1.0486 |

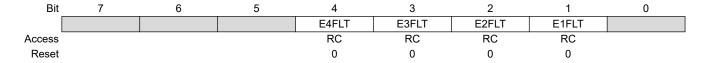

#### 7.15 Diode Faults

The EMC1822/23/24/25/43 devices detect an open on the DP and DN pins, and a short across the DP and DN pins. For each temperature measurement made, the device checks for a Diode Fault on the external diode channel(s). When a Diode Fault is detected, the  $\overline{ALERT}$  pin asserts (unless masked) and the temperature data reads 00h in the MSB and LSB registers (note that the low limit is not be checked). A Diode Fault is defined as one of the following: an open between DP and DN, a short from  $V_{DD}$  to DP or a short from  $V_{DD}$  to DN.

If a short occurs across DP and DN or a short occurs from DP to GND, the Low Limit Status bit is not set and the ALERT pin does not assert. This condition is indistinguishable from a temperature measurement of 0.000°C (-64°C in extended range) resulting in temperature data of 00h in the MSB and LSB registers.

If a short from DN to GND occurs (with a diode connected), temperature measurements will continue as normal with no alerts.

#### 7.16 Consecutive Alerts

The EMC1822/23/24/25/43 device family contains multiple consecutive alert counters. One set of counters applies to the  $\overline{\text{ALERT}}$  pin and the second set of counters applies to the  $\overline{\text{THERM}}$  pin. Each temperature measurement channel has a separate consecutive alert counter for each of the  $\overline{\text{ALERT}}$  and  $\overline{\text{THERM}}$  pins. All counters are user programmable and determine the number of consecutive measurements that a temperature channel(s) must be out-of-limit or reporting a Diode Fault before the corresponding pin is asserted.

The Consecutive Alert register determines how many times an out-of-limit error or Diode Fault must be detected in consecutive measurements before the ALERT or THERM pin is asserted.

© 2018-2020 Microchip Technology Inc. Datasheet DS20006048B-page 26

System Block Diagram

An out-of-limit condition (for example, HIGH, LOW or FAULT) occurring on the same temperature channel in consecutive measurements will increment the consecutive alert counter. The counters will also be reset if no out-of-limit condition or Diode Fault condition occurs in a consecutive reading.

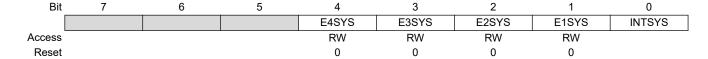

When the ALERT pin is configured as an interrupt and when the consecutive alert counter reaches its programmed value, the following occurs: the status bit(s) for that channel and the last error condition(s) (for example, E1HIGH, or E2LOW and/or E2FAULT) are set to '1', the ALERT pin is asserted, the consecutive alert counter is cleared and measurements continue to be performed.

When the ALERT pin is configured as a comparator, the consecutive alert counter will ignore Diode Fault and low limit errors, and only increment if the measured temperature exceeds the high limit. Additionally, once the consecutive alert counter reaches the programmed limit, the ALERT pin is asserted, but the counter does not reset. It remains set until the temperature drops below the high limit minus the Therm Hysteresis value.

Channels that are not enabled are not included in the consecutive alert checking. The signal logic chain is: Limit  $\rightarrow$  Counter  $\rightarrow$  Status  $\rightarrow$  Mask  $\rightarrow$  Pin (THERM and ALERT).

For example, if the CALRT[2:0] bits are set for four consecutive alerts on an EMC1822/23/24/25/43 device, the high limits are set at +70°C and none of the channels are masked, then the ALERT pin is asserted after the following five measurements:

- Internal Diode reads +71°C and both the external diodes read +69°C. Consecutive alert counter for INT is incremented to 1

- Both the Internal Diode and the External Diode 1 read +71°C and External Diode 2 reads +68°C. Consecutive alert counter for INT is incremented to 2 and EXT1 is set to 1.

- The External Diode 1 reads +71°C and both Internal Diode and External Diode 2 read +69°C. Consecutive alert counters for INT and EXT2 are cleared and EXT1 is incremented to 2.

- The Internal Diode reads +71°C and both external diodes read +71°C. Consecutive alert counter for INT is set to 1, EXT2 is set to 1 and EXT1 is incremented to 3.

- The Internal Diode reads +71°C and both external diodes read +71°C. Consecutive alert counter for INT is

incremented to 2, EXT2 is set to 2 and EXT1 is incremented to 4. The appropriate status bits are set for EXT

and the ALERT pin is asserted. EXT1 counter is reset to 0 and all other counters hold the last value until the

next temperature measurement.

All temperature channels use this value to set the respective counters. The consecutive Therm counter is incremented whenever any measurement exceeds the corresponding Therm limit.

If the temperature drops below the Therm limit, the counter is reset. If a number of consecutive measurements above the Therm limit occurs, the THERM pin is asserted low.

Once the THERM pin has been asserted, the consecutive Therm counter will not reset until the corresponding temperature drops below the Therm limit minus the Therm Hysteresis value.

The bits are decoded as shown in the table below. The default setting is four consecutive out-of-limit conversions.

All temperature channels use this value to set the respective counters. The bits are decoded as shown in the table below. The default setting is 1 consecutive out-of-limit conversion.

When the ALERT pin is in Comparator mode, the low limit and Diode Fault will bypass the consecutive alert counter and set the appropriate status bits, but will NOT assert the ALERT pin.

When a value is written to 8.11.23 CONSEC ALERT (Address 22h) that is not defined below, the command is ignored and the last valid value is maintained.

Table 7-10. Consecutive ALERT/ THERM Settings

| 2 | 1 | 0 | Number of Consecutive Out-of-Limit Measurements |

|---|---|---|-------------------------------------------------|

| 0 | 0 | 0 | 1<br>(default for CALRT[2:0])                   |

| 0 | 0 | 1 | 2                                               |

| 0 | 1 | 1 | 3                                               |

| 1 | 1 | 1 | 4<br>(default for CTHRM[2:0])                   |

### 7.17 "Hottest Of" Comparison

At the end of every measurement cycle, the EMC1822/23/24/25/43 devices compare all of the user-selectable internal and external diode channels to determine which of these channels is reporting the hottest temperature. The hottest temperature is stored in the Hottest Temperature registers and the appropriate status bit is set in the Hottest Status register. If multiple temperature channels measure the same temperature and are equal to the hottest temperature, the hottest status will be displayed for all selected temperature channels with the hottest temperature measurement.

As an optional feature, the EMC1822/23/24/25/43 devices can also flag an event if the hottest temperature channel changes by enabling the REMHOT (Remember Hottest) bit (see 8.11.45 HOTTEST CONFIG). For example, suppose that External Diode Channels 1, 3 and 4 are programmed to be compared in the "Hottest Of" comparison. If the External Diode 1 channel reports the hottest temperature of the three, its temperature is copied into the Hottest Temperature registers (in addition to the External Diode 1 Temperature registers) and it is flagged in the Hottest Status bit. If, on the next measurement, the External Diode 3 channel temperature has increased, such that it is now the hottest temperature, the EMC1822/23/24/25/43 devices can flag this event as an interrupt condition and assert the ALERT pin.

### 7.18 Rate of Change

The Rate of Change (ROC) function approximates the derivative of the temperature using a difference equation. The equation below is the basis for calculation.

The ROC can be enabled for the first two standard diode connections. If Diode 2 is an anti-parallel connected diode, the ROC feature is applied to Diode 3. For the EMC1843, the ROC only applies to External Diode 1.

#### **Equation: Rate of Change**

$$^{\triangle}_{\Delta} \frac{T}{t} = \frac{\left[T(t \max) - T(t_0)\right] \times gain}{(sample - 1)}$$

#### Where:

| T(t <sub>max</sub> ) | = | Temperature at the end of the interval       |

|----------------------|---|----------------------------------------------|

| $T(t_0)$             | = | Temperature at the beginning of the interval |

The ROC period ( $T_0$  to  $T_{max}$ ) can be approximated by the combination of conversion rate (see Table 7-4) and ROC samples (Address 43h, 48h). The table below shows the samples defined by the bit settings.

For example, setting the conversion rate to 1 conversion per second and the number of ROC samples to 65 samples would give an approximate ROC period of 65 seconds or approximately 1 minute.

The gain applied to the result is stored in 8.11.29 ROC GAIN (Address 3Dh). The effective gains are shown in the register definition.

Since this is sampled over time, there is a bit for each channel that indicates a change in slope has occurred. These bits (one for each channel) assert when the result of two consecutive sample differences exceeds the threshold limit

System Block Diagram

as defined by the hysteresis value defined in 8.11.30 ROC CONFIG (Address 3Eh). The ROC calculations are not affected.

The Limit registers (8.11.34 R LIMH and 8.11.35 R LIML) and Results registers (8.11.32 R RESH and 8.11.33 R2/3 RESL) are signed, two's complement numbers stored in two consecutive registers.

If the Rate of Change result stored in registers 40h and 44h exceeds the programmed limit, the appropriate Status register bits will be set in 8.11.31 ROC STATUS (Address 3Fh). The ALERT pin may be asserted or masked, as set by 8.11.30 ROC CONFIG (Address 3Eh). The MASK bit does not prevent the status bits from updating, but if set, it prevents the ALERT pin from asserting.

In addition to the functions described above, two additional temperature values are stored in registers for retrieval. The maximum temperature for a given sample period is stored in a register (4Ah) that updates every sample period and in a second register (4Dh, 4Fh) that stores a "global value", and cleared only when read. The purpose of this register is to determine a maximum or minimum temperature, independent of the sample period.

Below is an example of setting up the Rate of Change feature and interpreting the results.

- 1. Enable Standby mode: Write a value of 40h into register 03h.

- 2. Set ROC gain: Write a value of 09h in register 3Dh. This sets the gain value of two for both Ext1 and Ext2/3.

- 3. Set ROC samples Ext1, Ext2/3: Write a value of 02h/02h in registers 43h/48h. This sets the ROC samples to five for both EXT1 and Ext2/3.

- Set ROC Alert Limit Ext1/Ext2: Write a value of 01h/01h in registers 41h/46h. This sets the ROC limit to two for both Ext1 and Ext2/3.

- Enable ROC and Hysteresis: Write a value of 20h in register 3Eh. This enables the ROC and sets the hysteresis value to zero.

#### ROC example:

- 1. Stabilize ambient temperature of device to +25°C.

- 2. Initiate one-shot conversion: Write a value of FFh in register 0Fh.