# **ECE1200**

# eSPI to LPC Bridge

#### **Features**

- Detects and Supports Modern Standby State (S0ix) with Low Standby Current

- · ACPI 6.1 Compliant

- · Configuration Register Set

- Compatible with ISA Plug-and-Play Standard

- Host-Programmable Base Address

- Supports LPC-based SIO and EC devices such as:

- SCH555x, SCH5347B

- SCH311x, SCH322x

- eSPI Peripheral Channel Cycles in 64K I/O Space will pass through as LPC I/O cycles, except for the local Plug-and-Play INDEX/DATA portal registers

- eSPI Peripheral Channel Cycles in Memory Space will all pass through as LPC Memory Cycles

- · Enhanced Serial Peripheral Interface (eSPI)

- 1.8V Operation

- Intel eSPI Base Specification 1.0 compliant

- Supports the Peripheral Channel and Virtual Wire Channel interfaces

- Supports up to 50 MHz maximum operating frequency

- · LPC Master Interface

- 3.3V operation

- Generates LPC Clock on two output pins

- Provides 24 MHz nominal bus clock frequency

- Provides CLKRUN# clock control interface

- LPC Specification 1.1 Compatible

- LPC I/O and Memory Cycles Supported

- Supports Serial IRQ Interface, both Continuous and Quiet modes

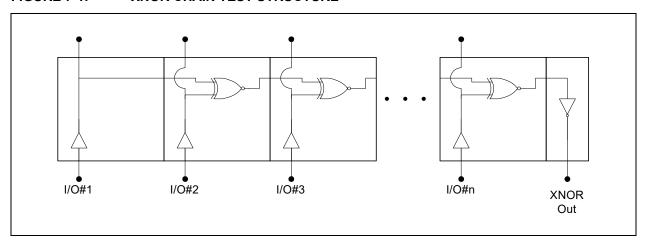

- · XNOR Board Test Mode

- Package Options

- 40-pin VQFN RoHS Compliant Package (LDX)

- · Industrial Temperature Range

- -40°C to +85°C

#### **Products**

| Catalog Part Number | Package             | Temperature<br>Range | Initial Register Portal<br>Address | Delivery<br>Packaging |

|---------------------|---------------------|----------------------|------------------------------------|-----------------------|

| ECE1200-I/LD        | 40-VQFN, sawn (LDX) | Industrial           | 8Ch                                | Tray                  |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

## **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## **Table of Contents**

| 1.0 General Description                         | 4  |

|-------------------------------------------------|----|

| 2.0 Pin Configuration                           | 10 |

| 3.0 Power, Clocks, and Resets                   | 16 |

| 4.0 LPC Interface                               | 20 |

| 5.0 Enhanced Serial Peripheral Interface (eSPI) | 25 |

| 6.0 Device Register Set and Initialization      | 33 |

| 7.0 Test Mechanisms                             | 58 |

| 8.0 Electrical Specifications                   | 60 |

| 9.0 Timing Diagrams                             |    |

| Appendix A: Data Sheet Revision History         |    |

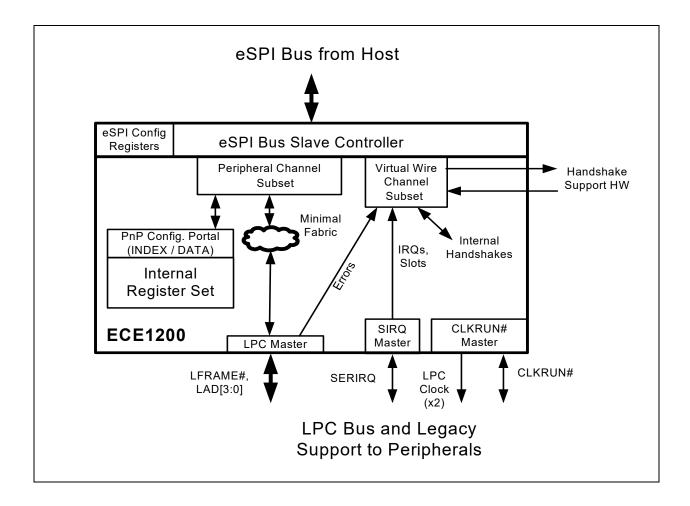

## 1.0 GENERAL DESCRIPTION

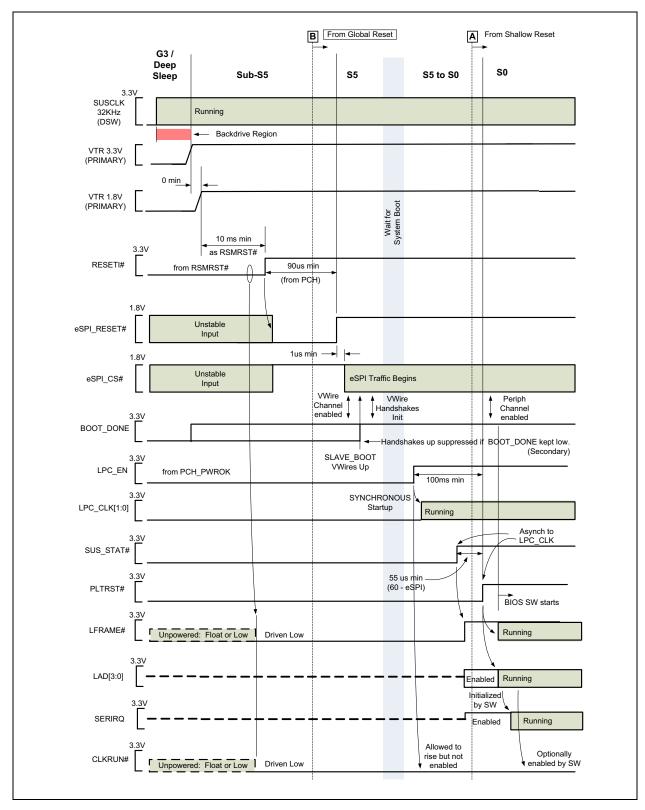

The ECE1200 is a device designed to implement a Bridge function from an eSPI-configured Intel Chipset to a legacy downstream system, providing Master interfaces for an LPC bus, Serial IRQ and CLKRUN# features.

The ECE1200 is directly powered by two Suspend (S5) supply planes, at 3.3V and 1.8V nominal. The 1.8V supply is provided on two sets of pins: VTR\_18 for I/O pins, and VTR\_18\_CORE for internal logic. The 3.3V supply VTR\_33 is for 3.3V I/O pins only.

The ECE1200 senses a Runtime power plane (VCC) using the pin LPC\_EN, which is intended to come from the PCH\_PWROK signal supplied from the system. It uses this to emulate VCC-powered functionality on the appropriate pins in order to avoid backdrive in the system.

TABLE 1-1: GENERAL TERMINOLOGY

| Term                         | Definition                                                                                                                                                                                                              |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Host, or Host Chipset | Refers to the complex of the System CPU and surrounding elements, from which originates the I/O and Memory traffic to the ECE1200 over the eSPI Interface.                                                              |

| PCH                          | The specific element of the Host Chipset that connects to the ECE1200 from the Host side, serving as the Master in the eSPI protocol, and controlling the pins that serve as Host-side sideband signals to the ECE1200. |

## 1.1 System Block Diagrams

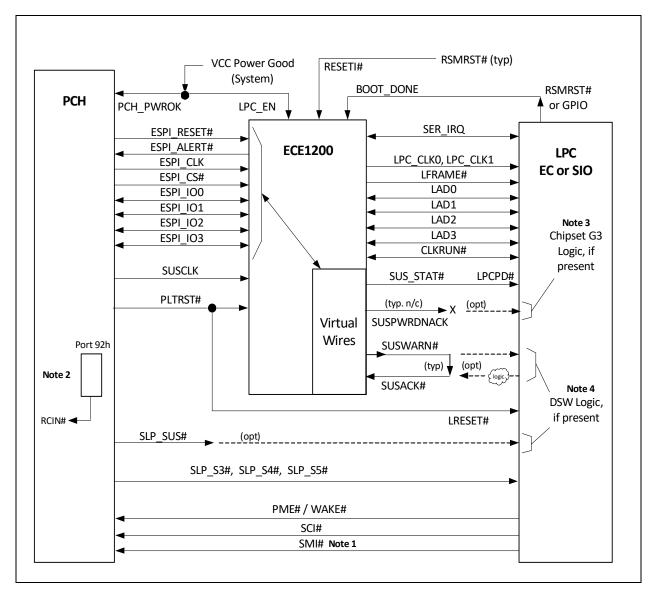

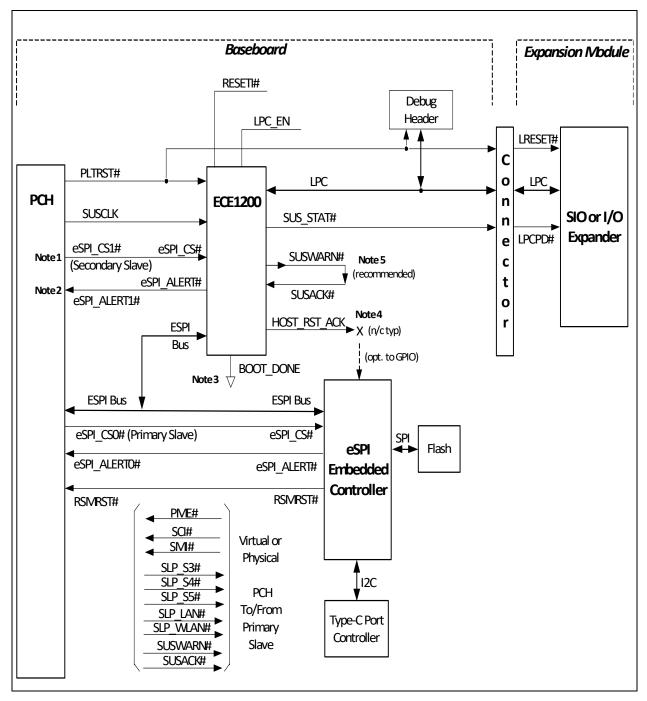

#### 1.1.1 GENERAL SYSTEM BLOCK DIAGRAM

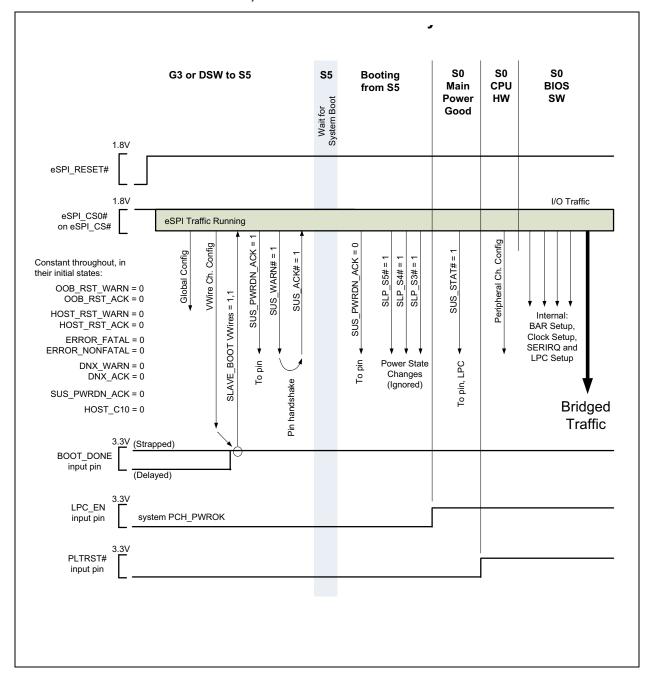

The ECE1200 is shown here as a single eSPI Slave, or the Primary Slave of two or more (on eSPI CS0#).

Note 1: SMI# can instead be presented on SER\_IRQ pin (time slot 2) and propagated to the PCH as a Virtual Wire.

- 2: RCIN# is not supported as a PCH pin in eSPI configuration, and should be exercised internal to the PCH.

- **3:** SUSPWRDNACK is an output extracted from a Virtual Wire, because some eSPI Chipsets do not provide it as a physical signal. If the LPC device can use this signal for support of the "Chipset G3" Deep Power-Down mechanism, then make the connection as shown. Otherwise, the pin may be left open.

- **4:** SUSWARN# and SUSACK# pins provide a **mandatory** handshake, propagated using Virtual Wires that may not be present as physical signals in all eSPI Chipsets. If the LPC device, or board HW, supports this handshake for the "DSW" Deep Sleep mechanism, then it may be connected to these pins for this purpose. Otherwise, the SUSWARN# and SUSACK# pins **must be connected** directly to each other at the ECE1200 as shown. Without some form of handshake connection between them, the system **will not boot**.

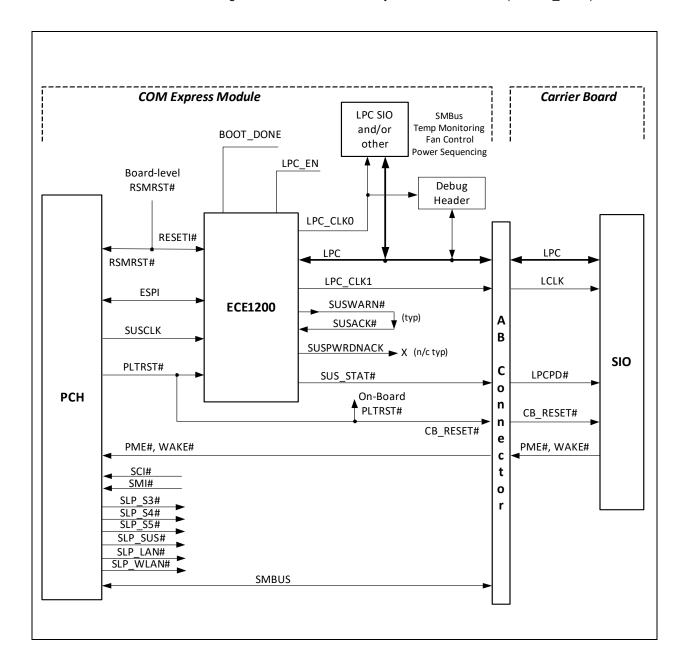

## 1.1.2 SYSTEM BLOCK DIAGRAM, COM EXPRESS

The ECE1200 is shown here as a single eSPI Slave, or the Primary Slave of two or more (on eSPI\_CS0#).

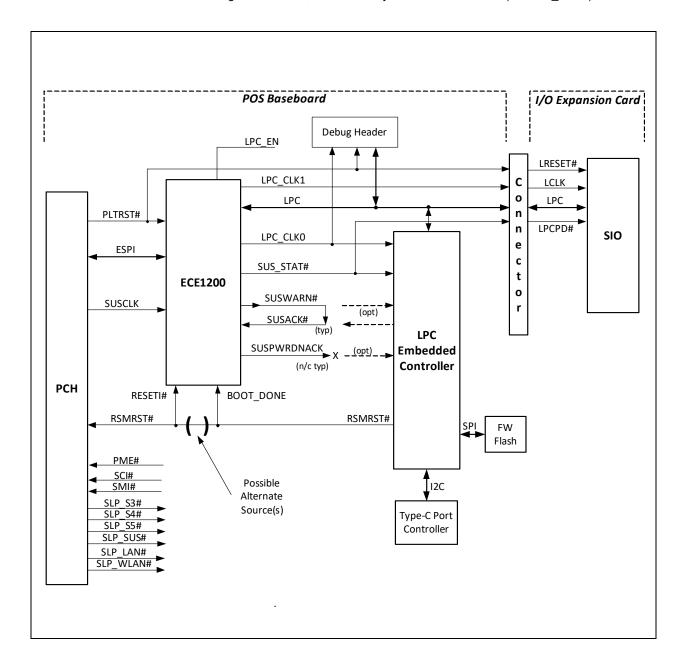

## 1.1.3 SYSTEM BLOCK DIAGRAM, POS

The ECE1200 is shown here as a single eSPI Slave, or the Primary Slave of two or more (on eSPI\_CS0#).

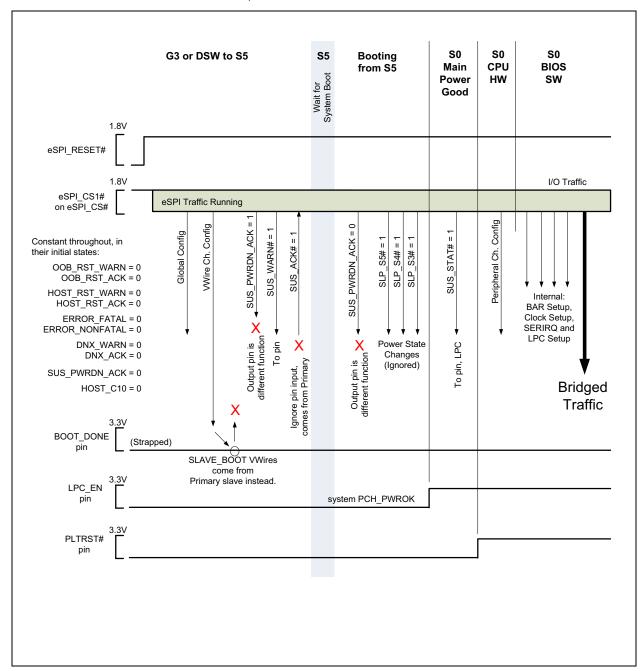

## 1.1.4 SYSTEM BLOCK DIAGRAM, ECE1200 AS SECONDARY ESPI SLAVE

**Note 1:** This configuration has two eSPI Slaves. The ECE1200 is the Secondary Slave device, with some limitations imposed by the Host PCH. It can receive any of the fixed Legacy decodes, but may have only one Generic I/O decode range and one Generic Memory decode range available to it from the PCH.

- 2: Each eSPI Slave has an individual eSPI\_CS# input, and will be configured by the PCH hardware (as directed by its Soft-Straps) to present its ALERT# events on its individual eSPI\_ALERT# output pin.

- **3:** The Primary eSPI Slave device will have the EC functionality, and will provide the mandatory eSPI hand-shaking. The pin BOOT\_DONE, strapped permanently low, inhibits these actions by the ECE1200.

- 4: In this configuration, the ECE1200 presents the output HOST\_RST\_ACK to indicate that its LPC bus has become idle after the last transfer from the Host CPU, before an LRESET# event. This may optionally be used by the Primary eSPI Slave device to delay its Virtual Wire handshake HOST\_RST\_WARN/HOST\_RST\_ACK with the Host Chipset.

This signal is not a requirement, but may assist in this eSPI-specific handshake feature if desired. Although the ECE1200 receives the HOST\_RST\_WARN Virtual Wire, it does not have direct authority to send the HOST\_RST\_ACK handshake response itself, and is required to go through the Primary Slave instead. Without this connection, there is no concern in legacy LPC systems. Historically, the LPC bus does not need to be idle before it gets reset. Neither the ECE1200 nor its downstream devices will be disrupted without it.

- 5: The SUSWARN# and SUSACK# signals are shown connected together. This is not strictly required in this configuration, but is harmless and inexpensive, and is recommended for uniformity since all other configurations do require some connection. If this cannot be done, then tie the SUSACK# pin to a valid digital state, low or high. SUSWARN# is an output, and may be left unconnected.

## 2.0 PIN CONFIGURATION

## 2.1 Description

The Pin Configuration chapter defines the Pin List and the Package.

## 2.2 Pin List

Pins are listed in Section 2.2.1 below.

**Note:** The column **Emulated Power Well** indicates when signals are enabled:

**VCC** means that the LPC\_EN pin must be high, meaning that Main (S0) power rails in the system are valid, before these pins are allowed to drive high.

VTR means that they may drive (high or low) as soon as all VTR power is present and RESETI# is high.

This behavior is ensured only if the TEST pin remains low.

# 2.2.1 PIN ASSIGNMENTS, 40-PIN VQFN

| 40-pin<br>VQFN | Pin Name                   | Direction<br>(Other than<br>Test Modes) | Pin<br>Type | Signal<br>Power Well | Emulated<br>Power<br>Well | Back-<br>drive<br>Protect |

|----------------|----------------------------|-----------------------------------------|-------------|----------------------|---------------------------|---------------------------|

|                | VSS (Pad on Underside)     |                                         | GND         | 0V                   |                           |                           |

| 1              | ESPI_ALERT#                | 0                                       | eSPI        | VTR_18               | VTR                       |                           |

| 2              | VTR_18                     |                                         | PWR         | 1.8V                 |                           |                           |

| 3              | ESPI_IO2                   | IO                                      | eSPI        | VTR_18               | VTR                       |                           |

| 4              | ESPI_IO0                   | IO                                      | eSPI        | VTR_18               | VTR                       |                           |

| 5              | ESPI_CLK                   | 1                                       | eSPI        | VTR_18               | VTR                       |                           |

| 6              | ESPI_IO1                   | Ю                                       | eSPI        | VTR_18               | VTR                       |                           |

| 7              | ESPI_IO3                   | IO                                      | eSPI        | VTR_18               | VTR                       |                           |

| 8              | VTR_18                     |                                         | PWR         | 1.8V                 |                           |                           |

| 9              | TEST                       | I                                       | DIO         | VTR_33               | VTR                       |                           |

| 10             | LPC_EN                     | I                                       | DIO         | VTR_33               | VTR                       |                           |

| 11             | VTR_33                     |                                         | PWR         | 3.3V                 |                           |                           |

| 12             | BOOT_DONE                  | I                                       | DIO         | VTR_33               | VTR                       |                           |

| 13             | PLTRST#                    | I                                       | DIO         | VTR_33               | VTR                       |                           |

| 14             | VTR_CORE_18                |                                         | PWR         | 1.8V                 | 1                         |                           |

| 15             | SUSCLK                     | I                                       | DIO         | VTR_33               | VTR                       | Υ                         |

| 16             | SUS_STAT#                  | 0                                       | PCI         | VTR_33               | VTR                       |                           |

| 17             | SUSACK#                    | I                                       | DIO         | VTR_33               | VTR                       |                           |

| 18             | RESETI#                    | I                                       | DIO         | VTR_33               | VTR                       |                           |

| 19             | SUSWARN#                   | 0                                       | DIO         | VTR_33               | VTR                       |                           |

| 20             | ESPI_STRAP_0               | Ι                                       | DIO         | VTR_33               | VTR                       |                           |

| 21             | ESPI_STRAP_1               | I                                       | DIO         | VTR_33               | VTR                       |                           |

| 22             | VTR_33                     |                                         | PWR         | 3.3V                 | -                         |                           |

| 23             | LPC_CLK0                   | 0                                       | LCLK        | VTR_33               | VCC                       |                           |

| 24             | LPC_CLK1                   | 0                                       | LCLK        | VTR_33               | VCC                       |                           |

| 25             | LAD0                       | Ю                                       | PCI         | VTR_33               | VCC                       |                           |

| 26             | LAD1                       | Ю                                       | PCI         | VTR_33               | VCC                       |                           |

| 27             | LAD2                       | Ю                                       | PCI         | VTR_33               | VCC                       |                           |

| 28             | LAD3                       | Ю                                       | PCI         | VTR_33               | VCC                       |                           |

| 29             | LFRAME#                    | 0                                       | PCI         | VTR_33               | VCC                       |                           |

| 30             | VTR_33                     |                                         | PWR         | 3.3V                 |                           |                           |

| 31             | SER_IRQ                    | Ю                                       | PCI         | VTR_33               | VCC                       |                           |

| 32             | CLKRUN#                    | Ю                                       | PCI_24      | VTR_33               | VCC                       |                           |

| 33             | No Connect                 |                                         |             |                      |                           |                           |

| 34             | No Connect                 |                                         |             |                      | -                         |                           |

| 35             | SUSPWRDNACK / HOST_RST_ACK | 0                                       | DIO         | VTR_33               | VTR                       |                           |

| 36             | ESPI_RESET#                | I                                       | eSPI        | VTR_18               | VTR                       |                           |

| 37             | No Connect                 |                                         |             |                      | -                         |                           |

| 38             | No Connect                 |                                         |             |                      |                           |                           |

| 39             | No Connect                 |                                         |             |                      |                           |                           |

| 40             | ESPI_CS#                   | I                                       | eSPI        | VTR_18               | VTR                       |                           |

## 2.3 Strapping Options

#### 2.3.1 TEST PIN

The pin named TEST must be kept permanently low in normal operation. It may be pulled high only for test purposes, and when high it redefines all pin functions. See Section 7.0, "Test Mechanisms," on page 58.

## 2.3.2 ESPI\_STRAP\_0, ESPI\_STRAP\_1 PINS

These pins should remain open (N/C) except for test purposes. They are included as inputs to the XNOR Chain test mode.

## 2.3.3 BOOT\_DONE PIN

This pin defines whether the eSPI role of the ECE1200 is as a Primary Slave or a Secondary Slave. It may be strapped in the system, or it may be dynamically changed (once) in the power-on sequence.

The state of BOOT\_DONE selects the multiplexed output function of pin SUSPWRDNACK / HOST\_RST\_ACK:

- BOOT DONE=1: SUSPWRDNACK

- BOOT\_DONE=0: HOST\_RST\_ACK

See Section 5.5.2, "BOOT\_DONE," on page 27 for details of its usage. See also the figures in Section 1.1, "System Block Diagrams," on page 5 for connection examples and notes for application.

## 2.4 Package

**Note:** For the most current package drawings, see the Microchip Packaging Specification at <a href="http://www.microchip.com/packaging">http://www.microchip.com/packaging</a>.

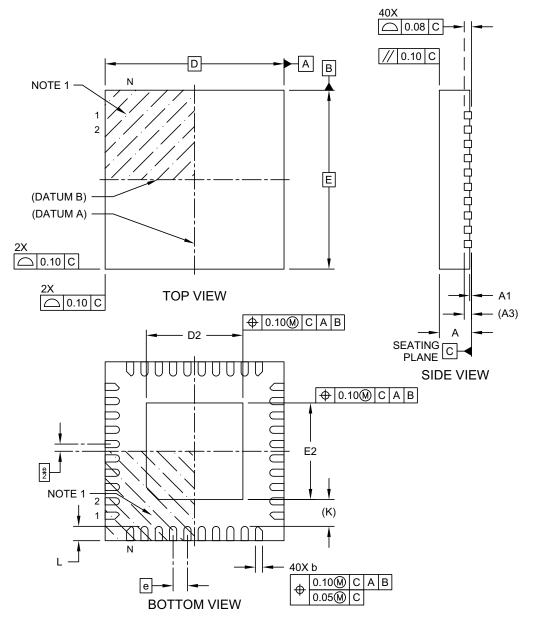

## 2.4.1 40-PIN VQFN PACKAGE OUTLINE

# 40-Lead Very Thin Plastic Quad Flat, No Lead Package (LDX) - 5x5 mm Body [VQFN] With 2.7x2.7 mm Exposed Pad

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-496 Rev A Sheet 1 of 2

© 2018 Microchip Technology Inc.

## 40-Lead Very Thin Plastic Quad Flat, No Lead Package (LDX) - 5x5 mm Body [VQFN] With 2.7x2.7 mm Exposed Pad

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                   |                                 | N              | IILLIMETER | S    |

|-------------------------|---------------------------------|----------------|------------|------|

| Dimension               | Limits                          | MIN            | NOM        | MAX  |

| Number of Terminals     | Ν                               | 40             |            |      |

| Pitch                   | е                               |                | 0.40 BSC   |      |

| Overall Height          | Α                               | 0.80           | 0.85       | 0.90 |

| Standoff                | A1                              | 0.00           | 0.02       | 0.05 |

| Terminal Thickness      | A3 0.20 REF                     |                |            |      |

| Overall Length          | D                               | 5.00BSC        |            |      |

| Exposed Pad Length      | D2                              | 2.60 2.70 2.80 |            | 2.80 |

| Overall Width           | Е                               | 5.00BSC        |            |      |

| Exposed Pad Width       | E2                              | 2.60           | 2.70       | 2.80 |

| Terminal Width          | b                               | 0.15           | 0.20       | 0.30 |

| Terminal Length         | Ĺ                               | 0.30           | 0.40       | 0.50 |

| Terminal-to-Exposed-Pad | minal-to-Exposed-Pad K 0.75 REF |                |            |      |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-496 Rev A Sheet 2 of 2

© 2018 Microchip Technology Inc.

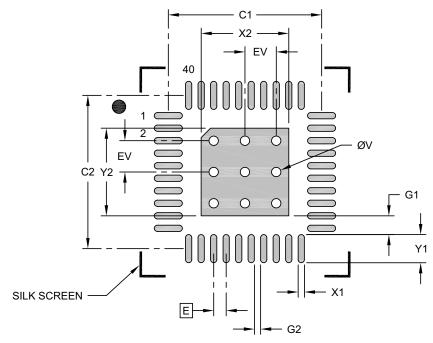

# 40-Lead Very Thin Plastic Quad Flat, No Lead Package (LDX) - 5x5 mm Body [VQFN] With 2.7x2.7 mm Exposed Pad

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                                  | N      | /ILLIMETER | S        |      |

|----------------------------------|--------|------------|----------|------|

| Dimension                        | Limits | MIN        | NOM      | MAX  |

| Contact Pitch                    | E      |            | 0.40 BSC |      |

| Optional Center Pad Width        | X2     |            |          | 2.80 |

| Optional Center Pad Length       | Y2     |            |          | 2.80 |

| Contact Pad Spacing              | C1     |            | 4.90     |      |

| Contact Pad Spacing              | C2     |            | 4.90     |      |

| Contact Pad Width (X40)          | X1     |            |          | 0.20 |

| Contact Pad Length (X40)         | Y1     |            |          | 0.90 |

| Contact Pad to Center Pad (X40)  | G1     | 0.60       |          |      |

| Contact Pad to Contact Pad (X36) | G2     | 0.20       |          |      |

| Thermal Via Diameter             | V      |            | 0.30     |      |

| Thermal Via Pitch                | EV     |            | 1.00     |      |

#### Notes:

- 1. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- 2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing C04-2496 Rev A

© 2018 Microchip Technology Inc.

## 3.0 POWER, CLOCKS, AND RESETS

## 3.1 Introduction

This Power, Clocks, and Resets (PCR) chapter identifies all the power supplies, clock sources, and reset inputs to the chip and defines all the derived power, clock, and reset signals. In addition, this section identifies Power, Clock, and Reset events that may be used to generate an interrupt event, as well as, the Chip Power Management Features.

## 3.2 References

No references have been cited for this chapter.

## 3.3 Interrupts

The Power, Clocks, and Resets logic generates no interrupt events to the Host system.

#### 3.4 Power

#### 3.4.1 POWER SOURCES

Table 3-1 lists the pins from which the ECE1200 draws current. These current values are defined in Section 8.3, "Power Consumption," on page 63.

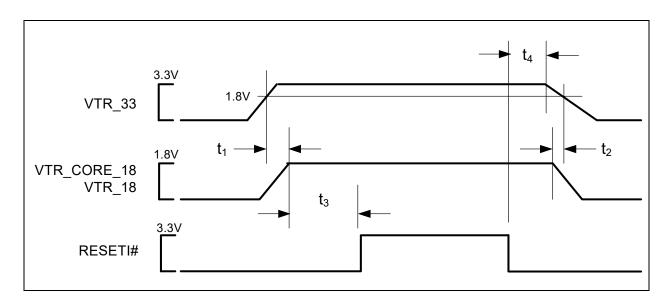

Timing sequences between these power rails are given in Section 9.5.1, "VTR Sequencing and RESETI# Timing," on page 70.

TABLE 3-1: POWER SOURCE DEFINITIONS

| Power Well | Nominal<br>Voltage | Description                                                                                                                                                                                                                            | Source        |

|------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| VTR_33     | 3.3V               | 3.3V I/O Power Supply This supply is used to power the 3.3V I/O pins.                                                                                                                                                                  | Pin Interface |

|            |                    | It is to be connected to the "Always-on" / "Suspend" / "S5" supply rails in system. There is no need to connect it to a deeper power well, such as the Deep Sleep Well, even if that is what powers the downstream LPC device(s).      |               |

|            |                    | This supply must be on prior to the RESETI# signal being deasserted (system RSMRST#).                                                                                                                                                  |               |

| VTR_18     | 1.8V               | 1.8V I/O Power Supply This supply is used to power the 1.8V I/O pins.                                                                                                                                                                  | Pin Interface |

|            |                    | It is to be connected to the 1.8V "Always-on" / "Suspend" / "S5" supply rails in system. There is no need to connect it to a deeper power well, such as the Deep Sleep Well, even if that is what powers the downstream LPC device(s). |               |

|            |                    | This supply must be on prior to the RESETI# signal being deasserted (system RSMRST#).                                                                                                                                                  |               |

TABLE 3-1: POWER SOURCE DEFINITIONS (CONTINUED)

| Power Well  | Nominal<br>Voltage | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Source        |

|-------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| VTR_CORE_18 | 1.8V               | 1.8V Core Logic Power Supply This supply is used to power the internal logic.  It is to be connected to the 1.8V "Always-on" / "Suspend" / "S5" supply rails in system. It is on its own pin in order to allow isolation and decoupling from the VTR_18 pin, otherwise it is identical. There is no need to connect it to a deeper power well, such as the Deep Sleep Well, even if that is what powers the downstream LPC device(s).  This supply must be on prior to the RESETI# sig- nal being deasserted (system RSMRST#). | Pin Interface |

Note: The

The VTR\_33 supply must always be at or above the voltage on the 1.8V supply pins, including during power-on and power-off sequences, otherwise excessive current may occur. VTR\_18 and VTR\_CORE\_18 must turn on at the same time as, or after, the VTR\_33 supply is powered. VTR\_18 and VTR\_CORE\_18 must come from the same system well, rising and falling together.

#### 3.4.2 POWER GOOD SIGNALS

The Power Good timing is defined in the Section 9.5, "Voltage Sequencing and Power Good Timing," on page 70.

TABLE 3-2: POWER GOOD SIGNAL DEFINITIONS

| Power Good<br>Signal | Description                                                                              | Source                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESETI#              | This is the Power-On Reset (POR) input for all the VTR input wells.                      | RESETI# is to be held low initially, and set high following a delay after all of the VTR power pins have reached their valid levels. RESETI# is to be pulled low as soon as either of these voltages drop below this threshold. At no time may this signal glitch during power transitions.  It is strongly recommended that this pin be connected to the system RSMRST# signal, which will assure these needs. |

| LPC_EN               | This input is used to indicate when the Main (S0) power rail voltages are on and stable. | LPC_EN indicates to the ECE1200 when the downstream resources (LPC, Serial IRQ and CLKRUN#) are powered. The low state prevents these pins from driving high, avoiding backdrive of the other components. At no time may this signal glitch during power transitions.  It is strongly recommended that this pin be connected to the system PCH_PWROK signal, which will assure these needs.                     |

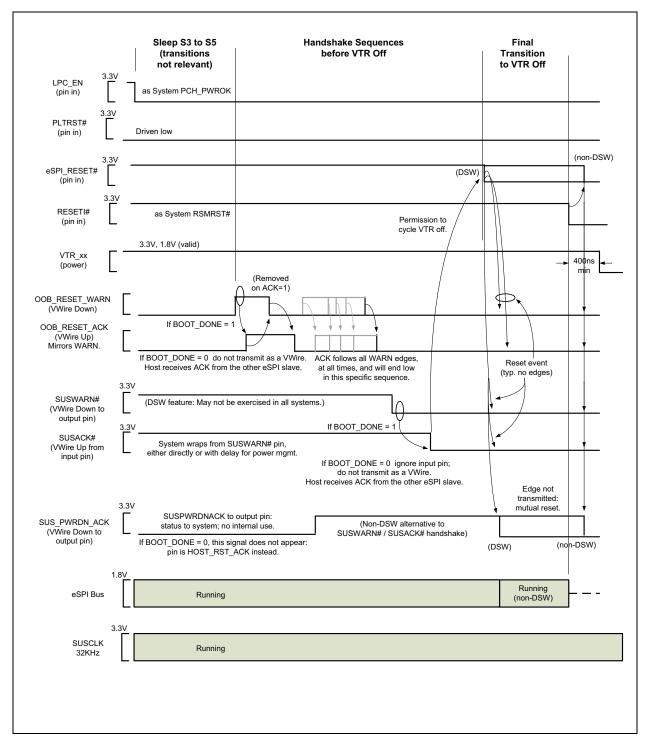

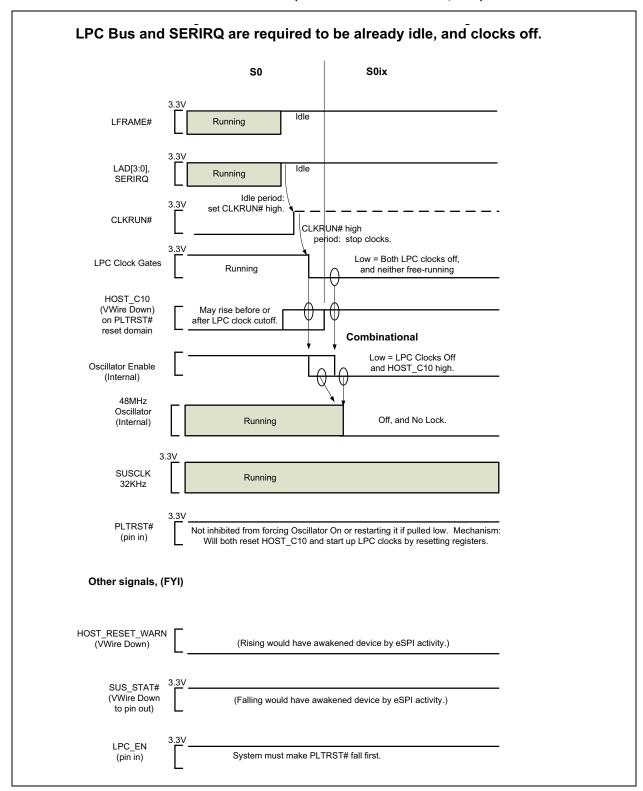

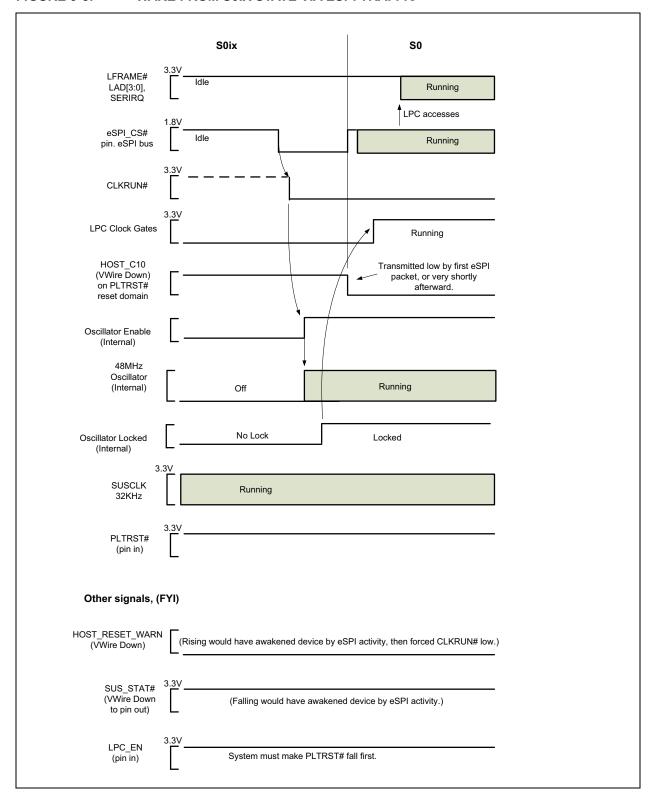

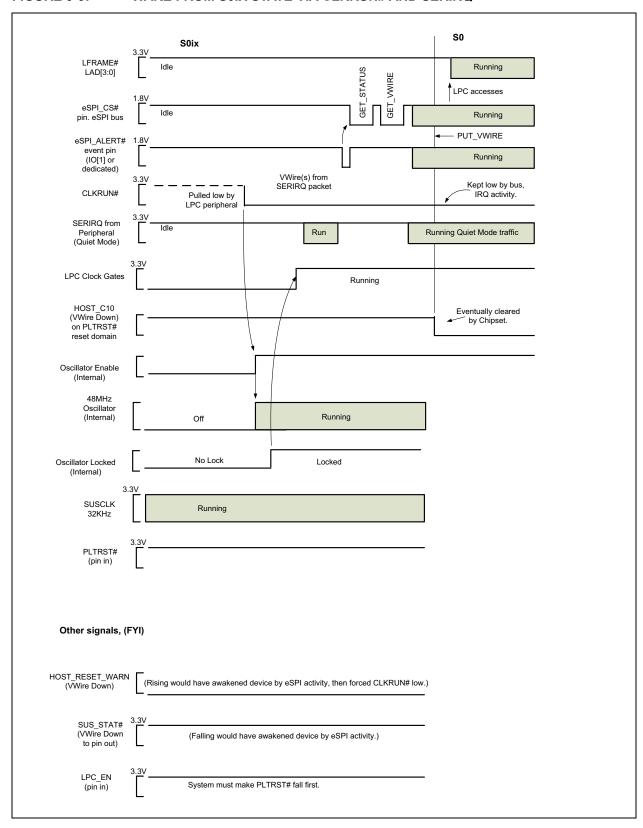

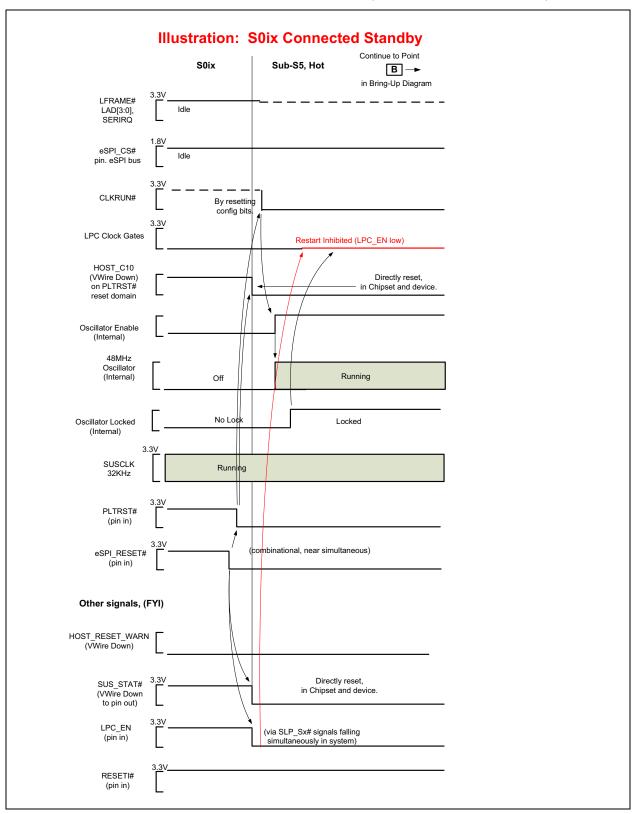

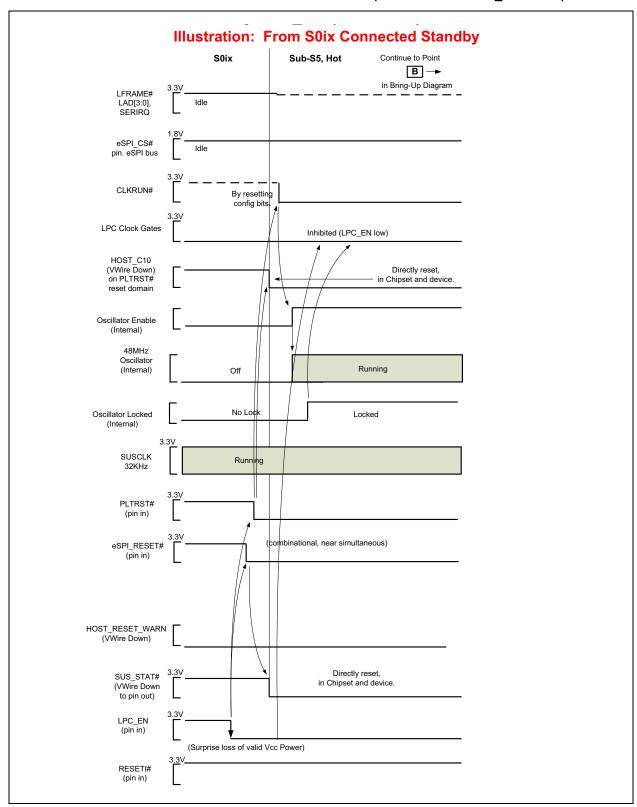

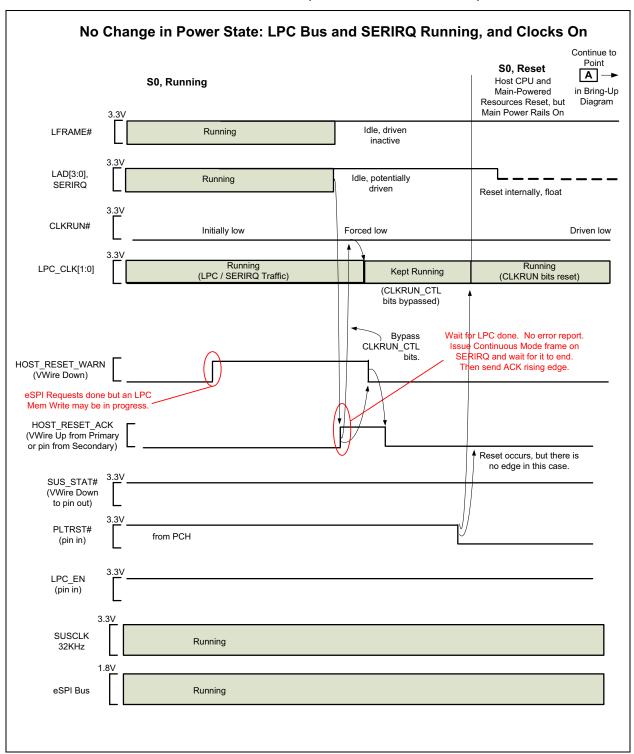

#### 3.4.3 SYSTEM POWER SEQUENCING

See Section 9.7, "System Power State Transition Diagrams," on page 70 for behavior under system power state changes.

## 3.5 Clocks

The following section defines the clocks that are generated and derived.

#### 3.5.1 CLOCK SOURCES

The table defines raw clocks that are either generated externally or via an internal oscillator.

TABLE 3-3: SOURCE CLOCK DEFINITIONS

| Clock Name | Frequency  | Description                                                                                             | Source                                                                                  |

|------------|------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

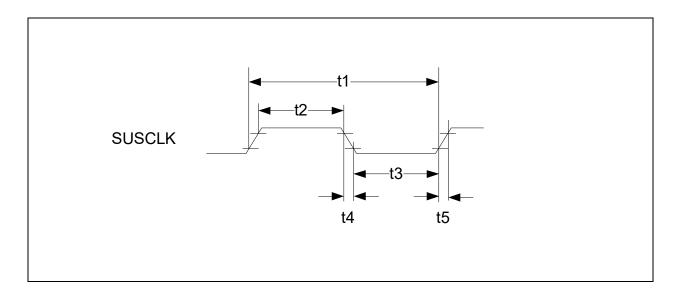

| SUSCLK     | 32.768 kHz | 32.768 kHz Suspend Well Clock input. Used to generate 48MHz internal clocking, and the 24MHz LPC Clock. | From Host Chipset. Note that this clock may be running before VTR voltages are present. |

| eSPI_CLK   | 2050 MHz   | eSPI Transfer Clock, asynchronous to all others. Only runs during active transfers.                     | From Host Chipset.                                                                      |

Note 3-1 The SUSCLK input from the Chipset may not be at a valid 32 kHz frequency until some period of time after the deassertion of RSMRST#. See chipset specification for the actual timing.

Note 3-2 The internal 48 MHz Ring Oscillator acquires a frequency lock referenced to the external 32kHz clock source. It is not externally presented, but it is the basis of the LPC\_CLK outputs when they are enabled.

#### 3.5.2 GENERATED CLOCK OUTPUTS

This section describes clocks generated by the ECE1200 that may be used by the external system.

TABLE 3-4: GENERATED CLOCK DEFINITIONS

| Clock Name                | Frequency | Description                                          | Source                 |

|---------------------------|-----------|------------------------------------------------------|------------------------|

| 48 MHz Ring<br>Oscillator | 48 MHz    | Multiplied up from 32KHz input                       | SUSCLK                 |

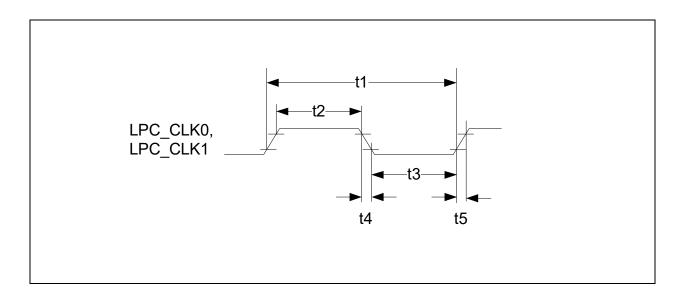

| LPC_CLK[1:0]              | 24 MHz    | System clock outputs for LPC, Serial IRQ and CLKRUN# | 48 MHz Ring Oscillator |

#### 3.6 Resets

TABLE 3-5: DEFINITION OF RESET SIGNALS

| Reset       | Description                                                                                                                                                                                            | Source                                                                                                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| RESETI#     | External Pin that serves as the VTR POR event when pulsed low. Resets the entire device.                                                                                                               | Pin Input Intended to come from system RSMRST#.                                                       |

| eSPI_RESET# | Reset signal associated with the eSPI interface. Restarts the eSPI interface if pulsed low. Will be held low by the system while RESETI# (RSMRST#) is low, and rises after the rising edge of RESETI#. | Pin Input Intended to come from system eSPI_RESET#.                                                   |

| PLTRST#     | Platform Reset.                                                                                                                                                                                        | Pin Input<br>Intended to come from system PLTRST#,<br>serving also as system LRESET# /<br>PCI_RESET#. |

## 3.7 Chip Power Management Features

Various mode bits in the register set may be set in order to save power. Some of these are the standard LPC features (Serial IRQ Quiet Mode, CLKRUN#), and some are added in order to place the part into deeper sleep states internally. See Section 6.6, "Low Power Modes," on page 35.

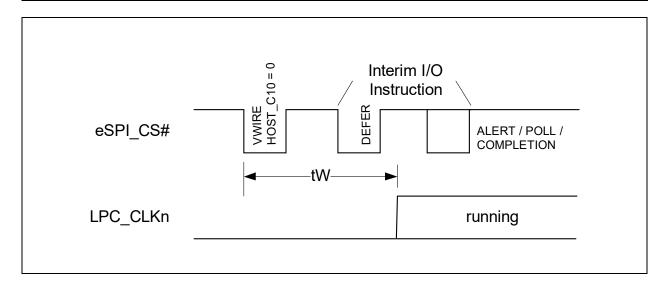

Sleep states generally involve only gating clocking internally, and exiting them is nearly immediate. Waking from a Sleep state only takes any significant amount of time if the ECE1200's own Deep Sleep mode is selected (VW\_C10\_STOPOSC in the Power Save Register) and the Host CPU is waking from the C10 power state. In this case a delay in response happens until the 48 MHz Ring Oscillator restarts and locks again to its frequency. Note that this delay may in turn be bypassed using the FORCE\_OSC\_LOCK bit, but this will provide an inaccurate (and slower) clock until a true lock has been achieved.

A Wake from Deep Sleep may also be triggered by the CLKRUN# pin, generally because of the Quiet Mode mechanism. It is necessary for the requesting device to tolerate the lack of LPC clocks during the Frequency Lock delay. The ECE1200 also responds by pulling CLKRUN# low itself at this time, enabling clocks, since the interface is no longer idle.

When there is a delay involved in exiting Deep Sleep, any I/O instruction from the Host CPU will be held using the Deferred Completion mechanism of eSPI until frequency lock has been acquired. Note that eSPI I/O traffic is not a Wake mechanism, since the CPU has to have awakened already for it to do this. The eSPI interface will already have transmitted the new HOST C10 Virtual Wire state, which performs the Wake.

## 4.0 LPC INTERFACE

## 4.1 Introduction

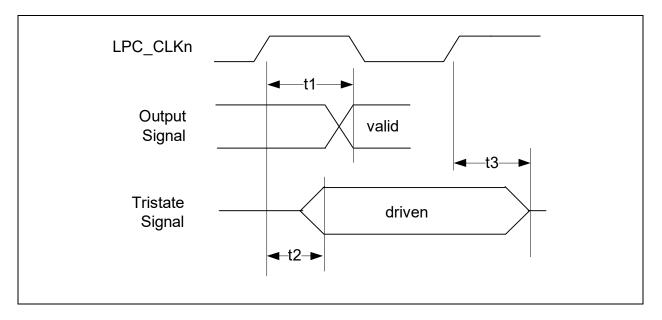

The Low Pin Count (LPC) Interface provides the Master end of the LPC Bus Interface, by bridging from the eSPI Interface (Section 5.0, "Enhanced Serial Peripheral Interface (eSPI)," on page 25). Generated LPC transfer cycles are defined in Table 4-2, "LPC Cycle Types Generated".

Also provided are the Master end of the legacy Serial IRQ interface for interrupts, and the legacy Clock Control interface via the CLKRUN# signal.

#### 4.2 References

- Intel® Low Pin Count (LPC) Interface Specification, v1.1

- PCI Local Bus Specification, Rev. 2.2

- Serial IRQ Specification for PCI Systems Version 6.0

- PCI Mobile Design Guide Rev 1.0

## 4.3 Interface

## 4.3.1 SIGNAL DESCRIPTION

TABLE 4-1: LPC LEGACY SIGNAL DESCRIPTION TABLE

| Name                                      | Direction    | Description                                                                                                                                                                                                      |

|-------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LAD[3:0]                                  | Input/Output | The 4-bit LPC multiplexed command, address, and data bus.                                                                                                                                                        |

| LFRAME#                                   | Output       | Active low signal indicates start of new cycle and termination of broken cycle.                                                                                                                                  |

| PLTRST#,<br>used as<br>LRESET#            | Input        | LRESET# is the LPC legacy name of the active low signal PLTRST# used as LPC Interface Reset. It is received from the Chipset's PLTRST# output, in parallel with all LPC slaves. Also called PCI Reset in system. |

| LPC_CLK_[1:0],<br>each used as an<br>LCLK | Outputs (2)  | Provided as a 24-MHz frequency. Two pins are provided for distribution of loading, and may be individually enabled, disabled or controlled by CLKRUN#.                                                           |

| SER_IRQ                                   | Input/Output | Serial IRQ pin used with the LCLK signal to transfer interrupts.                                                                                                                                                 |

| CLKRUN#                                   | Input/Output | Clock Control for LCLK outputs                                                                                                                                                                                   |

| SUS_STAT#,<br>used as<br>LPCPD#           | Output       | LPC Power Down: Indicates that the device should prepare for power to be removed from the LPC I/F. This is propagated from the Virtual Wire named SUS_STAT#.                                                     |

#### 4.3.2 REGISTER INTERFACES

The register set providing control for the LPC block is defined in Section 6.0, "Device Register Set and Initialization," on page 33. Initialization of registers is not required in order to propagate bridged I/O or Memory traffic to LPC, but is required for initializing and enabling SER IRQ and CLKRUN# features.

## 4.4 Power, Clocks and Reset

This section defines the Power, Clock, and Reset parameters of the block.

#### 4.4.1 POWER DOMAINS

| Name                                             | Description                                                                                                                                                                                                             |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LPC_EN<br>from PCH_PWROK<br>(VCC / Main / S0 On) | The LPC Interface block is powered by VTR_33 and VTR_CORE_18. However, these features are active only while LPC_EN is high, indicating that system Main (VCC / S0) power is also good. This is "Emulated VCC" behavior. |

#### 4.4.2 CLOCKING

The LPC Interface runs from a 48MHz internal reference, 48 MHz Ring Oscillator, which is derived from the SUSCLK input. In turn, it generates the 24MHz timebase for the LPC clocks.

#### 4.4.3 RESETS

| Name                    | Description                                                       |  |

|-------------------------|-------------------------------------------------------------------|--|

| RESETI#                 | Power on Reset to the entire chip, externally provided.           |  |

| PLTRST#<br>(as LRESET#) | This is the Platform Reset, used to reset internal LPC resources. |  |

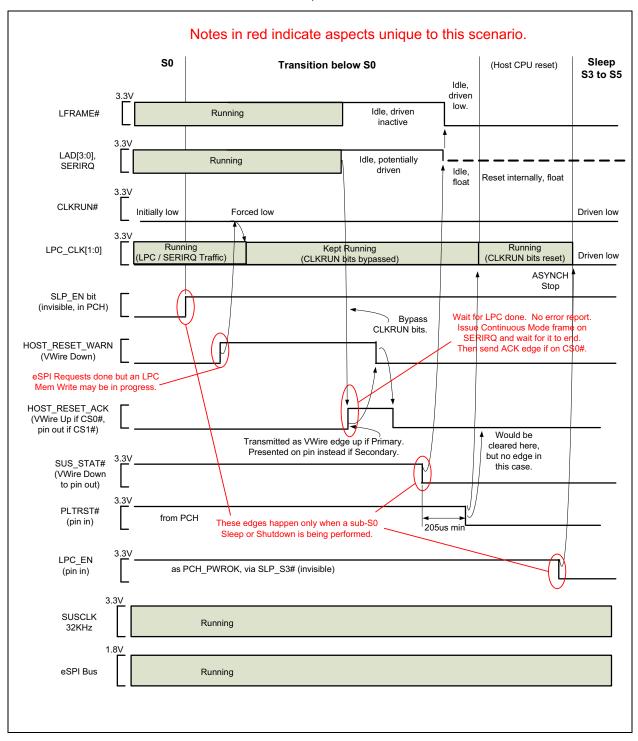

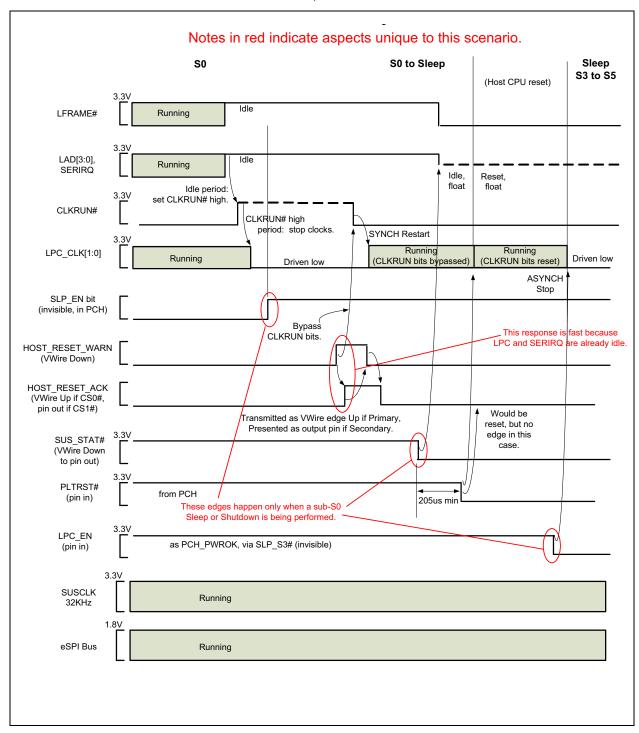

For the sequences of Power and Reset state transitions, see Section 9.7, "System Power State Transition Diagrams," on page 70.

## 4.5 LPC Controller Description

The LPC Controller is compliant with the Intel® Low Pin Count (LPC) Interface Specification, v1.1. Section 4.5.1, "Cycle Types Generated" further clarifies which LPC Interface features have been implemented and qualifies any system specific requirements.

The LPC Controller accepts all eSPI I/O and Memory traffic that is directed to it from the Chipset, and passes it to the LPC bus except for the two I/O addresses used for accessing its internal register set (see Section 6.0, "Device Register Set and Initialization," on page 33). Traffic that is unclaimed or rejected on the LPC bus may optionally be detected and reported to the Chipset by selectable eSPI mechanisms.

Slave devices on LPC may use the SER\_IRQ mechanism to notify the host of an event.See Section 4.7, "Serial IRQ," on page 23.

The CLKRUN# feature is provided, allowing negotiation with LPC slave devices to turn off the LPC clock(s) as desired.

## 4.5.1 CYCLE TYPES GENERATED

The following cycle types are generated by the LPC Interface Controller. Note that they are all 1 byte in length. eSPI I/O or Memory cycles that are larger than 1 byte are allowed, and are broken down into individual bytes, transferred least-significant byte first.

TABLE 4-2: LPC CYCLE TYPES GENERATED

| Cycle Type   | Transfer Size |

|--------------|---------------|

| I/O Read     | 1 byte        |

| I/O Write    | 1 byte        |

| Memory Read  | 1 byte        |

| Memory Write | 1 byte        |

#### 4.5.2 SYNC FIELD HANDLING

The SYNC field in an LPC transfer provides status for each byte transferred. The LPC Interface recognizes only the following SYNC encodings:

TABLE 4-3: SYNC FIELD ENCODINGS RECOGNIZED

| SYNC Code | Interpretation                    |  |  |

|-----------|-----------------------------------|--|--|

| 0000      | Ready                             |  |  |

| 0101      | Short Wait                        |  |  |

| 0110      | Long Wait                         |  |  |

| 1010      | Error                             |  |  |

| other     | Unrecognized, considered Reserved |  |  |

#### 4.5.2.1 Wait SYNCs on LPC

Both Long Wait and Short Wait SYNC responses are handled identically, expecting either the Ready or Error SYNC code to appear. The ECE1200 device does not impose a time-out, leaving that to the Host Chipset.

## 4.5.2.2 Unclaimed LPC Cycle

An unclaimed LPC cycle is detected if no recognized SYNC code is seen after 3 clocks, or if an unrecognized SYNC code is detected after Wait SYNCs. This will terminate the current byte by the ABORT mechanism, and all subsequent byte transfers from the same eSPI transfer will be abandoned. The result reported over eSPI will be determined based on the type of eSPI transfer:

#### Non-Posted (I/O Read, I/O Write or Memory Read):

UNSUCCESSFUL COMPLETION, and other reporting as programmed in the Unclaimed Non-Posted Error Handling Register, Section 6.9.4, on page 40.

#### Posted (Memory Write only):

as programmed in the Unclaimed Posted Error Handling Register, Section 6.9.8, on page 42.

UNSUCCESSFUL COMPLETION is not a possible response to a Posted transfer.

See Section 4.8, "Error Reporting and Logging Registers," on page 24 for details of error posting and logging within the ECE1200.

#### 4.5.2.3 Error (Abort) SYNC

An LPC cycle that is claimed, but is then terminated by the Error SYNC code, will terminate the current byte, and all subsequent byte transfers from the same eSPI transfer. The result reported over eSPI will be determined based on the type of eSPI transfer:

#### Non-Posted (I/O Read, I/O Write or Memory Read):

UNSUCCESSFUL COMPLETION, and other reporting as programmed in the Sync Abort Non-Posted Error Handling Register, Section 6.9.5, on page 41

#### Posted (Memory Write only):

as programmed in the Sync Abort Posted Error Handling Register, Section 6.9.9, on page 42.

UNSUCCESSFUL COMPLETION is not a possible response to a Posted transfer.

See Section 4.8, "Error Reporting and Logging Registers," on page 24 for details of error posting and logging within the ECE1200.

#### 4.6 LPC Clock Run Control CLKRUN#

The CLKRUN# pin is used to indicate the status of the LPC Clock(s) as well as to request that stopped clocks be restarted. The standard for CLKRUN# operation is in the document PCI Mobile Design Guide Rev 1.0.

There is only one CLKRUN# control, but it can be associated with either or both of the LPC Clock pins. A disabled Clock is not affected by CLKRUN#, and remains disabled.

CLKRUN# Support is off by default, meaning that CLKRUN# is driven permanently low and LPC clocks are not gated. This remains the initial state of CLKRUN# by default when the feature is enabled as well. If the Serial IRQ feature is in Quiet Mode and idle, and the LPC bus has been idle for a defined period of time, CLKRUN# will be driven high by the ECE1200, and then parked high using an external pull-up resistor. Any LPC Slave device that requires clocks still to be running will pull CLKRUN# back low itself, and clocks will then continue uninterrupted. If however no Slave device pulls CLKRUN# low, then the ECE1200 will stop the LPC clocks, holding them low.

Once clocks are off, activating CLKRUN# low will re-start them. This may happen by Slave device action, or by the ECE1200 internally upon detecting a request for LPC traffic from the Host Chipset.

When clocks are stopped by CLKRUN# activity, other power saving modes may be engaged. See Section 6.6, "Low Power Modes," on page 35 and Section 3.7, "Chip Power Management Features," on page 19.

#### 4.6.1 ENABLING THE CLKRUN# FUNCTION

See Section 6.8.6, "Set Up Optional CLKRUN# Clock Gating," on page 38.

#### 4.7 Serial IRQ

The ECE1200 device supports Serial IRQ as the Master controller, adhering to the Serial IRQ Specification for PCI Systems Version 6.0. Both Continuous Mode and Quiet Mode operation are supported. The full 21-slot frame format is presented, as has been common practice in LPC-based Southbridge devices.

Serial IRQ inputs are bridged to the equivalent eSPI Virtual Wire traffic. See Section 6.8.4, "Set Up Serial IRQ," on page 37 for the detail and programmable options of the Serial IRQ feature. The Serial IRQ Master supports the following serial inputs:

Legacy Interrupts:

- IRQ1

- IRQ[3:7]

- IRQ[9:12]

- IRQ[14:15]

PCI-Derived Interrupts, mappable to selected IRQ levels, including those above IRQ15:

- INTA#

- INTB#

- INTC#

- INTD#

Discrete signals:

- SMI#

- · IOCHCK# (IOCHK#)

Other inputs are considered deprecated vestiges according to common practice, and are ignored.

The SMI# input on Serial IRQ is considered a signal from downstream sources, and is not captured in the ECE1200 internal register set. Polling for it in the internal register set will fail, and it will appear only in the LPC source device.

The IOCHCK# (IOCHK#) input is treated as an error condition, and three situations may be detected

The IOCHK Non-Posted Error Handling Register, Section 6.9.5, on page 41 defines the action to be taken if the IOCHK# input is activated during the Wait phase of a Non-Posted LPC transfer (I/O Read or Write, or Memory Read).

# **ECE1200**

The IOCHK Posted Error Handling Register, Section 6.9.10, on page 42 defines the action to be taken if the IOCHK# input is activated during the Wait phase of a Posted LPC transfer (Memory Write).

These situations above do not by themselves terminate the LPC transfer, and the peripheral device must terminate the transfer itself (by a SYNC code other than Wait).

The IOCHK Idle Error Handling Register, Section 6.9.7, on page 41 defines the action to be taken if the IOCHK# input is activated outside of an LPC transfer.

## 4.7.1 ENABLING THE SERIAL IRQ FUNCTION

The Serial IRQ feature is disabled by default, and must be enabled. To enable Serial IRQ channel the host must initialize it as described in Section 6.8.4, "Set Up Serial IRQ," on page 37. This may be done either before or after LPC sources have been initialized.

## 4.8 Error Reporting and Logging Registers

#### 4.8.1 VIRTUAL WIRE STATES AND CLEARING

Four eSPI Virtual Wires are available for reporting LPC errors or the IOCHK# event, as programmed in the various Error Handling registers mentioned above. Each Virtual Wire, once posted and signaled to the Chipset, can be polled and cleared by register accesses. The Virtual Wires are:

- ERROR FATAL

- ERROR NONFATAL

- SMI#

- · SCI#

The Virtual Wires ERROR\_FATAL and ERROR\_NONFATAL are polled and cleared in the eSPI Virtual Wire Errors Register, Section 6.9.11, on page 43. They are also cleared by an eSPI\_RESET# event.

The Virtual Wires SMI# and SCI# are polled and cleared in the eSPI Virtual Wire Error Events Register, Section 6.9.12, on page 43. These Virtual Wires are cleared by PLTRST# events as well as eSPI\_RESET# events (eSPI\_RESET# low asserts PLTRST# low as well).

The SMI# Virtual Wire is not recorded in the ECE1200 if it is the result of a Serial IRQ report. In that case, it will be recorded in the originating device, and can be polled and cleared there, propagating through the ECE1200 as it changes state on the Serial IRQ port. A PLTRST# event will clear it in the ECE1200, as well as at the originating device.

#### 4.8.2 LPC CYCLE ERROR LOGGING

The various error conditions occurring during an LPC transfer are logged as individual bits in two registers:

- The LPC Error Log Non-Posted Register, Section 6.11.8, on page 56 holds errors detected in Non-Posted transfers.

- The LPC Error Log Posted Register, Section 6.11.9, on page 56 holds errors detected in Posted transfers.

In addition, the address and type of LPC access are captured on each error:

- The Error Cycle Attributes Register, Section 6.11.14, on page 57 holds the type of access: Read vs.Write and I/O vs. Memory.

- The four Error Cycle Address registers, starting at Section 6.11.10, on page 57, hold the address captured from the LPC bus on an error. I/O addresses load only the low-order two bytes of the address; Memory addresses load all four bytes.

## 5.0 ENHANCED SERIAL PERIPHERAL INTERFACE (ESPI)

## 5.1 Introduction

The Intel® Enhanced Serial Peripheral Interface (eSPI) in the ECE1200 is a hard-wired subset of the eSPI functionality, dedicated to bridging I/O and Memory traffic with LPC, and Serial IRQ traffic. It also implements Virtual Wires, by which it restores legacy signals and supports new eSPI requirements internally.

## 5.2 References

- 1. Intel Doc #327432, Enhanced Serial Peripheral Interface (eSPI): Interface Base Specification

- 2. Intel Doc #562633, Enhanced Serial Peripheral Interface (eSPI) Compatibility Specification

## 5.3 Terminology

This table defines specialized terms localized to this feature.

TABLE 5-1: TERMINOLOGY

| Term                                   | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Host                            | Refers to the external Chipset that originates the I/O and Memory traffic over the eSPI Interface.                                                                                                                                                                                                                                                                                                                                                                                                       |

| Master / Slave                         | Following the SPI convention, the System Host is the eSPI Master and the ECE1200 is the eSPI Slave. The Slave can request the Master's attention using the ALERT# functionality, but all traffic is driven by the Master.                                                                                                                                                                                                                                                                                |

| Virtual Wire /<br>Virtual Wire Channel | A Virtual Wire is a 1-bit digital state that is transferred between the System Host and the ECE1200. Some Virtual Wires are translated to/from physical pins by the ECE1200. Other Virtual Wires present IRQs to the Host System from the Serial IRQ feature, participate in handshakes for system power state transitions, or signal exceptions to the Host System.  The eSPI Virtual Wire Channel is a category of eSPI traffic that is multiplexed onto the eSPI pins for transferring Virtual Wires. |

| Peripheral Channel                     | This is a category of eSPI traffic that is multiplexed onto the eSPI pins for performing I/O and Memory traffic originating from the System Host.                                                                                                                                                                                                                                                                                                                                                        |

| eSPI Configuration Registers           | A set of registers that are dedicated to initial low-level setup of the eSPI bus by the System Host. They are accessible only using the eSPI GET_CONFIGURATION and SET_CONFIGURATION commands, and are separate from the internal register set that is accessed by I/O traffic.                                                                                                                                                                                                                          |

## 5.4 Bus Interface

## 5.4.1 BUS PINS

Table 5-2, "eSPI Bus Signal Description Table" lists the eSPI bus signals on the pin interface. These are documented by Intel specifications.

TABLE 5-2: ESPI BUS SIGNAL DESCRIPTION TABLE

| Signal Name | Direction    | Description                                                                                                                                                                                                                                   |

|-------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| eSPI_CS#    | Input        | eSPI Chip Select, Low-Active                                                                                                                                                                                                                  |

| eSPI_CLOCK  | Input        | eSPI Clock                                                                                                                                                                                                                                    |

| eSPI_ALERT# | Output       | eSPI Alert signal, Low-Active. Exercised only if the Host System specifically enables it, which it will do if there are other eSPI Slaves in the system. Otherwise the default configuration is to present ALERT# events on the eSPI_IO1 pin. |

| eSPI_RESET# | Input        | POR for eSPI domain, and the Global Reset exercised by the Host System for serious errors. Low-Active.                                                                                                                                        |

| eSPI_IO0    | Input/Output | eSPI Data Bus, bit 0. Input (MOSI) in x1 Bus Mode. In wider bus modes it holds the LS data bit.                                                                                                                                               |

| eSPI_IO1    | Input/Output | eSPI Data Bus, bit 1. Output (MISO) in x1 Bus Mode. Also, by default and if there is only a single Slave in a point-to-point configuration, it presents the ALERT# state while the eSPI bus is idle.                                          |

| eSPI_IO2    | Input/Output | eSPI Data Bus, bit 2.<br>Used only in x4 mode.                                                                                                                                                                                                |

| eSPI_IO3    | Input/Output | eSPI Data Bus, bit 3.<br>Used only in x4 mode, as MS bit.                                                                                                                                                                                     |

## 5.5 Sideband Support Interface

## 5.5.1 ESPI SIDEBAND SUPPORT PIN LIST

Table 5-3, "eSPI Sideband Signal Description Table" lists a set of signals that are typically needed for supporting (or bypassing) certain features of eSPI that are propagated as Virtual Wires.

TABLE 5-3: ESPI SIDEBAND SIGNAL DESCRIPTION TABLE

| Signal Name                   | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BOOT_DONE                     | Input     | Selects eSPI Slave role as Primary (high) vs. Secondary (low). Also allows a delayed assumption of the Primary Slave role. See Section 5.5.2, "BOOTDONE," on page 27                                                                                                                                                                                                                                                                                   |

| SUSWARN#                      | Output    | Presents the state of the Virtual Wire SUS_WARN#, restoring the legacy PCH pin function. Connect to the SUSACK# pin for a mandatory handshake, as per Section 1.1.1, "General System Block Diagram," on page 5, Figure Note 4. See also Section 5.5.3, "SUSWARN#," on page 28.                                                                                                                                                                         |

| SUSACK#                       | Input     | Edges on this pin are transmitted to the PCH as the Virtual Wire SUS_ACK#. Connect to the SUSWARN# pin for a mandatory handshake, as per Section 1.1.1, "General System Block Diagram," on page 5, Figure Note 4. See also Section 5.5.4, "SUSACK#," on page 28.                                                                                                                                                                                       |

| SUSPWRDNACK /<br>HOST_RST_ACK | Output    | In the Primary Slave role, presents the state of the Virtual Wire SUSPWRDNACK, restoring the legacy PCH pin function. See Section 1.1.1, "General System Block Diagram," on page 5, Figure Note 3. In the Secondary role, presents the HOST_RST_ACK state as a physical signal. See Section 1.1.4, "System Block Diagram, ECE1200 as Secondary eSPI Slave," on page 8, Figure Note 4. See also.Section 5.5.5, "SUSPWRDNACK / HOST_RST_ACK," on page 28 |

## 5.5.2 BOOT DONE

The BOOT\_DONE option selects the eSPI Slave role (Primary or Secondary) that the ECE1200 should assume. The Secondary Slave role is more passive than the Primary Slave role, in that it does not participate in Virtual Wire handshake responses over eSPI. It does receive the initial Virtual Wire, but for information only. For examples of system configurations and BOOT\_DONE connections for them, see the figures in Section 1.1, "System Block Diagrams," on page 5.

BOOT\_DONE is not sampled at any one time, but has its effect continuously, and may either be strapped to a static value or be changed once, as explained below.

- BOOT\_DONE = permanently High means that the ECE1200 serves as the Primary eSPI slave. This means that the Chipset has only one ESPI\_CS# pin, or that there are two eSPI slaves and the ESPI\_CS# on the ECE1200 is connected to the Chipset's ESPI\_CS0# pin.

- The output pin SUSPWRDNACK/HOST\_RST\_ACK is driven as the SUSPWRDNACK function, and the internal HOST\_RST\_ACK state is transmitted as a Virtual Wire.

- At the first opportunity, the Virtual Wires SLAVE\_BOOT\_LOAD\_DONE and SLAVE\_BOOT\_LOAD\_STATUS are both transmitted as '1' to the Chipset, freeing the system to boot above the S5 state.

- BOOT\_DONE = permanently Low means that the ECE1200 serves as a Secondary eSPI slave of two or more in the system (that is, it is connected to ESPI\_CS1# or higher from the Chipset).

- The SLAVE\_BOOT\_LOAD\_DONE and SLAVE\_BOOT\_LOAD\_STATUS Virtual Wires are not transmitted, and instead come from the Primary Slave, which is required to be present also.

- The output pin SUSWARN# is driven from its Virtual Wire, but is not expected to be used by the system. The input pin SUSACK# has no function in this configuration, and its state will be ignored.

- The output pin SUSPWRDNACK/HOST RST ACK is driven as the HOST RST ACK function.

- BOOT\_DONE = Low then High is a way of delaying booting of the system, by an ECE1200 wired as the Primary Slave, if some system consideration requires a further delay after RSMRST# has gone high. While BOOT\_DONE remains low, the Virtual Wires SLAVE\_BOOT\_LOAD\_DONE and SLAVE\_BOOT\_LOAD\_STATUS are not yet transmitted to the Chipset. On the rising edge of BOOT\_DONE, these Virtual Wires are transmitted as '1' values, and the ECE1200 assumes its Primary eSPI Slave role from this time onward. No Virtual Wire traffic is lost in this sequence, because it does not commence until the SLAVE\_BOOT\_LOAD\_xxx Virtual Wires have been sent from a Primary slave.

The output pin SUSPWRDNACK/HOST\_RST\_ACK is initially driven low (as HOST\_RST\_ACK, temporarily), then driven as the SUSPWRDNACK function (also initially low) when BOOT DONE rises.

TABLE 5-1: BOOT\_DONE

| BOOT_DONE | Description                                                                                                                                                                                                                                                                                           |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0         | ECE1200 assumes the Secondary eSPI Slave role. Certain Virtual Wire interactions will not occur, deferring to another Primary device for this traffic. SUSPWRDNACK/HOST_RST_ACK pin = HOST_RST_ACK                                                                                                    |

| 1         | ECE1200 assumes the Primary eSPI Slave role. At the first opportunity, it will transmit VWires SLAVE_BOOT_LOAD_DONE and SLAVE_BOOT_LOAD_STATUS as '1' to the Chipset.  SUSPWRDNACK/HOST_RST_ACK pin = SUSPWRDNACK                                                                                     |

| 0 then 1  | ECE1200 assumes the Primary eSPI Slave role at the rising edge. It will transmit VWires SLAVE_BOOT_LOAD_DONE and SLAVE_BOOT_LOAD_STATUS as '1' to the Chipset, either immediately or at the first opportunity provided by the eSPI Master in the Chipset.  SUSPWRDNACK/HOST_RST_ACK pin = SUSPWRDNACK |

| 1 then 0  | Undefined action, and not allowed. It may lead to undefined operation in the system.                                                                                                                                                                                                                  |

#### 5.5.3 SUSWARN#

This pin restores a pin that may no longer be available on an eSPI-configured Chipset. It presents the state of the Virtual Wire replacement.

Usage:

This output serves as the PCH-driven request to enter DSW Deep Sleep mode. When configured as the Primary eSPI Slave, the SUSWARN# pin must be connected to provide a handshake with the SUSACK# pin. This connection may be direct, or it may involve external circuitry and/or the EC to provide a gating delay, as required by the DSW needs of the system.

A connection between SUSWARN# and SUSACK# should be considered mandatory regardless of whether DSW Deep Sleep is being used in the system. Each edge presented on SUSWARN# must be followed by a corresponding edge on the SUSACK# pin, or else the system may hang and fail to boot.

See Section 1.1.1, "General System Block Diagram," on page 5, and Note 4 below it.

#### 5.5.4 SUSACK#

This input restores a pin that may no longer be available on an eSPI-configured Chipset. Edges on this pin are transmitted as Virtual Wire events to the Chipset.

Usage

It is intended to accept edges coming ultimately from the SUSWARN# pin. See Section 5.5.3, "SUSWARN#" above.

#### 5.5.5 SUSPWRDNACK / HOST RST ACK

This pin is multiplexed by the state of the BOOT DONE pin. See Section 5.5.2, "BOOT DONE," on page 27.

#### 5.5.5.1 Primary Slave Role: SUSPWRDNACK

In the Primary Slave role (BOOT\_DONE = 1), this pin presents the state of the Virtual Wire SUSPWRDNACK, replacing a physical signal no longer presented by some eSPI-mode PCH devices. It may be used by the EC or external circuitry as permission to remove Chipset Primary power for Deep Sleep (Chipset G3 mechanism).

In this role, the HOST RST ACK state is transmitted over eSPI as a Virtual Wire, and does not involve a physical signal.

## 5.5.5.2 Secondary Slave Role: HOST\_RST\_ACK

This pin is provided to supply optional support for an eSPI-specific handshake (HOST\_RST\_WARN/HOST\_RST\_ACK), which is performed separately by the Primary eSPI Slave (EC or SIO), to grant permission for the Chipset to issue an LRESET# event. A Secondary Slave cannot respond to this handshake over eSPI directly, though it does see the HOST\_RST\_WARN Virtual Wire.

The HOST\_RST\_ACK pin output goes high in response to the rising edge of Virtual Wire HOST\_RST\_WARN, delayed until the LPC and Serial IRQ interfaces have become idle in response. If the Primary Slave can make use of this signal to delay its own Virtual Wire HOST\_RST\_ACK response, this signal may be connected to it. Otherwise, this pin may be left unconnected.

The Virtual Wire SUSPWRDNACK is irrelevant to a Secondary Slave, intended to be processed by the Primary Slave instead.

## 5.6 Register Interface

The registers associated with eSPI itself are only the eSPI Configuration Registers. They are accessed only for initialization of eSPI communication parameters, by Chipset hardware after removal of the eSPI\_RESET# signal. See Section 5.8, "eSPI Configuration Registers," on page 30 for details of these special registers.

Other registers, used for controlling the Bridging functionality between eSPI and LPC, are described in Section 6.0, "Device Register Set and Initialization," on page 33.

## 5.7 Description

#### 5.7.1 OPERATING FREQUENCY

The part supports standard eSPI specifications up to the 50MHz operating frequency. It does not, however, enforce a limit to the Host Chipset, which remains in full control of the frequency selection. See the Intel Compatibility Specification document listed in Section 5.2, "References" for the "Soft-Straps" that declare this for the system.

Any additional eSPI Slave may have its own independent frequency setting, including the maximum 66MHz, and its traffic will have no effect on this device.

#### 5.7.2 PERIPHERAL CHANNEL SUBSET

The eSPI Peripheral Channel supports I/O and Memory traffic initiated by the Host System. It does not support eSPI Memory Mastering emulation to Host DRAM, nor the associated LTR command.

It therefore does not attempt to re-create legacy LPC DMA or Mastering.

#### 5.7.3 VIRTUAL WIRE CHANNEL SUBSET

As referenced to the Intel Compatibility Specification document listed in Section 5.2, "References", a subset of Virtual Wires is implemented as shown in Table 5-4. "RFU" represents a Virtual Wire that is implemented for future use only.

In Table 5-4, the following notations are used:

- IDX is the Virtual Wire Index number for the group of 4 Virtual Wires.

- Dir is the Virtual Wire direction for that Index: "Dn" (Down) is Master to Slave, "Up" is Slave to Master.

TABLE 5-4: VIRTUAL WIRES IMPLEMENTED

| SLP_S5# OOB_RST_ WARN WAKE# ERROR_            | SLP_S4#<br>PLTRST#<br>X                          | SLP_S3# SUS_STAT# OOB_RST                                      | x000<br>x000                                                                                                                 | eSPI_RESET#<br>eSPI_RESET#                                                                                                                                              |

|-----------------------------------------------|--------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WARN<br>WAKE#                                 |                                                  | _                                                              | x000                                                                                                                         | eSPL RESET#                                                                                                                                                             |

|                                               | Х                                                | OOR PST                                                        | 1                                                                                                                            | COLI_NEOLI#                                                                                                                                                             |

| ERROR_                                        |                                                  | ACK                                                            | 11x0                                                                                                                         | eSPI_RESET#                                                                                                                                                             |

| NONFATAL                                      | ERROR_<br>FATAL                                  | SLAVE_BOOT_<br>LOAD_DONE                                       | 0000                                                                                                                         | eSPI_RESET#                                                                                                                                                             |

| RCIN#                                         | SMI#                                             | SCI#                                                           | 0111                                                                                                                         | PLTRST#                                                                                                                                                                 |

| Х                                             | X                                                | HOST_RST_<br>WARN                                              | xxx0                                                                                                                         | PLTRST#                                                                                                                                                                 |

| Х                                             | RFU                                              | SUS_ACK#                                                       | xx00                                                                                                                         | eSPI_RESET#                                                                                                                                                             |

| Х                                             | SUS_PWRDN_<br>ACK                                | SUS_WARN#                                                      | 0x00                                                                                                                         | eSPI_RESET#                                                                                                                                                             |

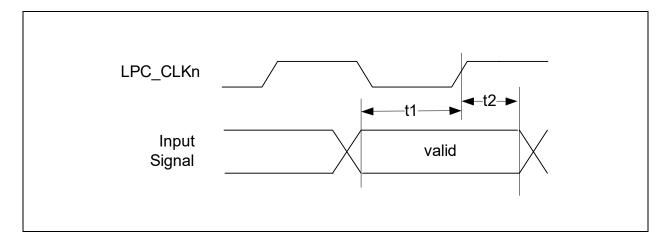

| Х                                             | SLP_WLAN#                                        | SLP_LAN#                                                       | xx00 eSPI_RESET#                                                                                                             |                                                                                                                                                                         |