MOSFET Full Bridge Hybrid

The DRF1510 is a full bridge hybrid containing four high power gate drivers and four power MOSFETs. It was designed to provide the system designer increased flexibility, higher performance, and lowered cost over a non-integrated solution. This low parasitic approach, coupled with the Schmitt trigger input, Kelvin signal ground, provide improved stability and control in Kilowatt to Multi-Kilowatt, High Frequency ISM applications.

#### **FEATURES**

- Switching Frequency: DC TO 13MHz

- · Low Pulse Width Distortion

- Single Power Supply (Per Section)

- CMOS Schmitt Trigger Input 1V Hysteresis

- RoHS Compliant

- Switching Speed 3-4ns

- B<sub>Vds</sub> = 500V

- I<sub>D</sub> = 25A avg. Per-section

- R<sub>ds(on)</sub> ≤ 0.33 Ohm

- P<sub>D</sub> = 550W Per-section

#### **TYPICAL APPLICATIONS**

- · Class D Full Bridge

- · Switch Mode Power Amplifiers

- · HV Pulse Generators

- Ultrasound Transducer Drivers

- · Acoustic Optical Modulators

**Driver Absolute Maximum Ratings (per-Section)**

| Symbol            | Parameter             | Ratings                     | Unit |

|-------------------|-----------------------|-----------------------------|------|

| $V_{dd}$          | Supply Voltage        | 15                          | V    |

| IN                | Input Voltage         | -5 to V <sub>dd</sub> + 0.3 | V    |

| T <sub>JMAX</sub> | Operating Temperature | 175                         | °C   |

# Driver Specifications (Per-Section) @ $T_c = 25$

| Symbol              | Parameter                                                              | Min | Тур  | Max                   | Unit |

|---------------------|------------------------------------------------------------------------|-----|------|-----------------------|------|

| $V_{dd}$            | Supply Voltage                                                         | 10  |      | 15                    | V    |

| IN                  | Input Voltage High                                                     | -5  |      | V <sub>dd</sub> + 0.3 | V    |

| IN <sub>(R)</sub>   | Input Voltage Rising Edge                                              |     | 2.5  |                       | ,,,  |

| IN <sub>(F)</sub>   | Input Voltage Falling Edge                                             |     | 2.5  |                       | ns   |

| I <sub>DDQ</sub>    | Quiescent Current @ V <sub>dd</sub> = 12V                              |     | 15   | 25                    | mA   |

| I <sub>o</sub>      | Output Current                                                         |     | 15   |                       | Α    |

| C <sub>oss</sub>    | Output Capacitance                                                     |     | 2500 |                       |      |

| C <sub>iss</sub>    | Input Capacitance Input                                                |     | 35   |                       | pF   |

| R <sub>IN</sub>     | Input Parallel Resistance, V <sub>in</sub> = 5V, V <sub>dd</sub> = 12V | 1   |      |                       | МΩ   |

| V <sub>th off</sub> | V Threshold Off, V <sub>dd</sub> = 12V, V <sub>in</sub> = 5 to 0V Ramp | 1.0 |      | 1.9                   | V    |

| V <sub>th on</sub>  | V Threshold On, V <sub>dd</sub> = 12V, V <sub>in</sub> = 0 to 5V Ramp  | 2.2 |      | 3.2                   | V    |

| R <sub>q</sub>      | Gate Resistance                                                        | 0.4 | 0.5  | 0.6                   | Ω    |

#### **ESD Characteristics**

| ı | Parameter      | Conditions       | Min | Тур | Max | Unit |

|---|----------------|------------------|-----|-----|-----|------|

|   | ESD Protection | Human Body Model |     | 1.5 |     | kV   |

## **MOSFET Absolute Maximum Ratings (Per-Section)**

| Symbol              | Parameter                                                                                           | Min | Тур  | Max  | Unit |

|---------------------|-----------------------------------------------------------------------------------------------------|-----|------|------|------|

| BV <sub>DSS</sub>   | Drain Source Breakdown Voltage, V <sub>dd</sub> = 12V, V <sub>in</sub> = 0, I <sub>DS</sub> = 250μA | 500 |      |      | V    |

| I <sub>D</sub>      | Continuous Drain Current @ T <sub>C</sub> = 25°C                                                    |     |      | 30   | А    |

| R <sub>DS(on)</sub> | Drain-Source On Resistance V <sub>dd</sub> = 12V, I <sub>DD</sub> = 10A                             |     | 0.25 | 0.33 | Ω    |

| T <sub>jmax</sub>   | Operating Temperature                                                                               |     |      | 175  | °C   |

| I <sub>DSS</sub>    | Zero Gate Voltage Current $V_{DS}$ = 500V, $V_{GS}$ = 0V                                            |     |      | 25   | μΑ   |

# **MOSFET Thermal Characteristics (Per-Section Applicable to Per-Module)**

| Symbol            | Parameter                                                    | Ratings    | Unit  |  |

|-------------------|--------------------------------------------------------------|------------|-------|--|

| R <sub>euc</sub>  | Thermal Resistance Junction to Case (Thermal Joint Compound) | .137       | °C/\\ |  |

| R <sub>0JHS</sub> | Thermal Resistance Junction to Heat Sink                     | .270       | °C/W  |  |

| T <sub>JSTG</sub> | Storage Temperature                                          | -55 to 150 | °C    |  |

| P <sub>D</sub>    | Maximum Power Dissipation @ T <sub>SINK</sub> = 25°C         | 550        | \.,,  |  |

| P <sub>DC</sub>   | Total Power Dissipation @ T <sub>C</sub> = 25°C              | 1095       | W     |  |

## **Driver Thermal Characteristics (Per-Section)**

| Symbol            | Parameter                                            | Ratings    | Unit   |  |

|-------------------|------------------------------------------------------|------------|--------|--|

| R <sub>euc</sub>  | Thermal Resistance Junction to Case                  | 1.4        | °C/\\/ |  |

| $R_{\thetaJHS}$   | Thermal Resistance Junction to Heat Sink             | 2.5        | °C/W   |  |

| T <sub>JSTG</sub> | Storage Temperature                                  | -55 to 150 | °C     |  |

| $P_{_{D}}$        | Maximum Power Dissipation @ T <sub>SINK</sub> = 25°C | 60         | w      |  |

| P <sub>DC</sub>   | Total Power Dissipation @ T <sub>C</sub> = 25°C      | 100        | VV     |  |

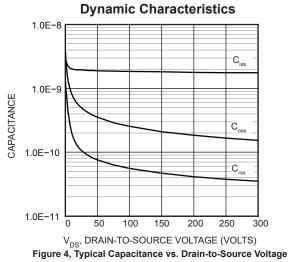

#### MOSFET Specification (Per-Section) @ T<sub>c</sub> = 25°C

| Symbol           | Parameter                                                                   | Min | Тур  | Max | Unit |

|------------------|-----------------------------------------------------------------------------|-----|------|-----|------|

| C <sub>iss</sub> | Input Capacitance (V <sub>gs</sub> = 0V, V <sub>DS</sub> = 150V)            |     | 1810 |     |      |

| C <sub>oss</sub> | Output Capacitance (V <sub>gs</sub> = 0V, V <sub>DS</sub> = 150V)           |     | 210  |     | pF   |

| C <sub>rss</sub> | Reverse Transfer Capacitance (V <sub>gs</sub> = 0V, V <sub>DS</sub> = 150V) |     | 48   |     |      |

| Per                            | Per Section Output Switching Performance, All Silicon Devices are Die Selected Temp = 25°C All DATA IS COLLECTED USING THE TEST CIRCUIT AS SHOWN IN FIGURE 2 |    |     |     |     |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|-----|-----|--|

| Symbol                         | Symbol Characteristic                                                                                                                                        |    |     |     | Тур |  |

| t <sub>f</sub>                 | Fall Time 90% to 10% $V_{dd}$ = 12V, $V_{in}$ = 0 to 5V , $V_{DS}$ = 100V, RL = 16.6 $\Omega$ , CL = 0.4 $\mu$ F                                             | 1  | TBD | 2.5 |     |  |

| t,                             | Rise Time 10% to 90% $V_{dd}$ = 12V, $V_{in}$ = 0 to 5V , $V_{DS}$ = 100V, RL = 16.6 $\Omega$ , CL = 0.4 $\mu$ F                                             | 10 | TBD | 35  |     |  |

| t <sub>DLY(ON)</sub>           | ON Delay Time, 50% to 50% $V_{dd}$ = 12V, $V_{in}$ = 0 to 5V , $V_{DS}$ = 100V, RL = 16.6 $\Omega$ , CL = 0.4 $\mu$ F                                        | 35 | TBD | 55  | ns  |  |

| $t_{	extsf{DLY}(	extsf{OFF})}$ | OFF Delay Time, 50% to 50% $V_{dd} = 12V$ , $V_{in} = 0$ to 5V, $V_{DS} = 100V$ , RL = 16.6 $\Omega$ , CL = 0.4 $\mu$ F                                      | 50 | TBD | 70  |     |  |

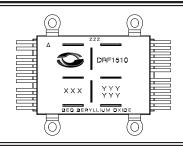

Figure 1, DRF1510 Simplified Circuit Diagram

The DRF1510 is a full bridge power hybrid, see Figure 1 above. Each half bridge of the hybrid consists of two Gate Drivers and two HV Power MOSFETs. In the left HB of the hybrid, U1, U3 is the Gate Driver for Q1, Q3. The input to U1, U3 (IN) with respect to ground (SG) is a CMOS level. C1, C3 provides internal high speed bypassing for the drivers power input +Vdd. Both pins (2, 5 & 13,16) must be attached to the 15V supply and bypassed near each pin. By including the driver high speed by-pass capacitors (C1-C4), their contribution to the internal parasitic loop inductance of the driver output is greatly reduced. This, coupled with the tight geometry of the hybrid, allows optimal gate drive to the MOSFET. The right HB of the hybrid is constructed in an identical manner, U2,4,C2,4 and Q2,4.

None of the inputs to U1 of the DRF1510 are isolated for direct connection to a ground referenced power supply or control circuitry. **Isolation appropriate to full bridge configuration is the responsibility of the end user.** The IN pin is the input for the control signal and is applied to a Schmitt Trigger. **The SG pin, a Kelvin return, is reserved for the control signal ground return only** (Pin 4, 9, 14, 20). On the output side are the Drain (25, 28, 31), Source (24, 27, 30) and Output (26, 29) connections. It is imperative that output currents be restricted to these pins by design.

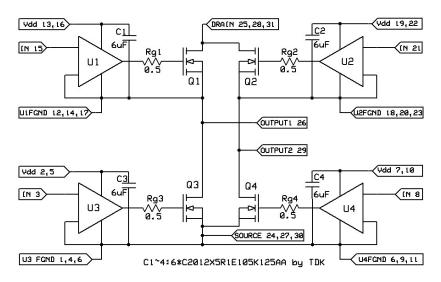

Figure 2, DRF1510 Test Circuit

The DRF1510 Test Circuits illustrated above are **for reference only**. These four circuits allow each of the sections in the Full Bridge to be tested independently. CKTA, C is configured to test the lower or negative supply section of the DRF1510 and CKTB, D is configured to test the upper or positive supply section. This method ties all pins of the unused section to the output CKTA, C or the ground CKTB, D. The internal sub circuit Test Configurations are shown below for the four test circuits above, A for A, B for B and C for C.

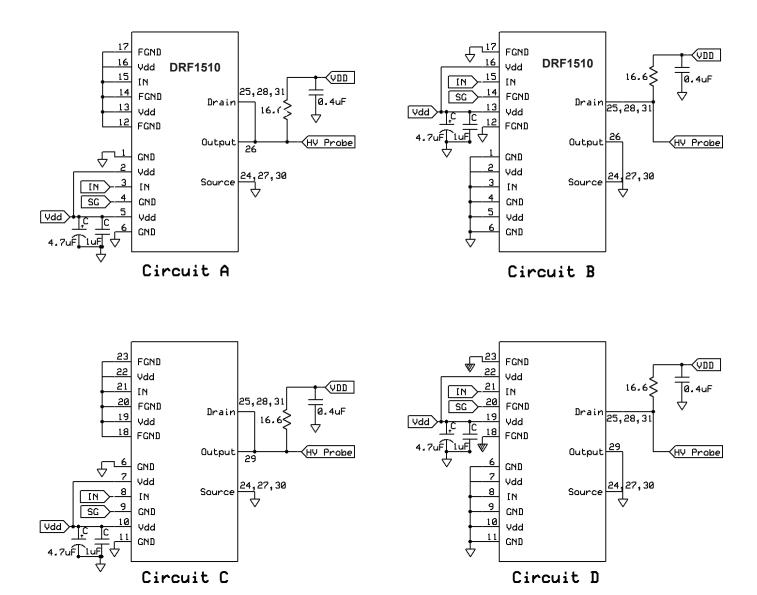

# Figure 3, DRF1510 Test Configurations

The DRF1510 Test configurations illustrated above are for reference only.

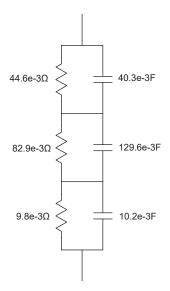

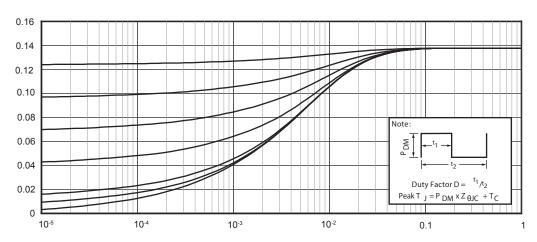

Figure 5a, Transient Thermal Impedance Model

Figure 5, Thermal Impedance Model and Effective Transient Thermal Impedance, Junction -To-Case vs Pulse Duration

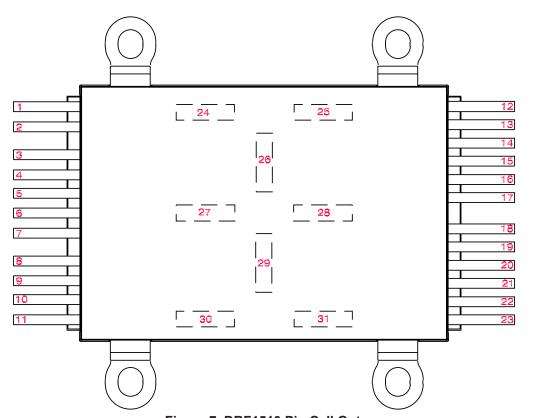

| DRF1510 Pin Assignments |                  |                                            |                  |  |  |  |

|-------------------------|------------------|--------------------------------------------|------------------|--|--|--|

| Pin 1                   | PGND_Low Side 1  | Pin 17                                     | FGND_High Side 1 |  |  |  |

| Pin 2                   | Vdd_Low Side 1   | Pin 18                                     | FGND_High Side 2 |  |  |  |

| Pin 3                   | IN_Low Side 1    | Pin 19                                     | Vdd_High Side 2  |  |  |  |

| Pin 4                   | PGND_Low Side 1  | Pin 20                                     | FGND_High Side 2 |  |  |  |

| Pin 5                   | Vdd_Low Side 1   | Pin 21                                     | IN_High Side 2   |  |  |  |

| Pin 6                   | PGND             | Pin 22                                     | Vdd_High Side 2  |  |  |  |

| Pin 7                   | Vdd_Low Side 2   | Pin 23                                     | FGND_High Side 2 |  |  |  |

| Pin 8                   | IN_Low Side 2    | Pin 24                                     | Source           |  |  |  |

| Pin 9                   | PGND_Low Side 2  | Pin 25                                     | Drain            |  |  |  |

| Pin 10                  | Vdd_Low Side 2   | Pin 26                                     | Output 1         |  |  |  |

| Pin 11                  | PGND_Low Side 2  | Pin 27                                     | Source           |  |  |  |

| Pin 12                  | FGND_High Side 1 | Pin 28                                     | Drain            |  |  |  |

| Pin 13                  | Vdd_High Side 1  | Pin 29                                     | Output 2         |  |  |  |

| Pin 14                  | FGND_High Side 1 | Pin 30                                     | Source           |  |  |  |

| Pin 15                  | IN_High Side 1   | Pin 31                                     | Drain            |  |  |  |

| Pin 16                  | Vdd_High Side 1  | FGND: Floating Ground / PGND: Power Ground |                  |  |  |  |

Figure 6, DRF1510 Mechanical Outline

Dimensions are in inches ( ± 0.008) and mm in brackets

Package withstand voltage 2500V

0.158 [4.00]

0.180 [4.57]

Ø0.125 [Ø3.18]x4 - Ø0.265 [Ø6.48] ×4 0.545 [13.85] -

Y Y Y Y Y Y

BEO BERYLLIUM OXIDE

X X X

0.028 [0.71]x4 0.050 [1.27]×23 -

Figure 7, DRF1510 Pin Call Out

## Disclaimer:

The information contained in the document (unless it is publicly available on the Web without access restrictions) is PROPRIETARY AND CONFIDENTIAL information of Microsemi and cannot be copied, published, uploaded, posted, transmitted, distributed or disclosed or used without the express duly signed written consent of Microsemi. If the recipient of this document has entered into a disclosure agreement with Microsemi, then the terms of such Agreement will also apply. This document and the information contained herein may not be modified, by any person other than authorized personnel of Microsemi. No license under any patent, copyright, trade secret or other intellectual property right is granted to or conferred upon you by disclosure or delivery of the information, either expressly, by implication, inducement, estoppels or otherwise. Any license under such intellectual property rights must be approved by Microsemi in writing signed by an officer of Microsemi.

Microsemi reserves the right to change the configuration, functionality and performance of its products at anytime without any notice. This product has been subject to limited testing and should not be used in conjunction with life-support or other mission-critical equipment or applications. Microsemi assumes no liability whatsoever, and Microsemi disclaims any express or implied warranty, relating to sale and/or use of Microsemi products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Any performance specifications believed to be reliable but are not verified and customer or user must conduct and complete all performance and other testing of this product as well as any user or customer's final application. User or customer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the customer's and user's responsibility to independently determine suitability of any Microsemi product and to test and verify the same. The information contained herein is provided "AS IS, WHERE IS" and with all faults, and the entire risk associated with such information is entirely with the User. Microsemi specifically disclaims any liability of any kind including for consequential, incidental and punitive damages as well as lost profit. The product is subject to other terms and conditions which can be located on the web at http://www.microsemi.com/terms-a-conditions.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Microchip: DRF1510