# CL88030/31

# Sequential Linear LED Driver with Four or Six Taps

#### **Features**

- Suitable for 120VAC/230VAC/277VAC Nominal Input Voltage

- ± 15% Input voltage tolerance recommended

- · Targeted for 2W and Greater Output Power

- Programmable Overtemperature Protection

- Provides gradual reduction in light output with increasing temperature

- Active Line Regulation

- Provides fairly constant output power over variations in AC line voltage

- Adjustable "knee" of regulation

- · Four Taps (CL88030) or Six Taps (CL88031) with Two Current Set Resistors

- Allows optimization of THD

- · Optional Reduced Flicker Index

- Provides near-continuous power to the LEDs

- Reduces strobing

- Uses an external capacitor

- · Compatible with Phase-cut Dimming, both Leading-edge and Trailing-edge

- Uses a Thermally Enhanced DFN-10 Package with Bottom Heatslug

- No high-voltage pins

- \_ Shunt regulator input

- Power dissipation is in the external FETs and LEDs, not in the IC

#### Applications

- · LED Lamps

- · LED Lighting Fixtures

#### Pin Diagram

#### CL88030T CL88031T 3 x 3 DFN\* 3 x 3 DFN\* GT1 1 0 GT1 1 ° 10 ALR 10 ALR GT2 2 9 BIAS GT2 BIAS 9 EP ' EΡ 8 OTP GT3 3 OTP GT3 3 8 11 11 7 CS 4 CS GT4 4 GT4 5 6 NC GT5 5 6 GT6 NC \* Includes Exposed Thermal Pad (EP); see Table 2-1

Description

The CL88030T and CL88031T LED Driver Integrated Circuits (ICs) are intended offline sequential linear LED drivers designed to provide LED power from a utility voltage input.

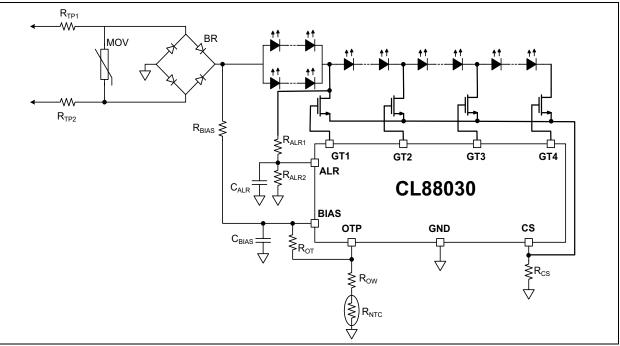

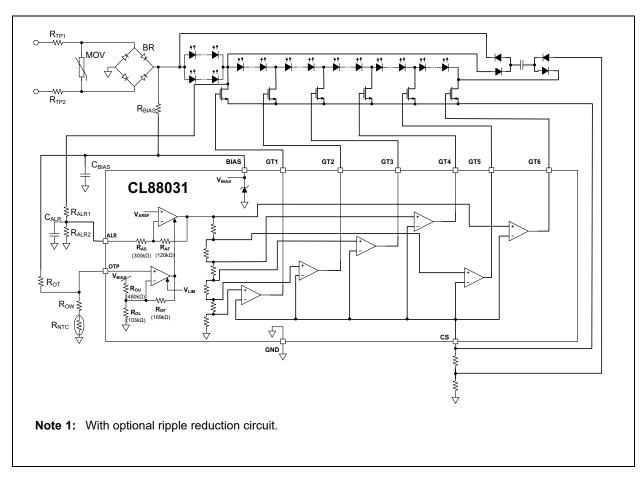

The CL88030/31 devices are designed to drive a long string of inexpensive, low-current LEDs directly from the AC mains. A basic driver circuit consists of Microchip's CL88030/31 LED driver IC, four power FETs (six if using the CL88031), four resistors, two capacitors and a bridge rectifier. Additional components are optional for various levels of transient protection. Adding an inexpensive NTC Thermistor assures overtemperature protection (OTP). No EMI filters or power factor correction circuits are needed (unless the optional flicker-reduction feature is desired).

A string of series/parallel LEDs is tapped at four (or six) locations, called "taps". Linear current regulators sink current at each tap through a single control point and are sequentially turned on and off. High efficiency is achieved by shutting off upstream regulators when downstream regulators achieve regulation. This makes controlling overall input current easier than trying to control multiple current paths by tracking the input sine wave voltage.

The CL88030/31 uses a self-commutation technique using only the tap currents themselves; this technique inherently provides smooth transitions from one regulator to the next without relying on tap voltages or the rectified AC to coordinate the transitions.

## **TYPICAL CL88030T APPLICATION CIRCUIT**

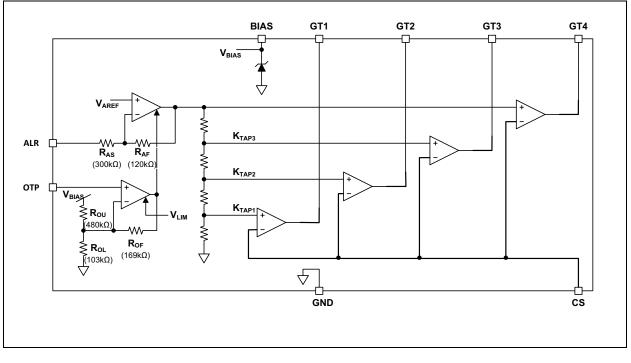

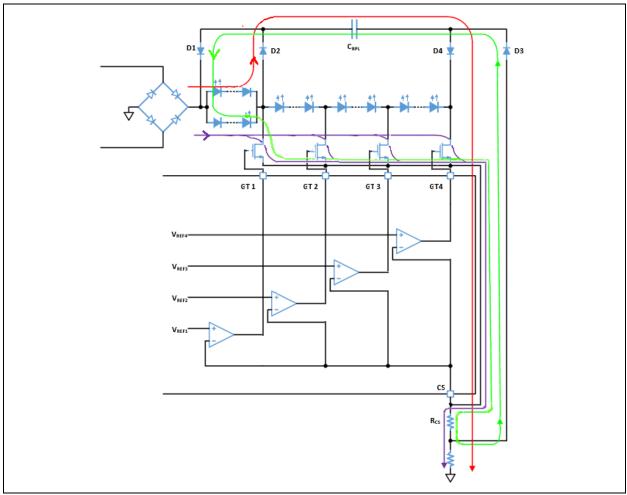

## CL88030 INTERNAL BLOCK DIAGRAM

# TYPICAL CL88031T APPLICATION CIRCUIT AND INTERNAL BLOCK DIAGRAM (Note 1)

## 1.0 ELECTRICAL CHARACTERISTICS

## **ABSOLUTE MAXIMUM RATINGS**

| GT1-4 (and GT5-6 on CL88031T)0.5V to (BIAS + 0.5V) | 1 |

|----------------------------------------------------|---|

| OTP, ALR, CS0.3V to 5.5V                           | / |

| BIAS0.3V to 13V                                    | / |

| Maximum Current into BIAS pin10 mA                 | ١ |

| Operating Junction Temperature40°C to +125°C       | ; |

| Lead Soldering Temperature for 10s 300°C           | ; |

| Storage Temperature65°C to +150°C                  | ; |

| ESD Voltage in any pin 2000V (HBM)                 | ` |

**Notice:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operational listings of this specification, is not intended. Exposure to maximum rating conditions for extended periods may affect device reliability.

## 1.1 ELECTRICAL SPECIFICATIONS

### TABLE 1-1: ELECTRICAL CHARACTERISTICS

Electrical Specifications: Unless otherwise specified, all specifications are for  $T_A = T_J = +25^{\circ}$ C.  $I_{BIAS} = 1.5$  mA. ALR pin open, OTP = 5V unless otherwise noted. Boldface specifications apply over the full temperature range  $T_A = T_J = -15^{\circ}$ C to  $+95^{\circ}$ C.

| Parameters                                                                           | Sym.                 | Min.                    | Тур.  | Max.        | Units | Conditions                       |

|--------------------------------------------------------------------------------------|----------------------|-------------------------|-------|-------------|-------|----------------------------------|

| Gate Output Low (all GTx), V <sub>CS</sub> = 2.0V                                    | V <sub>GT,low</sub>  | _                       | _     | 0.100       | V     | —                                |

| Gate Output High (all GTx), V <sub>CS</sub> = 0V                                     | V <sub>GT,high</sub> | V <sub>BIAS</sub> - 1.0 |       |             | V     | —                                |

| Voltage at BIAS pin<br>I <sub>BIAS</sub> = 0.8, 5 mA, V <sub>CS</sub> = 0V, CL88030  |                      | 10                      | 11    | 12          | V     | —                                |

| Voltage at BIAS pin<br>I <sub>BIAS</sub> = 1.0, 5 mA, V <sub>CS</sub> = 0V, CL88031  | V <sub>BIAS</sub>    | 10                      | 11    | 12          | v     | _                                |

| Gate Output High Current (all GTx)<br>100k GTx to GND, V <sub>CS</sub> = 0V          | I <sub>GT,high</sub> | 10                      |       | _           | μA    | _                                |

| Quiescent Current Consumption                                                        | I <sub>BIAS,Q</sub>  | _                       |       | 900<br>1300 | μA    | Characterization<br>Only, Note 1 |

| Reference Voltage for Tap 4                                                          | V <sub>GT4</sub>     | 1.210                   | 1.275 | 1.339       | V     | CL88030, Note 2                  |

| GT3 to GT4 Current Ratio                                                             | K <sub>TAP3</sub>    | 0.883                   | 0.929 | 0.975       |       | CL88030, Note 2                  |

| GT2 to GT4 Current Ratio                                                             | K <sub>TAP2</sub>    | 0.747                   | 0.786 | 0.825       | ratio | CL88030, Note 2                  |

| GT1 to GT4 Current Ratio                                                             | K <sub>TAP1</sub>    | 0.542                   | 0.571 | 0.600       |       | CL88030, Note 2                  |

| Reference Voltage for Tap 6                                                          | V <sub>GT6</sub>     | 1.210                   | 1.275 | 1.339       | V     | CL88031, Note 2                  |

| GT5 to GT6 Current Ratio                                                             | K <sub>TAP5</sub>    | 0.912                   | 0.960 | 1.008       | ratio | CL88031, Note 2                  |

| GT4 to GT6 Current Ratio                                                             | K <sub>TAP4</sub>    | 0.893                   | 0.940 | 0.987       |       | CL88031, Note 2                  |

| GT3 to GT6 Current Ratio                                                             | K <sub>TAP3</sub>    | 0.846                   | 0.890 | 0.935       |       | CL88031, Note 2                  |

| GT2 to GT6 Current Ratio                                                             | K <sub>TAP2</sub>    | 0.741                   | 0.780 | 0.819       |       | CL88031, Note 2                  |

| GT1 to GT6 Current Ratio                                                             | K <sub>TAP1</sub>    | 0.494                   | 0.520 | 0.546       |       | CL88031, Note 2                  |

| Limiting Voltage from OTP, V <sub>ALR</sub> = 0V, 100 pF<br>CS to GND, GT4/GT6 to CS | V <sub>LIM</sub>     | 1.296                   | 1.525 | 1.754       | V     | —                                |

| Nominal ALR Voltage Reference, ALR pin open, GT4/GT6 to CS, 100 pF, CS to GND        | V <sub>ALR,nom</sub> | —                       | 1.275 | _           | V     | —                                |

| ALR Voltage Ratio at GT4/GT6                                                         | K <sub>ALR,HI</sub>  | 0.801                   | 0.843 | 0.885       | ratio | Note 3                           |

| ALR Voltage Ratio at GT4/GT6                                                         | K <sub>ALR,LO</sub>  | 1.073                   | 1.129 | 1.186       | ratio | Note 4                           |

| OTP Response Voltage                                                                 | OTP                  | 0.90                    | 1.10  | 1.32        | V     | Note 5                           |

**Note 1:** Does not include GATE current, or current into ALR or OTP divider. 900 µA=CL88030,1300 µA=CL88031.

**2:** GTx connected to CS, 100 pF from CS to GND.

3: V<sub>ALR</sub> = 1.776V, GT4/GT6 to CS, 100 pF CS to GND.

4: V<sub>ALR</sub> = 0.863V, GT4/GT6 to CS, 100 pF CS to GND.

5: GT4/GT6 to CS (unity gain), OTP=1.658V, 100 pF CS to GND measure CS/GTx, see Equation 3-3.

#### TABLE 1-2: TEMPERATURE SPECIFICATIONS

| Parameters                   | Sym.            | Min. | Тур. | Max. | Units | Conditions |

|------------------------------|-----------------|------|------|------|-------|------------|

| Temperature Ranges           |                 |      |      |      |       |            |

| Operating Temperature Range  | Τ <sub>J</sub>  | -40  | —    | +125 | °C    | Note 1     |

| Storage Temperature Range    | T <sub>A</sub>  | -65  | —    | +150 | °C    | —          |

| Package Thermal Resistance   |                 |      |      |      |       |            |

| Thermal Resistance, 10LD-DFN | θ <sub>JC</sub> | _    | +8   | _    | °C/W  | Note 2     |

**Note 1:** The Operating Temperature Range is specified at the junction. The junction temperature must be computed using the thermal resistance (TR) from junction-to-case, and the case-to-ambient TR of the PCB design.

2: Thermal resistance is measured from junction to bottom metal slug.

#### 2.0 PIN DESCRIPTION

The descriptions of the pins are listed in Table 2-1.

| TABLE 2-1:         PIN DESCRIPTION |          | CRIPTION |                                                                                                                                                     |

|------------------------------------|----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| CL88030T                           | CL88031T | Pin Name | Description                                                                                                                                         |

| 1                                  | 1        | GT1      | Drives the FET for the most upstream LED string.                                                                                                    |

| 2                                  | 2        | GT2      | Drives the FET for the top 2 LED strings.                                                                                                           |

| 3                                  | 3        | GT3      | Drives the FET for the top 3 LED strings.                                                                                                           |

| 4                                  | 4        | GT4      | Drives the FET for the top 4 LED strings.                                                                                                           |

| 5                                  | _        | NC       | Not connected. To be left floating.                                                                                                                 |

| 6                                  | _        | NC       | Not connected. To be left floating.                                                                                                                 |

| 7                                  | 7        | CS       | Used to set the currents in the taps.                                                                                                               |

| 8                                  | 8        | OTP      | Provides remote Overtemperature Protection.                                                                                                         |

| 9                                  | 9        | BIAS     | Provides power to the IC using an internal shunt regulator. It is recommended to be bypassed with a low ESR ceramic capacitor (at least 1 $\mu$ F). |

| 10                                 | 10       | ALR      | An external resistive voltage divider and capacitor provide line regulation for the tap currents.                                                   |

| 11                                 | 11       | GND      | Circuit common electrical connection (ground).                                                                                                      |

|                                    | 5        | GT5      | Drives the FET for the top 5 LED strings.                                                                                                           |

|                                    | 6        | GT6      | Drives the FET for the top 6 LED strings.                                                                                                           |

#### 2.1 GT1 Pin

Gate drive voltage connection for external power FET for the first/top LED string.

#### 2.2 GT2 Pin

Gate drive voltage connection for external power FET for the second LED string.

#### 2.3 GT3 Pin

Gate drive voltage connection for external power FET for the third LED string.

#### 2.4 GT4 Pin

Gate drive voltage connection for external power FET for the fourth LED string.

#### 2.5 GT5 Pin

Gate drive voltage connection for external power FET for the fifth LED string.

#### 2.6 GT6 Pin

Gate drive voltage connection for external power FET for the sixth LED string.

#### 2.7 **Current Set Pin (CS)**

A resistor from this pin to ground sets the LED string current.

#### 2.8 **Overtemperature Protection Pin** (OTP)

This input is connected to a resistor/NTC-Thermistor combination to reduce the LED current when the temperature becomes too high.

#### 2.9 **BIAS Pin**

This is an input pin that provides voltage to the chip. The BIAS pin is the input to a shunt regulator and must be fed by a current source, not a fixed voltage.

#### 2.10 Active Line Regulation Pin (ALR)

This input pin is connected to an RC network to sense the input main voltage and regulate the LED string current against variations in AC input voltage.

#### 2.11 Ground Terminal (GND)

Reference ground for all input voltages.

## 3.0 FUNCTIONAL DESCRIPTION

### 3.1 Introduction

The CL88030/31 LED driver ICs are designed to drive a long string of inexpensive, low-current LEDs directly from the AC mains. A string of series/parallel LEDs is tapped at four (or six) locations. Linear current regulators sink current at each tap through a single control point and are sequentially turned on and off.

These ICs are targeted to drive a string of LEDs from a nominal utility mains input voltage and provide >2W of output power. It has an internal line regulation circuit to regulate the output power as the line voltage changes from minimum to maximum. It also includes a remote Overtemperature Protection which allows thermal de-rating of the output power using a remote NTC to sense the LED or lamp temperature.

## 3.2 Principle of Operation

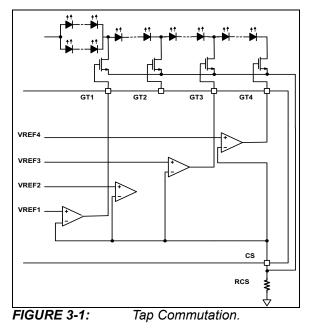

The CL88030 employs a very simple method of implementing single-point control and self-commutation, as shown in Figure 3-1. The single current sense resistor to ground ( $R_{CS}$ ) comprises single-point control. Each tap's error amplifier shares this single control point, although only one err amp is active at any one time.

Each current regulator has its own reference voltage derived from a resistive voltage divider such that:

$$V_{REF4} > V_{REF3} > V_{REF2} > V_{REF1}$$

Initially, V<sub>CS</sub> is at 0V, causing all the current regulators to be turned on but not conducting. Once the rectified AC rises high enough to forward bias the first LED string segment, the first current regulator begins conducting. Eventually it achieves regulation. At this point, V<sub>REF1</sub> and V<sub>CS</sub> are in equilibrium. As the rectified AC continues to rise, the next LED segment becomes forward biased. Since the second regulator's reference voltage (V<sub>REF2</sub>) is higher than V<sub>CS</sub>, the second regulator is already on and begins conducting (although not regulating), injecting current (I<sub>TAP2</sub>) into the single control point and raising the V<sub>CS</sub> voltage. The first regulator responds to the increase in V<sub>CS</sub> by reducing ITAP1 such that V<sub>CS</sub> remains equal to V<sub>REF1</sub>.

**EQUATION 3-1:**

$$I_{TAP1} = \frac{V_{REF1}}{R_{CS}} - I_{TAP2}$$

$I_{TAP1}$  continues to decrease as  $I_{TAP2}$  increases. When the rectified AC rises sufficiently for the second regulator to achieve regulation,  $V_{CS}$  increases to be equal with  $V_{REF2}$ . With  $V_{CS}$  now greater than  $V_{REF1}$ , the first regulator is effectively shut off and the second regulator takes over. This repeats for the other taps and also works in reverse as the rectified AC passes the peak and begins decreasing.

This simple self-commutating mechanism and single-point control automatically sequences the current regulators and assures smooth tap-to-tap transitions.

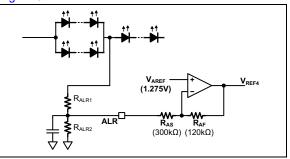

#### 3.2.1 ACTIVE LINE REGULATION (ALR)

Without compensating for line voltage variations, as the AC voltage increases, downstream LED segments become active. In addition, the dwell time at the higher tap currents increases as AC voltage goes up. This causes brightness to increase with AC voltage, resulting in poor line regulation.

The ALR circuit maintains fairly constant output power over variations in AC line voltage. It is not a closed-loop system that directly monitors and corrects output power. Instead, it monitors the voltage applied to the LED string and uses it to adjust the reference voltage provided by the OTP circuit. The circuit used for achieving the active line regulation is shown in Figure 3-2.

FIGURE 3-2: ALR Circuit.

Under normal operation (OTP not activated), the OTP limiting voltage is essentially the reference voltage used to set the tap currents. The ALR circuit adjusts this voltage up or down to compensate for variations in the AC line voltage as represented by the voltage at the ALR pin.

#### **EQUATION 3-2:**

$$V_{REF4} = 1.275V - \left(\frac{V_{ALR} - 1.275V}{300k\Omega} \cdot 120k\Omega\right)$$

The external resistor divider at the ALR pin is usually chosen such that the average voltage at the pin is 1.275V when the nominal voltage of 120  $V_{AC}$  is applied at the input. The ALR divider is connected after the first LED segment to increase its sensitivity to changes in the AC line voltage.

The function of the limiter circuit is threefold. Except during OTP, the limiting voltage is fixed. First, during the initial application of power, the ALR filter capacitor  $(C_{ALR})$  is at 0V. This would result in high LED current until  $C_{ALR}$  charges up. Without a limiter, this would cause a bright flash at turn on. The second purpose of the limiter is during dimming, where the average ALR voltage will be low, causing the LED drive current to be high. This defeats the dimmer and could result in excessive currents. Lastly, during an overtemperature condition, the OTP circuit gradually lowers the limiting voltage from its fixed value. This reduces the power applied to the LEDs, lowering their temperature until an equilibrium is established.

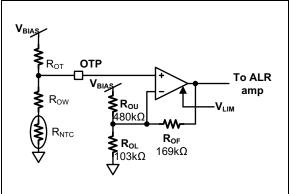

#### 3.2.2 OVERTEMPERATURE PROTECTION (OTP)

OTP uses an inexpensive, external NTC Thermistor to remotely sense LED temperature. The thermistor can be located in close proximity to the LEDs, providing near-direct LED temperature monitoring. The OTP temperature is adjustable via selection of NTC resistance. It is essential that OTP operate linearly, gradually reducing output power as temperature increases. The thermistor is arranged in a full-bridge configuration with the active arm consisting of the NTC and a discrete resistor to V<sub>BIAS</sub> (Figure 3-3). The passive arm consists of internal resistors. The thermistor's resistance versus temperature curve asymptotically approaches  $0\Omega$  as temperature rises. To provide a well-defined window between the threshold temperature and the extinguishing temperature, a small segment of the thermistor's resistance-temperature curve must be used.

#### FIGURE 3-3: OTP Equivalent Circuit.

$R_{OF}$  and the parallel combination of  $R_{OU}$  and  $R_{OL}$  determine OTP gain and set the width of the OTP window — the higher the gain, the narrower the window. Offset is determined by the passive arm of the bridge and sets the location of the OTP window along the temperature axis.

If OTP is unused, the OTP pin should be connected to 5V by making a resistor divider through the BIAS pin.

The output of the OTP amplifier (which is used as a limit for the ALR amplifier) can be expressed as:

#### **EQUATION 3-3:**

| $V_{REF4} = R_{OF} \cdot \left[ V_{OTP} \cdot \left( \frac{1}{R_{OF}} + \frac{1}{R_{OU}} + \frac{1}{R_{OL}} \right) - \frac{V_{BL}}{R_{OL}} \right]$ | $\frac{4S}{U}$ |

|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| $= (2.993 \cdot V_{OTP} - (0.3521 \cdot V_{BIAS}))$                                                                                                  |                |

Note that in Equation 3-3, it is assumed that the input voltage is at the nominal value and there is no adjustment to the reference due to the ALR circuit.

The output of the OTP amplifier is internally clamped to 1.575V, which corresponds to a voltage of 1.77V at the OTP pin. As the voltage at the OTP pin decreases to 1.686V, the output of the OTP amplifier falls to 1.275V. It is at this point, the OTP circuit starts modifying the tap currents and causes thermal derating.

Using two fixed resistors and one NTC, both the breakpoint and the slope of the derating curve can be set independently.

For example, consider a case with a breakpoint of 85°C with a derating curve such that the LED driver is at 20% of full power at 110°C. The NTC Thermistor used is a 470 k $\Omega$ , with a Bvalue of 4500K. The NTC resistance at a given temperature (T<sub>C</sub>, expressed in °C) can be expressed as:

#### **EQUATION 3-4:**

$$R_{NTC, Tc} = R_{NTC, 25C} \cdot e^{-B \cdot \left(\frac{l}{298K} - \frac{l}{Tc + 273}\right)}$$

Using Equation 3-4, the corresponding NTC resistances at 85°C and 110°C are 33.4 k $\Omega$  and 14.2 k $\Omega.$ Using these NTC resistance values,  $R_{OW}$  and  $R_{OT}$  can then be computed assuming 11 volts  $\mathsf{V}_{\mathsf{BIAS}}.$  The final set of values are provided in the Table 3-1.

#### **TABLE 3-1: OVERTEMPERATURE** PROTECTION

| Parameter           | 25°C    | 85°C    | 110°C   |

|---------------------|---------|---------|---------|

| R <sub>OT</sub>     | 511 kΩ  | 511 kΩ  | 511 kΩ  |

| R <sub>OW</sub>     | 57.6 kΩ | 57.6 kΩ | 57.6 kΩ |

| R <sub>NTC</sub>    | 470 kΩ  | 33.4 kΩ | 14.2 kΩ |

| V <sub>OTP</sub>    | 5.580V* | 1.661V  | 1.135V  |

| V <sub>OTPAMP</sub> | 1.575V  | 1.102V  | 0.183V  |

'Refer to Section 3.2.5, APPLICATION NOTES.

#### 3.2.3 **RIPPLE REDUCTION (OPTIONAL)**

Low output ripple is achieved using a capacitor and four diodes. The capacitor may be one or more paralleled ceramic capacitors or a single electrolytic. Multiple ceramic capacitors may be needed due to their poor voltage coefficient. The four diodes may be obtained in a single small package. The LED and rectifier arrangement is shown in Figure 3-4.

With this method, all currents, including ripple capacitor charging and discharging currents, are controlled, passing through the same single control point. This allows the input current wave shape to be maintained and avoids peak charging the ripple reduction capacitor.

FIGURE 3-4:

Ripple Reduction Circuit.

The CL88030/31, with the ripple reduction circuit, operates in four phases: recharge, hold-up, direct and under certain conditions, idle. Note that all active current paths include Segment 1, which assures uninterrupted light output during all phases of operation, excluding the idle phase.

#### Recharge (red path)

Recharging of the ripple capacitor ( $C_{RPL}$ ) occurs when ( $V_{RAC} - V_{SEG1}$ ) >  $V_{CRPL}$ . The maximum voltage that  $C_{RPL}$  can be charged to is:

$V_{CRP(max)} = V_{SEG2} + V_{SEG3} + V_{SEG4}$

The numbers of LEDs for each segment must be chosen carefully so not to exceed  $C_{RPL}$ 's voltage rating while at the same time allowing  $C_{RPL}$  to charge up to a voltage sufficient to drive at least SEG1. To provide continuous light output, the recharge path must include LEDs.

#### Hold-Up (green path)

When the rectified AC falls below  $V_{CRPL}$ , the capacitor takes over, supplying the LEDs. The discharge path flows through  $R_{SET1}$  only. Since this is lesser sense resistance than for the other current paths, the current for the hold-up phase will be higher. This allows for normal currents to be drawn from the AC line to better track the input voltage sine wave while allowing a higher current during the hold-up interval.

#### Direct (purple paths)

When  $V_{CRPL} < V_{RAC} < (V_{CRPL} + V_{SEG1})$ , the LEDs are supplied directly from the AC line. When the direct phase is active, the window is determined by  $V_{SEG1}$ .

#### Idle (no path)

At low AC line voltages, there is not enough voltage to charge  $C_{RPL}$  sufficiently to power Segment 1, and, therefore, strobing will occur. Also, strobing will occur if  $C_{RPL}$  is too small.

## 3.2.4 FET SELECTION

The advantage of external FETs is threefold. First, external FETs allow the LED driver to be scaled in both power and voltage. This allows us to produce one chip that can meet the needs of many different markets. Second, the heat can be spread over multiple devices, allowing for cooler overall operation. Third, without the high real estate used by integrated FETs, nor the high voltage requirements, the die can be made very small. The scalability and a small die result in a low-cost chip that can address a multitude of high-brightness markets.

Common AC line voltages used in lighting are 90VAC, 120VAC, 208VAC, 230VAC, 277VAC, 347VAC and 480VAC. A sequential linear driver can only be designed to handle one of these voltages. No multi-range, universal inputs can be realized.

Lighting induced transients on the AC line complicate the voltage requirements. Depending on where the lamp is used, transient survivability requirements can range from 500V for protected indoor locations up to 10 kV for unprotected outdoor locations. Since high-brightness lamps will be mainly used outdoors, transient survivability requirements will be on the high end of the range. Transient protection can absorb the transients, but there is a rather large gap between the normal peak line voltage and the clamping voltage provided by the protection circuits, which can be hundreds of volts. The low-voltage controller will be powered by a shunt regulator. This avoids any high voltage on the controller, enabling it to be a strictly low-voltage (~11V) chip. Due to the LED voltage drops, each tap has, theoretically, a different voltage requirement, and FET 1 sees higher current than FET 4. However, in practice, one common FET is used to handle all taps. From a BOM perspective, using a common, low-voltage (~11V) FET can keep the overall costs lower and is preferred. For these reasons, a common FET is used for each tap. Light output is estimated at 100 lm/watt.

### 3.2.5 APPLICATION NOTES

To prevent the OTP pin from going too high in voltage at cold temperatures, a 5.1V Zener clamp to GND may be needed.

Because FET gate capacitance can vary considerably, it may be necessary to add a small GTx to GND capacitor for stability.

## 4.0 PACKAGING INFORMATION

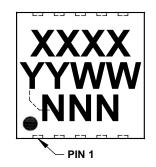

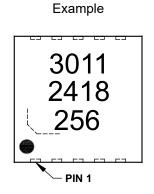

## 4.1 Package Marking Information

10-Lead DFN (3x3x0.9 mm)

| Part Number   | Code |

|---------------|------|

| CL88030T-E/MF | 3011 |

| CL88031T-E/MF | 3111 |

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>(e3)<br>* | Product Code or Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|--------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                                            |                                                                                                                                                                                                                                                                                                                                                                                                             |

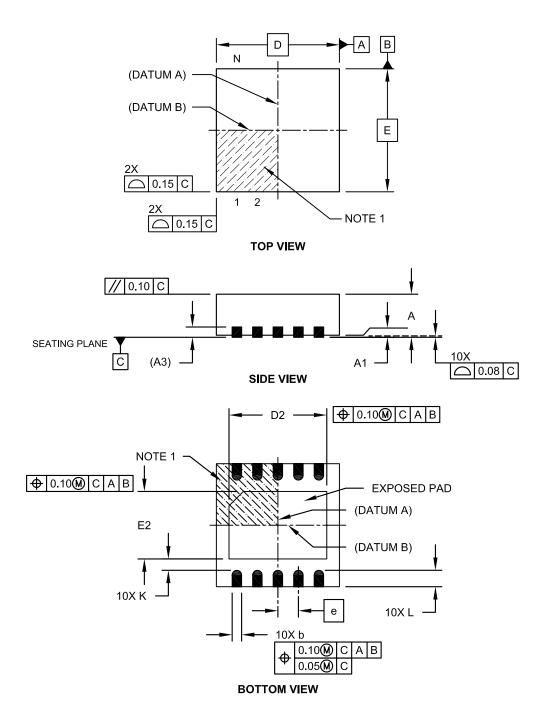

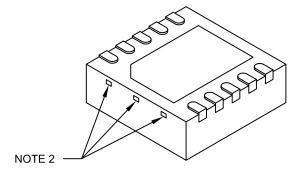

## 10-Lead Plastic Dual Flat, No Lead Package (MF) - 3x3x0.9mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing No. C04-063C Sheet 1 of 2

#### 10-Lead Plastic Dual Flat, No Lead Package (MF) - 3x3x0.9mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | N      | ILLIMETER | S        |      |

|------------------------|--------|-----------|----------|------|

| Dimension              | Limits | MIN       | NOM      | MAX  |

| Number of Pins         | N      |           | 10       | -    |

| Pitch                  | е      |           | 0.50 BSC |      |

| Overall Height         | A      | 0.80      | 0.90     | 1.00 |

| Standoff               | A1     | 0.00      | 0.02     | 0.05 |

| Contact Thickness      | A3     |           | 0.20 REF |      |

| Overall Length         | D      |           | 3.00 BSC |      |

| Exposed Pad Length     | D2     | 2.15      | 2.35     | 2.45 |

| Overall Width          | E      |           | 3.00 BSC |      |

| Exposed Pad Width      | E2     | 1.40      | 1.50     | 1.75 |

| Contact Width          | b      | 0.18      | 0.25     | 0.30 |

| Contact Length         | L      | 0.30      | 0.40     | 0.50 |

| Contact-to-Exposed Pad | K      | 0.20      | -        | -    |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package may have one or more exposed tie bars at ends.

3. Package is saw singulated.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing No. C04-063C Sheet 2 of 2

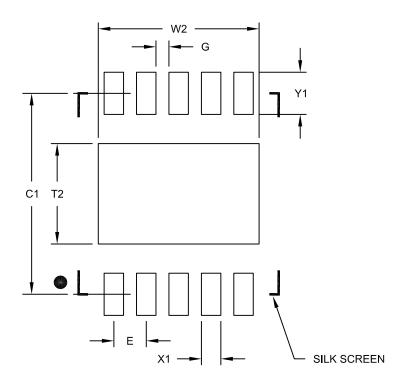

### 10-Lead Plastic Dual Flat, No Lead Package (MF) - 3x3x0.9mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                            | Ν                | <b>ILLIMETER</b> | S        |      |

|----------------------------|------------------|------------------|----------|------|

| Dimensio                   | Dimension Limits |                  |          | MAX  |

| Contact Pitch              | E                |                  | 0.50 BSC |      |

| Optional Center Pad Width  | W2               |                  |          | 2.48 |

| Optional Center Pad Length | T2               |                  |          | 1.55 |

| Contact Pad Spacing        | C1               |                  | 3.10     |      |

| Contact Pad Width (X10)    | X1               |                  |          | 0.30 |

| Contact Pad Length (X10)   | Y1               |                  |          | 0.65 |

| Distance Between Pads      | G                | 0.20             |          |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2063B

## APPENDIX A: REVISION HISTORY

#### Revision B (May 2024)

- Updated the Typical CL88031T Application Circuit and Block Diagram.

- Minor text changes throughout.

## Revision A (July 2018)

• Original Release of this Document.

NOTES:

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.                | <u> ҳ (1) - ҳ - ҳҳ</u>                                                                                 | Examples:                                                                                                                                                                                    |

|-------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device                  | Tape and Temperature Package<br>Reel Range                                                             | a) CL88030T-E/MF: Sequential Linear LED<br>Driver with 4 Taps;<br>Tape and Reel;<br>10LD DFN package                                                                                         |

| Device:                 | CL88030= Sequential Linear LED Driver with 4 Taps<br>CL88031= Sequential Linear LED Driver with 6 Taps | b) CL88031T-E/MF: Sequential Linear LED<br>Driver with 6 Taps;<br>Tape and Reel;<br>10LD DFN package                                                                                         |

| Tape and Reel<br>Option | T = Tape and Reel                                                                                      |                                                                                                                                                                                              |

| Temperature<br>Range    | E = $-40^{\circ}$ C to $+125^{\circ}$ C (Extended)                                                     | Note 1: Tape and Reel identifier only appears in the<br>catalog part number description. This<br>identifier is used for ordering purposes and<br>is not printed on the device package. Check |

| Package:                | MF = Plastic Dual Flat, No Lead Package (DFN),10-lead                                                  | with your Microchip Sales Office for package availability with the Tape and Reel option.                                                                                                     |

NOTES:

#### Note the following details of the code protection feature on Microchip products:

- · Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not

mean that we are guaranteeing the product is "unbreakable" Code protection is constantly evolving. Microchip is committed to

continuously improving the code protection features of our products.

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at https:// www.microchip.com/en-us/support/design-help/client-supportservices.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WAR-RANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDI-RECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSE-QUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### Trademarks

The Microchip name and logo, the Microchip logo, Adaptec, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, TimeCesium, TimeHub, TimePictra, TimeProvider, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, Clockstudio, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, EyeOpen, GridTime, IdealBridge, IGaT, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, IntelliMOS, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, MarginLink, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mSiC, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, Power MOS IV, Power MOS 7, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, Trusted Time, TSHARC, Turing, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

$\ensuremath{\textcircled{\sc 0}}$  2018-2024, Microchip Technology Incorporated and its subsidiaries.

All Rights Reserved.

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality. ISBN: 978-1-6683-4505-4

## **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

China - Beijing Tel: 86-10-8569-7000 China - Chengdu

Tel: 86-28-8665-5511 China - Chongqing Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

China - Nanjing Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

China - Shanghai Tel: 86-21-3326-8000

China - Shenyang Tel: 86-24-2334-2829

China - Shenzhen Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

**China - Wuhan** Tel: 86-27-5980-5300

China - Xian Tel: 86-29-8833-7252

China - Xiamen Tel: 86-592-2388138 China - Zhuhai

Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631 India - Pune

Tel: 91-20-4121-0141 Japan - Osaka

Tel: 81-6-6152-7160

Japan - Tokyo Tel: 81-3-6880- 3770 Korea - Daegu

Tel: 82-53-744-4301 Korea - Seoul

Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

Singapore Tel: 65-6334-8870

Taiwan - Hsin Chu Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

Taiwan - Taipei Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

Tel: 31-416-690399 Fax: 31-416-690340

Italy - Milan

Italy - Padova

EUROPE

Austria - Wels

Tel: 43-7242-2244-39

Tel: 45-4485-5910

Fax: 45-4485-2829

Tel: 358-9-4520-820

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79

Germany - Garching

Tel: 49-2129-3766400

Germany - Heilbronn

Germany - Karlsruhe

Tel: 49-7131-72400

Tel: 49-721-625370

Germany - Munich

Tel: 49-89-627-144-0

Fax: 49-89-627-144-44

Germany - Rosenheim

Israel - Hod Hasharon

Tel: 49-8031-354-560

Tel: 972-9-775-5100

Tel: 39-0331-742611

Fax: 39-0331-466781

Tel: 39-049-7625286

**Netherlands - Drunen**

Tel: 49-8931-9700

Germany - Haan

Finland - Espoo

France - Paris

Fax: 43-7242-2244-393

Denmark - Copenhagen

Norway - Trondheim Tel: 47-7288-4388

Poland - Warsaw Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Gothenberg Tel: 46-31-704-60-40

**Sweden - Stockholm** Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820