## **CIP Hybrid Power Starter Kit User's Guide**

### Preface

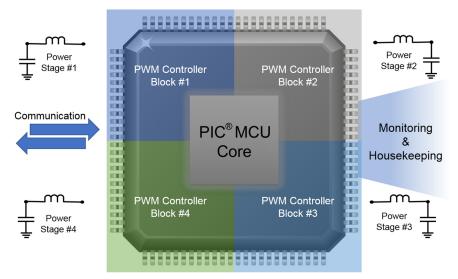

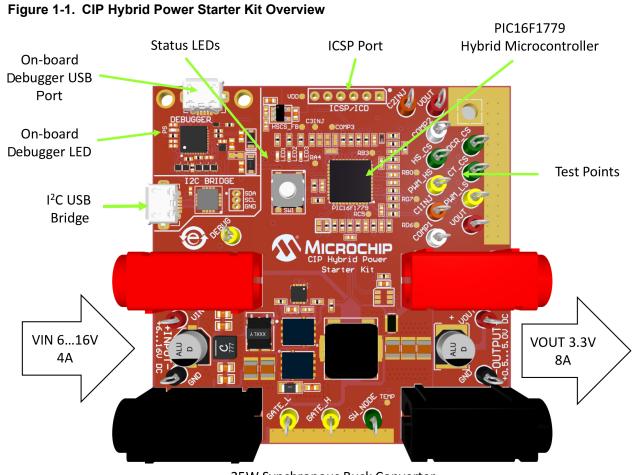

The Core Independent Peripheral (CIP) Hybrid Power Starter Kit is a hardware platform designed to demonstrate the flexibility of Microchip's CIP hybrid power microcontroller as used in a Switched Mode Power Supply (SMPS) application. The board incorporates the PIC16F1779 as the freely programmable Power Management IC (PMIC) device of a synchronous buck converter.

The synchronous buck converter on the board accepts input voltages ranging from 6V to 16V and delivers an output voltage of 3.3V with a maximum load current of 8A. The output of the power supply is rated for maximum 25W.

The CIP Hybrid Power Starter Kit supports three different control modes:

- Voltage Mode Control (VMC)

- Peak Current Mode Control (PCMC)

- · Average Current Mode Control (ACMC) the components are not populated by default

In addition, the synchronous buck converter plant has been equipped with three different current sensing options to allow users to experiment with different Pulse-Width Modulator (PWM) controller feedback configurations:

- Current Sense Transformer

- DC Resistance Sensing

- High-Side Shunt Amplifier the component is not populated by default

The CIP Hybrid Power Starter Kit introduces the PIC16F1779 CIP hybrid power microcontroller. This device incorporates four digitally enhanced analog PWM controller function blocks into a low-power, 8-bit microcontroller architecture allowing users to tailor features and functions to application specific requirements. The PWM controller functional blocks are built in as CIPs, making MCU core activity independent from the PWM controller functional block operation.

The PWM controller blocks can be configured at design time or during run time. This is useful for creating nonlinear operating profiles for applications such as programmable power supplies like USB Power delivery DC/DC converters, multi-loop control systems in battery chargers and LED drivers as well as intelligent PMIC devices for embedded systems supporting proprietary or standardized communication like PMBus<sup>™</sup> protocols.

#### PIC16F1779 CIP Hybrid Power Microcontroller

The CIP Hybrid Power Starter Kit features an on-board debugger that provides access to a serial port interface (serial to USB bridge), which is a mass storage interface for easy 'drag and drop' programming. It allows configuration and full access to the PIC<sup>®</sup> microcontroller In-circuit Serial Programming (ICSP) for programming and debugging using the MPLAB<sup>®</sup> X Integrated Development Environment (IDE) without the need for further hardware development tools to start an evaluation and development process.

The CIP Hybrid Power Starter Kit comes preprogrammed and configured in PCMC utilizing the current sense transformer feedback option for demonstrating the functional operation of the synchronous buck converter. Further code examples and configurations are available for download from the CIP Hybrid Power Starter Kit product webpage.

## **Table of Contents**

| Pre | eface. |                                                                     | 1    |

|-----|--------|---------------------------------------------------------------------|------|

| 1.  | Intro  | duction                                                             | 5    |

|     | 1.1.   | Features                                                            | 5    |

|     | 1.2.   | Kit Overview                                                        | 5    |

| 2.  | Getti  | ng Started                                                          | 8    |

|     | 2.1.   | Connecting the Board to the PC                                      | 8    |

|     | 2.2.   | The USB Programming Interface                                       |      |

|     | 2.3.   | Connecting the Board to the DC Power Supply and Load                | 9    |

|     | 2.4.   | Test Modes                                                          | 9    |

|     | 2.5.   | Design Documentation and Relevant Links                             | 10   |

| 3.  | On-E   | Board Debugger                                                      | 11   |

|     | 3.1.   | Virtual COM Port                                                    | 11   |

|     | 3.2.   | Mass Storage Disk                                                   | 13   |

|     | 3.3.   | On-Board Debugger Implementation                                    | 14   |

| 4.  | Test   | Modes Operation                                                     | . 15 |

|     | 4.1.   | Open Loop (PWM+COG) Mode                                            |      |

|     | 4.2.   | Open Loop with Current Limit (PWM+COG+CMP+PRG+FVR) Mode             |      |

|     | 4.3.   | PCMC Closed Loop Mode                                               |      |

|     | 4.4.   | VMC Closed Loop Mode                                                | 32   |

| 5.  | Hard   | ware Revision History                                               | . 38 |

|     | 5.1.   | Identifying Product ID and Revision                                 | 38   |

|     | 5.2.   | Revision 3                                                          | 38   |

| 6.  | Docu   | iment Revision History                                              | . 39 |

| 7.  | Appe   | endix                                                               | .40  |

|     | 7.1.   | Appendix A: Hardware Components                                     | . 40 |

|     | 7.2.   | Appendix B: PCMC Test Point Measurements                            |      |

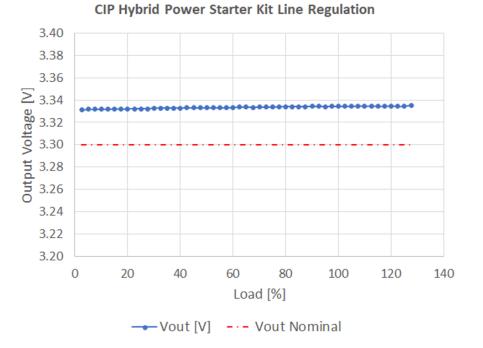

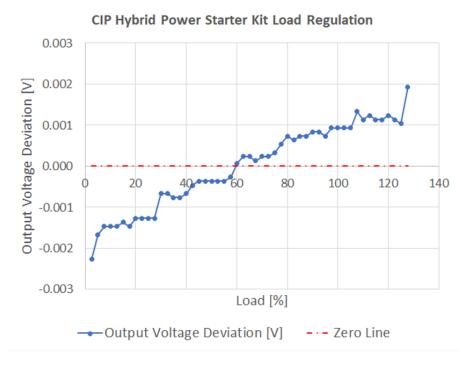

|     | 7.3.   | Appendix C: Efficiency, Line Regulation and Load Regulation in PCMC |      |

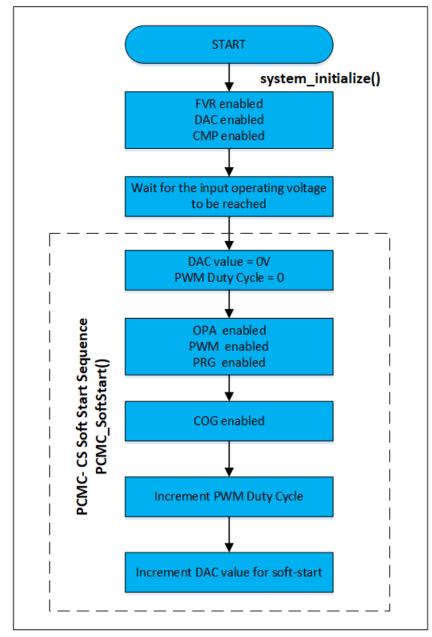

|     | 7.4.   | Appendix D: Firmware Flowchart                                      |      |

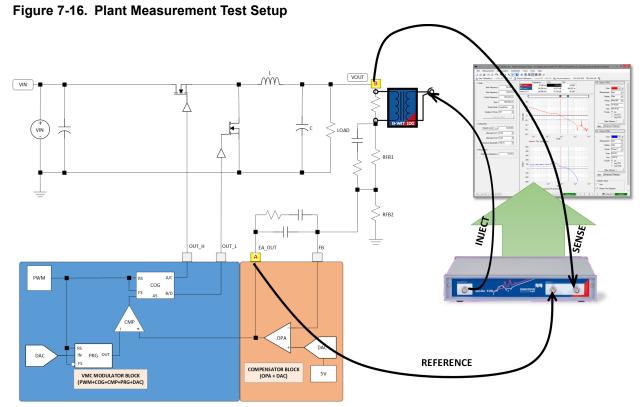

|     | 7.5.   | Appendix E: Bode 100 Gain/Phase Measurement Test Setup              | 47   |

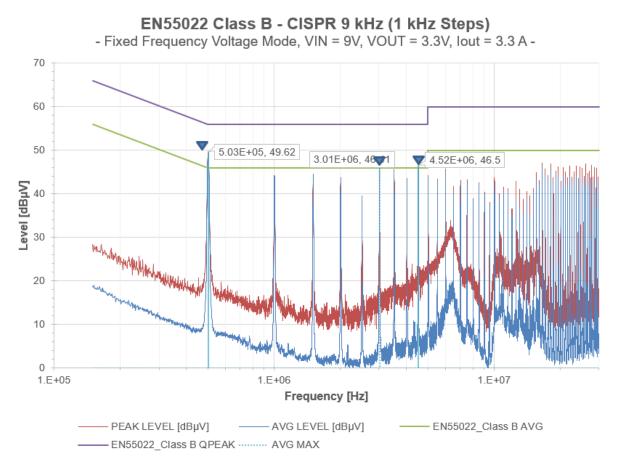

|     | 7.6.   | Appendix F: Pre-Compliance Conducted Noise Measurement              | 49   |

|     | 7.7.   | Appendix G: Power Supply Design Considerations                      | 50   |

|     | 7.8.   | Appendix H: Additional Configuration for Fault Detection            | 53   |

| The | e Micr | ochip Web Site                                                      | . 58 |

| Cu  | stome  | er Change Notification Service                                      | .58  |

| Cu  | stome  | er Support                                                          | . 58 |

| Microchip Devices Code Protection Feature  | .58 |

|--------------------------------------------|-----|

| Legal Notice                               | .59 |

| Trademarks                                 | 59  |

| Quality Management System Certified by DNV | .60 |

| Worldwide Sales and Service                | .61 |

### 1. Introduction

#### 1.1 Features

- PIC16F1779 CIP Hybrid Power Microcontrollers

- One Power on LED and Two Status LEDs

- One Mechanical User Switch

- On-Board Debugger:

- Board identification in MPLAB X IDE

- One green power and status LED

- Programming and debugging

- Virtual COM port (CDC)

- One logic analyzer channel (DGI GPIO)

- I<sup>2</sup>C Bridge Support

- Nominal Operating Conditions:

- Input voltage: +9V DC

- Output voltage: +3.3V

- Max. output current: 8A

- Max. output power: 25W

- Absolute Maximum Ratings:

- Input voltage: +6 to +16V DC

- Output voltage: +0.5 to +5V

- Output current: 8A

- Output power: 30W

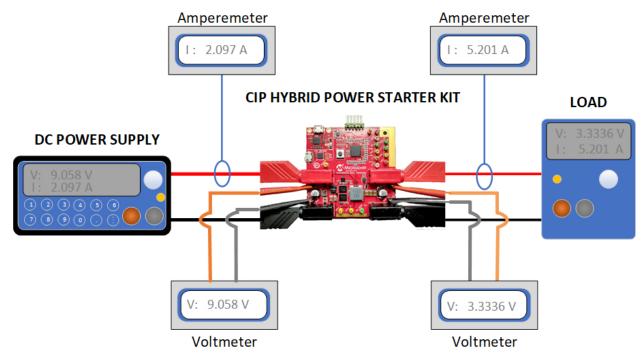

- Efficiency: 94.4% at 65% Load

#### 1.2 Kit Overview

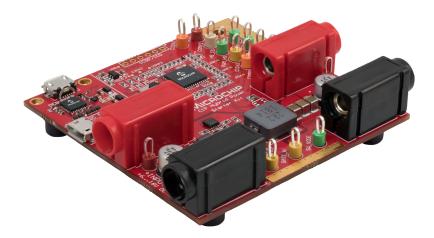

The CIP Hybrid Power Starter Kit is a hardware platform designed to demonstrate the flexibility of the PIC16F1779 hybrid microcontroller as a freely programmable power management device used on a synchronous buck converter.

#### Introduction

25W Synchronous Buck Converter

#### 1.2.1 Test Points

Measurements can be done through the available test points listed below.

#### Table 1-1. Test Points Labels

| Test Point | Description                                                         |

|------------|---------------------------------------------------------------------|

| VIN        | Input Voltage                                                       |

| VOUT       | Output Voltage                                                      |

| GND        | Ground                                                              |

| GATE_L     | MOSFET Driver Low-side gate drive                                   |

| GATE_H     | MOSFET Driver High-side gate drive                                  |

| SW_NODE    | Switch node signal                                                  |

| COMP1      | Type II compensator output for Current mode control                 |

| COMP2      | Type III compensator output for Voltage mode control <sup>(1)</sup> |

| PWM_LS     | PIC16F1779 Low-side PWM signal                                      |

| PWM_HS     | PIC16F1779 High-side PWM signal                                     |

| continued  |                                                                                      |

|------------|--------------------------------------------------------------------------------------|

| Test Point | Description                                                                          |

| C1INJ      | BODE injection for Current mode control                                              |

| C2INJ      | BODE injection for Voltage mode control                                              |

| CT_CS      | Current transformer current sensing                                                  |

| DCR_CS     | Inductor DC resistance current sensing <sup>(2)</sup>                                |

| HS_CS      | High-side shunt current sensing                                                      |

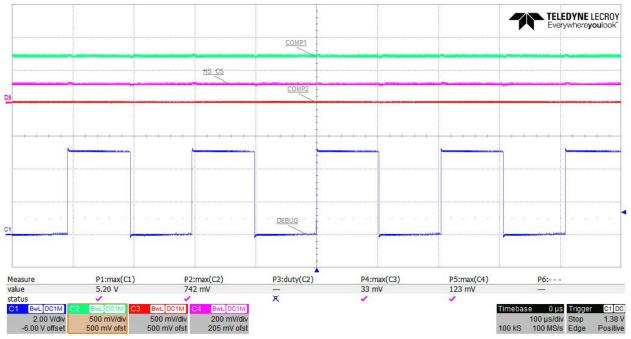

| DEBUG      | Microcontroller debug pin with 5 kHz frequency (100 us on/100 us off) <sup>(3)</sup> |

#### Note:

- 1. Active only when used.

- 2. Active only when configured and enabled by software.

- 3. Active only when driven by software.

#### 1.2.2 LED Indicators

The CIP Hybrid Power Starter Kit features four LEDs with the following functions. The green LED1 indicates that the board has enough power to provide proper 5V bias to the microcontroller. The red LED2 and blue LED3 are test LEDs that indicate the board is operating properly. The function of the LEDs can be modified and programmed by the user to give other status signals that are relevant to the board. By default, when the CIP Hybrid Power Starter Kit is functional, the blue LED3 flashes with 600 ms period (300 ms on, 300 ms off). The red LED2 is controlled by the pushbutton switch. LED2 lights up when the switch is pressed. The green PD LED shows the status of the board during programming.

#### Table 1-2. LED Indicators

| LED Color | Label | System Element Monitored           |

|-----------|-------|------------------------------------|

| Green     | LED1  | Board Power On Indicator           |

| Red       | LED2  | Test Status <sup>(1)</sup>         |

| Blue      | LED3  | Test Status <sup>(1)</sup>         |

| Green     | PS    | On-board debugger Power/<br>Status |

#### Note:

1. Must be enabled by software.

### 2. Getting Started

#### 2.1 Connecting the Board to the PC

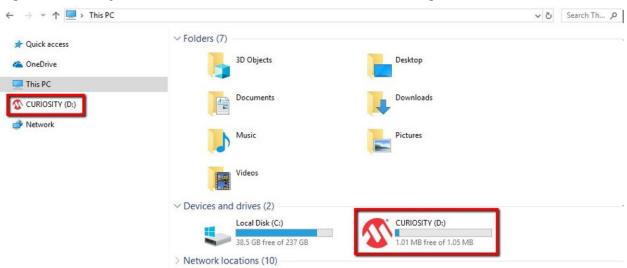

Connect the CIP Hybrid Power Starter Kit to the computer using a standard micro-USB cable. Once plugged in, the LED1 is ON, the LED3 is toggling and the PS is lit up, indicating that the board is receiving power from the USB. The board appears as a removable storage device on the host PC, as shown in the figure below. Double click the CURIOSITY drive to open it and get started.

**Note:** All procedures are the same for Windows<sup>®</sup>, Mac OS<sup>®</sup> and Linux<sup>®</sup> environments.

Figure 2-1. CIP Hybrid Power Starter Kit Board as Removable Storage

The CURIOSITY drive contains the following files:

- AUTORUN.ICO icon file for the Microchip logo.

- AUTORUN.INF system file required for Windows Explorer to show the icon file.

- KIT-INFO.HTM redirects the user to a site containing information about the board.

- KIT-INFO.TXT a text file with details about the board like the serial number.

- STATUS.TXT a text file containing the status condition of the board.

Double click on the KIT-INFO.HTM file to access the CIP Hybrid Power Starter Kit webpage. On this page, the user can quickly see additional example codes to operate the board in other test modes: open loop and closed loop configurations.

#### 2.2 The USB Programming Interface

While the CIP Hybrid Power Starter Kit comes out of the box fully programmed and provisioned, the user can still access the firmware through the USB interface. There are two methods to do it: through drag and drop, or through the on-board programmer/debugger using the MPLAB X IDE starting with version 5.10.

#### 2.2.1 USB Mass Storage (Drag and Drop)

One way to program the device is to drag and drop a hex file into the CURIOSITY drive. The XC8 compiler tool chain generates a hex file for each project it builds. This hex file contains the code of the

project. The USB debugger facilitates putting code into the board by having this drag and drop feature. This feature does not require any USB driver to be installed and works in all major operating system environments. Alternative application example .hex files for the board firmware will be available for download from the Downloads section at the bottom of the CIP Hybrid Power Starter Kit webpage.

#### 2.2.2 USB Programmer/Debugger Interface

The PIC16F1779 microcontroller can also be programmed and debugged directly via the MPLAB X starting with version 5.10. The CIP Hybrid Power Starter Kit is automatically detected by the MPLAB X IDE, enabling full programming and debugging through the on-board debugger interface. The Xplained Window appears and provides relevant information about the CIP Hybrid Power Starter Kit.

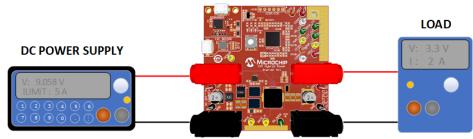

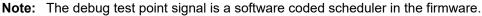

#### 2.3 Connecting the Board to the DC Power Supply and Load

The CIP Hybrid Power Starter Kit comes preprogrammed in the PCMC configuration. The kit can be quickly tested for output voltage regulation. The steps are as follows:

- 1. Connect a DC power supply to the input connector J1 and J2 (observe the polarity). Set the DC supply to 9V and current limit of 5A.

- 2. Attach an electronic load to the output connector J3 and J4 (observe the polarity). Set the electronic load to constant current of 2A.

- 3. Turn on the DC supply; the blue LED is flashing with an interval of 600 ms (300 ms on/300 ms off).

- 4. When the switch is pressed, the red LED turns on; when the switch is released, it turns off.

- 5. Measure voltage at output. A regulated VOUT of 3.3V is present. Figure 2-2. Connecting Board to DC Power Supply and Load

#### **CIP HYBRID POWER STARTER KIT**

#### 2.4 Test Modes

The CIP Hybrid Power Starter Kit has four different test modes. These modes can be programmed to the microcontroller either through drag and drop programming or using the MPLAB X IDE.

| Test Mode                        | Description                                                              |

|----------------------------------|--------------------------------------------------------------------------|

| Open Loop                        | Runs the board in open loop using only PWM and COG peripherals           |

| Open Loop with Current Limit     | Runs the board in open loop using PWM, COG, CMP, PRG and FVR peripherals |

| Peak Current Mode Control (PCMC) | Runs the synchronous buck converter in PCMC closed loop                  |

| Voltage Mode Control (VMC)       | Runs the synchronous buck converter in VMC closed loop                   |

#### 2.5 Design Documentation and Relevant Links

The following list contains links to the most relevant documents and software for the CIP Hybrid Power Starter Kit board. For users accessing the electronic version of this document, the underlined labels are clickable and will redirect to the appropriate website.

- MPLAB X IDE a free IDE to develop applications for Microchip microcontrollers and digital signal controllers.

- MPLAB Code Configurator (MCC) a free, graphical programming environment that generates seamless, easy-to-understand C code to be inserted into the project. Using an intuitive interface, it enables and configures a rich set of peripherals and functions specific to the application.

- MCC SMPS Library an MCC plug-in that allows quick and easy configuration, and code generation for 8-bit PIC SMPS applications. This library contains a set of modules for generic fundamental SMPS building blocks and topologies. These support PIC device families designed for CIP Hybrid Power Controllers.

- MPLAB MINDI<sup>™</sup> Analog Simulator a comprehensive tool for circuit analysis consisting of the SIMPLIS/Simetrix environment and built-in Microchip component libraries for simulation.

- Microchip Sample Store a Microchip sample store where samples of devices can be ordered.

- AN1978 SEPIC LED Driver Demo Board for Automotive Applications a LED Driver design using PIC16F1769.

- AN2122 Flyback SMPS Using a Microcontroller as Control Unit a Flyback Converter design using PIC16F1769.

- AN2455 Operational Amplifier PSpice<sup>®</sup> Model of 8-Bit PIC Microcontrollers a comparative study of the actual PIC16F1769 internal operational amplifier with the PSpice model for simulation.

- AN2456 Configurability in a Switched Mode Power Supply Controller describes the advantages and flexibility of a configurable SMPS microcontroller.

- AN1471 Efficiency Analysis of a Synchronous Buck Converter using Microsoft<sup>®</sup> Office<sup>®</sup> Excel<sup>®</sup>-Based Loss Calculator provides designers of synchronous buck converters with a fast and accurate way to calculate system power losses, as well as overall system efficiency.

- TB3103 Buck Converter Using the PIC16F753 Analog Features describes a synchronous buck power supply based on the PIC16F753 using 100% analog control for output regulation.

- TB3104 Boost Converter Using the PIC16F753 Analog Features describes a boost power supply based on the PIC16F753 using 100% analog control for output regulation.

- TB3155 Multiphase Interleaved PWM Controller with Diode Emulation Using 8-Bit PIC Microcontrollers - outlines a method of realizing a multiphase PWM controller by configuring Microchip's 8-bit PIC microcontrollers.

## 3. On-Board Debugger

The CIP Hybrid Power Starter Kit contains an on-board debugger for programming and debugging. The on-board debugger is a composite USB device of several interfaces: a debugger, a mass storage device, a data gateway, and a Virtual COM port (CDC).

Together with Microchip MPLAB X, the on-board debugger interface can program and debug the PIC16F1779.

A Data Gateway Interface (DGI) is available for use with the logic analyzer channels for code instrumentation, to visualize the program flow. DGI GPIOs can be graphed using the Data Visualizer.

The Virtual COM port is connected to a UART on the PIC16F1779 and provides an easy way to communicate with the target application through terminal software.

The on-board debugger controls one Power and Status LED (marked PS) on the CIP Hybrid Power Starter Kit board. The table below shows how the LED is controlled in different operation modes.

| Operation Mode   | Status LED                                                                                                                     |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Boot Loader mode | LED blink at 1 Hz during power-up.                                                                                             |  |  |  |  |  |

| Power-up         | LED is lit - constant.                                                                                                         |  |  |  |  |  |

| Normal operation | LED is lit - constant.                                                                                                         |  |  |  |  |  |

| Programming      | Activity indicator; the LED flashes slowly during programming/debugging.                                                       |  |  |  |  |  |

| Fault            | The LED flashes fast if a power fault is detected.                                                                             |  |  |  |  |  |

| Sleep/Off        | LED is off. The on-board debugger is either in Sleep mode or powered down.<br>This can occur if the kit is externally powered. |  |  |  |  |  |

Table 3-1. On-board Debugger LED Control

#### 3.1 Virtual COM Port

A general purpose bridge between a host PC and a target device.

#### 3.1.1 Overview

The debugger implements a composite USB device that includes a standard Communications Device Class (CDC) interface, which appears on the host as a Virtual COM Port. The CDC can be used to stream arbitrary data in both directions between the host and the target: the characters sent from the host will appear in the UART form on the CDC TX pin, and the UART characters sent into the CDC RX pin will be sent back to the host.

On Windows machines, the CDC will enumerate as Curiosity Virtual COM Port and appear in the Ports section of the device manager. The COM port number is usually shown here.

**Info:** On older Windows systems, a USB driver is required for CDC. This driver is included in Atmel<sup>®</sup> Studio and MPLAB X installations.

On Linux machines, the CDC will enumerate and appear as  $/{\tt dev}/{\tt ttyACM\#}.$

On MAC machines, the CDC will enumerate and appear as /dev/tty.usbmodem#. Depending on which terminal program is used, it will appear in the available list of modems as usbmodem#.

#### 3.1.2 Limitations

Not all UART features are implemented in the debugger CDC. The constraints are outlined here:

- **Baud rate** must be in the range 1200 bps to 500 kbps. Values outside this range will be capped to these values, without warning. Baud rate can be changed on-the-fly.

- Character format: only 8-bit characters are supported.

- **Parity**: can be odd, even, or none.

- Hardware flow control: not supported.

- Stop bits: one or two bits are supported.

#### 3.1.3 Signaling

During the USB enumeration, the host OS will start both communication and data pipes of the CDC interface. At this point, it is possible to set and read back the baud rate and other UART parameters of the CDC, but data sending and receiving will not be enabled.

When a terminal connects on the host, it must assert the DTR signal. This is a virtual control signal that is implemented on the USB interface, but not in hardware on the debugger. Asserting DTR from the host will indicate to the debugger that a CDC session is active, will enable its level shifters (if available), and will start the CDC data send and receive mechanisms.

Deasserting the DTR signal will not disable the level shifters, but it will disable the receiver, so no further data will be streamed to the host. Data packets that are already queued up for sending to the target will continue to be sent out, but no further data will be accepted.

#### 3.1.4 Advanced Use

#### **CDC Override Mode**

In normal operation, the on-board debugger is a true UART bridge between the host and the device. However, under certain use cases, the debugger can override the Basic Operating mode and use the CDC pins for other purposes.

Dropping a text file (with extension .txt) into the debugger's mass storage drive can be used to send characters out of the CDC TX pin. The text file must start with the characters:

CMD:SEND\_UART=

The maximum message length is 50 characters - all remaining data in the frame are ignored.

The default baud rate used in this mode is 9600 bps, but if the CDC is already active or has been configured, the baud rate last used still applies.

#### **USB-Level Framing Considerations**

**Sending data** from the host to the CDC can be done byte-wise or in blocks, which will be chunked into 64-byte USB frames. Each such frame will be queued up for sending to the CDC TX pin. Sending a small amount of data per frame can be inefficient, particularly at low baud rates, since the debugger buffers frames, not bytes. A maximum of 4 x 64-byte frames can be active at any time, the debugger will throttle the incoming frames accordingly. Sending full 64-byte frames containing data is the most efficient.

When **receiving data** from the target, the debugger will queue up the incoming bytes into 64-byte frames, which are sent to the USB queue for transmission to the host when they are full. Incomplete frames are also pushed to the USB queue at approximately 100 ms intervals, triggered by USB start-of-frame tokens. Up to 8 x 64-byte frames can be active at any time.

If the host, or the software running on it, fails to receive data fast enough, an overrun will occur. When this happens, the last-filled buffer frame will be recycled instead of being sent to the USB queue, and a full frame of data will be lost. To prevent this occurrence, the user must ensure that the CDC data pipe is being read continuously, or the incoming data rate must be reduced.

#### 3.2 Mass Storage Disk

A simple way to program the target device is through drag and drop with .hex files.

#### 3.2.1 Mass Storage Device

The debugger implements a highly optimized variant of the FAT12 file system that has a number of limitations, partly due to the nature of FAT12 itself, and partly due to optimizations made to fulfill its purpose in this development kit.

The CURIOSITY drive is USB Chapter 9 compliant as a mass storage device, but does not in any way fulfill the expectations of a general purpose mass storage device. This behavior is intentional.

The debugger enumerates as a Curiosity Nano USB device that can be found in the disk drives section of the Windows device manager. The CURIOSITY drive appears in the file manager and claims the next available drive letter in the system.

The CURIOSITY drive contains approximately one MB of free space. This does not reflect the size of the target device's Flash in any way. When programming a .hex file, the binary data are encoded in ASCII with metadata providing a large overhead, so one MB is a trivially chosen value for disk size.

It is not possible to format the CURIOSITY drive. When programming a file to the target, the filename may appear in the disk directory listing - this is merely the operating system's view of the directory, which, in reality, has not been updated. It is not possible to read out the file contents. Removing and replugging the kit will return the file system to its original state, but the target will still contain the application that has been previously programmed.

To erase the target device, simply copy a text file starting with "CMD:ERASE" onto the disk.

By default, the CURIOSITY drive contains several read-only files for generating icons as well as reporting status and linking to further information:

- AUTORUN.ICO icon file for the Microchip logo.

- AUTORUN. INF system file required for Windows Explorer to show the icon file.

- KIT-INFO.HTM redirect to the development board website.

- KIT-INFO.TXT a text file containing details about the kit firmware, name, serial number and device.

- STATUS.TXT a text file containing the programming status of the board.

**Info:** When STATUS.TXT is updated by the debugger dynamically, the contents may be cached by the OS and not reflect the correct status.

#### 3.2.2 Configuration Words/Fuse Bytes

#### Configuration Words (PIC<sup>®</sup> MCU Targets)

Configuration Word settings included in the project being programmed after program Flash is programmed. The debugger will *not* mask out any bits in the Configuration Words when writing them, but since it uses Low-Voltage Programming mode, it is unable to clear the LVP Configuration bit. If the incorrect clock source is selected, for example, and the board does not boot, it is always possible to perform a bulk erase (always done before programming) and restore the device to its default settings.

#### 3.3 On-Board Debugger Implementation

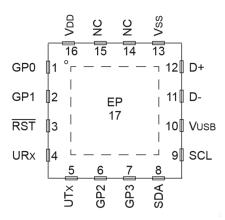

The CIP Hybrid Power Starter Kit implementation of the on-board debugger and the connections to the PIC16F1779 device are shown in the table below.

#### Table 3-2. Debugger Connections

| Debugger Pin | PIC16F1779 Pin | Function   | Shared Functionality            |

|--------------|----------------|------------|---------------------------------|

| DBG0         | RB7            | ICSP Data  | -                               |

| DBG1         | RB6            | ICSP Clock | -                               |

| DBG2         | RA6            | DGI GPIO0  | Debug test point <sup>(1)</sup> |

| DBG3         | RE3            | MCLR       | -                               |

| CDC TX       | RB4            | UART RX    | -                               |

| CDC RX       | RB5            | UART TX    | -                               |

#### Note:

1. Driven by user firmware.

## 4. Test Modes Operation

The CIP Hybrid Power microcontroller is highly configurable and programmable to allow four different modes on the synchronous buck power train. The project files and codes for the different test modes can be found on the CIP Hybrid Power Starter kit landing page. The desired mode of operation can be downloaded to the board directly through drag and drop programming of the .hex file found in the project folder location. Alternatively, MPLAB X IDE and MCC SMPS Library can be used to program and configure the CIP Hybrid Power microcontroller to the desired test mode. Install the latest stable release of the MCC SMPS Library on MCC prior to performing these configurations. The MCC SMPS Library User's Guide explains in detail on how to configure the peripherals.

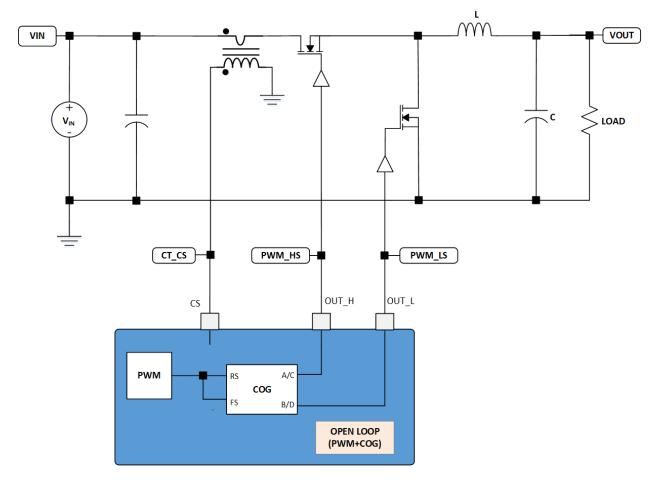

### 4.1 Open Loop (PWM+COG) Mode

This configuration enables the digital PWM module and complementary output control with dead times. The PWM outputs of PIC16F1779 produce a fixed switching frequency of 500 kHz with a fixed duty ratio of ~20%. The signal is fed to the rising and falling source of the Complementary Output Generator (COG) which produces the complementary PWM signals for driving the high-side and low-side switches. The Open Loop mode is very useful during the hardware validation of the power converters to analyze operation and signal integrity under stable conditions. The figure below shows the block diagram of the open loop configuration.

#### Figure 4-1. Open Loop Configuration

#### 4.1.1 MCC SMPS Library Configuration for Open Loop

The following instructions show how to setup the peripherals of the CIP Hybrid Power Starter Kit to be able to operate in Open Loop test mode.

- 1. Open MPLAB X. Connect the CIP Hybrid Power Starter Kit to the computer through an on-board debugger USB port using a conventional micro-USB cable. MPLAB X will detect the CIP Hybrid Power Starter Kit and an Xplained Window appears that provides relevant information about the board.

- 2. Create new Standalone Project in MPLAB X. Select the PIC16F1779 device. Select the CIP Hybrid Starter Kit as programming tool. Name this project "OpenLoop".

| Xplained Window 88                     |             |                                  |

|----------------------------------------|-------------|----------------------------------|

| MCU Boards                             |             | CIP Hybrid Power Starter Kit     |

| 🕜 CIP Hybrid Po                        | New Project |                                  |

| Output - Xplained Ac<br>Xplained Board | -           | Select Tool (Optional)           |

|                                        |             | < Back Next > Finish Cancel Help |

Figure 4-2. Creating New MPLAB X Standalone Embedded Project

- 3. Open MCC. Save the MCC configuration as OpenLoop.mc3.

- 4. Change the internal oscillator clock to 8 MHz from the System Module in the Project Resources area. On the Pin Manager, change the package to QFN44.

#### **Test Modes Operation**

| Figure 4-3. S                   | system                                     | n Mod   | ule \$ | Settings                         |                                                              |       |               |          |        |      |       |      |      |      |      |      |      |      |     |

|---------------------------------|--------------------------------------------|---------|--------|----------------------------------|--------------------------------------------------------------|-------|---------------|----------|--------|------|-------|------|------|------|------|------|------|------|-----|

| Projects Files                  | Res                                        | ou ×    | =      | Start Page :                     | Start Page × Pin Module × Interrupt Module × System Module × |       |               |          |        |      |       |      |      |      |      |      |      |      |     |

| Project Reso Ge I System Module |                                            |         |        |                                  |                                                              |       |               |          |        |      |       |      |      |      |      |      |      |      |     |

| <ul> <li>System</li> </ul>      | ▼ System                                   |         |        |                                  |                                                              |       |               |          |        |      |       |      |      |      |      |      |      |      |     |

| Interrupt N                     | /lodule                                    |         |        | ිදි Easy S                       | etup 📃 🗄 R                                                   | egist | ers           |          |        |      |       |      |      |      |      |      |      |      |     |

| Pin Modul                       | e                                          |         |        | ▼ INTERN                         | NAL OSCILL                                                   | ATOF  | ۲             |          |        |      |       |      |      |      |      |      |      |      |     |

| System Mo                       | odule                                      |         |        | Current S                        | system cloc                                                  | k 32  | MHz (4x PLI   | _)       |        |      |       |      |      |      |      |      |      |      |     |

| <ul> <li>SMPS Power</li> </ul>  | <ul> <li>SMPS Power Controllers</li> </ul> |         |        | Oscillato                        | r Select                                                     | IN    | NTOSC oscilla | ator     | : 1/0  | fur  | nctio | n or | n CL | .KIN | pin  | 1    |      |      |     |

| CIP Blocks                      | CIP Blocks                                 |         |        | System C                         | lock Select                                                  | F     | OSC           |          |        | *    | ]     |      |      |      |      |      |      |      |     |

|                                 |                                            |         |        | Internal (                       | Clock                                                        | 8     | MHz_HF        |          |        | •    | C     | ) -  | PLL  | Cap  | babl | e Fr | eque | ency | ,   |

| Device Resour                   | ces                                        | 0       | -      | External Clock 1 MHz             |                                                              |       |               |          |        |      |       |      |      |      |      |      |      |      |     |

| ▼ Documents                     |                                            |         | Â      | PLL Enabled Software PLL Enabled |                                                              |       |               |          |        |      |       |      |      |      |      |      |      |      |     |

| PIC16F177                       | 9 Produ                                    | ct Page |        |                                  |                                                              |       |               |          |        |      |       |      |      |      |      |      |      |      |     |

| ▼ Peripherals                   |                                            |         | U      | Output - M                       | PLAB® Cod                                                    | e Con | figurator     | No       | otific | atio | ons [ | мсс  | ]    | Pi   | n M  | ana  | ger: | Grid | Vie |

| ADC                             |                                            |         |        | Package:                         | QFN44                                                        | •     | Pin No:       | 19       | 20     | 21   | 22    | 23   | 24   | 33   | 32   | 9    | 10   | 11   | 12  |

|                                 | ► <sup>«∿</sup> " CCP                      |         |        |                                  |                                                              |       |               | Port A ▼ |        |      |       |      |      | F    | Por  |      |      |      |     |

| <ul> <li>CLC</li> </ul>         |                                            |         |        | Module                           | Funct                                                        | tion  | Direction     | 0        | 1      | 2    | 3     | 4    | 5    | 6    | 7    | 0    | 1    | 2    | 3   |

|                                 |                                            |         |        | OSC                              | CLKOU                                                        | T     | output        |          |        |      |       |      |      | î    |      |      |      |      |     |

| 🕨 🗠 COG                         | ► 🐣 COG                                    |         |        |                                  | GPIO                                                         |       | input         | î.       | î.     | î.   | î.    | î.   | î.   | î.   | î.   | î.   | î.   | î.   | î.  |

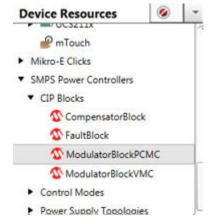

5. Go to the Device Resources area, click **SMPS Power Controllers** and expand **CIP Blocks**, double click on **ModulatorBlockPCMC**. This action will move the selected module to the Project Resources area.

Figure 4-4. ModulatorBlockPCMC

6. In the Project Resources area, click the **ModulatorBlockPCMC**. On the **Configuration** tab, under Hardware Settings, select Half-Bridge mode. Change the switching frequency to 500 kHz, and the duty cycle to 20%. Check **Standalone Open Loop PWM**.

## CIP Hybrid Power Starter Kit Test Modes Operation

#### Figure 4-5. Hardware Settings for Open Loop

#### ModulatorBlockPCMC

| 🕼 Easy Setup                                        |                     |           |  |  |  |  |  |  |  |

|-----------------------------------------------------|---------------------|-----------|--|--|--|--|--|--|--|

| Information                                         | Configuration       | Schematic |  |  |  |  |  |  |  |

| Hardware Settings                                   |                     |           |  |  |  |  |  |  |  |

| Mode: Half-                                         | Mode: Half-Bridge 💌 |           |  |  |  |  |  |  |  |

| Switching Frequency: $31.25 \le 500 \le 8000.0$ kHz |                     |           |  |  |  |  |  |  |  |

| Max. Duty Cycle: 0 ≤ 20 ≤ 100 %                     |                     |           |  |  |  |  |  |  |  |

| ✓ Standalone Open Loop PWM                          |                     |           |  |  |  |  |  |  |  |

7. Under the Complementary Output Generator Settings, change rising dead time to 15 ns, falling dead time to 60 ns, and blanking time to 250 ns.

#### Figure 4-6. Complementary Output Generator Settings for Open Loop

| Complementary Output Generator Settings: |     |          |    |                |    |          |  |  |  |

|------------------------------------------|-----|----------|----|----------------|----|----------|--|--|--|

| Rising:                                  |     |          |    | Falling:       |    |          |  |  |  |

| Dead Time: 0 ≤                           | 15  | ≤ 315    | ns | Dead Time: 0 ≤ | 60 | ≤ 315 ns |  |  |  |

| Blanking: 0 ≤                            | 250 | ≤1968.75 | ns |                |    |          |  |  |  |

|                                          |     |          |    |                |    |          |  |  |  |

8. Select COG4 and PWM11 in the Sub-Module Selection and click the **Upload** button. Check if COG4 and PWM11 have been correctly added to the Project Resources area.

#### Figure 4-7. Sub-Module Selection for Open Loop

| ▼ Sub-Module Selection |            |        |

|------------------------|------------|--------|

| Upload Submodules      | Upload All |        |

| Select PRG             | PRG1 -     | Upload |

| Select CMP (SW)        | CMP1 👻     | Upload |

| Select COG             | COG4 👻     | Upload |

| Select PWM             | PWM11 -    | Upload |

| Select DAC (5-bit)     | DAC3 👻     | Upload |

| Select CMP (FAULT)     | CMP1 -     | Upload |

| Upload FVR             | FVR 👻      | Upload |

9. Go to the Pin Manager: Grid View. Search for the Modulator section. Select RD5 as the output pin for signal OUT\_H and RD4 as the output pin for signal OUT\_L.

#### **Test Modes Operation**

| Package:      | QFN44 👻  | Pin No:   | 19 | 20 | 21 | 22  | 23    | 24 | 33 | 32 | 9 | 10 | 11 | 12  | 14 | 15 | 16 | 17 | 34 | 35 | 36 | 37   | 42    | 43 | 44 | 1 | 38 | 39 | 40 | 41   | 2  | 3  | 4 | 5 | 25 | 26   | 27 |

|---------------|----------|-----------|----|----|----|-----|-------|----|----|----|---|----|----|-----|----|----|----|----|----|----|----|------|-------|----|----|---|----|----|----|------|----|----|---|---|----|------|----|

|               | -        |           |    |    |    | Por | t A ' | •  |    |    |   |    |    | Por | B  | 7  |    |    |    |    | F  | Port | t C Y | •  |    |   |    |    |    | Port | D  |    |   |   |    | Port | E▼ |

| Module        | Function | Direction | 0  | 1  | 2  | 3   | 4     | 5  | 6  | 7  | 0 | 1  | 2  | 3   | 4  | 5  | 6  | 7  | 0  | 1  | 2  | 3    | 4     | 5  | 6  | 7 | 0  | 1  | 2  | 3    | 4  | 5  | 6 | 7 | 0  | 1    | 2  |

|               | COG4A    | output    |    |    |    |     |       |    |    |    | î | î  | î. | î.  | î. | î. | î. | î  | î. | î  | î  | î    | î     | î. | î  | î |    |    |    |      |    |    |   |   |    |      |    |

|               | COG4B    | output    | î. | î  | î. | î   | î     | î  | î  | î  |   |    |    |     |    |    |    |    |    |    |    |      |       |    |    |   |    |    |    |      |    |    |   |   | î  | î    | î. |

| COG4 🔻        | COG4C    | output    | î. | î  | î. | î   | î     | î  | î  | î  |   |    |    |     |    |    |    |    |    |    |    |      |       |    |    |   | î. | î  | î  | î.   | î  | q, | î | î |    |      |    |

|               | COG4D    | output    | î. | î. | î. | î   | î     | î  | î  | î  |   |    |    |     |    |    |    |    |    |    |    |      |       |    |    |   | î. | î  | î. | î.   | ą, | î  | î | î |    |      |    |

|               | COG4IN   | input     |    |    |    |     |       |    |    |    | î | î  | î  | î.  | î. | î. | î. | î  |    |    |    |      |       |    |    |   | î  | î  | î  | î    | î  | î  | î | î |    |      |    |

|               | OUT_H    | output    | î. | î  | î  | î   | î     | î  | î  | î  | î | î  | î. | î.  | î. | î  | î  | î  | î. | î  | î  | î    | î     | î  | î  | î | î  | î  | î  | î    | î. | q. | î | î |    |      |    |

| AodulatorBlo. | OUT_L    | output    | î  | î. | î  | î   | î     | î  | î  | î  |   |    |    |     |    |    |    |    |    |    |    |      |       |    |    |   | î  | î. | î  | î    | q_ | î  | î | î | î  | î    | î  |

| OSC           | CLKOUT   | output    |    |    |    |     |       |    | î  |    |   |    |    |     |    |    |    |    |    |    |    |      |       |    |    |   |    |    |    |      |    |    |   |   |    |      |    |

| PWM11         | PWM110UT | output    |    |    |    |     |       |    |    |    | î | î  | î  | î.  | î. | î. | î  | î  |    |    |    |      |       |    |    |   | î  | î  | î  | î    | î  | î  | ĥ | î |    |      |    |

|               | CDIO     | innut     | 2  | 0  | 0  | 0   | 2     | 0  | 0  | 0  | 0 | 2  | 0  | 2   | 0  | 0  | 0  | 2  | 2  | •  | 0  | •    | 0     | 0  | 0  | 0 | 0  | 0  | 0  | 0    | 0  | 0  | • | • | •  | 0    |    |

- 10. Click the Generate button from Project Resources area to generate the code.

- 11. Program the PIC16F1779 device on the CIP Hybrid Power Starter Kit by clicking the "Make and Program Device Main Project" icon.

#### Figure 4-9. Generating Code Button and Programming

X MPLAB X IDE v5.10.05 - OpenLoop : default

| File Edit View Navigate Source Refactor Production Debug Team | Tools Window Help         |                                                                  |

|---------------------------------------------------------------|---------------------------|------------------------------------------------------------------|

| 😷 🞦 😫 🦻 🍘 🕼 default 💷 🍸                                       |                           | • 🙀 🏗 • 🚾 PC: 0x0 z dc c : W:0x0 : bank 0 🛒 🚅 How                |

| Projects Files Resource Management [MCC] ×                    | Xplained Window Make and  | Program Device Main Project em Module × Interrupt Module × PWM11 |

| Project Resources Generate Import Export                      | System Module             |                                                                  |

| ▼ System                                                      | 🛱 Easy Setup 🗏 Ree        | gisters                                                          |

| Interrupt Module                                              |                           | gisters                                                          |

| Pin Module                                                    | VINTERNAL OSCILLA         | TOR                                                              |

| System Module                                                 | Current System clock      | 32 MHz (4x PLL)                                                  |

| <ul> <li>SMPS Power Controllers</li> </ul>                    | Oscillator Select         | INTOSC oscillator: I/O function on CLKIN pin                     |

| ▼ CIP Blocks                                                  |                           |                                                                  |

|                                                               | System Clock Select       | FOSC                                                             |

| ▼ Peripherals                                                 | Internal Clock            | 8MHz_HF                                                          |

| M PWM11 [SMPS Power Library by Microchip Te                   |                           |                                                                  |

| COG4 [SMPS Power Library by Microchip Tech                    | External Clock            | 1 MHz                                                            |

|                                                               | ✓ PLL Enabled             | Software PLL Enabled                                             |

|                                                               |                           |                                                                  |

| Device Resources                                              |                           | · · · · · · · · · · · · · · · · · · ·                            |

| ▼ Documents                                                   | Output × Notifications [M | CC] Pin Manager: Grid View                                       |

12. Alternatively, the user can also download the Open Loop firmware to the CIP Hybrid Power Starter Kit by dragging the generated .hex file of the project to the CURIOSITY drive. The .hex file is located on the --dist\default\production folder.

**Test Modes Operation**

| 📙 🛛 🔁 = 🕴 production                                                                                           | n                                                                                                                                                                   |                                       | - 🗆 X                                 |

|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------|

| File Home Share                                                                                                | View                                                                                                                                                                |                                       | ~ 🕐                                   |

| $\leftarrow \rightarrow \checkmark \uparrow \square \ll M$                                                     | PLABXProjects > OpenLoop.X > dist >                                                                                                                                 | › default › produ                     | ction V 🖸 Search producti 🔎           |

| <ul> <li>Box Sync</li> <li>OneDrive - Mide</li> <li>This PC</li> <li>CURIOSITY (D)</li> <li>Network</li> </ul> | Name  memoryfile.xml  OpenLoop.X.production.cmf  OpenLoop.X.production.elf  OpenLoop.X.production.hex  OpenLoop.X.production.hxl  py to CURIOSITY (D:) pduction.lst | [^<br>1<br>1<br>1<br>1<br>1<br>1<br>× | OpenLoop.X.production.hex<br>HEX File |

| 12 items 1 item selected                                                                                       | 997 bytes                                                                                                                                                           |                                       |                                       |

#### Figure 4-10. Drag and Drop Method for Programming the Device

13. The CIP Hybrid Power Starter Kit can now be tested for Open Loop operation and will immediately start to generate the PWM output signals driving the synchronous buck converter.

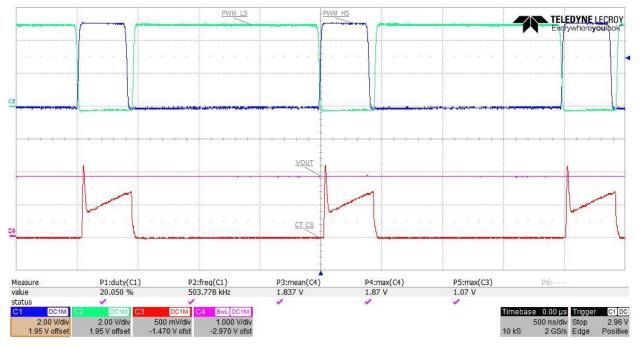

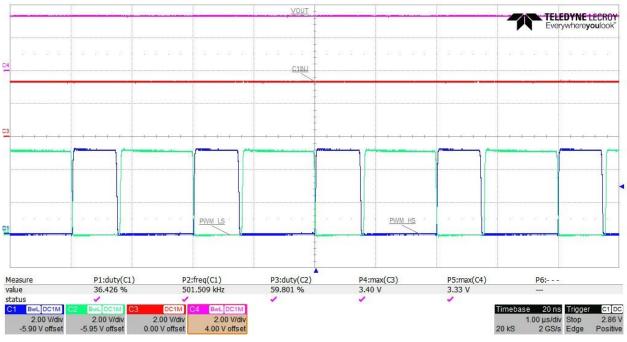

#### 4.1.2 Open Loop Test

Below are the steps for testing the Open Loop operation of the CIP Hybrid Power Starter Kit.

- 1. Remove programming interface. Place CH1 oscilloscope probe to PWM\_HS test point, CH2 oscilloscope probe to PWM\_LS test point, CH3 oscilloscope probe to CT\_CS test point, and CH4 oscilloscope probe to VOUT test point.

- 2. Connect DC supply (set to 9V) and LOAD (set to 2A). Power-up the board. PWM\_HS, PWM\_LS and CT\_CS signals and VOUT can be monitored.

- 3. Increasing VIN will increase VOUT following the equation VOUT = [duty ratio] \* VIN.

#### Figure 4-11. PWM\_HS, PWM\_LS and CT\_CS Signals and VOUT Measurement

#### 4.2 Open Loop with Current Limit (PWM+COG+CMP+PRG+FVR) Mode

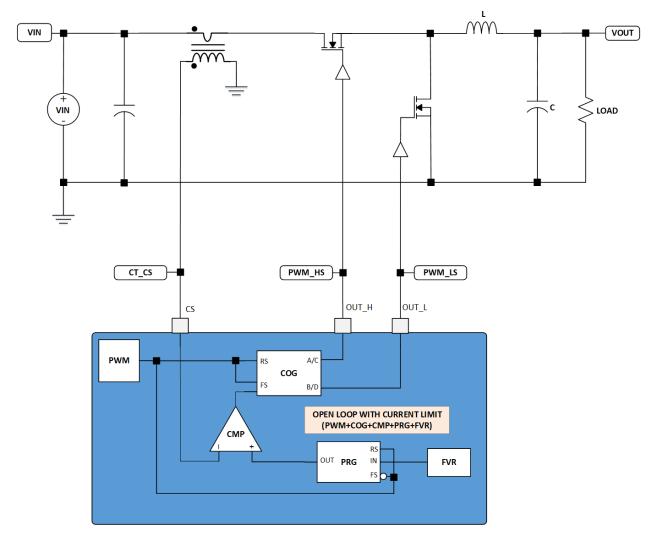

The current limit is simulated by adding another falling source to the COG module. This falling source is derived from the comparator CMP output. The CMP controls the duty cycle by comparing the input current sense signal from the current transformer to a reference level set by the fixed voltage reference (FVR). The reference signal is slope-compensated before being fed to the comparator by adding a negative ramp to the FVR using the Programmable Ramp Generator (PRG). The figure below shows the block diagram of the open loop configuration.

#### 4.2.1 MCC SMPS Library Configuration for Open Loop with Current Limit

The following instructions show how to setup the peripherals of the CIP Hybrid Power Starter Kit to be able to operate in Open Loop with Current Limit test mode.

1. Open MPLAB X. Connect the CIP Hybrid Power Starter Kit to the computer through an on-board debugger USB port using a conventional micro-USB cable. MPLAB X will detect the CIP Hybrid Power Starter Kit and an Xplained Window appears that provides relevant information about the board.

- 2. Create new Standalone Project in MPLAB X. Select the PIC16F1779 device. Select the CIP Hybrid Starter Kit as programming tool. Name this project "OpenLoopCurrentLimit".

- 3. Open MCC. Save the MCC configuration as OpenLoopCurrentLimit.mc3.

- 4. In the Project Resources area, change the internal oscillator clock to 8 MHz from the System Module. On the Pin Manager, change the package to QFN44.

- 5. Go to the Device Resources area, click **SMPS Power Controllers** and expand **CIP Blocks**, double click on **ModulatorBlockPCMC**. This action will move the selected module to the Project Resources area.

- 6. In the Project Resources area, click the **ModulatorBlockPCMC**. Go to the **Configuration** tab, under Hardware Settings, change the switching frequency to 500 kHz, and the duty cycle to 50%. Uncheck **Standalone Open Loop PWM**.

| Start Page ×  | 🖭 main.c 🛛 × | Pin Module > | System | Module | ×   | Interrupt Mo | odule | × |

|---------------|--------------|--------------|--------|--------|-----|--------------|-------|---|

| ModulatorBloc | ckPCMC       |              |        |        |     |              |       |   |

| 🕸 Easy Setu   | up           |              |        |        |     |              |       |   |

| Hardware S    | Settings     |              |        |        |     |              |       |   |

| Mode: Hal     | lf-Bridge    | •            |        |        |     |              |       |   |

| Switching Fr  | requency:    | 31.2         | 25 ≤   | 500    | ≤ 8 | 8000.0kHz    |       |   |

| Max. Duty C   | Cycle:       |              | 0 ≤    | 50     | ≤ ' | 100 %        |       |   |

| Standa        | lone Open L  | oop PWM      |        |        |     |              |       |   |

Figure 4-13. Hardware Settings for Open Loop with Current Limit

7. Under the Ramp Generator Settings, add slope compensation ramp of 2 V/us and use FVR\_buffer2 as the DC offset.

Figure 4-14. Ramp Generator Settings for Open Loop with Current Limit

| Ramp Generator Settings:       |             |   |   |  |

|--------------------------------|-------------|---|---|--|

| Slope Compensation Ramp Slope: | 2.00 V/us   | * |   |  |

| Voltage Input Source:          | FVR_buffer2 |   | • |  |

8. Under the Comparator Settings, select PRG3 as the positive input of the comparator. **Figure 4-15. Comparator Settings for Open Loop with Current Limit**

| Comparator Settings:         |       |   |

|------------------------------|-------|---|

| Enable Comparator Hysteresis |       |   |

| Positive Input:              | PRG3  | - |

| Negative Input:              | CIN2- | - |

| Invert Output Polarity       |       |   |

9. Under the Complementary Output Generator Settings, change rising dead time to 15 ns, falling dead time to 60 ns, and blanking time to 250 ns.

#### Figure 4-16. Complementary Output Generator Settings for Open Loop with Current Limit

| Complementa | ary O | utput Ge | nerator Se | tting | S:                  |    |          |

|-------------|-------|----------|------------|-------|---------------------|----|----------|

| Rising:     |       |          |            |       | Falling:            |    |          |

| Dead Time:  | 0 ≤   | 15       | ≤ 315      | ns    | Dead Time: $0 \leq$ | 60 | ≤ 315 ns |

| Blanking: 0 | ) ≤   | 250      | ≤1968.75   | ns    |                     |    |          |

|             |       |          |            |       |                     |    |          |

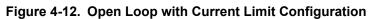

Select PRG3, CMP8, COG4, PWM11 and FVR on the Sub-Module Selection and Upload All button. Check if all the peripherals have been correctly added to the Project Resources area.

Figure 4-17. Sub-Module Selection for Open Loop with Current Limit

11. Go to Pin Manager: Grid View. Select RD5 as output pin for signal OUT\_H, RD4 as output pin for signal OUT\_L and RD3 as input pin for feedback signal CS.

Figure 4-18. Pin Manager Selection for Open Loop with Current Limit

| Dutput     | Notification | s Notifi  | cat | ion | s [I | MC( | []       | P | Pin | Ma | nag | jer: | G  | rid \ | /iev | N× |    |    |    |    |    |     |   |   |   |   |          |    |    |    |    |    |    |    |           |  |  |

|------------|--------------|-----------|-----|-----|------|-----|----------|---|-----|----|-----|------|----|-------|------|----|----|----|----|----|----|-----|---|---|---|---|----------|----|----|----|----|----|----|----|-----------|--|--|

|            |              |           |     |     | P    | ort | <b>A</b> | ▼ |     |    |     |      | I  | Por   | t B  | ▼  |    |    |    |    | P  | ort | C | ▼ |   |   | Port D ▼ |    |    |    |    |    |    |    |           |  |  |

| Module     | Function     | Direction | 0   | 1   | 2    | 3   | 4        | 5 | 6   | 7  | 0   | 1    | 2  | 3     | 4    | 5  | 6  | 7  | 0  | 1  | 2  | 3   | 4 | 5 | 6 | 7 | 0        | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 0         |  |  |

|            | COG4A        | output    |     |     |      |     |          |   |     |    | î   | î    | î  | î     | î    | î  | î  | î  | î  | î  | î  | î   | î | î | î | î |          |    |    |    |    |    |    |    | $\square$ |  |  |

|            | COG4B        | output    | î   | ĵ,  | Ъ    | Ъ   | ì        | ì | î.  | Ъ  |     |      |    |       |      |    |    |    |    |    |    |     |   |   |   |   |          |    |    |    |    |    |    |    | în (      |  |  |

| COG4 ▼     | COG4C        | output    | ì   | î.  | î.   | Ъ   | Ъ        | Ъ | î.  | ì  |     |      |    |       |      |    |    |    |    |    |    |     |   |   |   |   | ĵ,       | Ъ  | ĵ, | Ъ  | î. | q, | î. | î. |           |  |  |

|            | COG4D        | output    | î   | î   | î    | ĥ   | ĵ,       | î | î   | î  |     |      |    |       |      |    |    |    |    |    |    |     |   |   |   |   | î        | ĵ, | ĵ. | ĵ, | q, | î  | î  | î  |           |  |  |

|            | COG4IN       | input     |     |     |      |     |          |   |     |    | î   | î    | î, | î.    | î    | î  | î  | î  |    |    |    |     |   |   |   |   | î        | î. | ì  | î. | î  | î. | î  | î  | $\square$ |  |  |

|            | CS           | input     | î.  |     |      |     |          |   |     |    |     |      |    |       |      |    |    |    |    |    |    |     |   |   | Ъ |   |          | ì  |    | q, |    | î. |    |    |           |  |  |

| 1odulator. | . OUT_H      | output    | î.  | î.  | î.   | î.  | î.       | ì | ì   | ì  | ì   | ì    | ì  | î.    | ì    | î  | î. | î. | î. | î. | î. | ì   | ì | ì | ì | ì | î.       | î. | î. | î. | î. | q, | 1  | î. |           |  |  |

|            | OUT_L        | output    | î   | î   | î    | î   | î        | î | î   | î  |     |      |    |       |      |    |    |    |    |    |    |     |   |   |   |   | î        | î  | ì  | î  | ą, | î  | 1  | î  | ì         |  |  |

| OSC        | CLKOUT       | output    |     |     |      |     |          |   | ì   |    |     |      |    |       |      |    |    |    |    |    |    |     |   |   |   |   |          |    |    |    |    |    |    |    |           |  |  |

- 12. Click **Generate** button to generate the code. Program the PIC16F1779 device on the CIP Hybrid Power Starter Kit by clicking the "Make and Program Device Main Project" icon.

- 13. Alternatively, the user can also download the Open Loop firmware to the CIP Hybrid Power Starter Kit by dragging the generated .hex file of the project to the CURIOSITY drive. The .hex file is located on the --dist\default\production folder.

14. The CIP Hybrid Power Starter Kit can now be tested for Open Loop with Current Limit operation and will immediately start to generate the PWM output signals driving the synchronous buck converter.

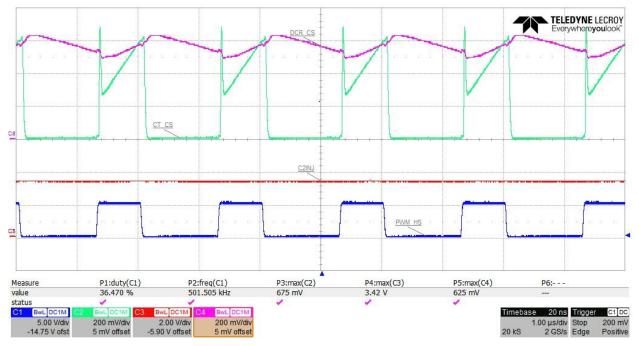

#### 4.2.2 Open Loop with Current Limit Test

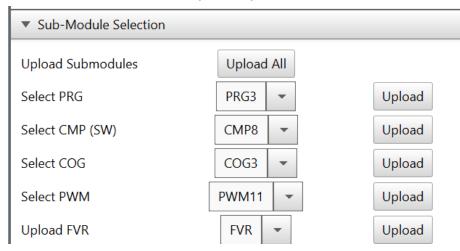

Below are the steps for testing the Open Loop with Current Limit operation of the CIP Hybrid Power Starter Kit.

- 1. Remove programming interface. Place CH1 oscilloscope probe to PWM\_HS test point, CH2 oscilloscope probe to PWM\_LS test point, CH3 oscilloscope probe to CT\_CS test point, and CH4 oscilloscope probe to VOUT test point.

- 2. Connect DC supply (set to 6V) and LOAD (set to 2A). Power-up the board. PWM\_HS, PWM\_LS and CT\_CS signals and VOUT can be monitored.

- 3. Increasing VIN increases VOUT, but duty cycle is decreases because the CT\_CS signal is touching the PRG signal at the defined slope.

Figure 4-19. PRG Effect on CT\_CS Signal and PWM Duty Cycle

4. Increasing the load will decrease VOUT, since the duty cycle is being limited by the CT\_CS signal touching the PRG signal.

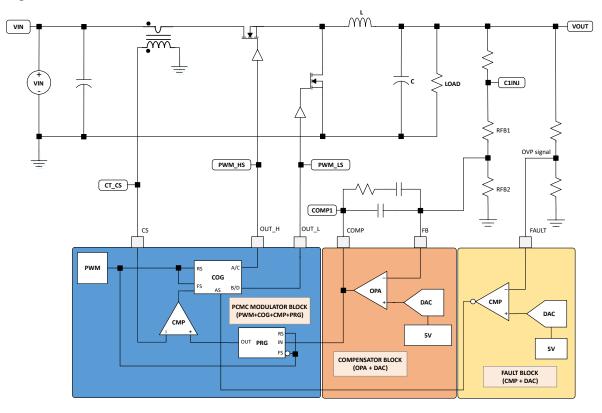

#### 4.3 PCMC Closed Loop Mode

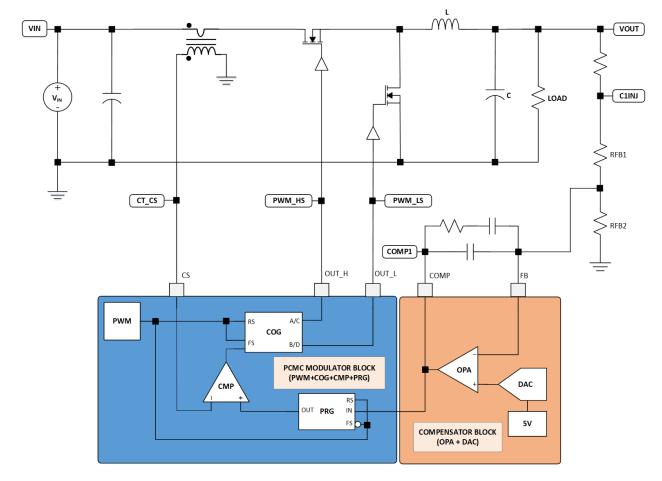

Peak Current Mode Control is a dual loop control mode consisting of an outer voltage feedback loop and an inner inductor current feedback loop.

The outer voltage loop uses an on-chip Operational Amplifier (OPA) as differential error amplifier, comparing the output voltage feedback signal against an internal reference voltage. This reference voltage is applied by a Digital-to-Analog Converter (DAC), which is configured and set by firmware. The inverting input and output of the error amplifier are routed to device pins to insert an external RC compensation filter into the amplifier feedback loop.

The inner inductor current feedback loop is closed by routing the inductor current feedback signal on to an analog comparator CMP, which compares the current feedback signal against the output of the error

© 2018 Microchip Technology Inc.

amplifier. The comparator output is further routed into the PWM output generator logic COG, truncating the active on-time when the inductor current exceeds the reference signal level.

In this setup, the digital PWM module is determining the switching period and maximum duty ratio at which the active on-time will be terminated in case the COG has not been tripped by the current loop comparator CMP.

To prevent sub-harmonic oscillations in this fixed frequency, continuous conduction mode PCMC system, the PRG is put between the error amplifier OPA output and the inductor current comparator CMP reference input. This module is modulating a negative ramp onto output signal of the error amplifier OPA. The PRG modulation ramp is synchronized with the PWM to reset the negative sawtooth waveform at the end of the period. The figure below shows the peripheral configuration of the microcontroller for PCMC Closed Loop operation.

#### Figure 4-20. PCMC Closed Loop Configuration

#### 4.3.1 MCC SMPS Library Configuration for PCMC Closed Loop

The following instructions show how to setup the peripherals of the CIP Hybrid Power Starter Kit to be able to operate in PCMC test mode.

1. Open MPLAB X. Connect the CIP Hybrid Power Starter Kit to the computer through an on-board debugger USB port using a conventional micro-USB cable. MPLAB X will detect the CIP Hybrid Power Starter Kit and an Xplained Window appears that provides relevant information about the board.

- 2. Create new Standalone Project in MPLAB X. Select the PIC16F1779 device. Select the CIP Hybrid Starter Kit as programming tool. Name this project "PCMC".

- 3. Open MCC. Save the MCC configuration as PCMC.mc3.

- 4. In the Project Resources area, change the internal oscillator clock to 8 MHz from the System Module. On the Pin Manager, change the package to QFN44.

- Go to the Device Resources area, click SMPS Power Controllers and expand Power Supply Topologies, double click on SyncBuck. This action will move the SyncBuck to the Project Resources area.

Figure 4-21. Selecting SyncBuck from Device Resources

| Device Resources                           | - |

|--------------------------------------------|---|

| 📽 mTouch                                   | ^ |

| Mikro-E Clicks                             |   |

| Internet Of Things                         |   |

| <ul> <li>SMPS Power Controllers</li> </ul> |   |

| CIP Blocks                                 |   |

| Control Modes                              |   |

| Power Supply Topologies                    |   |

| SyncBuck                                   | Ú |

- 6. In the Project Resources area, click on **SyncBuck**. On the **Configuration** tab, under Hardware Settings, select PCMC as the control mode. Change the switching frequency to 500 kHz, the duty cycle to 90%, reference voltage to 2.5V, leading edge blanking to 250 ns, rising edge dead time to 15 ns, and falling edge dead time to 60 ns. Choose PWM Controller Block 3.

- 7. Click the **Upload All** button. This action will load all the peripherals of the PWM Controller Block 3 on the Project Resources area.

#### Figure 4-22. Hardware Settings for PCMC Synchronous Buck Converter

#### SyncBuck

| ිසsy Setup                  |                 |           |     |        |     |

|-----------------------------|-----------------|-----------|-----|--------|-----|

| Hardware Settings           |                 |           |     |        |     |

| Control Mode: PCMC 💌        |                 |           |     |        |     |

|                             | Desired         |           |     | Actual |     |

| Sw Frequency: 31.25 ≤       | 500             | ≤ 8000.0  | kHz | 500    | kHz |

| Max. Duty Cycle: 10 ≤       | 90              | ≤ 100     | %   | 90     | %   |

| Vref: 0 ≤                   | 2.5             | ≤ 5       | V   | 2.5    | V   |

| Leading Edge Blanking: 0 ≤  | 250             | ≤ 1968.75 | ns  | 250    | ns  |

| Rising Edge Dead Time: 0 ≤  | 15              | ≤ 315     | ns  | 50     | ns  |

| Falling Edge Dead Time: 0 ≤ | 60              | ≤ 315     | ns  | 70     | ns  |

| Slope Compensation: Click U | pload All 👻     |           |     |        |     |

|                             |                 | _         |     |        |     |

|                             |                 |           |     |        |     |

| PWM Controller Block:       | Controller Blog | ck 3 💌    |     |        |     |

| Sub-Module Selection        |                 |           |     |        |     |

| Upload Submodules           | Upload Al       |           |     |        |     |

Add slope compensation of 0.3 V/us.

Figure 4-23. Slope Compensation for PCMC Synchronous Buck Converter

| Slope Compensation: | 0.30 V/us | - |  |

|---------------------|-----------|---|--|

|                     |           |   |  |

|                     |           |   |  |

PWM Controller Block: PWM Controller Block 3 -

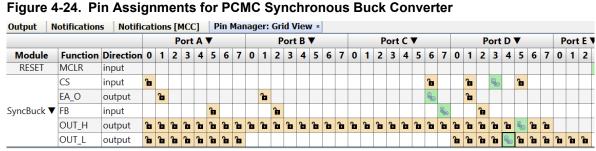

Go to the Pin Manager: Grid View. Assign RD3 as input pin for CS, RC6 as output pin for signal EA\_OUT, RC7 as input pin for signal FB, RD5 as output pin for signal OUT\_H, and RD4 as output pin for signal OUT\_L.

#### **Test Modes Operation**

#### 10. Soft start is enabled by default on the PCMC Control Mode section. Figure 4-25. Enabling Soft Start in PCMC Synchronous Buck Converter

| Project Resour Gen Im                       | <b></b> | E | РСМС                    |         |             |          |     |       |     |

|---------------------------------------------|---------|---|-------------------------|---------|-------------|----------|-----|-------|-----|

| 🕸 CompensatorBlock                          | [       | × | فَظَ Easy Setup         |         |             |          |     |       |     |

| ModulatorBlockPCMC                          |         | × | Information Configurat  | tion So | chematic    |          |     |       |     |

| TaultBlock                                  | [       | × | Hardware Settings       |         |             |          |     |       |     |

| <ul> <li>Control Modes</li> </ul>           |         |   |                         |         |             |          |     |       |     |

| 🕸 РСМС                                      | [       | × | PWM Mode: Half-Bridg    | e 🔹     |             |          |     |       |     |

| <ul> <li>Power Supply Topologies</li> </ul> |         |   |                         | -       | Desired     |          |     | Actua |     |

| SyncBuck                                    | [       | × | Sw Frequency: 3         | 1.25 ≤  | 500         | ≤ 8000.0 | kHz | 500   | kHz |

| ▼ Derinherals                               |         | ~ | Max. Duty Cycle:        | 10 ≤    | 90          | ≤ 100    | %   | 90    | %   |

| Device Resources                            | ۷       | - | Vref:                   | 0 ≤     | 2.5         | ≤ 5      | v   | 2.5   | V   |

| <ul> <li>Documents</li> </ul>               |         | Â | Leading Edge Blanking:  | 0 ≤     | 250         | ≤1968.75 | ns  | 250   | ns  |

| PIC16F1779 Product Page                     |         |   | Rising Edge Dead Time:  | 0 ≤     | 15          | ≤ 315    | ns  | 15.0  | ns  |

| <ul> <li>Peripherals</li> </ul>             |         |   |                         |         | <u></u>     |          |     |       |     |

| ADC                                         |         |   | Falling Edge Dead Time: | 0 ≤     | 60          | ≤ 315    | ns  | 60.0  | ns  |

| ▶ 🗠 ССР                                     |         |   | Slope Compensation:     |         | 0.30 V/us 🔻 |          |     |       |     |

| 🕨 🏊 CLC                                     |         |   | V Enable Soft Start     |         |             |          |     |       |     |

11. Enabling soft start disables the COG, PWM and OPA peripherals at power on.

## CIP Hybrid Power Starter Kit Test Modes Operation

| Registers        |                                                            |

|------------------|------------------------------------------------------------|

| gs               |                                                            |

|                  |                                                            |

| Half-Bridge mode | -                                                          |

| FOSC             | Max Cumulative Uncertanity 3                               |

| Interrupt        |                                                            |

| ££               |                                                            |

|                  |                                                            |

| Registers        |                                                            |

| ings             |                                                            |

| ]                |                                                            |

|                  | ▼ Clock                                                    |

| active_hi 🔹      | Clock Source FOSC                                          |

| standard_PWM 🔹   | Prescalar No_Prescalar                                     |

|                  | gs Half-Bridge mode FOSC Interrupt Registers ngs active_hi |

#### Figure 4-26. COG, PWM and OPA Disabled Initially for Soft Start

#### OPA3

| 🛱 Easy Setup 📄 F  | Registers |   |  |  |

|-------------------|-----------|---|--|--|

| Hardware Settings |           |   |  |  |

| Enable OPAMP      |           |   |  |  |

| Channel Select    |           |   |  |  |

| Positive Channel  | DAC5_out  | • |  |  |

| Negetive Changed  |           | _ |  |  |

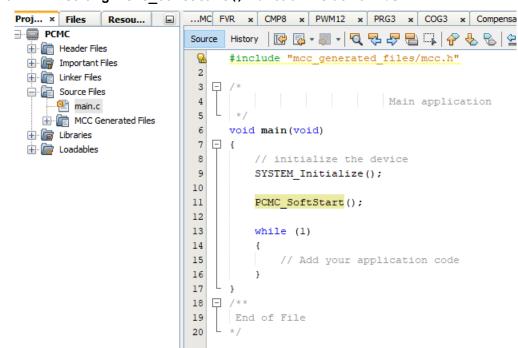

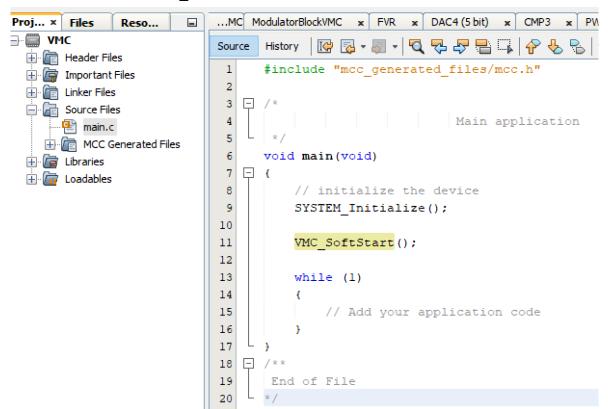

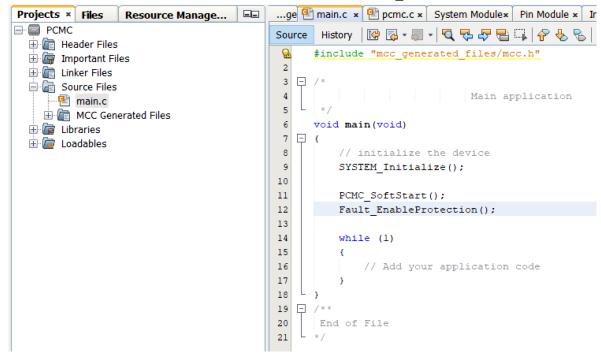

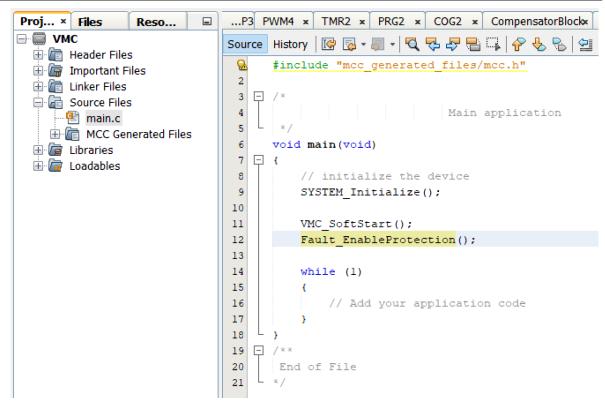

12. Click Generate button to generate the code. On the main.c, add the following line of code, PCMC\_SoftStart();.

#### **Test Modes Operation**

Figure 4-27. Inserting 'PCMC SoftStart()' function inside main.c

- 13. Program the PIC16F1779 device on the CIP Hybrid Power Starter Kit by clicking the "Make and Program Device Main Project" icon.

- 14. Alternatively, the user can also download the PCMC firmware to the CIP Hybrid Power Starter Kit by dragging the generated . hex file of the project to the CURIOSITY drive. The .hex file is located on the --dist\default\production folder.

- 15. The board is now configured for PCMC-CS operation.

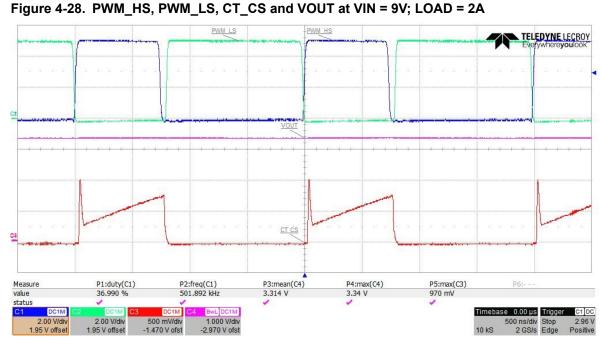

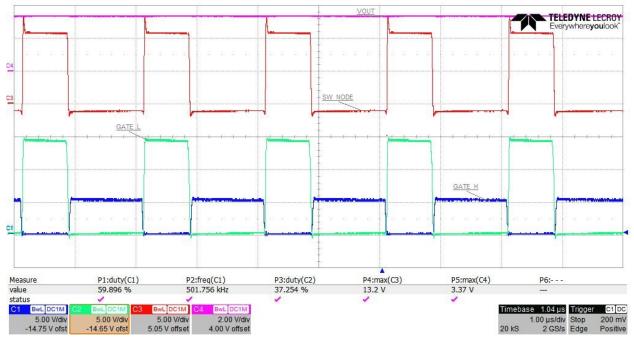

#### 4.3.2 PCMC Closed Loop Test

Below are the steps for testing the PCMC Closed Loop operation of the CIP Hybrid Power Starter Kit.

- Remove programming interface. Place CH1 oscilloscope probe to PWM\_HS test point, CH2 oscilloscope probe to PWM\_LS test point, CH3 oscilloscope probe to CT\_CS test point, and CH4 oscilloscope probe to VOUT test point.

- 2. Connect DC supply (set to 6V) and LOAD (set to 2A). Power-up the board. PWM\_HS, PWM\_LS and CT\_CS signals and VOUT can be monitored.

- 3. Increase VIN up to 16V. VOUT is regulated to 3.3V.

- 4. Increase LOAD to 4A. VOUT is regulated to 3.3V.

**Test Modes Operation**

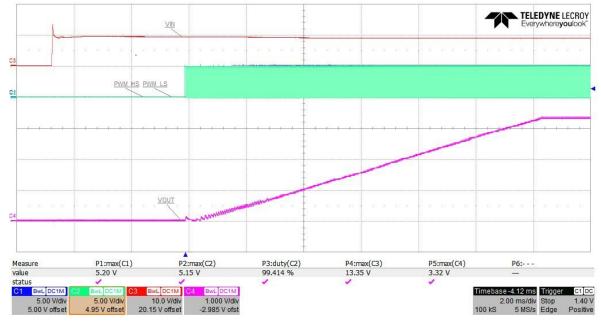

5. Connect CH3 to VIN. Capture soft start by lowering the oscilloscope time base and setting positive edge trigger source to VOUT.

Figure 4-29. Monitoring Soft Start at Start-up

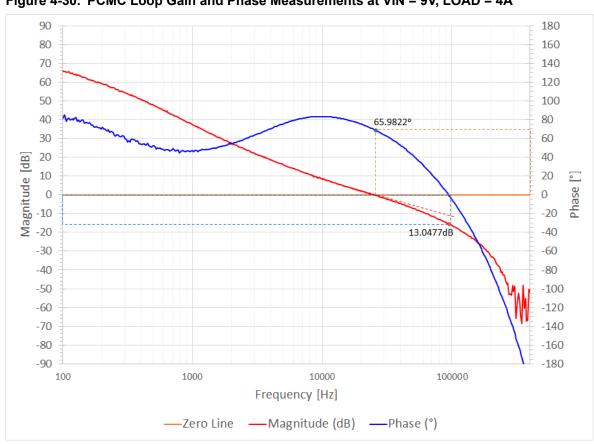

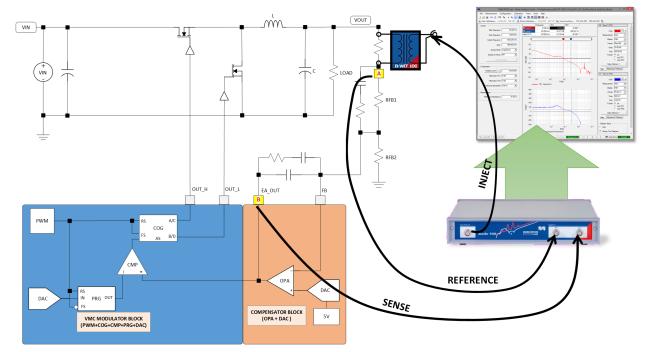

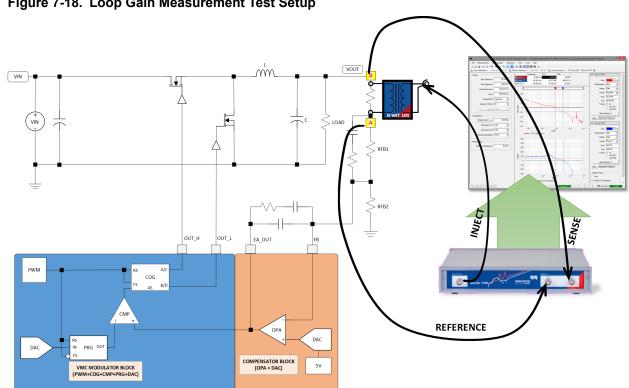

6. The control loop stability is observed by measuring the frequency response of the open loop gain in the closed loop system. This magnitude/phase measurement is commonly used to determine the three main stability criteria indicators phase margin, gain margin and gain slope at the crossover frequency of the gain.

## **CIP Hybrid Power Starter Kit Test Modes Operation**

Figure 4-30. PCMC Loop Gain and Phase Measurements at VIN = 9V, LOAD = 4A

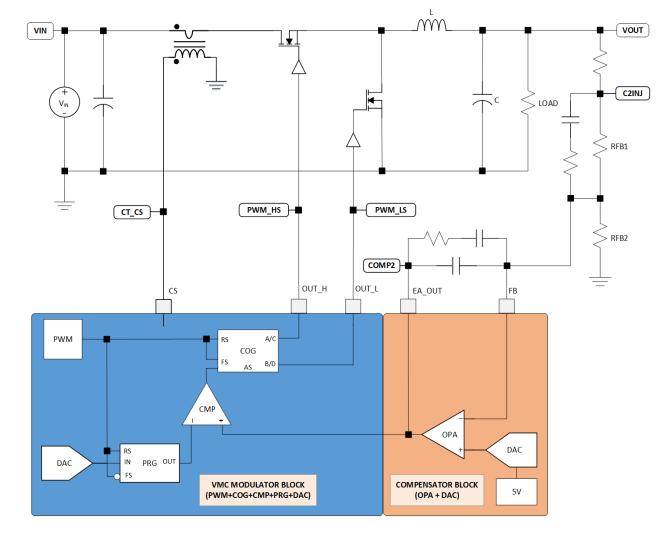

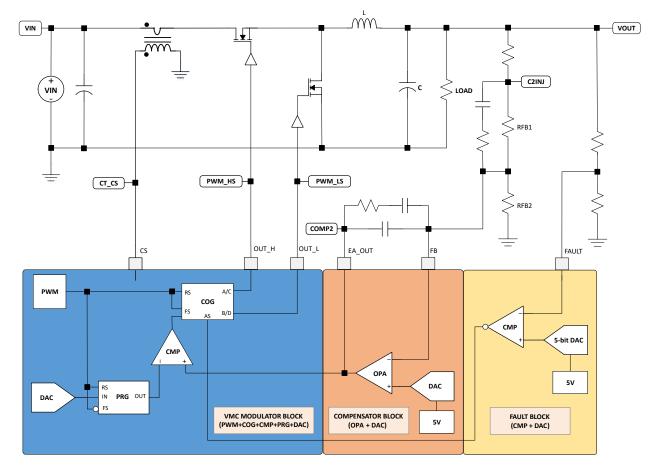

#### 4.4 VMC Closed Loop Mode

Voltage Mode Control is established by closing the voltage feedback loop through an error amplifier and analog ramp comparator CMP.

The voltage loop uses an on-chip Operational Amplifier (OPA) as differential error amplifier, comparing the output voltage feedback signal against an internal reference voltage. This reference voltage is applied by DAC, which is configured and set by firmware. The inverting input and output of the error amplifier are routed to device pins to insert an external RC compensation filter into the amplifier feedback loop.

The PRG is configured to produce a positive sawtooth waveform, which is synchronized and driven by the digital PWM generator. The peak voltage of the sawtooth is determined by the switching frequency and user-selected slew rate of the ramp voltage. An analog comparator is used to compare the PRG sawtooth waveform against the error amplifier output signal (reference). The comparator output is further routed into the PWM output generator logic COG, truncating the active on-time when the PRG sawtooth ramp exceeds the error amplifier reference signal level. The COG logic performs the function of an SR latch, preventing undesired resets until the end of the switching period.

In this setup, the digital PWM module is determining the switching period and maximum duty ratio at which the active on-time will be terminated in case the COG has not been tripped by the ramp generator comparator.

© 2018 Microchip Technology Inc.

**Test Modes Operation**

#### 4.4.1 MCC SMPS Library Configuration for VMC Closed Loop

The following instructions show how to setup the peripherals of the CIP Hybrid Power Starter Kit to be able to operate in VMC test mode.

- 1. Open MPLAB X. Connect the CIP Hybrid Power Starter Kit to the computer through an on-board debugger USB port using a conventional micro-USB cable. MPLAB X will detect the CIP Hybrid Power Starter Kit and an Xplained Window appears that provides relevant information about the board.

- 2. Create new Standalone Project in MPLAB X. Select the PIC16F1779 device. Select the CIP Hybrid Starter Kit as programming tool. Name this project "VMC".

- 3. Open MCC. Save the MCC configuration as VMC.mc3.

- 4. In the Project Resources area, change the internal oscillator clock to 8 MHz from the System Module. On the Pin Manager, change the package to QFN44.

- 5. Go to the Device Resources area, click **SMPS Power Controllers** and expand **Power Supply Topologies**, double click on **SyncBuck**. This action will move the SyncBuck to the Project Resources area.

- In the Project Resources area, click on SyncBuck. On the Configuration tab, under Hardware Settings, select VMC as control mode. Change the switching frequency to 500 kHz, the duty cycle to 90%, reference voltage to 2.5V, leading edge blanking to 250 ns, rising edge dead time to 15 ns and falling edge dead time to 60 ns. Add sawtooth ramp of 2.5V/us. Choose PWM Controller Block 2.

- 7. Click the **Upload All** button. This action will load all the peripherals of the PWM Controller Block 3 on the Project Resources area.

Figure 4-32. Hardware Settings for VMC Synchronous Buck Converter