### ATA6622C/ATA6624C/ATA6626C

# LIN Bus Transceiver with 3.3V (5V) Regulator and Watchdog

#### **DATASHEET**

#### **Features**

- Master and slave operation possible

- Supply voltage up to 40V

- Operating voltage V<sub>S</sub> = 5V to 27V

- Typically 10µA supply current during Sleep Mode

- Typically 57µA supply current in Silent Mode

- Linear low-drop voltage regulator, 85mA current capability:

- Normal, Fail-safe, and Silent Mode

- Atmel ATA6622C VCC = 3.3V ±2%

- Atmel ATA6624C VCC = 5.0V ±2%

- Atmel ATA6626C VCC = 5.0V ±2%. TXD time-out timer disabled

- In Sleep Mode VCC is switched off

- VCC- undervoltage detection (4ms reset time) and watchdog reset logical combined at open drain output NRES

- Negative trigger input for watchdog

- Boosting the voltage regulator possible with an external NPN transistor

- LIN physical layer according to LIN 2.0, 2.1 and SAEJ2602-2

- Wake-up capability via LIN-bus, wake pin, or KI\_15 pin

- INH output to control an external voltage regulator or to switch off the master pull up resistor

- TXD time-out timer; Atmel ATA6626C: TXD time-out timer Is disabled

- Bus pin is overtemperature and short circuit protected versus GND and battery

- Adjustable watchdog time via external resistor

- Advanced EMC and ESD performance

- Fulfills the OEM "Hardware Requirements for LIN in automotive Applications Rev.1.0"

- Interference and damage protection according to ISO7637

- Qualified according to AEC-Q100

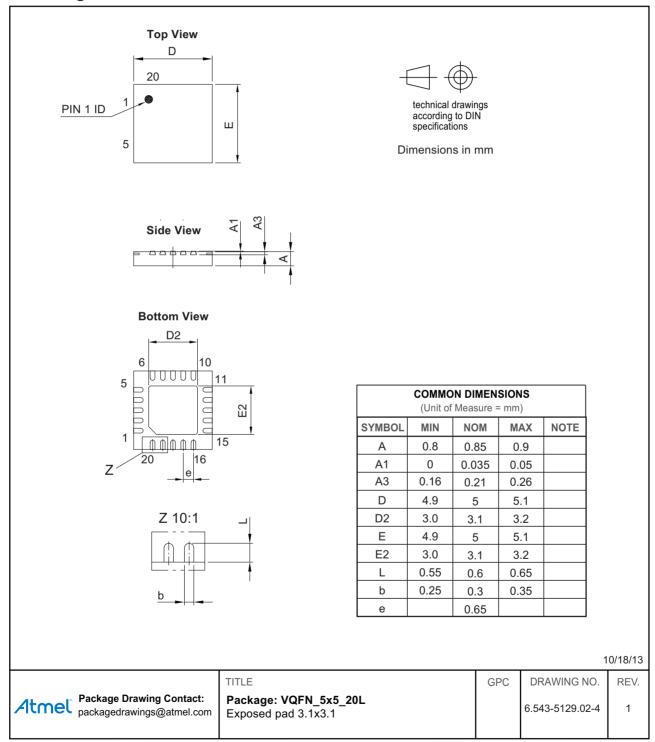

- Package: QFN 5mm x 5mm with 20 pins (Moisture Sensitivity Level 1)

# 1. Description

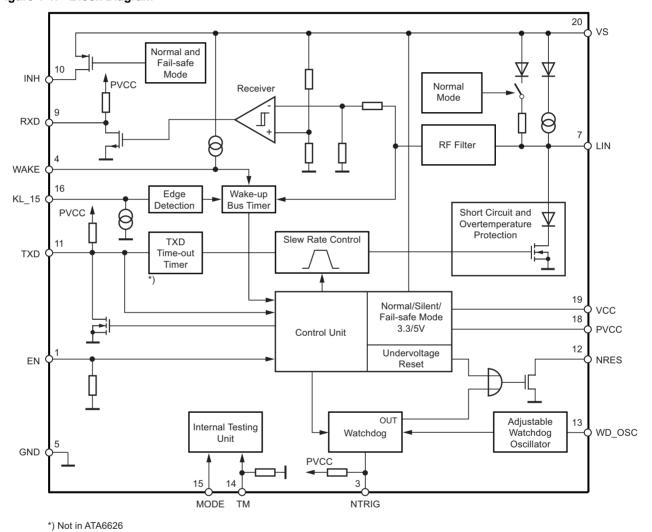

The Atmel® ATA6622C is a fully integrated LIN transceiver, which complies with the LIN 2.0, 2.1 and SAEJ2602-2 specifications. It has a low-drop voltage regulator for 3.3V/85mA output and a window watchdog. The Atmel ATA6624C has the same functionality as the Atmel ATA6622C; however, it uses a 5V/85mA regulator. The Atmel ATA6626C has the same functionality as Atmel ATA6624C without a TXD time-out timer. The voltage regulator is able to source 85mA, but the output current can be boosted by using an external NPN transistor. This chip combination makes it possible to develop inexpensive, simple, yet powerful slave and master nodes for LIN-bus systems. Atmel ATA6622C/ATA6624C/ATA6626C are designed to handle the low-speed data communication in vehicles, e.g., in convenience electronics. Improved slope control at the LIN-driver ensures secure data communication up to 20kBaud. Sleep Mode and Silent Mode guarantee very low current consumption. The Atmel ATA6626C is able to switch the LIN unlimited to dominant level via TXD for low data rates.

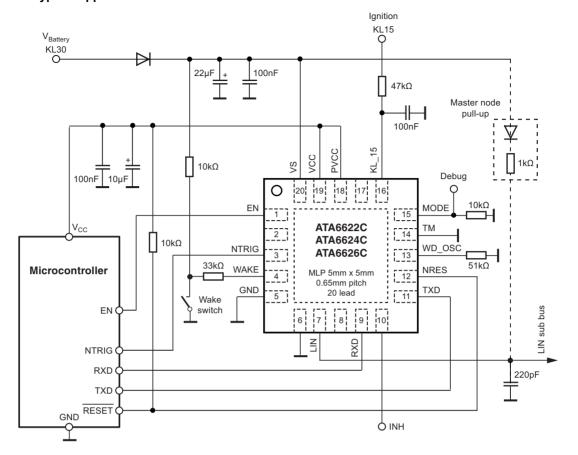

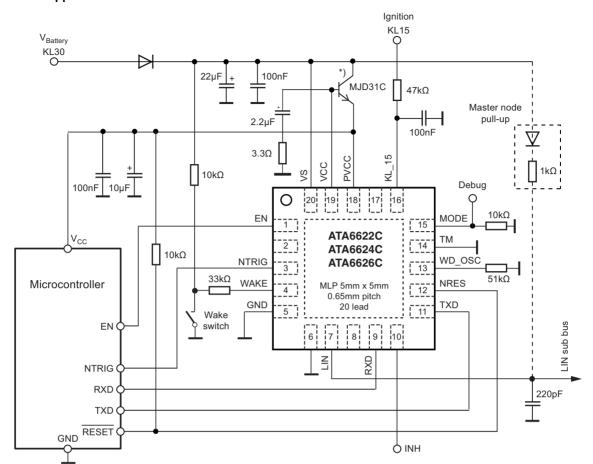

Figure 1-1. Block Diagram

# 2. Pin Configuration

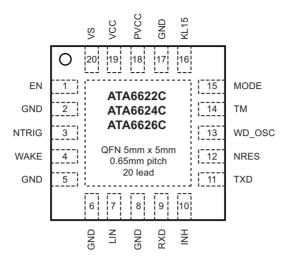

Figure 2-1. Pinning QFN20

Table 2-1. Pin Description

| Pin      | Symbol | Function                                                                                |

|----------|--------|-----------------------------------------------------------------------------------------|

| 1        | EN     | Enables the device in Normal Mode                                                       |

| 2        | GND    | System ground (optional)                                                                |

| 3        | NTRIG  | Low-level watchdog trigger input from microcontroller                                   |

| 4        | WAKE   | High-voltage input for local wake-up request; if not needed, connect directly to VS     |

| 5        | GND    | System ground (mandatory)                                                               |

| 6        | GND    | System ground (optional)                                                                |

| 7        | LIN    | LIN-bus line input/output                                                               |

| 8        | GND    | System ground (optional)                                                                |

| 9        | RXD    | Receive data output                                                                     |

| 10       | INH    | Battery related output for controlling an external voltage regulator                    |

| 11       | TXD    | Transmit data input; active low output (strong pull down) after a local wake-up request |

| 12       | NRES   | Output undervoltage and watchdog reset (open drain)                                     |

| 13       | WD_OSC | External resistor for adjustable watchdog timing                                        |

| 14       | TM     | For factory testing only (tie to ground)                                                |

| 15       | MODE   | Low, watchdog is on; high, watchdog is off                                              |

| 16       | KL_15  | Ignition detection (edge sensitive)                                                     |

| 17       | GND    | System ground (optional)                                                                |

| 18       | PVCC   | 3.3V/5V regulator sense input pin                                                       |

| 19       | VCC    | 3.3V/5V regulator output/driver pin                                                     |

| 20       | VS     | Battery supply                                                                          |

| Backside |        | Heat slug is connected to all GND pins                                                  |

### 3. Functional Description

#### 3.1 Physical Layer Compatibility

Since the LIN physical layer is independent from higher LIN layers (e.g., the LIN protocol layer), all nodes with a LIN physical layer according to revision 2.x can be mixed with LIN physical layer nodes, which, according to older versions (i.e., LIN 1.0, LIN 1.1, LIN 1.2, LIN 1.3), are without any restrictions.

#### 3.2 Supply Pin (VS)

The LIN operating voltage is  $V_S$  = 5V to 27V. An undervoltage detection is implemented to disable data transmission if  $V_S$  falls below  $VS_{th}$  < 4V in order to avoid false bus messages. After switching on VS, the IC starts in Fail-safe Mode, and the voltage regulator is switched on.

The supply current is typically  $10\mu A$  in Sleep Mode and  $57\mu A$  in Silent Mode.

#### 3.3 Ground Pin (GND)

The IC does not affect the LIN Bus in the event of GND disconnection. It is able to handle a ground shift up to 11.5% of VS. The mandatory system ground is pin 5.

#### 3.4 Voltage Regulator Output Pin (VCC)

The internal 3.3V/5V voltage regulator is capable of driving loads up to 85mA. It is able to supply the microcontroller and other ICs on the PCB and is protected against overloads by means of current limitation and overtemperature shut-down. Furthermore, the output voltage is monitored and will cause a reset signal at the NRES output pin if it drops below a defined threshold  $V_{thun}$ . To boost up the maximum load current, an external NPN transistor may be used, with its base connected to the VCC pin and its emitter connected to PVCC.

#### 3.5 Voltage Regulator Sense Pin (PVCC)

The PVCC is the sense input pin of the 3.3V/5V voltage regulator. For normal applications (i.e., when only using the internal output transistor), this pin is connected to the VCC pin. If an external boosting transistor is used, the PVCC pin must be connected to the output of this transistor, i.e., its emitter terminal.

#### 3.6 Bus Pin (LIN)

A low-side driver with internal current limitation and thermal shutdown and an internal pull-up resistor compliant with the LIN 2.x specification are implemented. The allowed voltage range is between –27V and +40V. Reverse currents from the LIN bus to VS are suppressed, even in the event of GND shifts or battery disconnection. LIN receiver thresholds are compatible with the LIN protocol specification. The fall time from recessive to dominant bus state and the rise time from dominant to recessive bus state are slope controlled.

#### 3.7 Input/Output Pin (TXD)

In Normal Mode the TXD pin is the microcontroller interface used to control the state of the LIN output. TXD must be pulled to ground in order to have a low LIN-bus. If TXD is high or unconnected (internal pull-up resistor), the LIN output transistor is turned off, and the bus is in recessive state. During Fail-safe Mode, this pin is used as output. It is current-limited to < 8mA. and is latched to low if the last wake-up event was from pin WAKE or KL 15.

#### 3.8 TXD Dominant Time-out Function

The TXD input has an internal pull-up resistor. An internal timer prevents the bus line from being driven permanently in dominant state. If TXD is forced to low for longer than  $t_{DOM} > 6ms$ , the LIN-bus driver is switched to recessive state.

To reactivate the LIN bus driver, switch TXD to high (> 10µs).

The time-out function is disabled in the ATA6626C. Switching to dominant level on the LIN bus occurs without any time limitations.

#### 3.9 Output Pin (RXD)

This output pin reports the state of the LIN-bus to the microcontroller. LIN high (recessive state) is reported by a high level at RXD; LIN low (dominant state) is reported by a low level at RXD. The output has an internal pull-up resistor with typically  $5k\Omega$  to VCC. The AC characteristics can be defined with an external load capacitor of 20pF.

The output is short-circuit protected. RXD is switched off in Unpowered Mode (i.e.,  $V_S = 0V$ ).

#### 3.10 Enable Input Pin (EN)

The Enable Input pin controls the operation mode of the device. If EN is high, the circuit is in Normal Mode, with transmission paths from TXD to LIN and from LIN to RXD both active. The VCC voltage regulator operates with 3.3V/5V/85mA output capability.

If EN is switched to low while TXD is still high, the device is forced to Silent Mode. No data transmission is then possible, and the current consumption is reduced to  $I_{VS}$  typ. 57 $\mu$ A. The VCC regulator has its full functionality.

If EN is switched to low while TXD is low, the device is forced to Sleep Mode. No data transmission is possible, and the voltage regulator is switched off.

#### 3.11 Wake Input Pin (WAKE)

The Wake Input pin is a high-voltage input used to wake up the device from Sleep Mode or Silent Mode. It is usually connected to an external switch in the application to generate a local wake-up. A pull-up current source, typically 10µA, is implemented.

If a local wake-up is not needed in the application, connect the Wake pin directly to the VS pin.

#### 3.12 Mode Input Pin (MODE)

Connect the MODE pin directly or via an external resistor to GND for normal watchdog operation. To debug the software of the connected microcontroller, connect MODE pin to 3.3V/5V and the watchdog is switched off.

#### 3.13 TM Input Pin

The TM pin is used for final production measurements at Atmel<sup>®</sup>. In normal application, it has to be always connected to GND.

#### 3.14 KL 15 Pin

The KL\_15 pin is a high-voltage input used to wake up the device from Sleep or Silent Mode. It is an edge sensitive pin (low-to-high transition). It is usually connected to ignition to generate a local wake-up in the application when the ignition is switched on. Although KL\_15 pin is at high voltage ( $V_{Batt}$ ), it is possible to switch the IC into Sleep or Silent Mode. Connect the KL\_15 pin directly to GND if you do not need it. A debounce timer with a typical Tdb<sub>Kl 15</sub> of 160 $\mu$ s is implemented.

The input voltage threshold can be adjusted by varying the external resistor due to the input current  $I_{KL\_15}$ . To protect this pin against voltage transients, a serial resistor of  $47k\Omega$  and a ceramic capacitor of 100nF are recommended. With this RC combination you can increase the wake-up time  $Tw_{KL\_15}$  and, therefore, the sensitivity against transients on the ignition KI 15

You can also increase the wake-up time using external capacitors with higher values.

#### 3.15 INH Output Pin

The INH Output pin is used to switch an external voltage regulator on during Normal or Fail-safe Mode. The INH pin is switched off in Sleep or Silent Mode. It is possible to switch off the external  $1k\Omega$  master resistor via the INH pin for master node applications. The INH pin is switched off during VCC undervoltage reset.

#### 3.16 Reset Output Pin (NRES)

The Reset Output pin, an open drain output, switches to low during  $V_{CC}$  undervoltage or a watchdog failure.

#### 3.17 WD\_OSC Output Pin

The WD\_OSC Output pin provides a typical voltage of 1.2V, which supplies an external resistor with values between  $34k\Omega$  and  $120k\Omega$  to adjust the watchdog oscillator time.

### 3.18 NTRIG Input Pin

The NTRIG Input pin is the trigger input for the window watchdog. A pull-up resistor is implemented. A negative edge triggers the watchdog. The trigger signal (low) must exceed a minimum time  $t_{triqmin}$  to generate a watchdog trigger.

### 3.19 Wake-up Events from Sleep or Silent Mode

- LIN-bus

- WAKE pin

- EN pin

- KL\_15

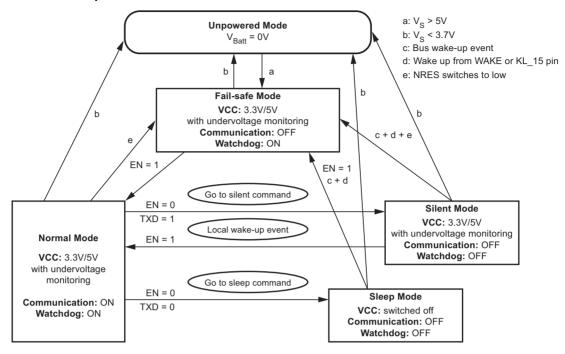

## 4. Modes of Operation

Figure 4-1. Modes of Operation

Table 4-1. Table of Modes

| Mode of<br>Operation | Transceiver | vcc     | Watchdog | WD_OSC | INH | RXD                           | LIN              |

|----------------------|-------------|---------|----------|--------|-----|-------------------------------|------------------|

| Fail-safe            | Off         | 3.3V/5V | On       | 1.23V  | On  | High,<br>except after wake-up | Recessive        |

| Normal               | On          | 3.3V/5V | On       | 1.23V  | On  | LIN depending                 | TXD<br>depending |

| Silent               | Off         | 3.3V/5V | Off      | 0V     | Off | High                          | Recessive        |

| Sleep                | Off         | 0V      | Off      | 0V     | Off | 0V                            | Recessive        |

#### 4.1 Normal Mode

This is the normal transmitting and receiving mode of the LIN Interface in accordance with the LIN specification LIN 2.x. The voltage regulator is active and can source up to 85mA. The undervoltage detection is activated. The watchdog needs a trigger signal from NTRIG to avoid resets at NRES. If NRES is switched to low, the IC changes its state to Fail-safe Mode.

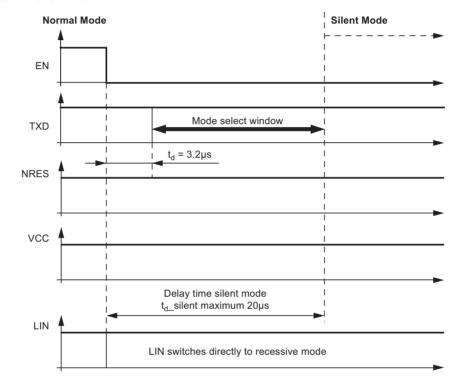

#### 4.2 Silent Mode

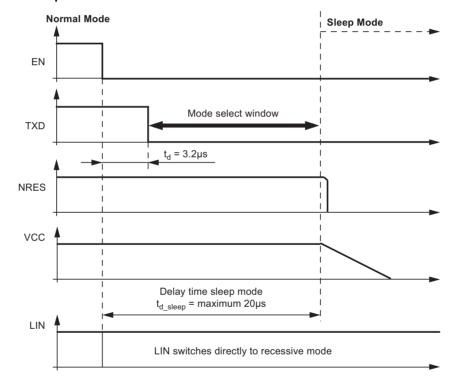

A falling edge at EN when TXD is high switches the IC into Silent Mode. The TXD Signal has to be logic high during the Mode Select window (see Figure 4-2). The transmission path is disabled in Silent Mode. The overall supply current from  $V_{Batt}$  is a combination of the  $I_{VSSi}$  = 57µA plus the VCC regulator output current  $I_{VCC}$ .

The internal slave termination between the LIN pin and the VS pin is disabled in Silent Mode, only a weak pull-up current (typically  $10\mu A$ ) between the LIN pin and the VS pin is present. Silent Mode can be activated independently from the actual level on the LIN, WAKE, or KL\_15 pins.

If an undervoltage condition occurs, NRES is switched to low, and the IC changes its state to Fail-safe Mode.

A voltage less than the LIN Pre\_Wake detection VLINL at the LIN pin activates the internal LIN receiver and switches on the internal slave termination between the LIN pin and the  $V_S$  pin.

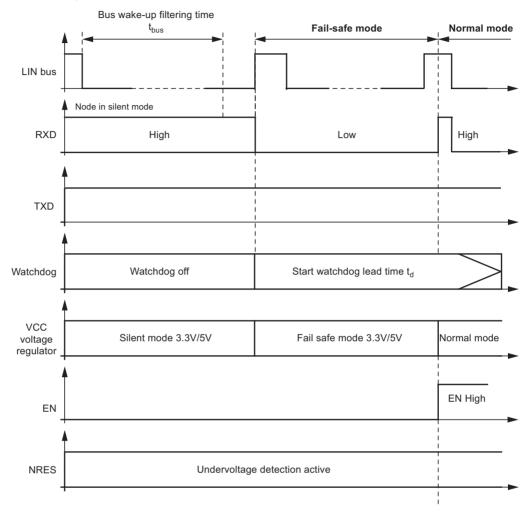

Figure 4-2. Switch to Silent Mode

A falling edge at the LIN pin followed by a dominant bus level maintained for a certain time period (> t<sub>bus</sub>) and the following rising edge at the LIN pin (see Figure 4-3 on page 9) results in a remote wake-up request. The device switches from Silent Mode to Fail-safe Mode. The remote wake-up request is indicated by a low level at the RXD pin to interrupt the microcontroller (see Figure 4-3 on page 9). EN high can be used to switch directly to Normal Mode.

Figure 4-3. LIN Wake Up from Silent Mode

#### 4.3 Sleep Mode

A falling edge at EN when TXD is low switches the IC into Sleep Mode. The TXD Signal has to be logic low during the Mode Select window (Figure 4-4 on page 10). In order to avoid any influence to the LIN-pin during switching into sleep mode it is possible to switch the EN up to 3.2 µs earlier to LOW than the TXD. Therefore, the best and easiest way are two falling edges at TXD and EN at the same time. The transmission path is disabled in Sleep Mode. The supply current I<sub>VSsleep</sub> from V<sub>Batt</sub> is typically 10μA.

The VCC regulator is switched off. NRES and RXD are low. The internal slave termination between the LIN pin and VS pin is disabled, only a weak pull-up current (typically 10µA) between the LIN pin and the VS pin is present. Sleep Mode can be activated independently from the current level on the LIN, WAKE, or KL 15 pin.

A voltage less than the LIN Pre Wake detection VLINL at the LIN pin activates the internal LIN receiver and switches on the internal slave termination between the LIN pin and the V<sub>S</sub> pin.

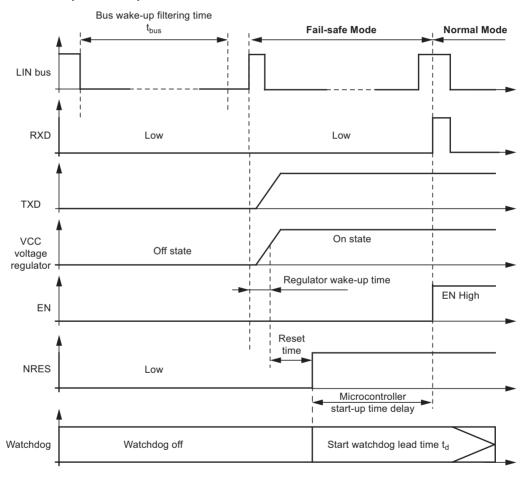

A falling edge at the LIN pin followed by a dominant bus level maintained for a certain time period (> t<sub>bus</sub>) and a following rising edge at pin LIN results in a remote wake-up request. The device switches from Sleep Mode to Fail-safe Mode.

The VCC regulator is activated, and the remote wake-up request is indicated by a low level at the RXD pin to interrupt the microcontroller (see Figure 4-5 on page 11).

EN high can be used to switch directly from Sleep/Silent to Fail-safe Mode. If EN is still high after VCC ramp up and undervoltage reset time, the IC switches to the Normal Mode.

Figure 4-4. Switch to Sleep Mode

### 4.4 Fail-safe Mode

The device automatically switches to Fail-safe Mode at system power-up. The voltage regulator is switched on (see Figure 5-1 on page 13). The NRES output switches to low for  $t_{res}$  = 4ms and gives a reset to the microcontroller. LIN communication is switched off. The IC stays in this mode until EN is switched to high. The IC then changes to Normal Mode. A power down of  $V_{Batt}$  ( $V_{S}$  < 3.7V) during Silent or Sleep Mode switches the IC into Fail-safe Mode after power up. A low at NRES switches into Fail-safe Mode directly. During Fail-safe Mode the TXD pin is an output and signals the last wake-up source.

#### 4.5 Unpowered Mode

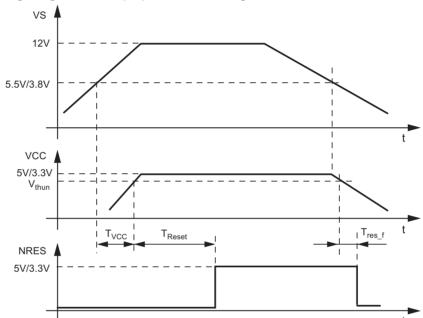

If you connect battery voltage to the application circuit, the voltage at the VS pin increases according to the block capacitor (see Figure 5-1 on page 13). After VS is higher than the VS undervoltage threshold VS<sub>th</sub>, the IC mode changes from Unpowered Mode to Fail-safe Mode. The VCC output voltage reaches its nominal value after  $t_{VCC}$ . This time,  $t_{VCC}$ , depends on the VCC capacitor and the load.

The NRES is low for the reset time delay t<sub>reset</sub>. During this time, t<sub>reset</sub>, no mode change is possible.

Figure 4-5. LIN Wake Up from Sleep Mode

### 5. Wake-up Scenarios from Silent or Sleep Mode

#### 5.1 Remote Wake-up via Dominant Bus State

A voltage less than the LIN Pre\_Wake detection V<sub>LINL</sub> at the LIN pin activates the internal LIN receiver.

A falling edge at the LIN pin followed by a dominant bus level  $V_{BUSdom}$  maintained for a certain time period (>  $t_{BUS}$ ) and a rising edge at pin LIN result in a remote wake-up request. The device switches from Silent or Sleep Mode to Fail-safe Mode. The VCC voltage regulator is/remains activated, the INH pin is switched to high, and the remote wake-up request is indicated by a low level at the RXD pin to generate an interrupt for the microcontroller. A low level at the LIN pin in the Normal Mode starts the bus wake-up filtering time, and if the IC is switched to Silent or Sleep Mode, it will receive a wake-up after a positive edge at the LIN pin.

#### 5.2 Local Wake-up via Pin WAKE

A falling edge at the WAKE pin followed by a low level maintained for a certain time period ( $> t_{WAKE}$ ) results in a local wake-up request. The device switches to Fail-safe Mode. The local wake-up request is indicated by a low level at the RXD pin to generate an interrupt in the microcontroller and a strong pull down at TXD. When the Wake pin is low, it is possible to switch to Silent or Sleep Mode via pin EN. In this case, the wake-up signal has to be switched to high  $> 10 \mu$  before the negative edge at WAKE starts a new local wake-up request.

#### 5.3 Local Wake-up via Pin KL 15

A positive edge at pin KL\_15 followed by a high voltage level for a certain time period (>  $t_{KL_15}$ ) results in a local wake-up request. The device switches into the Fail-safe Mode. The extra long wake-up time ensures that no transients at KL\_15 create a wake up. The local wake-up request is indicated by a low level at the RXD pin to generate an interrupt for the microcontroller and a strong pull down at TXD. During high-level voltage at pin KL\_15, it is possible to switch to Silent or Sleep Mode via pin EN. In this case, the wake-up signal has to be switched to low > 250 $\mu$ s before the positive edge at KL\_15 starts a new local wake-up request. With external RC combination, the time is even longer.

#### 5.4 Wake-up Source Recognition

The device can distinguish between a local wake-up request (Wake or KL\_15 pins) and a remote wake-up request (dominant LIN bus state). The wake-up source can be read on the TXD pin in Fail-safe Mode. A high level indicates a remote wake-up request (weak pull up at the TXD pin); a low level indicates a local wake-up request (strong pull down at the TXD pin). The wake-up request flag (signalled on the RXD pin), as well as the wake-up source flag (signalled on the TXD pin), is immediately reset if the microcontroller sets the EN pin to high (see Figure 4-2 on page 8 and Figure 4-3 on page 9) and the IC is in Normal Mode. The last wake-up source flag is stored and signalled in Fail-safe Mode at the TXD pin.

#### 5.5 Fail-safe Features

- During a short-circuit at LIN to V<sub>Battery</sub>, the output limits the output current to I<sub>BUS\_lim</sub>. Due to the power dissipation, the chip temperature exceeds T<sub>LINoff</sub>, and the LIN output is switched off. The chip cools down and after a hysteresis of T<sub>hys</sub>, switches the output on again. RXD stays on high because LIN is high. During LIN overtemperature switch-off, the VCC regulator works independently.

- During a short-circuit from LIN to GND the IC can be switched into Sleep or Silent Mode. If the short-circuit disappears, the IC starts with a remote wake-up.

- The reverse current is very low < 2μA at the LIN pin during loss of V<sub>Batt</sub>. This is optimal behavior for bus systems where some slave nodes are supplied from battery or ignition.

- During a short circuit at VCC, the output limits the output current to I<sub>VCClim</sub>. Because of undervoltage, NRES switches to low and sends a reset to the microcontroller. The IC switches into Fail-safe Mode. If the chip temperature exceeds the value T<sub>VCCoff</sub>, the VCC output switches off. The chip cools down and after a hysteresis of T<sub>hys</sub>, switches the output on again. Because of the Fail-safe Mode, the VCC voltage will switch on again although EN is switched off from the microcontroller. The microcontroller can start with its normal operation.

- EN pin provides a pull-down resistor to force the transceiver into recessive mode if EN is disconnected.

- RXD pin is set floating if V<sub>Batt</sub> is disconnected.

- TXD pin provides a pull-up resistor to force the transceiver into recessive mode if TXD is disconnected.

- If TXD is short-circuited to GND, it is possible to switch to Sleep Mode via ENABLE after t<sub>dom</sub> > 20ms (only for Atmel® ATA6622C/ATA6624C).

- If the WD OSC pin has a short-circuit to GND and the NTRIG Signal has a period time > 27ms, the watchdog runs with an internal oscillator and guarantees a reset after the second NTRIG signal at the latest.

- If the resistor at WO OSC pin is disconnected, the watchdog runs with an internal oscillator and guarantees a reseet after the second NTRIG signal at the latest.

#### 5.6 **Voltage Regulator**

The voltage regulator needs an external capacitor for compensation and for smoothing the disturbances from the microcontroller. It is recommended to use an electrolythic capacitor with C > 1.8µF and a ceramic capacitor with C = 100nF. The values of these capacitors can be varied by the customer, depending on the application.

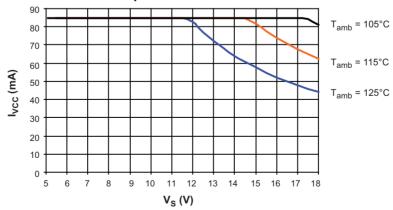

The main power dissipation of the IC is created from the VCC output current I<sub>VCC</sub>, which is needed for the application. In Figure 5-2 on page 13 the safe operating area of the Atmel ATA6624C/ATA6626C is shown.

Figure 5-1. VCC Voltage Regulator: Ramp-up and Undervoltage Detection

Figure 5-2. Power Dissipation: Safe Operating Area: VCC Output Current versus Supply Voltage V<sub>s</sub> at Different Ambient Temperatures Due to R<sub>thja</sub> = 35K/W

For programming purposes of the microcontroller it is potentially necessary to supply the V<sub>CC</sub> output via an external power supply while the  $V_S$  Pin of the system basis chip is disconnected. This will not affect the system basis chip.

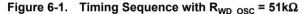

### 6. Watchdog

The watchdog anticipates a trigger signal from the microcontroller at the NTRIG (negative edge) input within a time window of  $T_{wd}$ . The trigger signal must exceed a minimum time  $t_{trigmin} > 200$ ns. If a triggering signal is not received, a reset signal will be generated at output NRES. The timing basis of the watchdog is provided by the internal oscillator. Its time period,  $T_{osc}$ , is adjustable via the external resistor  $R_{wd}$  osc  $(34k\Omega$  to  $120k\Omega)$ .

During Silent or Sleep Mode the watchdog is switched off to reduce current consumption.

The minimum time for the first watchdog pulse is required after the undervoltage reset at NRES disappears. It is defined as lead time t<sub>d</sub>. After wake up from Sleep or Silent Mode, the lead time t<sub>d</sub> starts with the negative edge of the RXD output.

### 6.1 Typical Timing Sequence with $R_{WD OSC} = 51k\Omega$

The trigger signal T<sub>wd</sub> is adjustable between 20ms and 64ms using the external resistor R<sub>WD OSC</sub>.

For example, with an external resistor of  $R_{WD\ OSC}$  = 51k $\Omega$  ±1%, the typical parameters of the watchdog are as follows:

$$\begin{array}{l} t_{osc} = 0.405 \times R_{WD\_OSC} - 0.0004 \times (R_{WD\_OSC})^2 \ (R_{WD\_OSC} \ in \ k\Omega; \ t_{osc} \ in \ \mu s) \\ t_{OSC} = 19.6 \mu s \ due \ to \ 51 k\Omega \\ t_d = 7895 \times 19.6 \mu s = 155 ms \\ t_1 = 1053 \times 19.6 \mu s = 20.6 ms \\ t_2 = 1105 \times 19.6 \mu s = 21.6 ms \\ t_{nres} = constant = 4 ms \end{array}$$

After ramping up the battery voltage, the 3.3V/5V regulator is switched on. The reset output NRES stays low for the time  $t_{reset}$  (typically 4ms), then it switches to high, and the watchdog waits for the trigger sequence from the microcontroller. The lead time,  $t_d$ , follows the reset and is  $t_d$  = 155ms. In this time, the first watchdog pulse from the microcontroller is required. If the trigger pulse NTRIG occurs during this time, the time  $t_1$  starts immediately. If no trigger signal occurs during the time  $t_d$ , a watchdog reset with  $t_{NRES}$  = 4ms will reset the microcontroller after  $t_d$  = 155ms. The times  $t_1$  and  $t_2$  have a fixed relationship between each other. A triggering signal from the microcontroller is anticipated within the time frame of  $t_2$  = 21.6ms. To avoid false triggering from glitches, the trigger pulse must be longer than  $t_{TRIG,min}$  > 200ns. This slope serves to restart the watchdog sequence. If the triggering signal fails in this open window  $t_2$ , the NRES output will be drawn to ground. A triggering signal during the closed window  $t_1$  immediately switches NRES to low.

#### Worst Case Calculation with R<sub>WD\_OSC</sub> = $51k\Omega$ 6.2

The internal oscillator has a tolerance of 20%. This means that  $t_1$  and  $t_2$  can also vary by 20%. The worst case calculation for the watchdog period t<sub>wd</sub> is calculated as follows.

The ideal watchdog time t<sub>wd</sub> is between the maximum t<sub>1</sub> and the minimum t<sub>1</sub> plus the minimum t<sub>2</sub>.

$$\begin{array}{l} t_{1,\text{min}} = 0.8 \times t_1 = 16.5 \text{ms}, \ t_{1,\text{max}} = 1.2 \times t_1 = 24.8 \text{ms} \\ t_{2,\text{min}} = 0.8 \times t_2 = 17.3 \text{ms}, \ t_{2,\text{max}} = 1.2 \times t_2 = 26 \text{ms} \end{array}$$

$$t_{2,min} = 0.8 \times t_2 = 17.3 \text{ms}, t_{2,max} = 1.2 \times t_2 = 26 \text{ms}$$

$$t_{\text{wdmax}} = t_{1\text{min}} + t_{2\text{min}} = 16.5\text{ms} + 17.3\text{ms} = 33.8\text{ms}$$

$t_{\text{wdmin}} = t_{1\text{max}} = 24.8\text{ms}$

$t_{wd} = 29.3 \text{ms} \pm 4.5 \text{ms} (\pm 15\%)$

A microcontroller with an oscillator tolerance of ±15% is sufficient to supply the trigger inputs correctly.

Table 6-1. Typical Watchdog Timings

| $egin{array}{c} {\sf R}_{\sf WD\_OSC} \ {\sf k}\Omega \end{array}$ | Oscillator<br>Period<br>t <sub>osc</sub> /µs | Lead<br>Time<br>t <sub>d</sub> /ms | Closed<br>Window<br>t <sub>1</sub> /ms | Open Window<br>t <sub>2</sub> /ms | Trigger Period from<br>Microcontroller t <sub>wd</sub> /ms | Reset Time<br>t <sub>nres</sub> /ms |

|--------------------------------------------------------------------|----------------------------------------------|------------------------------------|----------------------------------------|-----------------------------------|------------------------------------------------------------|-------------------------------------|

| 34                                                                 | 13.3                                         | 105                                | 14.0                                   | 14.7                              | 19.9                                                       | 4                                   |

| 51                                                                 | 19.61                                        | 154.8                              | 20.64                                  | 21.67                             | 29.32                                                      | 4                                   |

| 91                                                                 | 33.54                                        | 264.80                             | 35.32                                  | 37.06                             | 50.14                                                      | 4                                   |

| 120                                                                | 42.84                                        | 338.22                             | 45.11                                  | 47.34                             | 64.05                                                      | 4                                   |

# 7. Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameters                                                                                                                                             | Symbol            | Min.         | Тур. | Max.                 | Unit     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------|------|----------------------|----------|

| Supply voltage V <sub>S</sub>                                                                                                                          | V <sub>S</sub>    | -0.3         |      | +40                  | V        |

| Pulse time $\leq$ 500ms; T <sub>a</sub> = 25°C<br>Output current I <sub>VCC</sub> $\leq$ 85mA                                                          | V <sub>S</sub>    |              |      | +40                  | V        |

| Pulse time $\leq$ 2min; $T_a = 25^{\circ}C$<br>Output current $I_{VCC} \leq 85mA$                                                                      | V <sub>S</sub>    |              |      | 27                   | V        |

| WAKE (with $33k\Omega$ serial resistor) KL_15 (with $47k\Omega/100nF$ ) DC voltage Transient voltage due to ISO7637 (coupling 1nF)                     |                   | –1<br>–150   |      | +40<br>+100          | V        |

| INH - DC voltage                                                                                                                                       |                   | -0.3         |      | V <sub>S</sub> + 0.3 | V        |

| LIN - DC voltage                                                                                                                                       |                   | -27          |      | +40                  | V        |

| Logic pins (RxD, TxD, EN, NRES, NTRIG, WD_OSC, MODE, TM)                                                                                               |                   | -0.3         |      | +5.5                 | V        |

| Output current NRES                                                                                                                                    | I <sub>NRES</sub> |              |      | +2                   | mA       |

| PVCC DC voltage<br>VCC DC voltage                                                                                                                      |                   | -0.3<br>-0.3 |      | +5.5<br>+6.5         | V<br>V   |

| ESD according to IBEE LIN EMC Test Spec. 1.0 following IEC 61000-4-2 - Pin VS, LIN, KL_15 (47kΩ/100nF) to GND - Pin WAKE (33kΩ serial resistor) to GND |                   | ±6<br>±5     |      |                      | KV<br>KV |

| ESD HBM following STM5.1 with 1.5kΩ 100pF - Pin VS, LIN, KL_15, WAKE to GND                                                                            |                   | ±6           |      |                      | KV       |

| HBM ESD<br>ANSI/ESD-STM5.1<br>JESD22-A114<br>AEC-Q100 (002)                                                                                            |                   | ±3           |      |                      | KV       |

| CDM ESD STM 5.3.1                                                                                                                                      |                   | ±750         |      |                      | V        |

| Machine Model ESD AEC-Q100-RevF(003)                                                                                                                   |                   | ±200         |      |                      | V        |

| Junction temperature                                                                                                                                   | T <sub>j</sub>    | -40          |      | +150                 | °C       |

| Storage temperature                                                                                                                                    | T <sub>s</sub>    | <b>–</b> 55  |      | +150                 | °C       |

### 8. Thermal Characteristics

| Parameters                                                                 | Symbol            | Min. | Тур. | Max. | Unit |

|----------------------------------------------------------------------------|-------------------|------|------|------|------|

| Thermal resistance junction to heat slug                                   | R <sub>thjc</sub> |      |      | 10   | K/W  |

| Thermal resistance junction to ambient, where heat slug is soldered to PCB | R <sub>thja</sub> |      | 35   |      | K/W  |

| Thermal shutdown of VCC regulator                                          |                   | 150  | 165  | 170  | °C   |

| Thermal shutdown of LIN output                                             |                   | 150  | 165  | 170  | °C   |

| Thermal shutdown hysteresis                                                |                   |      | 10   |      | °C   |

#### **Electrical Characteristics** 9.

| No. | Parameters                                             | Test Conditions                                                                                      | Pin | Symbol               | Min. | Тур. | Max.                   | Unit | Type* |

|-----|--------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----|----------------------|------|------|------------------------|------|-------|

| 1   | VS Pin                                                 |                                                                                                      |     |                      |      |      |                        |      |       |

| 1.1 | Nominal DC voltage range                               |                                                                                                      | VS  | V <sub>S</sub>       | 5    |      | 27                     | V    | А     |

| 1.2 | Supply current in Sleep                                | Sleep Mode $\begin{aligned} &V_{LIN} > V_S - 0.5V \\ &V_S < 14V \ (T_j = 25^{\circ}C) \end{aligned}$ | VS  | I <sub>VSsleep</sub> | 3    | 10   | 14                     | μА   | В     |

| 1.2 | Mode                                                   | Sleep Mode $V_{LIN} > V_S - 0.5V$ $V_S < 14V (T_j = 125^{\circ}C)$                                   | VS  | I <sub>VSsleep</sub> | 5    | 11   | 16                     | μA   | A     |

| 1.3 | Supply current in Silent                               | Bus recessive $V_S < 14V (T_j = 25^{\circ}C)$ Without load at VCC                                    | VS  | I <sub>VSsi</sub>    | 47   | 57   | 67                     | μА   | В     |

| 1.5 | Mode                                                   | Bus recessive $V_S < 14V (T_j = 125^{\circ}C)$ Without load at VCC                                   | VS  | I <sub>VSsi</sub>    | 56   | 66   | 76                     | μA   | A     |

| 1.4 | Supply current in Normal Mode                          | Bus recessive<br>V <sub>S</sub> < 14V<br>Without load at VCC                                         | VS  | I <sub>VSrec</sub>   | 0.3  |      | 0.8                    | mA   | А     |

| 1.5 | Supply current in Normal Mode                          | Bus dominant $V_S < 14V$ $V_{CC}$ load current 50 mA                                                 | VS  | I <sub>VSdom</sub>   | 50   |      | 53                     | mA   | A     |

| 1.6 | Supply current in Fail-<br>safe Mode                   | Bus recessive $V_S < 14V$ Without load at VCC                                                        | VS  | I <sub>VSfail</sub>  | 250  |      | 550                    | μA   | A     |

| 1.7 | V <sub>S</sub> undervoltage threshold                  |                                                                                                      | VS  | V <sub>Sth</sub>     | 3.7  | 4.4  | 5                      | V    | Α     |

| 1.8 | VS undervoltage threshold hysteresis                   |                                                                                                      | VS  | V <sub>Sth_hys</sub> |      | 0.2  |                        | V    | Α     |

| 2   | RXD Output Pin                                         |                                                                                                      |     |                      |      |      |                        |      |       |

| 2.1 | Low-level output sink current                          | Normal Mode<br>$V_{LIN} = 0V$<br>$V_{RXD} = 0.4V$                                                    | RXD | I <sub>RXD</sub>     | 1.3  | 2.5  | 8                      | mA   | A     |

| 2.2 | Low-level output voltage                               | I <sub>RXD</sub> = 1mA                                                                               | RXD | V <sub>RXDL</sub>    |      |      | 0.4                    | V    | Α     |

| 2.3 | Internal resistor to V <sub>CC</sub>                   |                                                                                                      | RXD | R <sub>RXD</sub>     | 3    | 5    | 7                      | kΩ   | Α     |

| 3   | TXD Input/Output Pin                                   |                                                                                                      |     |                      |      |      |                        |      |       |

| 3.1 | Low-level voltage input                                |                                                                                                      | TXD | $V_{TXDL}$           | -0.3 |      | +0.8                   | V    | Α     |

| 3.2 | High-level voltage input                               |                                                                                                      | TXD | $V_{TXDH}$           | 2    |      | V <sub>CC</sub> + 0.3V | V    | А     |

| 3.3 | Pull-up resistor                                       | V <sub>TXD</sub> = 0V                                                                                | TXD | R <sub>TXD</sub>     | 125  | 250  | 400                    | kΩ   | Α     |

| 3.4 | High-level leakage current                             | V <sub>TXD</sub> = VCC                                                                               | TXD | I <sub>TXD</sub>     | -3   |      | +3                     | μA   | Α     |

| 3.5 | Low-level output sink current at local wake-up request | Fail-safe Mode<br>$V_{LIN} = V_{S}$<br>$V_{WAKE} = 0V$<br>$V_{TXD} = 0.4V$                           | TXD | I <sub>TXDwake</sub> | 2    | 2.5  | 8                      | mA   | A     |

|     | 1000/ 1 1 1                                            | P = 100% correlation tosted                                                                          |     |                      |      |      |                        |      |       |

<sup>\*)</sup> Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

#### **Electrical Characteristics (Continued)** 9.

| No. | Parameters                              | Test Conditions                                                                                                      | Pin   | Symbol              | Min.                     | Тур. | Max.                   | Unit    | Type* |

|-----|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------|---------------------|--------------------------|------|------------------------|---------|-------|

| 4   | EN Input Pin                            |                                                                                                                      |       |                     |                          |      |                        |         |       |

| 4.1 | Low-level voltage input                 |                                                                                                                      | EN    | $V_{ENL}$           | -0.3                     |      | +0.8                   | V       | Α     |

| 4.2 | High-level voltage input                |                                                                                                                      | EN    | $V_{ENH}$           | 2                        |      | V <sub>CC</sub> + 0.3V | V       | Α     |

| 4.3 | Pull-down resistor                      | V <sub>EN</sub> = V <sub>CC</sub>                                                                                    | EN    | R <sub>EN</sub>     | 50                       | 125  | 200                    | kΩ      | Α     |

| 4.4 | Low-level input current                 | V <sub>EN</sub> = 0V                                                                                                 | EN    | I <sub>EN</sub>     | -3                       |      | +3                     | μA      | Α     |

| 5   | NTRIG Watchdog Input                    | Pin                                                                                                                  |       |                     |                          |      |                        |         |       |

| 5.1 | Low-level voltage input                 |                                                                                                                      | NTRIG | $V_{NTRIGL}$        | -0.3                     |      | +0.8                   | V       | Α     |

| 5.2 | High-level voltage input                |                                                                                                                      | NTRIG | $V_{NTRIGH}$        | 2                        |      | V <sub>CC</sub> + 0.3V | V       | Α     |

| 5.3 | Pull-up resistor                        | V <sub>NTRIG</sub> = 0V                                                                                              | NTRIG | R <sub>NTRIG</sub>  | 125                      | 250  | 400                    | kΩ      | Α     |

| 5.4 | High-level leakage current              | $V_{NTRIG} = V_{CC}$                                                                                                 | NTRIG | I <sub>NTRIG</sub>  | -3                       |      | +3                     | μA      | Α     |

| 6   | Mode Input Pin                          | •                                                                                                                    |       |                     |                          |      |                        |         |       |

| 6.1 | Low-level voltage input                 |                                                                                                                      | MODE  | $V_{MODEL}$         | -0.3                     |      | +0.8                   | V       | Α     |

| 6.2 | High-level voltage input                |                                                                                                                      | MODE  | V <sub>MODEH</sub>  | 2                        |      | V <sub>CC</sub> + 0.3V | V       | Α     |

| 6.3 | Leakage current                         | $V_{MODE} = V_{CC}$ or $V_{MODE} = 0V$                                                                               | MODE  | I <sub>MODE</sub>   | -3                       |      | +3                     | μA      | А     |

| 7   | INH Output Pin                          |                                                                                                                      |       |                     |                          |      |                        |         |       |

| 7.1 | High-level voltage                      | I <sub>INH</sub> = -15mA                                                                                             | INH   | $V_{INHH}$          | V <sub>S</sub> –<br>0.75 |      | V <sub>S</sub>         | V       | Α     |

| 7.2 | Switch-on resistance between VS and INH |                                                                                                                      | INH   | R <sub>INH</sub>    |                          | 30   | 50                     | Ω       | Α     |

| 7.3 | Leakage current                         | Sleep Mode<br>V <sub>INH</sub> = 0V/27V, V <sub>S</sub> = 27V                                                        | INH   | I <sub>INHL</sub>   | -3                       |      | +3                     | μA      | Α     |

| 8   | Load 3 (Medium): 6.8nF,                 | d Conditions:<br>2; Load 2 (Large): 10nF, 500<br>, 660 $\Omega$ , Characterized on Sa<br>the Timing Parameters for P | mples |                     |                          | .0.0 |                        | ŀkBit/s |       |

| 8.1 | Driver recessive output voltage         | Load1/Load2                                                                                                          | LIN   | V <sub>BUSrec</sub> | $0.9 \times V_S$         |      | V <sub>S</sub>         | V       | Α     |

| 8.2 | Driver dominant voltage                 | $V_{VS} = 7V$<br>$R_{load} = 500\Omega$                                                                              | LIN   | V_LoSUP             |                          |      | 1.2                    | V       | Α     |

| 8.3 | Driver dominant voltage                 | $V_{VS} = 18V$<br>$R_{load} = 500\Omega$                                                                             | LIN   | V_ <sub>HiSUP</sub> |                          |      | 2                      | V       | Α     |

| 8.4 | Driver dominant voltage                 | $V_{VS} = 7.0V$<br>$R_{load} = 1000\Omega$                                                                           | LIN   | V_LoSUP_1k          | 0.6                      |      |                        | V       | Α     |

| 8.5 | Driver dominant voltage                 | $V_{VS} = 18V$<br>$R_{load} = 1000\Omega$                                                                            | LIN   | V_HiSUP_1k          | 0.8                      |      |                        | V       | А     |

| 8.6 | Pull-up resistor to V <sub>S</sub>      | The serial diode is mandatory                                                                                        | LIN   | $R_{LIN}$           | 20                       | 30   | 60                     | kΩ      | А     |

| 8.7 | Voltage drop at the serial diodes       | In pull-up path with $R_{slave}$ $I_{SerDiode} = 10mA$                                                               | LIN   | $V_{SerDiode}$      | 0.4                      |      | 1.0                    | V       | D     |

<sup>\*)</sup> Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

# 9. Electrical Characteristics (Continued)

| No.  | Parameters                                                                                                                                                       | Test Conditions                                                                                | Pin | Symbol                   | Min.                     | Тур.                    | Max.                     | Unit | Type* |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----|--------------------------|--------------------------|-------------------------|--------------------------|------|-------|

| 8.8  | LIN current limitation V <sub>BUS</sub> = V <sub>Batt_max</sub>                                                                                                  |                                                                                                | LIN | I <sub>BUS_LIM</sub>     | 40                       | 120                     | 200                      | mA   | А     |

| 8.9  | Input leakage current at<br>the receiver including<br>pull-up resistor as<br>specified                                                                           | Input leakage current Driver off V <sub>BUS</sub> = 0V V <sub>Batt</sub> = 12V                 | LIN | I <sub>BUS_PAS_dom</sub> | -1                       | -0.35                   |                          | mA   | Α     |

| 8.10 | Leakage current LIN recessive                                                                                                                                    | Driver off<br>$8V < V_{Batt} < 18V$<br>$8V < V_{BUS} < 18V$<br>$V_{BUS} \ge V_{Batt}$          | LIN | I <sub>BUS_PAS_rec</sub> |                          | 10                      | 20                       | μΑ   | Α     |

| 8.11 | Leakage current when control unit disconnected from ground. Loss of local ground must not affect communication in the residual network.                          | $GND_{Device} = V_S$ $V_{Batt} = 12V$ $0V < V_{BUS} < 18V$                                     | LIN | I <sub>BUS_NO_gnd</sub>  | -10                      | +0.5                    | +10                      | μА   | A     |

| 8.12 | Leakage current at a disconnected battery. Node has to sustain the current that can flow under this condition. Bus must remain operational under this condition. | V <sub>Batt</sub> disconnected<br>V <sub>SUP_Device</sub> = GND<br>0V < V <sub>BUS</sub> < 18V | LIN | I <sub>BUS_NO_bat</sub>  |                          | 0.1                     | 2                        | μА   | A     |

| 8.13 | Capacitance on pin LIN to GND                                                                                                                                    |                                                                                                | LIN | C <sub>LIN</sub>         |                          |                         | 20                       | pF   | D     |

| 9    | LIN Bus Receiver                                                                                                                                                 |                                                                                                |     |                          |                          |                         |                          |      |       |

| 9.1  | Center of receiver threshold                                                                                                                                     | $V_{BUS\_CNT} = (V_{th\_dom} + V_{th\_rec})/2$                                                 | LIN | V <sub>BUS_CNT</sub>     | 0.475×<br>V <sub>S</sub> | 0.5 ×<br>V <sub>S</sub> | 0.525 × V <sub>S</sub>   | V    | Α     |

| 9.2  | Receiver dominant state                                                                                                                                          | V <sub>EN</sub> = 5V                                                                           | LIN | $V_{BUSdom}$             |                          |                         | $0.4 \times V_S$         | V    | Α     |

| 9.3  | Receiver recessive state                                                                                                                                         | V <sub>EN</sub> = 5V                                                                           | LIN | V <sub>BUSrec</sub>      | $0.6 \times V_S$         |                         |                          | V    | Α     |

| 9.4  | Receiver input hysteresis                                                                                                                                        | $V_{hys} = V_{th\_rec} - V_{th\_dom}$                                                          | LIN | V <sub>BUShys</sub>      | 0.028 × V <sub>S</sub>   | $0.1 \times V_S$        | 0.175 × V <sub>S</sub>   | V    | Α     |

| 9.5  | Pre_Wake detection<br>LIN<br>High-level input voltage                                                                                                            |                                                                                                | LIN | V <sub>LINH</sub>        | V <sub>S</sub> – 2V      |                         | V <sub>S</sub> + 0.3V    | V    | Α     |

| 9.6  | Pre_Wake detection<br>LIN<br>Low-level input voltage                                                                                                             | Activates the LIN receiver                                                                     | LIN | V <sub>LINL</sub>        | -27                      |                         | V <sub>S</sub> –<br>3.3V | V    | А     |

$<sup>^{\</sup>star}$ ) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

# 9. Electrical Characteristics (Continued)

| No.   | Parameters                                                                     | Test Conditions                                                                                                                                                                                                       | Pin      | Symbol                  | Min.  | Тур. | Max.  | Unit | Type* |

|-------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------|-------|------|-------|------|-------|

| 10    | Internal Timers                                                                |                                                                                                                                                                                                                       | '        |                         |       |      |       |      |       |

| 10.1  | Dominant time for wake-up via LIN bus                                          | V <sub>LIN</sub> = 0V                                                                                                                                                                                                 | LIN      | t <sub>bus</sub>        | 30    | 90   | 150   | μs   | А     |

| 10.2  | Time delay for mode<br>change from Fail-safe<br>into Normal Mode via<br>EN pin | V <sub>EN</sub> = 5V                                                                                                                                                                                                  | EN       | t <sub>norm</sub>       | 5     | 15   | 20    | μs   | Α     |

| 10.3  | Time delay for mode<br>change from Normal<br>Mode to Sleep Mode via<br>EN pin  | V <sub>EN</sub> = 0V                                                                                                                                                                                                  | EN       | t <sub>sleep</sub>      | 2     | 7    | 12    | μs   | A     |

| 10.4  | TXD dominant time-out time (ATA6626C disabled)                                 | V <sub>TXD</sub> = 0V                                                                                                                                                                                                 | TXD      | t <sub>dom</sub>        | 6     | 13   | 20    | ms   | Α     |

| 10.5  | Time delay for mode<br>change from Silent<br>Mode into Normal Mode<br>via EN   | V <sub>EN</sub> = 5V                                                                                                                                                                                                  | EN       | t <sub>s_n</sub>        | 5     | 15   | 40    | μs   | A     |

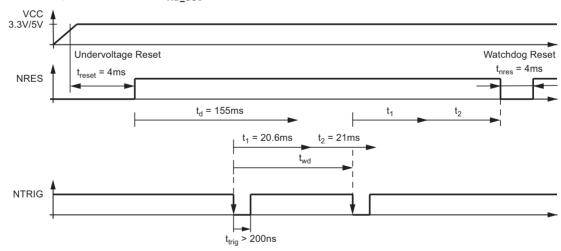

| 10.6  | Duty cycle 1                                                                   | $\begin{aligned} & TH_{Rec(max)} = 0.744 \times V_S \\ & TH_{Dom(max)} = 0.581 \times V_S \\ & V_S = 7.0V \text{ to } 18V \\ & t_{Bit} = 50 \mu s \\ & D1 = t_{bus\_rec(min)} / (2 \times t_{Bit}) \end{aligned}$     | LIN      | D1                      | 0.396 |      |       |      | Α     |

| 10.7  | Duty cycle 2                                                                   | $\begin{aligned} & TH_{Rec(min)} = 0.422 \times V_S \\ & TH_{Dom(min)} = 0.284 \times V_S \\ & V_S = 7.6V \text{ to } 18V \\ & t_{Bit} = 50 \mu s \\ & D2 = t_{bus\_rec(max)}/(2 \times t_{Bit}) \end{aligned}$       | LIN      | D2                      |       |      | 0.581 |      | A     |

| 10.8  | Duty cycle 3                                                                   | $\begin{aligned} & TH_{Rec(max)} = 0.778 \times V_S \\ & TH_{Dom(max)} = 0.616 \times V_S \\ & V_S = 7.0V \text{ to } 18V \\ & t_{Bit} = 96 \mu s \\ & D3 = t_{bus\_rec(min)} / (2 \times t_{Bit}) \end{aligned}$     | LIN      | D3                      | 0.417 |      |       |      | Α     |

| 10.9  | Duty cycle 4                                                                   | $\begin{aligned} & TH_{Rec(min)} = 0.389 \times V_{S} \\ & TH_{Dom(min)} = 0.251 \times V_{S} \\ & V_{S} = 7.6V \text{ to } 18V \\ & t_{Bit} = 96\mus \\ & D4 = t_{bus\_rec(max)} / (2 \times t_{Bit}) \end{aligned}$ | LIN      | D4                      |       |      | 0.590 |      | Α     |

| 10.10 | Slope time falling and rising edge at LIN                                      | V <sub>S</sub> = 7.0V to 18V                                                                                                                                                                                          | LIN      | t <sub>SLOPE_fall</sub> | 3.5   |      | 22.5  | μs   | Α     |

| 11    |                                                                                | Parameters of the LIN Physic<br>I Conditions: C <sub>RXD</sub> = 20pF                                                                                                                                                 | al Layer |                         |       |      |       |      |       |

| 11.1  | Propagation delay of receiver (Figure 9-1 on page 23)                          | $V_S = 7.0V \text{ to } 18V$<br>$t_{rx\_pd} = max(t_{rx\_pdr}, t_{rx\_pdf})$                                                                                                                                          | RXD      | t <sub>rx_pd</sub>      |       |      | 6     | μs   | А     |

| 11.2  | Symmetry of receiver propagation delay rising edge minus falling edge          | $V_S = 7.0V \text{ to } 18V$<br>$t_{rx\_sym} = t_{rx\_pdr} - t_{rx\_pdf}$                                                                                                                                             | RXD      | t <sub>rx_sym</sub>     | -2    |      | +2    | μs   | А     |

<sup>\*)</sup> Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

#### **Electrical Characteristics (Continued)** 9.

| No.  | Parameters                                 | Test Conditions                                  | Pin        | Symbol               | Min.                | Тур. | Max.                  | Unit   | Type* |

|------|--------------------------------------------|--------------------------------------------------|------------|----------------------|---------------------|------|-----------------------|--------|-------|

| 12   | NRES Open Drain Outpo                      | ut Pin                                           |            |                      |                     |      |                       |        |       |

| 12.1 | Low-level output voltage                   | $V_S \ge 5.5V$ $I_{NRES} = 1mA$                  | NRES       | V <sub>NRESL</sub>   |                     |      | 0.14                  | V      | А     |

| 12.2 | Low-level output low                       | 10k $\Omega$ to 5V<br>V <sub>CC</sub> = 0V       | NRES       | V <sub>NRESLL</sub>  |                     |      | 0.14                  | V      | А     |

| 12.3 | Undervoltage reset time                    | $V_S \ge 5.5V$ $C_{NRES} = 20pF$                 | NRES       | t <sub>reset</sub>   | 2                   | 4    | 6                     | ms     | Α     |

| 12.4 | Reset debounce time for falling edge       | $V_S \ge 5.5V$ $C_{NRES} = 20pF$                 | NRES       | t <sub>res_f</sub>   | 1.5                 |      | 10                    | μs     | А     |

| 13   | Watchdog Oscillator                        |                                                  |            |                      |                     |      |                       |        |       |

| 13.1 | Voltage at WD_OSC in Normal Mode           | $I_{WD\_OSC} = -200\mu A$<br>$V_{VS} \ge 4V$     | WD_<br>OSC | $V_{WD\_OSC}$        | 1.13                | 1.23 | 1.33                  | V      | А     |

| 13.2 | Possible values of resistor                |                                                  | WD_<br>OSC | R <sub>OSC</sub>     | 34                  |      | 120                   | kΩ     | Α     |

| 13.3 | Oscillator period                          | $R_{OSC} = 34k\Omega$                            |            | tosc                 | 10.65               | 13.3 | 15.97                 | μs     | Α     |

| 13.4 | Oscillator period                          | $R_{OSC} = 51k\Omega$                            |            | t <sub>osc</sub>     | 15.68               | 19.6 | 23.52                 | μs     | Α     |

| 13.5 | Oscillator period                          | $R_{OSC} = 91k\Omega$                            |            | t <sub>osc</sub>     | 26.83               | 33.5 | 40.24                 | μs     | Α     |

| 13.6 | Oscillator period                          | $R_{OSC} = 120k\Omega$                           |            | t <sub>osc</sub>     | 34.2                | 42.8 | 51.4                  | μs     | Α     |

| 14   | Watchdog Timing Relativ                    | ve to t <sub>OSC</sub>                           |            |                      | 1                   |      |                       | 1      |       |

| 14.1 | Watchdog lead time after Reset             |                                                  |            | t <sub>d</sub>       |                     | 7895 |                       | cycles | А     |

| 14.2 | Watchdog closed window                     |                                                  |            | t <sub>1</sub>       |                     | 1053 |                       | cycles | Α     |

| 14.3 | Watchdog open window                       |                                                  |            | t <sub>2</sub>       |                     | 1105 |                       | cycles | Α     |

| 14.4 | Watchdog reset time NRES                   |                                                  | NRES       | t <sub>nres</sub>    | 3.2                 | 4    | 4.8                   | ms     | Α     |

| 15   | KL_15 Pin                                  |                                                  |            |                      | 1                   |      |                       |        |       |

| 15.1 | High-level input voltage $R_V = 47k\Omega$ | Positive edge initializes a wake-up              | KL_15      | $V_{KL\_15H}$        | 4                   |      | V <sub>S</sub> + 0.3V | V      | Α     |

| 15.2 | Low-level input voltage $R_V = 47k\Omega$  |                                                  | KL_15      | V <sub>KL_15L</sub>  | -1                  |      | +2                    | V      | А     |

| 15.3 | KL_15 pull-down current                    | V <sub>S</sub> < 27V<br>V <sub>KL_15</sub> = 27V | KL_15      | I <sub>KL_15</sub>   |                     | 50   | 65                    | μA     | А     |

| 15.4 | Internal debounce time                     | Without external capacitor                       | KL_15      | Tdb <sub>KL_15</sub> | 80                  | 160  | 250                   | μs     | Α     |

| 15.5 | KL_15 wake-up time                         | $R_V = 47k\Omega$ , C = 100nF                    | KL_15      | Tw <sub>KL_15</sub>  | 0.4                 | 2    | 4.5                   | ms     | С     |

| 16   | WAKE Pin                                   |                                                  |            |                      |                     |      |                       |        |       |

| 16.1 | High-level input voltage                   |                                                  | WAKE       | $V_{WAKEH}$          | V <sub>S</sub> – 1V |      | V <sub>S</sub> + 0.3V | V      | А     |

| 16.2 | Low-level input voltage                    | Initializes a wake-up signal                     | WAKE       | $V_{WAKEL}$          | -1                  |      | V <sub>S</sub> – 3.3V | V      | А     |

| 16.3 | WAKE pull-up current                       | V <sub>S</sub> < 27V<br>V <sub>WAKE</sub> = 0V   | WAKE       | I <sub>WAKE</sub>    | -30                 | -10  |                       | μA     | Α     |

| 16.4 | High-level leakage current                 | V <sub>S</sub> = 27V<br>V <sub>WAKE</sub> = 27V  | WAKE       | I <sub>WAKEL</sub>   | -5                  |      | +5                    | μA     | Α     |

<sup>\*)</sup> Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

# 9. Electrical Characteristics (Continued)

| No.   | Parameters                                    | Test Conditions                                                                                                                                           | Pin        | Symbol               | Min.        | Тур. | Max.  | Unit | Type* |

|-------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------|-------------|------|-------|------|-------|

| 16.5  | Time of low pulse for wake-up via WAKE pin    | V <sub>WAKE</sub> = 0V                                                                                                                                    | WAKE       | I <sub>WAKEL</sub>   | 30          | 70   | 150   | μs   | А     |

| 17    | VCC Voltage Regulator                         | ATA6622C, PVCC = VCC                                                                                                                                      |            |                      |             |      |       |      |       |

| 17.1  | Output voltage VCC                            | 4V < V <sub>S</sub> < 18V<br>(0mA to 50mA)                                                                                                                | VCC        | VCC <sub>nor</sub>   | 3.234       |      | 3.366 | V    | Α     |

| 17.1  | Output voltage voo                            | 4.5V < V <sub>S</sub> < 18V<br>(0mA to 85mA)                                                                                                              | VCC        | VCC <sub>nor</sub>   | 3.234       |      | 3.366 | V    | С     |

| 17.2  | Output voltage VCC at low VS                  | 3V < V <sub>S</sub> < 4V                                                                                                                                  | VCC        | VCC <sub>low</sub>   | $V_S - V_D$ |      | 3.366 | V    | Α     |

| 17.3  | Regulator drop voltage                        | $V_S > 3V$<br>$I_{VCC} = -15mA$                                                                                                                           | VS,<br>VCC | $V_{D1}$             |             |      | 200   | mV   | А     |

| 17.4  | Regulator drop voltage                        | $V_S > 3V$<br>$I_{VCC} = -50 \text{mA}$                                                                                                                   | VS,<br>VCC | $V_{D2}$             |             | 500  | 700   | mV   | А     |

| 17.5  | Line regulation                               | 4V < V <sub>S</sub> < 18V                                                                                                                                 | VCC        | VCC <sub>line</sub>  |             | 0.1  | 0.2   | %    | Α     |

| 17.6  | Load regulation                               | 5mA < I <sub>VCC</sub> < 50mA                                                                                                                             | VCC        | VCC <sub>load</sub>  |             | 0.1  | 0.5   | %    | Α     |

| 17.7  | Power supply ripple rejection                 | 10Hz to 100kHz<br>$C_{VCC}$ = 10 $\mu$ F<br>$V_S$ = 14V, $I_{VCC}$ = -15mA                                                                                | VCC        |                      | 50          |      |       | dB   | D     |

| 17.8  | Output current limitation                     | V <sub>S</sub> > 4V                                                                                                                                       | VCC        | I <sub>VCClim</sub>  | -240        | -160 | -85   | mA   | Α     |

| 17.9  | External load capacity                        | $0.2\Omega$ < ESR < $5\Omega$ at $100 \text{kHz}$ for phase margin $\geq 60^\circ$ ESR < $0.2\Omega$ at $100 \text{kHz}$ for phase margin $\geq 30^\circ$ | VCC        | $C_load$             | 1.8         | 10   |       | μF   | D     |

| 17.10 | VCC undervoltage threshold                    | Referred to VCC<br>V <sub>S</sub> > 4V                                                                                                                    | VCC        | $V_{thunN}$          | 2.8         |      | 3.2   | V    | Α     |

| 17.11 | Hysteresis of undervoltage threshold          | Referred to VCC<br>V <sub>S</sub> > 4V                                                                                                                    | VCC        | Vhys <sub>thun</sub> |             | 150  |       | mV   | А     |

| 17.12 | Ramp-up time $V_S > 4V$<br>to $V_{CC} = 3.3V$ | $C_{VCC}$ = 2.2 $\mu$ F<br>$I_{load}$ = -5mA at VCC                                                                                                       | VCC        | T <sub>VCC</sub>     |             | 100  | 250   | μs   | Α     |

| 18    | VCC Voltage Regulator                         | ATA6624C/ATA6626C, PVC                                                                                                                                    | C = VCC    |                      |             |      |       |      |       |

| 18.1  | Output voltage VCC                            | 5.5V < V <sub>S</sub> < 18V<br>(0mA to 50mA)                                                                                                              | VCC        | VCC <sub>nor</sub>   | 4.9         |      | 5.1   | V    | А     |

| 10.1  | Output voltage voc                            | 6V < V <sub>S</sub> < 18V<br>(0mA to 85mA)                                                                                                                | VCC        | VCC <sub>nor</sub>   | 4.9         |      | 5.1   | V    | С     |

| 18.2  | Output voltage VCC at low VS                  | 4V < V <sub>S</sub> < 5.5V                                                                                                                                | VCC        | VCC <sub>low</sub>   | $V_S - V_D$ |      | 5.1   | V    | А     |

| 18.3  | Regulator drop voltage                        | $V_S > 4V$<br>$I_{VCC} = -20mA$                                                                                                                           | VS,<br>VCC | $V_{D1}$             |             |      | 250   | mV   | Α     |

| 18.4  | Regulator drop voltage                        | $V_S > 4V$<br>$I_{VCC} = -50$ mA                                                                                                                          | VS,<br>VCC | $V_{D2}$             |             | 400  | 600   | mV   | Α     |

| 18.5  | Regulator drop voltage                        | $V_S > 3.3V$<br>$I_{VCC} = -15mA$                                                                                                                         | VS,<br>VCC | $V_{D3}$             |             |      | 200   | mV   | А     |

| 18.6  | Line regulation                               | 5.5V < V <sub>S</sub> < 18V                                                                                                                               | VCC        | VCC <sub>line</sub>  |             | 0.1  | 0.2   | %    | Α     |

| 18.7  | Load regulation                               | 5mA < I <sub>VCC</sub> < 50mA                                                                                                                             | VCC        | VCC <sub>load</sub>  |             | 0.1  | 0.5   | %    | Α     |

<sup>\*)</sup> Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

#### **Electrical Characteristics (Continued)** 9.

$5V < V_S < 27V$ ,  $-40^{\circ}C < Tj < 150^{\circ}C$ , unless otherwise specified. All values refer to GND pins

| No.   | Parameters                                 | Test Conditions                                                                                                                                           | Pin | Symbol               | Min. | Тур. | Max. | Unit | Type* |

|-------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------|------|------|------|------|-------|

| 18.8  | Power supply ripple rejection              | 10Hz to 100kHz<br>$C_{VCC}$ = 10 $\mu$ F<br>$V_S$ = 14V, $I_{VCC}$ = -15mA                                                                                | VCC |                      | 50   |      |      | dB   | D     |