# PolarFire® SoC Product Overview

# Overview

PolarFire® SoC is built upon the award-winning PolarFire FPGA non-volatile FPGA platform. Featuring a five core Linux capable processor subsystem based on the RISC-V ISA, PolarFire SoC brings to market an innovative, midrange, embedded compute platform that inherits all the benefits of the PolarFire FPGA product family. The RISC-V CPU micro-architecture implementation is a simple, 5-stage single issue in order pipeline that does not suffer from the Meltdown and Spectre exploits found in common out-of-order machines. All five CPU cores are coherent with the memory subsystem allowing a versatile mix of deterministic real time systems and Linux in a single, multi-core CPU cluster. With Secure Boot built-in, innovative Linux and Real Time modes, a large Flexible L2 memory subsystem, and a rich set of embedded peripherals, PolarFire SoC provides designers new choices in secure, power-efficient, embedded compute platforms. This document describes the features of PolarFire SoC extended commercial (0 °C to 100 °C  $T_i$ ) and industrial (-40 °C to 100 °C  $T_i$ ) device offerings.

# Microprocessor Subsystem Features

- 64-bit RV64GC (RV64GC or RV64IMAFDC: RISC-V 64-bit Integer, Multiply and divide, Atomic, Floating point single and Double precision and Compressed instruction set support) quad application processing cores, F<sub>MAX</sub> of 667 MHz (–40 °C to 100 °C T<sub>i</sub>), 3.125 CoreMarks/MHz, 1.714 DMIPS/MHz

- L1 memory subsystem with single-error correct, double-error detect (SECDED)

- 32 KB 8-way instruction cache or optional 28 Kbyes tightly integrated memory

- · 32 KB 8-way data cache

- Memory Management Unit (MMU)

- · Physical Memory Protection (PMP) unit

- 64-bit RV64IMAC (RV64IMAC: RISC-V 64-bit Integer, Multiply and divide, Atomic, and Compressed instruction set support) monitor processor core, F<sub>MAX</sub> of 667 MHz (–40 °C to 100 °C T<sub>j</sub>), 3.125 CoreMarks/MHz, 1.714 DMIPS/MHz

- L1 memory subsystem with SECDED

- · 16 KB 2-way instruction cache

- 8 KB scratch pad memory

- PMP unit

- Flexible 2 MB L2 memory subsystem with SECDED configurable as:

- 16-way set associative L2 cache with write-back policy

- Loosely Integrated Memory (LIM) mode for deterministic access

- Coherent directly addressable Scratchpad Memory mode for shared messages across cores

- Integrated 36-bit DDR4/DDR3/LPDDR4/LPDDR3 memory controller with SECDED

- DDR4 at 1.6 Gbps with a 8 GB address reach

- · Cache coherent CPU bus matrix

- AMBA I/O switch with QoS and Memory Protection Unit (MPU)

- Integrated 128 KB embedded non-volatile memory (eNVM) for boot code

- Boot options

- Microchip secure boot

- User defined, PUF-protected secure boot

- Boot directly from eNVM

- Platform interrupt controller

- 185 interrupt sources from the microprocessor subsystem and FPGA fabric with seven priority levels

- Local interrupt controller

- 48 local interrupts sourced from the FPGA drive the local interrupt controller on each core

- - Ten hardware triggers per CPU (triggers can be configured as a breakpoint or a watchpoint)

- Instruction trace on all CPUs

- Performance counters

- Runtime-configurable AXI bus monitors

- Monitor AXI commands to DDR

- Monitor an AXI port going into or out of the AMBA I/O AXI switch

- 32-bit fabric monitor

- SmartDebug

- · Dynamically monitor any two nets in the FPGA on two pins without changing the FPGA design

- · Read/write to FPGA flip-flops and memories

- · Halt clock trees, inspect logic tree

- · FPGA breakpoints

- SmartDebug integrated into processor debug transport layer—debug from a single tool chain

- Secure debug remotely over Ethernet (both the processor subsystem and the FPGA design)

- Processor I/O

- Two GigE MACs

- One USB 2.0 OTG

- MMC 5.1 SD/SDIO

- Two CAN 2.0 A and B

- Execute in place Quad SPI flash controller

- Five multi-mode UARTs

- Two SPI, two I<sup>2</sup>C

- RTC, GPIO

- Five watchdog timers

- Timers

- Processor to FPGA Interconnect

- Two 64-bit processor-fabric bidirectional AXI4 interfaces

- One 64-bit fabric-to-processor AXI4 interface

- One 32-bit processor-to-fabric APB interface

# FPGA Features

- · Up to 461k logic elements consisting of a 4-input look-up table (LUT) with a fractureable D-type flip-flop

- 20 Kb dual- or two-port large static random access memory (LSRAM) block with built-in SECDED

- 64 × 12 two-port µRAM block implemented as an array of latches

- 18 × 18 math block with a pre-adder, a 48-bit accumulator, and an optional 16-deep × 18 coefficient ROM

- Built-in µPROM, modifiable at program time and readable at run time for user data storage

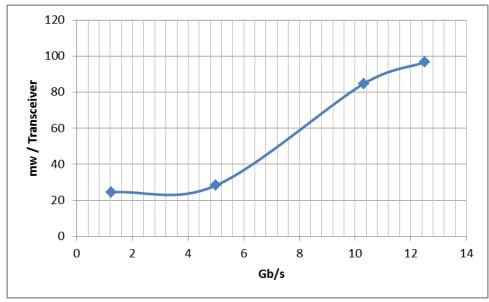

- High-speed serial connectivity with built-in, multi-gigabit, multi-protocol transceivers from 250 Mbps to 12.7 Gbps

- Integrated dual x4 PCIe Gen2 endpoint (EP) and root port (RP) designs

- High-speed I/O (HSIO) supporting up to 1600 Mbps DDR4, 1333 Mbps DDR3L, and 1333 Mbps LPDDR3/DDR3 memories with integrated I/O digital

- General-purpose I/O (GPIO) supporting 3.3 V, built-in CDR for serial gigabit Ethernet, 1067 Mbps DDR3, and 1250 Mbps LVDS I/O speed with integrated I/O digital logic

- Low-power, phase-locked loops (PLLs) and delay-locked loops (DLLs) for high precision and low jitter

• 1.0 V and 1.05 V operating modes

### **Low-Power Features**

- · Low device static power

- Low inrush current

- Low-power transceivers

# **Reliability Features**

- · FPGA configuration cells single-event upset (SEU) immune

- · Built-in SECDED and memory interleaving on FPGA fabric LSRAMs

- · SECDED on all processor memories

- Error signals trapped and exported to the FPGA fabric

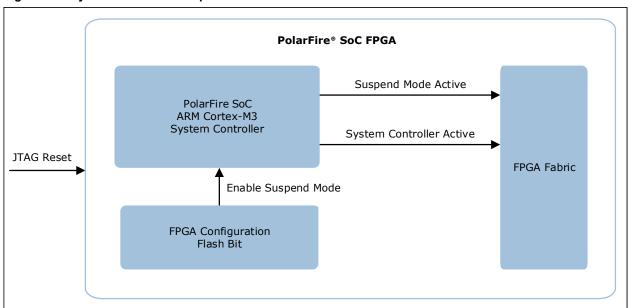

- · System controller suspend mode for safety-critical designs

### **Security Features**

- · Cryptography Research Incorporated (CRI)-patented differential power analysis (DPA) bitstream protection

- Integrated dual physically unclonable function (PUF)

- 56 KB of secure, non-volatile memory (sNVM)

- · Built-in tamper detectors and countermeasures

- Digest integrity check for FPGA, μPROM, sNVM, and eNVM

- · Side channel resistant Crypto co-processor in "S" data security devices

### SoftConsole Embedded IDE

- · Eclipse IDE

- · Firmware catalog for device drivers

# Libero® SoC Design Suite

- · Complete FPGA development environment

- · Includes Synplify Pro synthesis and Mentor ModelSim ME simulation

# PolarFire SoC MSS Configurator

- Generates a Libero MSS component for the FPGA design

- · Generates C data structures to initialize the memory map in the embedded environment

- Configures the following:

- MSS clocks

- Fabric interfaces

- IO banks

- DDR memories

- Debug features

### PolarFire SoC Icicle Kit

The Icicle kit is a low-cost development platform for the PolarFire SoC FPGA. It features:

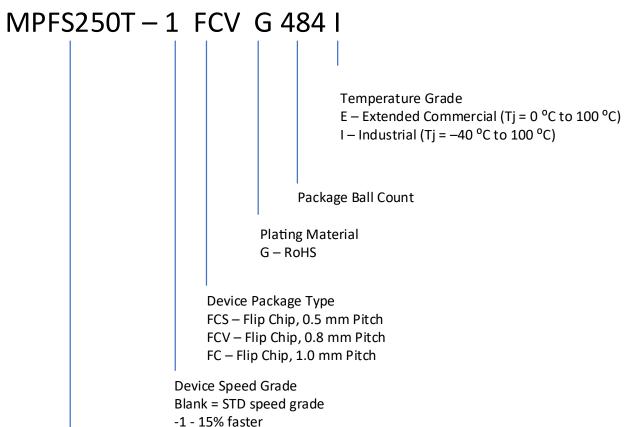

- PolarFire SoC FPGA (MPFS250T-FCVG484E)

- 2 GB LPDDR4 memory

- 8 GB eMMC

- · SD card interface

- 4 x 12.7 Gbps SERDES

DS60001656C-page 3

- PCle Gen2 rootport

- · 2 x Gigabit Ethernet

- Raspberry Pi IO

- · mikroBUS interface

# Mi-V Ecosystem

The Mi-V RISC-V ecosystem is a continuously expanding, comprehensive suite of tools and design resources developed by Microchip and numerous third parties to fully support RISC-V designs. The Mi-V ecosystem aims to increase adoption of RISC-V ISA and Microchip's PolarFire SoC FPGA and RISC-V soft CPUs.

# **Table of Contents**

| Ov  | erview             |                                             |    |

|-----|--------------------|---------------------------------------------|----|

|     | •                  | ubsystem Features                           |    |

| 1.  | Block Diagram      |                                             | 7  |

| 2.  | Product Family Ta  | able                                        | 8  |

| 3.  | Microprocessor S   | ubsystem                                    | 10 |

|     | 3.1. CPUs          |                                             | 10 |

|     | 3.2. Debug         |                                             | 14 |

|     | 3.3. Interrupts    |                                             | 15 |

|     | 3.4. Memory S      | ubsystems                                   | 16 |

|     | 3.5. Processor     | I/O                                         | 18 |

|     | 3.6. Processor-    | to-Fabric Interconnect                      | 23 |

|     | 3.7. Secure Bo     | ot                                          | 24 |

|     | 3.8. Peripheral    | Memory SECDED Reporting and Error Injection | 24 |

|     | 3.9. DMA Cont      | roller                                      | 24 |

| 4.  | Programmable Lo    | gic Subsystem                               | 25 |

|     | 4.1. Clock Man     | agement                                     | 25 |

|     | 4.2. Debug Pro     | be System                                   | 26 |

|     | 4.3. I/Os          |                                             | 26 |

|     | 4.4. Non-Volati    | e FPGA Fabric                               | 33 |

|     | 4.5. PCI Expre     | SS                                          | 36 |

| 5.  | System Controlle   | -                                           | 38 |

|     | 5.1. System Se     | rvices                                      | 38 |

|     | 5.2. Programm      | ing                                         | 38 |

| 6.  | Low Power          |                                             | 40 |

|     | 6.1. Non-Volati    | e Technology                                | 40 |

|     | 6.2. Lower Pov     | er "L" Devices                              | 40 |

|     | 6.3. Low-Powe      | r Transceiver Lane                          | 40 |

| 7.  | Reliability        |                                             | 41 |

|     | 7.1. FPGA Fab      | ric                                         | 41 |

|     | 7.2. LSRAM         |                                             | 41 |

|     | 7.3. μSRAM         |                                             | 41 |

|     | 7.4. Digests       |                                             | 41 |

|     | 7.5. System Co     | ntroller Suspend Mode                       | 41 |

| 8.  | Security           |                                             | 43 |

|     | 8.1. Design Se     | curity                                      | 43 |

| 9.  | PolarFire SoC De   | vice Offerings                              | 44 |

| 10. | Ordering Informati | ion                                         | 45 |

| 11. Revision History                      | 46 |

|-------------------------------------------|----|

| The Microchip Website                     | 47 |

| Product Change Notification Service       | 47 |

| Customer Support                          | 47 |

| Microchip Devices Code Protection Feature | 47 |

| Legal Notice                              | 48 |

| Trademarks                                | 48 |

| Quality Management System                 | 49 |

| Worldwide Sales and Service               | 50 |

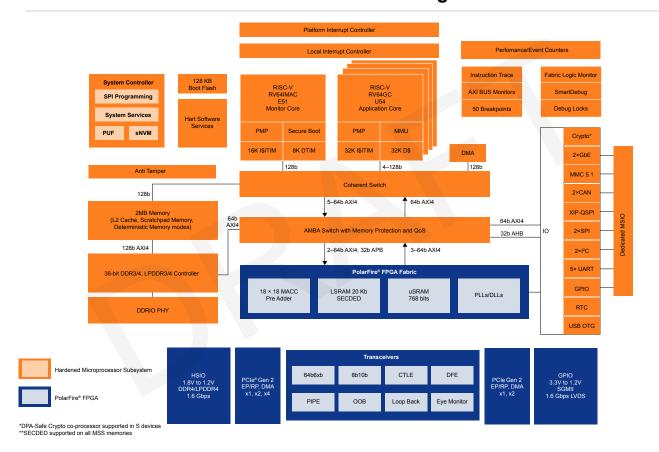

# 1. Block Diagram

The following illustration shows the functional blocks of PolarFire SoC.

Figure 1-1. Block Diagram

# PolarFire® SoC Block Diagram

Note: The microprocessor subsystem and the FPGA operate on the same power domain.

# 2. Product Family Table

The following table lists the product overview and packaging overview of the PolarFire SoC product family. The processor subsystem is common to all devices in the product family.

Table 2-1. PolarFire SoC Product Family

|                    | Features                                    | MPFS025T | MPFS095T | MPFS160T | MPFS250T | MPFS460T |

|--------------------|---------------------------------------------|----------|----------|----------|----------|----------|

| FPGA<br>fabric     | k Logic<br>Elements<br>(4LUT + DFF)         | 23       | 93       | 161      | 254      | 461      |

|                    | Math Blocks<br>(18x18 MACC)                 | 68       | 292      | 498      | 784      | 1420     |

|                    | LSRAM Blocks<br>(20 Kb)                     | 84       | 308      | 520      | 812      | 1460     |

|                    | uSRAM Blocks<br>(64x12)                     | 204      | 876      | 1494     | 2352     | 4260     |

|                    | Total RAM Mb                                | 1.8      | 6.7      | 11.3     | 17.6     | 31.6     |

|                    | uPROM KB                                    | 194      | 387      | 415      | 470      | 553      |

|                    | User DLLs/<br>PLLs                          | 8 each   |

| High-<br>speed I/O | 250 Mbps to<br>12.5 Gbps<br>SERDES<br>Lanes | 4        | 4        | 8        | 16       | 20       |

|                    | PCIe Gen2<br>End Points/<br>Root Ports      | 2        | 2        | 2        | 2        | 2        |

| Total<br>FPGA I/O  | HSIO+GPIO                                   | 108      | 276      | 312      | 372      | 468      |

| Total MSS<br>I/O   | MSS I/O                                     | 136      | 136      | 136      | 136      | 136      |

| MSS DDR<br>DB      | MSS DDR<br>Data Bus                         | 16       | 32       | 32       | 32       | 32       |

| conti     | continued                                  |                |               |               |                |                |  |  |  |

|-----------|--------------------------------------------|----------------|---------------|---------------|----------------|----------------|--|--|--|

|           | Features                                   | MPFS025T       | MPFS095T      | MPFS160T      | MPFS250T       | MPFS460T       |  |  |  |

| Packaging | Type/Size/<br>Pitch                        | MSS IO/HSIO/GI | PIO/XCVRs     |               |                |                |  |  |  |

|           | FCSG325<br>(11x11,<br>11x14.5*, 0.5<br>mm) | 102/32/48/2    | 102/32/48/2   | _             | _              | _              |  |  |  |

|           | FCSG536<br>(16x16, 0.5<br>mm)              | _              | 136/60/108/4  | 136/60/108/4  | 136/60/108/4   | _              |  |  |  |

|           | FCVG484<br>(19x19, 0.8<br>mm)              | 136/60/48/4    | 136/60/48/4   | 136/60/84/4   | 136/60/84/4    | _              |  |  |  |

|           | FCVG784<br>(23x23, 0.8<br>mm)              | _              | 136/144/132/4 | 136/144/168/8 | 136/144/180/8  | _              |  |  |  |

|           | FCG1152<br>(35x35, 1.0<br>mm)              | _              | _             | _             | 136/144/228/16 | 136/180/288/20 |  |  |  |

### Notes:

- 1. Devices in the same package type are pin compatible.

- 2. Extended Commercial and Industrial temperature grade devices are available in Green RoHS packages.

# 3. Microprocessor Subsystem

### 3.1 CPUs

### 3.1.1 E51 Monitor Core

The E51 monitor core is a 64-bit embedded RISC-V CPU, including an instruction fetch unit, an execution pipeline, and a data memory system. The monitor core supports the standard RISC-V RV64IMAC user-level instruction set, with machine and user privilege modes. The E51 monitor core typically runs a bare metal code called Hart Software Services.

Table 3-1. E51 Monitor Core

| Feature                        | Description                                           |

|--------------------------------|-------------------------------------------------------|

| ISA                            | RV64IMAC                                              |

| Instruction cache              | 16 KB two way                                         |

| Data tightly integrated memory | 8 KB                                                  |

| ECC support                    | Single-error correct, double-error detect on the DTIM |

| Privilege modes                | Machine (M), User (U)                                 |

### 3.1.1.1 Hart Software Services (HSS)

The Hart Software Services is a bare metal code that is built over the PolarFire SoC Hardware Abstraction Layer (HAL). The HSS functions as a zero stage bootloader for bare metal, RTOS, SMP Linux, and AMP systems. It also configures the MSS for peripheral selection, DDR configuration, L2 memory subsystem configuration, fabric interface controllers, clocks, IO configuration, physical memory protection, and so on, with the configuration set by the MSS configurator tool.

The HSS also enables inter-core communication as well as handles interfacing with the system controller for system services. The HSS is designed to run on the E51 core and is available as open source.

### 3.1.1.2 E51 Instruction Fetch Unit

The E51 instruction fetch unit consists of a two-way, 16 KB instruction cache that supports 64-byte cache lines. The access latency is one clock cycle. Writes to memory may be synchronized with the instruction fetch stream with a FENCE.I instruction. The branch predictor comprises a branch target buffer (BTB), which predicts the target of taken branches and jumps; a branch history table (BHT), which predicts the direction of conditional branches; and a return-address stack (RAS), which predicts the target of procedure returns. The BTB is configured to hold 40 entries. The RAS is configured to hold two entries. The BHT uses a gshare prediction scheme with 7 bits of global history to access an array of 128, two-bit saturating counters. The branch predictor has a one-cycle latency, so that correctly predicted control-flow instructions result in no penalty. The branch predictor can be turned off during device configuration to create deterministic systems.

# 3.1.1.3 E51 I-Cache Reconfiguration

The instruction cache can be partially reconfigured into an Instruction Tightly Integrated Memory (ITIM), which occupies a fixed address range in the memory map. ITIM provides high performance, predictable instruction delivery. Fetching an instruction from ITIM is as fast as an instruction-cache hit, with no possibility of a cache miss. ITIM can hold data as well as instructions, though loads and stores to ITIM are not as performant as loads and stores to DTIM. The instruction cache can be configured as ITIM for all ways except for 1 in units of cache lines (64 bytes). A single cache way must remain as an instruction cache. ITIM is allocated simply by storing to it. A store to the nth byte of the ITIM memory map reallocates the first n+1 bytes of instruction cache as ITIM, rounded up to the next cache line. ITIM is deallocated by storing zero to the first byte after the ITIM region. The deallocated ITIM space is automatically returned to the instruction cache. For determinism, software must clear the contents of ITIM after allocating it. It is unpredictable whether ITIM contents are preserved between deallocation and allocation. ITIM is typically used for reduced latency requirements like for an ISR.

#### 3.1.1.4 **E51 Execution Pipeline**

The E51 execution unit is a single-issue, in-order pipeline. The pipeline comprises five stages: instruction fetch, instruction decode and register fetch, execute, data memory access, and register writeback. The pipeline has a peak execution rate of one instruction per clock cycle. It is fully bypassed, so that most instructions have an apparent one-cycle result latency. There are several exceptions:

- LD and LW have a two-cycle result latency, assuming a cache hit.

- LH, LHU, LB, and LBU have a three-cycle result latency, assuming a cache hit.

- · MUL, MULW, MULH, MULHU, MULHSU, DIV, DIVU, REM, REMU, DIVW, DIVUW, REMW, and REMUW have between a 2-cycle and 66-cycle result latency, depending on operand values.

- CSR reads have a three-cycle result latency.

The pipeline only interlocks on read-after-write and write-after-write hazards, so instructions may be scheduled to avoid stalls.

The iterative multiplier is configured to produce 16 bits per cycle with an early-out option. The iterative divider has latency of between three and 66 cycles and an early-out option.

Branch and jump instructions transfer control from the memory access pipeline stage. Correctly predicted branches and jumps incur no penalty, whereas mispredicted branches and jumps incur a three-cycle penalty. Most CSR writes result in a pipeline flush, a five-cycle penalty.

#### 3.1.1.5 **E51 Data Memory System**

The E51 data memory system consists of 8 KB Data Tightly-Integrated Memory (DTIM). The access latency is two clock cycles for full words and three clock cycles for smaller quantities. Misaligned accesses are not supported in hardware and result in a trap to support software emulation. Stores are pipelined and commit on cycles where the data memory system is otherwise idle. Loads to addresses currently in the store pipeline result in a five-cycle penalty.

#### 3.1.1.6 **E51 Memory Error Correction**

The E51 DTIM implements single-error correcting, double-error detecting (SECDEC) error correcting code (ECC). The granularity at which this protection is applied (the codeword) is 32 bits (with an ECC overhead of 7 bits per codeword).

### 3.1.1.6.1 E51 Memory Single-Bit Errors

When a single bit error is detected in the E51 L1 memory used as a cache, the error is corrected and the cache line is flushed consequently writing to the next level in the memory hierarchy (L2 cache). When a single bit error is detected in the the E51 L1 memory configured as an ITIM, the error is corrected and written back to the ITIM location.

### 3.1.1.6.2 E51 Memory Error Reporting

ECC events are reported by the Bus-Error Unit (BEU) for a given core. The BEU can be configured to generate interrupts either globally to the Platform Level Interrupt Controller (PLIC), or locally to the specific part where the ECC event occurred. When BEU interrupts are enabled, software can then be used to monitor and count ECC events. In order to detect uncorrectable ECC errors in the L1 memory system, interrupts must be enabled in the BEU. Specifically, to halt execution of a core when an uncorrectable instruction is detected, the BEU must be configured to generate a local interrupt. Uncorrectable ECC errors in the L1 system are also reported to the FPGA fabric as a HALT CPU n signal, where n indicates the core (0= E51 core).

#### 3.1.1.7 **E51 Local Interrupts**

The E51 supports up to 48 local interrupt sources routed directly to the core. The local interrupts are sourced from the FPGA fabric. The E51 core receives the same 48 interrupt sources from the FPGA fabric as do the U54 cores.

#### 3.1.2 **U54 Application Cores**

The U54 application core is 64-bit embedded RISC-V microprocessor, including an instruction fetch unit, an execution pipeline, and a data memory system. The application core supports the standard RISC-V RV64IMAFDC (RV64GC) user-level instruction set, with machine, supervisor, and user privilege modes. The U54s may run a rich operating system such as Linux, an RTOS or a bare metal application.

Overview DS60001656C-page 11 © 2021 Microchip Technology Inc.

Table 3-2. U54 Application Cores

| Feature                                      | Description                                                                                                                              |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| ISA                                          | RV64IMAFDC (RV64GC)                                                                                                                      |

| Instruction cache                            | 32 KB, 8-way                                                                                                                             |

| Instruction tightly integrated memory (ITIM) | Maximum of 28 KB                                                                                                                         |

| Data cache                                   | 32 KB, 8-way                                                                                                                             |

| ECC support                                  | Single-error correct, double-error detect on the instruction cache/ITIM and data cache                                                   |

| Virtual memory support                       | The U54 has support for Sv39 virtual memory support with a 39-bit virtual address space, 38-bit physical address space, and 32-entry TLB |

| Privileged modes                             | Machine (M), Supervisor (S), User (U)                                                                                                    |

# 3.1.2.1 U54 Instruction Memory System

The instruction memory system consists of a dedicated 32 KB, 8-way, set-associative, Virtually Indexed Physically Tagged (VIPT) instruction cache. The access latency of all blocks in the instruction memory system is one clock cycle. The instruction cache is not kept coherent with the rest of the platform memory system. Writes to instruction memory must be synchronized with the instruction fetch stream by executing a FENCE. I instruction. The instruction cache has a line size of 64 bytes and a cache line fill will trigger a burst access outside of the PolarFire SoC CPU core complex. The core will cache instructions from executable addresses, with the exception of the ITIM. Trying to execute an instruction from a non-executable address will result in a synchronous trap.

### 3.1.2.2 U54 I-Cache Reconfiguration

The instruction cache can be partially reconfigured into an Instruction Tightly Integrated Memory (ITIM), which occupies a fixed address range in the memory map. ITIM provides high-performance, predictable instruction delivery. Fetching an instruction from ITIM is as fast as an instruction-cache hit, with no possibility of a cache miss. ITIM can hold data as well as instructions, though loads and stores to ITIM are not as performant as loads and stores to DTIM. The instruction cache can be configured as ITIM for all ways except for 1 in units of cache lines (64 bytes). A single-instruction cache way must remain as an instruction cache. ITIM is allocated simply by storing to it. A store to the nth byte of the ITIM memory map reallocates the first n+1 bytes of instruction cache as ITIM, rounded up to the next cache line. ITIM is deallocated by storing zero to the first byte after the ITIM region. The deallocated ITIM space is automatically returned to the instruction cache. For determinism, software must clear the contents of ITIM after allocating it. It is unpredictable whether ITIM contents are preserved between deallocation and allocation.

#### 3.1.2.3 U54 Instruction Fetch Unit

The U54 instruction fetch unit contains branch prediction hardware to improve performance of the processor core. The branch predictor comprises a 40-entry branch target buffer (BTB) that predicts the target of taken branches, a 128-entry branch history table (BHT) that predicts the direction of conditional branches, and a 2-entry return-address stack (RAS) that predicts the target of procedure returns. The branch predictor has a one-cycle latency, so that correctly predicted control-flow instructions result in no penalty. Mispredicted control-flow instructions incur a three-cycle penalty. The branch predictor can be turned off during device configuration to create deterministic systems. The U54 implements the standard Compressed (C) extension to the RISC-V architecture which allows for 16-bit RISC-V instructions.

### 3.1.2.4 U54 Execution Pipeline

The U54 execution unit is a single-issue, in-order pipeline. The pipeline comprises five stages: instruction fetch, instruction decode and register fetch, execute, data memory access, and register writeback.

The pipeline has a peak execution rate of one instruction per clock cycle, and is fully bypassed so that most instructions have a one-cycle result latency. There are several exceptions:

- · LW has a two-cycle result latency, assuming a cache hit.

- LH, LHU, LB, and LBU have a three-cycle result latency, assuming a cache hit.

- · CSR reads have a three-cycle result latency.

- MUL, MULH, MULHU, and MULHSU have a 5-cycle result latency.

- DIV, DIVU, REM, and REMU have between a 2-cycle and 33-cycle result latency, depending on the operand values.

The pipeline only interlocks on read-after-write and write-after-write hazards, so instructions may be scheduled to avoid stalls.

The U54 implements the standard Multiply (M) extension to the RISC-V architecture for integer multiplication and division. The U54 has a 16-bit per cycle hardware multiply and a 4-bit per cycle hardware divide.

Branch and jump instructions transfer control from the memory access pipeline stage. Correctly predicted branches and jumps incur no penalty, whereas mispredicted branches and jumps incur a three-cycle penalty.

Most CSR writes result in a pipeline flush with a five-cycle penalty.

#### 3.1.2.5 **U54 Data Memory System**

The U54 data memory system has a 8-way set-associative 32 KB write-back data cache with 64 B cache lines. The data cache is Virtually Indexed Physically Tagged (VIPT). Access latency is two clock cycles for words and double-words, and three clock cycles for smaller quantities. Misaligned accesses are not supported in hardware and result in a trap to support software emulation. The data caches are kept coherent with a directory-based cache coherence manager, which resides in the outer L2 cache. Stores are pipelined and commit on cycles where the data memory system is otherwise idle. Loads to addresses currently in the store pipeline result in a five-cycle penalty.

#### 3.1.2.6 **U54 Atomic Operations**

The U54 core supports the RISC-V standard Atomic (A) extension on regions of the memory map denoted by the attribute A. Atomic memory operations to regions that do not support them generate an access exception precisely at the core. The load-reserved and store-conditional instructions are only supported on cached regions; therefore, generate an access exception on DTIM and other uncached memory regions. See The RISC-V Instruction Set Manual, Volume I: User-Level ISA, Version 2.1 [1] for more information on the instructions added by this extension.

#### 3.1.2.7 **U54 Floating Point Unit (FPU)**

The U54 FPU provides full hardware support for the IEEE® 754-2008 floating-point standard for 32-bit, singleprecision and 64-bit, double-precision arithmetic. The FPU includes a fully pipelined fused-multiply-add unit and an iterative divide and square-root unit, magnitude comparators, and float-to-integer conversion units, all with full hardware support for subnormals and all IEEE default values.

#### 3.1.2.8 **U54 Virtual Memory Support**

The U54 has support for virtual memory through the use of a Memory Management Unit (MMU). The MMU supports the Bare and Sv39 modes as described in the RISC-V Instruction Set Manual, Volume II: Privileged Architecture, Version 1.10 [2]. The U54 MMU has a 39-bit virtual address space mapped to a 38-bit physical address space. A hardware page-table walker refills the address translation caches. Both instruction and data address translation caches are fully associative, and have 32 entries. The MMU supports 2 MB megapages and 1 GB gigapages to reduce translation overheads for large contiguous regions of virtual and physical address space. Note that the U54 does not automatically set the Accessed (A) and Dirty (D) bits in a Sv39 Page Table Entry (PTE). Instead, the U54 MMU will raise a page fault exception for a read to a page with PTE.A=0 or a write to a page with PTE.D=0.

#### 3.1.2.9 **U54 Local Interrupts**

Each U54 supports up to 48 local interrupt sources that are routed directly to the core. The local interrupts are sourced from the FPGA fabric. Each U54 core receives the same 48 interrupt sources from the FPGA fabric.

### 3.1.2.10 U54 Memory Error Correction

The U54 ITIM and DTIM implement single-error correcting, double-error detecting (SECDEC) error correcting code (ECC). The granularity at which this protection is applied (the codeword) is 32-bit (with an ECC overhead of 7 bits per codeword).

## 3.1.2.10.1 U54 Memory Single-Bit Errors

When a single bit error is detected in the U54 L1 memory used as a cache, the error is corrected and the cache line is flushed consequently writing to the next level in the memory hierarchy (L2 cache). When a single bit error is detected in the the U54 L1 memory configured as an ITIM, the error is corrected and written back to the ITIM location.

Overview DS60001656C-page 13 © 2021 Microchip Technology Inc.

### 3.1.2.10.2 U54 Memory Error Reporting

ECC events are reported by the Bus-Error Unit (BEU) for a given core. The BEU can be configured to generate interrupts either globally to the Platform Level Interrupt Controller (PLIC), or locally to the specific part where the ECC event occurred. When BEU interrupts are enabled, software can then be used to monitor and count ECC events. In order to detect uncorrectable ECC errors in the L1 memory system, interrupts must be enabled in the BEU. Specifically, to halt execution of a core when an uncorrectable instruction is detected, the BEU must be configured to generate a local interrupt. Uncorrectable ECC errors in the L1 system are also reported to the FPGA fabric as a HALT\_CPU\_n signal, where n = 0—5 and n = 1 through 5 = 1 the U54 application cores.

# 3.1.3 Physical Memory Protection

Each CPU in PolarFire SoC includes a physical memory protection (PMP) unit compliant with the *RISC-V Instruction Set Manual, Volume II: Privileged Architecture, Version 1.10.* The PMP unit can be used to set memory access privileges (read, write, execute) for specified memory regions. Each PMP supports 16 regions with a minimum region size of 4 bytes.

### 3.1.3.1 Functional Description

PolarFire SoC includes a Physical Memory Protection (PMP) unit, which can be used to restrict access to memory and isolate processes from each other. The PMP unit has 16 regions and a minimum granularity of 4 bytes. It is permitted to have overlapping regions. The PolarFire SoC PMP unit implements the architecturally defined pmpcfgX CSRs pmpcfg0 and pmpcfg2 supporting 16 regions. pmpcg1 and pmpcfg3 are implemented but hardwired to zero.

### 3.1.3.2 Region Locking

The PMP allows for region locking whereby once a region is locked, further writes to the configuration and address registers are ignored. Locked PMP entries may only be unlocked with a system reset. A region may be locked by setting the L bit in the pmpicfg register. In addition to locking the PMP entry, the L bit indicates whether the R/W/X permissions are enforced on M-Mode accesses. When the L bit is set, these permissions are enforced for all privilege modes. When L bit is clear, the R/W/X restrictions apply only to U-mode.

# 3.2 Debug

# 3.2.1 CPU Debug

Each CPU has up to ten breakpoint registers. Breakpoints can halt the respective CPU under the following conditions.

- · Address match on Load

- · Address match on Store

- · Address match on Instruction Fetch

- · Address match on User mode

- · Address match on Supervisor mode

- · Address match on Machine mode

A successful match on address can generate an exception or place the machine into debug mode.

# 3.2.2 Trace

PolarFire SoC includes an Instruction trace interface module. For each core, the following can be captured when an instruction is retired or trapped and trace is enabled.

- · The address of the instruction

- The instruction

- · Privileged mode during execution

- · Trap or retired indication

- Interrupt or exception indication

- Exception cause

- Exception data

© 2021 Microchip Technology Inc. Overview DS60001656C-page 14

PolarFire SoC uses UltraSoC debug infrastructure to compress and transport debug information over a variety of ports.

- Ethernet

- JTAG

- · FPGA fabric

### 3.2.3 AXI Bus Monitors

There are two AXI bus monitors within the MSS that allow, at run time, observation of AXI transactions. They can be used for debugging, reporting diagnostics, performance profiling, bare metal security, and other applications. For example, the AXI monitors can passively filter on specific addresses, which master is performing the R/W, without affecting traffic at run time.

The AXI-64 bus monitor is configured to provide full address and data trace on the slave side of the AXI switch.

The AXI-128 bus monitor is configured to provide full address trace on the AXI4-128 bus connecting the MSS L2 interface to the DDR memory. Data trace is not supported in this case. This allows the ability to trace the effectiveness of the cache and DDR response rates

### 3.2.4 Fabric Monitor

PolarFire SoC incorporates a FPGA Fabric Monitor within the MSS. 32 General purpose inputs to the MSS from the FPGA are available for monitoring FPGA logic. Eight general purpose outputs can be driven into the FPGA fabric to control either users logic or debug instrumentation. The Fabric Monitor pipes data over the debug transport layer and out through one of the defined debug ports, most commonly Ethernet.

### 3.2.5 SmartDebug

Two specified user I/Os is configured (at design capture stage) as either two single-ended live probes or one differential live probe. These live probes provide read access to any register in the FPGA fabric to the output pipeline registers in the LSRAMs and to all the registers in the math block in real-time without having to re-instrument the code. A snapshot of all internal probe points is created and read out asynchronously. The live-probe feature is like a two-channel oscilloscope, whose two channels can be routed out to I/Os for external observation, and to internal ports to allow fabric design observation. Selecting different probe points within the device occurs dynamically through commands over the JTAG port using SmartDebug. Reprogramming of the device is not needed.

The following are included in the debug probe system.

- Active probe allows dynamic asynchronous read and write to a flip-flop or a probe point. This enables quick

internal observation of the logic output or experimentation on how the logic is affected by writing to a probe

point.

- Memory debug allows dynamic asynchronous read and write to a μSRAM or a large SRAM block to quickly verify if the content of the memory is changing as expected.

- Probe insertion allows routing of nodes or debug points in the FPGA design externally through unused I/Os. An

oscilloscope/logic analyzer can be attached to monitor them as live signals.

# 3.3 Interrupts

Each hardware thread (hart) in PolarFire SoC has support for the following interrupts: local (including software and timer) and global. Local interrupts are signaled directly to an individual hart with a dedicated interrupt value. This allows for reduced interrupt latency as there is no arbitration required to determine which hart will service a given request, nor additional memory accesses required to determine the cause of the interrupt. Software and timer interrupts are local interrupts generated by the Core Local Interruptor (CLINT). Global interrupts by contrast, are routed through a Platform-Level Interrupt Controller (PLIC), which can direct interrupts to any hart in the system via the external interrupt. Decoupling global interrupts from the hart(s) allows the design of the PLIC to be tailored to the platform, permitting a broad range of attributes like the number of interrupts and the prioritization and routing schemes. By default all interrupts are handled in machine mode. The U54s, which support supervisor mode, can selectively delegate interrupts to supervisor mode.

© 2021 Microchip Technology Inc. Overview DS60001656C-page 15

Figure 3-1. Interrupts E51 **PLIC** Bus Ern Hart 0 -Global Interrupts (169)-U54 Hart 1 CLINT U54 Hart 4

For more information on interrupts, see the PolarFire SoC MSS Technical Reference Manual.

#### 3.4 **Memory Subsystems**

PolarFire SoC contains an on-chip 128 KB embedded non-volatile memory (eNVM) for user code, a flexible L2 memory subsystem, and an integrated DDR memory controller.

#### 3.4.1 **L2 Memory Subsystem**

The PolarFire SoC Level 2 Cache Controller is used to provide access to fast copies of memory for masters in a core complex. The Level 2 Cache Controller also acts as a directory-based coherency manager. The Level 2 Cache Controller offers extensive flexibility as it allows for several features in addition to the Level 2 Cache functionality, such as memory-mapped access to L2 Cache RAM for disabled cache ways, scratchpad functionality, way masking and locking, and ECC support with error tracking statistics, error injection, and interrupt signaling capabilities.

The L2 Cache Controller consists of 4 banks where each bank contains 512 sets of 16 ways, and each way contains a 64-byte block. This subdivision into banks helps facilitate increased available bandwidth between CPU masters and the L2 Cache, as each bank has its own 128-bit inner port. As such, multiple requests to different banks may proceed in parallel. The outer port of the L2 Cache Controller is a 128-bit port shared among all banks and is connected to the DDR controller.

When cache ways are disabled, they are addressable in the L2 Loosely Integrated Memory (L2LIM) address space as described in the PolarFire SoC MSS Technical Reference Manual. Fetching instructions or data from the L2-LIM provides deterministic behavior equivalent to an L2 cache hit, with no possibility of a cache miss. Accesses to L2-LIM are always given priority over cache way accesses which target the same L2 cache bank. Out of reset all ways, except for way 0, are disabled. Cache ways can be enabled by writing to specific control registers. Once a cache way is enabled, it can not be disabled unless the CPU complex is reset. The highest numbered L2 cache way is mapped to the lowest L2-LIM address space, and way 1 occupying the highest L2-LIM address range. As L2 cache ways are enabled, the size of the L2-LIM address space shrinks.

The L2 Cache Controller has a dedicated scratchpad address region that allows for allocation into the cache using an address range which is not memory backed. This address region is denoted as the L2 Zero Device in the memory map. Writes to the scratchpad region will allocate into cache ways that are enabled and not masked. Care must be taken with the scratchpad, however, as there is no memory backing this address space. Cache evictions from addresses in the scratchpad will result in data loss. The main advantage of the L2 Scratchpad over the L2-LIM is

that it is a cacheable region allowing for data stored to the scratchpad to also be cached in a master's L1 data cache resulting in faster access.

#### 3.4.1.1 **DDR Memory Controller**

The hardened, 32-bit DDR memory controller supports the following features:

- DDR4, LPDDR4, DDR3, and LPDDR3 memory support

- Dual Rank support for dual die packages

- Max rate support 1600 Mbps

- DDR memory test feature

- Reorder queue to optimize DDR performance

- Two AXI interfaces

- 128-bit from CPU L2 Cache

- 64-bit from central AXI switch

- 32 outstanding transactions per AXI interface

- An integrated Clock Domain Crossing (CDC) circuit allowing the DDR controller clock to be independent of the CPU clock

- A dedicated PLL for DDR clock generation

It can support up to 8 GB of external DDR4 memory and 4 GB of DDR3 memory. SECDED capability is also provided when configured to a 36-bit bus width, as listed in the following table.

Table 3-3. DDR Memory Controller

| Configuration        | Active Pads | Lane 0 | Lane 1 | Lane 2 | Lane 3 | Lane 4 <sup>1</sup> |

|----------------------|-------------|--------|--------|--------|--------|---------------------|

| 5x8 DDR with SECDED  | 36          | DDRx8  | DDRx8  | DDRx8  | DDRx8  | DDRx8 (4 used)      |

| 4x8 DDR              | 32          | DDRx8  | DDRx8  | DDRx8  | DDRx8  | Not used            |

| 3x16 DDR with SECDED | 36          | DDRx16 |        | DDRx16 |        | DDRx16 (4 used)     |

| 2x16 DDR             | 32          | DDRx16 |        | DDRx16 |        | Not used            |

| 3x16 DDR with SECDED | 18          | DDRx8  | DDRx8  | _      | _      | DDRx8 (2 used)      |

| 2x16 DDR             | 16          | DDRx8  | DDRx8  | _      | _      | _                   |

| 1x16 DDR with SECDED | 18          | DDRx16 |        | _      | _      | DDRx16 (2 used)     |

| 1x16 DDR             | 16          | DDRx16 |        | _      | _      | _                   |

| 1x32 DDR             | 32          | DDRx32 |        |        |        | _                   |

### Note:

Lane 4 is only 4 bits wide, the upper data bits on the DDR memory are not connected. 1.

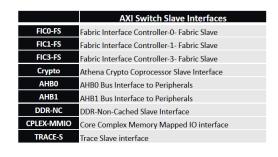

#### 3.4.1.2 **Processor Interconnect**

There are two interconnect switches built into the MSS. First, there is a fully populated coherent switch that manages coherence through the memory subsystems and provides a deterministic data path to the L2 memory subsystem when it is configured as a loosely integrated memory. Additionally, a central AMBA I/O switch manages the interconnect between the CPU complex, the peripheral I/O space, the hardened DDR memory controller, and the FPGA fabric. The AMBA switch also includes Quality of Service (QoS) features. The QoS feature is essentially a 4-bit value denoting priority for the data path. The central I/O switch is partially connected and supports 15 masters with nine slaves. The AMBA switch also contains a Memory Protection Unit (MPU) scheme that mimics the Physical Memory Protection (PMP) scheme defined in the RISC-V Privileged Specification. Specifically, the bus masters listed in the following table pass through the AMBA MPU. PMP region address granularity start at 4096 and increase by powers of two. Regions can be defined to support execution, read or write. An additional lock bit can be set on each register that prevents further modification to the MPU protection scheme until the next power on reset.

Overview DS60001656C-page 17 © 2021 Microchip Technology Inc.

Figure 3-2. AXI Switch Connectivity

|            | FICO-FM | FIC1-FM | FIC2-FM | Crypto | GEM0 | GEM1 | USB | MMC | SCB | CPLEX-D0 | CPLEX-D1 | CPLEX-F0 | CPLEX-F1 | CPLEX-NC | TRACE-M |

|------------|---------|---------|---------|--------|------|------|-----|-----|-----|----------|----------|----------|----------|----------|---------|

| FICO-FS    | Υ       | Υ       | N       | Υ      | Υ    | Υ    | Υ   | Υ   | Υ   | N        | N        | Υ        | N        | N        | Υ       |

| FIC1-FS    | Υ       | Υ       | N       | Υ      | Υ    | Υ    | Υ   | Υ   | Υ   | N        | N        | N        | Υ        | N        | Υ       |

| FIC3-FS    | Υ       | Υ       | N       | Υ      | N    | N    | N   | N   | Υ   | Υ        | N        | N        | N        | N        | N       |

| Crypto     | Υ       | Υ       | N       | N      | Υ    | Υ    | Υ   | Υ   | Υ   | Υ        | N        | N        | N        | N        | N       |

| AHB0       | Υ       | Υ       | N       | Y      | N    | N    | N   | N   | Υ   | Υ        | N        | N        | N        | N        | N       |

| AHB1       | Υ       | Υ       | N       | N      | N    | N    | N   | N   | Υ   | N        | Υ        | N        | N        | N        | N       |

| DDR-NC     | Υ       | Υ       | Υ       | Υ      | Υ    | Υ    | Υ   | Υ   | Υ   | N        | N        | N        | N        | Υ        | Υ       |

| CPLEX-MMIO | Υ       | Υ       | Υ       | Υ      | Υ    | Υ    | Υ   | Υ   | Υ   | N        | N        | N        | N        | N        | N       |

| TRACE-S    | N       | N       | N       | N      | N    | N    | N   | N   | Υ   | Υ        | N        | N        | N        | N        | N       |

| Key      | AXI Switch Master Interfaces                 |

|----------|----------------------------------------------|

| FICO-FM  | Fabric Interface Controller-0- Fabric Master |

| FIC1-FM  | Fabric Interface Controller-1- Fabric Master |

| FIC2-FM  | Fabric Interface Controller-2- Fabric Master |

| Crypto   | Athena Crypto Coprocessor                    |

| GEM0     | Gigabit Ethernet MAC 0                       |

| GEM1     | Gigabit Ethernet MAC 1                       |

| USB      | USB                                          |

| MMC      | MMC                                          |

| SCB      | System Controller                            |

| CPLEX-D0 | Core Complex-D0 Interface                    |

| CPLEX-D1 | Core Complex-D1 Interface                    |

| CPLEX-F0 | Core Complex-F0 Interface                    |

| CPLEX-F1 | Core Complex-F1 Interface                    |

| CPLEX-NC | Core Complex - Non-Cached Interface          |

| TRACE-M  | Trace Master Interface                       |

|          |                                              |

Table 3-4. Processor Interconnect

| Master     | PMP Region Count |

|------------|------------------|

| FIC_0      | 16               |

| FIC_1      | 16               |

| FIC_2      | 8                |

| Crytpo     | 4                |

| Ethernet_0 | 8                |

| Ethernet_1 | 8                |

| USB        | 4                |

| MMC        | 4                |

| DRI        | 8                |

| Trace      | 2                |

# 3.5 Processor I/O

The PolarFire SoC Microprocessor Subsystem supports 38 general-purpose IOs called as MSS IOs apart from DDR IOs, SGMII IO for Ethernet MACs, and IOs for reference clocks.

The MSS IOs support the following peripherals.

- · eMMC/SD/SDIO

- USB

- QSPI-XIP

- Two CAN

- Five UARTs

- Two SPI

- Two I2C

- MSS GPIO

System registers are available to select the signals connected to different IOs.

All these IOs are bonded out to pins in all PolarFire SoC packages.

For more details on MSS IOs, see the PolarFire SoC MSS Technical Reference Manual.

### 3.5.1 Gigabit Ethernet MAC

PolarFire SoC contains two identical Gigabit Ethernet MACs (GEM) integrated into the MSS. Each MAC can contain a maximum frame length of 10,240 bytes that are SECDED protected. Additionally, the GEM supports a built-in packet buffer DMA. Each GEM supports the following IEEE® 802 standards:

- IEEE 802.3br Frame Pre-Emption (or Interspersing Express Traffic)

- IEEE 802.1Qci Receive (Ingress) Traffic Policing

- IEEE 802.1Qbb Priority-Based Flow Control

- IEEE 802.1Q VLAN Tagging with Recognition of Incoming VLAN and Priority Tagged Frames

- IEEE 802.1AS

- IEEE 802.1Qav

- IEEE 802.1Qbv

- IEEE 1588-2002 (v1), IEEE 1588-2008 (v1 and v2)

- IEEE 802.1CB Frame Redundancy and Elimination

#### 3.5.1.1 PHY Interfaces

Each GEM is configured to simultaneously support TBI and GMII/MII modes. When using TBI, the PCS block of the MAC is used, but not as an IEEE802.3X interface to a transceiver, but rather, is fed into a dedicated MSS SERDES block and from there, interfaces to a PHY. This serialized interface between MAC and PHY is known as SGMII and is part of the MSS. In SGMII mode, the PCS interface and the link speed auto-negotiation blocks are re-purposed from their 802.3X function and are instead used to convey control information related to the MAC-PHY interface.

# 3.5.1.1.1 Direct SGMII I/O

The following functionality provides an SGMII interface from the GEM to the built-in MSS SGMII PHY:

- Clock Domain Recovery (CDR) of received 125 MHz clock

- · Serializing/De-serializing

- PLL for synthesis of a 125 MHz transmit clock

- I/O buffers (four I/Os per MAC instance) allowing for differential transmit and receive data pairs

Note: It is not possible to support the SyncE protocol when using the direct MSS SGMII interface.

### 3.5.1.1.2 GMII/MII To FPGA Fabric

A GMII/MII interface is provided between each MAC and the FPGA fabric to provide flexibility. In particular, it allows:

Connecting to a FPGA fabric transceiver channel to provide an SGMII interface. Note that in this case, the

transceiver would be configured to perform 8b10b encoding/decoding in its PCS. This particular approach to

implementing an SGMII interface differs from the direct hard SGMII interface of the MSS in that it allows support

of the SyncE protocol, which is often used in conjunction with IEEE 1588.

### 3.5.1.1.3 PHY Management

Each MAC has an MDC output and an MDIO input and output port, which may be brought out separately for each MAC instance within the MSS either to MSSIO or to the FPGA fabric. If desired, however, the user could bring out only one management interface (and not use the second), as it is possible to control multiple PHYs using the one interface (if hardware separation is not required).

# 3.5.1.2 MSS Receive Filtering

## 3.5.1.2.1 Internal Filtering

The GEM is configured to have four internal specific address filters configured. Each filter can be configured to contain a MAC address, which can be specified to be compared against the source address (SA) or destination address (DA) of each received frame. There is also a mask field to allow certain bytes of the address to be excluded

© 2021 Microchip Technology Inc. Overview DS60001656C-page 19

in the comparison. If the filtering matches for a specific frame, then it is passed on to the DMA memory. Otherwise the frame is dropped. Frames may also be filtered using the Type ID field for matching. There are four Type ID registers in the internal register space and these may be enabled individually. Hashing of the received frame's DA may be configured, as described in the PolarFire SoC MSS Technical Reference Manual.

#### 3.5.1.2.2 External Filtering

To allow for more sophisticated matching of incoming frames, based on more than just addresses, for example, an external filtering interface is present. As a frame is received, the MAC parses the frame and determines what field is currently present. A strobe signal is provided to allow latching of each field in the fabric. Customized (combinational) matching circuitry can then analyze whether or not it is interested in the particular frame (filtering use case) or what receive priority queue to put the frame in (prioritizing use case).

### 3.5.2 MMC 5.1/SD/SDIO/eMMC

PolarFire SoC contains one MMC5.1 compliant peripheral and PHY. The controller interfaces to MSS I/O through the IOMUXs to MSSIO exclusively. PolarFire SoC MSS I/Os do not support the dynamic voltage scaling of some SD cards, external voltage level translators should be used if required. The following eMMC/SD card standards are supported in PolarFire SoC. The SDIO/eMMC interface supports its own DMA controllers for data transfers. The DMA controllers support SDMA and ADMA2 modes.

### 3.5.2.1 SD Card Standards

- · Default Speed (DS)

- · High Speed (HS)

- UHS-I SDR12

- UHS-I SDR25

- UHS-I SDR50

- UHS-I SDR104

- UHS-I DDR50

### 3.5.2.2 eMMC Standards

- Standard Speed

- High Speed

- DDR52

- HS200

- HS400

- HS400 Enhanced Strobe

### 3.5.3 USB 2.0 OTG

PolarFire SoC includes a USB 2.0 OTG-compliant core with an ULPI interface to the IOMUX, and then on to dedicated MSS I/O. The USB core supports the following features:

- Operates either as the function controller of a high/full-speed USB peripheral or as the host/peripheral in point-to-point or multi-point communications with other USB functions

- Complies with the USB 2.0 standard for high-speed (480 Mbps) functions and with the on-the-go supplement to the USB 2.0 specification

- Supports OTG communications with one or more high-, full-, or low-speed device

- · Supports Session Request Protocol (SRP) and Host Negotiation Protocol (HNP)

- · Supports suspend and resume signaling

- · Supports Link Power Management

- · Offers dynamic allocation of endpoints to maximize number of devices supported

- Number of Tx endpoints: 4 (plus control endpoint)

- Number of Rx endpoints: 4 (plus control endpoint)

- Multipoint capabilities supported

- · Software connect/disconnect feature enabled

- · High bandwidth support for ISO enabled endpoints

© 2021 Microchip Technology Inc. Overview DS60001656C-page 20

- · Hardware-selectable option for 8-bit/4-bit LPI interface

- Vendor control and status register enabled with width of 4 and 8, respectively

- Number of DMA channels: 4

- Dynamic FIFO support allows dynamic allocation of buffer depth per enabled endpoint

#### 3.5.4 **User Crypto**

PolarFire SoC embeds an Athena TeraFire F5200B side channel resistant crypto coprocessor and is available on "S" data security devices. For the list of devices that support data security, see Table 9-1. PolarFire SoC Offerings. The user crypto core can be mapped between the MSS and the FPGA fabric via a hardware based handshaking mechanism. The crypto core also supports the F5200B streaming interface directly into the fabric. Internal memories in the Athena core are SECDED protected.

#### 3.5.4.1 TeraFire EXP-F5200B Supported Protocols Features

- TRNG SP800-90A CTR DRBG-2565; SP800-90B (draft) NRBG

- AES 128/192/256 key lengths E/D (ECB, CBC, CTR, OFB, CFB, GCM, KeyWrap)

- SHA-1/224/256/384/512

- HMAC-SHA-1/224/256/384/512; GMAC-AES; CMAC-AES

- SHA-256 Key Tree

- ECC: NIST P256/384/521 and Brainpool P256/384/512 curves; KeyGen, KAS ECC CDH, ECDSA SigGen & SigVer, PKG, PKV

- IFC: 1024/1536/2048/3072/4096 RSA E/D; SSA\_PKCS1\_V1\_5 SigGen & SigVer; ANSI X9.31 SigGen & SigVer

- FFC: 1024/153/2048/3072/4096; KAS DH, DSA SigGen & SigVer

#### 3.5.5 **Controller Area Network**

PolarFire SoC integrates two controller area network cores compliant to CAN 2.0 A and B and conforms to ISO 11898-1. Internal message SRAM is SECDED-protected. The following are CAN controller features.

#### 3.5.5.1 **Receive Path**

- · 32 receive buffers

- Each buffer has its own message filter

- Message filter covers: ID, IDE, RTR, data byte 1, and data byte 2

- Message buffers can be linked together to build a bigger message array

- Automatic remote transmission request (RTR) response handler with optional generation of RTR interrupt

#### 3.5.5.2 **Transmit Path**

- 32 Tx message holding registers with programmable priority arbitration

- Message abort command

- Single-shot transmission (no automatic re-transmission upon error or arbitration loss)

#### 3.5.5.3 **Debugging Support**

- · Listen only mode

- · Internal loop back mode

- External loop back mode

- Error capture register

- SRAM test mode to support software based memory testing (SRAM is addressable by the CPUs if the core is disabled)

#### 3.5.6 **QSPI XIP Controller**

PolarFire SoC integrates a Quad SPI (QSPI) flash controller with eXecute In Place (XIP) capabilities. The following are QSPI features.

· Master SPI Data Rate

- Programmable SPI clock HCLK/2, HCLK/4 or HCLK/6

- Maximum data rate is HCLK/2

- FIFOs

- Transmit and Receive FIFO

- 16-byte transmit FIFO depth

- 32-byte receive FIFO depth

- SPI Protocol

- Master operation

- Motorola SPI supported

- Slave select operation in idle cycles configurable

- Supports extended SPI operation (1, 2, and 4 bits)

- Supports QSPI operation (4-bit operation)

- Supports BSPI operation (2-bit operation)

- Support XIP (execute in place)

- Supports 3 or 4-byte SPI address.

- · Frame Size

- Supports 8-bit frames directly

- Back-to-back frame operation supports >8-bit frames

- Supports up to 4GB Transfer (2\*\*32 bytes)

- · Processor Overhead Reduction

- Support of SPI flash command/data packets with automatic data generation and discard function

# 3.5.7 Serial Peripheral Interface

Serial peripheral interface (SPI) is a synchronous serial data protocol that enables the microprocessor or microcontroller and peripheral devices to communicate with each other. The SPI controller provides a serial interface compliant with the Motorola SPI, Texas Instruments synchronous serial, and National Semiconductor MICROWIRE™ formats. In addition, SPI supports interfacing with large SPI flash and EEPROM devices and a hardware-based slave protocol engine. There are two identical SPI controllers in the MSS.

- · The SPI peripherals support the following features.

- · Master and Slave modes

- Selectable slaves (up to 8)

- · Configurable slave select operation

- · Configurable clock polarity

- · Separate transmit (Tx) and receive (Rx) FIFOs to reduce interrupt service loading

### 3.5.8 Multi-Mode UART

The PolarFire SoC multi-mode universal asynchronous/synchronous receiver/transmitter (MMUART) performs serial-to parallel conversion on data originating from modems or other serial devices, and performs parallel-to serial conversion on data from the CPUs. PolarFire SOC contains 5 identical MMUARTs. The MMUART is software compatible with the popular 16550 UART device.

The MMUART peripherals support the following features.

- · Asynchronous and synchronous operations

- Full programmable serial interface characteristics

- Data width is programmable to 5, 6, 7, or 8 bits

- Even, odd, or no-parity bit generation/detection

- 1, 1½, and 2 stop bit generation

- · 9-bit address flag capability used for multi-drop addressing topologies

- · Separate transmit (Tx) and receive (Rx) FIFOs to reduce processor interrupt service loading

- Single-wire half-duplex mode in which Tx pad can be used for bi-directional data transfer

- Local interconnect network (LIN) header detection and auto baud rate calculation

- Communication with ISO 7816 smart cards

- Fractional baud rate capability

- Return to Zero Inverted (RZI) mod/demod blocks that allow infrared data association (IrDA) and serial infrared (SIR) communications

- The most significant bit (MSB) or the least significant bit (LSB) as the first bit while sending or receiving data

#### I<sup>2</sup>C 3.5.9

Philips inter-integrated circuit (I<sup>2</sup>C) is a two-wire serial bus interface that provides data transfer between many devices. PolarFire SoC contains two identical I<sup>2</sup>C peripherals in the MSS that provide a mechanism for serial communication between the PolarFire SoC and external I<sup>2</sup>C compliant devices. I<sup>2</sup>C peripherals support the following features:

- Master and Slave modes

- 7-bit addressing format and data transfers up to 100 Kbps in Standard mode and up to 400 Kbps in Fast mode

- Multi-master collision detection and arbitration

- Own slave address and general call address detection

- Second slave address detection

- System management bus (SMBus) timeout and real-time idle condition counters

- Input glitch or spike filters

#### 3.5.10 **Real Time Counter**

PolarFire SoC integrates a real time calendar with built-in clock prescaler and an alarm wake-up comparator. It has the following two modes of operation.

- Real time Calendar (counts seconds, minutes, hours, days, weeks, months, and years)

- Binary counter (counts from 0 to 243)

#### 3.5.11 **Watchdog Timer**

There are five watchdogs in the MSS, one per CPU. The watchdog guards against system crashes by requiring that it is regularly serviced by the assigned processor. The watchdog is not enabled at reset and generates a NMI upon reaching the trigger value. Once enabled, the watchdog cannot be disabled.

#### 3.5.12 Timer

The PolarFire SoC system timer consists of two programmable 32-bit decrement counters that generate interrupts to the MSS and FPGA fabric. The two 32-bit timers are identical and have the following features.

- One-shot mode

- Periodic mode

- Concatenation mode in which two 32-bit timers can be concatenated to create a 64-bit timer

- Option to enable or disable the interrupt requests when timer reaches zero

- Controls to start, stop, and reset the timer

#### 3.6 Processor-to-Fabric Interconnect

The interconnect between the FPGA fabric and the MSS switches are either AXI- or APB-based. There are three AXI 64-bit interfaces. Two interfaces support a full, 64-bit AXI bus into the fabric from the MSS and from the fabric to the MSS. One AXI 64-bit interface supports a full, 64-bit AXI bus from the fabric into the MSS. The AXI buses all have DLLs to cancel out any insertion delay and can operate asynchronously to the processors operating frequency. In addition, a 32-bit APB bus is provided to the fabric from the MSS.

Overview DS60001656C-page 23 © 2021 Microchip Technology Inc.

Table 3-5. Processor-to-Fabric Interconnect

| Interface | Туре | Width | MSS to Fabric | Fabric to MSS | DLL |

|-----------|------|-------|---------------|---------------|-----|

| FIC_0     | AXI4 | 64b   | Yes           | Yes           | Yes |

| FIC_1     | AXI4 | 64b   | Yes           | Yes           | Yes |

| FIC_2     | AXI4 | 64b   | No            | Yes           | Yes |

| FIC_3     | APB  | 32b   | Yes           | No            | Yes |

#### 3.7 **Secure Boot**

PolarFire SoC comes with two secure boot options. For the default PolarFire SoC secure boot method, the system controller will copy the Microchip secure boot loader from its private, secure memory area and load it into the 8 KB DTIM of the E51 monitor core. Reset will be released to the CPUs and the boot code will start executing. The default secure boot loader will perform a signature check on the 128 KB eNVM then run a hash on the eNVM image. If no errors are reported, the code will jump to the eNVM. If errors are reported, the system controller will activate a tamper alarm that asserts a signal to the FPGA fabric. Users can then decide on a plan of action.

The second secure boot method allows users to place their own boot code in the secure non-volatile memory (sNVM) area of the chip. The sNVM is a 56 KB nonvolatile memory that can be protected by the built-in Physically Unclonable Function (PUF), meaning the unique PUF ID can serve as an initialization vector for an AES encrypt/ decrypt operation performed by the side-channel resistant system controller co-processor. On power-up, the system controller will decrypt and copy the user code from sNVM and write it to the E51 monitor core DTIM. From there, your custom secure boot loader starts executing.

#### 3.8 Peripheral Memory SECDED Reporting and Error Injection

The Gigabit Ethernet MACs, the MMC 5.1 controller, the USB OTG controller, the CAN controllers, the crypto core and memory in the built-in MSS DDR controller are protected with by single-error correct, double-error detect (SECDED) error correction code (ECC) subsystem, which adds 7 bits to 32-bit memories and 8 bits to 64-bit memories. The memories within the CPU system have their own ECC control and reporting systems. The external DDR memory supports optional ECC (using a fifth DDR bank). Each MSS internal memory system has its own set of control and status registers, which consists of a status, interrupt enable, count, and error injection registers. When a two-bit error is detected, the data will not be corrected. If the data is being read over an internal AMBA bus, the system will respond with an APB, AHB, or AXI error response marking the data as corrupted. If the interrupt is enabled, an interrupt will also be generated. If the data is not being read over an AMBA bus like USB, CAN, Ethernet transmit data then corrupted data will be transmitted, and an interrupt generated. The system can then respond to the bus error event or interrupt and take the appropriate recovery action. ECC error injection is supported to ease customer validation of the error correcting subsystem. Data may be written with 1-, 2-, or 3-bit errors by setting the appropriate EDAC error injection control registers.

#### 3.9 **DMA Controller**

The PolarFire SoC MSS Direct Memory Access (DMA) controller supports up to 4 channels of independent simultaneous transfers. Each channel has its own set of control registers and two interrupts, complete and error. Bus transaction sizes are programmable and the transactions can be auto-loaded into the DMA engine. The DMA engine works in conjunction with hart software services (firmware running on the E51).

#### 4. Programmable Logic Subsystem

The following section describes the programmable logic subsystem.

#### 4.1 **Clock Management**

In each PolarFire SoC FPGA, there are eight DLLs and eight PLLs to provide flexible clock generation and management capabilities. In addition to these DLLs and PLLs, up to 15 transceiver lane transmit PLLs are also available.

The following are key highlights of the clock management architecture.

- · High-speed buffers and routing for low-skew clock distribution

- Frequency synthesis and phase shifting

- · Low-jitter clock generation and jitter filtering

#### 4.1.1 **DLL**

The DLL provides a calculated PVT compensated delay to the I/O's digital delay lines and delay or phase-shifted clocks to the FPGA fabric.

The following are the major modes to which the DLL can be configured.

- Time reference mode—the DLL takes a single clock as an input and determines how many delay line buffer taps are required for a signal to pass through them to rotate a signal. The main use of time reference mode is to know how many delay taps are needed to delay the clock by 90 degrees. The value is then provided to the data strobe signal (DQS)/DQSn input signals for double data rate (DDR) memory controllers to delay all DQS/DQSn signals by the required 90-degree phase shift to capture the data from the memory devices. Multiple memory interfaces of the same clock rate can reuse the same DLL with lane level controls for PVT updates.

- Clock injection delay mode—the DLL can be used to compensate for the clock injection delay associated with the source synchronous receive interfaces. The DLL can match delays for the global, regional, and high-speed bank clocks. There are two outputs from the DLL in this mode: a x1 output fixed in time and another output that can be divided by x1, x2, or x4 and can be phase shifted.

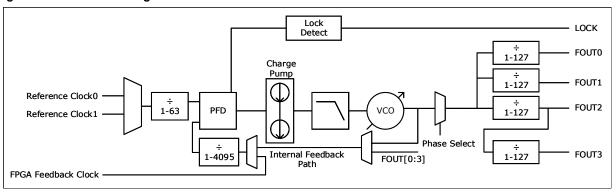

#### PLL 4.1.2

The programmable delta-sigma, low-jitter fractional PLLs are multi-function and general-purpose frequency synthesizers, as shown in the PLL Block Diagram. Wide input and output ranges along with the best-in-class jitter performance allow these PLLs to be used for almost any clocking application. With excellent supply noise immunity, the PLL is ideal for use in noisy FPGA environments.

- The PLL output clock is available in eight phases with 45-degree phase differences. All eight phases are selectable to drive four separate outputs from the PLL, where each output can select any of the eight phases independent of other output selections and each output can also be driven to a zero output when not used.

- Each of the four outputs from the PLL can then be divided independently for any value from 1 to 127. Each of the PLL outputs can have the output divider released by up to seven VCO/4 cycles. The delayed outputs can be set independently for each output clock.

- Fractional-N (24-bit accuracy) capability is added to the feedback divider to have the VCO frequency be a non-integer divide of the reference clock input frequency. The base frequency is applied to all PLL outputs.

- The PLL supports glitch-free start and stop on any one of the four outputs independently by either a register map or a fabric control. This capability also allows the output divider values and the VCO/4 phase selection to be modified glitch-free during the time that the clock is stopped.

- For fine granularity phase control of the PLLs, they can be cascaded with DLLs located near the PLLs, whereby the DLL delay lines can be used in a process, voltage, and temperature (PVT) compensated or non-PVT compensated mode to provide the phase control needed.

The following illustration shows the flow of the PLL functionality.

Figure 4-1. PLL Block Diagram

### 4.1.3 Clock Network

The clock network is designed to route clocks and asynchronous reset signals to large sections of the fabric with limited skew. On occasion, the network can also be used for other high fanout signals that can tolerate long delays, such as non-timing-critical synchronous enables or resets. There are two main clock networks for the FPGA fabric, global, and regional clocks.

### 4.1.3.1 Global Clocks

There are 24 clocks on the device with global, low-skew scope to all synchronous elements. The global can be divided into left and right sides of the device. Thus, the number of global clocks can increase to 48 total clocks with 24 in the left and 24 in the right.

### 4.1.3.2 Regional Clocks

There are up to 38 regional clock domains that interface to the edges of the device. The regional clocks provide a fixed number of logic elements based on the size of the device. Up to 14 clocks are available for the FPGA I/Os and up to 24 clocks are available for the transceiver lanes, one for each lane direction. These are the fast insertion clock networks used to move data in and out of the fabric.

# 4.2 Debug Probe System

Two specified user I/Os can be configured (at design capture stage) as either two, single-ended live probes or one, differential live probe. These live probes can provide read access to any register in the FPGA fabric, to the output pipeline registers in the LSRAMs, and to all the registers in the math block in real time without having to re-instrument the code. A snapshot of all internal probe points can be created and read-out asynchronously. The live-probe feature can be considered a two-channel oscilloscope, whose two channels can be routed out to I/Os for external observation and to internal ports for fabric design observation. Selecting different probe points within the PolarFire SoC FPGA occurs dynamically through commands over the JTAG port using SmartDebug. Reprogramming of the FPGA is not required.

The features of the debug probe system are:

- Active probe allows dynamic asynchronous read and write to a flip-flop or a probe point. This enables quick

internal observation of the logic output or experimentation on how the logic will be affected by writing to a probe

point.

- Memory debug allows dynamic asynchronous read and write to a µSRAM or a large SRAM block to quickly verify if the content of the memory is changing as expected.

- Probe insertion allows routing of nodes or debug points in the FPGA design externally through unused I/Os. An

oscilloscope/logic analyzer can be attached to monitor them as live signals.

# 4.3 I/Os

PolarFire SoC FPGA device user I/Os support multiple I/O standards while providing the high bandwidth needed to maximize the internal logic capabilities of the device and achieve the required system-level performance.

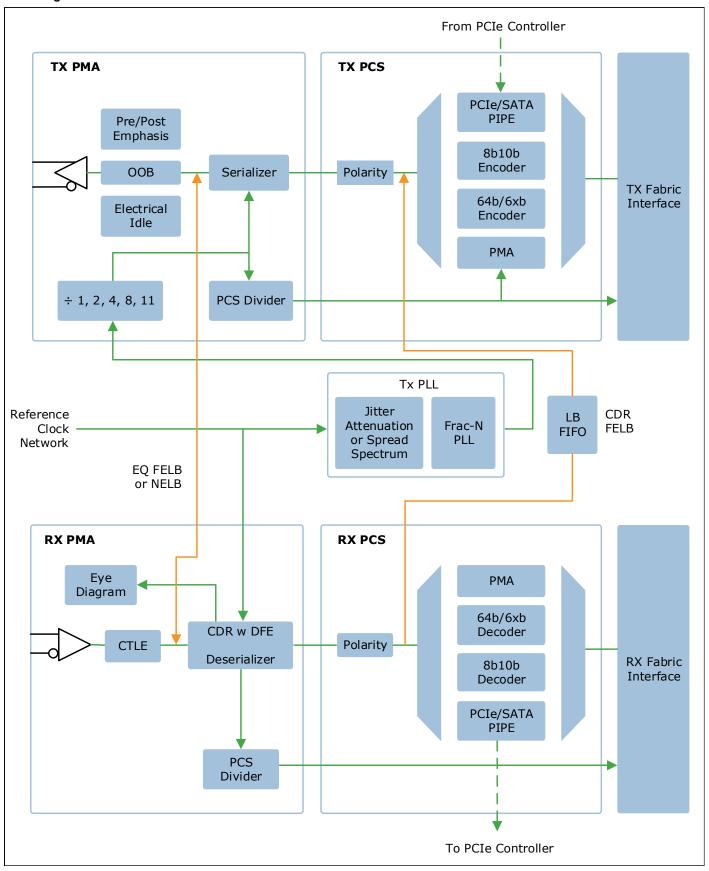

# 4.3.1 Low-Power, High-Speed Transceiver Lane

All PolarFire SoC FPGAs contain state-of-the-art low-power transceiver lane capabilities from speeds as low as 250 Mbps up to 12.7 Gbps. The PMA is designed to support multiple protocols (as listed in the following table) with state-of-the-art control and debug features. PCI Express Gen1 or Gen2 support is provided by a hard macro. All other protocols are implemented with a soft IP. Serial Gigabit Ethernet is also supported with GPIO 3.3 V LVDS differential pairs. A single transmit PLL can provide a high-speed clock up to four transceiver lanes.

Table 4-1. Transceiver Lane Protocol Support

| Protocol             | Data Rate (Gbps) | Channels Bonded |

|----------------------|------------------|-----------------|

| PCle                 | 2.5, 5           | 1, 2, 4         |

| Interlaken           | 6.375, 12.7      | 1–16            |

| 10GBASE-KR           | 10.3125–12.7     | 1               |

| SGMII/QSGMII         | 1.25–5           | 1               |

| XAUI                 | 3.125            | 4               |

| RXAUI                | 3.125, 6.25      | 2, 3, 4, 6      |

| HiGig/HiGig+/HiGiGII | 3.75–4.065       | 4               |

| Fiber Channel        | 0.6144–12.165    | 1               |

| SRIO                 | 1.25–6.3         | 1, 2, 4, 8      |

| SATA                 | 1.5–6            | 1               |

| JESD204B             | 0.5–12.5         | 1–4             |

| Display Port         | 2, 5, 8          | 4               |

| SDI                  | 0.277–11.88      | 1               |

### 4.3.1.1 Low-Power Transceiver Lane Features

The following are features of the low-power transceiver lane.

- · Advanced low-power modes

- · Programmable transmit amplitude and emphasis control

- · Low-speed CDR operation with support for 270 Mbps SMPTE serial line rates

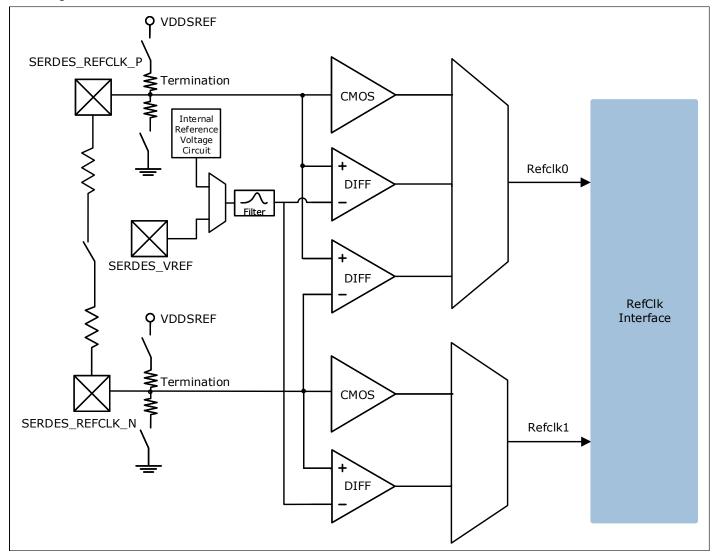

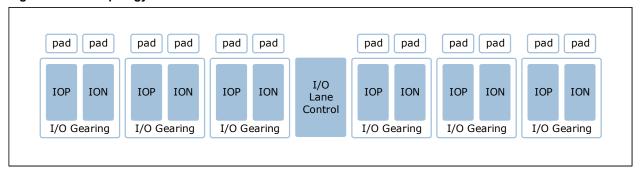

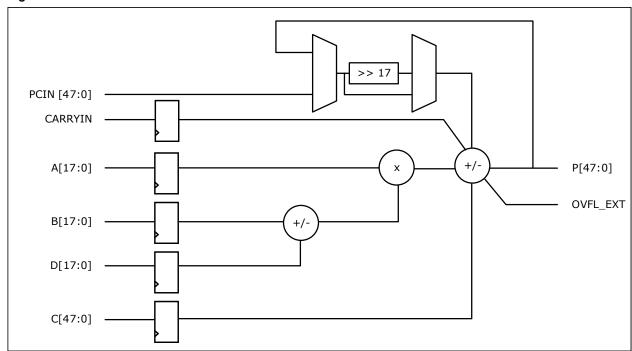

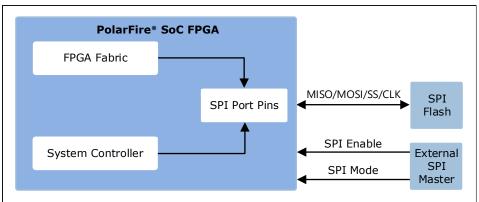

- Continuous time linear equalization (CTLE) and decision feedback equalization (DFE) for long-reach or backplane applications