# **TMC6100 DATASHEET**

Universal high voltage BLDC/PMSM/Servo MOSFET 3-halfbridge gate-driver with up to 1.5A drive current. Tiny QFN package with high creeping distance. External MOSFETs for up to 100A current.

+

+

#### +

+

#### **FEATURES AND BENEFITS**

**3-phase** motors up to 100A coil current (external MOSFETs) **Voltage Range** 8 ... 60V DC **Gate Drive Programmable** 0.5A / 1A / 1.5A **Full Protection and Diagnostics** via SPI interface

**Gate Off Drive** with  $1\Omega$  (LS) /  $1.3\Omega$  (HS) safe hold off resistance

SPI & Stand-Alone operation

Charge Pump for 100% Duty Cycle operation

Optional BBM break-before-make logic for single line control

**Programmable Short and Overload** current threshold and retry **Programmable Control Interface** with 3-line or 6-line drive

Full Protection & Diagnostics

**Compact Size** 7x7mm<sup>2</sup> QFN package

Double Pin Distance for safe operation at high voltage

|      | APPLICATIONS                    |

|------|---------------------------------|

|      | PMSM FOC drives and BLDC motors |

|      | Industrial Drives               |

|      | Factory Automation              |

|      | Lab Automation                  |

|      | Robotics                        |

|      | CNC machines                    |

|      | Textile Machines                |

|      | Pumps                           |

| - H. | Surveillance Cameras            |

|      | Home Automation                 |

| i i  | Printers                        |

#### DESCRIPTION

The TMC6100 is a high-power gate-driver for PMSM servo or BLDC motors. Using six external MOSFETs it controls motors from Watt to Kilowatt. Software controlled drive strength allows insystem EME optimization. Programmable safety features like short detection and overtemperature thresholds together with an SPI interface for diagnostics allow robust and reliable designs. With the TMC6100, a minimum number of external components is required to build a rugged drive with full protection and diagnostics.

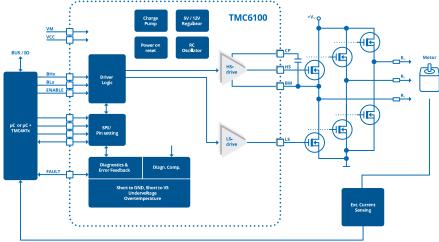

# BLOCK DIAGRAM

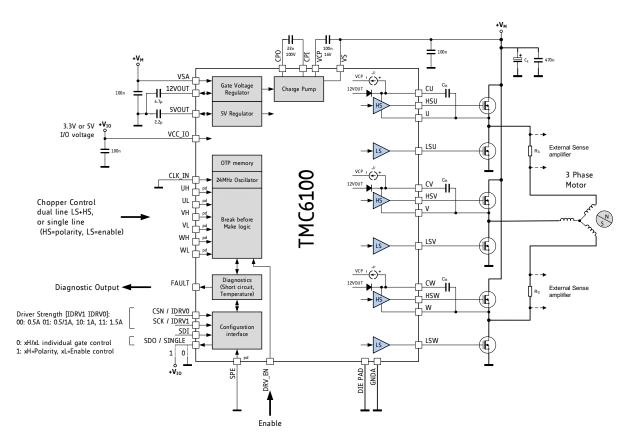

### **APPLICATION EXAMPLES: PMSM AND BLDC MOTORS**

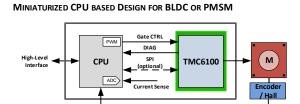

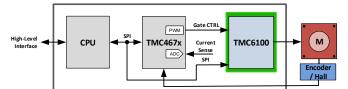

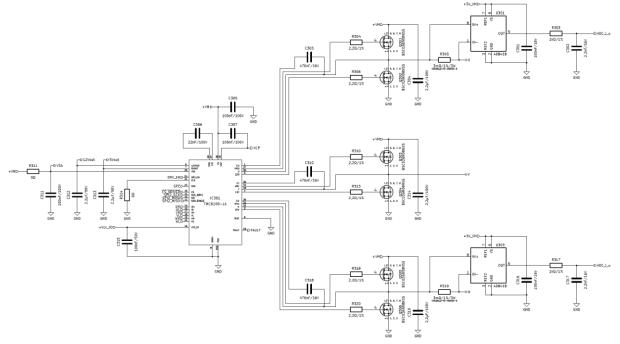

The TMC6100 is a compact driver IC for PMSM drivers. Its special package has sufficient creeping distance, even for voltages of 48V. On the control side, it mates with sophisticated FOC TMC467x and TMC867x family controller chips, or with any microcontroller. Its versatile interface matches simple BLDC drives with minimum requirements on the  $\mu$ C PWM, as well as advanced PMSM control algorithms. The small form factor of the TMC6100 keeps costs down and allows for miniaturized layouts. Extensive support at the chip, board, and software levels enables rapid design cycles and fast time-to-market with competitive products. High integration and reliability deliver cost savings in related systems such as power supplies and cooling.

HIGH PERFORMANCE FOC SERVO DESIGN FOR PMSM

A CPU with internal BLDC or sine wave PWM unit drives the gate control lines based on encoder or hall sensor feedback. External current sensing is required, either using simple Op AMPs for foot point sensing, or series shunt amplifiers. Use of SPI is not required, unless more sophisticated diagnostics is desired.

When using one of the TRINAMIC FOC controllers, the CPU is completely offloaded from time-intensive regulation loop tasks, and software design shrinks to initialization and target parameter setting. The TMC6100 optimally complements a TMC467x family controller.

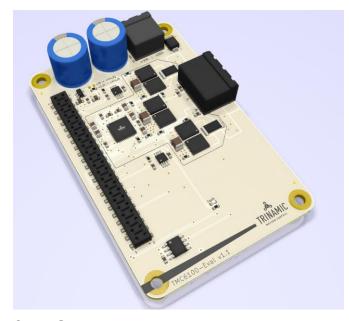

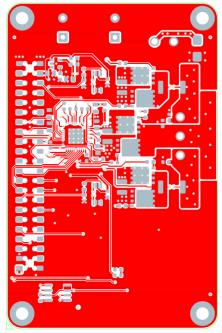

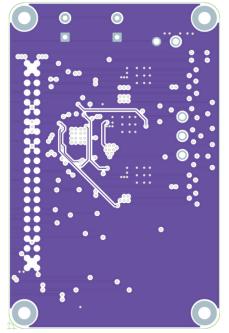

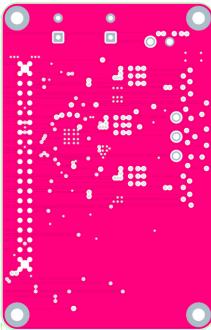

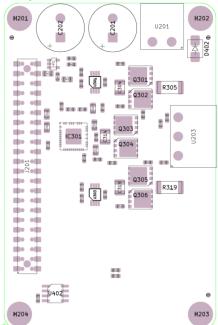

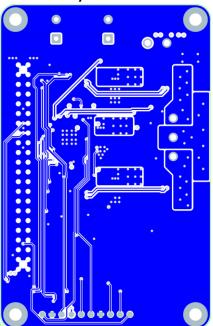

The TMC6100-EVAL is part of TRINAMICs universal evaluation board system which provides a convenient handling of the hardware as well as a user-friendly software tool for evaluation. The TMC6100 evaluation board system consists of three parts: LANDUNGSBRÜCKE (base board), ESELSBRÜCKE (connector board including several test points), and TMC6100-EVAL, plus a TMC4671-EVAL FOC controller.

#### **ORDER CODES**

| Order code     | PN        | Description                                           | Size [mm <sup>2</sup> ] |

|----------------|-----------|-------------------------------------------------------|-------------------------|

| TMC6100-TA     | 00-0201   | Three phase gate-driver for external MOSFETs; QFN 7x7 | 7 x 7                   |

| TMC6100-TA-T   | 00-0201-T | -T denotes tape on reel packed devices                |                         |

| TMC6100-EVAL   | 40-0197   | Evaluation board for TMC6100.                         | 85 x 80                 |

| LANDUNGSBRÜCKE | 40-0167   | Baseboard for TMC6100-EVAL and further boards.        | 85 x 55                 |

| ESELSBRÜCKE    | 40-0098   | Connector board for plug-in evaluation board system.  | 61 x 38                 |

# **Table of Contents**

| 1 | PRI                                                         | NCIPLES OF OPERATION                                                                                                                             | 4                                      |

|---|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|   | 1.1                                                         | CONTROL INTERFACES                                                                                                                               | 6                                      |

| 2 | PIN                                                         | ASSIGNMENTS                                                                                                                                      | 7                                      |

|   | 2.1<br>2.2                                                  | PACKAGE OUTLINE<br>SIGNAL DESCRIPTIONS                                                                                                           |                                        |

| 3 | SAM                                                         | IPLE CIRCUITS                                                                                                                                    | 10                                     |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5                             | STANDARD APPLICATION CIRCUIT<br>EXTERNAL GATE VOLTAGE REGULATOR<br>ZERO STANDBY CURRENT<br>MOSFETS AND SLOPE CONTROL<br>TUNING THE MOSFET BRIDGE | 11<br>12<br>13                         |

| 4 | SPI                                                         | INTERFACE                                                                                                                                        | 18                                     |

|   |                                                             |                                                                                                                                                  |                                        |

|   | 4.1<br>4.2<br>4.3                                           | SPI DATAGRAM STRUCTURE<br>SPI SIGNALS<br>TIMING                                                                                                  | 19                                     |

| 5 | 4.2<br>4.3                                                  | SPI SIGNALS                                                                                                                                      | 19<br>20                               |

| 5 | 4.2<br>4.3                                                  | SPI SIGNALS<br>TIMING                                                                                                                            | 19<br>20<br><b>21</b>                  |

| 5 | 4.2<br>4.3<br><b>REG</b>                                    | SPI SIGNALS<br>TIMING<br>ISTER MAPPING                                                                                                           | 19<br>20<br><b>21</b><br>22            |

| - | 4.2<br>4.3<br><b>REG</b>                                    | SPI SIGNALS<br>TIMING<br>ISTER MAPPING<br>GENERAL CONFIGURATION REGISTERS                                                                        | 19<br>20<br>21<br>22<br>27<br>27       |

| - | 4.2<br>4.3<br><b>REG</b><br>5.1<br><b>DIA</b><br>6.1<br>6.2 | SPI SIGNALS<br>TIMING<br>ISTER MAPPING<br>GENERAL CONFIGURATION REGISTERS<br>GNOSTICS AND PROTECTION<br>TEMPERATURE SENSORS                      | 19<br>20<br>21<br>22<br>27<br>27<br>27 |

|    | 8.1<br>8.2                           | USING THE INTERNAL CLOCK<br>USING AN EXTERNAL CLOCK    |                |

|----|--------------------------------------|--------------------------------------------------------|----------------|

| 9  | Α                                    | BSOLUTE MAXIMUM RATINGS                                | 30             |

| 10 | D                                    | ELECTRICAL CHARACTERISTICS                             | 30             |

|    | 10.1<br>10.2<br>10.3                 | DC AND TIMING CHARACTERISTICS                          | 31             |

| 11 | 1                                    | LAYOUT CONSIDERATIONS                                  | 35             |

|    | 11.1<br>11.2<br>11.3<br>11.4<br>11.5 | WIRING GND<br>WIRING BRIDGE SUPPLY<br>SUPPLY FILTERING | 35<br>35<br>35 |

| 17 | 2                                    | PACKAGE MECHANICAL DATA                                | 38             |

|    | 12.1<br>12.2                         |                                                        |                |

| 1  | 3                                    | DISCLAIMER                                             | 40             |

| 1/ | 4                                    | ESD SENSITIVE DEVICE                                   | 40             |

| 1! | 5                                    | DESIGNED FOR SUSTAINABILITY                            | 40             |

| 16 | 5                                    | TABLE OF FIGURES                                       | 41             |

| 17 | 7                                    | REVISION HISTORY                                       | 41             |

## **1** Principles of Operation

The TMC6100 is a MOSFET gate driver for three phase PMSM and BLDC motors. Ideally suited for applications in the range of 12V to 48V, it supports motor power ratings from 1 Watt to 1kW. It complements with TRINAMICs TMC467x & TMC867x families of three phase motor controller ICs. Internal break-before-make timing is provided for the ease-of-use in combination with simple microcontrollers for PWM generation. A complete set of protection and diagnostic functions makes the power stage more rugged than a discrete setup.

#### THE **TMC6100** OFFERS TWO BASIC MODES OF OPERATION:

#### MODE 1: Stand-alone driver with pin configuration

Enable this mode by tying low pin SPE. The interface pins allow a number of different settings for BBM generation.

#### MODE 2: SPI controlled

This mode allows detailed control over the protection, diagnostic and control features, e.g. for tuning overcurrent detection. Enable this mode by tying high pin SPE.

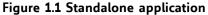

Figure 1.2 Standalone application using single shunt current sensing

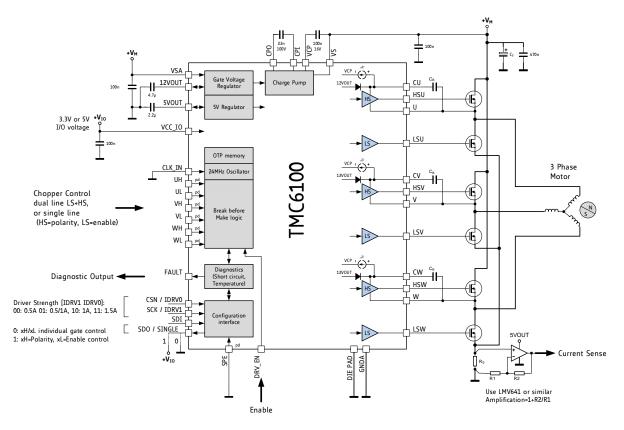

Figure 1.3 SPI mode configuration

### **1.1** Control Interfaces

The TMC6100 supports six control lines for the MOSFET drivers. High-side and low-side outputs can be individually controlled, or by an individual enable pin plus polarity pin, using internal BBM circuitry. An SPI interface or standalone configuration is supported.

### **1.1.1** Standalone Configuration

Standalone configuration covers the most important settings like driver current and current amplifier amplification factor and the selection of internal or external BBM operation using four pins. Additional settings like BBM time and sensitivity of short detection can be modified using pre-programming via OTP memory, e.g. via an initial programming during product testing. This way, the driver can be fully operated and all protection mechanisms are in place. The fault output signals any critical driver error. It becomes cleared by disabling *I* re-enabling the driver.

However, no advanced debugging is possible, like individual testing of failure mechanisms or setting a more sensitive temperature threshold.

Hint

Standalone configuration is recommended for low-cost applications with small motors (e.g. motor current up to 10A RMS), where advanced debugging is not required or not possible. In case a sensitive overtemperature threshold must be set, the SPI interface should be used.

### 1.1.2 SPI Interface

The SPI interface is a bit-serial interface synchronous to a bus clock. For every bit sent from the bus master to the bus slave another bit is sent simultaneously from the slave to the master. Communication between an SPI master and the TMC6100 slave always consists of sending one 40-bit command word and receiving one 40-bit status word.

The SPI command rate typically is a few commands for initialization or for diagnostic feedback.

#### Attention

When operating in SPI mode, set drive mode (single line or individual control signals) first. For safety reasons, the driver starts up in single line mode. Note, that this setting will prevent operation if a controller operates the IC using individual control signals. Therefore, initialize the control mode first.

## 2 Pin Assignments

### 2.1 Package Outline

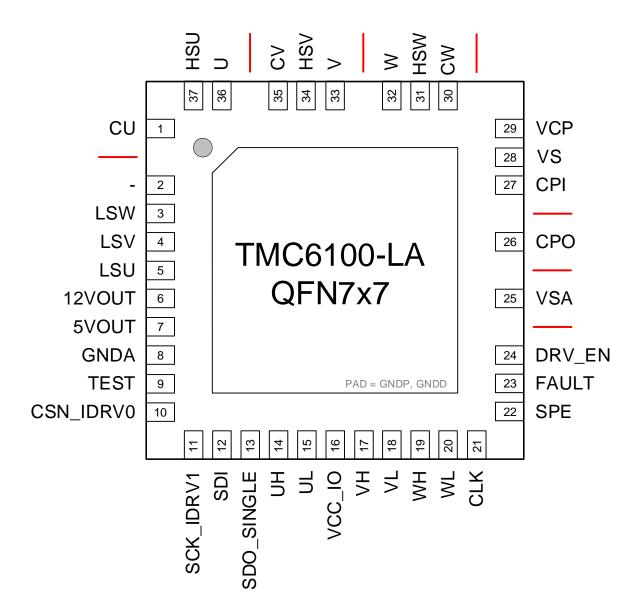

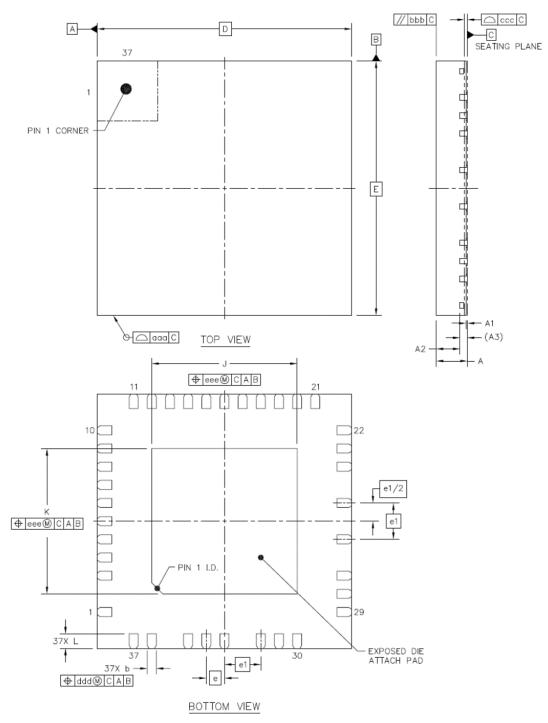

Figure 2.1 TMC6100-LA pinning QFN 37 special (7x7mm<sup>2</sup>)

### 2.2 Signal Descriptions

| Pin | QFN | Туре | Function                                                                                                          |

|-----|-----|------|-------------------------------------------------------------------------------------------------------------------|

| CU  | 1   |      | Bootstrap capacitor positive connection. Tie to U terminal using 470nF to $1\mu$ F, 16V or 25V ceramic capacitor. |

| -   | 2   | N.C. | Unused pin (may be tied to GND)                                                                                   |

| LSW | 3   |      | Low side gate driver output.                                                                                      |

| LSV | 4   |      | Low side gate driver output.                                                                                      |

| LSU | 5   |      | Low side gate driver output.                                                                                      |

| Pin        | QFN | Туре       | Function                                                                                                                                                                                                                                                                                                                                                                      |

|------------|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12VOUT     | 6   |            | Output of internal 11.5V gate voltage regulator and supply pin<br>of low side gate drivers. Attach $2.2\mu$ F to $22\mu$ F ceramic<br>capacitor to GND plane near to pin for best performance. Use<br>at least 5-10 times more capacity than for bootstrap capacitors.<br>In case an external gate voltage supply is available, tie VSA<br>and 12VOUT to the external supply. |

| 5VOUT      | 7   |            | Output of internal 5V regulator. Attach 2.2µF to 10µF ceramic capacitor to GNDA near to pin for best performance.                                                                                                                                                                                                                                                             |

| GNDA       | 8   |            | Analog GND. Connect to GND plane near pin.                                                                                                                                                                                                                                                                                                                                    |

| TEST       | 9   | AI         | leave open                                                                                                                                                                                                                                                                                                                                                                    |

| CSN_IDRV0  | 10  | DI         | SPI chip select input (negative active) (SPE=1) or<br>Configuration input for gate driver current LSB (SPE=0)                                                                                                                                                                                                                                                                 |

| SCK_IDRV1  | 11  | DI         | SPI serial clock input (SPE=1) or<br>Configuration input for gate driver current MSB (SPE=0)                                                                                                                                                                                                                                                                                  |

| SDI        | 12  | DI         | SPI data input                                                                                                                                                                                                                                                                                                                                                                |

| SDO_SINGLE | 13  | DIO        | SPI data output (tristate) (SPE=1) or<br>Configuration input for internal bridge control mode (0: dual<br>line, 1: xH=phase polarity, xL=phase enable) (SPE=0)                                                                                                                                                                                                                |

| UH         | 14  | DI<br>(pd) | High side control input (or bridge polarity in single mode)                                                                                                                                                                                                                                                                                                                   |

| UL         | 15  | DI<br>(pd) | Low side control input (or bridge enable in single mode)                                                                                                                                                                                                                                                                                                                      |

| VCC IO     | 16  | - 1        | 3.3V to 5V IO supply voltage for all digital pins.                                                                                                                                                                                                                                                                                                                            |

| VH         | 17  | DI<br>(pd) | High side control input (or bridge polarity in single mode)                                                                                                                                                                                                                                                                                                                   |

| VL         | 18  | DI<br>(pd) | Low side control input (or bridge enable in single mode)                                                                                                                                                                                                                                                                                                                      |

| WH         | 19  | DI<br>(pd) | High side control input (or bridge polarity in single mode)                                                                                                                                                                                                                                                                                                                   |

| WL         | 20  | DI<br>(pd) | Low side control input (or bridge enable in single mode)                                                                                                                                                                                                                                                                                                                      |

| CLK        | 21  | DI         | CLK input. Tie to GND using short wire for internal clock or<br>supply external clock. Internal clock-fail over circuit protects<br>against loss of external clock signal.                                                                                                                                                                                                    |

| SPE        | 22  | DI<br>(pd) | Mode selection input. When tied low, the chip is in standalone<br>mode and SPI pins have their configuration pin functions.<br>When tied high, the SPI interface is enabled. Integrated pull<br>down resistor.                                                                                                                                                                |

| FAULT      | 23  | DO         | Diagnostics output.<br>High upon driver error condition. Clear by cycling EN.                                                                                                                                                                                                                                                                                                 |

| DRV_EN     | 24  | DI         | Positive active enable input. The power stage becomes<br>switched off (all motor outputs floating) when this pin<br>becomes driven to a low level. Cycle low to clear FAULT.                                                                                                                                                                                                  |

| VSA        | 25  |            | Analog supply voltage for 11.5V and 5V regulator. Normally tied to VS. Provide a 100nF filtering capacitor to GND.                                                                                                                                                                                                                                                            |

| CPO        | 26  |            | Charge pump capacitor output.                                                                                                                                                                                                                                                                                                                                                 |

| CPI        | 27  |            | Charge pump capacitor input. Tie to CPO using 22nF 100V capacitor. In case ringing of the power supply leads to considerable supply ripple, add a 10-220hm series resistor.                                                                                                                                                                                                   |

| VS         | 28  |            | Motor supply voltage. Provide filtering capacity near pin with<br>short loop to GND plane. Must be tied to the positive bridge<br>supply voltage. Severe ringing must be avoided.                                                                                                                                                                                             |

| VCP        | 29  |            | Charge pump voltage. Tie to VS using 100nF capacitor.                                                                                                                                                                                                                                                                                                                         |

| Pin             | QFN | Туре | Function                                                                                                                                                                                                                                |

|-----------------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CW              | 30  |      | Bootstrap capacitor positive connection. Tie to W terminal using 470nF to $1\mu$ F, 16V or 25V ceramic capacitor.                                                                                                                       |

| HSW             | 31  |      | High side gate driver output.                                                                                                                                                                                                           |

| W               | 32  |      | Bridge center and bootstrap capacitor negative connection.<br>Connect to source pin of HS-MOSFET.                                                                                                                                       |

| V               | 33  |      | Bridge center and bootstrap capacitor negative connection.<br>Connect to source pin of HS-MOSFET.                                                                                                                                       |

| HSV             | 34  |      | High side gate driver output.                                                                                                                                                                                                           |

| CV              | 35  |      | Bootstrap capacitor positive connection. Tie to V terminal using 470nF to $1\mu$ F, 16V or 25V ceramic capacitor.                                                                                                                       |

| U               | 36  |      | Bridge center and bootstrap capacitor negative connection.<br>Connect to source pin of HS-MOSFET.                                                                                                                                       |

| HSU             | 37  |      | High side gate driver output.                                                                                                                                                                                                           |

| Exposed die pad | -   |      | Connect the exposed die pad to a GND plane. Provide as many<br>as possible vias for heat transfer to GND plane. Serves as GND<br>pin for the low side gate drivers and for digital logic. Ensure<br>low loop inductivity to bridge GND. |

\*(pd) denominates a pin with pulldown resistor

## 3 Sample Circuits

The following sample circuits show the required external components in different operation and supply modes. The connection of the external current amplifier, bus interface and further digital signals are left out for clarity.

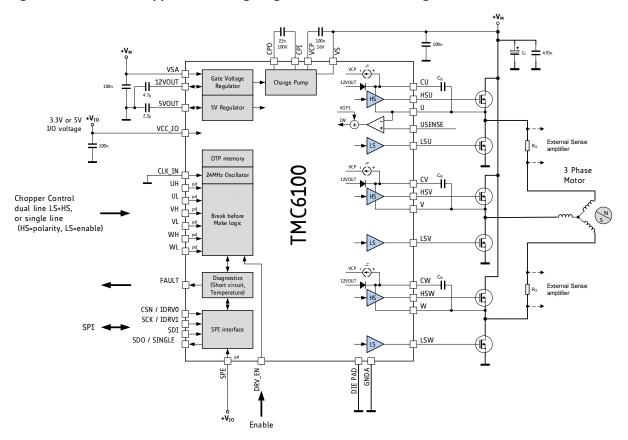

### 3.1 Standard Application Circuit

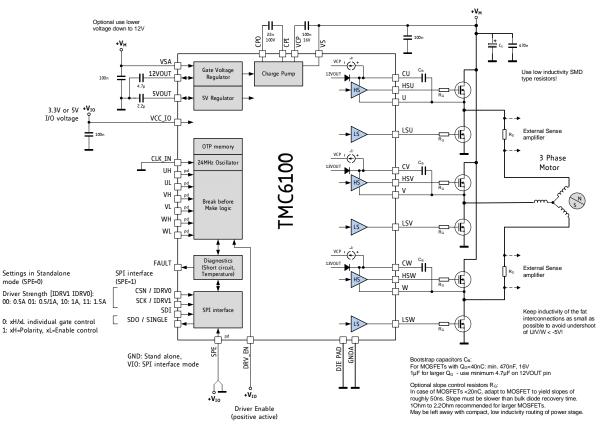

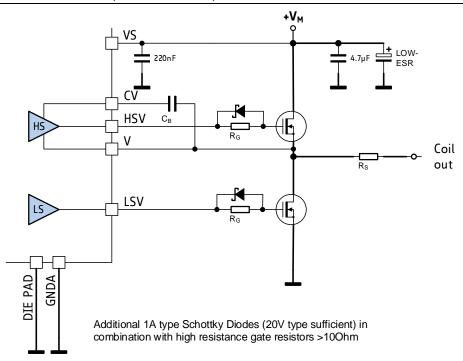

#### Figure 3.1 Standard application circuit

The standard application circuit uses a minimum set of additional components. Six MOSFETs are selected for the desired current, voltage and package type. Two or three sense resistors are matched to the maximum motor coil current, and to the desired external current amplifier output swing and amplification setting. Use low ESR capacitors for filtering the power supply. A minimum capacity of 100µF per ampere of coil current near to the power bridge is recommended for keeping power supply ripple low. The capacitors need to cope with the current ripple caused by chopper operation. Current ripple in the supply capacitors also depends on the power supply internal resistance and cable length. Supply VCC\_IO from 5VOUT, or from an external source, e.g. a 3.3V regulator. In order to minimize linear voltage regulator power dissipation of the internal 5V and 11.5V voltage regulators in applications where VM is high, a different (lower) supply voltage should be used for VSA, when available (see chapter 3.2).

#### Important layout hints

Place all filter capacitors as close as possible to the power MOSFETs. Place the TMC6100 near to the MOSFETs and use short interconnection lines in order to minimize parasitic trace inductance. Use a solid common GND for all GND and GNDA connections. Connect 5VOUT filtering capacitor directly to 5VOUT and GNDA pin. See layout hints for more details. Low ESR electrolytic capacitors are recommended for VS filtering.

#### Attention

In case VSA is supplied by a different voltage source, make sure that VSA does not drop out during motor operation. The motor driver should be disabled in case VSA becomes switched off before VS. Hard switching edges on VSA might result in bridge cross-conduction otherwise. It is safest to derive VSA voltage from VS supply. VS power slope also should be limited to 0.5V/µs or less.

#### Attention

Make sure, that VCC\_IO does not drop out during operation of the motor. Disable the drive when a falling supply voltage is detected. It is safest to use the same source for VCC\_IO as for the controller driving the motor.

Hint

VCC\_IO undervoltage detection disables the MOSFET drivers. This will avoid motor overcurrent due to instable input levels during power-up / power-down for most cases. However, it is best practice to disable the motor prior to switching off power supply, and to make sure, that the motor power supply does come up without or not remain with missing VCC\_IO supply.

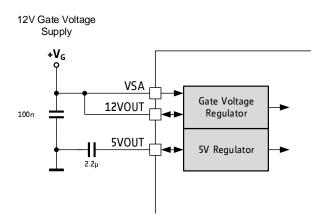

### 3.2 External Gate Voltage Regulator

At high supply voltages like 48V, the internal gate voltage regulator and the internal 5V regulator have considerable power dissipation, especially with high MOSFET gate charges or high chopper frequency. A good thermal coupling of the heat slug to the system PCB GND plane is required to dissipate heat. Still, the thermal thresholds will be lowered significantly by self-heating. To reduce power dissipation, supply an external gate driver voltage to the TMC6100. Figure 3.2 shows the required connection. The internal gate voltage regulator becomes disabled in this constellation. 12V +/-1V is recommended for best results.

Figure 3.2 External gate voltage supply

Hint

With MOSFETs above 50nC of total gate charge or chopper frequency >40kHz, it is recommended to use a VSA supply not higher than 40V in order to keep reasonable power dissipation.

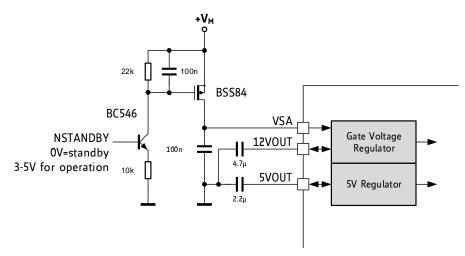

### 3.3 Zero Standby Current

Battery powered applications often require low current standby, while keeping the supply switched on. The TMC6100 can support these applications by completely powering down the control side, VSA, and with this also the charge pump and 5V supply. See Figure 3.3 for an example using a P-MOSFET as high-side switch. Gate charge *I* discharge is limited to avoid too steep slopes and excess current. VCC\_IO may remain active during standby operation. Make sure that the motor becomes disabled before switching off the power supply!

#### Figure 3.3 Standby Switch

Hint

Realize zero standby current by switching off VSA in standby mode. VCC\_IO may remain active. Ensure a slope-controlled power-up of 1V/µs or less to avoid excess current into VSA.

#### Attention

Test your circuit thoroughly in order to ensure a safe and clean power-up and standby power-up and power-down event! When powering down the control side of the MOSFET drivers, MOSFET gate-off is only ensured by high-resistive resistors within the TMC6100. This makes the circuit more susceptible to injection of charge from MOSFET drain to gate, e.g. to high supply voltage slopes. Any spurious cross-conduction could lead to destructive currents through the power MOSFETs.

### 3.4 MOSFETs and Slope Control

The selection of power MOSFETs depends on a number of factors, like package size, on-resistance, voltage rating and supplier. It is not true, that larger, lower RDSon MOSFETs will always be better, as a larger device also has higher capacitances and may add more ringing in trace inductance and power dissipation in the gate drive circuitry. Adapt the MOSFETs to the required motor voltage (adding 5-10V of reserve to the peak supply voltage) and to the desired maximum current, in a way that resistive power dissipation still is low for the chosen MOSFET package. The TMC6100 drives the MOSFET gates with roughly 10V, so normal, 10V specified types are sufficient. Logic level FETs (4.5V specified RDSon) will also work but may be more critical with regard to bridge cross-conduction due to lower V<sub>GS(th)</sub>.

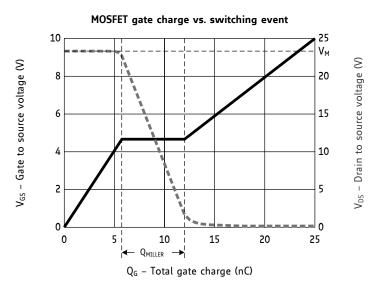

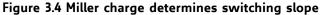

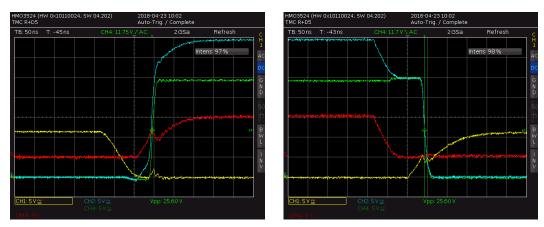

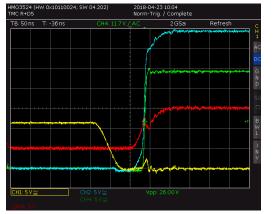

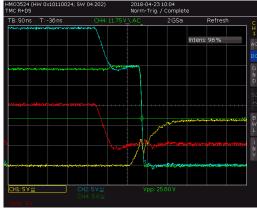

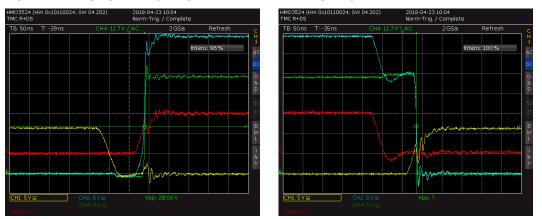

The gate-drive current and MOSFET gate resistors  $R_G$  (optional) should basically be adapted to the MOSFET gate-drain charge (Miller charge) in order to yield reasonable slope times. Figure 3.4 shows the influence of the Miller charge on the switching event. Figure 3.5 additionally shows the switching events in different load situations (load pulling the output up or down), and the required bridge brake-before-make time.

The following table shall serve as a thumb rule for programming the MOSFET driver current (*DRVSTRENGTH* setting) and the selection of gate resistors:

| MOSFET MILLER CHARGE VS. DRVSTRENGTH AND RG |             |                             |  |  |

|---------------------------------------------|-------------|-----------------------------|--|--|

| Miller Charge                               | DRVSTRENGTH | Value of $R_G$ [ $\Omega$ ] |  |  |

| [nC] (typ.)                                 | setting     |                             |  |  |

| <10                                         | 0 or 1      | ≤ 10 (recommended)          |  |  |

| 1020                                        | 0 to 2      | ≤ 5 (optional)              |  |  |

| 2080                                        | 1 to 3      | ≤ 2.5 (optional)            |  |  |

| >80                                         | 3           | ≤ 1 (optional)              |  |  |

The TMC6100 provides increased gate-off drive current to avoid bridge cross-conduction induced by high dV/dt. This protection will be less efficient with gate resistors exceeding the values given in the table. For larger values of  $R_{G}$ , a parallel diode may be required to ensure keeping the MOSFET safely off during switching events of the opposite MOSFET.

Hints

Choose modern MOSFETs with fast and soft recovery bulk diode and low reverse recovery charge.

A small, SMD MOSFET package allows compacter routing and reduces parasitic inductance effects.

Figure 3.5 Slopes, Miller plateau and blank time (BMx=U V or W output)

| Parameter | Description                                                                                          | Setting | Comment                  |

|-----------|------------------------------------------------------------------------------------------------------|---------|--------------------------|

| BBMCLKS   | Break-before-make time setting to ensure non-                                                        | 015     | time[ns]≈                |

|           | overlapping switching of high-side and low-side                                                      |         | 42ns*BBMCLKS             |

|           | MOSFETs. Digital BBM time in clock cycles (typ. 42ns/CLK).                                           |         | Ensure -30% headroom     |

|           | BBMCLKS is used in combination with singleline=1.                                                    |         | Reset Default: OTP 14    |

|           | It is not applicable with individual LS and HS                                                       |         | 4, when not programmed   |

|           | signals.                                                                                             |         |                          |

|           | Additionally, a minimum BBM time of 75ns is                                                          |         |                          |

|           | enforced by analog circuitry even with individual control signals. This prevents short-circuiting of |         |                          |

|           | the bridge                                                                                           |         |                          |

| DRV_      | Selection of gate driver current. Adapts the gate                                                    | 03      | Reset Default = 2 in SPI |

| STRENGTH  | driver current to the gate charge of the external                                                    |         | mode                     |

|           | MOSFETs.                                                                                             |         |                          |

#### DRV\_CONF Parameters

Use the lowest gate driver strength setting *DRV\_STRENGTH* giving favorable switching slopes, before increasing the value of the gate series resistors. A slope time of nominal 40ns to 80ns is absolutely sufficient and will normally be covered by a Break-Before-Make time setting of 1 to 4 (4 is default). In case slower slopes have to be used, e.g. with large MOSFETs, ensure that the break-before-make time sufficiently covers the switching event, in order to avoid bridge cross conduction. The shortest break-before-make time, safely covering the switching event, gives best results. Add roughly 30% of reserve, to cover production stray of MOSFETs and driver.

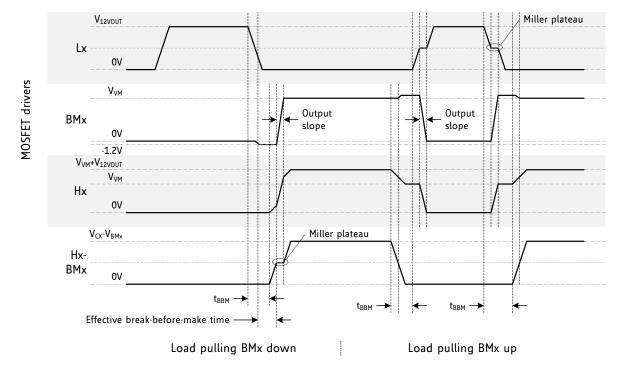

### 3.5 Tuning the MOSFET Bridge

A clean switching event is favorable to ensure low power dissipation and good EMC behavior. Unsuitable layout or components endanger stable operation of the circuit. Therefore, it is important to understand the effect of parasitic trace inductivity and MOSFET reverse recovery.

Stray inductance in power routing will cause ringing whenever the opposite MOSFET is in diode conduction prior to switching on a low-side or high-side MOSFET. Diode conduction occurs during break-before make time whenever the load current is inverse to the following bridge polarity. The MOSFET bulk diode has a certain, type specific reverse recovery time and charge. This time typically is in the range of a few 10ns. During reverse recovery time, the bulk diode will cause high current flow across the bridge. This current is taken from the power supply filter capacitors (see thick lines Figure 3.6). Once the diode opens, parasitic inductance tries to keep the current flowing. A high, fast slope results and leads to ringing in all parasitic inductivities (see Figure 3.7). This may lead to bridge voltage undershooting the GND level as well as fast pulses on VS and all MOSFET connections. It must be ensured, that the driver IC does not see spikes on its BM pins to GND going below -5V. Severe VS ripple might overload the charge-pump circuitry. Measure the voltage directly at the driver pins to driver GND. The amount of undershooting depends on energy stored in parasitic inductivities from low side drain to low side source and via the sense resistor RS to GND.

When using relatively small MOSFETs, a soft slope control requires a high gate series resistance. This endangers safe MOSFET switch off. Add additional diodes to ensure safe MOSFET off conditions with slow switch-on slopes (Figure 3.10).

Decide use and value of the additional components based on measurements of the actual circuit using the final layout!

#### Figure 3.6 Bridge protection options for power routing inductivity

#### **ENSURE RELIABLE OPERATION**

- Use SMD MOSFETs and short interconnections

- Provide sufficient power filtering capacity close to the bridge and close to VS pin

- Tune MOSFET switching slopes (measure switch-on event at MOSFET gate) to be slower than the MOSFET bulk diode reverse recovery time. This will reduce cross conduction.

- Add optional gate resistors close to MOSFET gate and output capacitors to ensure clean switching and reliable operation by minimizing ringing. Figure 3.6 shows the options plus some variations.

- Some MOSFETs eliminate reverse recovery charge by integrating a fast diode from source to drain.

Figure 3.9 Ringing of output (green) and Gate voltages (yellow, blue) with DRVSTRENGTH=3

#### BRIDGE OPTIMIZATION EXAMPLE

A driver for 15A, 60V has been designed using the MOSFET BSC037N08NS (3.7m $\Omega$ , 80V, Q<sub>G</sub>=56nC, t<sub>RR</sub>=41ns) in the standard schematic.

The MOSFETs offer roughly 20ns slope time at the lowest driver strength setting. Switching quality is good and signals are clean (Figure 3.7, ff.). At double drive strength, the slope time halves, and switching events still are clean. When increasing to full gate drive strength faster slopes lead to increased ringing on all signals. Low or medium slope setting is best. Additional gate resistors or 1nF output capacitors do not bring any additional improvement. The layout already proves to be good. *No additional components were required!*

#### Figure 3.10 Diodes for safe off condition with high gate series resistance

#### BRIDGE LAYOUT CONSIDERATIONS

- Tune the bridge layout for minimum loop inductivity. A compact layout is best.

- Keep MOSFET gate connections short and straight and avoid loop inductivity between bridge feedback (U,V,W) and corresponding HS driver pin. Loop inductance is minimized with parallel traces, or adjacent traces on adjacent layers. A wider trace reduces inductivity (don't use minimum trace width).

- Place the TMC6100 near the low side MOSFETs GND connections, with its GND connections directly connected to the same GND plane.

- Optimize switching behavior by using lowest acceptable gate current setting.

- Check influence of optional components shown in Figure 3.6.

- Measure the performance of the bridge by probing BM pins directly at the bridge or at the TMC6100 using a short GND tip on the scope probe rather than a GND cable, if available.

# 4 SPI Interface

### 4.1 SPI Datagram Structure

The TMC6100 uses 40 bit SPI<sup>™</sup> (Serial Peripheral Interface, SPI is Trademark of Motorola) datagrams for communication with a microcontroller. Microcontrollers which are equipped with hardware SPI are typically able to communicate using integer multiples of 8 bit. The NCS line of the device must be handled in a way, that it stays active (low) for the complete duration of the datagram transmission.

Each datagram sent to the device is composed of an address byte followed by four data bytes. This allows direct 32 bit data word communication with the register set. Each register is accessed via 32 data bits even if it uses less than 32 data bits.

For simplification, each register is specified by a one-byte address:

- For a read access the most significant bit of the address byte is 0.

- For a write access the most significant bit of the address byte is 1.

| SPI DATAGRAM STRUCTURE                                                                                              |                                                                                                                             |            |                               |                 |  |

|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------|-----------------|--|

| MSB (transmitted first)                                                                                             |                                                                                                                             | 40 bit     |                               |                 |  |

| 39                                                                                                                  |                                                                                                                             |            |                               | 0               |  |

| → 8 bit address<br>$\leftarrow$ 8 bit SPI status $\leftarrow$ → 32 bit data                                         |                                                                                                                             |            |                               |                 |  |

| 39 32                                                                                                               |                                                                                                                             | 31         | 0                             |                 |  |

| → to TMC6100<br>RW + 7 bit address<br>← from TMC6100                                                                | 8 bit data                                                                                                                  | 8 bit data | 8 bit data                    | 8 bit data      |  |

| unused<br>39 / 38 32                                                                                                | 31 24                                                                                                                       | 23 16      | 15 8                          | 7 0             |  |

| w 3832                                                                                                              | 3128 2724                                                                                                                   | 2320 1916  | 1512 118                      | 70              |  |

| 3       3       3       3       3       3       3         9       8       7       6       5       4       3       2 | 3       3       2       2       2       2       2       2         1       0       9       8       7       6       5       4 |            | 1 1 1 1 1 1 1 5 4 3 2 1 0 9 8 | 7 6 5 4 3 2 1 0 |  |

Read and write functionality of the individual registers may differ.

### 4.1.1 Selection of Write / Read (WRITE\_notREAD)

The read and write selection is controlled by the MSB of the address byte (bit 39 of the SPI datagram). This bit is 0 for read access and 1 for write access. So, the bit named W is a WRITE\_notREAD control bit. The active high write bit is the MSB of the address byte. So, 0x80 has to be added to the address for a write access. The SPI interface always delivers data back to the master, independent of the W bit. Read data coming back in a write access should be ignored.

Read data is transferred back to the master directly in the read access. Internal read access occurs during the transmission in the moment when the address bits have been received.

Example:

For a read access to the register (*GSTAT*) with the address 0x00, the address byte has to be set to 0x00. For a write access to the register (*GCONF*), the address byte has to be set to 0x80 + 0x01 = 0x81. For read access, the data bits don't care. So, one can set them to 0.

| action                  | data sent to TMC6100 | data received from TMC6100 |

|-------------------------|----------------------|----------------------------|

| read GSTAT              | → 0x010000000        | ← AA & GSTAT               |

| write GCONF:= 0x0000010 | → 0x800000010        | ← 0x01 & unused            |

$^{\star}$  ) AA: is a placeholder for the address byte used in the previous access

### 4.1.2 Data Alignment

All data are right aligned. Some registers represent unsigned (positive) values, some represent integer values (signed) as two's complement numbers, single bits or groups of bits are represented as single bits respectively as integer groups.

### 4.2 SPI Signals

The SPI bus on the TMC6100 has four signals:

- SCK bus clock input

- SDI serial data input

- SDO serial data output

- CSN chip select input (active low)

The slave is enabled for an SPI transaction by a low on the chip select input CSN. Bit transfer is synchronous to the bus clock SCK, with the slave latching the data from SDI on the rising edge of SCK and driving data to SDO following the falling edge. The most significant bit is sent first. A minimum of 40 SCK clock cycles is required for a bus transaction with the TMC6100.

The TMC6100 does not allow cascading of SPI slaves. Use individual CSN lines for each device.

CSN must be low during the whole bus transaction. When CSN goes high, the contents of the internal shift register are latched into the internal control register and recognized as a command from the master to the slave.

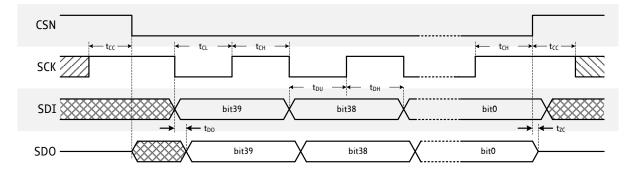

### 4.3 Timing

The SPI interface is synchronized to the internal system clock, which limits the SPI bus clock SCK to 1/4 of the system clock frequency. If the system clock is based on the on-chip oscillator, an additional 10% safety margin must be used to ensure reliable data transmission. All SPI inputs as well as the ENN input are internally filtered to avoid triggering on pulses shorter than 20ns. Figure 4.1 shows the timing parameters of an SPI bus transaction, and the table below specifies their values.

#### Figure 4.1 SPI timing

Hint Usually this SPI timing is referred to as SPI MODE 3

| SPI interface timing                                |                   | AC-Characteristics<br>clock period: t <sub>CLK</sub>                                                  |                     |                        |                      |      |  |  |

|-----------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------|---------------------|------------------------|----------------------|------|--|--|

| Parameter                                           | Symbol            | Conditions                                                                                            | Min                 | Тур                    | Max                  | Unit |  |  |

| SCK valid before or after change of CSN             | t <sub>cc</sub>   |                                                                                                       | 10                  |                        |                      | ns   |  |  |

| CSN high time                                       | t <sub>сsн</sub>  | *) Min time is for<br>synchronous CLK<br>with SCK high one<br>t <sub>CH</sub> before CSN high<br>only | t <sub>clk</sub> *) | >2t <sub>CLK</sub> +10 |                      | ns   |  |  |

| SCK low time                                        | t <sub>CL</sub>   | *) Min time is for<br>synchronous CLK<br>only                                                         | t <sub>clk</sub> *) | >t <sub>CLK</sub> +10  |                      | ns   |  |  |

| SCK high time                                       | t <sub>сн</sub>   | *) Min time is for<br>synchronous CLK<br>only                                                         | t <sub>CLK</sub> *) | >t <sub>CLK</sub> +10  |                      | ns   |  |  |

| SCK frequency using internal clock                  | f <sub>scк</sub>  | assumes minimum<br>OSC frequency                                                                      |                     |                        | 3.5                  | MHz  |  |  |

| SCK frequency using external clock                  | f <sub>scк</sub>  | assumes<br>synchronous CLK                                                                            |                     |                        | f <sub>CLK</sub> /6  | MHz  |  |  |

| SDI setup time before rising edge of SCK            | t <sub>DU</sub>   |                                                                                                       | 10                  |                        |                      | ns   |  |  |

| SDI hold time after rising edge<br>of SCK           | t <sub>DH</sub>   |                                                                                                       | 10                  |                        |                      | ns   |  |  |

| Data out valid time after falling<br>SCK clock edge | t <sub>DO</sub>   | no capacitive load<br>on SDO                                                                          |                     |                        | t <sub>CLK</sub> +10 | ns   |  |  |

| SDI, SCK and CSN filter delay time                  | t <sub>FILT</sub> | rising and falling<br>edge                                                                            | 12                  | 20                     | 30                   | ns   |  |  |

# 5 Register Mapping

This chapter gives an overview of the complete register set. Some of the registers bundling a number of single bits are detailed in extra tables. The functional practical application of the settings is detailed in dedicated chapters.

#### Note

- All registers become reset to 0 upon power up, unless otherwise noted. - Add 0x80 to the address Addr for a write access!

| ΝΟΤΑΤ | OF HEXADECIMAL AND BINARY NUMBERS             |

|-------|-----------------------------------------------|

| 0x    | precedes a hexadecimal number, e.g. 0x04      |

| %     | precedes a multi-bit binary number, e.g. %100 |

| NOTATION OF R/W FIELD |                                |

|-----------------------|--------------------------------|

| R                     | Read only                      |

| W                     | Write only                     |

| R/W                   | Read- and writable register    |

| R+WC                  | Clear upon write back with '1' |

#### **OVERVIEW REGISTER MAPPING**

| REGISTER                        | DESCRIPTION                                                                                                                                                                           |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Configuration Registers | These registers contain <ul> <li>global configuration</li> <li>global status flags</li> <li>interface configuration</li> <li>driver configuration</li> <li>OTP programming</li> </ul> |

# 5.1 General Configuration Registers

| GENER | AL CONFI | GURAT  | ION REGISTERS | (0x000x0F)                                                                                                                                                                                                                                                                                    |

|-------|----------|--------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R/W   | Addr     | n      | Register      | Description I bit names                                                                                                                                                                                                                                                                       |

|       |          |        |               | Bit GCONF – Global configuration flags                                                                                                                                                                                                                                                        |

|       |          |        |               | 0       disable: Driver Disable         1:       Disable       driver (e.g. for Resetting of short condition)         1       singleline: Interface mode (reset default = 1)         0:       Individual signals L+H                                                                          |

|       |          |        |               | 1: H-Input is control signal, L-Input is Enable                                                                                                                                                                                                                                               |

| RW    | 0x00     | 17     | GCONF         | <ul> <li>2 faultdirect</li> <li>0: Fault output active when at least one bridge is shut down continuously due to overcurrent or overtemperature</li> <li>1: Fault output shows each protective action of the</li> </ul>                                                                       |

|       | 0,00     | 1/     | deola         | overcurrent shutdown                                                                                                                                                                                                                                                                          |

|       |          |        |               | 5:3 unused                                                                                                                                                                                                                                                                                    |

|       |          |        |               | 6 1: Normal operation - set upon write access for reduced power consumption                                                                                                                                                                                                                   |

|       |          |        |               | 7 test_mode<br>0: Normal operation<br>1: Enable analog test output on pin DRV_EN.<br>BBM_CLKS[10] selects the function of DRV_EN:                                                                                                                                                             |

|       |          |        |               | 02: T120, DAC, VDDH<br>Attention: Not for user, set to 0 for normal operation!                                                                                                                                                                                                                |

|       |          |        |               | 31:8 unused                                                                                                                                                                                                                                                                                   |

|       |          |        |               | Bit GSTAT – Global status flags                                                                                                                                                                                                                                                               |

|       |          |        |               | (Re-Write with '1' bit to clear respective flags, or cycle<br>DRV_EN to clear all bits except for reset and drv_otpw)<br>Attention: Switch off the affected MOSFET by its HS/LS<br>input in order to clear a pending short condition. Just<br>resetting the flag will not switch it on again. |

|       |          | x01 15 | 15 GSTAT      | 0 reset<br>1: Indicates that the IC has been reset. All registers<br>have been cleared to reset values.<br>Attention: DRV EN must be high to allow clearing reset                                                                                                                             |

| R+    | 0.01     |        |               | 1       drv_otpw         1:       Indicates, that the driver temperature has exceeded overtemperature prewarning-level. No action is taken. This flag is latched.                                                                                                                             |

| wc    | 0x01     |        |               | <ul> <li>2 drv_ot</li> <li>1: Indicates, that the driver has been shut down due to overtemperature. This flag can only be cleared when the temperature is below the limit again. It is latched for information.</li> <li>ORed to STATUS output.</li> </ul>                                    |

|       |          |        |               | <ul> <li>3 uv_cp</li> <li>1: Indicates an undervoltage on the charge pump.<br/>The driver is disabled during undervoltage. This<br/>flag is latched for information.</li> <li>ORed to STATUS output.</li> </ul>                                                                               |

|       |          |        |               | <ul> <li>4 shortdet_u</li> <li>1: U short counter has triggered at least once.</li> <li>ORed to STATUS output.</li> </ul>                                                                                                                                                                     |

| GENER | AL CONFI | GURAT  | ION REGISTERS | (0x000   | x0F)                                                                                                                                                           |

|-------|----------|--------|---------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R/W   | Addr     | n      | Register      | Descri   | ption I bit names                                                                                                                                              |

|       |          |        |               | 5        | <ul> <li>s2gu</li> <li>1: Short to GND detected on phase U. The driver becomes disabled until flag becomes cleared.</li> <li>ORed to STATUS output.</li> </ul> |

|       |          |        |               | 6        | <ul> <li>s2vsu</li> <li>1: Short to VS detected on phase U. The driver becomes disabled until flag becomes cleared.</li> <li>ORed to STATUS output.</li> </ul> |

|       |          |        |               | 7        | -                                                                                                                                                              |

|       |          |        |               | 8        | <ul> <li>shortdet_v</li> <li>1: V short counter has triggered at least once.</li> <li>ORed to STATUS output.</li> </ul>                                        |

|       |          |        |               | 9        | <ul> <li>s2gv</li> <li>1: Short to GND detected on phase V. The driver becomes disabled until flag becomes cleared.</li> <li>ORed to STATUS output.</li> </ul> |

|       |          |        |               | 10       | <ul> <li>s2vsv</li> <li>1: Short to VS detected on phase V. The driver becomes disabled until flag becomes cleared.</li> <li>ORed to STATUS output.</li> </ul> |

|       |          |        |               | 11       | -                                                                                                                                                              |

|       |          |        |               | 12       | shortdet_w<br>1: short counter has triggered at least once.<br>ORed to STATUS output.                                                                          |

|       |          |        |               | 13       | <ul> <li>s2gw</li> <li>1: Short to GND detected on phase W. The driver becomes disabled until flag becomes cleared.</li> <li>ORed to STATUS output.</li> </ul> |

|       |          |        |               | 14       | <ul> <li>s2vsw</li> <li>1: Short to VS detected on phase W. The driver becomes disabled until flag becomes cleared.</li> <li>ORed to STATUS output.</li> </ul> |

|       |          |        |               | Bit      | INPUT                                                                                                                                                          |

|       |          |        |               | 0        | Reads the state of all input pins available<br>UL                                                                                                              |

|       |          |        |               | 1        | UH                                                                                                                                                             |

|       |          |        |               | 2        | VL                                                                                                                                                             |

|       |          |        |               | 3        | VH                                                                                                                                                             |

|       |          | 8      |               | 4        | WL<br>WH                                                                                                                                                       |

| R     | 0x04     | 0<br>+ | IOIN          | 6        | DRV_EN                                                                                                                                                         |

|       |          | 8      |               | 7        | 0                                                                                                                                                              |

|       |          |        |               | 8        | OTPW                                                                                                                                                           |

|       |          |        |               | 9        | OT136°C                                                                                                                                                        |

|       |          |        |               | 10       | OT143°C                                                                                                                                                        |

|       |          |        |               | 11       | OT150°C                                                                                                                                                        |

|       |          |        |               | 31<br>24 | <i>VERSION</i> : 0x10=first version of the IC<br>Identical numbers mean full digital compatibility.                                                            |

| W     | 0x06     |        | OTP_PROG      | Bit      | OTP_PROGRAM - OTP programming                                                                                                                                  |

| ٧V    | 0,00     |        |               |          | Write access programs OTP memory (one bit at a time),                                                                                                          |

23

| GENER | AL CONFI | GURAT | ON REGISTERS | (0x000 | x0F)                                                                                             |

|-------|----------|-------|--------------|--------|--------------------------------------------------------------------------------------------------|

| R/W   | Addr     | n     | Register     | Descri | ption <i>I bit names</i>                                                                         |

|       |          |       | _            | •      | Read access refreshes read data from OTP after a write                                           |

|       |          |       |              | 20     | OTPBIT                                                                                           |

|       |          |       |              |        | Selection of OTP bit to be programmed to the selected                                            |

|       |          |       |              |        | byte location (n=07: programs bit n to a logic 1)                                                |

|       |          |       |              | 54     | ОТРВҮТЕ                                                                                          |

|       |          |       |              |        | Set to 00                                                                                        |

|       |          |       |              | 158    | OTPMAGIC                                                                                         |

|       |          |       |              |        | Set to 0xbd to enable programming. A programming                                                 |

|       |          |       |              |        | time of minimum 10ms per bit is recommended (check                                               |

|       |          |       |              |        | by reading OTP_READ).                                                                            |

| _     |          |       |              | Bit    | <b>OTP_READ</b> (Access to OTP memory result and update)                                         |

| R     | 0x07     |       | OTP_READ     |        | See table 5.1.1!                                                                                 |

|       |          |       |              | 70     | OTPO byte 0 read data                                                                            |

|       |          |       |              | 40     | FCLKTRIM (Reset default: OTP)                                                                    |

|       |          |       |              |        | 031: Lowest to highest clock frequency. Check at                                                 |

| RW    | 0x08     | 5     | FACTORY_     |        | charge pump output. The frequency span is not guaranteed, but it is tested, that tuning to 12MHz |

| RVV   | 0x00     | 2     | CONF         |        | internal clock is possible. The devices come preset to                                           |

|       |          |       |              |        | 12MHz clock frequency by OTP programming.                                                        |

|       |          |       |              |        | (Reset Default: OTP)                                                                             |

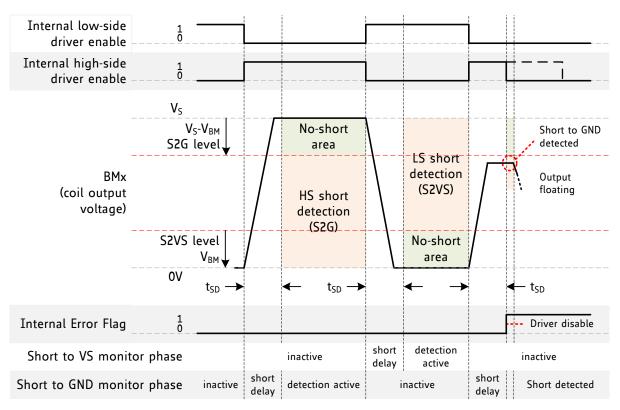

|       |          |       |              | Bit    | SHORT_CONF                                                                                       |

|       |          |       |              | 30     | S2VS LEVEL:                                                                                      |

|       |          |       |              |        | Short to VS detector level for lowside FETs. Checks for                                          |

|       |          |       |              |        | voltage drop in LS MOSFET and bottom shunt resistor.                                             |

|       |          |       |              |        | 1 (highest sensitivity) 15 (lowest sensitivity)                                                  |

|       |          |       |              |        | (Reset Default: OTP 6 or 12)                                                                     |

|       |          |       |              | 118    | S2G_LEVEL:                                                                                       |

|       |          |       |              |        | Short to GND detector level for highside FETs. Checks                                            |

|       |          |       |              |        | for voltage drop on high side MOSFET                                                             |

|       |          |       |              |        | 2 (highest sensitivity) 15 (lowest sensitivity)                                                  |

|       |          |       |              |        | Hint: Use high setting. Tune S2VS level for more                                                 |

|       |          |       |              |        | sensitive overcurrent detection.                                                                 |

|       |          |       |              | 1716   | (Reset Default: OTP 6 or 12)<br>SHORTFILTER:                                                     |

|       |          |       |              | 1710   | Spike filtering bandwidth for short detection                                                    |

| RW    | 0x09     | 19    | SHORT_       |        | 0 (lowest, 100ns), 1 (1 $\mu$ s), 2 (2 $\mu$ s) 3 (3 $\mu$ s)                                    |

|       | 0,007    | - /   | CONF         |        | Hint: Increase value, if erroneous short detection                                               |

|       |          |       |              |        | occurs.                                                                                          |

|       |          |       |              |        | (Reset Default = %01)                                                                            |

|       |          |       |              | 20     | shortdelay: Short detection delay                                                                |

|       |          |       |              |        | 0=750ns: normal, 1=1500ns: high                                                                  |

|       |          |       |              |        | The short detection delay shall cover the bridge                                                 |

|       |          |       |              |        | switching time. 0 will work for most applications.                                               |

|       |          |       |              |        | (Reset Default = 0)                                                                              |

|       |          |       |              | 2524   | RETRY: Number of retries for short detection                                                     |

|       |          |       |              |        | 0: Half bridge disabled after first short detection                                              |

|       |          |       |              |        | 13: Half bridge re-enabled in next chopper cycles 1                                              |

|       |          |       |              |        | time to 3 times. With retry, the short-counter is                                                |

|       |          |       |              |        | decreased once each 256 chopper cycles per coil,                                                 |

|       |          |       |              |        | unless the upper limit has been reached.<br>(Reset Default = 3)                                  |

|       |          |       |              |        | (Neser Dejuuli = 5)                                                                              |

|     | JUANT |          | 0x000   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|-------|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|