# μP Reset Circuits with Capacitor-Adjustable Reset/Watchdog Timeout Delay

#### **General Description**

The MAX6746–MAX6753 low-power microprocessor ( $\mu$ P) supervisory circuits monitor single/dual system supply voltages from 1.575V to 5V and provide maximum adjustability for reset and watchdog functions. These devices assert a reset signal whenever the V<sub>CC</sub> supply voltage or RESET IN falls below its reset threshold or when manual reset is pulled low. The reset output remains asserted for the reset timeout period after V<sub>CC</sub> and RESET IN rise above the reset threshold. The reset function features immunity to power-supply transients.

The MAX6746–MAX6753 have  $\pm 2\%$  factory-trimmed reset threshold voltages in approximately 100mV increments from 1.575V to 5.0V and/or adjustable reset threshold voltages using external resistors.

The reset and watchdog delays are adjustable with external capacitors. The MAX6746–MAX6751 contain a watchdog select input that extends the watchdog timeout period by 128x. The MAX6752/MAX6753 contain a window watchdog timer that looks for activity outside an expected window of operation.

The MAX6746–MAX6753 are available with a push-pull or open-drain active-low RESET output. The MAX6746– MAX6753 are available in an 8-pin SOT23 package and are fully specified over the automotive temperature range (-40°C to +125°C).

#### **Applications**

- Medical Equipment

- Automotive

- Intelligent Instruments

- Portable Equipment

- Battery-Powered Computers/Controllers

- Embedded Controllers

- Critical µP Monitoring

- Set-Top Boxes

- Computers

<u>Selector Guide</u> and <u>Ordering Information</u> appear at end of data sheet.

#### **Benefits and Features**

- Configurable Reset and Watchdog Options Enables Wide Variety of Applications

- Factory-Set Reset Threshold Options from 1.575V to 5V in ~100mV Increments

- · Adjustable Reset Threshold Options

- Single/Dual Voltage Monitoring

- Capacitor-Adjustable Reset Timeout

- Capacitor-Adjustable Watchdog Timeout

- Min/Max (Windowed) Watchdog Option

- Manual-Reset Input Option

- Push-Pull or Open-Drain RESET Output Options

- 3.7µA Supply Current Reduces System Power Consumption

- Integrated Power Supply Protection Increases

Robustness

- Power-Supply Transient Immunity

- Guaranteed RESET Valid for V<sub>CC</sub> ≥ 1V

- 8-Pin SOT23 Packages Saves Board Space

- AEC-Q100 Qualified. Refer to <u>Ordering Information</u> for Specific /V Trim Variants

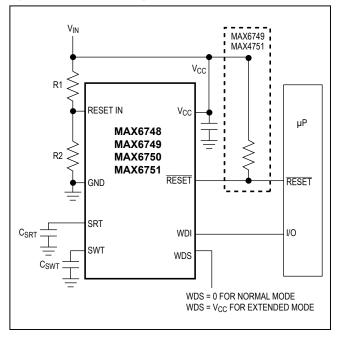

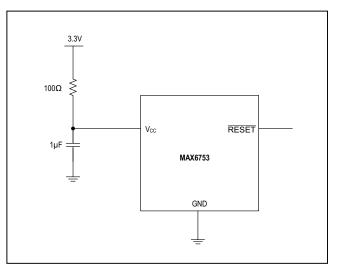

## **Typical Operating Circuit**

## µP Reset Circuits with Capacitor-Adjustable Reset/Watchdog Timeout Delay

### **Absolute Maximum Ratings**

| V <sub>CC</sub> to GND                                  | 0.3V to +6.0V                     |

|---------------------------------------------------------|-----------------------------------|

| SRT, SWT, SET0, SET1, RESET IN, WD                      |                                   |

| WDI, to GND                                             | 0.3V to (V <sub>CC</sub> + 0.3V)  |

| RESET (Push-Pull) to GND                                | 0.3V to (V <sub>CC</sub> + 0.3V)  |

| RESET (Open-Drain) to GND                               | 0.3V to +6.0V                     |

| Input Current (All Pins)                                | ±20mA                             |

| Output Current (RESET)                                  | ±20mA                             |

| Stresses beyond those listed under "Absolute Maximum Ra | tings" may cause permanent damage |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### 8 SOT23

| PACKAGE CODE                           | K8+5           |  |  |  |

|----------------------------------------|----------------|--|--|--|

| Outline Number                         | <u>21-0078</u> |  |  |  |

| Land Pattern Number                    | <u>90-0176</u> |  |  |  |

| Thermal Resistance, Single-Layer Board |                |  |  |  |

| Junction-to-Ambient ( $\theta_{JA}$ )  | N/A            |  |  |  |

| Junction-to-Case ( $\theta_{JC}$ )     | 800            |  |  |  |

| Thermal Resistance, Four-Layer Board   |                |  |  |  |

| Junction-to-Ambient ( $\theta_{JA}$ )  | 196            |  |  |  |

| Junction-to-Case (θ <sub>JC</sub> )    | 70             |  |  |  |

|                                        |                |  |  |  |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

#### **Electrical Characteristics**

( $V_{CC}$  = +1.2V to +5.5V,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise specified. Typical values are at  $V_{CC}$  = +5V and  $T_A$  = +25°C.) (Note 1)

| PARAMETER                                              | SYMBOL            | C                                                 | ONDITIONS                                        | MIN                  | TYP   | MAX                     | UNITS |

|--------------------------------------------------------|-------------------|---------------------------------------------------|--------------------------------------------------|----------------------|-------|-------------------------|-------|

| Commission ( ) ( = 14 = m =                            | N/                | T <sub>A</sub> = 0°C to +125°C                    |                                                  | 1.0                  |       | 5.5                     |       |

| Supply Voltage                                         | V <sub>CC</sub>   | $T_A = -40^{\circ}C$ to $0^{\circ}C$              | ;                                                | 1.2                  |       | 5.5                     | V     |

|                                                        |                   | V <sub>CC</sub> ≤ 5.5V                            |                                                  |                      | 5     | 10                      |       |

| Supply Current                                         | ICC               | V <sub>CC</sub> ≤ 3.3V                            |                                                  |                      | 4.2   | 9                       | μA    |

|                                                        |                   | V <sub>CC</sub> ≤ 2.0V                            |                                                  |                      | 3.7   | 8                       |       |

| V <sub>CC</sub> Reset Threshold                        | V <sub>TH</sub>   | See V <sub>TH</sub><br>selection table            | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$   | V <sub>TH</sub> - 2% |       | V <sub>TH</sub> +<br>2% | V     |

| Hysteresis                                             | V <sub>HYST</sub> |                                                   |                                                  |                      | 0.8   |                         | %     |

| V <sub>CC</sub> Reset Threshold<br>(MAX6752AKA32 Only) |                   | TA = -40°C to +12                                 | 25°C                                             | 3.136                |       | 3.224                   | V     |

| Hysteresis (MAX6752AKA32 Only)                         | V <sub>HYST</sub> |                                                   |                                                  | 0.65                 | 0.80  | 0.90                    | %     |

| V <sub>CC</sub> to Reset Delay                         |                   | V <sub>CC</sub> falling from V<br>-100mV at 1mV/µ | / <sub>TH</sub> + 100mV to V <sub>TH</sub><br>is |                      | 20    |                         | μs    |

| Deast Timesout Devied                                  |                   | C <sub>SRT</sub> = 1500pF                         |                                                  | 5.692                | 7.590 | 9.487                   |       |

| Reset Timeout Period                                   | t <sub>RP</sub>   | C <sub>SRT</sub> = 100pF                          |                                                  |                      | 0.506 |                         | ms    |

| SRT Ramp Current                                       | IRAMP             | V <sub>SRT</sub> = 0 to 1.23                      | 200                                              | 250                  | 300   | nA                      |       |

| SRT Ramp Threshold                                     | V <sub>RAMP</sub> | V <sub>CC</sub> = 1.6V to 5                       | / (V <sub>RAMP</sub> rising)                     | 1.173                | 1.235 | 1.297                   | V     |

# μP Reset Circuits with Capacitor-Adjustable Reset/Watchdog Timeout Delay

## **Electrical Characteristics (continued)**

( $V_{CC}$  = +1.2V to +5.5V,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise specified. Typical values are at  $V_{CC}$  = +5V and  $T_A$  = +25°C.) (Note 1)

| PARAMETER                                              | SYMBOL            | CONDITIONS                                                                 | MIN                  | TYP                   | MAX                  | UNITS |  |  |

|--------------------------------------------------------|-------------------|----------------------------------------------------------------------------|----------------------|-----------------------|----------------------|-------|--|--|

| Normal Watchdog Timeout Period                         | +                 | C <sub>SWT</sub> = 1500pF                                                  | 5.692                | 7.590                 | 9.487                |       |  |  |

| (MAX6746–MAX6751)                                      | twD               | C <sub>SWT</sub> = 100pF                                                   |                      | 0.506                 |                      | ms    |  |  |

| Extended Watchdog Timeout                              |                   | C <sub>SWT</sub> = 1500pF                                                  | 728.6                | 971.5                 | 1214.4               | ms    |  |  |

| (MAX6746–MAX6751)                                      | twd               | C <sub>SWT</sub> = 100pF                                                   |                      | 64.77                 |                      | ms    |  |  |

| Slow Watchdog Period                                   | <b>t</b>          | C <sub>SWT</sub> = 1500pF                                                  | 728.6                | 971.5                 | 1214.4               |       |  |  |

| (MAX6752/MAX6753)                                      | <sup>t</sup> WD2  | C <sub>SWT</sub> = 100pF                                                   |                      | 64.77                 |                      | ms    |  |  |

| Fast Watchdog Timeout Period,                          |                   | C <sub>SWT</sub> = 1500pF                                                  | 91.08                | 121.43                | 151.80               | 100.0 |  |  |

| SET Ratio = 8,<br>(MAX6752/MAX6753)                    | <sup>t</sup> WD1  | C <sub>SWT</sub> = 100pF                                                   |                      | 8.09                  |                      | ms    |  |  |

| Fast Watchdog Timeout Period,                          |                   | C <sub>SWT</sub> = 1500pF                                                  | 45.53                | 60.71                 | 75.89                | 122.0 |  |  |

| SET Ratio = 16,<br>(MAX6752/MAX6753)                   | <sup>t</sup> WD1  | C <sub>SWT</sub> = 100pF                                                   |                      | 4.05                  |                      | ms    |  |  |

| Fast Watchdog Timeout Period,                          | +                 | C <sub>SWT</sub> = 1500pF                                                  | 11.38                | 15.18                 | 18.98                | ma    |  |  |

| SET Ratio = 64,<br>(MAX6752/MAX6753)                   | t <sub>WD1</sub>  | C <sub>SWT</sub> = 100pF                                                   |                      | 1.01                  |                      | ms    |  |  |

| Fast Watchdog Minimum Period<br>(MAX6752/MAX6753)      |                   |                                                                            | 2000                 |                       |                      | ns    |  |  |

| SWT Ramp Current                                       | I <sub>RAMP</sub> | $V_{SWT}$ = 0 to 1.23V, $V_{CC}$ = 1.6V to 5V                              | 200                  | 250                   | 300                  | nA    |  |  |

| SWT Ramp Threshold                                     | V <sub>RAMP</sub> | $V_{CC}$ = 1.6V to 5V (V <sub>RAMP</sub> rising)                           | 1.173                | 1.235                 | 1.297                | V     |  |  |

| RESET Output-Voltage Low                               | V <sub>OL</sub>   | V <sub>CC</sub> ≥ 1.0V, I <sub>SINK</sub> = 50µA                           |                      | 0.3                   |                      |       |  |  |

| Open-Drain, Push-Pull                                  |                   | V <sub>CC</sub> ≥ 2.7V, I <sub>SINK</sub> = 1.2mA                          |                      |                       | 0.3                  | V     |  |  |

| (Asserted)                                             |                   | V <sub>CC</sub> ≥ 4.5V, I <sub>SINK</sub> = 3.2mA                          |                      |                       | 0.4                  |       |  |  |

|                                                        |                   | $V_{CC} \ge 1.8V$ , $I_{SOURCE} = 200\mu A$                                | 0.8 x V <sub>C</sub> | c                     |                      |       |  |  |

| RESET Output-Voltage High,<br>Push-Pull (Not Asserted) | V <sub>OH</sub>   | V <sub>CC</sub> ≥ 2.25V, I <sub>SOURCE</sub> = 500µA                       | 0.8 x V <sub>C</sub> | 0.8 x V <sub>CC</sub> |                      |       |  |  |

|                                                        | _                 | V <sub>CC</sub> ≥ 4.5V, I <sub>SOURCE</sub> = 800µA                        | 0.8 x V <sub>C</sub> | 0.8 x V <sub>CC</sub> |                      | I     |  |  |

| RESET Output Leakage Current,<br>Open Drain            | I <sub>LKG</sub>  | $V_{CC}$ > $V_{TH}$ , reset not asserted,<br>$V_{\overline{RESET}}$ = 5.5V |                      |                       | 1.0                  | μA    |  |  |

| DIGITAL INPUTS (MR, SET0, SET                          | 1, WDI, WD        | S)                                                                         |                      |                       |                      |       |  |  |

|                                                        | VIL               | V <sub>CC</sub> ≥ 4.0V                                                     |                      |                       | 0.8                  |       |  |  |

| Input Logic Lovels                                     | VIH               | VCC = 4.00                                                                 | 2.4                  |                       |                      | V     |  |  |

| Input Logic Levels                                     | VIL               | V <sub>CC</sub> < 4.0V                                                     |                      | C                     | .3 x V <sub>CC</sub> | z v   |  |  |

|                                                        | V <sub>IH</sub>   |                                                                            | 0.7 x V <sub>C</sub> | C                     |                      |       |  |  |

| MR Minimum Pulse Width                                 |                   |                                                                            | 1                    |                       |                      | μs    |  |  |

| MR Glitch Rejection                                    |                   |                                                                            |                      | 100                   |                      | ns    |  |  |

| MR-to-RESET Delay                                      |                   |                                                                            |                      | 200                   |                      | ns    |  |  |

| MR Pullup Resistance                                   |                   | Pullup to V <sub>CC</sub>                                                  | 12                   | 20                    | 28                   | kΩ    |  |  |

| WDI Minimum Pulse Width                                |                   |                                                                            | 300                  |                       |                      | ns    |  |  |

## μP Reset Circuits with Capacitor-Adjustable Reset/Watchdog Timeout Delay

### **Electrical Characteristics (continued)**

(V<sub>CC</sub> = +1.2V to +5.5V,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise specified. Typical values are at  $V_{CC} = +5V$  and  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                | SYMBOL                | CONDITIONS                       |       | TYP   | MAX   | UNITS |

|--------------------------|-----------------------|----------------------------------|-------|-------|-------|-------|

| RESET IN                 |                       |                                  |       |       |       |       |

| RESET IN Threshold       | V <sub>RESET IN</sub> | T <sub>A</sub> = -40°C to +125°C | 1.216 | 1.235 | 1.254 | V     |

| RESET IN Leakage Current | IRESET IN             |                                  | -50   | ±1    | +50   | nA    |

| RESET IN to RESET Delay  |                       | RESET IN falling at 1mV/µs       |       | 20    |       | μs    |

Note 1: Production testing done at  $T_A = +25^{\circ}$ C. Over temperature limits are guaranteed by design.

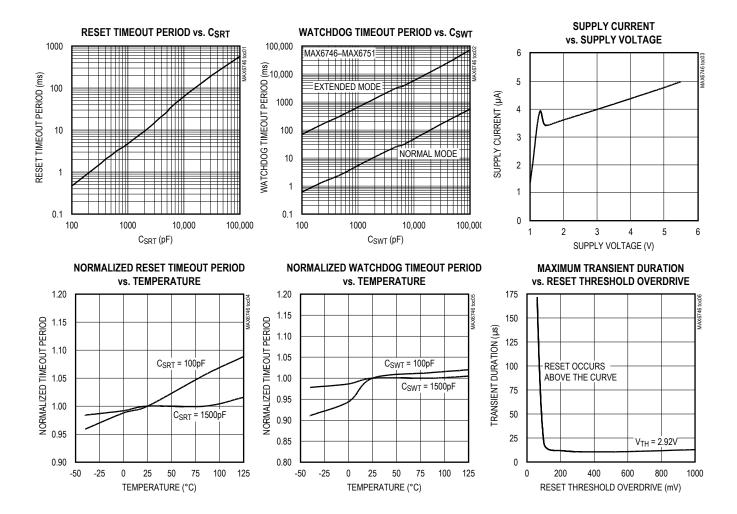

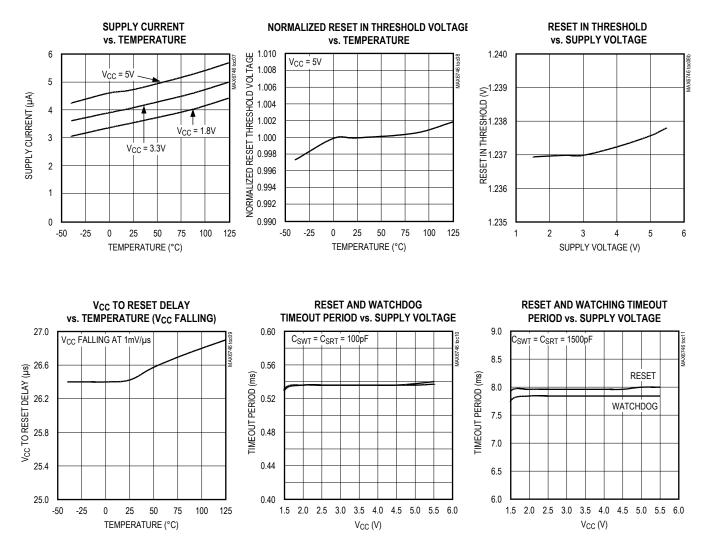

## **Typical Operating Characteristics**

(V<sub>CC</sub> = +5V,  $T_A$  = +25°C, unless otherwise noted.)

# μP Reset Circuits with Capacitor-Adjustable Reset/Watchdog Timeout Delay

## **Typical Operating Characteristics (continued)**

(V<sub>CC</sub> = +5V,  $T_A$  = +25°C, unless otherwise noted.)

# μP Reset Circuits with Capacitor-Adjustable Reset/Watchdog Timeout Delay

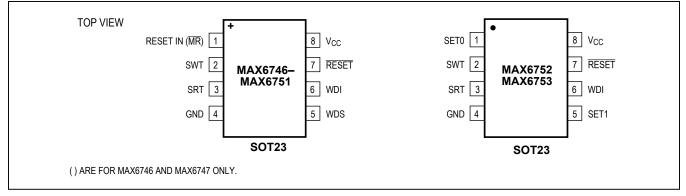

## **Pin Configurations**

## **Pin Descriptions**

|                    | PIN                 |                    |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------|---------------------|--------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX6746<br>MAX6747 | MAX6748–<br>MAX6751 | MAX6752<br>MAX6753 | NAME     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1                  | _                   | _                  | MR       | Manual-Reset Input. Pull $\overline{\text{MR}}$ low to manually reset the device. Reset remains asserted for the reset timeout period after $\overline{\text{MR}}$ is released.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                    | 1                   |                    | RESET IN | Reset Input. High-impedance input to the adjustable reset comparator.<br>Connect RESET IN to the center point of an external resistor-divider to<br>set the threshold of the externally monitored voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| _                  | _                   | 1                  | SET0     | Logic Input. SET0 selects watchdog window ratio or disables the watchdog timer. See Table 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2                  | 2                   | 2                  | SWT      | Watchdog Timeout Input.<br>MAX6746–MAX6751: Connect a capacitor between SWT and ground to<br>set the basic watchdog timeout period ( $t_{WD}$ ). Determine the period by<br>the formula $t_{WD} = 4.94 \times 10^6 \times C_{SWT}$ with $t_{WD}$ in seconds and $C_{SWT}$<br>in Farads. Extend the basic watchdog timeout period by using the WDS<br>input. Connect SWT to ground to disable the watchdog timer function.<br>MAX6752/MAX6753: Connect a capacitor between SWT and ground<br>to set the slow watchdog timeout period ( $t_{WD2}$ ). Determine the slow<br>watchdog period by the formula: $t_{WD2} = 0.65 \times 10^9 \times C_{SWT}$ with $t_{WD2}$ in<br>seconds and $C_{SWT}$ in Farads. The fast watchdog timeout period is set<br>by pin strapping SET0 and SET1 (Connect SET0 high and SET1 low to<br>disable the watchdog timer function.) See Table 1. |

| 3                  | 3                   | 3                  | SRT      | Reset Timeout Input. Connect a capacitor from SRT to GND to select the reset timeout period. Determine the period as follows: $t_{RP}$ = 4.94 x $10^6$ x C <sub>SRT</sub> with $t_{RP}$ in seconds and C <sub>SRT</sub> in Farads.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4                  | 4                   | 4                  | GND      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5                  | 5                   | _                  | WDS      | Watchdog Select Input. WDS selects the watchdog mode. Connect WDS to ground to select normal mode and the watchdog timeout period. Connect WDS to $V_{CC}$ to select extended mode, multiplying the basic timeout period by a factor of 128. A change in the state of WDS clears the watchdog timer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

# µP Reset Circuits with Capacitor-Adjustable Reset/Watchdog Timeout Delay

## **Pin Descriptions (continued)**

|                    | PIN                 |                    |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|--------------------|---------------------|--------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MAX6746<br>MAX6747 | MAX6748–<br>MAX6751 | MAX6752<br>MAX6753 | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| _                  | _                   | 5                  | SET1            | Logic Input. SET1 selects the watchdog window ratio or disables the watchdog timer. See Table 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 6                  | 6                   | 6                  | WDI             | <ul> <li>Watchdog Input.</li> <li>MAX6746–MAX6751: A falling transition must occur on WDI within the selected watchdog timeout period or a reset pulse occurs. The watchdog timer clears when a transition occurs on WDI or whenever RESET is asserted. Connect SWT to ground to disable the watchdog timer function.</li> <li>MAX6752/MAX6753: WDI falling transitions within periods shorter than tWD1 or longer than tWD2 force RESET to assert low for the reset timeout period. The watchdog timer clears when a valid transition occurs on WDI or whenever RESET is deasserted. The watchdog timer clears when a valid transition occurs on WDI or whenever RESET is asserted. Connect SET0 high and SET low to disable the watchdog timer function. See the Watchdog Timer section.</li> </ul> |  |

| 7                  | 7                   | 7                  | RESET           | Push/Pull or Open-Drain Reset Output. $\overline{\text{RESET}}$ asserts whenever $V_{CC}$ or $\overline{\text{RESET}}$ IN drops below the selected reset threshold voltage (V <sub>TH</sub> or V <sub>RESET</sub> IN, respectively) or manual reset is pulled low. $\overline{\text{RESET}}$ remains low for the reset timeout period after all reset conditions are deasserted, and then goes high. The watchdog timer triggers a reset pulse (t_RP) whenever a watchdog fault occurs.                                                                                                                                                                                                                                                                                                               |  |

| 8                  | 8                   | 8                  | V <sub>CC</sub> | Supply Voltage. $V_{CC}$ is the power-supply input and the input for fixed threshold $V_{CC}$ monitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

# µP Reset Circuits with Capacitor-Adjustable Reset/Watchdog Timeout Delay

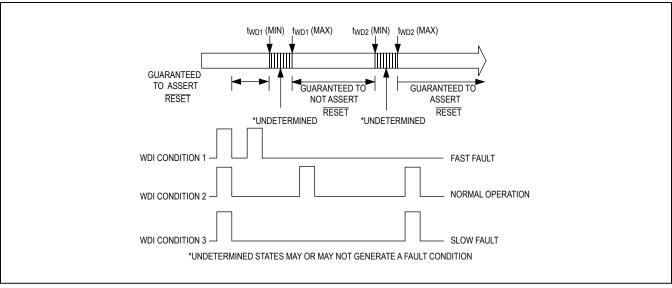

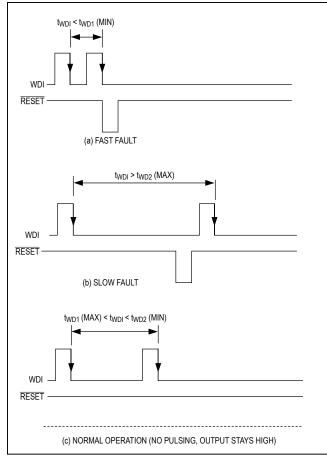

Figure 1. MAX6752/MAX6753 Detailed Watchdog Input Timing Relationship

### **Detailed Description**

The MAX6746–MAX6753 assert a reset signal whenever the V<sub>CC</sub> supply voltage or RESET IN falls below its reset threshold. The reset output remains asserted for the reset timeout period after V<sub>CC</sub> and RESET IN rise above its respective reset threshold. A watchdog timer triggers a reset pulse whenever a watchdog fault occurs.

The reset and watchdog delays are adjustable with external capacitors. The MAX6746–MAX6751 contain a watchdog select input that extends the watchdog timeout period to 128x.

The MAX6752 and MAX6753 have a sophisticated watchdog timer that detects when the processor is running outside an expected window of operation. The watchdog signals a fault when the input pulses arrive too early (faster that the selected  $t_{WD1}$  timeout period) or too late (slower than the selected  $t_{WD2}$  timeout period) (see Figure 1).

#### **Reset Output**

The reset output is typically connected to the reset input of a  $\mu$ P. A  $\mu$ P's reset input starts or restarts the  $\mu$ P in a known state. The MAX6746–MAX6753  $\mu$ P supervisory circuits provide the reset logic to prevent code-execution errors during power-up, power-down, and brownout conditions (see the <u>Typical Operating Circuit</u>). RESET changes from high to low whenever the monitored voltage, RESET IN and/or V<sub>CC</sub> drop below the reset threshold voltages. Once V<sub>RESET IN</sub> and/or V<sub>CC</sub> exceeds its respective reset threshold voltage(s), RESET remains low for the reset timeout period, then goes high. **RESET** is guaranteed to be in the correct logic state for  $V_{CC}$  greater than 1V. For applications requiring valid reset logic when  $V_{CC}$  is less than 1V, see the <u>Ensuring a Valid RESET Down to VCC = 0V</u> (Push-Pull RESET) section.

#### **RESET IN Threshold**

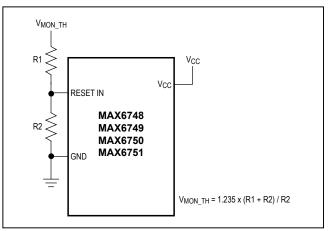

The MAX6748–MAX6751 monitor the voltage on RESET IN using an adjustable reset threshold (V<sub>RESET IN</sub>) set with an external resistor voltage-divider (Figure 2). Use the following formula to calculate the externally monitored voltage (V<sub>MON TH</sub>):

Figure 2. Calculating the Monitored Threshold Voltage (VMON TH)

# µP Reset Circuits with Capacitor-Adjustable Reset/Watchdog Timeout Delay

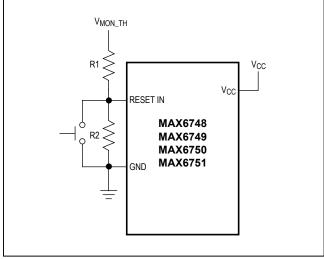

Figure 3. Adding an External Manual-Reset Function to the MAX6748–MAX6751

where  $V_{MON\_TH}$  is the desired reset threshold voltage and  $V_{TH}$  is the reset input threshold (1.235V). Resistors R1 and R2 can have very high values to minimize current consumption due to low leakage currents. Set R2 to some conveniently high value (500k $\Omega$ , for example) and calculate R1 based on the desired reset threshold voltage, using the following formula:

R1 = R2 x ( $V_{MON}_{TH}/V_{RESET IN}$  - 1) (Ω)

The MAX6748 and MAX6749 do not monitor  $V_{CC}$  supply voltage; therefore,  $V_{CC}$  must be greater than 1.5V to guarantee RESET IN threshold accuracy and

timing performance. The MAX6748 and MAX6749 can be configured to monitor V\_{CC} voltage by connecting V\_{CC} to V\_{MON\_TH}.

#### Dual-Voltage Monitoring (MAX6750/MAX6751)

The MAX6750 and MAX6751 contain both factory-trimmed threshold voltages and an adjustable reset threshold input, allowing the monitoring of two voltages,  $V_{CC}$  and  $V_{MON}_{TH}$  (see Figure 2). RESET is asserted when either of the voltages fall below its respective threshold voltages.

#### Manual Reset (MAX6746/MAX6747)

Many  $\mu$ P-based products require manual-reset capability to allow an operator or external logic circuitry to initiate a reset. The manual-reset input ( $\overline{MR}$ ) can connect directly to a switch without an external pullup resistor or debouncing network.  $\overline{MR}$  is internally pulled up to V<sub>CC</sub> and, therefore, can be left unconnected if unused.

$\overline{\text{MR}}$  is designed to reject fast, falling transients (typically 100ns pulses) and must be held low for a minimum of 1µs to assert the reset output. A 0.1µF capacitor from  $\overline{\text{MR}}$  to ground provides additional noise immunity. After  $\overline{\text{MR}}$  transitions from low to high, reset remains asserted for the duration of the reset timeout period.

A manual-reset option can easily be implemented with the MAX6748–MAX6751 by connecting a normally open momentary switch in parallel with R2 (Figure 3). When the switch is closed, the voltage on RESET IN goes to zero, initiating a reset. Similar to the MAX6746/MAX6747 manual reset, reset remains asserted while the voltage at RESET IN is zero and for the reset timeout period after the switch is opened.

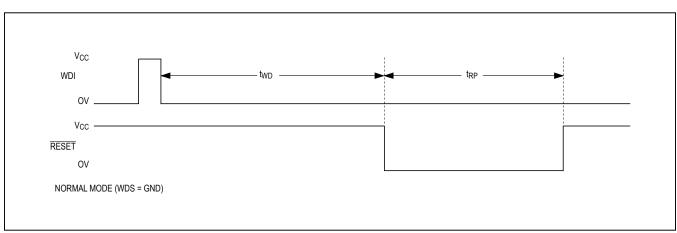

Figure 4a. Watchdog Timing Diagram, WDS = GND

## µP Reset Circuits with Capacitor-Adjustable Reset/Watchdog Timeout Delay

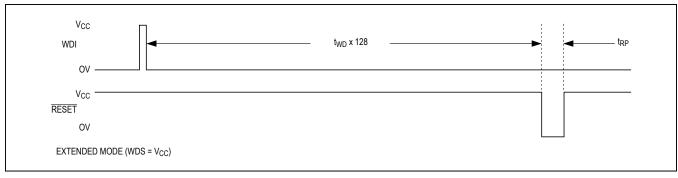

Figure 4b. Watchdog Timing Diagram, WDS =  $V_{CC}$

#### Watchdog Timer

#### MAX6746-MAX6751

The watchdog's circuit monitors the  $\mu$ P's activity. It the  $\mu$ P does not toggle the watchdog input (WDI) within t<sub>WD</sub> (user-selected), RESET asserts for the reset timeout period. The internal watchdog timer is cleared by any event that asserts RESET, by a falling transition at WDI (which can detect pulses as short as 300ns), or by a transition at WDS. The watchdog timer remains cleared while reset is asserted; as soon as reset is released, the timer starts counting.

The MAX6746–MAX6751 feature two modes of watchdog operation: normal mode and extended mode. In normal mode (Figure 4a), the watchdog timeout period is determined by the value of the capacitor connected between SWT and ground. In extended mode (Figure 4b), the watchdog timeout period is multiplied by 128. For example, in extended mode, a  $0.1\mu$ F capacitor gives a watchdog timeout period of 65s (see the Extended-Mode Watchdog Timeout Period vs. C<sub>SWT</sub> graph in the *Typical Operating Circuit*). To disable the watchdog timer function, connect SWT to ground.

#### MAX6752/MAX6753

The MAX6752 and MAX6753 have a windowed watchdog timer that asserts  $\overline{\text{RESET}}$  for the adjusted reset timeout period when the watchdog recognizes a fast watchdog fault (t<sub>WDI</sub> < t<sub>WD1</sub>), or a slow watchdog fault (period > t<sub>WD2</sub>). The reset timeout period is adjusted independently of the watchdog timeout period.

The slow watchdog period (t<sub>WD2</sub>) is calculated as follows:

$t_{WD2} = 0.65 \times 10^9 \times C_{SWT}$

with t<sub>WD2</sub> in seconds and C<sub>SWT</sub> in Farads.

The fast watchdog period  $(t_{WD1})$  is selectable as a ratio from the slow watchdog fault period  $(t_{WD2})$ . Select the fast watchdog period by pin strapping SET0 and SET1, where high is V<sub>CC</sub> and low is GND. Table 1 illustrates

#### Table 1. Min/Max Watchdog Setting

| SET0 | SET1 | RATIO             |  |

|------|------|-------------------|--|

| Low  | Low  | 8                 |  |

| Low  | High | 16                |  |

| High | Low  | Watchdog Disabled |  |

| High | High | 64                |  |

the SET0 and SET1 configuration for the 8, 16, and 64 window ratio (  $t_{WD2}/t_{WD1}).$

For example, if  $C_{SWT}$  is 1500pF, and SET0 and SET1 are low, then  $t_{WD2}$  is 975ms (typ) and  $t_{WD1}$  is 122ms (typ).

**RESET** asserts if the watchdog input has two falling edges too close to each other (faster than  $t_{WD1}$ ) (Figure 5a) or falling edges that are too far apart (slower than  $t_{WD2}$ ) (Figure 5b). Normal watchdog operation is displayed in Figure 5c. The internal watchdog timer is cleared when a WDI falling edge is detected within the valid watchdog window or when RESET is deasserted. All WDI inputs are ignored while RESET is asserted.

The watchdog timer begins to count after RESET is deasserted. The watchdog timer clears and begins to count after a valid WDI falling logic input. WDI falling transitions within periods shorter than  $t_{WD1}$  or longer than  $t_{WD2}$  force RESET to assert low for the reset timeout period. WDI falling transitions within the  $t_{WD1}$  and  $t_{WD2}$  window do not assert RESET. WDI transitions between  $t_{WD1(min)}$  and  $t_{WD1(max)}$  or  $t_{WD2(min)}$  and  $t_{WD2(max)}$  are not guaranteed to assert or deassert RESET. To guarantee that the window watchdog does not assert RESET, strobe WDI between  $t_{WD1(max)}$  and  $t_{WD2(min)}$ . The watchdog timer is cleared when RESET is asserted or after a falling transition on WDI, or after a state change on SET0 or SET1. Disable the watchdog timer by connecting SET0 high and SET1 low.

# µP Reset Circuits with Capacitor-Adjustable Reset/Watchdog Timeout Delay

Figure 5. MAX6752/MAX6753 Window Watchdog Diagram

## **Applications Information**

#### Selecting Reset/Watchdog Timeout Capacitor

The reset timeout period is adjustable to accommodate a variety of  $\mu$ P applications. Adjust the reset timeout period (t<sub>RP</sub>) by connecting a capacitor (C<sub>SRT</sub>) between SRT and ground. Calculate the reset timeout capacitor as follows:

#### $C_{SRT} = t_{RP}/(4.94 \times 10^6)$

with t<sub>RP</sub> in seconds and C<sub>SRT</sub> in Farads.

The watchdog timeout period is adjustable to accommodate a variety of  $\mu$ P applications. With this feature, the watchdog timeout can be optimized for software execution. The programmer can determine how often the watchdog time should be serviced. Adjust the watchdog timeout period (t<sub>WD</sub>) by connecting a specific value capacitor (C<sub>SWT</sub>) between SWT and GND. For normal mode operation, calculate the watchdog timeout capacitor as follows:

$$C_{SWT} = t_{WD}/(4.94 \times 106)$$

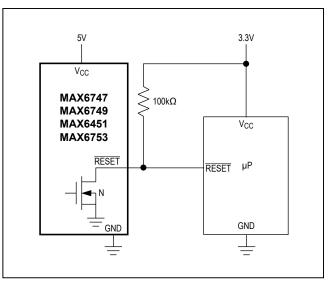

Figure 6. Interfacing to Other Voltage Levels

with  $t_{WD}\xspace$  in seconds and  $C_{SWT}\xspace$  in Farads.

For the MAX6752 and MAX6753 windowed watchdog function, calculate the slow watchdog period,  $t_{WD2}$  as follows:

$$t_{WD2} = 0.65 \times 10^9 \times C_{SWT}$$

$C_{SRT}$  and  $C_{SWT}$  must be a low-leakage (< 10nA) type capacitor. Ceramic capacitors are recommended.

#### **Transient Immunity**

In addition to issuing a reset to the  $\mu$ P during power-up, power-down, and brownout conditions, these supervisors are relatively immune to short-duration supply transients (glitches). The Maximum Transient Duration vs. Reset Threshold Overdrive graph in the <u>Typical Operating</u> <u>Characteristics</u> shows this relationship.

The area below the curves of the graph is the region in which these devices typically do not generate a reset pulse. This graph was generated using a falling pulse applied to V<sub>CC</sub>, starting above the actual reset threshold (V<sub>TH</sub>) and ending below it by the magnitude indicated (reset threshold overdrive). As the magnitude of the transient increases (farther below the reset threshold), the maximum allowable pulse width decreases. Typically, a V<sub>CC</sub> transient that goes 100mV below the reset threshold and lasts 50µs or less does not cause a reset pulse to be issued. For applications where the power supply to V<sub>CC</sub> has high transient rates, dV/dt > 5V/50µS, an RC filter on V<sub>CC</sub> is required. See Figure 8. Application Circuit for High-Input Voltage Transient Applications.

## μP Reset Circuits with Capacitor-Adjustable Reset/Watchdog Timeout Delay

# Interfacing to Other Voltages for Logic Compatibility

The open-drain  $\overrightarrow{\text{RESET}}$  output can be used to interface to a  $\mu$ P with other logic levels. As shown in Figure 6, the open-drain output can be connected to voltages from 0 to 6V.

Generally, the pullup resistor connected to  $\overline{\text{RESET}}$  connects to the supply voltage that is being monitored at the IC's V<sub>CC</sub> pin. However, some systems can use the open-drain output to level-shift from the monitored supply to reset circuitry powered by some other supply. Keep in mind that as the supervisor's V<sub>CC</sub> decreases towards 1V, so does the IC's ability to sink current at  $\overline{\text{RESET}}$ . Also, with any pullup resistor,  $\overline{\text{RESET}}$  is pulled high as V<sub>CC</sub> decays toward zero. The voltage where this occurs depends on the pullup resistor value and the voltage to which it is connected.

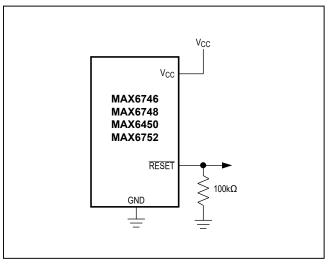

Figure 7. Ensuring  $\overline{RESET}$  Valid to  $V_{CC} = 0V$

# Ensuring a Valid RESET Down to $V_{CC} = 0V$ (Push-Pull RESET)

When V<sub>CC</sub> falls below 1V,  $\overline{\text{RESET}}$  current sinking capabilities decline drastically. The high-impedance CMOS logic inputs connected to  $\overline{\text{RESET}}$  can drift to undetermined voltages. This presents no problems in most applications, since most  $\mu$ Ps and other circuitry do not operate with V<sub>CC</sub> below 1V.

In those applications where RESET must be valid down to 0V, add a pulldown resistor between RESET and GND for the MAX6746/MAX6748/MAX6750/MAX6752 push/pull outputs. The resistor sinks any stray leakage currents, holding RESET low (Figure 7). The value of the pulldown resistor is not critical; 100k $\Omega$  is large enough not to load RESET and small enough to pull RESET to ground. The external pulldown cannot be used with the open-drain reset outputs.

Figure 8. Application Circuit for High-Input Voltage Transient Applications

# μP Reset Circuits with Capacitor-Adjustable Reset/Watchdog Timeout Delay

# Table 2. Reset Threshold Voltage Suffix $(T_A = -40^{\circ}C \text{ to } +125^{\circ}C)$

| SUFFIX                     | MIN   | TYP   | MAX   |

|----------------------------|-------|-------|-------|

| 50                         | 4.900 | 5.000 | 5.100 |

| 49                         | 4.802 | 4.900 | 4.998 |

| 48                         | 4.704 | 4.800 | 4.896 |

| 47                         | 4.606 | 4.700 | 4.794 |

| 46                         | 4.533 | 4.625 | 4.718 |

| 45                         | 4.410 | 4.500 | 4.590 |

| 44                         | 4.288 | 4.375 | 4.463 |

| 43                         | 4.214 | 4.300 | 4.386 |

| 42                         | 4.116 | 4.200 | 4.284 |

| 41                         | 4.018 | 4.100 | 4.182 |

| 40                         | 3.920 | 4.000 | 4.080 |

| 39                         | 3.822 | 3.900 | 3.978 |

| 38                         | 3.724 | 3.800 | 3.876 |

| 37                         | 3.626 | 3.700 | 3.774 |

| 36                         | 3.528 | 3.600 | 3.672 |

| 35                         | 3.430 | 3.500 | 3.570 |

| 34                         | 3.332 | 3.400 | 3.468 |

| 33                         | 3.234 | 3.300 | 3.366 |

| 32                         | 3.136 | 3.200 | 3.264 |

| 32A<br>(MAX6752AKA32 Only) | 3.136 | 3.200 | 3.224 |

| 31                         | 3.014 | 3.075 | 3.137 |

| 30                         | 2.940 | 3.000 | 3.060 |

| 29                         | 2.867 | 2.925 | 2.984 |

| 28                         | 2.744 | 2.800 | 2.856 |

| 27                         | 2.646 | 2.700 | 2.754 |

| 26                         | 2.573 | 2.625 | 2.678 |

| 25                         | 2.450 | 2.500 | 2.550 |

| 24                         | 2.352 | 2.400 | 2.448 |

| 23                         | 2.267 | 2.313 | 2.359 |

| 22                         | 2.144 | 2.188 | 2.232 |

| 21                         | 2.058 | 2.100 | 2.142 |

| 20                         | 1.960 | 2.000 | 2.040 |

| 19                         | 1.862 | 1.900 | 1.938 |

| 18                         | 1.764 | 1.800 | 1.836 |

| 17                         | 1.632 | 1.665 | 1.698 |

| 16                         | 1.544 | 1.575 | 1.607 |

### **Table 3. Standard Version Table**

| PART        | TOP MARK |  |  |

|-------------|----------|--|--|

| MAX6746KA16 | AEDI     |  |  |

| MAX6746KA23 | AEDJ     |  |  |

| MAX6746KA26 | AEDK     |  |  |

| MAX6746KA29 | AALN     |  |  |

| MAX6746KA46 | AEDL     |  |  |

| MAX6747KA16 | AALO     |  |  |

| MAX6747KA23 | AEDM     |  |  |

| MAX6747KA26 | AEDN     |  |  |

| MAX6747KA29 | AEDO     |  |  |

| MAX6747KA46 | AEDP     |  |  |

| MAX6748KA   | AALP     |  |  |

| MAX6749KA   | AALQ     |  |  |

| MAX6750KA16 | AEDQ     |  |  |

| MAX6750KA23 | AALR     |  |  |

| MAX6750KA26 | AEDR     |  |  |

| MAX6750KA29 | AEDS     |  |  |

| MAX6750KA46 | AEDT     |  |  |

| MAX6751KA16 | AEDU     |  |  |

| MAX6751KA23 | AEDV     |  |  |

| MAX6751KA26 | AEDW     |  |  |

| MAX6751KA29 | AEDX     |  |  |

| MAX6751KA46 | AEDY     |  |  |

| MAX6752KA16 | AEDZ     |  |  |

| MAX6752KA23 | AEEA     |  |  |

| MAX6752KA26 | AALT     |  |  |

| MAX6752KA29 | AEEB     |  |  |

| MAX6752KA46 | AEEC     |  |  |

| MAX6753KA16 | AEED     |  |  |

| MAX6753KA23 | AEEE     |  |  |

| MAX6753KA26 | AEEF     |  |  |

| MAX6753KA29 | AEEG     |  |  |

| MAX6753KA46 | AEEH     |  |  |

**Note:** Standard versions are shown in **bold**. There is a 2500-piece minimum order increment for standard versions.

Sample stock is typically held on standard versions only. Nonstandard versions require a minimum order increment of 10,000 pieces. Contact factory for availability

# μP Reset Circuits with Capacitor-Adjustable Reset/Watchdog Timeout Delay

## **Selector Guide**

| PART    | FIXED V <sub>CC</sub><br>RESET<br>THRESHOLD | ADJUSTABLE<br>RESET<br>THRESHOLD | STANDARD<br>WATCHDOG<br>TIMER | MIN/MAX<br>WATCHDOG<br>TIMER | PUSH/ PULL<br>RESET | OPEN-DRAIN<br>RESET | MANUAL-<br>RESET<br>INPUT |

|---------|---------------------------------------------|----------------------------------|-------------------------------|------------------------------|---------------------|---------------------|---------------------------|

| MAX6746 | X                                           | —                                | Х                             | —                            | Х                   | —                   | Х                         |

| MAX6747 | X                                           | —                                | Х                             | —                            | —                   | Х                   | Х                         |

| MAX6748 | _                                           | Х                                | Х                             | —                            | Х                   | —                   | _                         |

| MAX6749 | _                                           | Х                                | Х                             | —                            | —                   | Х                   | _                         |

| MAX6750 | X                                           | Х                                | Х                             | —                            | Х                   | —                   | _                         |

| MAX6751 | X                                           | Х                                | Х                             | —                            | —                   | Х                   | _                         |

| MAX6752 | X                                           | —                                | _                             | Х                            | Х                   | —                   | _                         |

| MAX6753 | X                                           | —                                |                               | Х                            | _                   | Х                   | _                         |

## µP Reset Circuits with Capacitor-Adjustable Reset/Watchdog Timeout Delay

## **Ordering Information**

| PART              | TEMP RANGE      | PIN-PACKAGE |

|-------------------|-----------------|-------------|

| MAX6746KA -T      | -40°C to +125°C | 8 SOT23     |

| MAX6746KA+T       | -40°C to +125°C | 8 SOT23     |

| <br>MAX6747KA+T   | -40°C to +125°C | 8 SOT23     |

| <br>MAX6746KA/V+T | -40°C to +125°C | 8 SOT23     |

| MAX6746KA23/V+T   | -40°C to +125°C | 8 SOT23     |

| MAX6746KA28/V+T   | -40°C to +125°C | 8 SOT23     |

| MAX6746KA29/V+T   | -40°C to +125°C | 8 SOT23     |

| MAX6746KA31/V+T   | -40°C to +125°C | 8 SOT23     |

| MAX6747KAT        | -40°C to +125°C | 8 SOT23     |

| MAX6747KA/V+T     | -40°C to +125°C | 8 SOT23     |

| MAX6747KA30/V+T   | -40°C to +125°C | 8 SOT23     |

| MAX6747KA31/V+T   | -40°C to +125°C | 8 SOT23     |

| MAX6747KA46/V+T   | -40°C to +125°C | 8 SOT23     |

| MAX6748KA+T       | -40°C to +125°C | 8 SOT23     |

| MAX6749KA+T       | -40°C to +125°C | 8 SOT23     |

| MAX6750KA+T       | -40°C to +125°C | 8 SOT23     |

| MAX6750KA/V+T     | -40°C to +125°C | 8 SOT23     |

| MAX6750KA30/V+T   | -40°C to +125°C | 8 SOT23     |

| MAX6750KA32/V+T   | -40°C to +125°C | 8 SOT23     |

| MAX6751KAT        | -40°C to +125°C | 8 SOT23     |

| MAX6751KA+T       | -40°C to +125°C | 8 SOT23     |

| MAX6751KA/V+T*    | -40°C to +125°C | 8 SOT23     |

| MAX6751KA17/V+T   | -40°C to +125°C | 8 SOT23     |

| MAX6751KA30/V+T   | -40°C to +125°C | 8 SOT23     |

| MAX6751KA50/V+T   | -40°C to +125°C | 8 SOT23     |

| MAX6752KA+T       | -40°C to +125°C | 8 SOT23     |

| MAX6752KA/V+T*    | -40°C to +125°C | 8 SOT23     |

| MAX6752AKA32+T    | -40°C to +125°C | 8 SOT23     |

| MAX6752AKA32/V+T  | -40°C to +125°C | 8 SOT23     |

| MAX6752KA32/V+T   | -40°C to +125°C | 8 SOT23     |

| MAX6753KAT        | -40°C to +125°C | 8 SOT23     |

| MAX6753KA+T       | -40°C to +125°C | 8 SOT23     |

| MAX6753KA/V+T     | -40°C to +125°C | 8 SOT23     |

| MAX6753KA28/V+T   | -40°C to +125°C | 8 SOT23     |

| MAX6753KA29/V+T   | -40°C to +125°C | 8 SOT23     |

| MAX6753KA30/V+T   | -40°C to +125°C | 8 SOT23     |

| MAX6753KA46/V+T   | -40°C to +125°C | 8 SOT23     |

**Note:** "\_\_" represents the two number suffix needed when ordering the reset threshold voltage value for the MAX6746/MAX6747 and MAX6750–MAX6753. The reset threshold voltages are available in approximately 100mV increments. Table 2 contains the suffix and reset factory-trimmed voltages. All devices are available in tape-and-reel only. There is a 2500-piece minimum order increment for standard versions (see Table 3). Sample stock is typically held on standard versions only. Nonstandard versions require a minimum order increment of 10,000 pieces. Contact factory for availability. Devices are available in both leaded and lead(Pb)-free packaging. +Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

N denotes an automotive qualified part.

\*Future product—contact factory for availability.

PROCESS: BICMOS

## μP Reset Circuits with Capacitor-Adjustable Reset/Watchdog Timeout Delay

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                        | PAGES<br>CHANGED |

|--------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0                  | 7/02             | Initial release                                                                                                                                    | _                |

| 3                  | 12/05            | Added the lead-free notation                                                                                                                       | 1                |

| 4                  | 9/10             | Added the automotive version of the MAX6746 and the MAX6753 and revised the <i>Typical Operating Characteristics</i>                               | 1, 4             |

| 5                  | 12/10            | Added the automotive version of the MAX6750                                                                                                        | 1                |

| 6                  | 4/11             | Added the automotive version of the MAX6747                                                                                                        | 1                |

| 7                  | 12/13            | Added the automotive version of the MAX6751                                                                                                        | 1                |

| 8                  | 2/14             | Added a future product reference to MAX6751KA/V+T                                                                                                  | 1                |

| 9                  | 5/14             | Corrected typo                                                                                                                                     | 10               |

| 10                 | 6/14             | Added the automotive version of the MAX6752                                                                                                        | 1                |

| 11                 | 9/15             | Added MAX6752A to data sheet with new limits                                                                                                       | 2, 12, 14        |

| 12                 | 12/15            | Added lead-free part numbers to <i>Ordering Information</i> table and lead-free package code to <i>Package Information</i> table                   | 14               |

| 13                 | 2/16             | Added MAX6752AKA32+T to Ordering Information table                                                                                                 | 14               |

| 14                 | 9/16             | Updated t <sub>WD</sub> equation value in <i>Pin Configuration</i> table and <i>Applications Information</i> section                               | 6, 10            |

| 15                 | 1/17             | Added text to Transient Immunity section and added Figure 8                                                                                        | 10, 11           |

| 16                 | 10/17            | Added AEC qualification text to <i>Benefits and Features</i> section and updated<br><i>Ordering Information</i> table with additional part numbers | 1, 14            |

| 17                 | 12/17            | Updated Ordering Information table with additional part numbers                                                                                    | 14               |

| 18                 | 3/18             | Updated Absolute Maxim Rating and added Package Information section                                                                                | 2                |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated: MAX6753KA31/V+T