# Dual 24-Bit, Low-Power, High-SNR, 4ksps Delta-Sigma ADCs with Integrated PGAs

### **General Description**

The MAX11284 is a dual 24-bit delta sigma ADC that achieves excellent SNR while dissipating a low 3.6mW per ADC. Precision DC and AC measurements can be made at sample rates up to 4ksps. Integral nonlinearity is guaranteed to 4ppm maximum and the THD is -120dB. The MAX11284 communicates through an SPI-compatible serial interface and is available in a small, 40-pin TQFN package.

The PGAs can operate in either low-noise  $(9.1\text{nV}/\sqrt{\text{Hz}})$  or low-power  $(13.6\text{nV}/\sqrt{\text{Hz}})$  mode, and have selectable gain values ranging from 1x to 128x. Optional buffers are also included to provide isolation of the signal inputs from the switched capacitor sampling network. This allows the ADCs to be used with high-impedance sources without compromising available dynamic range.

The MAX11284 operates from a single 2.7V to 3.6V analog supply, or split  $\pm$ 1.8V analog supplies, allowing the analog input to be sampled below ground. The digital supply range is 2.0V to 3.6V, allowing communication with 2.5V, 3V, or 3.3V logic.

### **Applications**

- Seismic Data Acquisition

- Scientific Instrumentation

- High-Precision Portable Sensors

- Medical Equipment

- ATE

#### **Benefits and Features**

- High Resolution for Instrumentation Applications That Require a Wide Dynamic Range

- 131dB SNR at 31.25sps in Buffer Mode

- 114dB SNR at 2000sps in Buffer Mode

- Low Power

- Digital Current with FIR Filter, 1ksps: 500µA

- Analog Current PGA Low-Power Mode: 2.1mA

- Sleep Current: 1.2µA

- High Accuracy for DC Measurements

- 1ppm INL (typ), 4ppm (max)

- Single/Split Analog Supplies Provide Input Voltage Range Flexibility

- 2.7V to 3.6V (Single-Supply) or ±1.8V (Split Supplies)

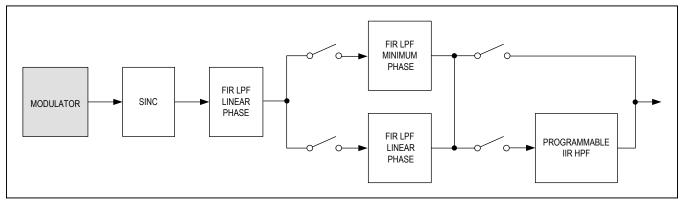

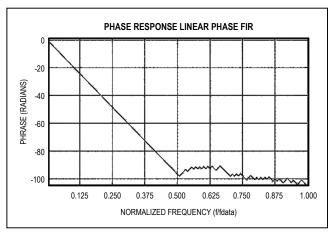

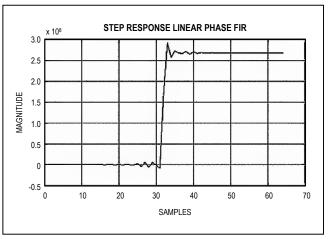

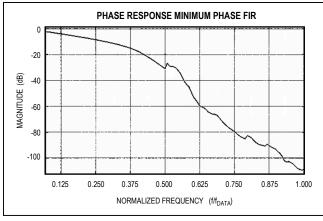

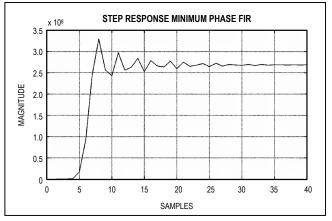

- Digital Filters

- Programmable SINC + FIR + IIR

- Linear/Minimum Phase Response

- Programmable High-Pass Filter

- Selectable FIR Data Rates: 31.25sps to 4ksps

- Enables System Integration

- Low-Noise and Low-Power mode PGA with Gains of 1, 2, 4, 8, 16, 32, 64, 128

- Signal Buffer Optional

- 2 General-Purpose I/Os

- Integrated Offset and Gain Self-Calibration and System Gain and Offset Calibration Registers

- Small 40-Pin TQFN Package

Ordering Information appears at end of data sheet.

# Dual 24-Bit, Low-Power, High-SNR, 4ksps Delta-Sigma ADCs with Integrated PGAs

#### **Absolute Maximum Ratings**

| AVDD_A/B to AVSS_A/B0.3V to +3.9V                              | [ |

|----------------------------------------------------------------|---|

| DVDD_A/B to DGND_A/B0.3V to +3.9V                              |   |

| DVDD_A/B to AVSS_A/B0.3V to +3.9V                              | ( |

| AVSS_A/B to DGND_A/B1.95V to +0.3V                             | ( |

| Analog Inputs (AIN_, REF, CAP )                                | ( |

| to AVSS0.3V to the lower of 3.9V or (V <sub>AVDD</sub> + 0.3V) |   |

| Digital Inputs                                                 | ( |

| (RSTB_, SYNC_, DIN_, SCLK_, CLK, GPIO_)                        |   |

| to DGND0.3V to the lower of 3.9V or (V <sub>DVDD</sub> + 0.3V) | 5 |

| Digital Outputs (RDYB_, DOUT_, GPIO_)                          | l |

| to DGND0.3V to the lower of 3.9V or (V <sub>DVDD</sub> + 0.3V) | 5 |

| Digital Inputs                                                 |   |

| (RSTB_, SYNC_, DIN, SCLK, CSB_, GPIO_) to                      |   |

| AVSS0.3V to +3.9V                                              |   |

|                                                                |   |

### Package Thermal Characteristics (Note 1)

TQFN 6 x 6 x 0.75mm

Digital Outputs

| (RDYB_, DOUT_, GPIO_) to AVSS0.3V to +3.9V                               |

|--------------------------------------------------------------------------|

| CAPREG to DGND0.3V to +2.2V                                              |

| CAPREG to AVSS0.3V to +3.9V                                              |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ , multi-layer board) |

| TQFN (derate 37mW/°C above +70°C)2963mW                                  |

| Operating Temperature Range40°C to +85°C                                 |

| Junction Temperature (continuous)+150°C                                  |

| Storage Temperature Range65°C to +150°C                                  |

| Lead Temperature (soldering, 10s)+300°C                                  |

| Soldering Temperature (reflow)+260°C                                     |

|                                                                          |

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Electrical Characteristics**

$(V_{AVDD} = V_{AVDD} = V_{AVDD} = 2.7V, V_{AVSS} = V_{AVSS} = V_{AVSS} = 0V, V_{DVDD} = V_{DVDD} = V_{DVDD} = 2.0V, V_{REFP} = V_{REFP} = V_{REFP} = 2.5V, V_{REFN} = V_{REFN} = 0V; f_{DATA} = 1000$ sps, External Clock = 2.048MHz; Continuous conversion mode (SCYCLE = 0); PGA maximum output is 300mV below AVDD and minimum output is 300mV above AVSS,  $T_A = -40^{\circ}$ C to 85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.) (Note 2)

| PARAMETER              | SYMBOL                 | CONDITIONS                      | MIN | ТҮР  | MAX | UNITS  |  |  |

|------------------------|------------------------|---------------------------------|-----|------|-----|--------|--|--|

| STATIC PERFORMANCE     | •                      |                                 | ÷   |      |     |        |  |  |

|                        |                        | Bypass, buffer                  |     | 1    | 4   |        |  |  |

| Integral Nonlinearity  |                        | PGA = 1, 2                      |     | 1    |     |        |  |  |

| (Sample Rate = 250sps) | INL                    | PGA = 4                         |     | 1    | 6   | ppm    |  |  |

|                        |                        | PGA > 4                         |     | 2    |     |        |  |  |

| Offset Error           | V <sub>OS</sub>        | After system offset calibration |     | 10   |     | nV     |  |  |

| Offset Drift           | VOS DRIFT              |                                 |     | 50   |     | nV/°C  |  |  |

| Gain Error             | G <sub>ERR</sub>       | After system gain calibration   |     | 2    |     | ppm    |  |  |

| Gain Drift             | G <sub>ERR_DRIFT</sub> |                                 |     | 0.05 |     | ppm/°C |  |  |

| DC Common-Mode         | CMD                    | Bypass and Buffer mode          |     | 130  |     |        |  |  |

| Rejection (Note 4)     | CMR <sub>DC</sub>      | PGA gain = 4                    |     | 130  | dB  |        |  |  |

# Dual 24-Bit, Low-Power, High-SNR, 4ksps Delta-Sigma ADCs with Integrated PGAs

### **Electrical Characteristics (continued)**

$(V_{AVDD} = V_{AVDD\_A} = V_{AVDD\_B} = 2.7V, V_{AVSS} = V_{AVSS\_A} = V_{AVSS\_B} = 0V, V_{DVDD} = V_{DVDD\_A} = V_{DVDD\_B} = 2.0V, V_{REFP\_A} = V_{REFP} = V_{REFP\_B} = 2.5V, V_{REFN\_A} = V_{REFN\_B} = 0V$ ;  $f_{DATA} = 1000$  sps, External Clock = 2.048MHz; Continuous conversion mode (SCYCLE = 0); PGA maximum output is 300mV below AVDD and minimum output is 300mV above AVSS,  $T_A = -40^{\circ}$ C to 85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.) (Note 2)

| PARAMETER                             | SYMBOL              | CONDITIONS                                                                         | MIN                         | ТҮР   | MAX                         | UNITS |  |  |  |  |

|---------------------------------------|---------------------|------------------------------------------------------------------------------------|-----------------------------|-------|-----------------------------|-------|--|--|--|--|

| AVDD, AVSS DC Supply                  |                     | Bypass and buffer mode                                                             |                             | 105   |                             | -10   |  |  |  |  |

| Rejection Ratio                       | PSRRA               | PGA gain = 4                                                                       |                             | dB    |                             |       |  |  |  |  |

| DVDD DC Supply Rejection              |                     | Bypass and buffer mode                                                             |                             | 125   |                             | ٩D    |  |  |  |  |

| Ratio                                 | PSRRD               | PGA gain = 4                                                                       |                             | 125   |                             | dB    |  |  |  |  |

| DYNAMIC PERFORMANCE                   |                     |                                                                                    |                             |       |                             |       |  |  |  |  |

| Signal-to-Noise Ratio                 |                     | Bypass, buffer, V <sub>AVDD</sub> = V <sub>REF</sub><br>= 3.6V (see Tables 1 to 6) | 113.6                       | 118   |                             |       |  |  |  |  |

| (Notes 4, 6)                          | SNR                 | PGA gain = 4, V <sub>AVDD</sub> = V <sub>REF</sub><br>= 3.6V (see Tables 1 to 6)   | 113.3                       | 117.5 |                             | dB    |  |  |  |  |

| Signal-to-Noise Ratio                 |                     | Bypass, buffer, V <sub>REF</sub> = 2.5V<br>(see Tables 1 to 6)                     | 110.5                       | 114.5 |                             | 10    |  |  |  |  |

| (Notes 4, 6)                          | SNR                 | PGA gain = 4, $V_{REF}$ = 2.5V<br>(see Tables 1 to 6)                              | 110                         | 114   |                             | dB    |  |  |  |  |

|                                       |                     | Bypass, buffer                                                                     |                             | -120  | -115                        |       |  |  |  |  |

|                                       |                     | PGA = 1, 2                                                                         |                             | -119  |                             |       |  |  |  |  |

| Total Harmonic Distortion             | TUD                 | PGA = 4                                                                            |                             | -119  | -112                        |       |  |  |  |  |

| (f <sub>SIGNAL</sub> = 31.25Hz)       | THD                 | PGA = 8                                                                            |                             | -119  |                             | dB    |  |  |  |  |

|                                       |                     | PGA = 16, 32, 64                                                                   |                             | -114  |                             |       |  |  |  |  |

|                                       |                     | PGA = 128                                                                          |                             | -110  |                             |       |  |  |  |  |

| Spurious-Free Dynamic                 | SFDR                | Bypass, buffer                                                                     |                             | 120   |                             | dD    |  |  |  |  |

| Range (f <sub>SIGNAL</sub> = 31.25Hz) | SFUR                | PGA = 4                                                                            |                             | dB    |                             |       |  |  |  |  |

| ANALOG INPUTS/REFEREN                 | CE INPUTS           |                                                                                    |                             |       |                             |       |  |  |  |  |

| AINI Valtaga Danga                    | M                   | Unipolar                                                                           | 0                           |       | V <sub>REF</sub>            | v     |  |  |  |  |

| AIN Voltage Range                     | V <sub>RNG</sub>    | Bipolar                                                                            | -V <sub>REF</sub>           |       | $V_{REF}$                   |       |  |  |  |  |

|                                       |                     | Bypass mode                                                                        | V <sub>AVSS</sub> +<br>0.05 |       | V <sub>AVDD</sub><br>- 0.05 |       |  |  |  |  |

| Absolute Input Voltage                | VABS <sub>RNG</sub> | PGA mode                                                                           | V <sub>AVSS</sub> +<br>0.3  | ,     | V <sub>AVDD</sub> -<br>1.3  | V     |  |  |  |  |

|                                       |                     | Buffer mode                                                                        | V <sub>AVSS</sub> + 0.1     |       |                             |       |  |  |  |  |

| AIN DC Input Leakage<br>(Note 4)      | IIN <sub>LEAK</sub> |                                                                                    | -10                         |       | +10                         | nA    |  |  |  |  |

| AIN Common-Mode Input<br>Conductance  | G <sub>AINCM</sub>  | Bypass                                                                             |                             | ±2    |                             | nA/V  |  |  |  |  |

# Dual 24-Bit, Low-Power, High-SNR, 4ksps Delta-Sigma ADCs with Integrated PGAs

### **Electrical Characteristics (continued)**

$(V_{AVDD} = V_{AVDD\_A} = V_{AVDD\_B} = 2.7V, V_{AVSS} = V_{AVSS\_A} = V_{AVSS\_B} = 0V, V_{DVDD} = V_{DVDD\_A} = V_{DVDD\_B} = 2.0V, V_{REFP\_A} = V_{REFP} = V_{REFP\_B} = 2.5V, V_{REFN} = V_{REFN\_A} = V_{REFN\_B} = 0V$ ;  $f_{DATA} = 1000$ sps, External Clock = 2.048MHz; Continuous conversion mode (SCYCLE = 0); PGA maximum output is 300mV below AVDD and minimum output is 300mV above AVSS,  $T_A = -40^{\circ}$ C to 85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.) (Note 2)

| PARAMETER                                              | SYMBOL               | CONDITIONS                       | MIN TYP  | P MAX               | UNITS               |  |

|--------------------------------------------------------|----------------------|----------------------------------|----------|---------------------|---------------------|--|

| AIN Common-Mode Input                                  |                      | Buffer                           | ±12      | 5                   |                     |  |

| Current                                                |                      | PGA                              | ±5       | nA                  |                     |  |

| AIN Differential Mode Input<br>Conductance             | G <sub>AINDIFF</sub> | Bypass                           | ±6       |                     | μΑ/V                |  |

| AIN Differential Mode Input                            |                      | Buffer                           | ±5       |                     |                     |  |

| Current                                                |                      | PGA                              | ±0.7     |                     | nA                  |  |

| REF Differential Input<br>Conductance                  | G <sub>REFDIFF</sub> | Active conversion state          | ±46.     | 5                   | μΑ/V                |  |

| REF Input Current at Power<br>Down                     | IREF_PD              | Sleep and standby states         | ±2.5     | 5                   | μA                  |  |

| AIN Input Capacitance                                  | C <sub>IN</sub>      | Buffer disabled                  | 3        |                     | pF                  |  |

| REF Input Capacitance                                  | C <sub>REF</sub>     | Buffer disabled                  | 4.5      |                     | pF                  |  |

| Input and REF Sampling<br>Rate                         | fS                   |                                  | 1.02     | 4                   | MHz                 |  |

| V <sub>REFP</sub> – V <sub>REFN</sub> Voltage<br>Range | VRABS <sub>RNG</sub> | (Note 5)                         |          | V <sub>AVDD</sub>   | V                   |  |

| REF Voltage Range                                      | V <sub>REF</sub>     |                                  | 2.0      | V <sub>AVDD</sub>   | V                   |  |

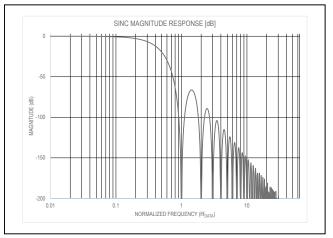

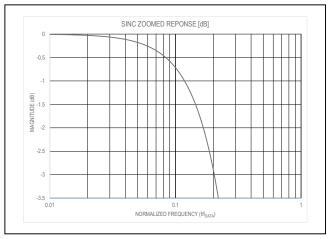

| DIGITAL FILTER RESPONSE                                | (Note 3)             |                                  |          |                     |                     |  |

| SINC FILTER                                            |                      |                                  |          |                     |                     |  |

| Bandwidth (-3dB)                                       | BW <sub>SINC</sub>   |                                  | 0.20     | 3                   | f <sub>DATA</sub>   |  |

| Settling Time (Latency)                                |                      |                                  | 5        |                     | 1/f <sub>DATA</sub> |  |

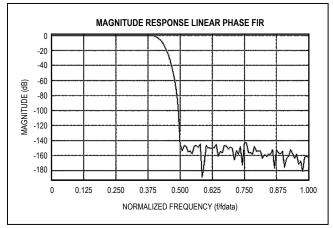

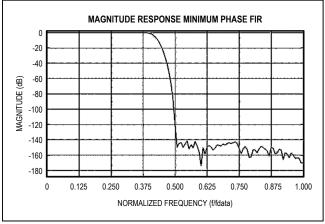

| FIR FILTER                                             |                      |                                  |          |                     |                     |  |

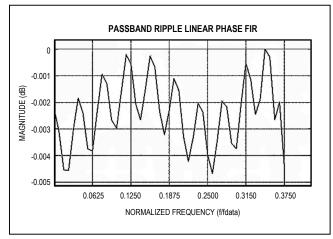

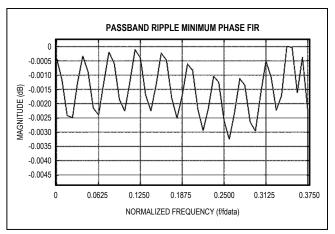

| Passband Ripple                                        |                      |                                  | -0.003   | +0.003              | dB                  |  |

| Passband (-0.01dB)                                     |                      |                                  | 0.375    | 0.375               | f <sub>DATA</sub>   |  |

| Bandwidth (-3dB)                                       | BW <sub>FIR</sub>    |                                  | 0.413    | 0.413               | f <sub>DATA</sub>   |  |

| High-Pass Filter Corner                                | f <sub>HP</sub>      | IIR filter; CTRL3 FILT bits = 11 | 0.000375 | 0.1                 | f <sub>DATA</sub>   |  |

| Stopband Attenuation                                   |                      |                                  | 135      |                     | dB                  |  |

| Stopband                                               | fstop                |                                  | 0.5      |                     | fDATA               |  |

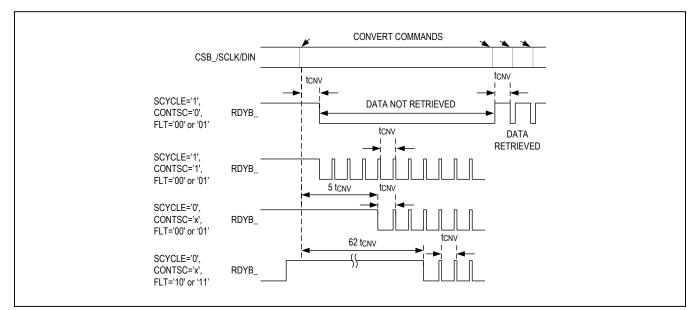

| Crown Dolou                                            |                      | Minimum phase filter             | 5        |                     | 4 /5                |  |

| Group Delay                                            |                      | Linear phase filter              | 31       | 1/f <sub>DATA</sub> |                     |  |

| Cottling Time (Latersy)                                |                      | Minimum phase filter             | 10       |                     | 4.15                |  |

| Settling Time (Latency)                                |                      | Linear phase filter              | 62       | 1/f <sub>DATA</sub> |                     |  |

# Dual 24-Bit, Low-Power, High-SNR, 4ksps Delta-Sigma ADCs with Integrated PGAs

### **Electrical Characteristics (continued)**

$(V_{AVDD} = V_{AVDD\_A} = V_{AVDD\_B} = 2.7V, V_{AVSS} = V_{AVSS\_A} = V_{AVSS\_B} = 0V, V_{DVDD} = V_{DVDD\_A} = V_{DVDD\_B} = 2.0V, V_{REFP\_A} = V_{REFP} = V_{REFP\_B} = 2.5V, V_{REFN\_A} = V_{REFN\_B} = 0V$ ;  $f_{DATA} = 1000$  sps, External Clock = 2.048MHz; Continuous conversion mode (SCYCLE = 0); PGA maximum output is 300mV below AVDD and minimum output is 300mV above AVSS,  $T_A = -40^{\circ}$ C to 85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.) (Note 2)

| PARAMETER                            | SYMBOL                | CONDITIONS                                                     | MIN                       | TYP  | MAX                       | UNITS |

|--------------------------------------|-----------------------|----------------------------------------------------------------|---------------------------|------|---------------------------|-------|

| LOGIC INPUTS                         |                       |                                                                | ·                         |      |                           |       |

| Input Current                        | ILEAK_DIG             | Leakage current only                                           | -1                        |      | +1                        | μA    |

| Input Low Voltage                    | V <sub>IL</sub>       |                                                                |                           |      | 0.3x<br>V <sub>DVDD</sub> | V     |

| Input High Voltage                   | V <sub>IH</sub>       |                                                                | 0.7x<br>V <sub>DVDD</sub> |      |                           | V     |

| Input Hysteresis                     | V <sub>HYS</sub>      |                                                                |                           | 200  |                           | mV    |

| GPIO Input Low Voltage               | V <sub>IL_GPIO</sub>  |                                                                |                           |      | 0.4                       | V     |

| GPIO Input High Voltage              | VIH_GPIO              |                                                                | 1.0                       |      |                           | V     |

| GPIO Input Hysteresis                | V <sub>HYS_GPIO</sub> |                                                                |                           | 20   |                           | mV    |

| LOGIC OUTPUTS                        |                       | Ι                                                              | I                         |      |                           |       |

| Output Low Level                     | V <sub>OL</sub>       | I <sub>OL</sub> = 1mA                                          |                           |      | 0.4                       | V     |

| Output High Level                    | V <sub>OH</sub>       | I <sub>OH</sub> = 1mA                                          | 0.9x<br>V <sub>DVDD</sub> |      |                           | V     |

| Floating State Leakage<br>Current    | IDIGO_LEAK            |                                                                | -10                       |      | +10                       | μA    |

| Floating State Output<br>Capacitance | C <sub>DIGO</sub>     |                                                                |                           | 9    |                           | pF    |

| POWER REQUIREMENTS                   |                       |                                                                | L                         |      |                           |       |

| Analog Negative Supply               | V <sub>AVSS</sub>     | For split supplies,<br>V <sub>AVSS</sub> = - V <sub>AVDD</sub> | -1.8                      |      | 0                         | V     |

| Analog Positive Supply               | V <sub>AVDD</sub>     | For split supplies,<br>V <sub>AVDD</sub> = - V <sub>AVSS</sub> | V <sub>AVSS+</sub><br>2.7 |      | V <sub>AVSS+</sub><br>3.6 | V     |

| Digital Supply                       | V <sub>DVDD</sub>     |                                                                | 2.0                       |      | 3.6                       | V     |

| AVDD Sleep Current                   | IAVDD_SLEEP           | Per ADC channel                                                |                           | 0.35 | 3                         | μA    |

| AVDD Standby Current                 | IAVDD_STBY            | Per ADC channel                                                |                           | 0.5  | 3                         | μA    |

| DVDD Sleep Current                   | IDVDD_SLEEP           | Per ADC channel                                                |                           | 0.25 | 1                         | μA    |

| DVDD Standby Current                 | IDVDD_STBY            | Per ADC channel                                                |                           | 21   | 200                       | μA    |

# Dual 24-Bit, Low-Power, High-SNR, 4ksps Delta-Sigma ADCs with Integrated PGAs

### **Electrical Characteristics (continued)**

$(V_{AVDD} = V_{AVDD\_A} = V_{AVDD\_B} = 2.7V, V_{AVSS} = V_{AVSS\_A} = V_{AVSS\_B} = 0V, V_{DVDD} = V_{DVDD\_A} = V_{DVDD\_B} = 2.0V, V_{REFP\_A} = V_{REFP} = V_{REFP\_B} = 2.5V, V_{REFN} = V_{REFN\_A} = V_{REFN\_B} = 0V$ ;  $f_{DATA} = 1000$ sps, External Clock = 2.048MHz; Continuous conversion mode (SCYCLE = 0); PGA maximum output is 300mV below AVDD and minimum output is 300mV above AVSS,  $T_A = -40^{\circ}$ C to 85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.) (Note 2)

| PARAMETER              | SYMBOL                                                                    | CONDITIONS                                                                                                 | MIN | ТҮР  | MAX  | UNITS |

|------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----|------|------|-------|

|                        |                                                                           | Bypass mode, each ADC                                                                                      |     | 0.55 | 1.15 |       |

|                        |                                                                           | Buffers mode, each ADC                                                                                     |     | 0.65 | 1.2  |       |

| Analog Supply Current  | I <sub>AVDD</sub>                                                         | PGA low-power mode,<br>each ADC                                                                            |     | 1.05 | 1.7  | mA    |

|                        |                                                                           | PGA low-noise mode, each ADC                                                                               |     | 1.55 | 2.3  | -     |

|                        |                                                                           | SINC filter, each ADC                                                                                      |     | 0.2  | 0.3  |       |

| DVDD Operating Current |                                                                           | FIR filter, 1ksps, each ADC                                                                                |     | 0.25 | 0.5  | mA    |

|                        |                                                                           | FIR filter, 4ksps, each ADC                                                                                |     | 0.86 | 1.1  |       |

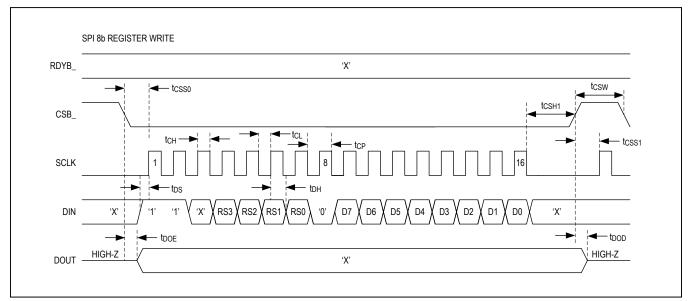

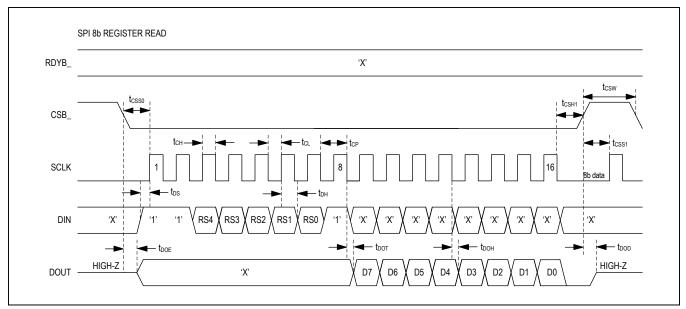

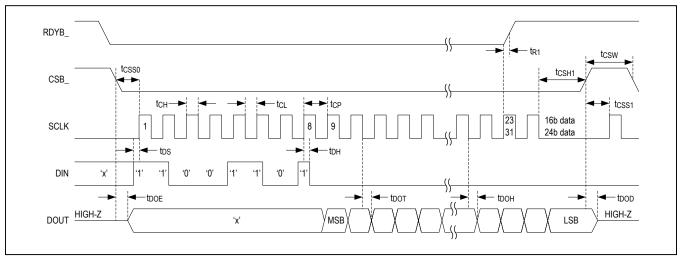

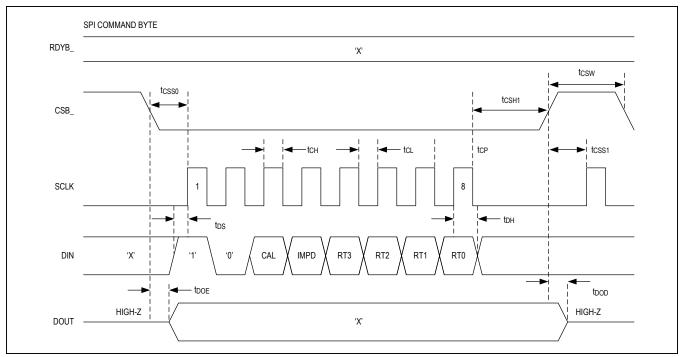

| SPI TIMING REQUIREMEN  | TS (SEE FIGURE                                                            | E 14–17)                                                                                                   |     |      |      |       |

| SCLK Frequency         | fsclk                                                                     |                                                                                                            |     |      | 5    | MHz   |

| SCLK Clock Period      | t <sub>CP</sub>                                                           |                                                                                                            | 200 |      |      | ns    |

| SCLK Pulse-Width High  | tсн                                                                       | Allow 40% duty cycle                                                                                       | 80  |      |      | ns    |

| SCLK Pulse-Width Low   | t <sub>CL</sub>                                                           | Allow 40% duty cycle                                                                                       | 80  |      |      | ns    |

| CSB Low Setup          | t <sub>CSS0</sub>                                                         | CSB low to 1st SCLK rise setup                                                                             | 40  |      |      | ns    |

| CSB High Setup         | t <sub>CSS1</sub>                                                         | Required to prevent a 17th SCLK<br>RE from being recognized by the<br>device in a free-running application | 40  |      |      | ns    |

| CSB Hold               | t <sub>CSH1</sub>                                                         | SCLK falling-edge to CSB rising-<br>edge, CSB hold time                                                    | 3   |      |      | ns    |

| CSB Pulse Width        | tcsw                                                                      | Minimum CSB pulse-width high                                                                               | 40  |      |      | ns    |

| DIN Setup              | t <sub>DS</sub>                                                           | DIN setup to SCLK rising-edge                                                                              | 40  |      |      | ns    |

| DIN Hold               | t <sub>DH</sub>                                                           | DIN hold after SCLK rising-edge                                                                            | 0   |      |      | ns    |

| DOUT Transition        | tdot                                                                      | DOUT transition valid after<br>SCLK fall                                                                   |     |      | 40   | ns    |

| DOUT Hold              | t <sub>DOH</sub>                                                          | Output hold time remains valid after SCLK fall                                                             | 3   |      |      | ns    |

| DOUT Disable           | t <sub>DOD</sub> CSB rise to DOUT disable,<br>C <sub>LOAD</sub> = 20pF 25 |                                                                                                            | 25  | ns   |      |       |

| CSB Fall to DOUT Valid | tDOE                                                                      | Default value of DOUT is '1'<br>for minimum specification, max<br>specification for valid '0' on RDYB      | 0   |      | 40   | ns    |

## Dual 24-Bit, Low-Power, High-SNR, 4ksps Delta-Sigma ADCs with Integrated PGAs

### **Electrical Characteristics (continued)**

$(V_{AVDD} = V_{AVDD\_A} = V_{AVDD\_B} = 2.7V, V_{AVSS} = V_{AVSS\_A} = V_{AVSS\_B} = 0V, V_{DVDD} = V_{DVDD\_A} = V_{DVDD\_B} = 2.0V, V_{REFP\_A} = V_{REFP\_B} = 2.5V, V_{REFN} = V_{REFN\_B} = 0V$ ;  $f_{DATA} = 1000$ sps, External Clock = 2.048MHz; Continuous conversion mode (SCYCLE = 0); PGA maximum output is 300mV below AVDD and minimum output is 300mV above AVSS,  $T_A = -40^{\circ}$ C to 85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                             | SYMBOL             | CONDITIONS                                                                                                      | MIN | TYP | MAX | UNITS              |

|---------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------|-----|-----|-----|--------------------|

| SCLK Fall to RDYB '1'                 | t <sub>R1</sub>    | RDYB transitions from '0' to '1' on<br>falling-edge of SCLK after LSB of<br>DATA is shifted onto DOUT           | 0   |     | 40  | ns                 |

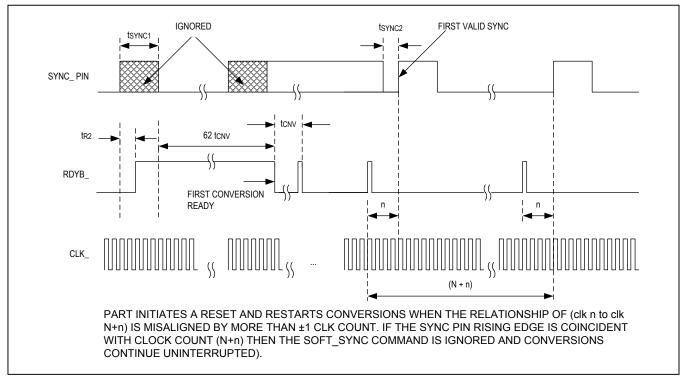

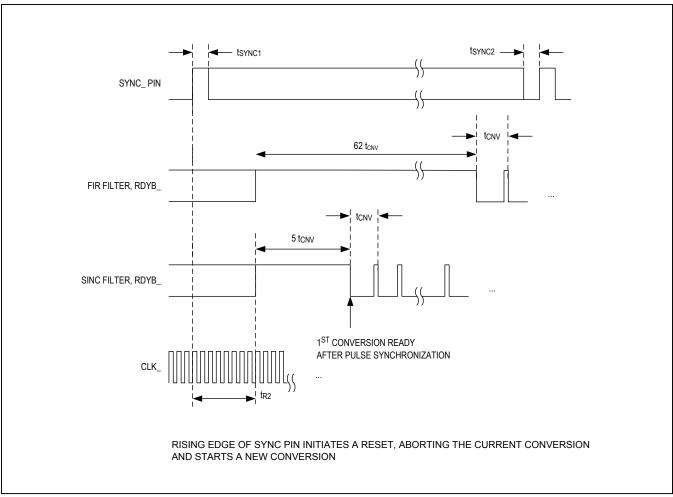

| RSTB Fall or SYNC Rise to<br>RDYB '1' | t <sub>R2</sub>    | RDYB transitions from '0' to '1' on falling-edge of RSTB or rising-edge of SYNC after 2 f <sub>CLK</sub> cycles |     |     | 2   | 1/f <sub>CLK</sub> |

| Minimum SYNC High Pulse<br>Width      | t <sub>SYNC1</sub> |                                                                                                                 | 2   |     |     | 1/f <sub>CLK</sub> |

| Minimum RSTB Low Pulse<br>Width       | t <sub>RSTB0</sub> |                                                                                                                 | 2   |     |     | 1/f <sub>CLK</sub> |

Note 2: Limits are 100% production tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range are guaranteed by design and device characterization.

Note 3: These specifications are not fully tested and are guaranteed by design and/or characterization

Note 4: Tested with input shorted ( $V_{AINP}$  -  $V_{AINN}$  = 0V). SNR = 20 x log10(( $V_{REF}$ )/( $\sqrt{2}$  x  $V_{NOISE_RMS}$ )). SNR is calculated for either a 3.6V reference or a 2.5V reference, as specified in the Conditions.

**Note 5:** Reference common mode  $(V_{AVSS} + 1V) \le (V_{REFP} + V_{REFN})/2 \le (V_{AVDD} + V_{ASS})/2 + 0.1V$ **Note 6:** Typical values tested with 150mV supply headroom,  $V_{AVSS} + 150mV \le PGA$  Output Voltage  $\le V_{AVDD} - 150mV$ .

# Dual 24-Bit, Low-Power, High-SNR, 4ksps Delta-Sigma ADCs with Integrated PGAs

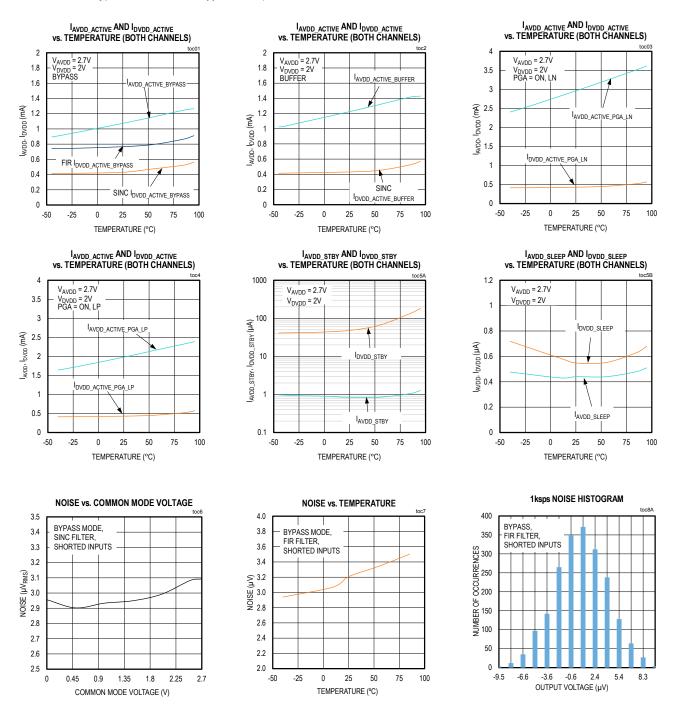

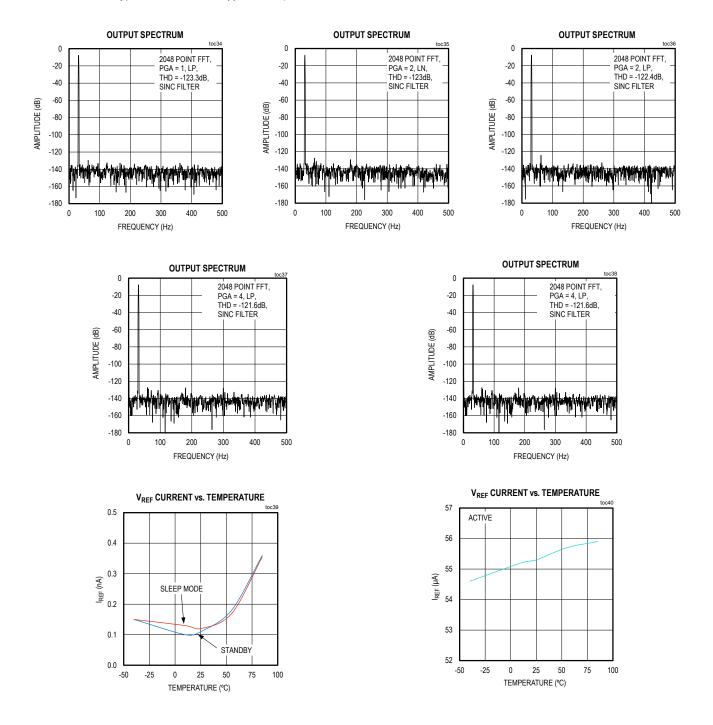

### **Typical Operating Characteristics**

$(V_{AVDD} = V_{AVDD\_A} = V_{AVDD\_B} = 2.7V, V_{AVSS} = V_{AVSS\_A} = V_{AVSS\_B} = 0V, V_{DVDD} = V_{DVDD\_A} = V_{DVDD\_B} = 2.0V, V_{REFP\_A} = V_{REFP\_B} = 2.5V, V_{REFN\_A} = V_{REFN\_B} = 0V$ ; f<sub>DATA</sub> = 1000sps, External Clock = 2.048MHz; Continuous conversion mode; (S<sub>CYCLE</sub> = 0); PGA maximum output is 300mV below AVDD and minimum output is 300mV above AVSS, T<sub>A</sub> = -40°C to 85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

## Dual 24-Bit, Low-Power, High-SNR, 4ksps Delta-Sigma ADCs with Integrated PGAs

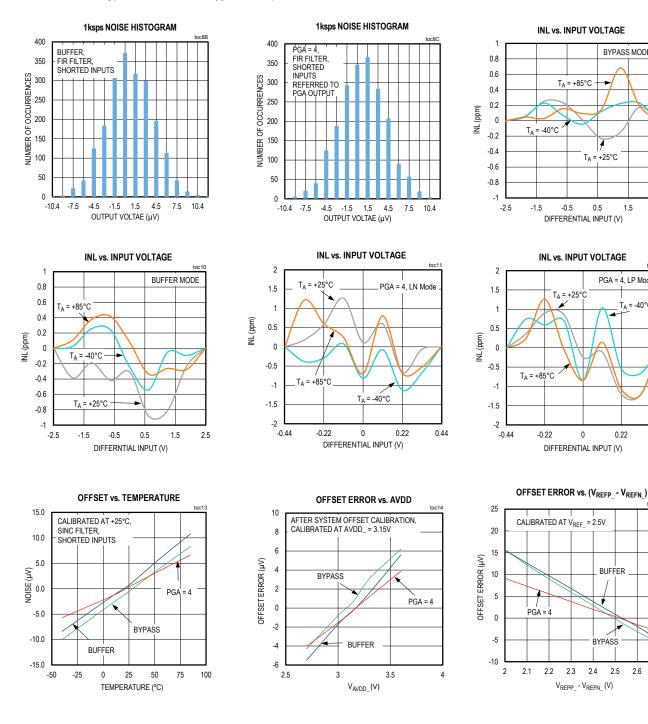

### **Typical Operating Characteristics (continued)**

$(V_{AVDD} = V_{AVDD\_A} = V_{AVDD\_B} = 2.7V, V_{AVSS} = V_{AVSS\_A} = V_{AVSS\_B} = 0V, V_{DVDD} = V_{DVDD\_A} = V_{DVDD\_B} = 2.0V, V_{REFP\_A} = V_{REFP\_B} = 2.5V, V_{REFN\_A} = V_{REFN\_B} = 0V$ ;  $f_{DATA} = 1000$ sps, External Clock = 2.048MHz; Continuous conversion mode;  $(S_{CYCLE} = 0)$ ; PGA maximum output is 300mV below AVDD and minimum output is 300mV above AVSS,  $T_A = -40^{\circ}$ C to 85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C.$ )

2.6 2.7

BYPASS MODE

1.5

PGA = 4, LP Mode

0.22

BUFFFR

۲

RYPASS

2.5

0.44

inc16

T<sub>A</sub> = -40°C

2.5

# Dual 24-Bit, Low-Power, High-SNR, 4ksps Delta-Sigma ADCs with Integrated PGAs

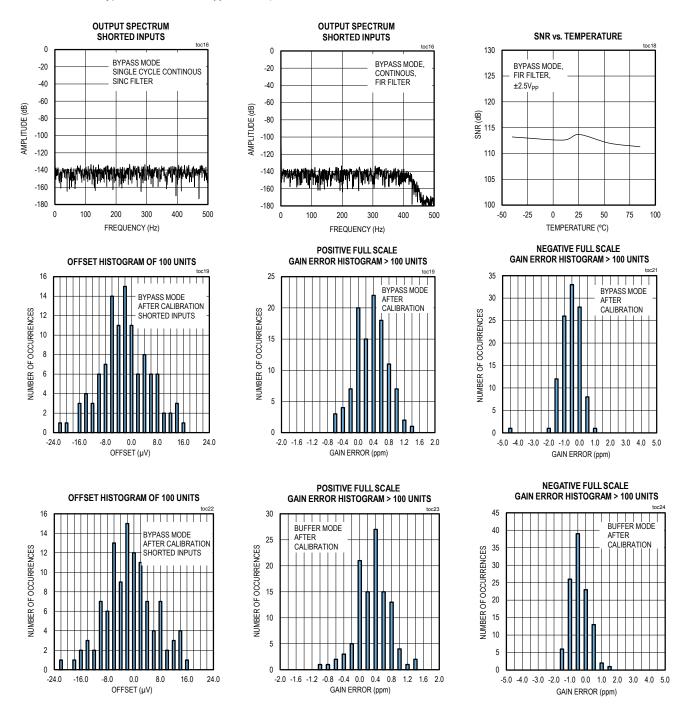

### **Typical Operating Characteristics (continued)**

$(V_{AVDD} = V_{AVDD} = V_{AVDD} = 2.7V, V_{AVSS} = V_{AVSS} = V_{AVSS} = 0V, V_{DVDD} = V_{DVDD} = V_{DVDD} = 2.0V, V_{REFP} = V_{REFP} = 2.5V, V_{REFN} = V_{REFN} = 0V; f_{DATA} = 1000$  sps, External Clock = 2.048MHz; Continuous conversion mode;  $(S_{CYCLE} = 0)$ ; PGA maximum output is 300mV below AVDD and minimum output is 300mV above AVSS,  $T_A = -40^{\circ}$ C to 85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.)

# Dual 24-Bit, Low-Power, High-SNR, 4ksps Delta-Sigma ADCs with Integrated PGAs

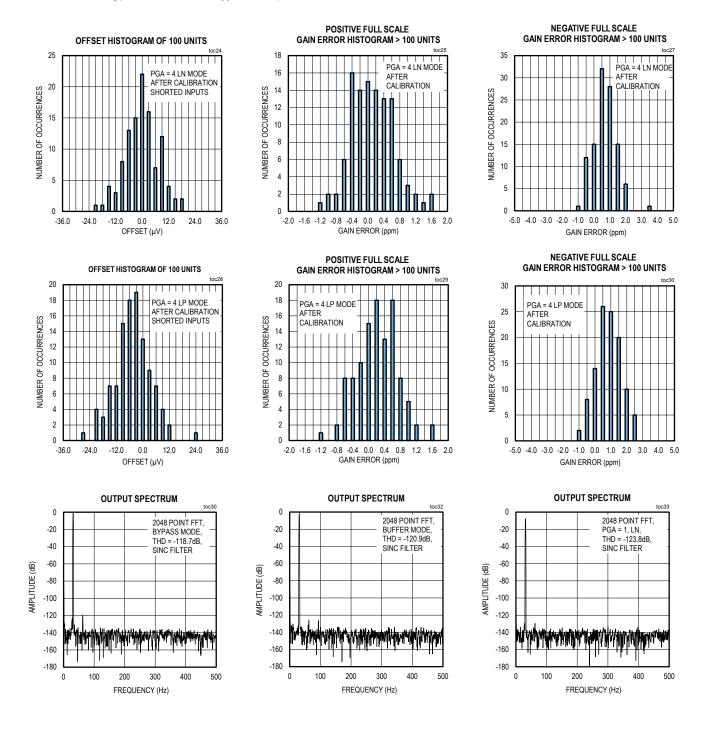

### **Typical Operating Characteristics (continued)**

$(V_{AVDD} = V_{AVDD} = V_{AVDD} = 2.7V, V_{AVSS} = V_{AVSS} = V_{AVSS} = 0V, V_{DVDD} = V_{DVDD} = V_{DVDD} = 2.0V, V_{REFP} = V_{REFP} = 2.5V, V_{REFN} = V_{REFN} = 0V; f_{DATA} = 1000$  sps, External Clock = 2.048MHz; Continuous conversion mode;  $(S_{CYCLE} = 0)$ ; PGA maximum output is 300mV below AVDD and minimum output is 300mV above AVSS,  $T_A = -40^{\circ}$ C to 85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.)

# Dual 24-Bit, Low-Power, High-SNR, 4ksps Delta-Sigma ADCs with Integrated PGAs

### **Typical Operating Characteristics (continued)**

$(V_{AVDD} = V_{AVDD} = V_{AVDD} = 2.7V, V_{AVSS} = V_{AVSS} = V_{AVSS} = 0V, V_{DVDD} = V_{DVDD} = V_{DVDD} = 2.0V, V_{REFP} = V_{REFP} = 2.5V, V_{REFN} = V_{REFN} = 0V; f_{DATA} = 1000$  sps, External Clock = 2.048MHz; Continuous conversion mode;  $(S_{CYCLE} = 0)$ ; PGA maximum output is 300mV below AVDD and minimum output is 300mV above AVSS,  $T_A = -40^{\circ}$ C to 85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.)

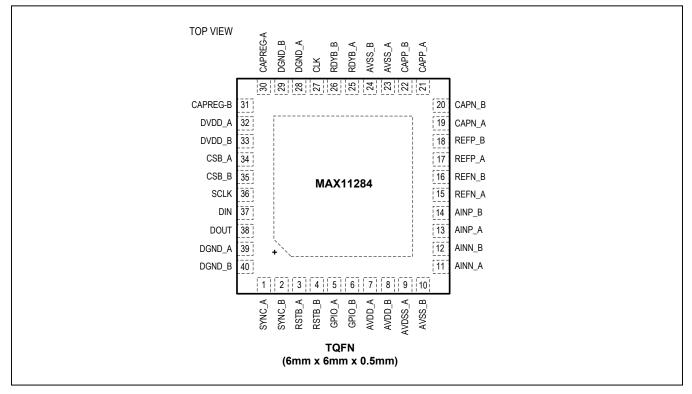

# Dual 24-Bit, Low-Power, High-SNR, 4ksps Delta-Sigma ADCs with Integrated PGAs

## **Pin Configuration**

### **Pin Description**

| PIN | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SYNC_A | SYNC Reset A. SYNC_A resets both the digital filter and the modulator of ADC A. Connect SYNC<br>from multiple MAX11284 ADCs in parallel to synchronize more than one ADC to an external trigger.<br>This is a digital input pin and is not internally pulled down. For normal operation, drive or pull this<br>pin low. |

| 2   | SYNC_B | SYNC Reset B. SYNC_B resets both the digital filter and the modulator of ADC B. Connect SYNC<br>from multiple MAX11284 ADCs in parallel to synchronize more than one ADC to an external trigger.<br>This is a digital input pin and is not internally pulled down. For normal operation, drive or pull this<br>pin low. |

| 3   | RSTB_A | Reset input for ADC A. RSTB_A causes a complete reset of all digital functions in ADC A, resulting in a power-on reset default state. This is a digital input and is not internally pulled up. For normal operation, drive or pull this pin high.                                                                       |

| 4   | RSTB_B | Reset input for ADC B. RSTB_B causes a complete reset of all digital functions in ADC B, resulting in a power-on reset default state. This is a digital input and is not internally pulled up. For normal operation, drive or pull this pin high.                                                                       |

| 5   | GPIO_A | General-Purpose I/O or Modulator Sync Output for ADC A. GPIO_A is configurable as a digital input or output. GPIO pins have weak pull ups and do not require external bias if unused. For lowest power operation, do not connect or drive high with GPIO configured as input (default).                                 |

# Dual 24-Bit, Low-Power, High-SNR, 4ksps Delta-Sigma ADCs with Integrated PGAs

## **Pin Description (continued)**

| PIN    | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                               |

|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6      | GPIO_B | General-Purpose I/O or Modulator Sync Output for ADC B. GPIO_B is configurable as a digital input or output. GPIO pins have weak pullups and do not require external bias if unused. For lowest power operation, do not connect or drive high with GPIO configured as input (default).                                                                                                                 |

| 7      | AVDD_A | Analog Positive Supply Voltage for ADC A. In single-supply mode, $V_{AVDD_A} = 2.7V$ to 3.6V with $V_{AVSS_A} = 0V$ . In dual-supply mode, AVDD_A and AVSS_A can range from ±1.35V to ±1.8V.                                                                                                                                                                                                           |

| 8      | AVDD_B | Analog Positive Supply Voltage for ADC B. In single-supply mode, $V_{AVDD_B} = 2.7V$ to 3.6V with $V_{AVSS_B} = 0V$ . In dual-supply mode, AVDD_B and AVSS_B can range from ±1.35V to ±1.8V.                                                                                                                                                                                                           |

| 9, 23  | AVSS_A | Analog Negative Supply Voltage for ADC A. Connect $A_{VSS\_A}$ to the most negative supply.<br>Connect $V_{AVSS\_A} = 0V$ in single-supply mode. Connect AVSS_A between -1.8V and 0V for dual-supply mode.                                                                                                                                                                                             |

| 10, 24 | AVSS_B | Analog Negative Supply Voltage for ADC B. Connect $A_{VSS\_B}$ to the most negative supply.<br>Connect $V_{AVSS\_B} = 0V$ in single-supply mode. Connect AVSS_B between -1.8V and 0V for dual-supply mode.                                                                                                                                                                                             |

| 11     | AINN_A | Negative Analog Input for ADC A. The analog inputs can measure both unipolar and bipolar ranges, depending on the AVDD_A and AVSS_A voltages.                                                                                                                                                                                                                                                          |

| 12     | AINN_B | Negative Analog Input for ADC B. The analog inputs can measure both unipolar and bipolar ranges, depending on the AVDD_B and AVSS_B voltages.                                                                                                                                                                                                                                                          |

| 13     | AINP_A | Positive Analog Input for ADC A. The analog inputs can measure both unipolar and bipolar ranges, depending on the AVDD_A and AVSS_A voltages.                                                                                                                                                                                                                                                          |

| 14     | AINP_B | Positive Analog Input for ADC B. The analog inputs can measure both unipolar and bipolar ranges, depending on the AVDD_B and AVSS_B voltages.                                                                                                                                                                                                                                                          |

| 15     | REFN_A | Negative Reference Input for ADC A. REFN_A must be less than REFP_A. REFN_A voltage must be between AVDD_A and AVSS_A.                                                                                                                                                                                                                                                                                 |

| 16     | REFN_B | Negative Reference Input for ADC B. REFN_B must be less than REFP_B. REFN_B voltage must be between AVDD_B and AVSS_B.                                                                                                                                                                                                                                                                                 |

| 17     | REFP_A | Positive Reference Input for ADC A. REFP_A must be greater than REFN_A. REFP_A voltage must be between AVDD_A and AVSS_A.                                                                                                                                                                                                                                                                              |

| 18     | REFP_B | Positive Reference Input for ADC B. REFP_B must be greater than REFN_B. REFP_B voltage must be between AVDD_B and AVSS_B.                                                                                                                                                                                                                                                                              |

| 19     | CAPN_A | PGA Filter Negative Capacitor Output for ADC_A. Connect a 10nF C0G capacitor between CAPN_A and CAPP_A.                                                                                                                                                                                                                                                                                                |

| 20     | CAPN_B | PGA Filter Negative Capacitor Output for ADC_B. Connect a 10nF C0G capacitor between CAPN_B and CAPP_B.                                                                                                                                                                                                                                                                                                |

| 21     | CAPP_A | PGA Filter Positive Capacitor Output for ADC_A. Connect a 10nF C0G capacitor between CAPN_A and CAPP_A.                                                                                                                                                                                                                                                                                                |

| 22     | CAPP_B | PGA Filter Positive Capacitor Output for ADC_B. Connect a 10nF C0G capacitor between CAPN_B and CAPP_B.                                                                                                                                                                                                                                                                                                |

| 25     | RDYB_A | Active-Low Data Ready Output or Internal Clock Output for ADC A. RDYB_A asserts low when the data is ready. When in continuous conversion mode, a SYNC or POR event inhibits output of the first 4 data values to allow for filter settling when the SINC filter is selected. A SYNC or POR event inhibits output of the first 63 data values to allow for filter settling when using the FIR filters. |

# Dual 24-Bit, Low-Power, High-SNR, 4ksps Delta-Sigma ADCs with Integrated PGAs

## **Pin Description (continued)**

| PIN    | NAME     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26     | RDYB_B   | Active-Low Data Ready Output or Internal Clock Output for ADC B. RDYB_B asserts low when the data is ready. When in continuous conversion mode, a SYNC or POR event inhibits output of the first 4 data values to allow for filter settling when the SINC filter is selected. A SYNC/POR event inhibits output of the first 63 data values to allow for filter settling when using the FIR filters.                                  |

| 27     | CLK      | External Clock Input for both ADCs. For external clock mode, set the EXTCLK bit = 1 and provide a digital clock signal at CLK. The MAX11284 is specified with a clock frequency of 2.048MHz. Other clock frequencies may be used, but the data rate and digital filter notch frequencies will scale accordingly. This is a digital input pin and is not internally pulled down. When external clock is disabled, drive this pin low. |

| 28, 39 | DGND_A   | Digital Ground for ADC_A                                                                                                                                                                                                                                                                                                                                                                                                             |

| 29, 40 | DGND_B   | Digital Ground for ADC_B                                                                                                                                                                                                                                                                                                                                                                                                             |

| 30     | CAPREG_A | Internal 1.8V Subregulator Reservoir Output for ADC A. Bypass with a 10µF capacitor to DGND. Minimum capacitor value required for stability is 220nF.                                                                                                                                                                                                                                                                                |

| 31     | CAPREG_B | Internal 1.8V Subregulator Reservoir Output for ADC B. Bypass with a 10µF capacitor to DGND. Minimum capacitor value required for stability is 220nF.                                                                                                                                                                                                                                                                                |

| 32     | DVDD_A   | Digital Supply Voltage for ADC_A. Supply DVDD with 2.0V to 3.6V, with respect to DGND.                                                                                                                                                                                                                                                                                                                                               |

| 33     | DVDD_B   | Digital Supply Voltage for ADC_B. Supply DVDD with 2.0V to 3.6V, with respect to DGND.                                                                                                                                                                                                                                                                                                                                               |

| 34     | CSB_A    | Active-Low Chip-Select Input for ADC_A. Set CSB low to access the serial interface. CSB is used for frame synchronization for communications when SCLK is continuous. Drive CSB high to reset the SPI interface.                                                                                                                                                                                                                     |

| 35     | CSB_B    | Active-Low Chip-Select Input for ADC_B. Set CSB low to access the serial interface. CSB is used for frame synchronization for communications when SCLK is continuous. Drive CSB high to reset the SPI interface.                                                                                                                                                                                                                     |

| 36     | SCLK     | Serial Clock Input for ADCs A and B. Apply an external serial clock at SCLK to issue commands or access data from the MAX11284.                                                                                                                                                                                                                                                                                                      |

| 37     | DIN      | Serial Data Input. Data is clocked into DIN on the rising edge of SCLK. DIN configures the internal register writes or a command operation.                                                                                                                                                                                                                                                                                          |

| 38     | DOUT     | Serial Data Output. DOUT outputs 24 bits of filtered data. DOUT transitions on the falling-edge of SCLK.                                                                                                                                                                                                                                                                                                                             |

# Dual 24-Bit, Low-Power, High-SNR, 4ksps Delta-Sigma ADCs with Integrated PGAs

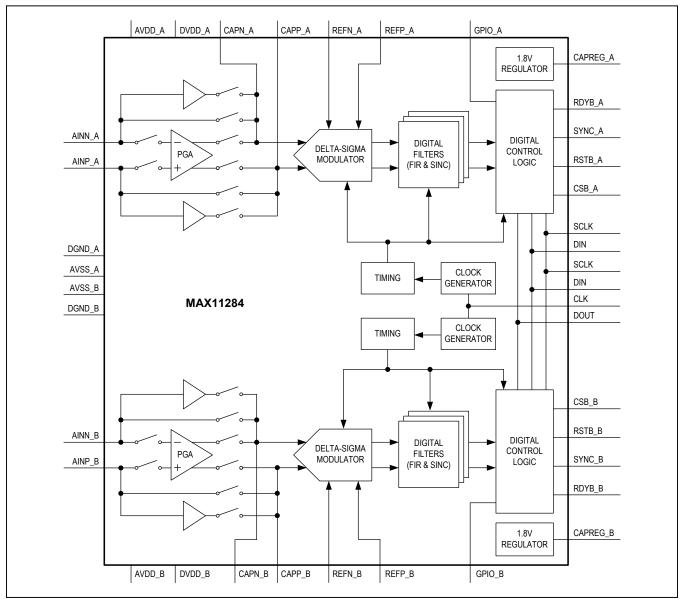

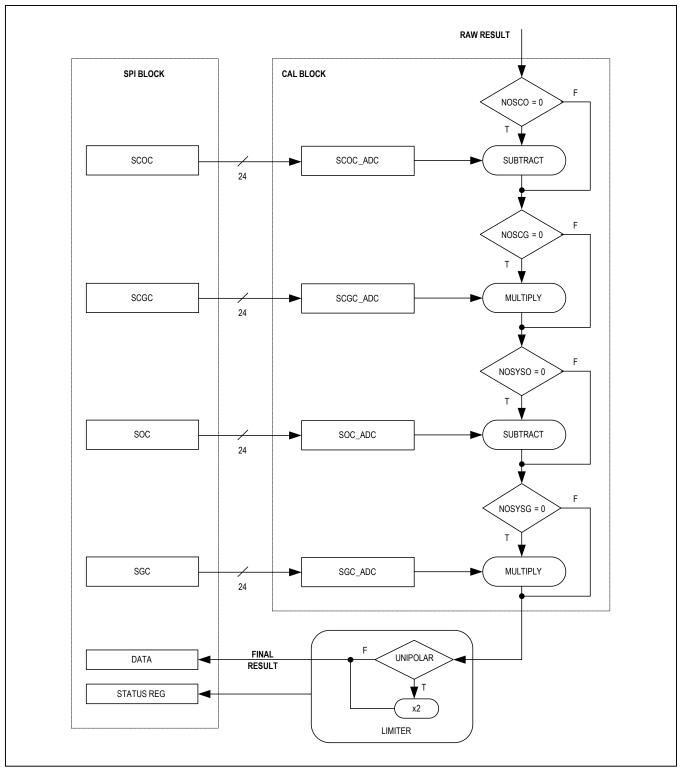

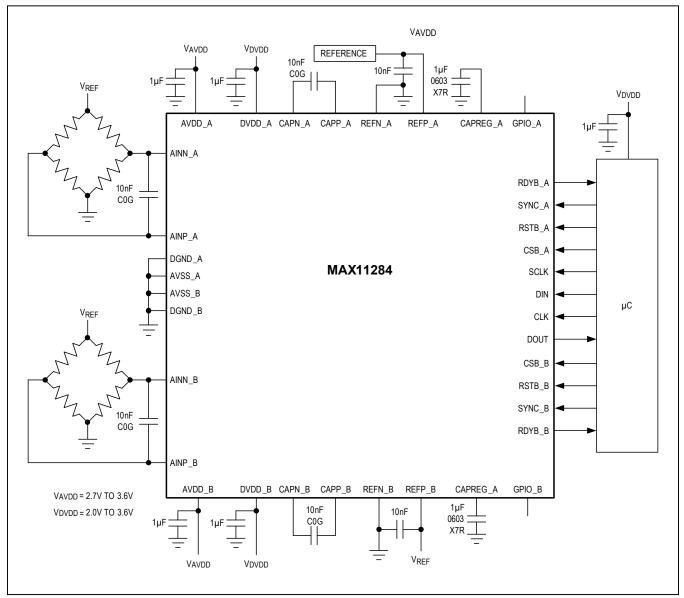

### **Functional Diagram**

### **Detailed Description**

The MAX11284 is a dual, low-power ADC that resolves a very high dynamic range. Consisting of two identical delta-sigma ADCs, this IC is capable of resolving microvoltlevel changes to the analog inputs, making it a good fit for seismic, instrumentation, and ATE applications. Input sources can connect directly to an ADC's delta sigma sampling network, a unity-gain buffer, or to a programmable gain amplifier. Each ADC includes a high-accuracy internal oscillator that requires no external components. The serial interface outputs data at sample rates up to 4ksps with the FIR filter and 16ksps with the SINC filter. The MAX11284 has three digital filters: SINC, FIR, and IIR. The fifth-order SINC filter is always enabled. The FIR filter can be enabled to get a very flat passband response with extremely sharp cut-off and high stopband rejection. A programmable IIR high-pass filter is also available for rejecting DC and lowfrequency signals.

# Dual 24-Bit, Low-Power, High-SNR, 4ksps Delta-Sigma ADCs with Integrated PGAs

Each ADC is highly configurable through the internal registers, which can be accessed through the SPI interface. This includes PGA gain selection, digital filter selection, offset and gain calibration, and a scalable sample rate to optimize performance.

#### System Clock

Each ADC incorporates a highly stable internal oscillator that provides the system clock, which is trimmed to 2.048MHz and is divided further down to run the digital and analog timing.

#### **Switch Control**

When EN is high, WP1 is connected to MST1, while WP2 is connected to MST2. When EN is low, both switches are open and the device enters a low-current shutdown mode.

#### **Voltage Reference Inputs**

Each ADC has a pair of differential inputs (REFP\_\_ and REFN\_\_) for an external reference voltage. Connect the external reference directly across the REFP\_\_ and REFN\_\_ pins to define the differential reference voltage. The V<sub>REFP</sub>\_ should always be greater than V<sub>REFN</sub>\_ and the common-mode voltage range is between 0.75V and V<sub>AVDD</sub> - 0.75V.

#### **Analog Inputs**

Each ADC has a pair of differential analog inputs (AINP\_\_\_\_\_\_ and AINN\_\_\_) that may be connected in one of three ways: direct connection, buffered connection, and PGA. See the <u>Control 2 Register (Read/Write)</u> section for information on programming and enabling the PGA, buffers, or direct connection. The default configuration is direct connect, with both PGA and input buffers powered down.

#### Input Buffers

The input buffer isolates the inputs from the capacitive load presented by the modulator, allowing for high sourceimpedance transducers.

#### **Bypass/Direct Connect**

The buffers and the PGA may be bypassed and the analog inputs routed directly to the modulator. This option lowers power dissipation since both buffers and PGA are shut off.

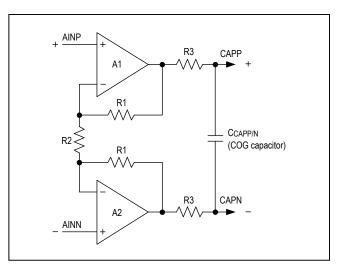

#### Programmable Gain Amplifier (PGA)

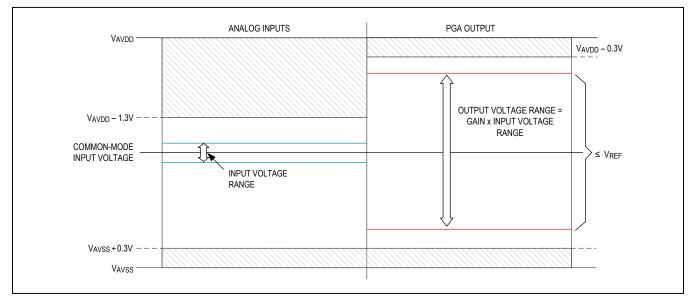

The integrated PGAs provide gain settings from 1x to 128x. See the <u>Control 2 Register (Read/Write)</u> section for information on controlling the PGAs. Figure 1 shows the PGA structure. The PGA's absolute input voltage range is VABS<sub>RNG</sub> as specified in the *Electrical*

<u>Characteristics</u> table. The PGA output voltage range is from AVSS\_\_+300mV to AVDD\_\_-300mV. The PGA output common-mode voltage is the same as the input common-mode voltage.

Note that linearity and performance degrade when the usable input common-mode voltage of the PGA is exceeded. The usable input and output common-mode ranges are shown in <u>Figure 2</u>. The following equations describe the relationship between the analog inputs and PGA output.

$$V_{CM} = (V_{AINP} + V_{AINN})/2$$

$V_{CAPP} = V_{CM} + GAIN \times (V_{AINP} - V_{CM})$

$V_{CAPN} = V_{CM} - GAIN \times (V_{CM} - V_{AINN})$

where,

AINP = Positive input to the PGA

AINN = Negative input to the PGA CAPP\_\_ = Positive output of PGA CAPN\_\_ = Negative output of PGA V<sub>CM</sub> = Input common mode voltage GAIN = PGA gain V<sub>REF</sub> = ADC reference input voltage

$V_{IN} = V_{AINP} - V_{AINN}$

**Note:** Input voltage range is limited by the reference voltage as described by  $V_{IN} \le \pm V_{REF}/GAIN$ .

Figure 1. PGA Structure

# Dual 24-Bit, Low-Power, High-SNR, 4ksps Delta-Sigma ADCs with Integrated PGAs

#### Input Voltage Range

The ADC input range is programmable for bipolar (- $V_{REF}$  to + $V_{REF}$ ) or unipolar (0 to  $V_{REF}$ ) ranges. The U/B bit in the CTRL1 register configures the ADCs for unipolar/ bipolar transfer functions. See Figure 2.

#### Noise Performance vs. Data Rate

The ADCs offer software-selectable output data rates in order to optimize data rate and noise. The RATE bits

in the command bytes determine the ADCs' output data rates. The single-cycle conversion mode provides zero latency. Set SCYCLE = 0 in the CTRL1 register to run in continuous conversion mode and SCYCLE = 1 for single-cycle conversion mode.

Single-cycle conversion mode gives an output result with no data latency for up to 3200sps. In continuous conversion mode, the maximum output data rate is 16ksps with the SINC filter and 4ksps with FIR filter.

Figure 2. Usable Input and Output Common-Mode Range

### Table 1. Continuous Mode SNR (dB) vs. Data Rate and PGA Gain with FIR Filter, AVDD = 2.7V\*

| ΠΔΤΔ  | DATA PGA GAIN SETTING |        |       |       |       |       |       |       |       |       | •     |       |       |       |       |       |       |       |

|-------|-----------------------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| RATE  | BYPASS                | BUFFER | 1     | 1     | 2     | 2     | 4     | 1     | 8     | 3     | 1     | 6     | 3     | 2     | 6     | 4     | 1:    | 28    |

| (sps) |                       |        | LN    | LP    |

| 31.25 | 128.7                 | 128.3  | 123.0 | 123.2 | 124.6 | 124.5 | 126.6 | 126.8 | 126.8 | 126.2 | 125.6 | 123.9 | 122.8 | 119.9 | 118.5 | 114.7 | 112.8 | 109.1 |

| 62.5  | 125.9                 | 125.6  | 120.4 | 120.4 | 121.7 | 121.8 | 124.0 | 124.0 | 124.1 | 123.6 | 122.9 | 120.9 | 119.9 | 117.2 | 115.5 | 111.9 | 109.7 | 105.9 |

| 125   | 123.3                 | 122.9  | 117.6 | 117.6 | 119.0 | 119.0 | 121.2 | 121.0 | 121.4 | 120.7 | 120.2 | 118.1 | 117.0 | 114.3 | 112.3 | 108.8 | 106.9 | 103.1 |

| 250   | 120.5                 | 120.0  | 114.6 | 114.8 | 116.1 | 115.9 | 118.0 | 117.9 | 117.9 | 117.4 | 116.0 | 114.8 | 112.4 | 110.2 | 107.1 | 104.8 | 101.3 | 98.7  |

| 500   | 117.5                 | 116.9  | 111.6 | 111.7 | 113.0 | 112.8 | 115.3 | 115.0 | 115.0 | 114.4 | 113.2 | 111.7 | 109.5 | 107.4 | 104.6 | 101.8 | 98.8  | 96.2  |

| 1000  | 114.4                 | 114.0  | 108.5 | 108.6 | 110.3 | 110.1 | 112.4 | 112.1 | 112.2 | 111.6 | 110.7 | 108.8 | 107.2 | 105.0 | 102.3 | 99.5  | 96.6  | 93.6  |

| 2000  | 111.4                 | 111.1  | 105.7 | 105.8 | 107.1 | 107.2 | 109.1 | 109.0 | 109.4 | 108.6 | 108.0 | 106.3 | 104.7 | 102.1 | 99.8  | 96.9  | 94.1  | 90.8  |

| 4000  | 108.3                 | 108.0  | 102.4 | 102.7 | 104.1 | 104.0 | 106.4 | 105.9 | 106.5 | 105.5 | 104.9 | 103.2 | 101.8 | 99.2  | 96.9  | 93.8  | 91.5  | 88.1  |

$V_{IN} = 0V. V_{AVDD} = 2.7V, V_{AVSS} = 0V, V_{REF} = 2.5V, T_A = +25°C, external clock. Data taken with PGA output 150mV from AVDD_and AVSS_. This table is not production tested and is based on characterization data.$

# Dual 24-Bit, Low-Power, High-SNR, 4ksps Delta-Sigma ADCs with Integrated PGAs

| DATA  |        |        |       |       |       |       |       |       | PG    | A GAIN | I SETT | ING   |       |       |       |       |       |       |

|-------|--------|--------|-------|-------|-------|-------|-------|-------|-------|--------|--------|-------|-------|-------|-------|-------|-------|-------|

| RATE  | BYPASS | BUFFER | 1     | 1     | 2     | 2     | 4     | 1     | 8     | 3      | 1      | 6     | 3     | 2     | 6     | 4     | 12    | 28    |

| (sps) |        |        | LN    | LP    | LN    | LP    | LN    | LP    | LN    | LP     | LN     | LP    | LN    | LP    | LN    | LP    | LN    | LP    |

| 31.25 | 0.620  | 0.628  | 0.628 | 0.612 | 0.311 | 0.315 | 0.166 | 0.162 | 0.089 | 0.095  | 0.053  | 0.065 | 0.039 | 0.054 | 0.032 | 0.049 | 0.030 | 0.046 |

| 62.5  | 0.865  | 0.855  | 0.842 | 0.848 | 0.435 | 0.430 | 0.224 | 0.222 | 0.121 | 0.128  | 0.073  | 0.091 | 0.054 | 0.073 | 0.045 | 0.067 | 0.044 | 0.067 |

| 125   | 1.165  | 1.165  | 1.172 | 1.171 | 0.592 | 0.598 | 0.308 | 0.316 | 0.165 | 0.180  | 0.100  | 0.127 | 0.075 | 0.102 | 0.065 | 0.096 | 0.060 | 0.092 |

| 250   | 1.606  | 1.630  | 1.637 | 1.607 | 0.834 | 0.846 | 0.444 | 0.448 | 0.249 | 0.264  | 0.161  | 0.186 | 0.127 | 0.164 | 0.117 | 0.153 | 0.114 | 0.153 |

| 500   | 2.259  | 2.315  | 2.330 | 2.310 | 1.181 | 1.208 | 0.609 | 0.630 | 0.345 | 0.369  | 0.224  | 0.263 | 0.177 | 0.226 | 0.157 | 0.216 | 0.152 | 0.206 |

| 1000  | 3.229  | 3.241  | 3.319 | 3.267 | 1.617 | 1.662 | 0.844 | 0.882 | 0.475 | 0.513  | 0.297  | 0.371 | 0.232 | 0.299 | 0.203 | 0.282 | 0.195 | 0.277 |

| 2000  | 4.565  | 4.537  | 4.585 | 4.525 | 2.342 | 2.310 | 1.234 | 1.249 | 0.659 | 0.719  | 0.406  | 0.490 | 0.308 | 0.419 | 0.273 | 0.379 | 0.261 | 0.382 |

| 4000  | 6.522  | 6.460  | 6.686 | 6.449 | 3.325 | 3.358 | 1.697 | 1.789 | 0.923 | 1.033  | 0.579  | 0.707 | 0.431 | 0.581 | 0.380 | 0.539 | 0.352 | 0.522 |

# Table 2. Continuous Mode Input Referred Noise ( $\mu V_{RMS}$ ) vs. Data Rate and PGA Gain with FIR Filter, AVDD = 2.7V\*

$*V_{IN} = 0V. V_{AVDD} = 2.7V, V_{AVSS} = 0V, V_{REF} = 2.5V, T_A = +25°C, external clock. This table is not production tested and is based on characterization data.$

### Table 3. Continuous Mode SNR (dB) vs. Data Rate and PGA Gain with FIR Filter, AVDD = 3.6V\*

| DATA  |        |        |       |       |       |       |       |       | PG    | A GAIN | I SETT | ING   |       |       |       |       |       |       |

|-------|--------|--------|-------|-------|-------|-------|-------|-------|-------|--------|--------|-------|-------|-------|-------|-------|-------|-------|

| RATE  | BYPASS | BUFFER | 1     | I     | 2     | 2     | 4     | Ļ     | 8     | 3      | 1      | 6     | 3     | 2     | 6     | 4     | 12    | 28    |

| (sps) |        |        | LN    | LP    | LN    | LP    | LN    | LP    | LN    | LP     | LN     | LP    | LN    | LP    | LN    | LP    | LN    | LP    |

| 31.25 | 131.5  | 130.9  | 126.9 | 127.0 | 127.8 | 128.3 | 130.4 | 130.5 | 130.0 | 129.0  | 128.3  | 126.7 | 125.6 | 122.7 | 121.1 | 117.7 | 115.6 | 112.0 |

| 62.5  | 129.1  | 128.6  | 124.5 | 124.6 | 125.4 | 125.6 | 128.5 | 127.8 | 127.6 | 126.6  | 125.9  | 124.0 | 122.9 | 119.8 | 118.2 | 114.7 | 112.7 | 109.1 |

| 125   | 126.7  | 126.0  | 121.9 | 121.6 | 122.8 | 122.8 | 125.5 | 125.2 | 124.7 | 123.9  | 123.2  | 121.1 | 120.0 | 117.1 | 115.3 | 111.6 | 109.7 | 105.9 |

| 250   | 123.7  | 123.2  | 119.0 | 118.9 | 120.1 | 120.1 | 122.3 | 122.0 | 121.3 | 120.7  | 119.0  | 117.8 | 114.9 | 112.9 | 110.1 | 107.5 | 104.3 | 101.6 |

| 500   | 120.7  | 120.4  | 116.0 | 116.2 | 117.1 | 117.0 | 119.6 | 119.2 | 118.6 | 117.8  | 116.4  | 115.1 | 112.3 | 110.2 | 107.3 | 104.6 | 101.7 | 98.8  |

| 1000  | 117.9  | 117.3  | 113.3 | 113.1 | 114.2 | 114.1 | 116.6 | 116.1 | 115.7 | 115.0  | 113.8  | 112.1 | 110.2 | 107.8 | 105.1 | 102.2 | 99.7  | 96.2  |

| 2000  | 114.9  | 114.4  | 110.2 | 110.1 | 110.9 | 110.8 | 113.7 | 113.4 | 112.5 | 112.3  | 110.8  | 109.3 | 107.6 | 104.7 | 102.7 | 99.6  | 97.0  | 93.5  |

| 4000  | 111.9  | 111.4  | 106.8 | 107.2 | 108.2 | 108.0 | 110.5 | 110.3 | 109.7 | 108.9  | 108.2  | 106.5 | 104.7 | 101.9 | 99.8  | 96.7  | 94.2  | 90.9  |

$V_{IN} = 0V. V_{AVDD} = 3.6V, V_{AVSS} = 0V, V_{REF} = 3.6V, T_A = +25°C, external clock. Data taken with PGA output 150mV from AVDD_and AVSS_. This table is not production tested and is based on characterization data.$

## Dual 24-Bit, Low-Power, High-SNR, 4ksps Delta-Sigma ADCs with Integrated PGAs

| DATA  |        |        |       |       |       |       |       |       | PG    | A GAIN | I SETT | ING   |       |       |       |       |       |       |

|-------|--------|--------|-------|-------|-------|-------|-------|-------|-------|--------|--------|-------|-------|-------|-------|-------|-------|-------|

| RATE  | BYPASS | BUFFER | 1     | 1     | 2     | 2     | 4     | 1     | 8     | 3      | 1      | 6     | 3     | 2     | 6     | 4     | 12    | 28    |

| (sps) |        |        | LN    | LP    | LN    | LP    | LN    | LP    | LN    | LP     | LN     | LP    | LN    | LP    | LN    | LP    | LN    | LP    |

| 31.25 | 0.675  | 0.683  | 0.674 | 0.665 | 0.345 | 0.326 | 0.177 | 0.174 | 0.092 | 0.103  | 0.056  | 0.067 | 0.038 | 0.054 | 0.032 | 0.047 | 0.030 | 0.046 |

| 62.5  | 0.890  | 0.895  | 0.888 | 0.872 | 0.457 | 0.444 | 0.219 | 0.237 | 0.122 | 0.136  | 0.074  | 0.092 | 0.052 | 0.074 | 0.045 | 0.067 | 0.042 | 0.064 |

| 125   | 1.177  | 1.206  | 1.189 | 1.229 | 0.616 | 0.614 | 0.310 | 0.321 | 0.169 | 0.186  | 0.100  | 0.129 | 0.073 | 0.102 | 0.062 | 0.096 | 0.060 | 0.093 |

| 250   | 1.664  | 1.667  | 1.673 | 1.688 | 0.837 | 0.843 | 0.446 | 0.462 | 0.250 | 0.269  | 0.164  | 0.189 | 0.131 | 0.166 | 0.113 | 0.153 | 0.111 | 0.152 |

| 500   | 2.343  | 2.300  | 2.353 | 2.290 | 1.190 | 1.200 | 0.613 | 0.639 | 0.344 | 0.377  | 0.220  | 0.258 | 0.176 | 0.225 | 0.158 | 0.214 | 0.150 | 0.210 |

| 1000  | 3.247  | 3.271  | 3.222 | 3.269 | 1.656 | 1.678 | 0.863 | 0.910 | 0.479 | 0.516  | 0.298  | 0.364 | 0.226 | 0.299 | 0.202 | 0.283 | 0.189 | 0.283 |

| 2000  | 4.555  | 4.600  | 4.592 | 4.648 | 2.409 | 2.442 | 1.204 | 1.248 | 0.688 | 0.705  | 0.423  | 0.501 | 0.305 | 0.423 | 0.268 | 0.381 | 0.257 | 0.386 |

| 4000  | 6.476  | 6.468  | 6.788 | 6.458 | 3.286 | 3.379 | 1.747 | 1.790 | 0.960 | 1.041  | 0.569  | 0.692 | 0.424 | 0.588 | 0.371 | 0.535 | 0.356 | 0.520 |

### Table 4. Continuous Mode Input Referred Noise (µV<sub>RMS</sub>) vs. Data Rate and PGA Gain with FIR Filter, AVDD = 3.6V\*

$V_{IN} = 0V$ .  $V_{AVDD} = 3.6V$ ,  $V_{AVSS} = 0V$ ,  $V_{REF} = 3.6V$ ,  $T_A = +25$ °C, external clock. This table is not production tested and is based on characterization data.

| DATA   |        |        |       |       |       |       |       |       | PGA   | GAIN  | SETT  | ING   |       |       |       |       |       |       |

|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| RATE   | BYPASS | BUFFER | 1     | I     | 2     | 2     | 4     | 1     | 8     | 3     | 1     | 6     | 3     | 2     | 6     | 4     | 12    | 28    |

| (sps)  |        |        | LN    | LP    |

| 0.4875 | 139.1  | 139.0  | 133.7 | 135.4 | 136.5 | 135.8 | 138.9 | 138.3 | 139.2 | 136.8 | 137.6 | 136.2 | 136.2 | 134.0 | 130.1 | 130.1 | 127.0 | 123.5 |

| 0.975  | 139.5  | 138.7  | 135.1 | 135.2 | 135.7 | 135.7 | 138.9 | 138.4 | 138.4 | 136.8 | 136.4 | 135.5 | 135.2 | 133.7 | 131.6 | 129.4 | 126.7 | 123.6 |

| 1.95   | 137.8  | 138.4  | 135.0 | 134.2 | 135.6 | 135.2 | 137.9 | 136.8 | 136.7 | 136.1 | 135.8 | 135.5 | 134.0 | 132.5 | 130.0 | 127.7 | 124.2 | 121.4 |

| 3.9    | 137.4  | 137.0  | 133.0 | 132.7 | 134.0 | 133.4 | 136.1 | 135.8 | 135.8 | 134.8 | 134.0 | 133.5 | 132.1 | 130.2 | 128.2 | 125.0 | 122.9 | 119.2 |

| 7.8    | 135.5  | 134.8  | 131.1 | 131.1 | 132.0 | 131.5 | 134.3 | 133.9 | 133.7 | 133.4 | 132.1 | 131.5 | 129.6 | 127.8 | 125.9 | 122.5 | 120.4 | 116.9 |

| 15.625 | 133.5  | 132.6  | 129.0 | 128.9 | 130.0 | 130.1 | 132.4 | 132.1 | 132.1 | 131.4 | 130.1 | 128.8 | 127.5 | 125.0 | 122.9 | 119.7 | 117.6 | 114.0 |

| 31.25  | 131.3  | 130.4  | 126.9 | 126.3 | 127.6 | 127.5 | 130.2 | 129.8 | 129.6 | 128.8 | 127.8 | 126.2 | 124.8 | 122.2 | 120.5 | 116.8 | 114.9 | 111.0 |

| 62.5   | 128.7  | 128.0  | 124.1 | 124.0 | 125.1 | 125.0 | 127.4 | 127.1 | 126.7 | 126.0 | 125.0 | 123.5 | 122.3 | 119.1 | 117.5 | 113.9 | 111.7 | 107.9 |

| 125    | 126.1  | 125.3  | 121.4 | 121.1 | 122.2 | 122.2 | 124.5 | 124.5 | 123.7 | 123.1 | 121.7 | 120.0 | 117.8 | 115.3 | 112.5 | 110.1 | 106.9 | 104.2 |

| 250    | 123.3  | 122.6  | 118.6 | 118.5 | 119.3 | 119.4 | 121.8 | 121.6 | 120.7 | 120.0 | 118.5 | 117.2 | 114.8 | 112.5 | 112.4 | 107.2 | 104.1 | 101.0 |

| 500    | 120.2  | 119.9  | 115.7 | 115.6 | 116.7 | 116.6 | 118.8 | 118.9 | 118.1 | 117.4 | 116.2 | 114.4 | 112.1 | 110.0 | 109.8 | 104.3 | 101.5 | 98.7  |

| 1,000  | 117.7  | 117.2  | 113.1 | 112.9 | 113.9 | 113.8 | 116.5 | 116.5 | 115.7 | 115.1 | 113.6 | 112.3 | 110.2 | 107.6 | 107.6 | 102.1 | 99.3  | 96.3  |

| 2,000  | 115.7  | 115.2  | 111.0 | 110.7 | 111.9 | 111.9 | 114.3 | 114.5 | 113.7 | 113.1 | 111.8 | 110.1 | 108.1 | 105.7 | 106.0 | 100.2 | 97.7  | 94.5  |

| 4,000  | 114.6  | 114.1  | 110.0 | 109.9 | 111.0 | 110.9 | 113.7 | 113.6 | 112.5 | 112.0 | 111.2 | 109.3 | 106.8 | 105.0 | 104.7 | 99.0  | 97.1  | 93.6  |

| 8,000  | 111.6  | 111.2  | 106.9 | 107.0 | 107.7 | 107.8 | 110.4 | 110.2 | 109.5 | 108.8 | 107.7 | 106.3 | 104.4 | 101.9 | 102.0 | 96.3  | 94.3  | 90.6  |

| 16,000 | 108.1  | 107.4  | 103.4 | 103.1 | 104.3 | 104.3 | 107.0 | 106.9 | 106.2 | 105.4 | 104.4 | 102.9 | 101.9 | 98.8  | 99.1  | 93.6  | 91.5  | 87.7  |

#### Table 5. Continuous Mode SNR (dB) vs. Data Rate and PGA Gain with Sinc Filter\*

$*V_{IN} = 0V$ .  $V_{AVDD} = 3.6V$ ,  $V_{AVSS} = 0V$ ,  $V_{REF} = 3.6V$ ,  $T_A = +25$ °C, external clock. This table is not production tested and is based on characterization data.

# Dual 24-Bit, Low-Power, High-SNR, 4ksps Delta-Sigma ADCs with Integrated PGAs

| DATA   |        |        |        |        |       |       |       |       | PG/   | GAIN  | SETT  | ING   |       |       |       |       |       |       |

|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| RATE   | BYPASS | BUFFER | 1      | l      | 2     | 2     | 4     | 1     | 8     | 3     | 1     | 6     | 3     | 2     | 6     | 4     | 12    | 28    |

| (sps)  |        |        | LN     | LP     | LN    | LP    | LN    | LP    | LN    | LP    | LN    | LP    | LN    | LP    | LN    | LP    | LN    | LP    |

| 0.4875 | 0.283  | 0.270  | 0.307  | 0.251  | 0.127 | 0.137 | 0.066 | 0.071 | 0.032 | 0.042 | 0.019 | 0.023 | 0.011 | 0.015 | 0.011 | 0.011 | 0.008 | 0.012 |

| 0.975  | 0.271  | 0.280  | 0.261  | 0.259  | 0.139 | 0.139 | 0.066 | 0.070 | 0.035 | 0.042 | 0.022 | 0.025 | 0.013 | 0.015 | 0.010 | 0.012 | 0.008 | 0.012 |

| 1.95   | 0.328  | 0.288  | 0.265  | 0.290  | 0.140 | 0.148 | 0.074 | 0.084 | 0.043 | 0.046 | 0.024 | 0.024 | 0.015 | 0.017 | 0.011 | 0.015 | 0.011 | 0.016 |

| 3.9    | 0.342  | 0.339  | 0.332  | 0.346  | 0.168 | 0.182 | 0.092 | 0.094 | 0.047 | 0.053 | 0.029 | 0.031 | 0.018 | 0.023 | 0.014 | 0.020 | 0.013 | 0.020 |

| 7.8    | 0.429  | 0.435  | 0.416  | 0.415  | 0.213 | 0.227 | 0.112 | 0.117 | 0.060 | 0.062 | 0.036 | 0.039 | 0.024 | 0.030 | 0.018 | 0.027 | 0.018 | 0.026 |

| 15.625 | 0.539  | 0.563  | 0.528  | 0.532  | 0.268 | 0.264 | 0.140 | 0.145 | 0.072 | 0.079 | 0.046 | 0.053 | 0.031 | 0.041 | 0.026 | 0.038 | 0.024 | 0.036 |

| 31.25  | 0.696  | 0.724  | 0.669  | 0.723  | 0.354 | 0.359 | 0.179 | 0.189 | 0.097 | 0.106 | 0.059 | 0.072 | 0.042 | 0.057 | 0.034 | 0.053 | 0.033 | 0.051 |

| 62.5   | 0.930  | 0.961  | 0.928  | 0.940  | 0.472 | 0.479 | 0.248 | 0.258 | 0.135 | 0.146 | 0.082 | 0.097 | 0.056 | 0.081 | 0.049 | 0.074 | 0.047 | 0.074 |

| 125    | 1.266  | 1.299  | 1.258  | 1.301  | 0.657 | 0.660 | 0.349 | 0.349 | 0.191 | 0.204 | 0.120 | 0.145 | 0.094 | 0.125 | 0.086 | 0.115 | 0.083 | 0.112 |

| 250    | 1.751  | 1.777  | 1.754  | 1.767  | 0.917 | 0.911 | 0.476 | 0.483 | 0.268 | 0.292 | 0.172 | 0.201 | 0.132 | 0.172 | 0.088 | 0.159 | 0.114 | 0.163 |

| 500    | 2.475  | 2.430  | 2.440  | 2.460  | 1.236 | 1.260 | 0.672 | 0.663 | 0.363 | 0.392 | 0.227 | 0.276 | 0.181 | 0.229 | 0.118 | 0.222 | 0.154 | 0.213 |

| 1,000  | 3.323  | 3.320  | 3.304  | 3.348  | 1.712 | 1.727 | 0.872 | 0.877 | 0.481 | 0.511 | 0.306 | 0.355 | 0.227 | 0.305 | 0.151 | 0.286 | 0.197 | 0.279 |

| 2,000  | 4.160  | 4.189  | 4.193  | 4.307  | 2.160 | 2.161 | 1.121 | 1.105 | 0.603 | 0.645 | 0.373 | 0.454 | 0.285 | 0.378 | 0.183 | 0.356 | 0.236 | 0.345 |

| 4,000  | 4.716  | 4.716  | 4.694  | 4.769  | 2.381 | 2.431 | 1.210 | 1.214 | 0.688 | 0.729 | 0.404 | 0.499 | 0.333 | 0.409 | 0.211 | 0.408 | 0.253 | 0.381 |

| 8,000  | 6.700  | 6.612  | 6.688  | 6.650  | 3.513 | 3.451 | 1.754 | 1.811 | 0.974 | 1.056 | 0.604 | 0.709 | 0.441 | 0.586 | 0.288 | 0.560 | 0.352 | 0.541 |

| 16,000 | 10.010 | 10.256 | 10.038 | 10.395 | 5.154 | 5.157 | 2.603 | 2.635 | 1.428 | 1.566 | 0.880 | 1.048 | 0.585 | 0.842 | 0.406 | 0.761 | 0.482 | 0.751 |

# Table 6. Continuous Mode Input-Referred Noise ( $\mu V_{RMS}$ ) vs. Data Rate and PGA Gain with Sinc Filter\*

$V_{IN} = 0V$ .  $V_{AVDD} = 3.6V$ ,  $V_{AVSS} = 0V$ ,  $V_{REF} = 3.6V$ ,  $T_A = +25$ °C, external clock. This table is not production tested and is based on characterization data.

#### **Power-On Reset**

The ADCs contain power-on reset (POR) supplymonitoring circuitry on both the digital supply (DVDD) and the positive analog supply (AVDD). The POR circuitry ensures proper device default conditions after either a digital or analog power-sequencing event.

The digital POR trigger threshold is typically 1.2V with respect to  $V_{DGND}$  and has 100mV of hysteresis. The analog POR trigger threshold is typically 1.25V with respect to  $V_{AVSS}$  and has 100mV of hysteresis. Both POR circuits have low-pass filters that prevent high-frequency supply glitches from triggering the POR.

#### **Power-Down Modes**

The ADCs can be powered down through the IMPD bit in the command byte (see <u>Table 10</u>). The PD[1:0] bits of the CTRL1 register are used to select the power-down state. The SPI interface remains fully functional in all power-down states.

**Sleep Mode:** Sleep mode can be set by writing 01 to the PD[1:0] bits. In this state, the internal subregulator that powers the digital core is powered off. This is the lowest power state for the device.