### **General Description**

The MAX8809A/MAX8810A synchronous, 2-/3-/4phase, step-down, current-mode controllers with integrated dual-phase MOSFET drivers provide flexible solutions that fully comply with Intel<sup>®</sup> VRD11/VRD10 and AMD K8 Rev F CPU core supplies. The flexible design supplies load currents up to 150A for low-voltage CPU core power requirements.

A tri-state SEL input is available to configure the VID logic for either the Intel VRD11/VRD10 or AMD K8 Rev F applications. An enable input (EN) is available to disable the IC. True-differential remote output-voltage sensing enables precise regulation at the load by eliminating the effects of trace impedance in the output and return paths. A high-accuracy DAC combined with precision current-sense amplifiers and droop control enable the MAX8809A/MAX8810A to meet the most stringent tolerance requirements of new-generation high-current CPUs. These ICs use either integral or voltage-positioning feedback control to achieve high output-voltage accuracy.

The COMP input allows for either positive or negative voltage offsets from the VID code voltage. A powergood signal (VRREADY) is provided for startup sequencing and fault annunciation. The SS/OVP pin enables the programming of the soft-start period, and provides an indication of an overvoltage condition. A soft-stop feature prevents negative voltage spikes on the output at turn-off, eliminating the need for an external Schottky clamp diode.

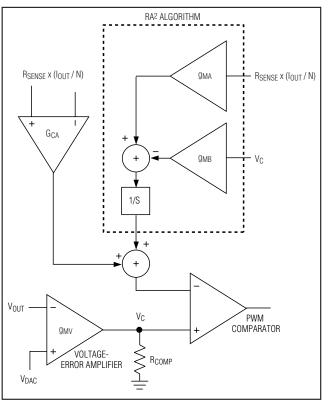

The MAX8809A/MAX8810A incorporate a proprietary "rapid active average" current-mode control scheme for fast and accurate transient-response performance, as well as precise load current sharing. Either the inductor DCR or a resistive current-sensing element is used for current sensing. When used with DCR sensing, rapid active current averaging (RA<sup>2</sup>) eliminates the tolerance effects of the inductance and associated current-sensing components, providing superior phase current matching, accurate current limit, and precise load-line.

The MAX8809A operates as a single-chip, 2-phase solution with integrated drivers. It also provides a 3rd-phase PWM output and easily supports 3-phase design by adding the MAX8552 high-performance driver. The MAX8810A enables up to 4-phase designs by adding the MAX8523 high-performance dual driver for a compact 2-chip solution.

Intel is a registered trademark of Intel Corp.

#### **Features**

- VRD11/VRD10 and K8 Rev F Compliant

- ±0.35% Initial Output Voltage Accuracy

- Dual Integrated Drivers with Integrated Bootstrap Diodes

- Up to 26V Input Voltage

- Adaptive Shoot-Through Protection

- Soft-Start, Soft-Stop, VRREADY Output

- Fast Load Transient Response

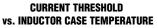

- Individual Phase, Fully Temperature-Compensated Cycle-by-Cycle Average Current Limit

- Current Foldback at Short Circuit

- Voltage Positioning or Integral Feedback

- Differential Remote Voltage Sensing

- Programmable Positive and Negative Offset Voltages

- ♦ 150kHz to 1.2MHz Switching Frequency per Phase

- NTC-Based, Temperature-Independent Load Line

- Precise Phase Current Sharing

- Programmable Thermal-Monitoring Output (VRHOT)

- ♦ 6A Peak MOSFET Drivers

- 0.3Ω/0.85Ω Low-Side, 0.8Ω/1.1Ω High-Side Drivers (typ)

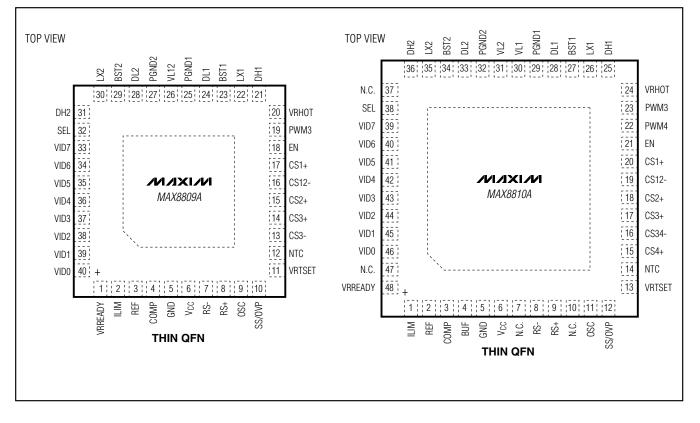

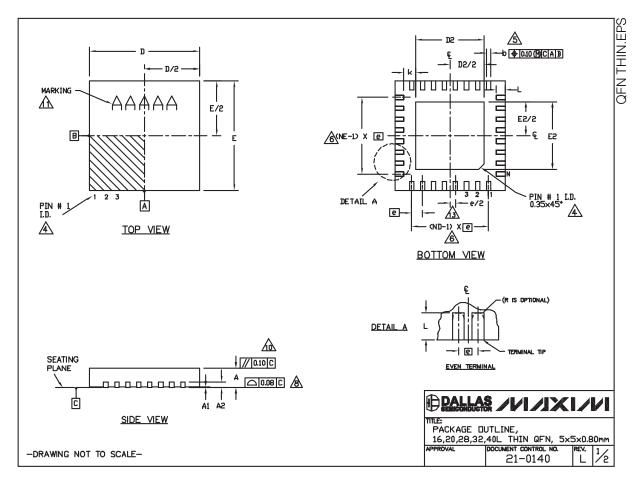

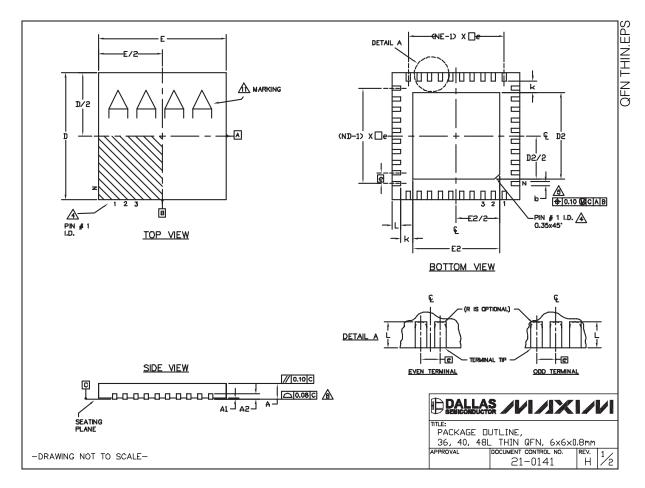

- ♦ 40-Pin and 48-Pin Thin QFN Packages

### **Applications**

Desktop PCs Servers, Workstations Desknote and LCD PCs Voltage-Regulator Modules

### **Ordering Information**

|              |                          | -           |               |

|--------------|--------------------------|-------------|---------------|

| PART         | PIN-<br>PACKAGE          | PKG<br>CODE | FUNCTION      |

| MAX8809AETL+ | 40 Thin QFN<br>5mm x 5mm | T4055-1     | 2-/3-phase    |

| MAX8810AETM+ | 48 Thin QFN<br>6mm x 6mm | T4866-1     | 2-/3-/4-phase |

+Denotes lead-free package.

**Note:** All parts are specified in the -40°C to +85°C extended temperature range.

Pin Configurations appear at end of data sheet.

Maxim Integrated Products 1

For pricing delivery, and ordering information please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| REF, COMP, SS/OVP, OSC, NTC, VRTSET,                 | CS_+ to CS0.3V to +0.3V                               |

|------------------------------------------------------|-------------------------------------------------------|

| RS+, RS-, PWM_ to GND0.3V to (V <sub>CC</sub> + 0.3V | ) DH_, DL_ Current±200mA <sub>RMS</sub>               |

| CS_+, CS, VID_, BUF, EN, ILIM, SEL, VRREADY,         | VL_ to BST_ Diode Current50mA <sub>RMS</sub>          |

| VRHOT, V <sub>CC</sub> to GND0.3V to +6              | Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

| BST_ to PGND0.3V to +35V                             | / 40-Pin Thin QFN 5mm x 5mm                           |

| LX_ to PGND1V to +28                                 | / (derate 35.7mW/°C above +70°C)                      |

| BST_ to VL1V to +30\                                 | 48-Pin Thin QFN 6mm x 6mm                             |

| DH_ to PGND0.3V to (V <sub>BST</sub> + 0.3V          | ) (derate 37mW/°C above +70°C)                        |

| DH_, BST_ to LX0.3V to +7V                           | / Operating Temperature Range40°C to +85°C            |

| VL_ to PGND0.3V to +7V                               | / Junction Temperature+150°C                          |

| DL_ to PGND0.3V to (V <sub>VL</sub> + 0.3V           | ) Storage Temperature Range65°C to +150°C             |

| PGND_ to GND                                         | Lead Temperature (soldering, 10s)+300°C               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### ELECTRICAL CHARACTERISTICS

(VVL = VBST = 6.5V, VCC = VEN = 5V, VILIM = 1.5V, VID\_ = SEL = REF = BUF = unconnected, VCOMP = VRS+ = 1.0V, RVRREADY =  $5k\Omega$  pullup to 5V,  $R_{SS/OVP} = 12k\Omega$  to GND,  $R_{NTC} = 10k\Omega$  to GND,  $f_{SW} = 300kHz$ ,  $R_{VRTSET} = 118k\Omega$  to GND,  $V_{CS_+} = V_{CS_-} = 1V$ , PWM\_ = unconnected,  $R_{VRHOT} = 249\Omega$  pullup to 1.05V,  $V_{GND} = V_{PGND_-} = V_{LX_-} = V_{RS_-} = 0V$ , DL\_ = DH\_ = unconnected,  $T_A = 0^{\circ}C$ to +85°C. Typical values are at  $T_A = +25$ °C, unless otherwise noted.)

| PARAMETER                                | CONDITIONS                                                                     | MIN   | ТҮР   | MAX   | UNITS |

|------------------------------------------|--------------------------------------------------------------------------------|-------|-------|-------|-------|

| V <sub>CC</sub> Operating Range          |                                                                                | 4.5   |       | 5.5   | V     |

|                                          | Rising                                                                         | 4.0   | 4.25  | 4.5   | V     |

| V <sub>CC</sub> UVLO Trip Level          | Falling                                                                        | 3.7   | 4.0   | 4.3   | v     |

| V <sub>CC</sub> Shutdown Supply Current  | V <sub>CC</sub> < 3.75V                                                        |       | 0.35  |       | mA    |

| V <sub>CC</sub> Standby Supply Current   | $V_{EN} = 0V$                                                                  |       | 0.5   |       | mA    |

| V <sub>CC</sub> Operating Supply Current | $V_{RS+}$ - $V_{RS-}$ = 1.0V, no switching, $V_{DAC}$ = 1.0V (Note 1)          |       | 13    |       | mA    |

| Thermal Shutdown                         | Temperature rising, hysteresis = 25°C (typ)                                    |       | +160  |       | °C    |

| INTERNAL REFERENCE (REF)                 |                                                                                |       |       |       |       |

| Output Voltage                           | I <sub>REF</sub> = -100μA                                                      | 1.992 | 2.000 | 2.008 | V     |

| Output Regulation (Sourcing)             | $V_{CC}$ = 4.5V at I_{REF} = -500µA to $V_{CC}$ = 5.5V at I_{REF} = -100µA     | -0.05 |       | +0.05 | %     |

| Output Regulation (Sinking)              | $V_{CC}$ = 4.5V at $I_{REF}$ = +100µA to $V_{CC}$ = 5.5V at $I_{REF}$ = +500µA | -0.2  |       | +0.2  | %     |

| Reference UVLO Trip Level                | Rising (100mV typ hysteresis)                                                  |       | 1.84  |       | V     |

| BUF REFERENCE                            |                                                                                |       |       |       |       |

| BUF Regulation Voltage                   | $I_{BUF} = 0A$                                                                 | 0.99  | 1.0   | 1.01  | V     |

| BUF Output Regulation                    | $V_{CC}$ = 4.5V at $I_{BUF}$ = +100µA to $V_{CC}$ = 5.5V at $I_{BUF}$ = +500µA | -0.25 |       | +0.25 | %     |

| SOFT-START                               |                                                                                |       |       |       |       |

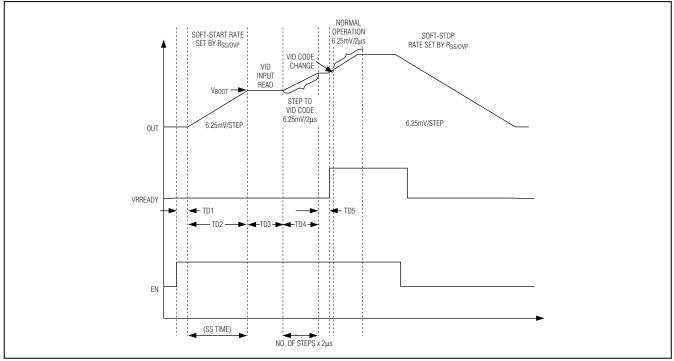

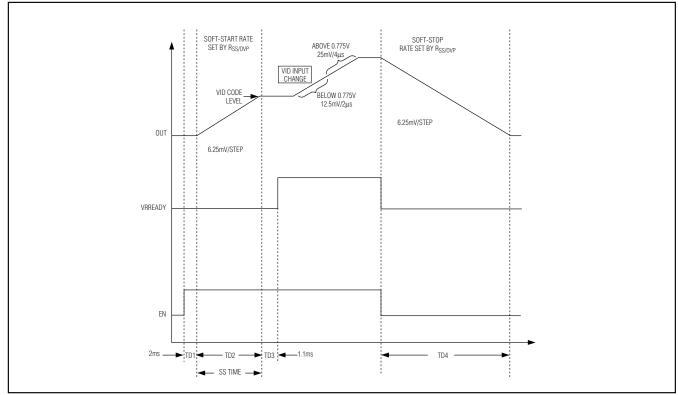

| EN Startup Delay (TD1)                   | From EN rising to VOUT rising                                                  | 1.6   | 2.2   | 2.8   | ms    |

| Soft-Start Period Range (TD2)            | $12k\Omega < R_{SS/OVP} < 90.9k\Omega$                                         | 0.5   |       | 6.5   | ms    |

| Soft-Start Tolerance                     | $R_{SS/OVP} = 56k\Omega$                                                       | 2.25  | 3.00  | 3.75  | ms    |

| Intel Boot-Level Duration (TD3)          | SEL = GND or SEL = $V_{CC}$                                                    | 175   | 250   | 350   | μs    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{VL} = V_{BST} = 6.5V, V_{CC} = V_{EN} = 5V, V_{ILIM} = 1.5V, VID_ = SEL = REF = BUF = unconnected, V_{COMP} = V_{RS+} = 1.0V, R_{VRTEADY} = 5k\Omega$  pullup to 5V,  $R_{SS/OVP} = 12k\Omega$  to GND,  $R_{NTC} = 10k\Omega$  to GND,  $f_{SW} = 300kHz$ ,  $R_{VRTSET} = 118k\Omega$  to GND,  $V_{CS_+} = V_{CS_-} = 1V$ , PWM\_ = unconnected,  $R_{VRHOT} = 249\Omega$  pullup to 1.05V,  $V_{GND} = V_{PGND_-} = V_{LX_-} = V_{RS-} = 0V$ ,  $DL_- = DH_- = unconnected$ ,  $T_A = 0^{\circ}C$  to +85°C. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                                    | CONDITIONS                          |                                                             | MIN                      | ТҮР                 | MAX   | UNITS |

|----------------------------------------------|-------------------------------------|-------------------------------------------------------------|--------------------------|---------------------|-------|-------|

| VOLTAGE REGULATION                           |                                     |                                                             |                          |                     |       |       |

| RS+ Input Bias Current                       | $V_{RS+} = 1V$                      |                                                             |                          | 0.1                 | 1     | μA    |

| RS- Input Bias Current                       | V <sub>RS-</sub> = 0.2V             |                                                             |                          | 0.1                 | 1     | μA    |

| Output Voltage Initial Accuracy              | V <sub>DAC</sub> = 1V (Note 1)      |                                                             |                          |                     | +0.35 | %     |

| -                                            | V <sub>DAC</sub> = 1V (Note 1),     | $T_A = +25^{\circ}C \text{ to } +85^{\circ}C$               | -3.5                     |                     | +3.5  |       |

| Droop Accuracy                               | $R_{\rm NTC} = 10k\Omega$           | $T_A = -5^{\circ}C \text{ to } +85^{\circ}C$                | -5.5                     |                     | +5.5  | %     |

| g <sub>MV</sub> Amplifier Transconductance   |                                     |                                                             | 1.94                     | 2.00                | 2.06  | mS    |

| g <sub>MV</sub> Gain Bandwidth Product       |                                     |                                                             |                          | 5                   |       | MHz   |

| Comp Output Current                          | $V_{DAC} - V_{RS+} = 200 \text{mV}$ | (Note 1)                                                    |                          | 385                 |       | μA    |

| CURRENT LIMIT                                | ·                                   |                                                             |                          |                     |       | •     |

| Average Current-Limit Trip Level<br>Accuracy | V <sub>ILIM</sub> = 1.5V            |                                                             | -6                       |                     | +6    | %     |

| ILIM Input Bias Current                      |                                     |                                                             |                          | 0.01                | 1     | μA    |

| ILIM Default Program Level                   | $V_{ILIM} > V_{CC} - 0.2V$          | VILIM > VCC - 0.2V                                          |                          |                     | 1.463 | V     |

| ENABLE INPUT (EN)                            |                                     |                                                             |                          |                     |       | 1     |

| Turn-On Threshold (Rising)                   | $V_{CC} = 4.5V$ to 5.5V, 100        | $V_{CC} = 4.5V$ to 5.5V, 100mV typ hysteresis 0.8 0.85 0.85 |                          |                     |       |       |

| LOGIC INPUTS (VID0-VID7)                     |                                     |                                                             |                          |                     |       | ,     |

| INTEL (SEL = HIGH OR LOW)                    |                                     |                                                             |                          |                     |       |       |

| Input Low Level                              | $V_{CC} = 4.5V$ to 5.5V             |                                                             |                          |                     | 0.4   | V     |

| Input High Level                             | $V_{CC} = 4.5V$ to 5.5V             |                                                             | 0.8                      |                     |       | V     |

| Input Pulldown Resistance                    |                                     |                                                             | 100                      |                     | 270   | kΩ    |

| AMD (SEL = UNCONNECTED)                      |                                     |                                                             |                          |                     |       |       |

| Input Low Level                              | $V_{CC} = 4.5V$ to 5.5V             |                                                             |                          |                     | 0.6   | V     |

| Input High Level                             | $V_{CC} = 4.5V$ to 5.5V             |                                                             | 1.4                      |                     |       | V     |

| Input Pulldown Resistance                    |                                     |                                                             | 100                      |                     | 270   | kΩ    |

| LOGIC INPUT (SEL)                            |                                     |                                                             |                          |                     |       |       |

| Internal Bias Resistance                     |                                     |                                                             | 50                       | 100                 | 200   | kΩ    |

| Internal Bias Voltage                        | $V_{CC} = 4.5V$ to 5.5V             |                                                             |                          | V <sub>CC</sub> / 2 |       | V     |

| Input Low Level                              | $V_{CC} = 4.5V$ to 5.5V             |                                                             |                          |                     | 0.5   | V     |

| Input High Level                             | $V_{CC} = 4.5V$ to 5.5V             |                                                             | V <sub>CC</sub> -<br>0.5 |                     |       | V     |

| VRREADY OUTPUT                               | •                                   |                                                             |                          |                     |       | •     |

| Output Low Level                             | $I_{VRREADY} = +4mA$                |                                                             |                          | 0.4                 | V     |       |

| Output High Leakage                          | VVRREADY = 5.5V                     |                                                             | Ì                        |                     | 1     | μA    |

| VRREADY Blanking Time                        |                                     | DY rising, R <sub>SS/OVP</sub> = $12k\Omega$                | 3.0                      |                     | 5.5   | ms    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{VL} = V_{BST} = 6.5V, V_{CC} = V_{EN} = 5V, V_{ILIM} = 1.5V, VID_ = SEL = REF = BUF = unconnected, V_{COMP} = V_{RS+} = 1.0V, R_{VRREADY} = 5k\Omega$  pullup to 5V, R<sub>SS/OVP</sub> = 12k $\Omega$  to GND, R<sub>NTC</sub> = 10k $\Omega$  to GND, f<sub>SW</sub> = 300kHz, R<sub>VRTSET</sub> = 118k $\Omega$  to GND, V<sub>CS\_+</sub> = V<sub>CS\_-</sub> = 1V, PWM\_ = unconnected, R<sub>VRHOT</sub> = 249 $\Omega$  pullup to 1.05V, V<sub>GND</sub> = V<sub>PGND\_</sub> = V<sub>LX\_</sub> = V<sub>RS-</sub> = 0V, DL\_ = DH\_ = unconnected, T\_A = 0°C to +85°C. Typical values are at T\_A = +25°C, unless otherwise noted.)

| PARAMETER                                       | CONDITIONS                                                                                              | MIN                         | ТҮР                         | MAX                         | UNITS |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------|-----------------------------|-------|

| VRREADY Upper Threshold                         | (V <sub>RS+</sub> - V <sub>RS-)</sub> rising                                                            | V <sub>DAC</sub> +<br>0.150 |                             | V <sub>DAC</sub> + 0.200    | v     |

| (Note 1)                                        | (V <sub>RS+</sub> - V <sub>RS-)</sub> falling                                                           | V <sub>DAC</sub> +<br>0.075 |                             | V <sub>DAC</sub> +<br>0.125 | v     |

| VRREADY Lower Threshold<br>(Note 1)             | (V <sub>RS+</sub> - V <sub>RS-)</sub> falling                                                           | V <sub>DAC</sub> -<br>0.250 |                             | V <sub>DAC</sub> -<br>0.200 | v     |

|                                                 | (V <sub>RS+</sub> - V <sub>RS-)</sub> rising                                                            | V <sub>DAC</sub> -<br>0.175 |                             | V <sub>DAC</sub> -<br>0.125 | v     |

| OVERVOLTAGE PROTECTION                          | -                                                                                                       |                             |                             |                             |       |

| Intel (SEL = High or Low)                       | (V <sub>RS+</sub> - V <sub>RS-)</sub> rising (Note 1)                                                   | V <sub>DAC</sub> +<br>0.150 | V <sub>DAC</sub> +<br>0.175 | V <sub>DAC</sub> +<br>0.200 | V     |

| AMD (SEL = Unconnected)                         | (V <sub>RS+</sub> - V <sub>RS-)</sub> rising                                                            | 1.750                       | 1.775                       | 1.800                       | V     |

| SS/OVP High Level                               | I <sub>SS/OVP</sub> = -10mA                                                                             | V <sub>CC</sub> -<br>0.450  |                             |                             | V     |

| OSCILLATOR                                      |                                                                                                         | ·                           |                             |                             |       |

| Oscillator Frequency Accuracy<br>(per Phase)    | Frequency per phase = 300kHz                                                                            | -10                         |                             | +10                         | %     |

| Switching Frequency Range<br>(per Phase)        |                                                                                                         | 150                         |                             | 1200                        | kHz   |

| CURRENT-SENSE AMPLIFIERS                        |                                                                                                         |                             |                             |                             |       |

| Current-Sense Amplifier Gain (G <sub>CA</sub> ) | $R_{NTC} = 10k\Omega$ , $T_A = +25^{\circ}C$ to $+85^{\circ}C$                                          | 28.8                        | 30.0                        | 31.2                        | V/V   |

| CS_+ Input Bias Current                         | $V_{CS\_+} = V_{CS\} = 2V$                                                                              |                             | 0.3                         | 3.0                         | μA    |

| CS Input Bias Current                           | $V_{CS_+} = V_{CS} = 2V$                                                                                |                             | 0.6                         | 5.5                         | μΑ    |

| CS to PWM_ Delay                                | V <sub>COMP</sub> falling                                                                               |                             | 20                          |                             | ns    |

| GAIN TEMPERATURE COMPENSATIO                    |                                                                                                         |                             |                             |                             | 1     |

| Compensation Accuracy                           | R <sub>NTC</sub> temperature = 0°C to +125°C<br>(10k NTC Panasonic ERTJ1VR103)                          | -6                          |                             | +6                          | %     |

| VRHOT TEMPERATURE MONITORIN                     | G                                                                                                       |                             |                             |                             |       |

| VRHOT Output Low Voltage                        | $I_{VRHOT} = +4mA$                                                                                      |                             |                             | 0.4                         | V     |

| VRHOT Output High Leakage Current               | $V_{VRHOT} = 5.5V$                                                                                      |                             |                             | 5                           | μA    |

| VRTSET Temperature Range                        |                                                                                                         | +60                         |                             | +125                        | °C    |

| VRTSET Accuracy                                 | R <sub>NTC</sub> temperature = +60°C to +125°C, 15°C<br>hysteresis (typ) (10k NTC Panasonic ERTJ1VR103) | -5                          |                             | +5                          | °C    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{VL} = V_{BST} = 6.5V, V_{CC} = V_{EN} = 5V, V_{ILIM} = 1.5V, VID_ = SEL = REF = BUF = unconnected, V_{COMP} = V_{RS+} = 1.0V, R_{VRTEADY} = 5k\Omega$  pullup to 5V,  $R_{SS/OVP} = 12k\Omega$  to GND,  $R_{NTC} = 10k\Omega$  to GND,  $f_{SW} = 300kHz$ ,  $R_{VRTSET} = 118k\Omega$  to GND,  $V_{CS_+} = V_{CS_-} = 1V$ , PWM\_ = unconnected,  $R_{VRHOT} = 249\Omega$  pullup to 1.05V,  $V_{GND} = V_{PGND_-} = V_{LX_-} = V_{RS-} = 0V$ ,  $DL_- = DH_- = unconnected$ ,  $T_A = 0^{\circ}C$  to +85°C. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                                             | CONDITIONS                                      | MIN  | ТҮР                      | MAX  | UNITS |

|-------------------------------------------------------|-------------------------------------------------|------|--------------------------|------|-------|

| PWM DRIVER                                            |                                                 | •    |                          |      | •     |

| Output Low Level                                      | $I_{PWM} = +5mA$                                |      | 0.1                      | 0.4  | V     |

| Output High Level                                     | I <sub>PWM</sub> = -5mA                         | 4.5  | 4.9                      |      | V     |

| Source Current                                        | $V_{PWM} = V_{CC} - 2V$                         |      | 52                       |      | mA    |

| Sink Current                                          | $V_{PWM} = 2V$                                  |      | 65                       |      | mA    |

| Rise/Fall Times                                       |                                                 |      | 10                       |      | ns    |

| PWM Disable Program Threshold                         | $4V < V_{CC} < 5.5V$                            | 3.0  | V <sub>CC</sub> -<br>0.7 |      | V     |

| GATE-DRIVER SPECIFICATIONS                            |                                                 | ŀ    |                          |      | •     |

| VL_, BST_ to LX_ Input Voltage Range                  |                                                 | 4.5  |                          | 6.5  | V     |

| LX Operating Range                                    |                                                 |      |                          | 26   | V     |

| VL_ UVLO Threshold (VL12,<br>MAX8809A; VL1, MAX8810A) | V <sub>VL_</sub> rising, 250mV hysteresis (typ) | 3.25 | 3.55                     | 3.80 | V     |

| Driver Static Supply Current, IVL                     | DH_ = BST_                                      |      | 1                        | 1.6  |       |

| (per Channel)                                         | DH_ = LX_                                       |      | 1.1                      | 1.8  | mA    |

| Boost Static Supply Current, IBST_<br>(per Channel)   | DH_ = BST_                                      |      | 0.6                      | 1    | mA    |

|                                                       | Sourcing current, $V_{VL}$ = 6.5V               |      | 1.1                      | 2.0  |       |

| DH Driver Resistance                                  | Sinking current, $V_{VL}$ = 6.5V                |      | 0.8                      | 1.2  | Ω     |

|                                                       | Sourcing current, $V_{VL}$ = 6.5V               |      | 0.85                     | 1.7  |       |

| DL Driver Resistance                                  | Sinking current, $V_{VL}$ = 6.5V                |      | 0.3                      | 0.6  | Ω     |

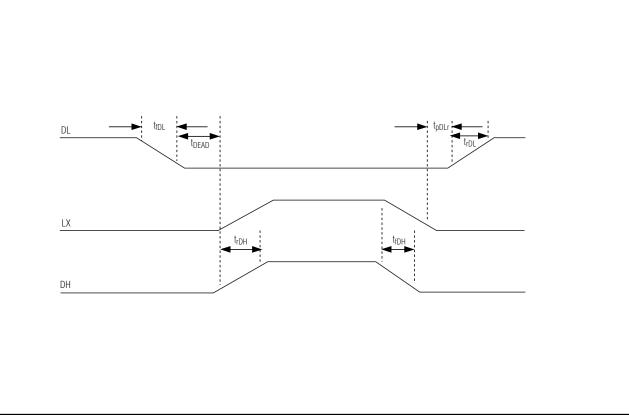

| DH_ Rise Time (t <sub>rDH</sub> )                     | C <sub>DH</sub> _ = 3000pF                      |      | 14                       |      | ns    |

| DH_ Fall Time (tfDH)                                  | C <sub>DH</sub> _ = 3000pF                      |      | 9                        |      | ns    |

| DL_ Rise Time (t <sub>rDL</sub> )                     | C <sub>DL_</sub> = 3000pF                       |      | 10                       |      | ns    |

| DL_ Fall Time (t <sub>fDL</sub> )                     | $C_{DL_{}} = 3000 pF$                           |      | 7                        |      | ns    |

| DH_ Propagation Delay (t <sub>pDHf</sub> )            | CS+ rising to DH falling                        |      | 32                       |      | ns    |

| Dead Time (t <sub>pDLr</sub> )                        | LX_ falling to DL_ rising                       |      | 18                       |      | ns    |

| Dead Time (t <sub>DEAD</sub> )                        | DL_ falling to DH_ rising                       |      | 35                       |      | ns    |

| INTERNAL BOOST-DIODE SPECIFIC                         | ATIONS                                          |      |                          |      |       |

| On-Resistance                                         | I <sub>BST</sub> = 2mA                          |      | 6                        |      | Ω     |

|                                                       |                                                 |      |                          |      |       |

### **ELECTRICAL CHARACTERISTICS**

$(V_{VL} = V_{BST} = 6.5V, V_{CC} = V_{EN} = 5V, V_{ILIM} = 1.5V, VID_ = SEL = REF = BUF = unconnected, V_{COMP} = V_{RS+} = 1.0V, R_{VRREADY} = 5k\Omega$  pullup to 5V, R<sub>SS/OVP</sub> = 12k $\Omega$  = R<sub>NTC</sub> = 10k $\Omega$  to GND, f<sub>SW</sub> = 300kHz, R<sub>VRTSET</sub> = 50k $\Omega$  to GND, V<sub>CS\_+</sub> = V<sub>CS\_-</sub> = 1V, PWM\_ = unconnected, R<sub>VRHOT</sub> = 249 $\Omega$  pullup to 1.05V, V<sub>GND</sub> = V<sub>PGND\_</sub> = V<sub>LX\_</sub> = V<sub>RS-</sub> = 0V, DL\_ = DH\_ = unconnected, T\_A = -40°C to +85°C.) (Note 2)

| PARAMETER                                    | CONDITIONS                                                                     | MIN    | ΤΥΡ | MAX    | UNITS |

|----------------------------------------------|--------------------------------------------------------------------------------|--------|-----|--------|-------|

| V <sub>CC</sub> Operating Range              |                                                                                | 4.5    |     | 5.5    | V     |

|                                              | Rising                                                                         | 4.0    |     | 4.5    | V     |

| V <sub>CC</sub> UVLO Trip Level              | Falling                                                                        | 3.7    |     | 4.3    | v     |

| INTERNAL REFERENCE (REF)                     |                                                                                |        |     |        |       |

| Output Voltage                               | I <sub>REF</sub> = -100μA                                                      | 1.99   |     | 2.01   | V     |

| Output Regulation (Sourcing)                 | $V_{CC}$ = 4.5V at $I_{REF}$ = -500µA to $V_{CC}$ = 5.5V at $I_{REF}$ = -100µA | -0.065 |     | +0.065 | %     |

| Output Regulation (Sinking)                  | $V_{CC}$ = 4.5V at $I_{REF}$ = +100µA to $V_{CC}$ = 5.5V at $I_{REF}$ = +500µA | -0.2   |     | +0.2   | %     |

| BUF REFERENCE                                | ·                                                                              | •      |     |        |       |

| BUF Regulation Voltage                       | I <sub>BUF</sub> = 0A                                                          | 0.99   |     | 1.01   | V     |

| BUF Output Regulation                        | $V_{CC}$ = 4.5V at $I_{BUF}$ = +100µA to $V_{CC}$ = 5.5V at $I_{REF}$ = +500µA | -0.4   |     | +0.4   | %     |

| SOFT-START                                   |                                                                                |        |     |        |       |

| EN Startup Delay (TD1)                       | From EN rising to V <sub>OUT</sub> rising                                      | 1.6    |     | 2.8    | ms    |

| Soft-Start Period Range (TD2)                | $12k\Omega < R_{SS/OVP} < 90.9k\Omega$                                         | 0.5    |     | 6.5    | ms    |

| Soft-Start Tolerance                         | $R_{SS/OVP} = 56k\Omega$                                                       | 2.25   |     | 3.75   | ms    |

| ntel Boot Level Duration (TD3)               | SEL = GND or SEL = $V_{CC}$                                                    | 175    |     | 350    | μs    |

| VOLTAGE REGULATION                           |                                                                                |        |     |        |       |

| RS+ Input Bias Current                       | $V_{RS+} = 1.0V$                                                               |        |     | 1      | μA    |

| RS- Input Bias Current                       | $V_{RS-} = 0.2V$                                                               |        |     | 1      | μA    |

| Output-Voltage Initial Accuracy              | V <sub>DAC</sub> = 1V (Note 1)                                                 | -0.35  |     | +0.35  | %     |

| g <sub>MV</sub> Amplifier Transconductance   |                                                                                | 1.91   |     | 2.06   | mS    |

| CURRENT LIMIT                                |                                                                                |        |     |        |       |

| Average Current-Limit Trip-Level<br>Accuracy | V <sub>ILIM</sub> = 1.5V                                                       | -11    |     | +11    | %     |

| LIM Input Bias Current                       |                                                                                |        |     | 1      | μA    |

| LIM Default Program Level                    | $V_{ILIM} > V_{CC} - 0.2V$                                                     | 1.197  |     | 1.463  | V     |

| ENABLE INPUT (EN)                            | · ·                                                                            | •      |     |        |       |

| Furn-On Threshold (Rising)                   | $V_{CC}$ = 4.5V to 5.5V, 100mV typ hysteresis                                  | 0.8    |     | 0.9    | V     |

| _OGIC INPUTS (VID0–VID7)                     |                                                                                |        |     |        |       |

| NTEL (SEL = HIGH OR LOW)                     |                                                                                |        |     |        |       |

| Input Low Level                              | V <sub>CC</sub> = 4.5V to 5.5V                                                 |        |     | 0.4    | V     |

| Input High Level                             | V <sub>CC</sub> = 4.5V to 5.5V                                                 | 0.8    |     |        | V     |

| Input Pulldown Resistance                    |                                                                                | 100    |     | 270    | kΩ    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{VL} = V_{BST} = 6.5V, V_{CC} = V_{EN} = 5V, V_{ILIM} = 1.5V, VID_ = SEL = REF = BUF = unconnected, V_{COMP} = V_{RS+} = 1.0V, R_{VRREADY} = 5k\Omega$  pullup to 5V, R<sub>SS</sub>/OVP = 12k $\Omega$  = R<sub>NTC</sub> = 10k $\Omega$  to GND, f<sub>SW</sub> = 300kHz, R<sub>VRTSET</sub> = 50k $\Omega$  to GND, V<sub>CS\_+</sub> = V<sub>CS\_-</sub> = 1V, PWM\_ = unconnected, R<sub>VRHOT</sub> = 249 $\Omega$  pullup to 1.05V, V<sub>GND</sub> = V<sub>PGND\_</sub> = V<sub>LX\_</sub> = V<sub>RS-</sub> = 0V, DL\_ = DH\_ = unconnected, T\_A = -40°C to +85°C.) (Note 2)

| PARAMETER                                    | CONDITIONS                                                    | MIN                         | TYP | MAX                         | UNITS |

|----------------------------------------------|---------------------------------------------------------------|-----------------------------|-----|-----------------------------|-------|

| AMD (SEL = UNCONNECTED)                      |                                                               |                             |     |                             |       |

| Input Low Level                              | V <sub>CC</sub> = 4.5V to 5.5V                                |                             |     | 0.6                         | V     |

| Input High Level                             | V <sub>CC</sub> = 4.5V to 5.5V                                | 1.4                         |     |                             | V     |

| Input Pulldown Resistance                    |                                                               | 100                         |     | 270                         | kΩ    |

| LOGIC INPUT (SEL)                            | · · ·                                                         |                             |     |                             |       |

| Internal Bias Resistance                     |                                                               | 50                          |     | 200                         | kΩ    |

| Input Low Level                              | $V_{CC} = 4.5V$ to 5.5V                                       |                             |     | 0.5                         | V     |

| Input High Level                             | $V_{CC} = 4.5V$ to 5.5V                                       | V <sub>CC</sub> -<br>0.5    |     |                             | V     |

| VRREADY OUTPUT                               |                                                               |                             |     |                             |       |

| Output Low Level                             | $I_{VRREADY} = +4mA$                                          |                             |     | 0.4                         | V     |

| Output High Leakage                          | $V_{VRREADY} = 5.5V$                                          |                             |     | 1                           | μA    |

| VRREADY Blanking Time                        | From EN rising to VRREADY rising, $R_{SS/OVP}$ = 12k $\Omega$ | 3.0                         |     | 5.5                         | ms    |

| VRREADY Upper Threshold<br>(Note 1)          | (V <sub>RS+</sub> - V <sub>RS-)</sub> rising                  | V <sub>DAC</sub> + 0.150    |     | V <sub>DAC</sub> +<br>0.200 |       |

|                                              | (V <sub>RS+</sub> - V <sub>RS-)</sub> falling                 | V <sub>DAC</sub> +<br>0.075 |     | V <sub>DAC</sub> +<br>0.125 | V     |

| VRREADY Lower Threshold                      | (V <sub>RS+</sub> - V <sub>RS-)</sub> falling                 | V <sub>DAC</sub> -<br>0.250 |     | V <sub>DAC</sub> -<br>0.200 |       |

| (Note 1)                                     | (V <sub>RS+</sub> - V <sub>RS-)</sub> rising                  | V <sub>DAC</sub> -<br>0.175 |     | V <sub>DAC</sub> -<br>0.125 | V     |

| OVERVOLTAGE PROTECTION                       | ·                                                             | •                           |     |                             |       |

| Intel (SEL = High or Low)                    | (V <sub>RS+</sub> - V <sub>RS-)</sub> rising (Note 1)         | V <sub>DAC</sub> +<br>0.150 |     | V <sub>DAC</sub> +<br>0.200 | V     |

| AMD (SEL = Unconnected)                      | (V <sub>RS+</sub> - V <sub>RS-)</sub> rising                  | 1.75                        |     | 1.80                        | V     |

| SS/OVP High Level                            | I <sub>SS/OVP</sub> = 10mA                                    | V <sub>CC</sub> -<br>0.450  |     |                             | V     |

| OSCILLATOR                                   |                                                               |                             |     |                             |       |

| Oscillator Frequency Accuracy<br>(per Phase) | Frequency per phase = 300kHz                                  | -20                         |     | +20                         | %     |

| Switching Frequency Range (per Phase)        |                                                               | 150                         |     | 1200                        | kHz   |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{VL} = V_{BST} = 6.5V, V_{CC} = V_{EN} = 5V, V_{ILIM} = 1.5V, VID_ = SEL = REF = BUF = unconnected, V_{COMP} = V_{RS+} = 1.0V, R_{VRREADY} = 5k\Omega$  pullup to 5V, R<sub>SS</sub>/OVP = 12k $\Omega$  = R<sub>NTC</sub> = 10k $\Omega$  to GND, f<sub>SW</sub> = 300kHz, R<sub>VRTSET</sub> = 50k $\Omega$  to GND, V<sub>CS\_+</sub> = V<sub>CS\_-</sub> = 1V, PWM\_ = unconnected, R<sub>VRHOT</sub> = 249 $\Omega$  pullup to 1.05V, V<sub>GND</sub> = V<sub>PGND\_</sub> = V<sub>LX\_</sub> = V<sub>RS-</sub> = 0V, DL\_ = DH\_ = unconnected, T<sub>A</sub> = -40°C to +85°C.) (Note 2)

| PARAMETER                                                      | CONDITIONS                                                                       | MIN  | ТҮР | MAX  | UNITS |

|----------------------------------------------------------------|----------------------------------------------------------------------------------|------|-----|------|-------|

| CURRENT-SENSE AMPLIFIERS                                       |                                                                                  | •    |     |      | •     |

| Current-Sense Amplifier Gain (G <sub>CA</sub> )                | $R_{\rm NTC} = 10 k\Omega$                                                       | 27   |     | 33   | V/V   |

| CS_+ Input Bias Current                                        | $V_{CS} + = V_{CS} - = 2V$                                                       |      |     | 4.5  | μA    |

| CS Input Bias Current                                          | $V_{CS}+ = V_{CS}- = 2V$                                                         |      |     | 7    | μA    |

| GAIN TEMPERATURE COMPENSATI                                    | ON (NTC)                                                                         |      |     |      |       |

| Temperature Compensation Accuracy                              | R <sub>NTC</sub> temperature = 0°C to +125°C<br>(10k NTC Panasonic ERTJ1VR103)   | -7.5 |     | +7.5 | %     |

| VRHOT TEMPERATURE MONITORIN                                    | G                                                                                |      |     |      |       |

| VRHOT Output Low Voltage                                       | 4mA sink current                                                                 |      |     | 0.4  | V     |

| VRHOT Output High Leakage Current                              | V <sub>VRHOT</sub> = 5.5V                                                        |      |     | 5    | μA    |

| VRTSET Temperature Range                                       |                                                                                  | +60  |     | +125 | °C    |

| VRTSET Accuracy                                                | R <sub>NTC</sub> temperature = +60°C to +125°C (10k NTC<br>Panasonic ERTJ1VR103) | -5   |     | +5   | °C    |

| PWM DRIVER                                                     | ·                                                                                |      |     |      |       |

| Output Low Level                                               | $I_{PWM} = +5mA$                                                                 |      |     | 0.4  | V     |

| Output High Level                                              | I <sub>PWM</sub> _ = -5mA                                                        | 4.5  |     |      | V     |

| PWM Disable Program Threshold                                  | $4V < V_{CC} < 5.5V$                                                             | 3    |     |      | V     |

| GATE-DRIVER SPECIFICATIONS                                     |                                                                                  |      |     |      |       |

| VL_, BST_ to LX_ Input Voltage Range                           |                                                                                  | 4.5  |     | 6.5  | V     |

| LX_ Operating Range                                            |                                                                                  |      |     | 26   | V     |

| VL_ UVLO Threshold (MAX8809A,<br>VL12; MAX8810A, VL1)          | V <sub>VL</sub> _rising, 250mV hysteresis (typ)                                  | 3.25 |     | 3.80 | V     |

| Driver Static Supply Current,                                  | DH_ = BST_                                                                       |      |     | 1.6  |       |

| I <sub>VL_</sub> (per Channel)                                 | DH_ = LX_                                                                        |      |     | 1.8  | mA    |

| Boost Static Supply Current,<br>I <sub>BST</sub> (per Channel) | DH_ = BST_                                                                       |      |     | 1    | mA    |

|                                                                | Sourcing current, $V_{VL}$ = 6.5V                                                | 1    |     | 2.0  | 0     |

| DH_ Driver Resistance                                          | Sinking current, $V_{VL_} = 6.5V$                                                |      |     | 1.2  | Ω     |

|                                                                | Sourcing current, $V_{VL}$ = 6.5V                                                |      |     | 1.7  | 0     |

| DL_ Driver Resistance                                          | Sinking current, $V_{VL} = 6.5V$                                                 |      |     | 0.6  | Ω     |

Note 1: V<sub>DAC</sub> refers to the internal voltage set by the VID code.

Note 2: Specifications to -40°C are guaranteed by design and characterization.

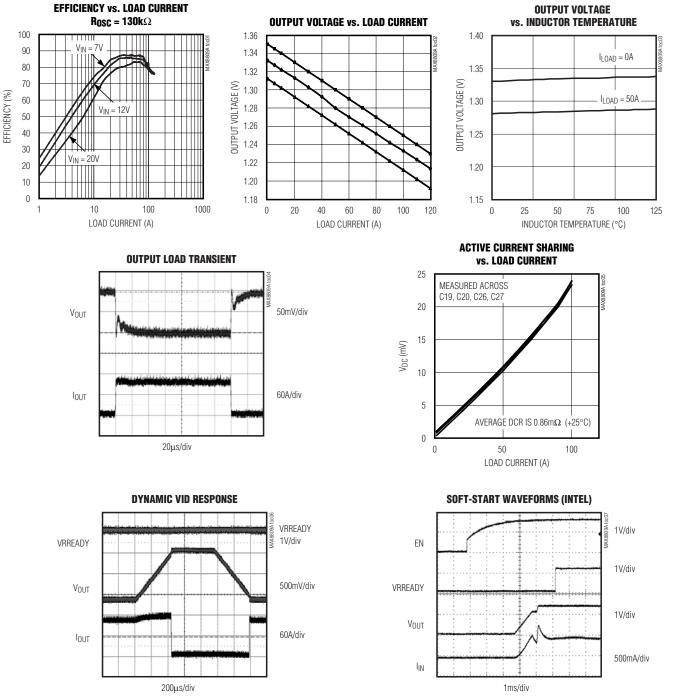

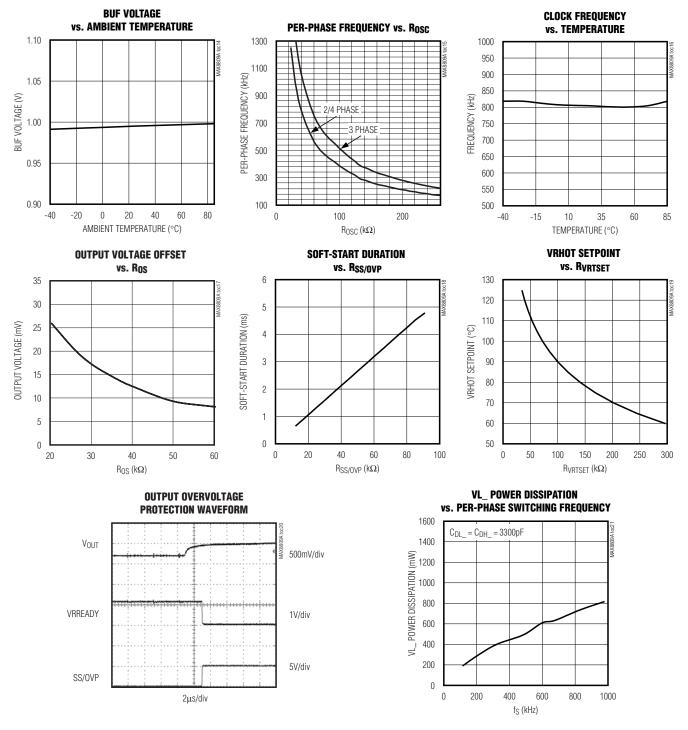

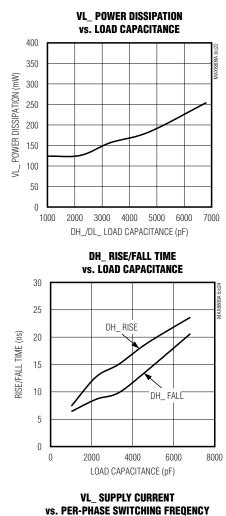

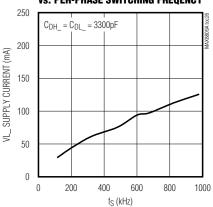

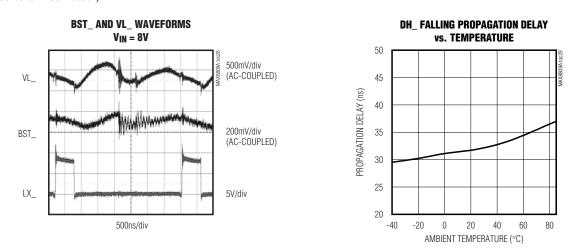

### **Typical Operating Characteristics**

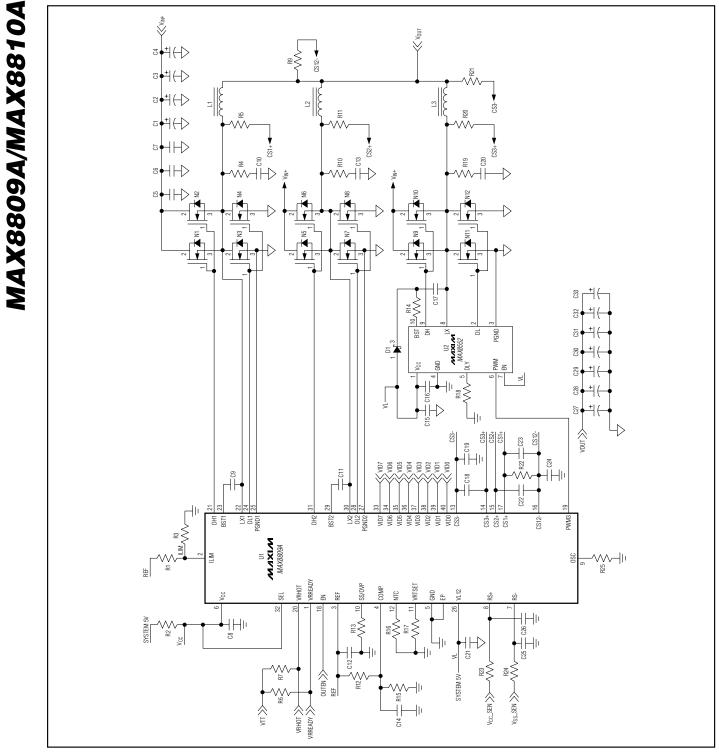

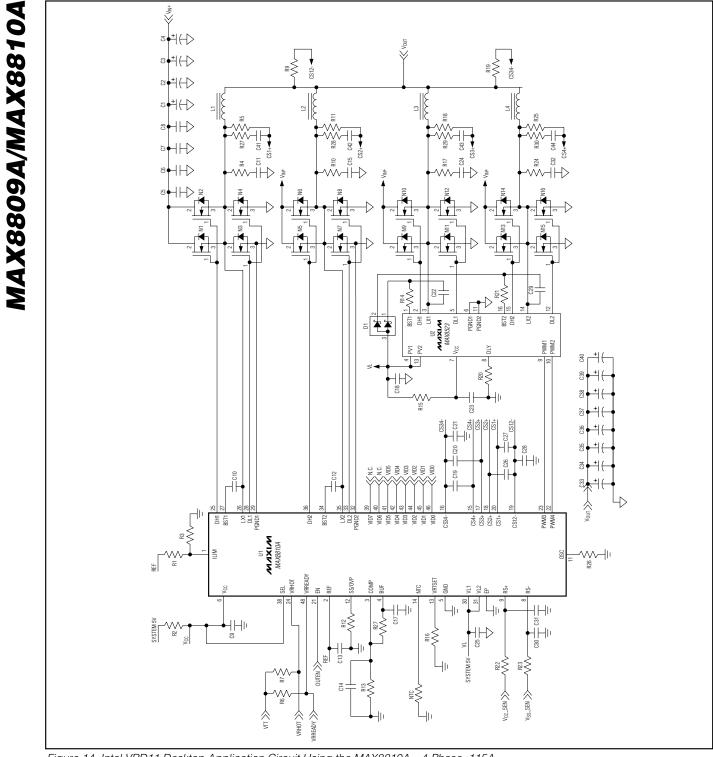

(Circuit of Figure 14,  $V_{IN}$  = 12V,  $V_{OUT}$  = 1.35V,  $I_{OUT\_MAX}$  = 115A,  $R_O$  = 1m $\Omega$ ,  $f_{SW}$  = 200kHz,  $V_{CC}$  = 5V,  $V_{VL\_}$  = 6.5V,  $T_A$  = +25°C, unless otherwise noted.)

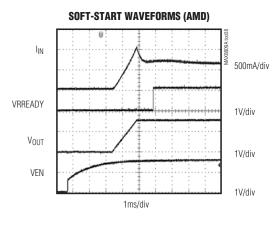

### **Typical Operating Characteristics (continued)**

(Circuit of Figure 14, V<sub>IN</sub> = 12V, V<sub>OUT</sub> = 1.35V, I<sub>OUT\_MAX</sub> = 115A, R<sub>O</sub> = 1m $\Omega$ , f<sub>SW</sub> = 200kHz, V<sub>CC</sub> = 5V, V<sub>VL</sub> = 6.5V, T<sub>A</sub> = +25°C, unless otherwise noted.)

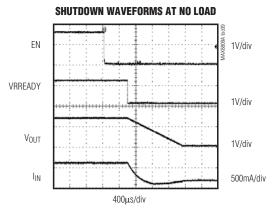

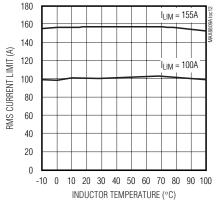

SHUTDOWN WAVEFORMS AT FULL LOAD

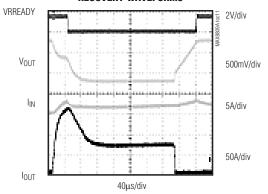

#### REFERENCE VOLTAGE vs. AMBIENT TEMPERATURE

/N/IXI/N

MAX8809A/MAX8810A

### **Typical Operating Characteristics (continued)**

(Circuit of Figure 14,  $V_{IN}$  = 12V,  $V_{OUT}$  = 1.35V,  $I_{OUT\_MAX}$  = 115A,  $R_O$  = 1m $\Omega$ , fsw = 200kHz,  $V_{CC}$  = 5V,  $V_{VL}$  = 6.5V, T<sub>A</sub> = +25°C, unless otherwise noted.)

MAX8809A/MAX8810A

### **Typical Operating Characteristics (continued)**

(Circuit of Figure 14,  $V_{IN}$  = 12V,  $V_{OUT}$  = 1.35V,  $I_{OUT}MAX$  = 115A,  $R_O$  = 1m $\Omega$ ,  $f_{SW}$  = 200kHz,  $V_{CC}$  = 5V,  $V_{VL}$  = 6.5V,  $T_A$  = +25°C, unless otherwise noted.)

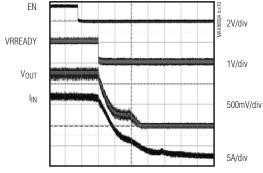

### **Typical Operating Characteristics (continued)**

(Circuit of Figure 14,  $V_{IN}$  = 12V,  $V_{OUT}$  = 1.35V,  $I_{OUT\_MAX}$  = 115A,  $R_O$  = 1m $\Omega$ , fsw = 200kHz,  $V_{CC}$  = 5V,  $V_{VL}$  = 6.5V,  $T_A$  = +25°C, unless otherwise noted.)

### **Pin Description**

| P        | IN       |                 | EUNICTION                                                                                                                                                                                                                                                                                                  |  |  |  |

|----------|----------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MAX8809A | MAX8810A | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                   |  |  |  |

| 1        | 48       | VRREADY         | Open-Drain, Power-Okay Indicator. VRREADY is an open-drain output that goes high impedance when the output is in regulation. VRREADY pulls low when the output is out of regulation, the IC is in shutdown, or $V_{CC}$ is below the UVLO threshold.                                                       |  |  |  |

| 2        | 1        | ILIM            | Current-Limit Set Input. Connect to the center tap of an external resistor-divider from REF to GND to set the cycle-by-cycle average current-limit threshold. Connect ILIM to $V_{CC}$ to select the default current-limit threshold.                                                                      |  |  |  |

| 3        | 2        | REF             | Internal Reference Output. REF regulates to 2V. Bypass REF to GND with a 0.1 $\mu$ F to 1 $\mu$ F ceramic capacitor. Do not use a capacitor greater than 1 $\mu$ F. REF sources up to 500 $\mu$ A for external loads. REF is enabled when V <sub>CC</sub> is above UVLO regardless of the state of EN.     |  |  |  |

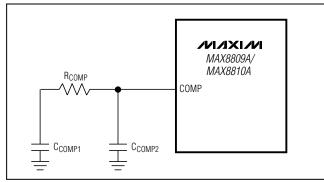

| 4        | 3        | COMP            | Error-Amplifier Output. Connect COMP to the compensation network to implement either voltage positioning or integral feedback-control. Connect a resistor from COMP to GND to set the offset voltage. See the <i>Loop-Compensation Design</i> section for details on determining the compensation network. |  |  |  |

| 5        | 5        | GND             | Analog Ground. Connect GND to the analog ground plane.                                                                                                                                                                                                                                                     |  |  |  |

| 6        | 6        | V <sub>CC</sub> | IC Supply Input. Connect $V_{CC}$ to a 4.5V to 5.5V power supply. Bypass $V_{CC}$ to GND with a 1µF or larger ceramic capacitor.                                                                                                                                                                           |  |  |  |

| 7        | 8        | RS-             | Output-Voltage Remote-Sense Negative Input. Connect RS- to the $V_{SS\_SEN}$ remotesense point at the load when using the remote sense. Otherwise, connect RS- to GND at the load.                                                                                                                         |  |  |  |

| 8        | 9        | RS+             | Output-Voltage Remote-Sense Positive Input. Connect RS+ to the $V_{CC\_SEN}$ remotesense point at the load when using remote sense. Otherwise, connect RS+ to the output at the load.                                                                                                                      |  |  |  |

### Pin Description (continued)

| PIN      |                 | NAME   |                                                                                                                                                                                                                                                                                                                                                               |

|----------|-----------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX8809A | X8809A MAX8810A |        | FUNCTION                                                                                                                                                                                                                                                                                                                                                      |

| 9        | 11              | OSC    | Internal Clock Oscillator Frequency Set Input. Connect a resistor from OSC to GND to set the internal oscillator frequency. See the <i>Setting the Switching Frequency</i> section for determining the resistor value.                                                                                                                                        |

| 10       | 12              | SS/OVP | Soft-Start Program Input and Overvoltage-Protection Fault Flag. Connect a resistor from SS/OVP to GND to set the soft-start period. SS/OVP pulls to $V_{CC}$ during an OVP event to signal the fault condition. See the <i>Soft-Start</i> section for determining the resistor value.                                                                         |

| 11       | 13              | VRTSET | Temperature Comparator Program Input. Connect a resistor from VRTSET to GND to set the VRHOT temperature threshold. Connect VRTSET to V <sub>CC</sub> to disable the VRHOT monitoring feature. See the <i>Temperature Monitoring (VRTSET, VRHOT)</i> section for resistor selection.                                                                          |

| 12       | 14              | NTC    | Temperature-Sensing Input. Connect a 10k $\Omega$ NTC thermistor between NTC and GND for load-line independent temperature compensation. Connect NTC to V <sub>CC</sub> to disable the temperature compensation and VRHOT monitoring features. See the <i>Temperature Monitoring (VRTSET, VRHOT)</i> section for more details on selection of the NTC device. |

| 13       | _               | CS3-   | Phase 3 Current-Sense Negative Input. Connect to the load side of the output current-<br>sensing element.                                                                                                                                                                                                                                                     |

| 14       | 17              | CS3+   | Phase 3 Current-Sense Positive Input. Connect CS3+ to the positive side of the output current-sense resistor, or the positive side of the filtering capacitor if inductor DCR current sensing is used.                                                                                                                                                        |

| 15       | 18              | CS2+   | Phase 2 Current-Sense Positive Input. Connect CS2+ to the positive side of the output current-sense resistor, or the positive side of the filtering capacitor if inductor DCR current sensing is used.                                                                                                                                                        |

| 16       | 19              | CS12-  | Phases 1 and 2 Current-Sense Common Negative Input. Connect to the load side of the output current-sensing elements.                                                                                                                                                                                                                                          |

| 17       | 20              | CS1+   | Phase 1 Current-Sense Positive Input. Connect CS1+ to the positive side of the output current-sense resistor, or the positive side of the filtering capacitor if inductor DCR current sensing is used.                                                                                                                                                        |

| 18       | 21              | EN     | Enable Input. Drive EN high to enable the IC. Drive EN low to place the IC in shutdown mode. If V <sub>CC</sub> is greater than the UVLO threshold, EN is internally pulled to V <sub>CC</sub> with a 100k $\Omega$ resistor. If V <sub>CC</sub> is less than the UVLO threshold, EN is internally pulled to GND with a 2k $\Omega$ resistor.                 |

| 19       | 23              | PWM3   | PWM Signal Output for phase 3. PWM3 is low during shutdown, UVLO, and OVP faults. Connect PWM3 to $V_{CC}$ to enable 2-phase operation.                                                                                                                                                                                                                       |

| 20       | 24              | VRHOT  | Temperature Fault Flag. VRHOT is an active-high, open-drain output that goes high impedance when the temperature sensed by the thermistor at NTC exceeds the temperature threshold programmed at VRTSET.                                                                                                                                                      |

| 21       | 25              | DH1    | Phase 1 High-Side MOSFET Gate-Drive Output. Connect to the gate of the high-side MOSFET for phase 1. DH1 is pulled low during shutdown, UVLO, and OVP faults.                                                                                                                                                                                                 |

| 22       | 26              | LX1    | Phase 1 Inductor Sense Point. Connect LX1 to the switched side of the inductor for phase 1.                                                                                                                                                                                                                                                                   |

### Pin Description (continued)

| PIN      |          |           | FUNCTION                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|----------|----------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| MAX8809A | MAX8810A | NAME      | FUNCTION                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 23       | 27       | BST1      | Phase 1 High-Side MOSFET Gate-Drive Supply. Connect a 0.22µF or larger ceramic capacitor from BST1 to LX1 to supply gate drive for the high-side MOSFET. See the <i>Boost Capacitor Selection</i> section for details on calculating the BST1 capacitor value.                                                                                                 |  |  |  |  |

| 24       | 28       | DL1       | Phase 1 Low-Side MOSFET Gate-Drive Output. Connect to the gate of the low-side MOSFET for phase 1. DL1 is pulled low during undervoltage lockout and pulled high during an OVP fault. DL1 is high in shutdown if $V_{CC}$ is greater than the UVLO threshold.                                                                                                  |  |  |  |  |

| 25       | 29       | PGND1     | Power Ground for the Phase 1 Driver. Connect PGND1 to the source of the phase 1 low-side MOSFET. PGND1 must be connected to PGND2 and GND externally. See the <i>PC Board Layout Guidelines</i> section for more details.                                                                                                                                      |  |  |  |  |

| 26       |          | VL12      | Phase 1 and 2 Low-Side MOSFET Gate-Drive Supply. Connect VL12 to a 4.5V to 6.5V supply. Bypass VL12 with a $2.2\mu$ F or larger ceramic capacitor to the power ground plane.                                                                                                                                                                                   |  |  |  |  |

| 27       | 32       | PGND2     | Power Ground for the Phase 2 Driver. Connect PGND2 to the source of the phase 2 low-side MOSFET. PGND2 must be connected to PGND1 and GND externally. See the <i>PC Board Layout Guidelines</i> section for more details.                                                                                                                                      |  |  |  |  |

| 28       | 33       | DL2       | Phase 2 Low-Side MOSFET Gate-Drive Output. Connect to the gate of the low-side MOSFET for phase 2. DL2 is pulled low during undervoltage lockout and pulled high during an OVP fault. DL2 is high in shutdown if $V_{CC}$ is greater than the UVLO threshold.                                                                                                  |  |  |  |  |

| 29       | 34       | BST2      | Phase 2 High-Side MOSFET Gate-Drive Supply. Connect a 0.22µF or larger ceramic capacitor from BST2 to LX2 to supply gate drive for the high-side MOSFET. See the <i>Boost Capacitor Selection</i> section for details on calculating the BST2 capacitor value.                                                                                                 |  |  |  |  |

| 30       | 35       | LX2       | Phase 2 Inductor Sense Point. Connect LX2 to the switched side of the inductor for phase 2.                                                                                                                                                                                                                                                                    |  |  |  |  |

| 31       | 36       | DH2       | Phase 2 High-Side MOSFET Gate-Drive Output. Connect to the gate of the high-side MOSFET for Phase 2. DH2 is pulled low during shutdown, UVLO, and OVP faults.                                                                                                                                                                                                  |  |  |  |  |

| 32       | 38       | SEL       | VID Table Selection Input. Connect SEL to GND to select the VRD10 VID code (Table 5). Connect SEL to $V_{CC}$ to select the VRD11 8-bit VID code (Table 6). Leave SEL unconnected to select the K8 Rev F VID code (Table 4).                                                                                                                                   |  |  |  |  |

| 33–40    | 39–46    | VID7-VID0 | Voltage Identification Code Inputs. Use VID_ to set the output voltage. SEL selects the VRD10, VRD11, or K8 Rev F VID logic codes. Connect VID_ to the system V <sub>TT</sub> with a 680 $\Omega$ resistor for logic-high for Intel VR solutions. Connect VID_ to the system V <sub>DDQ</sub> with a 1k $\Omega$ resistor for logic-high for AMD VR solutions. |  |  |  |  |

### Pin Description (continued)

| P        | IN            | NAME  | FUNCTION                                                                                                                                                                                                                         |

|----------|---------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX8809A | MAX8810A      | NAME  | FUNCTION                                                                                                                                                                                                                         |

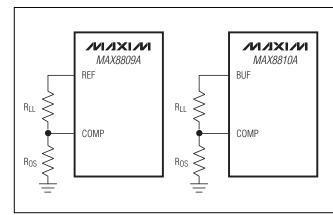

| _        | 4             | BUF   | 1V Reference Output. Bypass BUF to GND with a $1\mu$ F or larger ceramic capacitor.<br>Connect a resistor from COMP to BUF to set the load-line. See the <i>Loop-Compensation</i><br><i>Design</i> section for more details.     |

|          | 7, 10, 37, 47 | N.C.  | No Internal Connection                                                                                                                                                                                                           |

| _        | 15            | CS4+  | Phase 4 Current-Sense Positive Input. Connect CS4+ to the positive side of the output current-sense resistor, or the positive side of the filtering capacitor if inductor DCR current sensing is used.                           |

| _        | 16            | CS34- | Phases 3 and 4 Current-Sense Common Negative Input. Connect to the load side of the output current-sensing elements.                                                                                                             |

|          | 22            | PWM4  | PWM Signal Output for Phase 4. PWM4 is low during shutdown, UVLO, and OVP faults. Connect PWM4 to V <sub>CC</sub> to enable 3-phase operation. Connect PWM3 and PWM4 to V <sub>CC</sub> to enable 2-phase operation.             |

| _        | 30            | VL1   | Phase 1 Low-Side MOSFET Gate-Drive Supply. Connect VL1 to a 4.5V to 6.5V supply. VL1 must be connected to VL2 externally. Bypass the VL1/VL2 connection with a $2.2\mu$ F or larger ceramic capacitor to the power ground plane. |

|          | 31            | VL2   | Phase 2 Low-Side MOSFET Gate-Drive Supply. Connect VL2 to a 4.5V to 6.5V supply. VL2 must be connected to VL1 externally. Bypass the VL1/VL2 connection with a $2.2\mu$ F or larger ceramic capacitor to the power ground plane. |

| _        | _             | EP    | Exposed Paddle. Connect to the analog GND plane for enhanced thermal power dissipation.                                                                                                                                          |

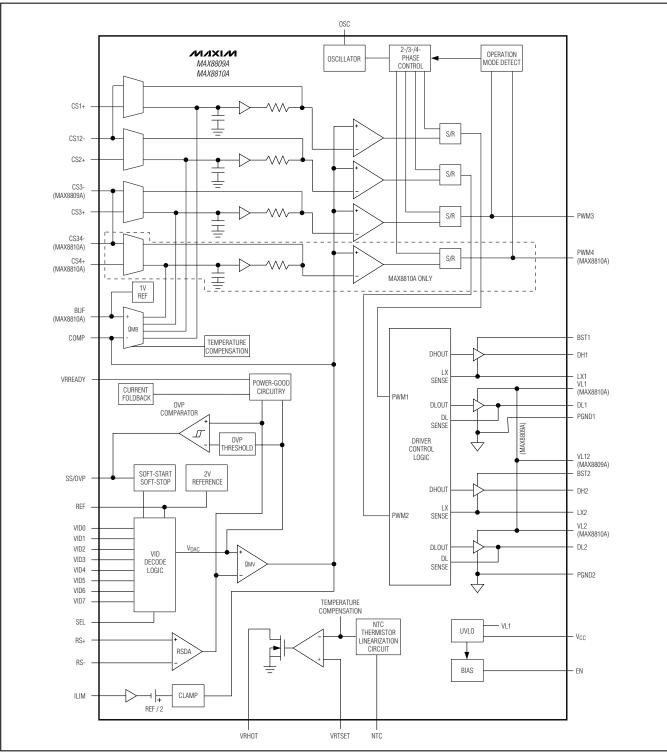

Figure 1. Block Diagram

MIXX/M

MAX8809A/MAX8810A

Figure 2. Driver Timing Diagram

### **Detailed Description**

The MAX8809A/MAX8810A synchronous, 2-/3-/4phase, step-down, current-mode controllers with integrated dual-phase MOSFET drivers provide flexible solutions that fully comply with Intel VRD11/VRD10 and AMD K8 Rev F CPU core supplies. The flexible design supplies load currents of up to 150A for low-voltage CPU core power supplies.

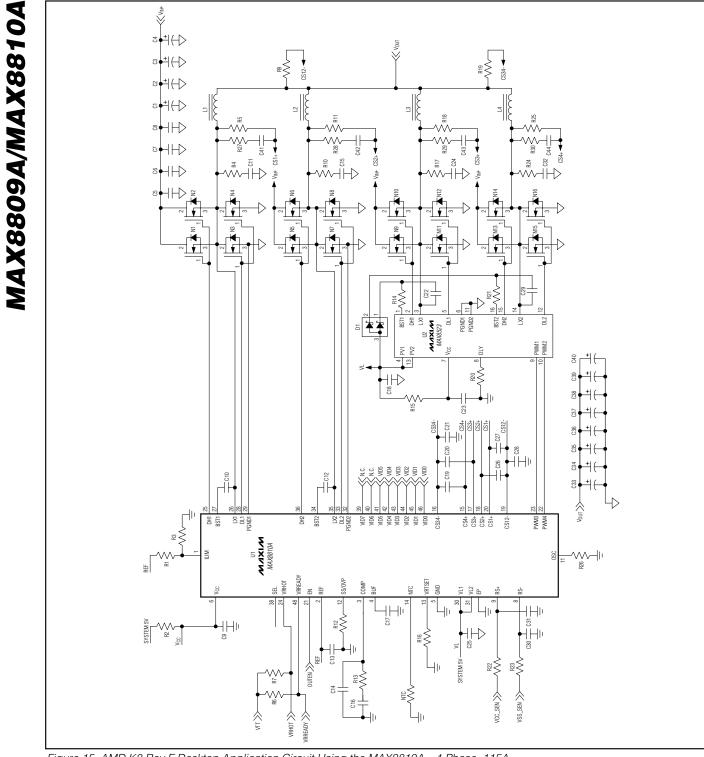

The MAX8809A is suitable for 2- or 3-phase core supply applications. With an integrated dual-MOSFET driver, the MAX8809A offers a single-chip IC solution for dual-phase core supplies. Together with the MAX8552, a high-performance single-phase MOSFET driver, the MAX8809A also supports 3-phase core supplies. Similarly, the MAX8810A features a single IC solution for dual-phase core supplies. It also features two-IC solutions for 3- or 4-phase core supplies by adding a single MOSFET driver (MAX8552) or a dual-MOSFET driver (MAX8523). Both the MAX8809A and MAX8810A fully comply with Intel VRD11, Extended VRD10, and the AMD K8 Rev F VID codes. The SEL input allows the user to select the architecture specifications.

#### **Clock Frequency (OSC)**

An external resistor, ROSC, from OSC to GND sets the internal clock frequency of the MAX8809A/MAX8810A. A 1% resistor is recommended to maintain good frequency accuracy. The internal clock frequency sets the per-phase switching frequency. The selection of switching frequency per phase is influenced by factors such as the switching speed of the MOSFETs, the inductor's core material, different types of input and output capacitors, and the available board space. Once the per-phase switching frequency is selected, the internal clock frequency is determined using the procedure in the *Setting the Switching Frequency* section.

#### Voltage Reference (REF)

A precision 2V reference is provided by the MAX8809A/ MAX8810A at the REF output. REF is capable of sinking and sourcing up to 500 $\mu$ A for external loads. Connect a 0.1 $\mu$ F to 1 $\mu$ F ceramic capacitor from REF to GND. Internal REFOK circuitry monitors the reference voltage. The reference voltage must be above the REFOK threshold of 1.84V to activate the controller. The controller is disabled if the reference voltage falls below 1.74V.

#### **Output Current Sensing (CS\_+, CS\_-)**

The output current of each phase is sensed differentially. A low-offset-voltage, differential-current amplifier (30V/V) at each phase allows low-resistance currentsense resistors to be used to minimize power dissipation. Sensing the current at the output of each phase offers advantages including less noise sensitivity, more accurate current sharing between phases, and the flexibility of using either a current-sense resistor or the DC resistance of the output inductor.

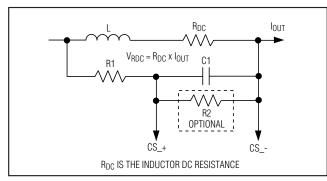

Using the DC resistance, R<sub>DC</sub>, of the output inductor (Figure 3) allows higher efficiency. In this configuration, the initial tolerance and temperature coefficient of R<sub>DC</sub> must be accounted for in the output-voltage droop-error budget. The temperature coefficient can be compensated; see the *Load-Line Independent Inductor DC Resistance Temperature Compensation* section for more details. An RC-filtering network is needed to extract the current information from the output inductor. The time constant of the RC network is calculated as follows:

$$R1 \times C1 = \frac{L}{R_{DC}}$$

where L is the inductance of the output inductor. For 20A or higher current-per-phase applications, the DC resistance of commercially available inductors is approximately  $1m\Omega$ . To minimize current-sense error due to the bias current at the current-sense inputs, choose R1 less than  $2k\Omega$ . Determine the value for C1 as:

Figure 3. Inductor R<sub>DC</sub> Current Sense

$$C1 = \frac{L}{(R_{DC} \times R1)}$$

Select a 1% resistor for R1. For mainstream PCs 20% tolerance is recommended for C1, and for performance PCs 10% tolerance should be considered. If using an inductor with R<sub>DC</sub> greater than  $1m\Omega$ , a resistor (R2) may be necessary to divide down the voltage across CS\_+ and CS\_-. The maximum average signal present at the input of the current-sense amplifier should not exceed 85mV.

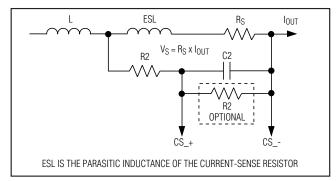

When a current-sense resistor is used for more accurate current sharing and load-line, a similar RC-filtering circuit is recommended to cancel the equivalent series inductance of the current-sense resistor, as shown in Figure 4. Again, select R2 less than  $2k\Omega$ , and C2 is determined by the following equation:

$$C2 = \frac{ESL}{(R_S \times R2)}$$

where ESL is the equivalent series inductance of the current-sense resistor and Rs is the value of the current-sense resistor. For example, a  $1m\Omega$ , 2025 package sense resistor has an ESL of 1.6nH. If using an Rs greater than  $1m\Omega$ , a resistor (R2) may be necessary to divide down the voltage across CS\_+ and CS\_-. The maximum average signal present at the input of the current-sense amplifier should not exceed 85mV.

#### Output Current Limit and Short-Circuit Protection (ILIM)

The MAX8809A/MAX8810A feature a precise average output current limit on a cycle-by-cycle basis using Maxim's proprietary RA<sup>2</sup> technology. The current-limit scheme is insensitive to input-voltage variation, the inductor tolerance, and the tolerance of the currentsense capacitor, permitting the use of low-cost components to reduce total BOM cost. Furthermore, the current limit is fully temperature compensated resulting

Figure 4. Resistor Current Sense

in a constant output current limit over the entire operational temperature range. This eliminates the need to oversize MOSFETs and inductors to compensate for thermal effects. Connecting ILIM to V<sub>CC</sub> programs the default current-limit threshold. To select a different current-limit threshold, connect a resistor-divider from REF to GND with ILIM connected to the center tap. The voltage at ILIM is proportional to the current-limit threshold. See the *Setting the Current-Limit* section for more details.

The current-limit circuitry terminates the DH\_ on-time immediately when the current-sense voltage ( $V_{CS_+} - V_{CS_-}$ ) exceeds the current-limit threshold, allowing the output inductor current to ramp down. At the next switching cycle, the PWM pulse is skipped if the output inductor current is still above the current-limit threshold. Otherwise, the new cycle initiates as normal.

The MAX8809A/MAX8810A offer foldback-current protection under soft-start and overload conditions. This feature allows the VRM to safely operate under shortcircuit conditions and to automatically recover once the short-circuit condition is removed. If the output voltage falls below the VRREADY threshold during an overcurrent event, the foldback current-limit circuitry sets the current-limit threshold to half the user-selected value.

#### **Output Differential Sensing (RS+, RS-)**

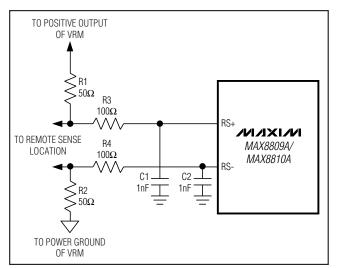

The MAX8809A/MAX8810A feature differential outputvoltage sensing to achieve the highest possible output accuracy. This allows the controllers to sense the actual voltage at the load, so the controller can compensate for losses in the power output and ground lines. Traces from the load point back to RS+ and RS- should be routed close to each other and as far away as possible

Figure 5. Recommended Filtering for Output-Voltage Remote Sensing

from noise sources (such as inductors and high di/dt traces). Use a ground plane to shield the remote-sense traces from noise sources. To filter out common-mode noise, RC filtering is recommended for these inputs as shown in Figure 5. For VRD applications, a 100 $\Omega$  resistor with a 1nF capacitor should be used. For VRM applications, additional 50 $\Omega$  resistors should be connected from these inputs to the local outputs of the converter before the VRM connector. This avoids excessive voltage at the CPU in case the remote-sense connections get disconnected.

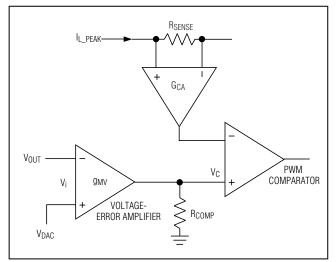

**Programming the Output-Voltage Droop** Both the MAX8809A and MAX8810A employ peak-current-mode control with finite gain to actively set the output-voltage droop. Figure 6 shows the simplified control block diagram. The relationship between the output inductor current in an N-phase DC-DC converter and the output voltage of the voltage-error amplifier is:

$$V_{C} = \frac{I_{OUT}}{N} \times R_{SENSE} \times G_{CA}$$

where G<sub>CA</sub> (30V/V typ) is the gain of the differential current amplifier and N is the number of phases. I<sub>OUT</sub> is the total output current. Therefore, when the output current increases, V<sub>C</sub> increases. On the other hand, V<sub>C</sub> is related to the output voltage of the converter by the following equation:

$$V_{C} = g_{MV} \times R_{COMP} \times (V_{DAC} - V_{OUT})$$

where  $g_{MV}$  is the transconductance of the voltage-error amplifier (2mS typ) and  $V_{DAC}$  is the VID-generated voltage.

Figure 6. Simplified Peak Current-Mode Control IC with Active Output-Voltage Positioning

M/IXI/M

The DC gain of the voltage-error amplifier is equal to  $g_{MV} \times R_{COMP}$ . From the previous equations it is clear that the output-voltage droop can be accurately programmed if the DC gain of the voltage-error amplifier is set to be a finite value. As the output current increases, V<sub>C</sub> increases and, consequently, V<sub>OUT</sub> decreases. Define the output-droop resistance, R<sub>DROOP</sub>, as:

$$R_{DROOP} = \frac{(V_{DAC} - V_{OUT})}{I_{OUT}}$$

then RDROOP can be expressed as:

$$R_{DROOP} = \frac{R_{SENSE} \times G_{CA}}{N \times g_{MV} \times R_{COMP}}$$