## MAXM17514

## 4A, 2.4V to 5.5V Input, High-Efficiency Power Module

### General Description

The MAXM17514 is a fixed-frequency, step-down power module in a thermally-efficient system-in-package (SiP) package that operates from a 2.4V to 5.5V input supply voltage and supports output currents up to 4A. The device includes switch-mode power-supply controller, dual nMOSFET power switches, a fully shielded inductor, as well as compensation components. The device supports 0.75V to 3.6V programmable output voltage. The high level of integration significantly reduces design complexity, manufacturing risks, and offers a true plug-and-play power-supply solution, reducing the time to market.

The MAXM17514 is available in a thermally enhanced, compact 28-pin, 10mm x 6.5mm x 2.8mm SiP package and can operate over the -40°C to +125°C industrial temperature range.

### Applications

- FPGA and DSP Point-of-Load Regulator

- Base Station Point-of-Load Regulator

- Industrial Control Equipment

- Servers

- ATE Equipment

- Medical Equipment

Ordering Information appears at end of data sheet.

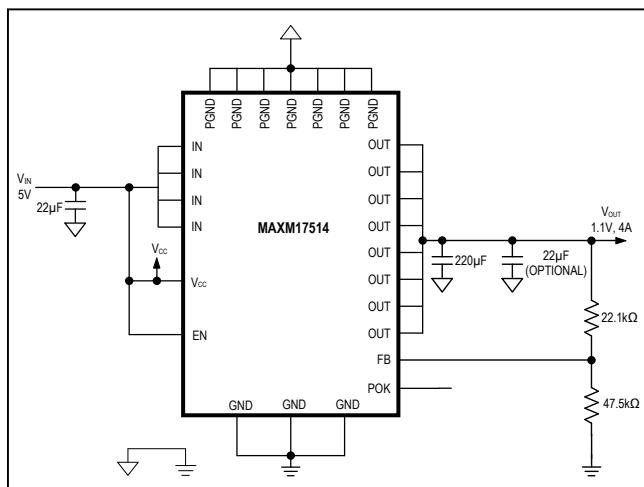

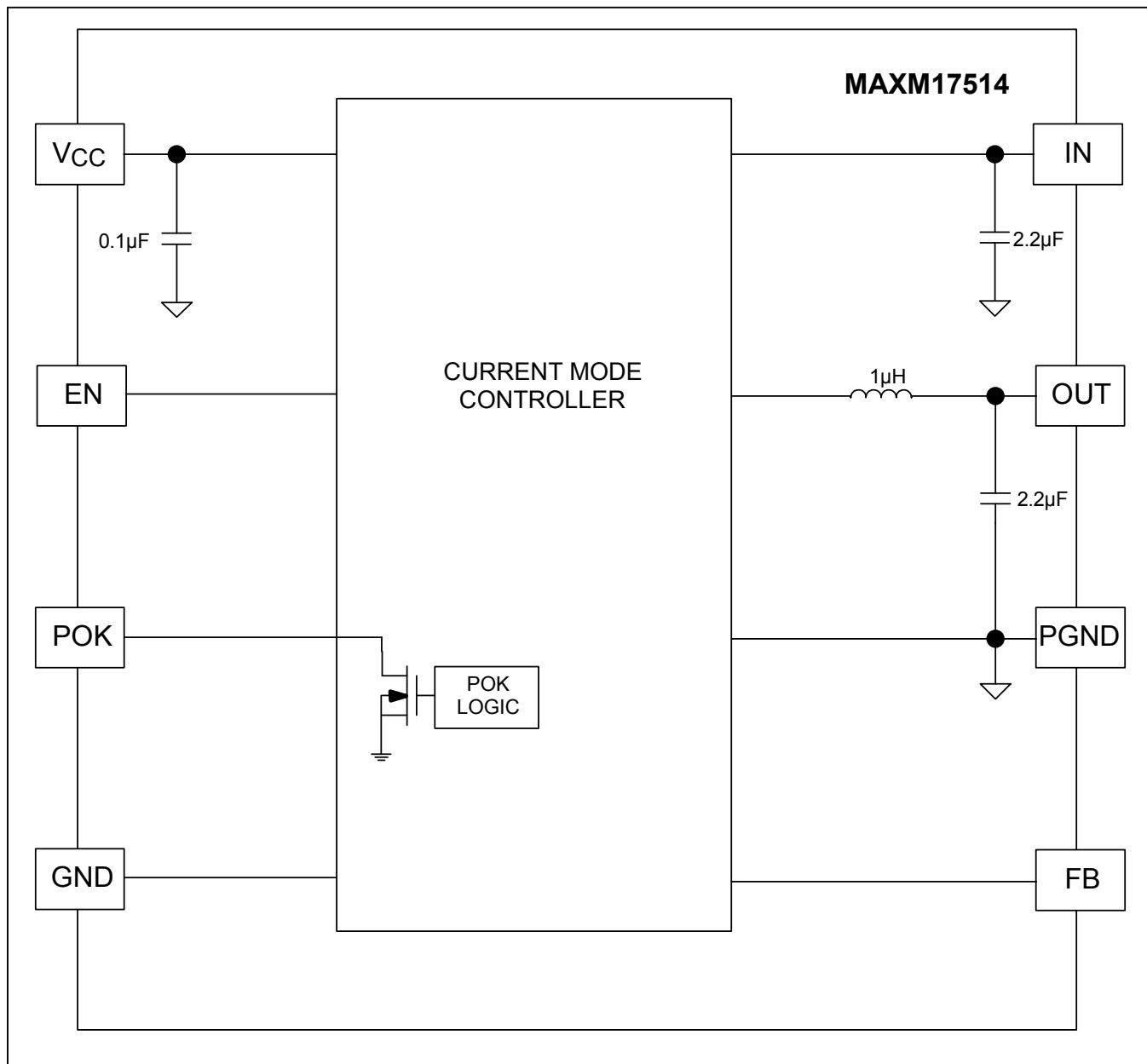

### Typical Application Circuit

### Benefits and Features

- Reduces Design Complexity, Manufacturing Risks, and Time-to-Market

- Complete Integrated Step-Down Power Supply in a Single Package

- Passes EN55022 (CISPR22) Class-B Radiated and Conducted EMI Standard

- Saves Board Space in Space-Constrained Applications

- Small Form Factor 6.5mm x 10mm x 2.8mm SiP Package

- Simplified PCB Design with as Few as Four External Components

- Offers Flexibility for Power-Design Optimization

- 2.4V to 5.5V Input Voltage Range

- 0.75V to 3.6V Programmable Output Voltage

- 4A Output Current

- Fixed 1MHz Switching Frequency

- Enable Input

- Power-Good Output

- Reduces Power Dissipation

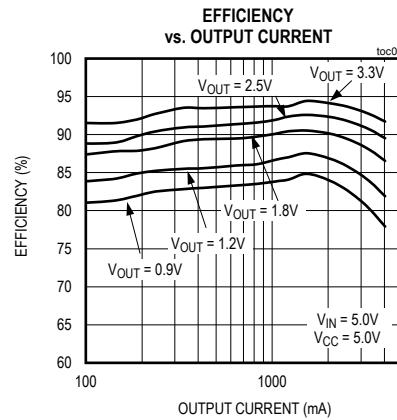

- Up to 94% Efficiency

- Autoswitch, Light-Load, Pulse-Skipping Mode

- High Impedance Shutdown

- < 1μA Shutdown Current

- Operates Reliably and Reduces System Downtime

- Voltage-Controlled Internal Soft-Start

- Fault Protection

- Output Undervoltage/Overvoltage Protection

- Thermal-Fault Protection

- Peak Current Limit

- -40°C to +125°C Operation

**Absolute Maximum Ratings**

|                        |                                   |                                                       |                                     |

|------------------------|-----------------------------------|-------------------------------------------------------|-------------------------------------|

| IN to PGND             | -0.3V to +6V                      | EP2 to PGND                                           | -0.3V to + (V <sub>IN</sub> + 0.3V) |

| V <sub>CC</sub> to GND | -0.3V to +6V                      | EP2 to GND                                            | -0.6V to + (V <sub>IN</sub> + 0.3V) |

| V <sub>CC</sub> to IN  | -0.3V to +6V                      | Continuous Power Dissipation (T <sub>A</sub> = +70°C) |                                     |

| EN to GND              | -0.3V to +6V                      | 28-Pin SIP (derate 37mW/°C above +70°C)               | 2000mW                              |

| FB, POK to GND         | -0.3V to (V <sub>CC</sub> + 0.3V) | Operating Temperature Range                           | -40°C to +125°C                     |

| OUT, EP3 to GND        | -0.6V to (V <sub>IN</sub> + 0.3V) | Junction Temperature                                  | +125°C                              |

| PGND to GND            | -0.3V to +0.3V                    | Storage Temperature Range                             | -55°C to +150°C                     |

| EP1 to GND             | -0.3V to +0.3V                    | Lead Temperature (soldering, 10s)                     | +245°C                              |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Package Thermal Characteristics (Note 1)**

SiP

|                                                           |        |

|-----------------------------------------------------------|--------|

| Junction-to-Ambient Thermal Resistance (θ <sub>JA</sub> ) | 25°C/W |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> )    | 6°C/W  |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to [www.maximintegrated.com/thermal-tutorial](http://www.maximintegrated.com/thermal-tutorial).

**Electrical Characteristics**

(V<sub>IN</sub> = V<sub>CC</sub> = V<sub>EN</sub> = 5V, T<sub>A</sub> = T<sub>J</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted. See *Typical Application Circuit* (Note 2)

| PARAMETER                                       | SYMBOL               | CONDITIONS                                                                                                           | MIN   | TYP    | MAX   | UNITS |

|-------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------|-------|--------|-------|-------|

| <b>INPUT SUPPLY (V<sub>IN</sub>)</b>            |                      |                                                                                                                      |       |        |       |       |

| IN Input Voltage Range                          | V <sub>IN</sub>      |                                                                                                                      | 2.4   | 5.5    |       | V     |

|                                                 |                      | V <sub>IN</sub> = V <sub>CC</sub>                                                                                    | 4.5   | 5.5    |       |       |

| IN Undervoltage Threshold                       |                      | Rising edge (100mV hysteresis)                                                                                       | 2.05  | 2.19   | 2.4   | V     |

| IN Standby Supply Current                       | I <sub>Q</sub>       | V <sub>IN</sub> = V <sub>CC</sub> = 4.5V, no load                                                                    | 1     | 5.5    |       | µA    |

| <b>V<sub>CC</sub> SUPPLY</b>                    |                      |                                                                                                                      |       |        |       |       |

| V <sub>CC</sub> Input Voltage Range             | V <sub>CC</sub>      |                                                                                                                      | 4.5   | 5.5    |       | V     |

| V <sub>CC</sub> Undervoltage Threshold          |                      | Rising edge (160mV hysteresis)                                                                                       | 3.9   | 4.2    | 4.5   | V     |

| V <sub>CC</sub> Shutdown Supply Current         | I <sub>VCC_SHD</sub> | EN = GND, POK unconnected, measured at V <sub>CC</sub> , T <sub>A</sub> = +25°C                                      | 0.1   | 1.0    |       | µA    |

| V <sub>CC</sub> Supply Current                  | I <sub>VCC</sub>     | Regulator enabled, no load, no switching (V <sub>FB</sub> = 1V)                                                      | 62    | 135    |       | µA    |

| <b>OUTPUT</b>                                   |                      |                                                                                                                      |       |        |       |       |

| Output Voltage Programmable Range               | V <sub>OUT</sub>     | V <sub>IN</sub> = V <sub>CC</sub> = 5.2V, I <sub>LOAD</sub> = 2A<br>(see derating curve for V <sub>OUT</sub> ≥ 2.5V) | 0.754 | 3.6    |       | V     |

| Unity Gain Output-Voltage Tolerance/FB accuracy |                      | FB = OUT, no load                                                                                                    | 0.757 | 0.770  | 0.783 | V     |

| FB Load Regulation Accuracy (RDROOP)            |                      | 2A < I <sub>OUT</sub> < 4A, FB = OUT                                                                                 | -7.5  | -4.4   | -1    | mV/A  |

| FB Line Regulation Accuracy                     |                      | FB = OUT, no load, 2.4V < V <sub>IN</sub> < 5.5V                                                                     | 1.253 | 4.5    |       | mV/V  |

| FB Input Bias Current                           |                      | T <sub>A</sub> = -40°C to +125°C (Note 3)                                                                            | -0.1  | -0.015 | +0.1  | µA    |

**Electrical Characteristics (continued)**

( $V_{IN} = V_{CC} = V_{EN} = 5V$ ,  $T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted. See *Typical Application Circuit*.) (Note 2)

| PARAMETER                                                | SYMBOL     | CONDITIONS                                         | MIN | TYP  | MAX | UNITS |

|----------------------------------------------------------|------------|----------------------------------------------------|-----|------|-----|-------|

| Average Output Current Limit                             |            | $V_{IN} = 5V$                                      | 4   | 8    |     | A     |

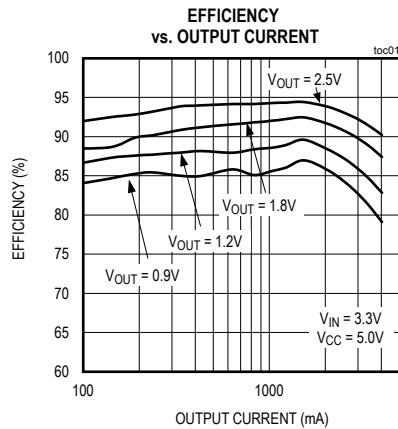

| <b>EFFICIENCY</b>                                        |            |                                                    |     |      |     |       |

| Efficiency                                               |            | $V_{IN} = 5V, V_{OUT} = 1.1V, I_{OUT} = 2A$        |     | 86   |     | %     |

|                                                          |            | $V_{IN} = 5V, V_{OUT} = 1.1V, I_{OUT} = 4A$        |     | 80   |     |       |

| <b>SWITCHING FREQUENCY</b>                               |            |                                                    |     |      |     |       |

| Switching Frequency                                      | $f_{SW}$   |                                                    | 0.9 | 1    | 1.1 | MHz   |

| <b>SOFT-START</b>                                        |            |                                                    |     |      |     |       |

| Soft-Start Ramp Time                                     | $t_{SS}$   |                                                    |     | 1.79 |     | ms    |

| Soft-Start Fault Blanking Time                           | $t_{SSLT}$ |                                                    |     | 3    |     | ms    |

| <b>POWER-GOOD OUTPUT (POK)</b>                           |            |                                                    |     |      |     |       |

| POK Upper Trip Threshold and Overvoltage-Fault Threshold |            | Rising edge, 50mV hysteresis                       | 830 | 850  | 870 | mV    |

| POK Lower Trip Threshold                                 |            | Falling edge, 50mV hysteresis                      | 658 | 690  | 725 | mV    |

| POK Leakage Current                                      | $I_{POK}$  | $T_A = +25^{\circ}C, V_{POK} = 5.5V$               |     | 0.1  | 1   | µA    |

| POK Propagation Delay Time                               | $t_{POK}$  | FB forced 50mV beyond POK trip threshold           |     | 2    |     | µs    |

| POK Output Low Voltage                                   |            | $I_{SINK} = 3mA$                                   |     |      | 100 | mV    |

| Overvoltage-Fault Latch-Delay Time                       |            | FB forced 50mV above POK upper-trip threshold      |     | 2    |     | µs    |

| Undervoltage-Fault Latch-Delay Time                      |            | FB forced 50mV below POK lower-trip threshold, TUV |     | 1.6  |     | ms    |

| <b>LOGIC INPUTS</b>                                      |            |                                                    |     |      |     |       |

| EN Input High Threshold                                  |            | Rising, hysteresis = 215mV (typ)                   | 1.0 | 1.4  | 1.6 | V     |

| EN Input Leakage Current                                 |            | $T_A = +25^{\circ}C$                               |     | 0.1  | 1   | µA    |

| <b>THERMAL SHUTDOWN</b>                                  |            |                                                    |     |      |     |       |

| Thermal-Shutdown Threshold                               | $T_{SHDN}$ | Hysteresis = 15°C                                  |     | +160 |     | °C    |

**Note 2:** Limits are 100% tested at  $T_A = +25^{\circ}C$ . Maximum and minimum limits are guaranteed by design and characterization over temperature.

**Note 3:** Design guaranteed by ATE characterization. Limits are not production tested.

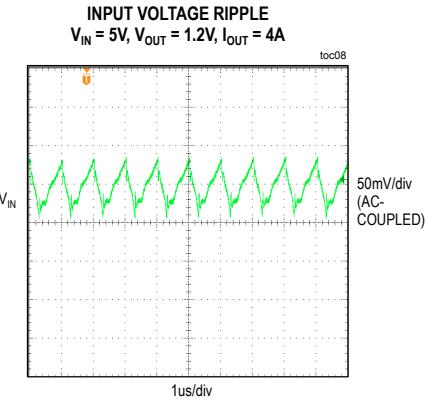

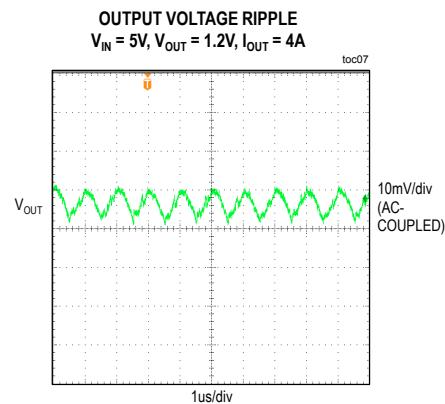

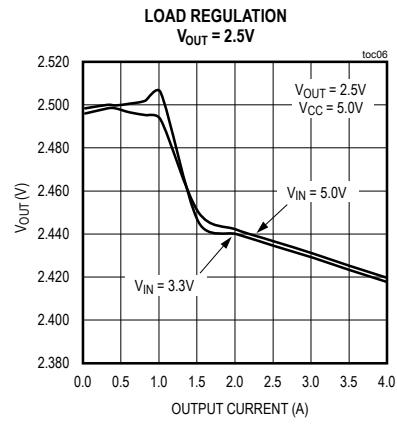

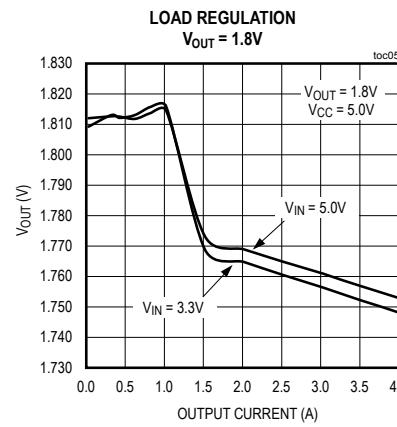

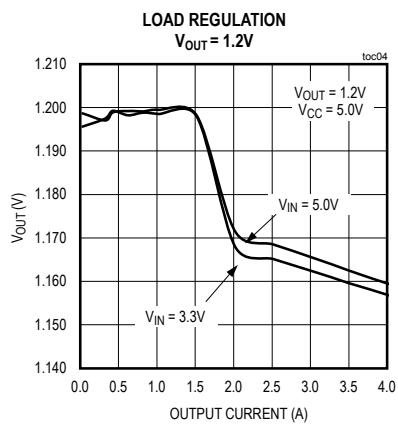

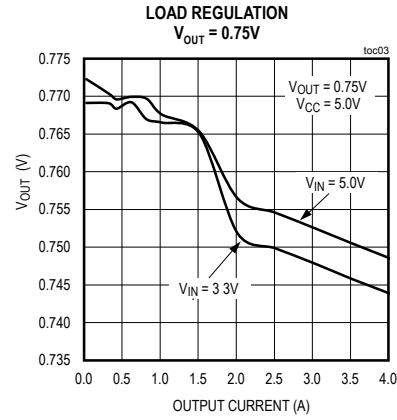

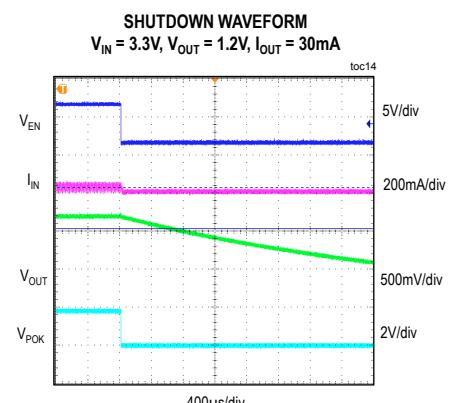

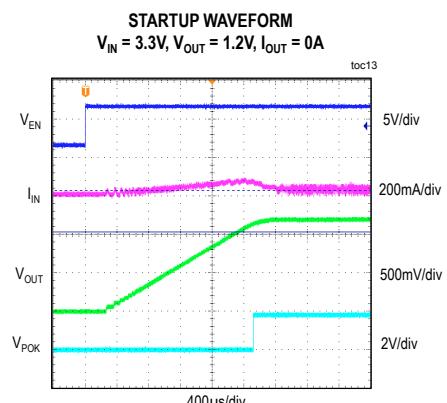

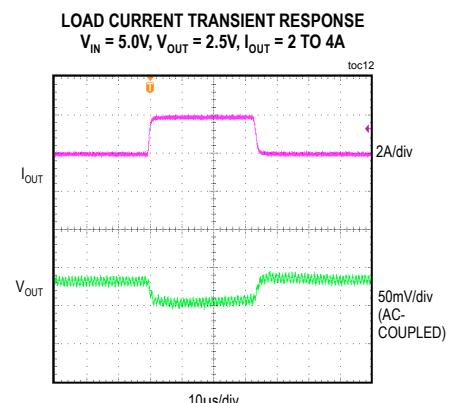

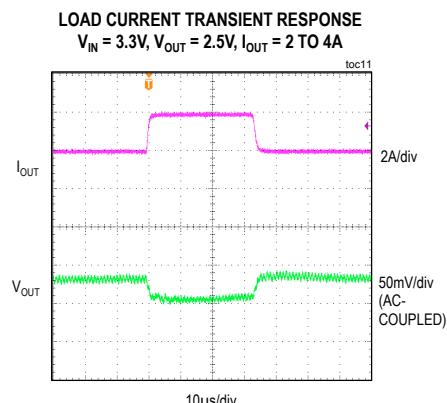

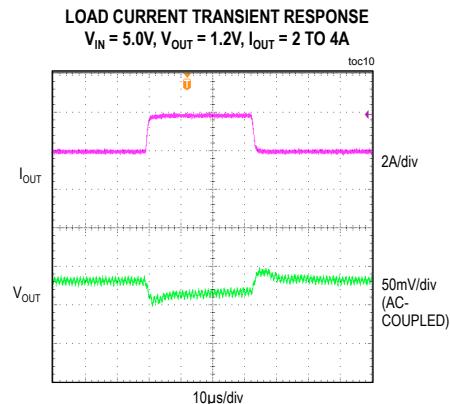

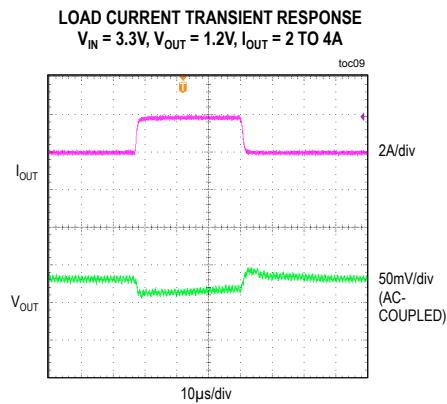

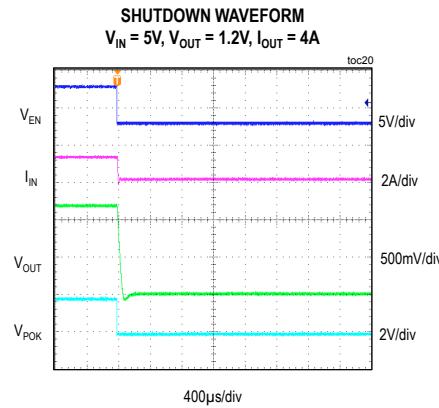

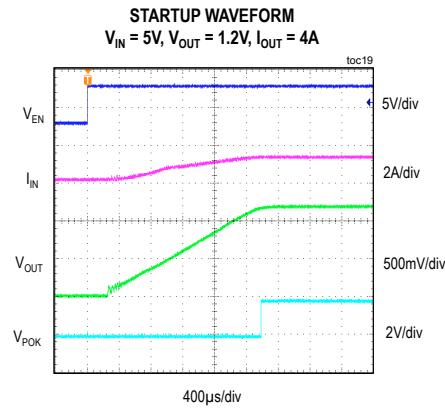

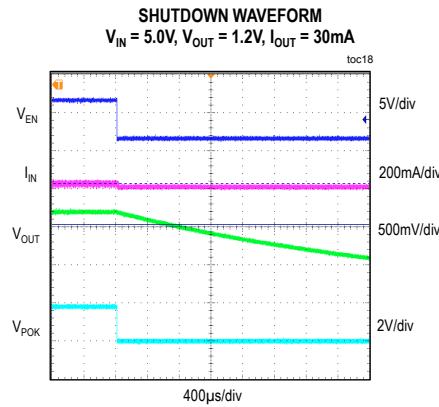

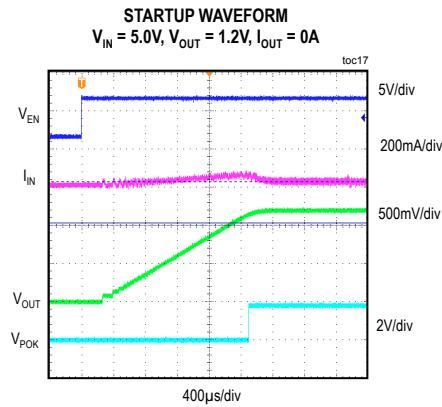

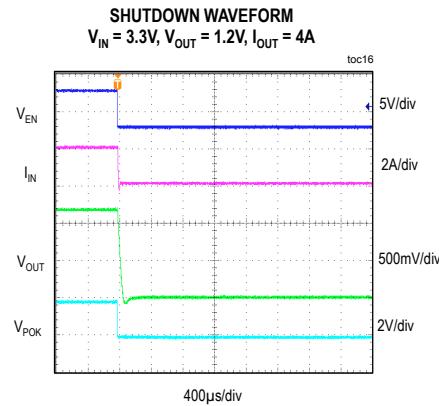

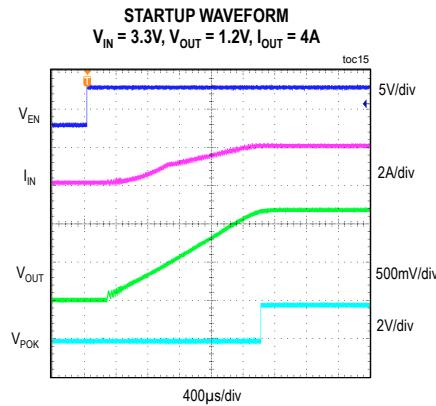

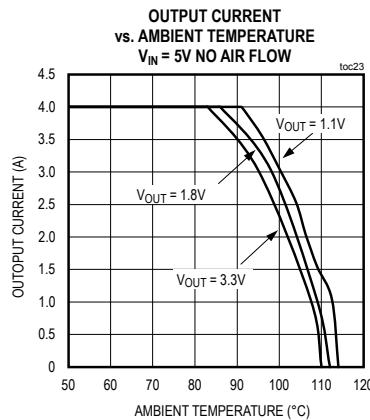

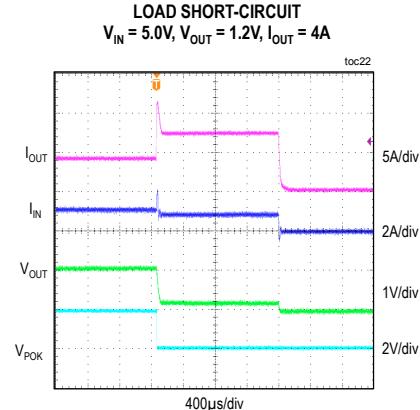

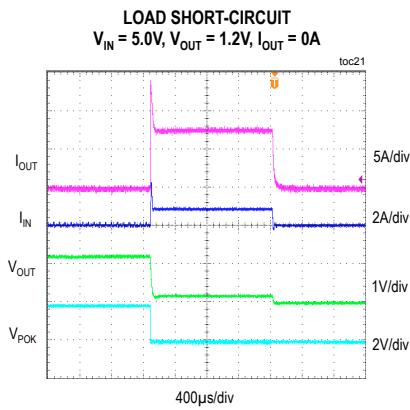

## Typical Operating Characteristics

(V<sub>CC</sub> = 5V, V<sub>IN</sub> = 3.3V - 5V, V<sub>OUT</sub> = 0.9V - 3.3V, I<sub>OUT</sub> = 0-4A, T<sub>A</sub> = +25°C, unless otherwise noted.)

## Typical Operating Characteristics (continued)

(V<sub>CC</sub> = 5V, V<sub>IN</sub> = 3.3V - 5V, V<sub>OUT</sub> = 0.9V - 3.3V, I<sub>OUT</sub> = 0-4A, T<sub>A</sub> = +25°C, unless otherwise noted.)

## Typical Operating Characteristics (continued)

(V<sub>CC</sub> = 5V, V<sub>IN</sub> = 3.3V - 5V, V<sub>OUT</sub> = 0.9V - 3.3V, I<sub>OUT</sub> = 0-4A, T<sub>A</sub> = +25°C, unless otherwise noted.)

**Typical Operating Characteristics (continued)** $(V_{CC} = 5V, V_{IN} = 3.3V - 5V, V_{OUT} = 0.9V - 3.3V, I_{OUT} = 0-4A, T_A = +25^{\circ}C$ , unless otherwise noted.)

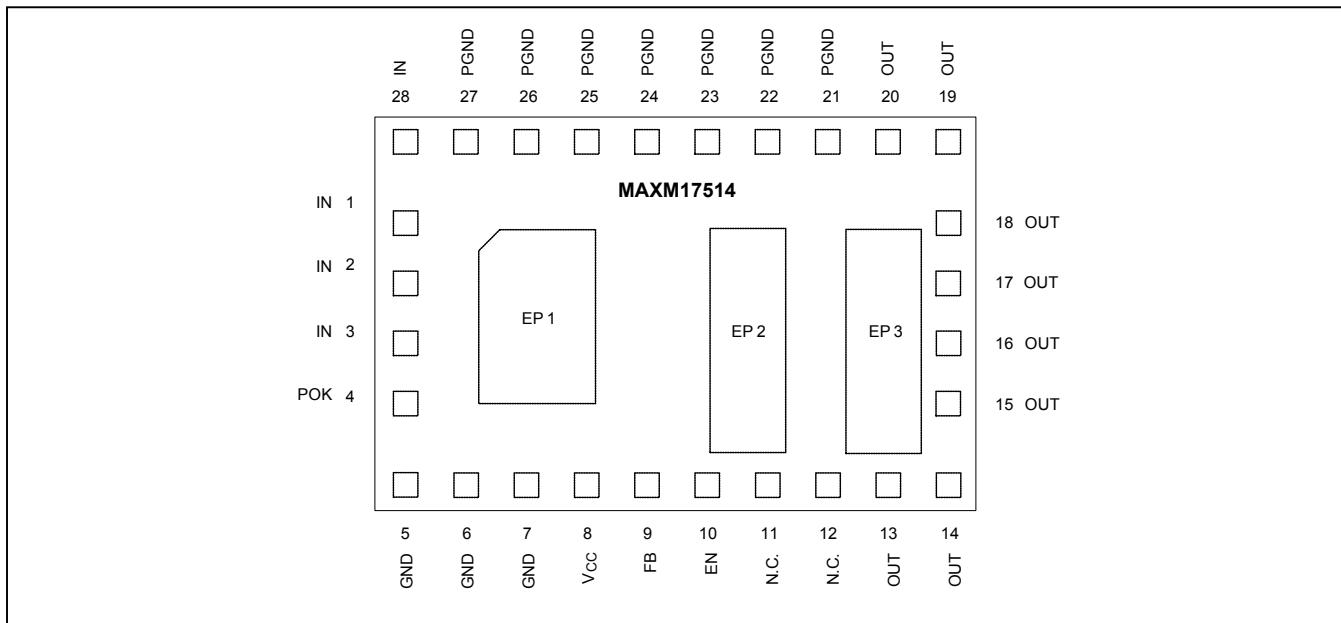

## Pin Configuration

## Pin Description

| PIN        | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                             |

|------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1–3,<br>28 | IN              | Input Supply Connection. Bypass to GND with a 22 $\mu$ F or 2 x 10 $\mu$ F ceramic capacitor. Supply range for this pin is 4.5V to 5.5V. When V <sub>CC</sub> can be supplied separately from a 4.5V to 5.5V source, the IN pin can then be powered from a 2.4V to 5.5V supply.                                                      |

| 4          | POK             | Open-Drain Power-Good Output. POK is pulled low if FB is more than 12% (typ) above or below the nominal regulation threshold. POK is held low in shutdown. POK becomes high impedance when FB is in regulation range. Pull this pin up with 10k $\Omega$ (typ) resistor value.                                                       |

| 5–7        | GND             | GND. Connect PGND and GND together at a single point.                                                                                                                                                                                                                                                                                |

| 8          | V <sub>CC</sub> | 5V Bias Supply Input for the Internal Switching Regulator Drivers. For IN from 4.5V to 5.5V, V <sub>CC</sub> can be connected to the IN supply. For IN supply voltages lower than the above range, V <sub>CC</sub> should be powered from a separate 5V $\pm$ 10% supply and bypassed with a 1 $\mu$ F or greater ceramic capacitor. |

| 9          | FB              | Feedback Input for the Internal Step-Down Converter. Connect FB to a resistive divider between OUT and GND to adjust the typical output voltage between 0.765V to 3.6V. Keep equivalent divider resistance lower than 50k $\Omega$ .                                                                                                 |

| 10         | EN              | Regulator Enable Input. When EN is pulled low, the regulator is disabled. When EN is driven high, the regulator is enabled.                                                                                                                                                                                                          |

| 11, 12     | N.C.            | No Connection                                                                                                                                                                                                                                                                                                                        |

| 13–20      | OUT             | Regulator Output Pins. Connect an output capacitor between OUT and PGND with a 220 $\mu$ F (typ) POSCAP low-ESR capacitor.                                                                                                                                                                                                           |

| 21–27      | PGND            | Power GND Return. Connect to GND.                                                                                                                                                                                                                                                                                                    |

| —          | EP1             | Exposed Pad 1. Connect this pad to the PGND ground plane of 1in by 1in copper for cooling.                                                                                                                                                                                                                                           |

| —          | EP2             | Exposed Pad 2. Connect this pad to the PCB for better thermal performance, but do not connect to any other node. Minimize area of copper island.                                                                                                                                                                                     |

| —          | EP3             | Exposed Pad 3. Connect this pad to the OUT pins and the copper area of 1in by 1in.                                                                                                                                                                                                                                                   |

## Functional Diagram

## Design Procedure

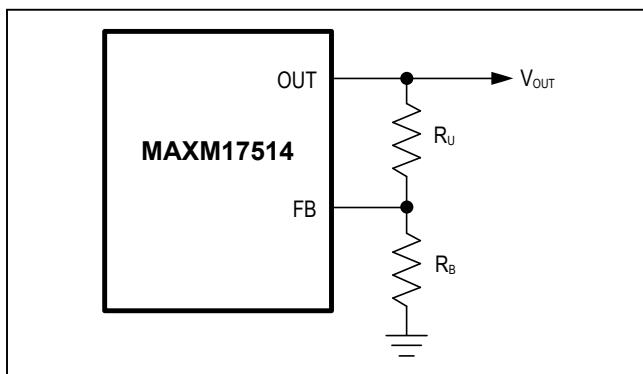

### Adjusting Output Voltage

The MAXM17514 produces an adjustable 0.75V to 3.6V output voltage from a 2.4V to 5.5V input voltage range by using a resistive feedback divider from OUT to FB. The device can deliver up to 4A output current up to an output voltage of 2.5V at +70°C. The output current derates for output voltages above 2.5V.

Adjusting the output voltage of the device requires a resistive divider network from OUT to FB, according to the equation below. From the initial output voltage, the load-line regulation reduces the effective feedback voltage by a typical 5mV/A as the output current increases.

$$R_U = R_B \times \left[ \frac{V_{OUT}}{0.765} - 1 \right] \text{ k}\Omega, \text{ where } R_B \text{ is in k}\Omega.$$

### Input Voltage Range

The maximum value ( $V_{IN(MAX)}$ ) and minimum value ( $V_{IN(MIN)}$ ) must accommodate the worst-case conditions accounting for the input voltage soars and drops. If there is a choice at all, lower input voltages result in better efficiency. With a maximum duty cycle of 87.5%,  $V_{OUT}$  is limited to  $0.875 \times V_{IN}$ .

### Input Capacitor Selection

The input capacitor must meet the ripple-current requirement ( $I_{RMS}$ ) imposed by the switching currents. The  $I_{RMS}$  requirements of the regulator can be determined by the following equation:

$$I_{RMS} = I_{OUT} \times \sqrt{D \times (1 - D)}$$

The worst-case RMS current requirement occurs when operating with  $D = 0.5$ . At this point, the above equation simplifies to  $I_{RMS} = 0.5 \times I_{OUT}$ .

Figure 1. Adjusting Output Voltage

The minimum input capacitor required can be calculated by the following equation:

$$C_{IN} = \frac{(I_{IN\_AVG}) \times (1 - D)}{(\Delta V_{IN}) \times f_{SW}}$$

where:

$I_{IN\_AVG}$  is the average input current given by:

$$I_{IN\_AVG} = \frac{V_{OUT}}{\eta \times f_{SW}}$$

$D$  is the operating duty cycle, which is approximately equal to  $V_{OUT}/V_{IN}$  where:

$\Delta V_{IN}$  is the required input-voltage ripple,

$f_{SW}$  is the operating switching frequency,

$P_{OUT}$  is the output power, which is equal to  $V_{OUT} \times I_{OUT}$ ,

$\eta$  is the efficiency.

For the device's system (IN) supply, ceramic capacitors are preferred due to their resilience to inrush surge currents typical of systems, and due to their low parasitic inductance, which helps reduce the high-frequency ringing on the IN supply when the internal MOSFETs are turned off. Choose an input capacitor that exhibits less than +10°C temperature rise at the RMS input current for optimal circuit longevity.

### Output Capacitor Selection

The output capacitor selection requires careful evaluation of several different design requirements (e.g., stability, transient response, and output ripple voltage) that place limits on the output capacitance and the effective series resistance (ESR). Based on these requirements, a combination of low-ESR polymer capacitors (lower cost but higher output ripple voltage) and ceramic capacitors (higher cost but low output ripple voltage) should be used to achieve stability with low output ripple.

### Loop Compensation

The gain portion of the loop gain is a result of error-amplifier gain, current-sensing gain, and load with an overall typical value at 1kHz of 36dB at  $V_{IN} = 5V$ , and 46dB at  $V_{IN} = 3V$ , with a typical limit to the gain-bandwidth (GBW) product of 120,000. The crossover should occur before this error-amplifier bandwidth limit of 120kHz (gain = 1). The output capacitor and load introduces a pole with the worst case at the maximum load (4A). If the load pole location is further than a frequency where the gain exceeds the GBW, the gain drop starts earlier at

the location where the loop gain is limited. This situation applies typically to an output voltage less than 1.8V, so zero frequency from the ESR is needed to increase the phase margin at the crossover frequency.

The recommended relationship between ESR and total output capacitance values are shown in [Table 1](#). When a low-ESR type capacitor is used with a ceramic capacitor, a recommended value of 44 $\mu$ F to 100 $\mu$ F ceramic capacitor should be used to make up the total capacitance value with the relationship between ESR and total output capacitance value, such that the zero frequency is between 32kHz and 40kHz. When only a low-ESR type capacitor is used, the zero frequency should be between 62kHz and 80kHz. Optionally, a small 10 $\mu$ F–22 $\mu$ F ceramic capacitor can be used to reduce output ripple.

Optionally, for an output greater than or equal to 1.8V, an all-ceramic capacitor solution can be used with a minimum capacitance value that locates the pole location below 1kHz with resistive load (4A), and with a simplified equation given by  $C_{OUTMIN}$  ( $\mu$ F) = 900/V<sub>OUT</sub>.

### Output Ripple Voltage

With polymer capacitors, the ESR dominates and determines the output ripple voltage. The step-down regulator's output ripple voltage (V<sub>RIPPLE</sub>) equals the total inductor ripple current ( $\Delta I_L$ ) multiplied by the output capacitor's ESR. Therefore, the maximum ESR to meet the output ripple-voltage requirement is:

$$R_{ESR} \leq \frac{V_{RIPPLE}}{\Delta I_L}$$

where:

$$\Delta I_L = \left( \frac{V_{IN} - V_{OUT}}{L} \right) \times \left( \frac{V_{OUT}}{V_{IN}} \right) \times f_{SW}$$

where f<sub>SW</sub> is the switching frequency and L is the inductor (1 $\mu$ H).

**Table 1. Output Capacitor Selection vs. ESR**

| TOTAL C <sub>OUT</sub> ( $\mu$ F) | LOW-ESR TYPE WITH CERAMIC-TYPE<br>ESR (m $\Omega$ ) | LOW-ESR TYPE WITHOUT CERAMIC-TYPE<br>ESR (m $\Omega$ ) |

|-----------------------------------|-----------------------------------------------------|--------------------------------------------------------|

| 250                               | 16–20                                               | 8–10                                                   |

| 300                               | 13–17                                               | 7–9                                                    |

| 350                               | 11–14                                               | 6, 7                                                   |

| 400                               | 10–12                                               | 5, 6                                                   |

| 450                               | 9–11                                                | 4–6                                                    |

| 500                               | 8–10                                                | 4, 5                                                   |

| 550                               | 7–9                                                 | 4, 5                                                   |

| 600                               | 7, 8                                                | 3, 4                                                   |

The actual capacitance value required relates to the physical case size needed to achieve the ESR requirement, as well as to the capacitor chemistry. Thus, polymer capacitor selection is usually limited by ESR and voltage rating rather than by capacitance value.

With ceramic capacitors, the ripple voltage due to capacitance dominates the output ripple voltage. Therefore, the minimum capacitance needed with ceramic output capacitors is:

$$C_{OUT} = \left( \frac{\Delta I_L}{8 \times f_{SW}} \right) \times \frac{1}{V_{RIPPLE}}$$

Alternatively, combining ceramics (for the low ESR) and polymers (for the bulk capacitance) helps balance the output capacitance vs. output ripple-voltage requirements.

### Load-Transient Response

The load-transient response depends on the overall output impedance over frequency, and the overall amplitude and slew rate of the load step. In applications with large, fast-load transients (load step > 80% of full load and slew rate > 10A/ $\mu$ s), the output capacitor's high-frequency response (ESL and ESR) needs to be considered. To prevent the output voltage from spiking too low under a load-transient event, the ESR is limited by the following equation (ignoring the sag due to finite capacitance):

$$R_{ESR} \leq \frac{V_{RIPPLESTEP}}{\Delta I_{OUTSTEP}}$$

where V<sub>RIPPLESTEP</sub> is the allowed voltage drop during load current transient, and I<sub>OUTSTEP</sub> is the maximum load current step.

The capacitance value dominates the mid-frequency output impedance and continues to dominate the load-transient response as long as the load transient's slew rate is fewer than two switching cycles. Under these

conditions, the sag and soar voltages depend on the output capacitance, inductance value, and delays in the transient response. Low inductor values allow the inductor current to slew faster, replenishing charge removed from or added to the output filter capacitors by a sudden load step, especially with low differential voltages across the inductor. The minimum capacitance needed to handle the sag voltage ( $V_{SAG}$ ) that occurs after applying the load current can be estimated by the following equation:

$$C_{OUT\_SAG} = \frac{1}{V_{SAG}} \times \left[ \frac{1}{2} \left( \frac{L \times \Delta I_{OUT\_STEP}^2}{(V_{IN} \times D_{MAX}) - V_{OUT}} \right) + (\Delta I_{OUT\_STEP} \times (t_{sw} - \Delta T)) \right]$$

where:

- $D_{MAX}$  is the maximum duty factor (87.5%),

- $t_{sw}$  is the switching period ( $1/f_{sw}$ ),

- $\Delta T$  equals  $V_{OUT}/V_{IN} \times t_{sw}$  when in PWM mode, or  $L \times I_{IDLE}/(V_{IN} - V_{OUT})$  when in Idle Mode (1.5A).

The minimum capacitance needed to handle the overshoot voltage ( $V_{SOAR}$ ) that occurs after load removal (due to stored inductor energy) can be calculated as:

$$C_{OUT\_SOAR} \approx \frac{(\Delta I_{OUT\_STEP})^2 L}{2 V_{OUT} V_{SOAR}}$$

When the device is operating under low duty cycle, the output capacitor size is usually determined by the  $C_{OUT\_SOAR}$ .

## Detailed Description

The MAXM17514 is a complete step-down switch-mode power-supply solution that can deliver up to 4A output current and up to 3.6V output voltage from a 2.4V to 5.5V input voltage range. The device includes switch-mode power-supply controller, dual n-channel MOSFET power switches, and an inductor. The device uses a fixed-frequency current-mode control scheme.

The device provides peak current-limit protection, output undervoltage protection, output overvoltage protection, and thermal protection. The device operates in skip mode at light loads to improve the light-load efficiency. Independent enable and an open-drain power-good output allow flexible system power sequencing. The fixed voltage soft-start reduces the inrush current by gradually ramping up the internal reference voltage.

*Idle Mode* is a trademark of Maxim Integrated Products, Inc

## Fixed-Frequency Current-Mode Controller

The heart of the current-mode PWM controller is a multistage, open-loop comparator that compares the output voltage-error signal with respect to the reference voltage, the current-sense signal, and the slope-compensation ramp (see the [Functional Diagram](#)). The device uses a direct summing configuration, approaching ideal cycle-to-cycle control over the output voltage without a traditional error amplifier and the phase shift associated with it.

## Light-Load Operation

The device features an inherent automatic switchover to pulse skipping (PFM operation) at light loads. This switchover is affected by a comparator that truncates the low-side switch on-time at the inductor current's zero crossing. The zero-crossing comparator senses the inductor current during the off-time. Once the current through the low-side MOSFET drops below the zero-crossing trip level, it turns off the low-side MOSFET. This prevents the inductor from discharging the output capacitors and forces the switching regulator to skip pulses under light-load conditions to avoid overcharging the output. Therefore, the controller regulates the valley of the output ripple under light-load conditions. The switching waveforms can appear noisy and asynchronous at light-load pulse-skipping operation, but this is a normal operating condition that results in high light-load efficiency.

## Idle Mode™ Current-Sense Threshold

In Idle Mode, the on-time of the step-down controller terminates when both the output voltage exceeds the feedback threshold, and the internal current-sense voltage falls below the Idle Mode current-sense threshold ( $I_{IDLE} = 1.5A$ ). Another on-time cannot be initiated until the output voltage drops below the feedback threshold. In this mode, the behavior appears like PWM operation with occasional pulse skipping, where inductor current does not need to reach the light-load level.

## Power-On Reset (POR) and UVLO

Power-on reset (POR) occurs when  $V_{CC}$  rises above approximately 2.1V, resetting the undervoltage, overvoltage, and thermal-shutdown fault latches. The  $V_{CC}$  input undervoltage-lockout (UVLO) circuitry prevents the switching regulators from operating if the 5V bias supply ( $V_{CC}$ ) is below its 4V UVLO threshold.

## Soft-Start

The internal step-down controller starts switching and the output voltage ramps up using soft-start. If the  $V_{CC}$  bias supply voltage drops below the UVLO threshold, the controller stops switching and disables the drivers (LX becomes high impedance) until the bias supply voltage recovers.

Once the 5V  $V_{CC}$  bias supply and  $V_{IN}$  rise above their respective input UVLO thresholds, and EN is pulled high, the internal step-down controller becomes enabled and begins switching. The internal voltage soft-starts gradually increment the feedback voltage by approximately 25mV every 61 switching cycles, making the output voltage reach its nominal regulation voltage 1.79ms after the regulator is enabled (see the Soft-Start Waveforms in the [Typical Operating Characteristics](#) section).

## Power-Good Output (POK)

POK is the open-drain output of the window comparator that continuously monitors the output for undervoltage and overvoltage conditions. POK is actively held low in shutdown (EN = GND). POK becomes high impedance after the device is enabled and the output remains within  $\pm 10\%$  of the nominal regulation voltage set by FB. POK goes low once the output drops 12% (typ) below or rises 12% (typ) above its nominal regulation point, or the output shuts down. For a logic-level POK output voltage, connect an external pullup resistor between POK and  $V_{CC}$ . A 10k $\Omega$  pullup resistor works well in most applications.

## Output Overvoltage Protection (OVP)

If the output voltage rises to 112% (typ) of its nominal regulation voltage, the controller sets the fault latch, pulls POK low, shuts down the regulator, and immediately pulls the output to ground through its low-side MOSFET. Turning on the low-side MOSFET with 100% duty cycle rapidly discharges the output capacitors and clamps the output to ground. However, this commonly undamped response causes negative output voltages due to the energy stored in the output LC at the instant of 0V fault. If the load cannot tolerate a negative voltage, place a power Schottky diode across the output to act as a reverse-polarity clamp. If the condition that caused the overvoltage persists (such as a shorted high-side MOSFET), the input source also fails (short-circuit fault). Cycle  $V_{CC}$

below 1V or toggle the enable input to clear the fault latch and restart the regulator.

## Output Undervoltage Protection (UVP)

The device includes an output undervoltage-protection (UVP) circuit that begins to monitor the output once the startup blanking period has ended. If the output voltage drops below 88% (typ) of its nominal regulation voltage, the regulator pulls the POK output low and begins the UVP fault timer. Once the timer expires after 1.6ms, the regulator shuts down, forcing the high-side MOSFET off and disabling the low-side MOSFET once the zero-crossing threshold has been reached. Cycle  $V_{CC}$  below 1V, or toggle the enable input to clear the fault latch and restart the regulator.

## Thermal-Fault Protection

The device features a thermal-fault protection circuit. When the junction temperature rises above +160°C (typ), a thermal sensor activates the fault latch, pulls down the POK output, and shuts down the regulator. Toggle EN to clear the fault latch, and restart the controllers after the junction temperature cools by 15°C (typ).

## Power Dissipation

The device output current needs to be derated if the output voltage is above 2.5V or if the device needs to operate in high ambient temperature. The amount of current derating depends upon the input voltage, output voltage, and ambient temperature. The derating curves given in the [Typical Operating Characteristics](#) section can be used as a guide.

The maximum allowable power losses can be calculated using the following equation:

$$PD_{MAX} = \frac{T_{JMAX} - T_A}{\theta_{JA}}$$

where:

$PD_{MAX}$  is the maximum allowed power losses with maximum allowed junction temperature,

$T_{JMAX}$  is the maximum allowed junction temperature,

$T_A$  is operating ambient temperature,

$\theta_{JA}$  is the junction-to-ambient thermal resistance.

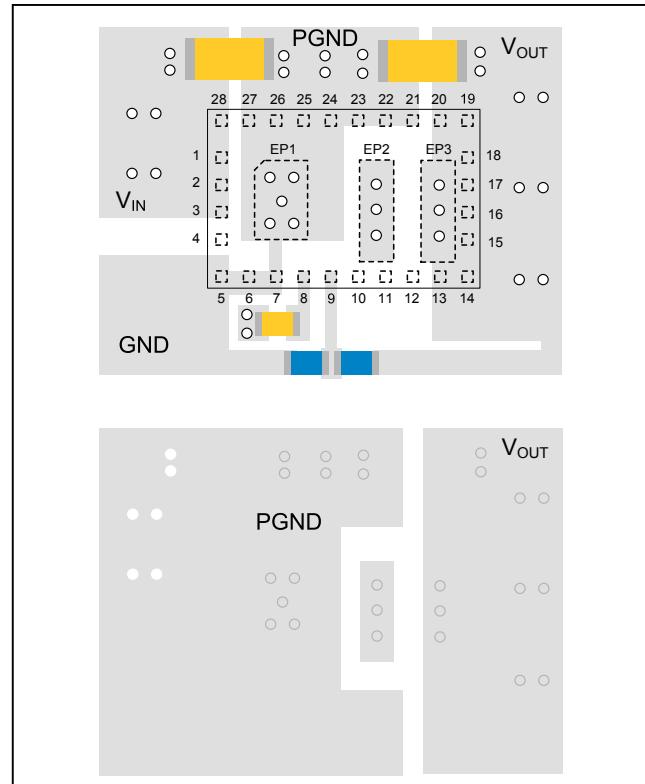

## PCB Layout Guidelines

Careful PCB layout is critical to achieving low switching losses and clean, stable operation. Use the following guidelines for good PCB layout:

- Keep the input capacitors as close as possible to the IN and PGND pins.

- Keep the output capacitors as close as possible to the OUT and PGND pins.

- Connect all the PGND connections to as large a copper plane area as possible on the top layer.

- Connect EP1 to the PGND and GND planes on the top layer.

- Use multiple vias to connect internal PGND planes to the top-layer PGND plane.

- Do not keep any solder mask on EP1–EP3 on bottom layer. Keeping solder mask on exposed pads decreases the heat-dissipating capability.

- Keep the power traces and load connections short. This practice is essential for high efficiency. Using thick copper PCBs (2oz vs. 1oz) can enhance full-load efficiency. Correctly routing PCB traces is a difficult task that must be approached in terms of fractions of centimeters, where a single milliohm of excess trace resistance causes a measurable efficiency penalty.

## Ordering Information

| PART           | TEMP RANGE      | MSL | PIN-PACKAGE |

|----------------|-----------------|-----|-------------|

| MAXM17514ALI+T | -40°C to +125°C | 3   | 28 SiP      |

+Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

## Chip Information

PROCESS: BiCMOS

Figure 2. Layout Recommendation

## Package Information

For the latest package outline information and land patterns (footprints), go to [www.maximintegrated.com/packages](http://www.maximintegrated.com/packages). Note that a “+”, “#”, or “-” in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | OUTLINE NO.             | LAND PATTERN NO.        |

|--------------|--------------|-------------------------|-------------------------|

| 28 SiP       | L286510+1    | <a href="#">21-0701</a> | <a href="#">90-0445</a> |

## Revision History

| REVISION NUMBER | REVISION DATE | DESCRIPTION                                 | PAGES CHANGED |

|-----------------|---------------|---------------------------------------------|---------------|

| 0               | 11/14         | Initial release                             | —             |

| 1               | 4/15          | Tightend FB accuracy and added MSL 3 rating | 2, 14         |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at [www.maximintegrated.com](http://www.maximintegrated.com).

*Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.*

# Mouser Electronics

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated:

[MAXM17514ALI+](#) [MAXM17514ALI+T](#)