## **General Description**

The MAX9959 provides all the key features of a device power supply (DPS) common to automatic test equipment (ATE) and other instrumentation. Its small size, high level of integration, and superb flexibility make the MAX9959 ideal and economical for multisite systems requiring many device power supplies.

The MAX9959 has multiple input control voltages that allow independent setting of both the output voltage, and the maximum and minimum (smallest positive or most negative) voltage or current. The MAX9959 is a voltage source when the load current is between the two programmed limits, and transitions gracefully into a precision current source/sink if a programmed current limit is reached. The output features two independently adjustable voltage clamps that limit both the negative and positive output voltage values between levels externally provided.

The MAX9959 can source voltages spanning 25V and can source currents as high as ±800mA. The DPS can support an external buffer for sourcing and sinking higher currents. Multiple MAX9959s can be configured in parallel to load-share, allowing higher output currents with greater flexibility.

The MAX9959 features operation over a wide range of loading conditions. Programmability allows optimizing of settling time, over-/undershoot, and stability. Built-in, configurable, range-change glitch-control circuits minimize output glitches during range transitions.

The MAX9959 offers load regulation of 1mV at 800mA load.

The MAX9959D features an internal  $300k\Omega$  sense resistor (RFS), between RCOMF and SENSE. The MAX9959F does not include this sense resistor. Both devices are available in the 100-pin TQFP package with an exposed pad on the top for heat removal.

### **Applications**

Memory Testers **VLSI Testers** System-On-a-Chip Testers Industrial Systems Structural Testers

**Features**

- ♦ 25V Span Output Voltage

- **♦ Programmable Current and Voltage Compliance**

- **♦ Programmable Current Ranges**

- ±200µA

- ±2mA

- ±20mA

- ±800mA

- ◆ Load Regulation of 1mV at 800mA

- **♦** External Buffer Support for Higher Currents

- **♦ Parallel Multiple Devices for Higher Currents**

- ♦ Programmable Gain Allows a Wide Range of DACs

- ◆ Device-Under-Test (DUT) Ground Sense

- **♦** Programmable Compensation for Wide Range of Loads

- **♦** Integrated Go/No-Go Comparators

- ◆ IDDQ Test Mode

- ♦ Range-Change Glitch Control

- ◆ Compact (14mm x 14mm) Package

- **♦ 3-Wire Compatible Serial Interface**

- **♦ Thermal Warning Flag and Thermal Shutdown**

## **Ordering Information**

| PART         | TEMP RANGE   | PIN-PACKAGE       |

|--------------|--------------|-------------------|

| MAX9959DCCQ  | 0°C to +70°C | 100 TQFP-EPR-IDP* |

| MAX9959DCCQ+ | 0°C to +70°C | 100 TQFP-EPR-IDP* |

| MAX9959FCCQ+ | 0°C to +70°C | 100 TQFP-EPR-IDP* |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

Pin Configuration appears at end of data sheet.

<sup>\*</sup>EPR = Exposed pad. Inverted die pad.

## **ABSOLUTE MAXIMUM RATINGS**

| VCC to VEE                   | +31V                                       | 100-Pin TQFP-EPR-IDP (derated at 16 | 6.7mW/°C       |

|------------------------------|--------------------------------------------|-------------------------------------|----------------|

| VCC to AGND                  | +20V                                       | above +70°C)                        | 13.33W         |

| VEE to AGND                  | 15V                                        | Junction Temperature                | +150°C         |

| V <sub>L</sub> to DGND       | +6V                                        | Storage Temperature Range           | 65°C to +150°C |

| AGND to DGND                 | 0.5V to +0.5V                              | Lead Temperature (soldering, 10s)   | +300°C         |

| Digital Inputs               | 0.3V to (V <sub>L</sub> + 0.3V)            | Soldering Temperature (reflow)      |                |

|                              | ( $V_{EE} - 0.3V$ ) to ( $V_{CC} + 0.3V$ ) | Lead(Pb)-Free Packages              | +260°C         |

| Continuous Power Dissipation | on $(T_A = +70^{\circ}C)$                  | Packages Containing Lead(Pb)        | +240°C         |

|                              |                                            |                                     |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +12V, V_{EE} = -12V, V_{L} = +3.3V, T_{J} = +30^{\circ}C$  to  $+100^{\circ}C$ . Typical values are at  $T_{J} = +30^{\circ}C$ , unless otherwise specified.) (Notes 1, 2)

| PARAMETER                                 | SYMBOL             | CONDITIONS                                                                                                                       | MIN                   | TYP  | MAX                   | UNITS  |

|-------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|-----------------------|--------|

| VOLTAGE OUTPUT                            |                    |                                                                                                                                  |                       |      |                       | •      |

|                                           |                    | DUT current below 10% of FSR current                                                                                             | V <sub>EE</sub> + 2.5 |      | V <sub>CC</sub> - 2.5 |        |

|                                           |                    | DUT current = +800mA, range A (Note 2)                                                                                           | 0                     |      | +7                    |        |

| Output Voltage Range                      | V <sub>DUT</sub>   | DUT current = -800mA, range A (Note 2)                                                                                           | -7                    |      | 0                     | V      |

|                                           |                    | DUT current at full scale (I <sub>DUT</sub> = 200μA, 2mA, 20mA, or 200mA)                                                        | V <sub>EE</sub> + 5   |      | V <sub>CC</sub> - 5   |        |

| Output Offset                             | Vos                | V <sub>IN</sub> = 0V, I <sub>OUT</sub> = 0A (no load), gain = +1                                                                 |                       |      | ±25                   | mV     |

| Output-Voltage Temperature<br>Coefficient | Vostc              |                                                                                                                                  |                       | ±50  |                       | μV/°C  |

|                                           |                    | Gain = +1                                                                                                                        |                       |      | ±1.25                 |        |

|                                           |                    | Gain = +2                                                                                                                        |                       |      | ±1.25                 | %      |

| Valtaga Cain Franc                        | \/                 | Gain = +6                                                                                                                        |                       |      | ±1.25                 |        |

| Voltage Gain Error                        | VGE                | Gain = -1                                                                                                                        |                       |      | ±1.25                 |        |

|                                           |                    | Gain = -2                                                                                                                        |                       |      | ±1.25                 |        |

|                                           |                    | Gain = -6                                                                                                                        |                       |      | ±1.25                 |        |

| Voltage-Gain Temperature<br>Coefficient   | VGETC              |                                                                                                                                  |                       | ±5   |                       | ppm/°C |

| Linearity Error                           | VLER               | Gain and offset errors calibrated out; I <sub>OUT</sub> = 0 for ranges A, C, and D; ±20mA for range B; gain = +1 (Notes 3, 4, 5) |                       |      | ±0.02                 | %FSR   |

| Off-State Leakage Current                 | HIZF <sub>LK</sub> | RCOMF = (V <sub>CC</sub> - 2.5V) to (V <sub>EE</sub> + 2.5V)                                                                     | -10                   |      | +10                   | nA     |

| Force-to-Sense Resistor                   | R <sub>FS</sub>    | "D" option only                                                                                                                  |                       | 300  |                       | kΩ     |

| DUT GROUND SENSE                          |                    |                                                                                                                                  |                       |      |                       |        |

| Voltage Range                             | ΔVDUTGND           | VDUTGSNS - VAGND                                                                                                                 | ±500                  | ±700 |                       | mV     |

| LOAD REGULATION (Note 6)                  |                    |                                                                                                                                  |                       |      |                       |        |

| Voltage                                   | ΔV <sub>DUT</sub>  | Range A, gain = +1, V <sub>IN</sub> = (V <sub>CC</sub> - 5V) to (V <sub>EE</sub> + 5V), ±800mA current load step (Note 5)        |                       | ±1   | ±7                    | mV     |

## **DC ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +12V, V_{EE} = -12V, V_{L} = +3.3V, T_{J} = +30^{\circ}C \text{ to } +100^{\circ}C.$  Typical values are at  $T_{J} = +30^{\circ}C$ , unless otherwise specified.) (Notes 1, 2)

| PARAMETER                                                    | SYMBOL            | CONDITIONS                                                                                                                                   | MIN  | TYP   | MAX   | UNITS           |  |

|--------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|-----------------|--|

| CURRENT OUTPUT                                               |                   | 1                                                                                                                                            | I.   |       |       | -1              |  |

|                                                              |                   | Range D, $R_D = 5000\Omega$                                                                                                                  |      |       | ±200  | μΑ              |  |

| Outside Outside Design                                       |                   | Range C, $R_C = 500\Omega$                                                                                                                   |      |       | ±2    |                 |  |

| Output Current Range                                         | IDUT              | Range B, $R_B = 50\Omega$                                                                                                                    |      |       | ±20   | mA              |  |

|                                                              |                   | Range A, $R_A = 1.25\Omega$                                                                                                                  |      |       | ±800  |                 |  |

| Input Voltage Range<br>Corresponding to the Full-Scale       | V <sub>INI</sub>  | IOSI = AGND                                                                                                                                  | -4   |       | +4    | V               |  |

| Force Current                                                |                   | VIOSI = VAGND + 4V                                                                                                                           | 0    |       | +8    |                 |  |

| Current-Sense-Amp Offset<br>Voltage Input                    | Viosi             | Relative to AGND                                                                                                                             | -0.2 |       | +4.4  | V               |  |

| Output Current Offset                                        | los               | VRCOMF = 0V (Note 4)                                                                                                                         |      | ±0.1  | ±0.5  | %FSR            |  |

| Force-Current Offset<br>Temperature Coefficient              | IOSTC             |                                                                                                                                              |      | ±20   |       | ppm/°C          |  |

| Gain Error                                                   | IGE               | V <sub>RCOMF</sub> = 0V, I <sub>OUT</sub> = ±FSR                                                                                             |      |       | ±1.0  | %               |  |

| Forced-Current Gain<br>Temperature Coefficient               | IGETC             |                                                                                                                                              |      | ±20   |       | ppm/°C          |  |

| Output Over Current-Limit<br>Range (Note 4)                  |                   | Range D, I <sub>OUT</sub> = ±200µA                                                                                                           | ±135 | ±147  | ±158  | 158<br>158 %FSR |  |

|                                                              | locl              | Range C, I <sub>OUT</sub> = ±2mA                                                                                                             | ±135 | ±147  | ±158  |                 |  |

|                                                              |                   | Range B, I <sub>OUT</sub> = ±20mA                                                                                                            | ±135 | ±147  | ±158  |                 |  |

|                                                              |                   | Range A, I <sub>OUT</sub> = ±800mA                                                                                                           | ±125 | ±138  | ±150  |                 |  |

| Linearity Error                                              | ILER              | Gain, offset, and CMR errors calibrated out; V <sub>IOSI</sub> = -0.2V and +4.4V; ranges B, C, and D (Notes 4, 5, 7)                         |      |       | ±0.02 | %FSR            |  |

| Rejection of Output Error Due to<br>Common-Mode Load Voltage | CMROER            | Range D, I <sub>OUT</sub> = 0, V <sub>RCOMF</sub> = (V <sub>EE</sub> + 2.5V)<br>and (V <sub>CC</sub> - 2.5V), measured across R <sub>D</sub> |      | 0.001 | 0.005 | %FSR/V          |  |

| CURRENT MONITOR                                              |                   |                                                                                                                                              | •    |       |       |                 |  |

|                                                              |                   | Range D                                                                                                                                      |      | ±200  |       | μΑ              |  |

| Magazirad Current Danga                                      | la um             | Range C                                                                                                                                      |      | ±2    |       |                 |  |

| Measured Current Range                                       | IDUTM             | Range B                                                                                                                                      |      | ±20   |       | mA              |  |

|                                                              |                   | Range A                                                                                                                                      |      | ±800  |       |                 |  |

| Current-Sense-Amp Voltage                                    | VISENSE           | IOSI = AGND                                                                                                                                  | -4   |       | +4    | V               |  |

| Range                                                        | VISENSE           | VIOSI = VAGND + 4V                                                                                                                           | 0    |       | +8    | V               |  |

| Current-Sense-Amp Offset<br>Voltage Input                    | V <sub>IOSI</sub> | Relative to AGND                                                                                                                             | -0.2 |       | +4.4  | V               |  |

| Current-Sense-Amp Offset                                     | I <sub>MOS</sub>  | V <sub>RCOMF</sub> = 0V (Note 4)                                                                                                             |      | ±0.1  | ±0.5  | %FSR            |  |

| Measured-Current Offset<br>Temperature Coefficient           | IMOSTC            |                                                                                                                                              |      | ±20   |       | ppm/°C          |  |

| Gain Error                                                   | I <sub>MGE</sub>  | V <sub>RCOMF</sub> = 0V, I <sub>OUT</sub> = ±FSR                                                                                             |      |       | ±1    | %               |  |

## **DC ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +12V, V_{EE} = -12V, V_{L} = +3.3V, T_{J} = +30^{\circ}C$  to  $+100^{\circ}C$ . Typical values are at  $T_{J} = +30^{\circ}C$ , unless otherwise specified.) (Notes 1, 2)

| PARAMETER                                                 | SYMBOL                                   | CONDITIONS                                                                                                                           | MIN                   | TYP                                | MAX                    | UNITS      |

|-----------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------|------------------------|------------|

| Measured-Current Gain Temperature Coefficient             | IMGETC                                   |                                                                                                                                      |                       | ±20                                |                        | ppm/°C     |

| Linearity Error                                           | I <sub>MLER</sub>                        | Gain, offset, and CMR errors calibrated out;<br>V <sub>IOSI</sub> = -0.2V and +4.4V, range B (Notes 4, 5)                            |                       |                                    | ±0.02                  | %FSR       |

| Rejection of Output Error Due to Common-Mode Load Voltage | CMR <sub>MOER</sub>                      | Range D, I <sub>OUT</sub> = 0A, V <sub>RCOMF</sub> = (V <sub>EE</sub> + 2.5V) and (V <sub>CC</sub> - 2.5V)                           |                       | 0.001                              | 0.005                  | %FSR/<br>V |

| VOLTAGE MONITOR                                           |                                          |                                                                                                                                      |                       |                                    |                        |            |

| Measured Output Voltage Range                             | V <sub>DUTM</sub>                        | Gain = +1, IOSV = AGND                                                                                                               | V <sub>EE</sub> + 2.5 |                                    | V <sub>C</sub> C - 2.5 | V          |

| Voltage-Sense-Amp Offset<br>Voltage Input                 | V <sub>IOSV</sub>                        | Relative to AGND                                                                                                                     | -0.2                  |                                    | +4.4                   | V          |

| Voltage-Sense-Amp Offset                                  | VDUTMOS                                  | Gain = +1                                                                                                                            |                       |                                    | ±25                    | mV         |

| Measured Voltage Offset Temperature Coefficient           | VDUTMOSTC                                |                                                                                                                                      |                       | ±10                                |                        | μV/°C      |

| Voltage-Sense-Amp Gain Error                              |                                          | Gain = +1                                                                                                                            |                       |                                    | ±1                     |            |

|                                                           | VDUTGE                                   | Gain = $+1/2$                                                                                                                        |                       |                                    | ±1                     | %          |

|                                                           |                                          | Gain = +1/6                                                                                                                          |                       |                                    | ±1                     |            |

| Measured-Voltage Gain Temperature Coefficient             | VDUTGETC                                 |                                                                                                                                      |                       | ±10                                |                        | ppm/°C     |

| Linearity Error                                           | VDUTLER                                  | Gain and offset errors calibrated out,<br>V <sub>IOSV</sub> = -0.2V and +4.4V, I <sub>OUT</sub> = 0A, gain<br>= +1, range B (Note 4) |                       |                                    | ±0.02                  | %FSR       |

| VOLTAGE/CURRENT CLAMPS                                    | (Note 8)                                 |                                                                                                                                      |                       |                                    |                        |            |

| Input Control Voltage                                     | V <sub>CLLO</sub> ,<br>V <sub>CLHI</sub> |                                                                                                                                      | V <sub>EE</sub> + 2.3 |                                    | V <sub>CC</sub> - 2.3  | V          |

| Voltage Clamp Range (Note 9)                              | VC <sub>RNG</sub>                        | DPS output current ≤ 10% of FSR                                                                                                      | V <sub>EE</sub> + 2.5 |                                    | V <sub>CC</sub> - 2.5  | V          |

| Voltage Clamp hange (Note 9)                              | VURNG                                    | DPS output current at FSR                                                                                                            | V <sub>EE</sub> + 5   |                                    | V <sub>C</sub> C - 5   |            |

| Voltage Clamp Gain                                        | VCGAIN                                   |                                                                                                                                      |                       | +1                                 |                        | V/V        |

| Voltage Clamp Accuracy                                    | VCERR                                    | Range A to D, I <sub>OUT</sub> ≤ 10% of FSR                                                                                          |                       |                                    | ±200                   | mV         |

| (Notes 2, 9)                                              | VOENN                                    | Range A to D, I <sub>OUT</sub> = ±FSR                                                                                                |                       |                                    | ±200                   | 1111       |

| Current Clamp Range                                       | IC <sub>RNG</sub>                        | (Note 10)                                                                                                                            |                       | V <sub>IOSI</sub><br>±1.5 x<br>FSR |                        | V          |

| Current Clamp Gain                                        | ICGAIN                                   |                                                                                                                                      |                       | 4                                  |                        | V/FSR      |

|                                                           |                                          | Range A, V <sub>OUT</sub> = ±FSR, I <sub>OUT</sub> = ±FSR (Notes 2, 10)                                                              |                       |                                    | ±0.15                  |            |

| Current Clamp Accuracy                                    | IC <sub>ERR</sub>                        | Range B to D, V <sub>OUT</sub> = ±FSR, gain and offset errors calibrated out (Note 10)                                               |                       |                                    | ±0.05                  | %FSR       |

| COMPARATOR INPUTS                                         | -                                        |                                                                                                                                      |                       |                                    |                        |            |

| Input Voltage Range                                       | CMPIRG                                   |                                                                                                                                      | VEE + 3.5             |                                    | Vcc - 3.5              | V          |

| Input Offset Voltage                                      | CMPIOS                                   | VITHHI = VITHLO = 0V                                                                                                                 |                       |                                    | ±30                    | mV         |

## **DC ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +12V, V_{EE} = -12V, V_{L} = +3.3V, T_{J} = +30^{\circ}C \text{ to } +100^{\circ}C.$  Typical values are at  $T_{J} = +30^{\circ}C$ , unless otherwise specified.) (Notes 1, 2)

| PARAMETER                               | SYMBOL                            | CONDITIONS                                                               | MIN                     | TYP  | MAX                     | UNITS |

|-----------------------------------------|-----------------------------------|--------------------------------------------------------------------------|-------------------------|------|-------------------------|-------|

| COMPARATOR OUTPUTS                      |                                   |                                                                          |                         |      |                         |       |

| Output High Voltage                     | СМРОН                             | $V_L = 2.375V$ to 3.3V, $R_{PULLUP} = 1k\Omega$                          | V <sub>L</sub> - 0.2    |      |                         | V     |

| Output Low Voltage                      | CMPOL                             | $V_L = 2.375V$ to 3.3V, $R_{PULLUP} = 1k\Omega$                          |                         |      | 0.4                     | V     |

| High-Impedance State<br>Leakage Current | CMPOLK                            |                                                                          |                         | ±5   |                         | nA    |

| High-Impedance Output<br>Capacitance    | CMP <sub>OC</sub>                 |                                                                          |                         | 1    |                         | pF    |

| ANALOG INPUTS                           | _                                 |                                                                          | _                       |      |                         |       |

| Input Current                           | liN                               |                                                                          |                         | ±5   |                         | nA    |

| Input Capacitance                       | CIN                               |                                                                          |                         | 4    |                         | рF    |

| DIGITAL INPUTS                          | 1                                 |                                                                          | 1                       |      |                         |       |

| Input High Voltage                      | VIH                               |                                                                          | V <sub>THR</sub> + 0.15 |      |                         | V     |

| Input Low Voltage                       | V <sub>IL</sub>                   |                                                                          |                         |      | V <sub>THR</sub> - 0.15 | V     |

| VTHR Input Range                        | V <sub>THR</sub>                  |                                                                          | 0.5                     |      | V <sub>L</sub> - 0.5    | V     |

| Input Current                           | I <sub>IN</sub>                   |                                                                          |                         | ±25  |                         | μΑ    |

| Input Capacitance                       | CIN                               |                                                                          |                         | 4    |                         | рF    |

| DIGITAL OUTPUTS                         |                                   |                                                                          |                         |      |                         |       |

| Output High Voltage                     | Voн                               | $V_L = 2.375V$ to 3.3V, relative to DGND,<br>$I_{OUT} = +1.0$ mA         | V <sub>L</sub> - 0.25   |      |                         | V     |

| Output Low Voltage                      | V <sub>OL</sub>                   | $V_L = 2.375V$ to 3.3V, relative to DGND, $I_{OUT} = -1.0$ mA            |                         |      | 0.2                     | V     |

| TEMPERATURE SENSOR                      | ,                                 |                                                                          | •                       |      |                         |       |

| Analog Output Offset                    | V <sub>TSNSO</sub>                | T <sub>J</sub> = +28°C                                                   |                         | 3.01 |                         | V     |

| Analog Output Gain                      | VTSNSG                            |                                                                          |                         | 10   |                         | mV/°C |

| Digital Output Temperature Threshold    | T <sub>TSNSR</sub>                | (Note 11)                                                                |                         | +130 |                         | °C    |

| Thermal-Shutdown Temperature            | T <sub>SDN</sub>                  |                                                                          |                         | +140 |                         | °C    |

| POWER SUPPLY                            |                                   |                                                                          | 1                       |      |                         |       |

| Positive Supply                         | Vcc                               | (Note 12)                                                                | 12                      |      | 18                      | V     |

| Negative Supply                         | VEE                               | (Note 12)                                                                | -15                     |      | -12                     | V     |

| Total Supply Voltage                    | V <sub>CC</sub> - V <sub>EE</sub> |                                                                          |                         |      | +30                     | V     |

| Logic Supply                            | V <sub>L</sub>                    |                                                                          | +2.375                  |      | +3.300                  | V     |

| Positive Supply Current                 | Icc                               | No load                                                                  |                         | 20   | 22                      | mA    |

| Negative Supply Current                 | IEE                               | No load                                                                  |                         | 19   | 21                      | mA    |

| Analog Ground Current                   | IAGND                             | No load                                                                  |                         | 0.8  | 1.0                     | mA    |

| Logic Supply Current                    | IL                                | No load, all digital inputs at DGND                                      |                         | 7.0  | 9.0                     | mA    |

| Digital Ground Current                  |                                   | No load, all digital inputs at DGND                                      |                         | 7.0  | 9.0                     | mA    |

| Power-Supply Rejection Ratio            | IDGND<br>PSRR                     | Each supply varied individually from min to max, V <sub>DUT</sub> = 5.0V |                         | 80   | 5.0                     | dB    |

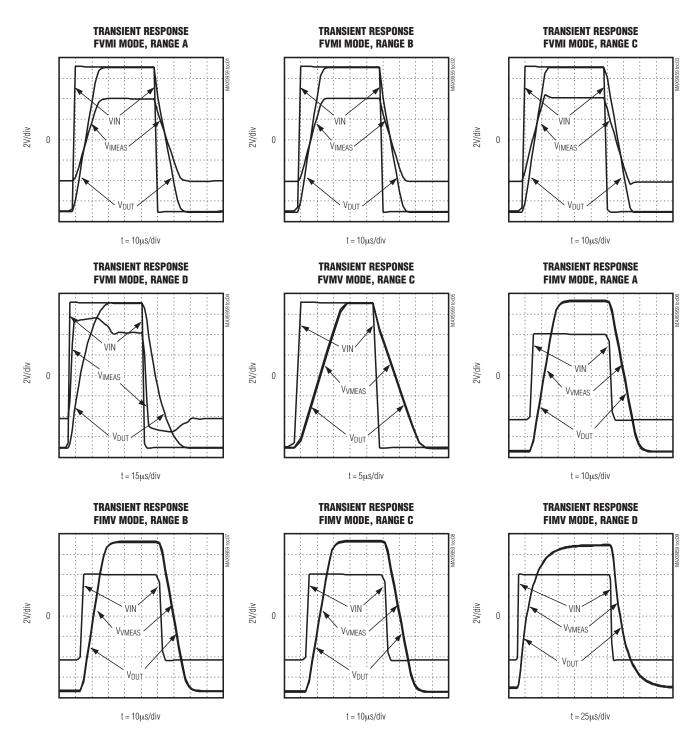

## **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +12V, V_{EE} = -12V, V_{L} = +3.3V, C_{C1} = 350 pF, C_{L} = 100 pF, C_{MEAS} = 100 pF, C_{IMEAS} = 100 pF, T_{J} = +30 ^{\circ}C \text{ to } +100 ^{\circ}C. \text{ Typical values are at } T_{J} = +35 ^{\circ}C, \text{ unless otherwise specified.}) \text{ (Notes 1, 2)}$

| PARAMETER                         | SYMBOL             | CONDITIONS                                                                                                | MIN | TYP | MAX  | UNITS   |

|-----------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------|-----|-----|------|---------|

| FORCE VOLTAGE (Notes 13, 1        | 14)                |                                                                                                           |     |     |      |         |

|                                   |                    | Range D = $\pm 200 \mu A$ , R <sub>L</sub> = $35 k\Omega$ to AGND                                         |     | 30  |      |         |

| Carrier a Time a                  |                    | Range C = $\pm 2$ mA, R <sub>L</sub> = $3.5$ k $\Omega$ to AGND                                           |     | 20  |      |         |

| Settling Time                     | FV <sub>ST</sub>   | Range B = $\pm 20$ mA, R <sub>L</sub> = $350\Omega$ to AGND                                               |     | 30  | 50   | μs      |

|                                   |                    | Range A = $\pm 800$ mA, R <sub>L</sub> = $8.75\Omega$ to AGND                                             |     | 25  |      |         |

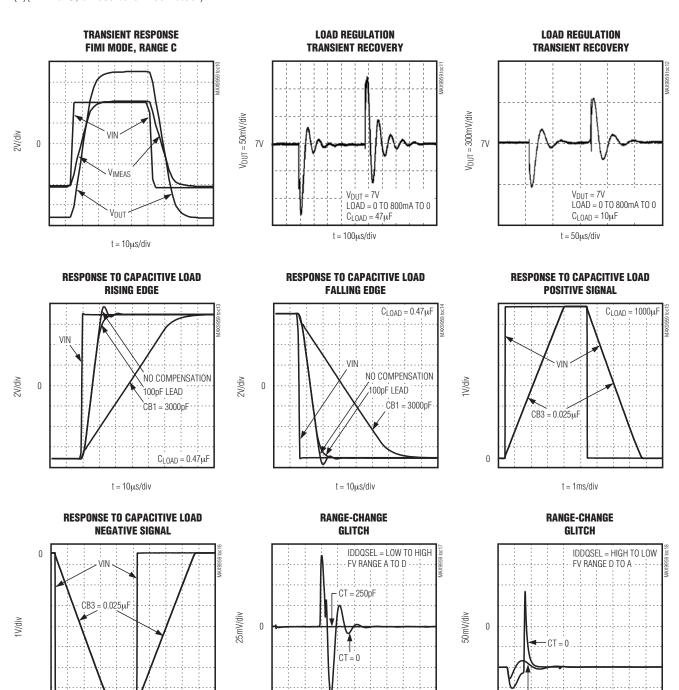

| LOAD REGULATION SETTLIN           | G TIME (No         | te 14)                                                                                                    |     |     |      |         |

| Settling Time                     | LR <sub>ST</sub>   | Range A, $V_{IN} = \pm 7V$ , $R_L = 8.75\Omega$ switched between open circuit to AGND, $C_L = 10\mu F$    |     | 100 |      | μs      |

| FORCE VOLTAGE/MEASURE             | CURRENT (          | Notes 13, 14, 15)                                                                                         | -   |     |      |         |

|                                   |                    | Range D = $\pm 200\mu$ A, R <sub>L</sub> = $35k\Omega$ to AGND                                            |     | 50  |      |         |

| Cattling Times                    | E) /N 41 ==        | Range C = $\pm 2$ mA, R <sub>L</sub> = $3.5$ k $\Omega$ to AGND                                           |     | 20  |      |         |

| Settling Time                     | FVMI <sub>ST</sub> | Range B = $\pm 20$ mA, R <sub>L</sub> = $350\Omega$ to AGND                                               |     | 25  | 50   | μs      |

|                                   |                    | Range A = $\pm 800$ mA, R <sub>L</sub> = $8.75\Omega$ to AGND                                             |     | 35  |      |         |

| FORCE CURRENT (Notes 13,          | 14)                |                                                                                                           |     |     |      |         |

|                                   |                    | Range D = $\pm 200\mu$ A, R <sub>L</sub> = $35k\Omega$ to AGND                                            |     | 100 |      |         |

| Sattling Time                     | Пот                | Range C = $\pm 2$ mA, R <sub>L</sub> = $3.5$ k $\Omega$ to AGND                                           |     | 35  |      |         |

| Settling Time                     | FIST               | Range B = $\pm 20$ mA, R <sub>L</sub> = $350\Omega$ to AGND                                               |     | 25  | 50   | μs      |

|                                   |                    | Range A = $\pm 800$ mA, R <sub>L</sub> = $8.75\Omega$ to AGND                                             |     | 20  |      |         |

| FORCE CURRENT/MEASURE             | VOLTAGE (          | Notes 13, 14, 15)                                                                                         |     |     |      |         |

|                                   |                    | Range D = $\pm 200\mu$ A, R <sub>L</sub> = $35k\Omega$ to AGND                                            |     | 100 |      | -<br>μs |

| Sattling Time                     | EIM)/              | Range C = $\pm 2$ mA, R <sub>L</sub> = $3.5$ k $\Omega$ to AGND                                           |     | 35  |      |         |

| Settling Time                     | FIMV <sub>ST</sub> | Range B = $\pm 20$ mA, R <sub>L</sub> = $350\Omega$ to AGND                                               |     | 25  | 50   |         |

|                                   |                    | Range A = $\pm 800$ mA, R <sub>L</sub> = $8.75\Omega$ to AGND                                             |     | 40  |      |         |

| FORCE OUTPUT                      |                    |                                                                                                           |     |     |      |         |

| Output Slew Rate                  | FOSLEW             | C <sub>L</sub> = 0F (Note 16)                                                                             | 0.7 |     | 2.1  | V/µs    |

| Stable Load Capacitance Range     | FO <sub>SLC</sub>  | (Notes 17, 18)                                                                                            |     |     | 1000 | μF      |

| Output Overshoot                  | FOosht             | $C_L < 20\mu F, CB1 = 3nF$                                                                                |     | 0   |      | %       |

| MEASURE OUTPUT                    |                    |                                                                                                           |     |     |      |         |

| Stable Load Capacitance Range     | MO <sub>SLC</sub>  | (Note 17)                                                                                                 |     |     | 1000 | рF      |

| COMPARATORS (CILIMHI/ILIML        | .o = 20pF, F       | $R_{PULLUP} = 1 k\Omega$ ) (Note 19)                                                                      |     |     |      |         |

| Propagation Delay                 | CMP <sub>PD</sub>  | 100mV overdrive, 1V <sub>P-P</sub> , measured from input threshold zero crossing to 50% of output voltage |     | 100 |      | ns      |

| Rise Time                         | CMPTR              | 20% to 80%                                                                                                |     | 80  |      | ns      |

| Fall Time                         | CMPTF              | 20% to 80%                                                                                                |     | 5   |      | ns      |

| Disable True to High<br>Impedance | CMPHIZT            | Measured from 50% of digital input voltage to 10% of output voltage                                       |     | 100 |      | ns      |

| Disable False to Active           | CMPHIZF            | Measured from 50% of digital input voltage to 90% of output voltage                                       |     | 100 |      | ns      |

### **AC ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +12V, V_{EE} = -12V, V_{L} = +3.3V, C_{C1} = 350pF, C_{L} = 100pF, C_{MEAS} = 100pF, C_{IMEAS} = 100pF, T_{J} = +30^{\circ}C$  to  $+100^{\circ}C$ . Typical values are at  $T_{J} = +35^{\circ}C$ , unless otherwise specified.) (Notes 1, 2)

| PARAMETER                  | SYMBOL          | CONDITIONS                                                        | MIN | TYP | MAX | UNITS |

|----------------------------|-----------------|-------------------------------------------------------------------|-----|-----|-----|-------|

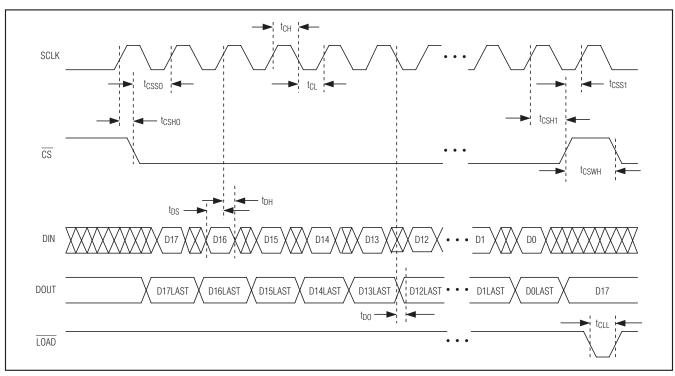

| SERIAL PORT TIMING CHA     | RACTERIS        | TICS (V <sub>L</sub> = 3.0V, C <sub>DOUT</sub> = 10pF) (Figure 4) |     |     |     |       |

| Serial Clock Frequency     | fsclk           |                                                                   |     |     | 20  | MHz   |

| SCLK Pulse-Width High      | tсн             |                                                                   | 12  |     |     | ns    |

| SCLK Pulse-Width Low       | tCL             |                                                                   | 12  |     |     | ns    |

| SCLK Fall to DOUT Valid    | t <sub>DO</sub> |                                                                   |     |     | 25  | ns    |

| CS Low to SCLK High Setup  | tcsso           |                                                                   | 10  |     |     | ns    |

| SCLK High to CS High Hold  | tCSH1           |                                                                   | 22  |     |     | ns    |

| SCLK High to CS Low Hold   | tcsH0           | (Note 17)                                                         | 0   |     |     | ns    |

| CS High to SCLK High Setup | tCSS1           |                                                                   | 5   |     |     | ns    |

| DIN to SCLK High Setup     | t <sub>DS</sub> |                                                                   | 10  |     |     | ns    |

| DIN to SCLK High Hold      | tDH             |                                                                   | 0   |     |     | ns    |

| CS Pulse-Width High        | tcswh           |                                                                   | 10  |     |     | ns    |

| CS Pulse-Width Low         | tcswl           |                                                                   | 10  |     |     | ns    |

| LOAD Pulse-Width Low       | tCLL            |                                                                   | 20  |     |     | ns    |

| Power-On Reset             | POR             |                                                                   |     | 50  |     | μs    |

- Note 1: All minimum and maximum test limits are 100% production tested at T<sub>J</sub> = +35°C ±15°C at nominal supplies. Specifications over the full operating temperature range are guaranteed by design and characterization.

- Note 2: Exercise care not to exceed the maximum power dissipation specifications listed in the *Absolute Maximum Ratings* section. With drive current of ±800mA limit DPS operation to two quadrants (i.e., when sourcing current limit V<sub>DUT</sub> to below +7V, when sinking current limit V<sub>DUT</sub> to above -7V). With drive current below ±800mA and four-quadrant operation, limit DPS power dissipation to below the allowed maximum.

- Note 3: VIN swept to achieve an output voltage of (VEE + 2.5V) to (VCC 2.5V), with IOUT = 0.

- Note 4: Parameters expressed in terms of %FSR (percent of full-scale range) are as a percent of the end-point-to-end-point range.

- **Note 5:** Case must be maintained to within ±5°C for linearity specifications to apply.

- **Note 6:** Load regulation is defined at a single programmed output voltage (force voltage mode), independent of linearity specification, with a 0 to 100% current step.

- **Note 7:** To maintain linearity, keep the clamps at least 700mV away from V<sub>RCOMF</sub>.

- Note 8: In the force-current and force-voltage modes, the reference-clamping voltage CLH must be greater than 0V, and CLL must be less than 0V. For high clamping accuracy, CLH-CLL is > 1V. To maintain 0.02% force-voltage linearity when the programmable current clamps are enabled, two conditions must be met: 1) CLH and CLL must be set 12.5% FSR higher than the forced current and 2) CLH and CLL must be set such that CLH is ≥ 1.6V + IOSI and CLL is ≤ -1.6V + IOSI (e.g., if driving ±1mA in the 2mA range, the current clamps must be set to a minimum of ±1.5mA, or CLH = 3V, CLL = -3V, and IOSI = 0V).

- Note 9: DPS in force current mode.

- Note 10: DPS in force voltage mode.

- Note 11: The temperature threshold may vary up to ±10°C from the specified threshold.

- Note 12: The device operates properly within absolute specifications, for varying supply voltages with equally varying output voltage settings.

- **Note 13:** Settling times are for a full-scale voltage or current step. FV<sub>ST</sub> measured from VIN to VDUT, FVMI<sub>ST</sub> from VIN to IMEAS, FI<sub>ST</sub> from VIN to VDUT, and FIMV<sub>ST</sub> from VIN to VMEAS.

- Note 14: Settling times are to 0.1% of FSR.

- **Note 15:** The actual settling time of the measure path (sense input to measure output) is less than 1µs. However, the RC time constant of the sense resistor and the load capacitance causes a longer overall settling time of VDUT. This settling time is a function of the current range resistor.

- Note 16: Slew rate is measured from the 20% to 80% points.

- Note 17: Guaranteed by design and characterization.

- Note 18: Range A.

- Note 19: The propagation delay time is measured by holding the current constant, and transitioning ITHHI or ITHLO.

## Typical Operating Characteristics

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

## Typical Operating Characteristics (continued)

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

$t = 10\mu s/div$

$C_{LOAD} = 1000 \mu F$

t = 1ms/div

CT = 250pF

$t = 5\mu s/div$

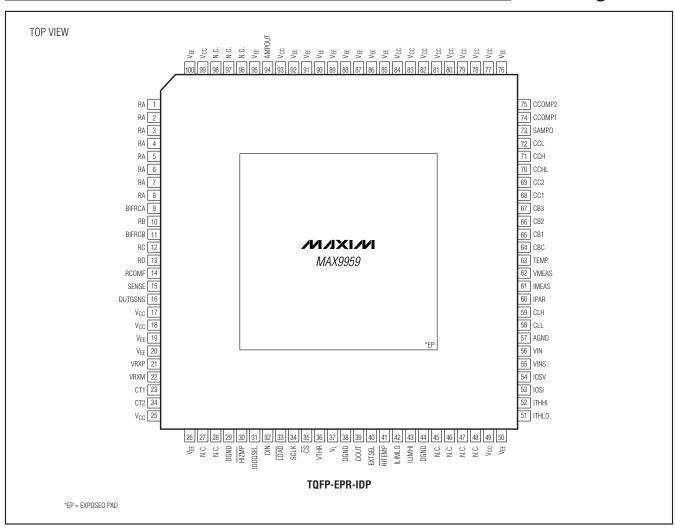

## **Pin Description**

| PIN                                   | NAME    | FUNCTION                                                                                                                                                                                    |

|---------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1–8                                   | RA      | Range A Outputs. Connect together and to a range-setting resistor.                                                                                                                          |

| 9                                     | BIFRCA  | Positive Current-Sense-Amplifier Input. Used in range A to provide a Kelvin connection to range-setting resistor.                                                                           |

| 10                                    | RB      | Range B Output. Connect to a range-setting resistor.                                                                                                                                        |

| 11                                    | BIFRCB  | Positive Current-Sense-Amplifier Input. Used in range B to provide a Kelvin connection to range-setting resistor.                                                                           |

| 12                                    | RC      | Range C Output. Connect to a range-setting resistor.                                                                                                                                        |

| 13                                    | RD      | Range D Output. Connect to a range-setting resistor.                                                                                                                                        |

| 14                                    | RCOMF   | Sense Resistors Kelvin Connection. The Kelvin connection for the sense resistors that connect to the DUT. RCOMF provides a feedback point for current sensing.                              |

| 15                                    | SENSE   | Sense Input. Kelvin connection to the DUT. Provides the feedback signal for FVMI and the measured signal for FIMV.                                                                          |

| 16                                    | DUTGSNS | DUT Ground Sense. In force voltage mode, senses the error between AGND and DUTGND and adjusts the output voltage to achieve the desired voltage drop across the DUT with respect to DUTGND. |

| 17, 18, 25, 49,<br>77–84, 93, 99      | Vcc     | Positive Analog Supply                                                                                                                                                                      |

| 19, 20, 26, 50, 76,<br>85–92, 95, 100 | VEE     | Negative Analog Supply                                                                                                                                                                      |

| 21                                    | VRXP    | Positive Current-Sense-Amplifier Input. Used in the external range to provide a Kelvin connection to the range-setting resistor.                                                            |

| 22                                    | VRXM    | Negative Current-Sense-Amplifier Input. Used in the external range to provide a Kelvin connection to the range-setting resistor.                                                            |

| 23                                    | CT1     | Range-Change Glitch-Control Capacitor Connection. Connect optional capacitor from CT1 to DGND.                                                                                              |

| 24                                    | CT2     | Range-Change Glitch-Control Capacitor Connection. Connect optional capacitor from CT2 to DGND.                                                                                              |

| 27, 28, 45–48,<br>96, 97, 98          | N.C.    | No Connection. Make no connection to these pins.                                                                                                                                            |

| 29, 38, 44                            | DGND    | Digital Ground                                                                                                                                                                              |

| 30                                    | HIZMP   | High-Impedance Control Input. Places current and voltage measure outputs into a high-impedance state.                                                                                       |

| 31                                    | IDDQSEL | IDDQ Test Select. In FV mode, switches between the programmed current range and range D, the lowest current range.                                                                          |

| 32                                    | DIN     | Data Input. Serial interface data input.                                                                                                                                                    |

| 33                                    | LOAD    | Load Data Input. A falling edge at LOAD transfers data from the input registers to the DPS registers.                                                                                       |

| 34                                    | SCLK    | Serial Clock Input. Serial interface clock.                                                                                                                                                 |

| 35                                    | CS      | Chip-Select Input                                                                                                                                                                           |

| 36                                    | VTHR    | Threshold Voltage Input. Sets the input logic threshold level of all digital inputs. Defaults to 1/2 V <sub>L</sub> if unconnected.                                                         |

| 37                                    | $V_{L}$ | Logic Power Supply                                                                                                                                                                          |

## Pin Description (continued)

| PIN | NAME   | FUNCTION                                                                                                                                                                                           |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 39  | DOUT   | Data Output. Serial interface data output.                                                                                                                                                         |

| 40  | EXTSEL | External Select Output. Selects the external range.                                                                                                                                                |

| 41  | HITEMP | High Temperature Indicator Output. Open-collector output goes low when the temperature of the die is above the specified safe operating temperature.                                               |

| 42  | ILIMLO | Low Current-Limit Output. A sensed current below the ITHLO level forces the ILIMLO output low. ILIMLO is an open-drain output.                                                                     |

| 43  | ILIMHI | High Current-Limit Output. A sensed current above the ITHHI level forces the ILIMHI output low. ILIMHI is an open-drain output.                                                                    |

| 51  | ITHLO  | Low Current-Limit Input. Voltage input that sets the lower threshold for the sense current comparator.                                                                                             |

| 52  | ITHHI  | High Current-Limit Input. Voltage input that sets the upper threshold for the sense current comparator.                                                                                            |

| 53  | IOSI   | Current-Sense Offset Voltage Input. Voltage input that sets an offset voltage for the current-sense amplifier in either FI or MI mode.                                                             |

| 54  | IOSV   | Measure Offset Voltage Input. Voltage input that sets an offset voltage for the measure voltage amplifier.                                                                                         |

| 55  | VINS   | Forced-Current Input. Voltage input that sets the forced current in FI slave mode.                                                                                                                 |

| 56  | VIN    | Forced-Current/Voltage Input. Voltage input that sets the forced current in FI mode or forced voltage in FV mode.                                                                                  |

| 57  | AGND   | Analog Ground                                                                                                                                                                                      |

| 58  | CLL    | Compliance Low Input. Voltage input that sets the low-side voltage/current compliance.                                                                                                             |

| 59  | CLH    | Compliance High Input. Voltage input that sets the high-side voltage/current compliance.                                                                                                           |

| 60  | IPAR   | Current-Controlled Proportional Voltage Output. IPAR outputs a voltage that is proportional to the DUT current. Used to slave additional parallel DPSs to provide increased output current.        |

| 61  | IMEAS  | Current-Controlled Proportional Voltage Output. IMEAS outputs a voltage that is proportional to the DUT current. High impedance when HIZMP is forced low.                                          |

| 62  | VMEAS  | Voltage-Controlled Proportional Voltage Output. VMEAS outputs a voltage equal to 1x, 1/2x, or 1/6x the voltage present at SENSE. High impedance when HIZMP is forced low.                          |

| 63  | TEMP   | Temperature Monitor Output. TEMP outputs a voltage proportional to die temperature of 10mV/K.                                                                                                      |

| 64  | CBC    | CB Common. Common point for bypass capacitor connections CB1, CB2, and CB3.                                                                                                                        |

| 65  | CB1    | Bypass Capacitor 1. Compensation capacitor 1 connection.                                                                                                                                           |

| 66  | CB2    | Bypass Capacitor 2. Compensation capacitor 2 connection.                                                                                                                                           |

| 67  | CB3    | Bypass Capacitor 3. Compensation capacitor 3 connection.                                                                                                                                           |

| 68  | CC1    | Main Compensation Capacitor. Compensation capacitor connection 1.                                                                                                                                  |

| 69  | CC2    | Main Compensation Capacitor. Compensation capacitor connection 2.                                                                                                                                  |

| 70  | CCHL   | Clamp Compensation Capacitor Common. Common connection for CCL and CCH.                                                                                                                            |

| 71  | CCH    | High Clamp Compensation Capacitor. High-side voltage clamp compensation capacitor connection.                                                                                                      |

| 72  | CCL    | Low Clamp Compensation Capacitor. Low-side voltage clamp compensation capacitor connection.                                                                                                        |

| 73  | SAMPO  | Lead Compensation Capacitor Common. Common connection for CCOMP1 and CCOMP2.                                                                                                                       |

| 74  | CCOMP1 | Compensation Capacitor 1. Lead compensation capacitor 1 connection.                                                                                                                                |

| 75  | CCOMP2 | Compensation Capacitor 2. Lead compensation capacitor 2 connection.                                                                                                                                |

| 94  | AMPOUT | Main Amplifier Output. Drives the external buffer when in external range mode.                                                                                                                     |

| _   | EP     | Exposed pad. Internally connected to V <sub>EE</sub> . Connect to a large V <sub>EE</sub> power plane or heatsink to maximize thermal performance. Not intended as an electrical connection point. |

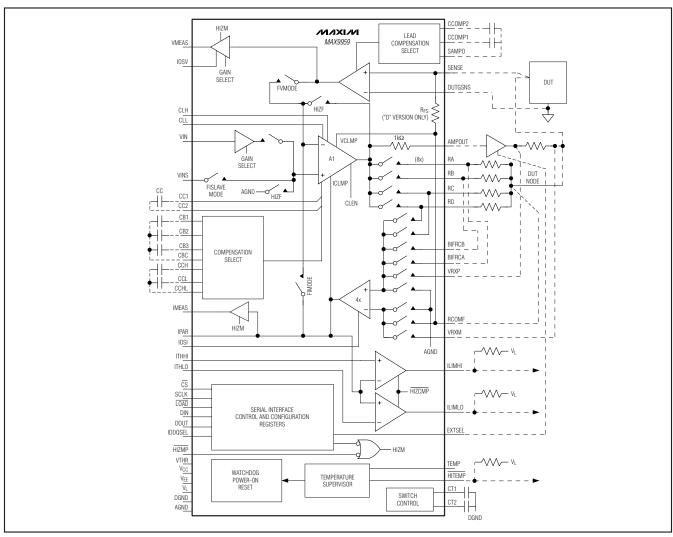

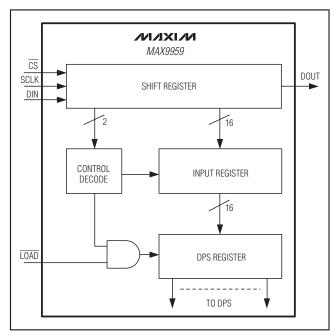

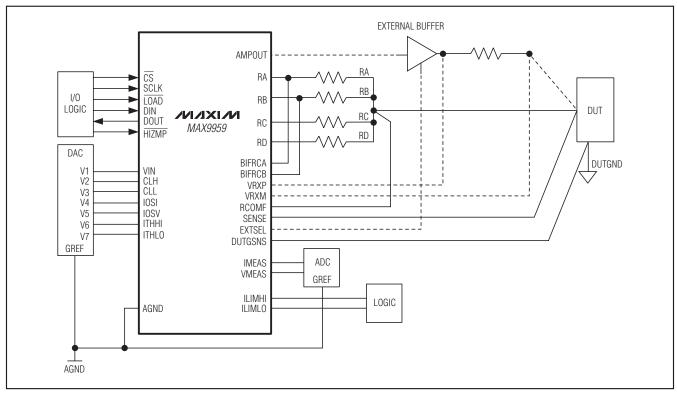

Figure 1. Functional Diagram

## \_Detailed Description

The MAX9959 device power supply (DPS) is a voltage source when the load current is between the two programmed limits and transitions gracefully into a precision current source/sink if a programmed current limit is reached. It provides voltage-control inputs that allow independent setting of the output voltage, the maximum voltage (current), and the minimum (smallest positive or most negative) voltage (current), and it can source voltages over a span of 25V at up to ±800mA of current. For currents less than ±200mA, the MAX9959 provides full four-quadrant operation. It supports the addition of an external buffer for sourcing and sinking higher currents, and multiple MAX9959s can be paralleled to load-share, thus realizing higher total current capability

with greater flexibility. Additionally, the output features two independently adjustable clamps that limit both the negative and positive output voltages or currents to externally provided limits. It offers voltage and current measurement outputs, a window comparator for go/nogo testing, a temperature monitor, a high-temperature warning flag, and a high-temperature shutdown.

The MAX9959D features an internal  $300 k\Omega$  sense resistor, RFS, between RCOMF and SENSE. The MAX9959F version does not include this sense resistor.

#### **Analog Signal Polarities**

In force-voltage mode the output voltage (SENSE/RCOMF in Figure 1, the *Functional Diagram*) is proportional to the input control voltage and determined by the choice

12 \_\_\_\_\_\_ /VI/XI/M

of one of three +/- gain settings controlled through the serial interface.

In force-current mode, the output current is proportional to the input control voltage and behaves according to the formula:

$$I_{OUT} = \frac{V_{IN}}{4R_{SENSE}}$$

Positive current is defined as flowing out of the MAX9959 DPS.

In high-impedance mode, outputs RA, RB, RC, and RD are high impedance.

### Current-Sense-Amplifier Offset Voltage Input

The current-sense amplifier monitors the voltage across the output resistors connected to RA, RB, RC, and RD in Figure 1. The current-sense offset voltage input, IOSI, introduces an offset to the current-sense amplifier. When IOSI is zero relative to AGND, the nominal output voltage range of the current-sense amplifier, corresponding to a +/- full-scale output current, is -4V to +4V. Voltage applied to IOSI adds directly to this output voltage. For example, if +4V is applied to IOSI, the voltage range corresponding to +/- full-scale current becomes 0 to +8V, within the range allowed by the power-supply rails.

### Measure Voltage-Sense-Amplifier Offset Voltage Input

The measure voltage-sense amplifier monitors the output voltage of the MAX9959. The measure offset voltage input, IOSV, introduces an offset to the measure voltage amplifier. Voltage applied to IOSV adds directly to this output voltage.

#### **External Mode Support**

The MAX9959 includes resources to drive an external amplifier to provide a current range beyond the highest range (or below the lowest current range) included within the device. A voltage output, AMPOUT, is provided for the input of the external amplifier, and a digital output, EXTSEL, goes high to activate the external amplifier. Feedback inputs VRXP and VRXM connect across the external amplifier's current-sense resistor. The external amplifier must have a high-impedance output when not selected (EXTSEL = low), if connected as shown in Figure 1.

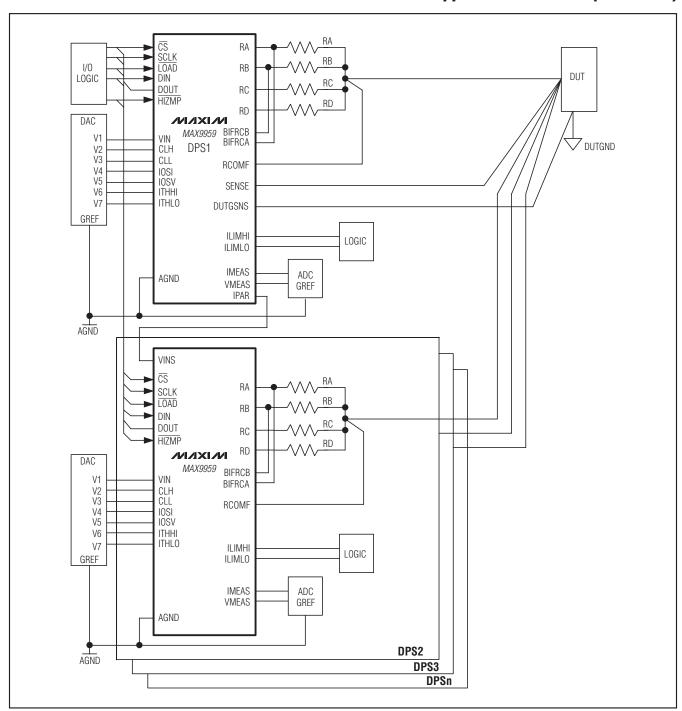

#### **Parallel DPS Operation**

The MAX9959 allows multiple devices to be configured in parallel to increase the available DUT drive current. One DPS must be configured as the master (in FV

mode), and the parallel devices must be configured as slaves (in FI slave mode). The connection between the master and slaves is made using the IPAR output and VINS input. IPAR outputs a voltage that is proportional to the DUT current and VINS provides a proportional force-current/voltage input. Up to 16 MAX9959s can be placed in parallel.

### **Voltage Clamps**

Internal programmable voltage clamps limit the output voltage to the programmed values when in FI mode. Set the clamp voltage limits with inputs CLH and CLL. The clamps handle the full ±800mA and are triggered by the voltage at RCOMF independent of the voltage at SENSE. Clamp enable bit, CLEN, in the serial control word, enables the voltage clamps.

### **Current Limit**

Programmable and default current limits are available at the output in the FI and FV modes. When programmable current compliance is enabled, the DPS output current limits at the preprogrammed setting for each current range. When the current limit is disabled, the DPS output current limits at the default value, 147% FSR (typ), of the selected current ranges for range B, C, and D. In range A, under FI or FV conditions, the DPS output current limits at 138% FSR (typ). For currents within each selected range, the FV output behaves as a constant voltage source. When the default or programmed current compliance limits are reached, the DPS transitions to constant current mode.

### **Current-Limit Flags**

The MAX9959 can flag currents within user-specified limits. This allows fast go/no-go testing in production environments. The window comparator continuously monitors the load current and compares it to inputs ITHHI and ITHLO. The comparator outputs are open collector and can be made high impedance with the serial interface.

#### Measure Amplifier High-Impedance Modes

Measure outputs VMEAS and IMEAS can be placed in a high-impedance state with logic input  $\overline{\text{HIZMP}}$  or serial interface bit  $\overline{\text{HIZMS}}$ . This allows busing of the measure outputs with other DPS measure outputs.

#### **Ground and DUT Ground Sense**

Two ground connections, AGND (analog ground) and DGND (digital ground), are both local grounds. Connect these grounds together on the printed circuit board (PCB). DUT ground-sense input, DUTGSNS, allows sensing with respect to the DUT in force voltage mode.

#### **Short-Circuit Protection**

RA, RB, RC, RD, AMPOUT, and SENSE withstand a short to any voltage between and including the supply rails.

#### Temperature Sensor and Over-Temperature Protection

The MAX9959 outputs a voltage proportional to its die temperature, at TEMP, of 10mV/K (or 10mV/°C) with the nominal output voltage being 3.43V at 343K (+70°C). If the temperature of the die enters the range of +120°C to +140°C, the open-collector output HITEMP goes low. If the die temperature exceeds +140°C, the temperature sensor issues a power-on reset, placing the DPS into its high-impedance state. A reduction in temperature after a temperature-initiated reset does not return the DPS to its original operating state; reprogramming is required.

### Mode and Range-Change Transients

Glitch minimization measures in the MAX9959 employ make-before-break switching and internal clamps to reduce output glitches. To guarantee minimum glitches between range changes, change between adjacent ranges, e.g., RA to RB, RD to RC. Do not switch to another range until the present range-change operation has been completed. In addition to the make-before-break measures, connections CT1 and CT2 are provided for optional capacitors that control the edge rate of the gate drive to the range-change switches. Two capacitors of 150pF each provide a reasonable balance between glitch control and range-change transition time.

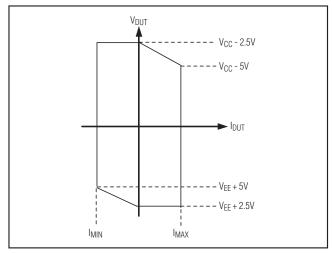

# DUT Voltage Swing vs. DUT Current and Power-Supply Voltages

The DUT voltage that the MAX9959 can deliver is limited by two main and two lesser factors:

- 1) The 2.5V overhead from each supply rail required by the amplifiers and other on-chip circuitry.

- 2) The voltage drop across the sense resistor and internal circuitry in series with the sense resistor. At full current the combined voltage drop is 2.5V, 1V across the resistor and 1.5V across the switches. This voltage is not all in addition to the overhead requirement. There is some overlap of the two effects; see Figure 2.

- 3) Variations in the system power-supply voltages.

- 4) Variations between the ground voltage of the device-under-test and AGND.

Neglecting the effects of items 3 and 4, the output capabilities of the DPS are demonstrated by Figure 2.

Figure 2 shows that for zero DUT current, the DUT voltage swing is from ( $V_{EE}$  + 2.5V) to ( $V_{CC}$  - 2.5V). For positive DUT currents, the maximum voltage drops off

Figure 2. Output Swing

linearly until it reaches  $V_{CC}$  - 5V at full current. Similarly for negative DUT currents, the magnitude of the negative voltage drops off linearly until it reaches  $V_{EE}$  + 5V.

When the DPS is driving more than ±200mA output current, the power dissipated by the DPS must be limited to below the power limit of the package (see the Absolute Maximum Ratings and Note 2). For example, when the DPS is driving ±800mA in range A, the VCC supply must not exceed +12V, and the VEE supply must not exceed -12V. When the DPS is sourcing current, the DUT node must not be driven below zero volts. When the DPS is sinking current, the DUT node must not be driven above zero volts (two-quadrant operation). When operating below ±800mA, four-guadrant operation may be possible depending on the power dissipation of the DPS. Power dissipation analysis must consider variations in the power-supply voltage and the voltage difference between the device-under-test ground and the DPS AGND (items 3 and 4 above).

Since the maximum output voltage range is relative to the supply voltage, any decrease in a supply voltage from nominal proportionally decreases the range. The maximum output voltage range is also reduced by the difference between the DUT ground and the analog ground potentials (DUTGSNS - AGND). Note that within these limitations, the forced DUT voltage is equal to DUT ground plus the input control voltage. Similarly, when measuring a voltage, the measured voltage is equal to the difference between the DUT voltage and DUT ground.

## **Configuration and Control**

Configuration of the MAX9959 is achieved through the serial interface, and through the dedicated logic-control inputs HIZMP, LOAD, and IDDQSEL.

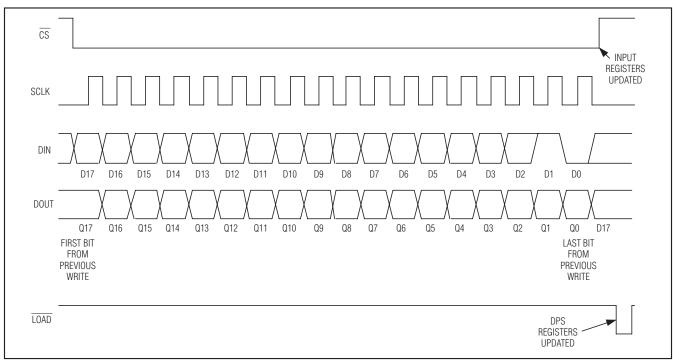

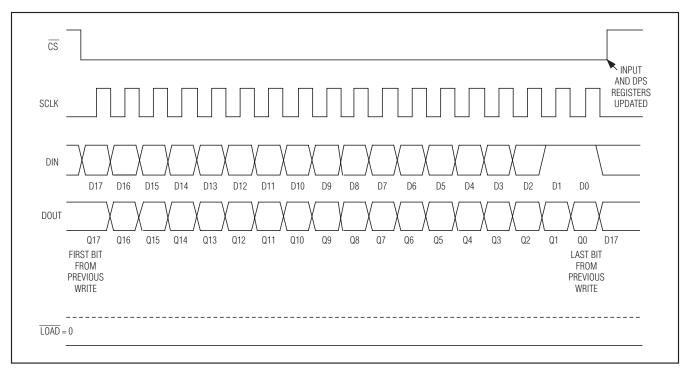

The serial interface has a shift register, an input register, and a DPS register (Figure 3). Serial data do not directly affect the DPS until the data reach the DPS register. Control of data flow to the DPS register is through two control bits (A0 and C0) and logic input LOAD. LOAD asynchronously transfers data from the input register into the DPS register. If LOAD is held low when data are latched into the input register, then the data transfer directly (transparently) into the DPS register. This allows changing the state of the DPS coincident with the end of serial-port data communication, or asynchronously with respect to serial-port communications. Asynchronous update using LOAD facilitates simultaneous updates of multiple daisy-chained DPS devices.

#### **DPS Data Control Bits**

An 18-bit word programs the MAX9959. Table 1 outlines the 18-bit control word structure.

#### **Serial Interface Data Flow Control Bits**

Bits 0 and 1 (C0 and A0) specify if and how data transfers from the shift register to the input and DPS registers. The specified actions shown in Table 2 occur when  $\overline{CS}$  goes high (Figures 5 and 6).

Figure 3. DPS Serial Port Block Diagram

When A0 = C0 = 0 (NOP), data move through the shift register to DOUT without change in mode or operation. This is useful when daisy-chaining devices to shift operational data through a number of devices to a specific device without altering some or all the device's operational data. To update multiple daisy-chained devices simultaneously use A0 = 1 and C0 = 0 to load the input register of the devices to be updated and activate  $\overline{\text{LOAD}}$  after  $\overline{\text{CS}}$  goes high (Figure 5). If  $\overline{\text{LOAD}}$  is held low while  $\overline{\text{CS}}$  is raised, data latched to the input register are also latched to the DPS register, independent of the state of C0.

Table 1. Data Control Bits and Bit Order

| DATA BIT | NAME              | FUNCTION                           |  |  |  |

|----------|-------------------|------------------------------------|--|--|--|

| 17       | FMODE             | Mode Select                        |  |  |  |

| 16       | G2                |                                    |  |  |  |

| 15       | G1                | Gain and Polarity Select           |  |  |  |

| 14       | G0                | ,                                  |  |  |  |

| 13       | RS2               |                                    |  |  |  |

| 12       | RS1               | Range Select                       |  |  |  |