#

### Low-Voltage, Triple, Hot-Swap Controllers/ Power Sequencers/Voltage Trackers

### **General Description**

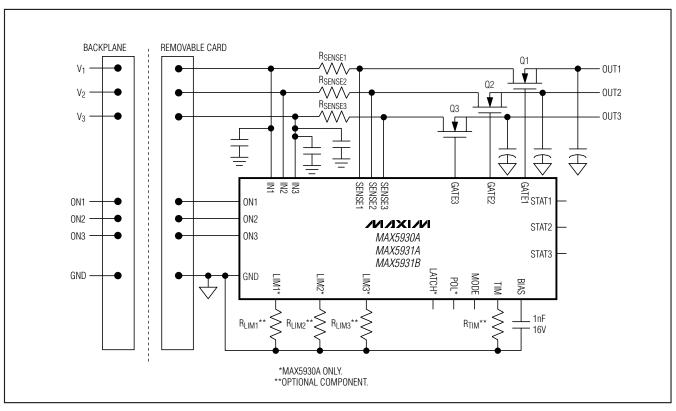

The MAX5930A/MAX5931A/MAX5931B +1V to +15V triple hot-swap controllers provide complete protection for multisupply systems. They allow the safe insertion and removal of circuit cards into live backplanes. These devices hot swap multiple supplies ranging from +1V to +15V, provided one supply is at or above +2.7V. The input voltage rails (channels) can be configured to sequentially turn-on/off, track each other, or have completely independent operation.

The discharged filter capacitors of the circuit card provide low impedance to the live backplane. High inrush currents from the backplane to the circuit card can burn up connectors and components, or momentarily collapse the backplane power supply leading to a system reset. The MAX5930A/MAX5931A/MAX5931B hot-swap controllers prevent such problems by gradually ramping up the output voltage and regulating the current to a preset limit when the board is plugged in, allowing the system to stabilize safely. After the startup cycle is complete, on-chip comparators provide VariableSpeed/BiLevel™ protection against short-circuit and overcurrent faults, and provide immunity against system noise and load transients.

The load is disconnected in the event of a fault condition. The MAX5930A/MAX5931A/MAX5931B fault-management mode is selectable, allowing latched fault or autoretry after a fault condition.

The MAX5930A/MAX5931A/MAX5931B offer a variety of options to reduce external component count and design time. All devices integrate an on-board charge pump to drive the gates of low-cost, external n-channel MOSFETs, an adjustable startup timer, and an adjustable current limit. The devices offer integrated features like startup current regulation and current glitch protection to eliminate external timing resistors and capacitors. The MAX5931A provides an opendrain, active-low status output for each channel, the MAX5931B provides an open-drain, active-high status output for each channel, and the MAX5930A status output polarity is selectable.

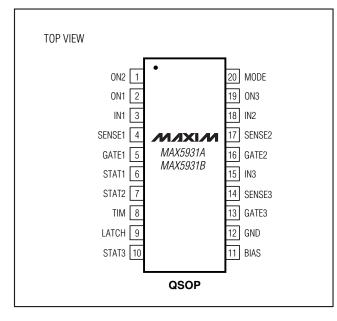

The MAX5930A is available in a 24-pin QSOP package, and the MAX5931A/MAX5931B are available in a 20-pin QSOP package. All devices are specified over the extended -40°C to  $+85^{\circ}$ C temperature range.

#### **Applications**

| Network Switches, Routers,<br>Hubs | Power-Supply<br>Sequencing/Tracking |

|------------------------------------|-------------------------------------|

| Hot Plug-In Daughter Cards         | Base-Station Line Cards             |

| RAID                               | Portable Computer Device            |

| Solid-State Circuit Breakers       | Bays (Docking Stations)             |

### \_Features

- Safe Hot Swap for +1V to +15V Power Supplies with Any Input Voltage (V<sub>IN</sub>) ≥ 2.7V

- Adjustable Circuit-Breaker/Current-Limit Threshold from 25mV to 100mV

- Configurable Tracking, Sequencing, or Independent Operation Modes

- VariableSpeed/BiLevel Circuit-Breaker Response

- Internal Charge Pumps Generate n-Channel MOSFET Gate Drives

- Inrush Current Regulated at Startup

- Autoretry or Latched Fault Management

- Programmable Undervoltage Lockout

- Status Outputs Indicate Fault/Safe Condition

### **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE |

|--------------|----------------|-------------|

| MAX5930AEEG+ | -40°C to +85°C | 24 QSOP     |

| MAX5931AEEP+ | -40°C to +85°C | 20 QSOP     |

| MAX5931BEEP+ | -40°C to +85°C | 20 QSOP     |

|              |                |             |

+Denotes a lead-free/RoHS-compliant package.

Selector Guide and Typical Operating Circuit appear at end of data sheet.

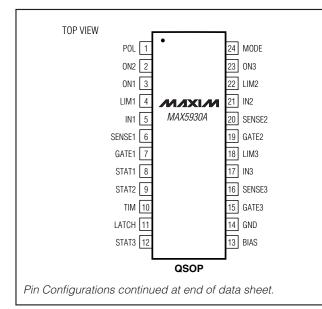

### **Pin Configurations**

VariableSpeed/BiLevel is a trademark of Maxim Integrated Products, Inc.

###

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages referenced to GND, unle | ess otherwise noted.)            |

|---------------------------------------|----------------------------------|

| ÎN                                    | 0.3V to +16V                     |

| GATE                                  | 0.3V to (IN_ + 6V)               |

| BIAS (Note 1)                         | (V <sub>IN</sub> - 0.3V) to +16V |

| ON_, STAT_, LIM_ (MAX5930A), TIM,     | , MODE,                          |

| LATCH, POL (MAX5930A)                 | 0.3V to (V <sub>IN</sub> + 0.3V) |

| SENSE                                 | 0.3V to (IN_ + 0.3V)             |

| Current into Any Pin                  | ±50mA                            |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

|-------------------------------------------------------|

| 20-Pin QSOP (derate 9.1mW/°C above +70°C)727mW        |

| 24-Pin QSOP (derate 9.5mW/°C above +70°C)762mW        |

| Operating Temperature Range40°C to +85°C              |

| Junction Temperature+150°C                            |

| Storage Temperature Range65°C to +150°C               |

| Lead Temperature (soldering, 10s)+300°C               |

Note 1:  $V_{IN}$  is the largest of  $V_{IN1}$ ,  $V_{IN2}$ , and  $V_{IN3}$ .

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = +1V \text{ to } +15V, \text{ provided at least one supply is larger than or equal to } +2.7V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } V_{IN1} = 12.0V, V_{IN2} = 5.0V, V_{IN3} = 3.3V, V_{ON} = +3.3V, \text{ and } T_A = +25^{\circ}C.) \text{ (Notes 1, 2)}$

| PARAMETER                                  | SYMBOL             | CONDITIONS                                                                              | MIN                                                   | ТҮР                       | МАХ  | UNITS |

|--------------------------------------------|--------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------|------|-------|

| POWER SUPPLIES                             |                    |                                                                                         | 1                                                     |                           |      |       |

| IN_ Input Voltage Range                    | V <sub>IN</sub> _  | At least one $V_{IN} \ge +2.7V$                                                         | 1.0                                                   |                           | 15   | V     |

| Supply Current                             | IQ                 | $I_{IN1} + I_{IN2} + I_{IN3}$ , $V_{ON} = 2.7V$ ,<br>$V_{IN} = +15V$ , after STAT_ high |                                                       | 2.5                       | 5    | mA    |

| CURRENT CONTROL                            |                    |                                                                                         |                                                       |                           |      |       |

|                                            |                    | LIM_ = GND (Note 4)                                                                     | 22.5                                                  | 25                        | 28   |       |

| Slow-Comparator Threshold                  | Veotu              | $R_{\text{LIM}} = 10 k\Omega (MAX5930A)$                                                | 80                                                    |                           | 125  | mV    |

| (VIN VSENSE_)<br>(Note 3)                  | VSC,TH             | R <sub>LIM</sub> from LIM_ to GND (MAX5930A)                                            | R <sub>LIM</sub> _ x 7.5 x<br>10 <sup>-6</sup> + 25mV |                           | 111V |       |

| Slow-Comparator Response Time              |                    | 1mV overdrive                                                                           |                                                       | 3                         |      | ms    |

| (Note 4)                                   | tSCD               | 50mV overdrive                                                                          |                                                       | 130                       |      | μs    |

| Fast-Comparator Threshold<br>(VIN VSENSE_) | V <sub>FC,TH</sub> |                                                                                         |                                                       | 2 x<br>V <sub>SC,TH</sub> |      | mV    |

| Fast-Comparator Response Time              | tFCD               | 10mV overdrive, from overload condition                                                 |                                                       | 200                       |      | ns    |

| SENSE_ Input Bias Current                  | IB SENSE_          | VSENSE_ = VIN_                                                                          |                                                       | 0.03                      | 1    | μA    |

| MOSFET DRIVER                              |                    |                                                                                         |                                                       |                           |      |       |

|                                            |                    | $R_{TIM} = 100 k\Omega$                                                                 | 8.0                                                   | 10.8                      | 13.6 |       |

| Startup Period (Note 5)                    | <sup>t</sup> START | $R_{TIM} = 4k\Omega$ (minimum value)                                                    | 0.30                                                  | 0.4                       | 0.55 | ms    |

|                                            |                    | TIM unconnected (default)                                                               | 5                                                     | 9                         | 14   |       |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = +1V \text{ to } +15V, \text{ provided at least one supply is larger than or equal to } +2.7V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } V_{IN1} = 12.0V, V_{IN2} = 5.0V, V_{IN3} = 3.3V, V_{ON} = +3.3V, \text{ and } T_A = +25^{\circ}C.) \text{ (Notes 1, 2)}$

| PARAMETER                               | SYMBOL              | CONDITIONS                                                                                                                                                                  | MIN  | ТҮР   | MAX  | UNITS |

|-----------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|

|                                         |                     | Charging, V <sub>GATE</sub> = GND, V <sub>IN</sub> = +5V<br>(Note 6)                                                                                                        | 80   | 100   | 125  | μA    |

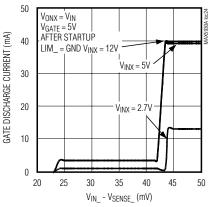

|                                         |                     | Discharging, during startup                                                                                                                                                 |      | 100   |      |       |

| Average Gate Current                    | IGATE               | Discharging, normal turn-off or triggered by the slow comparator after startup; $V_{GATE}$ = 5V, $V_{IN}$ = 10V, $V_{ON}$ = 0V                                              | 2    | 3     | 7    |       |

|                                         |                     | Discharging, triggered by a fault after<br>startup; V <sub>GATE</sub> = 5V, V <sub>IN</sub> = 10V, (V <sub>IN</sub> -<br>V <sub>SENSE</sub> ) > V <sub>FC,TH</sub> (Note 7) | 28   | 50    | 120  | • mA  |

| Gate-Drive Voltage                      | Vdrive              | $V_{GATE} - V_{IN}$ , $I_{GATE} = 1\mu A$                                                                                                                                   | 4.9  | 5.3   | 5.6  | V     |

| ON COMPARATOR                           |                     |                                                                                                                                                                             |      |       |      |       |

| ON_ Threshold                           | Volution            | Low to high                                                                                                                                                                 | 0.83 | 0.875 | 0.90 | V     |

| ON_ ITTESHOL                            | V <sub>ON_,TH</sub> | Hysteresis                                                                                                                                                                  |      | 25    |      | mV    |

| ON_ Propagation Delay                   |                     | 10mV overdrive                                                                                                                                                              |      | 10    |      | μs    |

| ON_ Voltage Range                       | V <sub>ON</sub> _   | Without false output inversion                                                                                                                                              |      |       | VIN  | V     |

| ON_ Input Bias Current                  | IBON                | $V_{ON} = V_{IN}$                                                                                                                                                           |      | 0.03  | 1    | μA    |

| ON_ Pulse-Width Low                     | <b>t</b> UNLATCH    | To unlatch after a latched fault                                                                                                                                            | 100  |       |      | μs    |

| DIGITAL OUTPUTS (STAT_)                 |                     |                                                                                                                                                                             |      |       |      |       |

| Output Leakage Current                  |                     | $V_{STAT} \leq 15V$                                                                                                                                                         |      |       | 1    | μA    |

| Output Voltage Low                      | V <sub>OL</sub> _   | POL = unconnected (MAX5930A),<br>I <sub>SINK</sub> = 1mA                                                                                                                    |      |       | 0.4  | V     |

| UNDERVOLTAGE LOCKOUT (L                 | JVLO)               |                                                                                                                                                                             |      |       |      |       |

| UVLO Threshold                          | Vuvlo               | Startup is initiated when this threshold is reached by any $V_{IN}$ and $V_{ON}$ > 0.9V (Note 8)                                                                            | 2.25 | 2.45  | 2.65 | V     |

| UVLO Hysteresis                         | VUVLO,HYST          |                                                                                                                                                                             |      | 250   |      | mV    |

| UVLO Glitch Filter Reset Time           | tD,GF               | $V_{IN} < V_{UVLO}$ maximum pulse width to reset                                                                                                                            |      |       | 10   | μs    |

| UVLO to Startup Delay                   | td,uvlo             | Time input voltage must exceed V <sub>UVLO</sub> before startup is initiated                                                                                                | 20   | 37.5  | 60   | ms    |

| Input Power-Ready Threshold             | VPWRRDY             | (Note 9)                                                                                                                                                                    | 0.9  | 0.95  | 1.0  | V     |

| Input Power-Ready Hysteresis            | VPWRHYST            |                                                                                                                                                                             |      | 50    |      | mV    |

| LOGIC AND TIMING                        |                     | •                                                                                                                                                                           |      |       |      |       |

| POL Input Pullup                        | IPOL                | POL = GND (MAX5930A)                                                                                                                                                        | 2    | 4     | 6    | μA    |

| LATCH Input Pullup                      | ILATCH              | LATCH = GND                                                                                                                                                                 | 2    | 4     | 6    | μA    |

| MODE Input Voltage                      | V <sub>MODE</sub>   | MODE unconnected (default to sequencing mode)                                                                                                                               | 1.0  | 1.25  | 1.5  | V     |

| Independent-Mode Selection<br>Threshold | VINDEP,TH           | V <sub>MODE</sub> rising                                                                                                                                                    |      |       | 0.4  | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = +1V \text{ to } +15V, \text{ provided at least one supply is larger than or equal to } +2.7V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } V_{IN1} = 12.0V, V_{IN2} = 5.0V, V_{IN3} = 3.3V, V_{ON} = +3.3V, \text{ and } T_A = +25^{\circ}\text{C}.) \text{ (Notes 1, 2)}$

| PARAMETER                            | SYMBOL             | CONDITIONS                                 | MIN | ТҮР            | МАХ | UNITS |

|--------------------------------------|--------------------|--------------------------------------------|-----|----------------|-----|-------|

| Tracking-Mode Selection<br>Threshold | Vtrack,th          | V <sub>MODE</sub> rising                   | 2.7 |                |     | V     |

| MODE Input Impedance                 | R <sub>MODE</sub>  |                                            |     | 200            |     | kΩ    |

| Autoretry Delay                      | <sup>t</sup> RETRY | Delay time to restart after fault shutdown |     | 64 x<br>tstart |     | ms    |

Note 2: All devices are 100% tested at T<sub>A</sub> = +85°C. Limits over temperature are guaranteed by design.

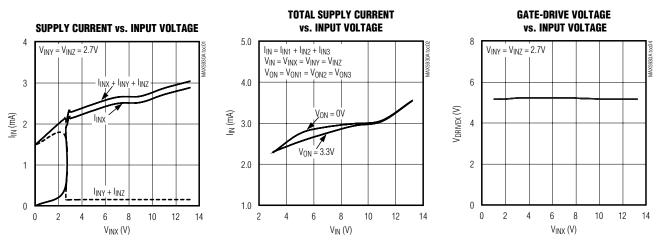

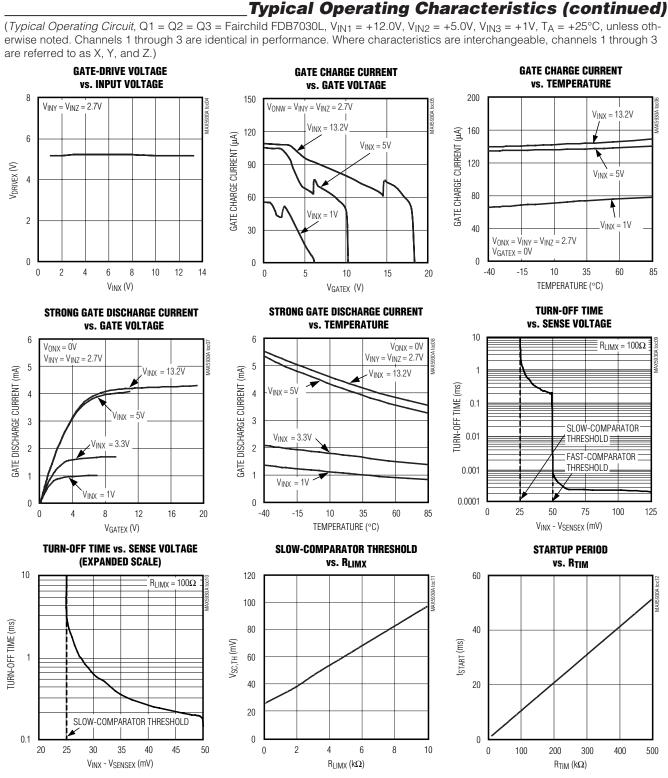

**Note 3:** The slow-comparator threshold is adjustable. V<sub>SC,TH</sub> = R<sub>LIM</sub> x 7.5µA + 25mV (see the *Typical Operating Characteristics* section).

**Note 4:** The current-limit slow-comparator response time is weighed against the amount of overcurrent, the higher the overcurrent condition, the faster the response time (see the *Typical Operating Characteristics* section).

**Note 5:** The startup period (t<sub>START</sub>) is the time during which the slow comparator is ignored and the device acts as a current-limiter by regulating the sense current with the fast comparator (see the *Startup Period* section).

Note 6: The current available at GATE is a function of V<sub>GATE</sub> (see the *Typical Operating Characteristics* section).

Note 7: After a fault triggered by the fast comparator, the gate is discharged by the strong discharge current.

**Note 8:** Each channel input while the other inputs are at +1V.

Note 9: Each channel input while any other input is at +3.3V.

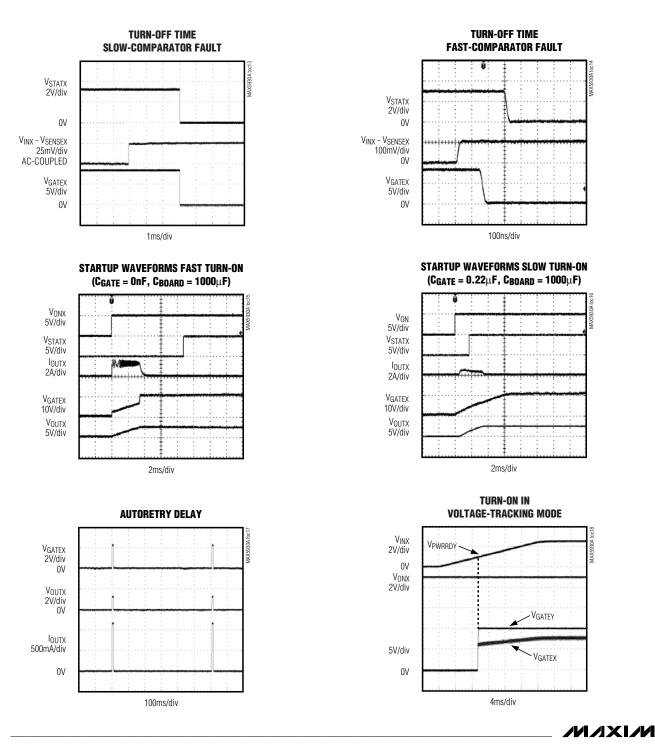

### **Typical Operating Characteristics**

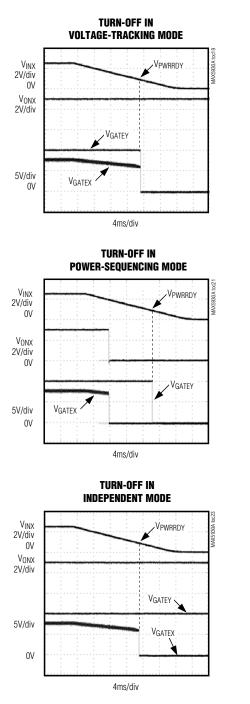

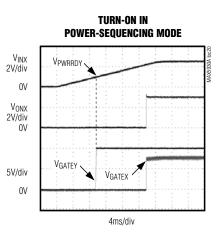

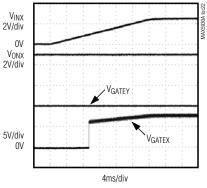

(*Typical Operating Circuit*, Q1 = Q2 = Q3 = Fairchild FDB7030L,  $V_{IN1} = +12.0V$ ,  $V_{IN2} = +5.0V$ ,  $V_{IN3} = +1V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted. Channels 1 through 3 are identical in performance. Where characteristics are interchangeable, channels 1 through 3 are referred to as X, Y, and Z.)

M/IXI/M

Turnia al Organizzatione Obarra atomiatica (a antinuo a

MAX5930A/MAX5931A/MAX59311

### **Typical Operating Characteristics (continued)**

(*Typical Operating Circuit*, Q1 = Q2 = Q3 = Fairchild FDB7030L,  $V_{IN1}$  = +12.0V,  $V_{IN2}$  = +5.0V,  $V_{IN3}$  = +1V,  $T_A$  = +25°C, unless otherwise noted. Channels 1 through 3 are identical in performance. Where characteristics are interchangeable, channels 1 through 3 are referred to as X, Y, and Z.)

6

### **Typical Operating Characteristics (continued)**

(*Typical Operating Circuit*, Q1 = Q2 = Q3 = Fairchild FDB7030L,  $V_{IN1}$  = +12.0V,  $V_{IN2}$  = +5.0V,  $V_{IN3}$  = +1V,  $T_A$  = +25°C, unless otherwise noted. Channels 1 through 3 are identical in performance. Where characteristics are interchangeable, channels 1 through 3 are referred to as X, Y, and Z.)

#### STRONG GATE DISCHARGE CURRENT vs. overdrive

### **Pin Description**

| PIN      |                       |        |                                                                                                                                                                                                             |

|----------|-----------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX5930A | MAX5931A/<br>MAX5931B | NAME   | FUNCTION                                                                                                                                                                                                    |

| 1        | _                     | POL    | STAT Output-Polarity Select. See Table 3 and the <i>Status Outputs (STAT_)</i> section.                                                                                                                     |

| 2        | 1                     | ON2    | On/Off Channel 2 Control Input. See the <i>Mode</i> section.                                                                                                                                                |

| 3        | 2                     | ON1    | On/Off Channel 1 Control Input. See the Mode section.                                                                                                                                                       |

| 4        | _                     | LIM1   | Channel 1 Current-Limit Setting. Connect a resistor from LIM1 to GND to set current-trip level. Connect to GND for the default 25mV threshold. Do not leave LIM1 unconnected.                               |

| 5        | 3                     | IN1    | Channel 1 Supply Input. Connect to a 1V to 15V supply voltage and to one end of R <sub>SENSE1</sub> . Bypass with a $0.1\mu$ F capacitor to ground.                                                         |

| 6        | 4                     | SENSE1 | Channel 1 Current-Sense Input. Connect SENSE1 to the drain of an external MOSFET and to one end of R <sub>SENSE1</sub> .                                                                                    |

| 7        | 5                     | GATE1  | Channel 1 Gate-Drive Output. Connect to the gate of the external n-channel MOSFET.                                                                                                                          |

| 8        | 6                     | STAT1  | Open-Drain Status Signal for Channel 1. STAT1 asserts when hot swap is successful and t <sub>START</sub> has elapsed. STAT1 deasserts if ON1 is low, or if channel 1 is turned off for any fault condition. |

| 9        | 7                     | STAT2  | Open-Drain Status Signal for Channel 2. STAT2 asserts when hot swap is successful and t <sub>START</sub> has elapsed. STAT2 deasserts if ON2 is low, or if channel 2 is turned off for any fault condition. |

| 10       | 8                     | TIM    | Startup Timer Setting. Connect a resistor from TIM to GND to set the startup period. Leave TIM unconnected for the default startup period of 9ms. $R_{TIM}$ must be between 4k $\Omega$ and 500k $\Omega$ . |

| 11       | 9                     | LATCH  | Latch/Autoretry Selection Input. Connect LATCH to GND for autoretry mode after a fault.<br>Leave LATCH unconnected for latch mode.                                                                          |

| 12       | 10                    | STAT3  | Open-Drain Status Signal for Channel 3. STAT3 asserts when hot swap is successful and t <sub>START</sub> has elapsed. STAT3 deasserts if ON3 is low, or if channel 3 is turned off for any fault condition. |

| 13       | 11                    | BIAS   | Supply Reference Output. The highest supply is available at BIAS for filtering. Connect a 1nF to 10nF ceramic capacitor from BIAS to GND. No other connections are allowed to BIAS.                         |

| 14       | 12                    | GND    | Ground                                                                                                                                                                                                      |

| 15       | 13                    | GATE3  | Channel 3 Gate-Drive Output. Connect to gate of external n-channel MOSFET.                                                                                                                                  |

| 16       | 14                    | SENSE3 | Channel 3 Current-Sense Input. Connect SENSE3 to the drain of an external MOSFET and to one end of R <sub>SENSE3</sub> .                                                                                    |

| 17       | 15                    | IN3    | Channel 3 Supply Input. Connect to a supply voltage from 1V to 15V and to one end of $R_{SENSE3}$ . Bypass with a 0.1µF capacitor to ground.                                                                |

| 18       | _                     | LIM3   | Channel 3 Current-Limit Setting. Connect a resistor from LIM3 to GND to set current-trip level. Connect to GND for the default 25mV threshold. Do not leave LIM3 unconnected.                               |

| 19       | 16                    | GATE2  | Channel 2 Gate-Drive Output. Connect to gate of external n-channel MOSFET.                                                                                                                                  |

| 20       | 17                    | SENSE2 | Channel 2 Current-Sense Input. Connect SENSE2 to the drain of an external MOSFET and to one end of R <sub>SENSE2</sub> .                                                                                    |

| 21       | 18                    | IN2    | Channel 2 Supply Input. Connect to a 1V to 15V supply voltage and to one end of R <sub>SENSE2</sub> . Bypass with a $0.1\mu$ F capacitor to ground.                                                         |

| 22       | _                     | LIM2   | Channel 2 Current-Limit Setting. Connect a resistor from LIM2 to GND to set current-trip level. Connect to GND for the default 25mV threshold. Do not leave LIM2 unconnected.                               |

M/IXI/M

### **Pin Description (continued)**

| P        | PIN                   |      |                                                                                                                                                                             |

|----------|-----------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX5930A | MAX5931A/<br>MAX5931B | NAME | FUNCTION                                                                                                                                                                    |

| 23       | 19                    | ON3  | On/Off Channel 3 Control Input. See the Mode section.                                                                                                                       |

| 24       | 20                    | MODE | Mode Configuration Input. Mode is configured according to Table 1 as soon as one of the IN_ voltages exceeds UVLO and before turning on OUT_ (see the <i>Mode</i> section). |

### **Detailed Description**

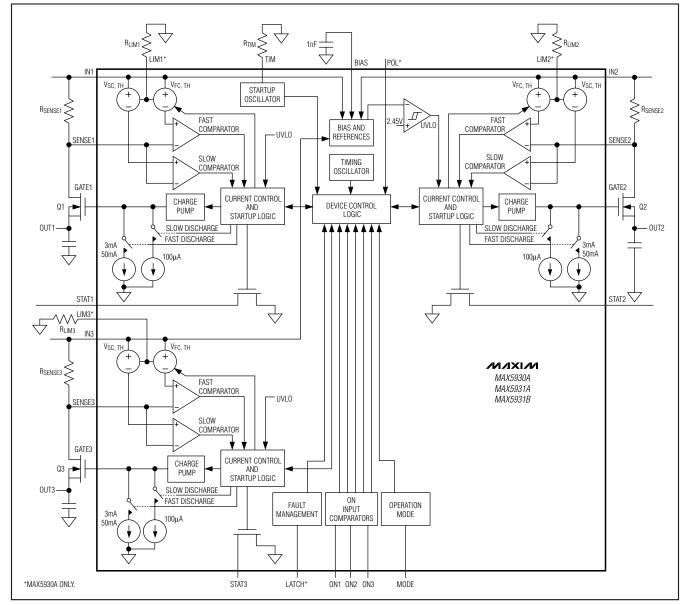

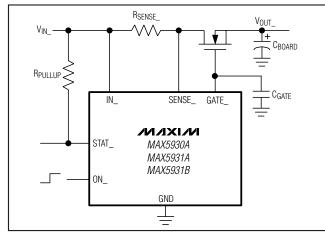

The MAX5930A/MAX5931A/MAX5931B are circuitbreaker ICs for hot-swap applications where a line card is inserted into a live backplane. The MAX5931A/ MAX5931B operate down to 1V provided one of the inputs is above 2.7V. Normally, when a line card is plugged into a live backplane, the card's discharged filter capacitors provide low impedance that can momentarily cause the main power supply to collapse. The MAX5930A/MAX5931A/MAX5931B reside either on the backplane or on the removable card to provide inrush current limiting and short-circuit protection. This is achieved by using external n-channel MOSFETs, external current-sense resistors, and on-chip comparators. The startup period and current-limit threshold of the MAX5930A/MAX5931A/MAX5931B can be adjusted with external resistors. Figure 1 shows the MAX5930A/ MAX5931A/MAX5931B functional diagram.

The MAX5930A offers three programmable current limits, selectable fault-management mode, and selectable STAT\_ output polarity. The MAX5930A features fixed current limits, selectable fault-management mode, and fixed STAT\_ output polarity.

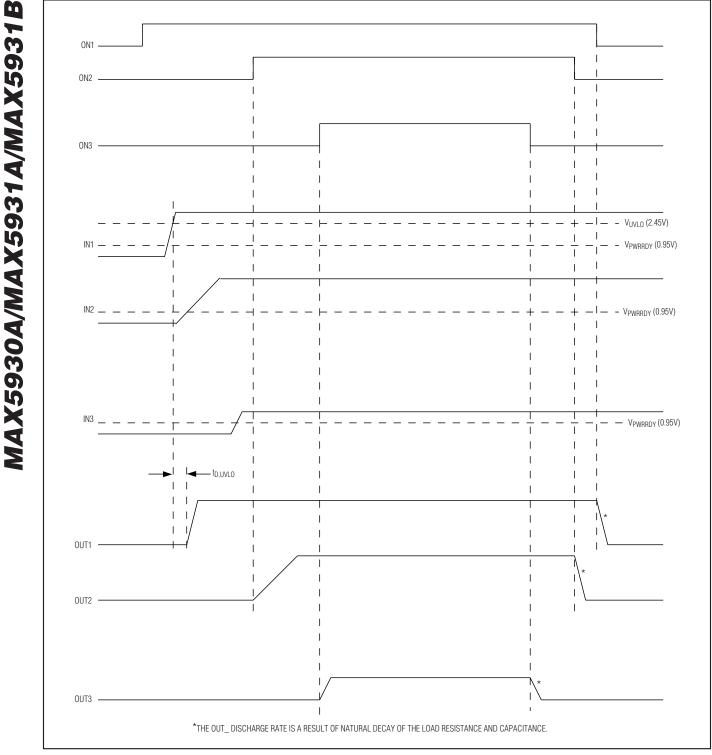

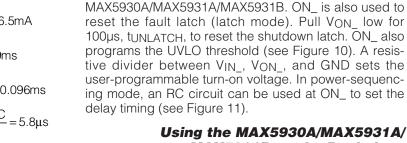

The MAX5930A/MAX5931A/MAX5931B support three modes of operation: voltage-tracking, power-sequencing, and independent mode. Select the appropriate mode according to Table 1.

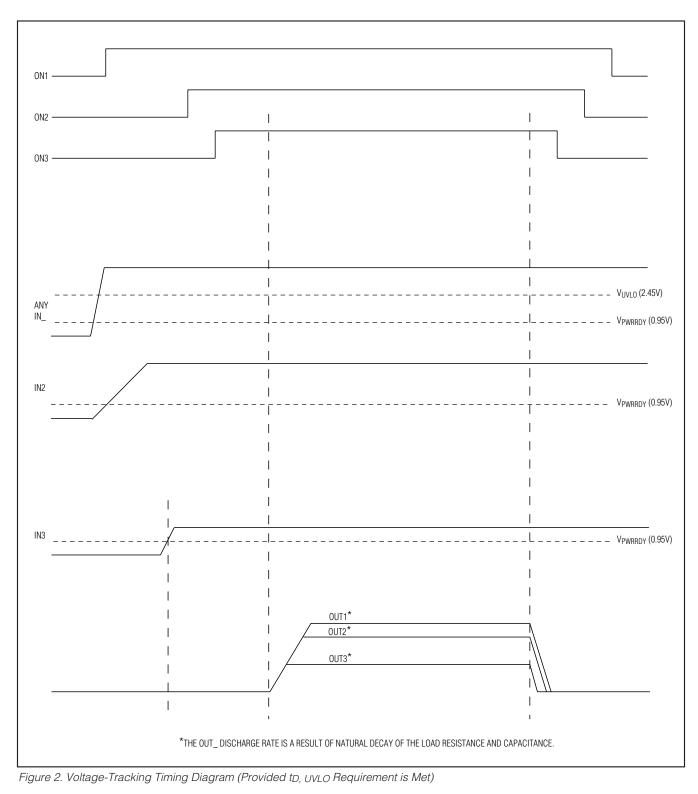

#### Voltage-Tracking Mode

Mode

Connect MODE high to enter voltage-tracking mode. While in voltage-tracking mode, all channels turn on and off together. To turn all channels on:

- At least one V<sub>IN</sub> must exceed V<sub>UVLO</sub> (2.45V) for the UVLO to startup delay (37.5ms).

- All V<sub>IN</sub>\_must exceed V<sub>PWRRDY</sub> (0.95V).

- All VON\_ must exceed VON,TH (0.875V).

- No faults may be present on any channel.

The MAX5930A/MAX5931A/MAX5931B turn off all channels if any of the above conditions are not met. After a fault-latched shutdown, cycle any of the ON\_ pins to unlatch and restart all channels.

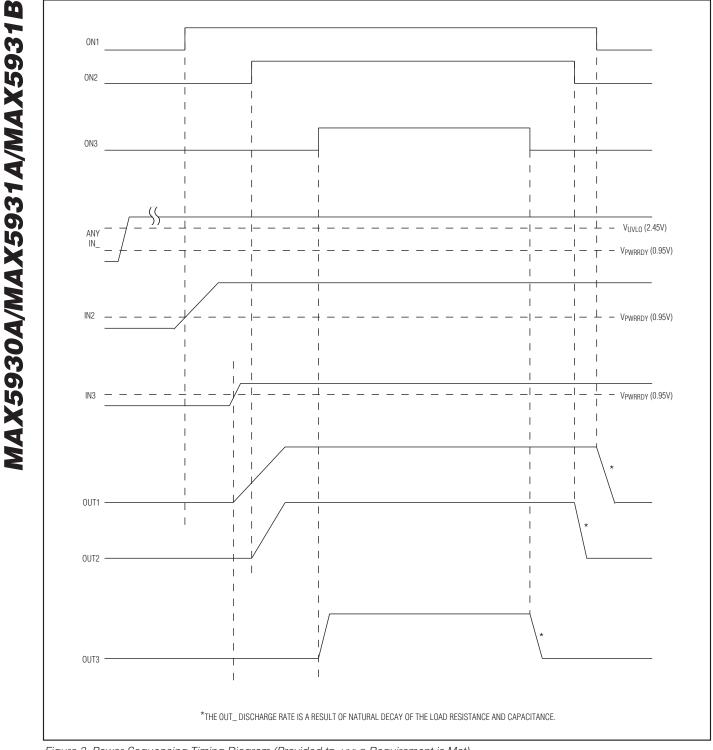

#### **Power-Sequencing Mode**

Leave MODE unconnected to enter power-sequencing mode. While in power-sequencing mode, the MAX5930A/MAX5931A/MAX5931B turn on and off each channel depending on the state of the corresponding V<sub>ON</sub>. To turn on a given channel:

- At least one V<sub>IN</sub> must exceed V<sub>UVLO</sub> (2.45V) for the UVLO to startup delay (37.5ms).

- All VIN\_ must exceed VPWRRDY (0.95V).

- The corresponding V<sub>ON</sub> must exceed V<sub>ON,TH</sub> (0.875V).

- No faults may be present on any channel.

The MAX5930A/MAX5931A/MAX5931B turn off all channels if any of the above conditions are not met. After a fault-latched shutdown, cycle any of the ON\_ inputs to unlatch and restart all channels, dependent on the corresponding  $V_{ON}$  state.

#### **Independent Mode**

Connect MODE to GND to enter independent mode. While in independent mode the MAX5930A/ MAX5931A/MAX5931B provide complete independent control for each channel. To turn on a given channel:

- At least one V<sub>IN</sub> must exceed V<sub>UVLO</sub> (2.45V) for the UVLO to startup delay (37.5ms).

- The corresponding  $V_{\text{IN}\_}$  must exceed  $V_{\text{PWRRDY}}$  (0.95V).

- The corresponding V<sub>ON</sub> must exceed V<sub>ON,TH</sub> (0.875V).

#### Table 1. Operational Mode Selection

| MODE                   | OPERATION          |

|------------------------|--------------------|

| High (Connect to BIAS) | Voltage Tracking   |

| Unconnected            | Voltage Sequencing |

| GND                    | Independent        |

///XI//

Figure 1. Functional Diagram

The MAX5930A/MAX5931A/MAX5931B turn off the corresponding channel if any of the above conditions are not met. During a fault condition on a given channel only, the affected channel is disabled. After a faultlatched shutdown, recycle the corresponding ON\_ inputs to unlatch and restart only the corresponding channel.

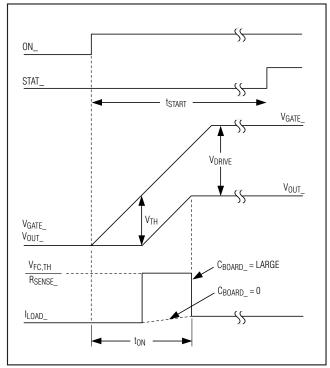

#### **Startup Period**

R<sub>TIM</sub> sets the duration of the startup period from 0.4ms (R<sub>TIM</sub> =  $4k\Omega$ ) to 51ms (R<sub>TIM</sub> =  $500k\Omega$ ) (see the *Setting the Startup Period*, *R<sub>TIM</sub>* section). The default startup period is fixed at 9ms when TIM is unconnected. The startup period begins after the turn-on conditions are met as described in the *Mode* section, and the device is not latched or in its autoretry delay (see the *Latched and Autoretry Fault Management* section).

MAX5930A/MAX5931A/MAX5931B

Figure 3. Power-Sequencing Timing Diagram (Provided tD, UVLO Requirement is Met)

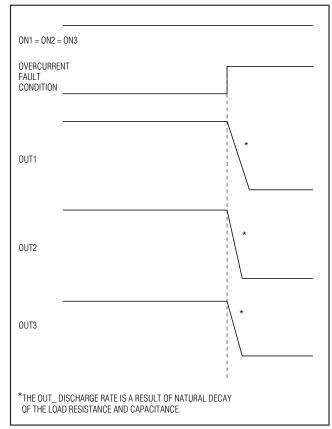

Figure 4. Power-Sequencing Fault Turn-Off

The MAX5930A/MAX5931A/MAX5931B limit the load current if an overcurrent fault occurs during startup instead of completely turning off the external MOSFETs. The slow comparator is disabled during the startup period and the load current can be limited in two ways:

- 1) Slowly enhancing the MOSFETs by limiting the MOSFET gate-charging current.

- 2) Limiting the voltage across the external currentsense resistor.

During the startup period, the gate-drive current is limited to 100µA and decreases with the increase of the gate voltage (see the *Typical Operating Characteristics* section). This allows the controller to slowly enhance the MOSFETs. If the fast comparator detects an overcurrent, the MAX5930A/MAX5931A/MAX5931B regulate the gate

voltage to ensure that the voltage across the sense resistor does not exceed  $V_{SU,TH}.$  This effectively regulates the inrush current during startup.

Figure 6 shows the startup waveforms. STAT\_ is asserted immediately after the startup period if no fault condition is present.

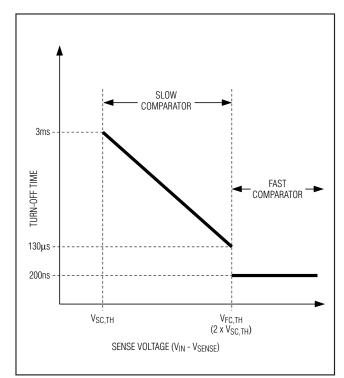

#### VariableSpeed/BiLevel Fault Protection

VariableSpeed/BiLevel fault protection incorporates comparators with different thresholds and response times to monitor the load current (Figure 7). During the startup period, protection is provided by limiting the load current. Protection is provided in normal operation (after the startup period has expired) by discharging the MOSFET gates with a strong 3mA/50mA pulldown current in response to a fault condition. After a fault, STAT\_ is deasserted. Use the LATCH input to control whether the STAT\_ outputs latch off or autoretry (see the Latched and Autoretry Fault Management section).

#### Slow-Comparator Startup Period

The slow comparator is disabled during the startup period while the external MOSFETs are turning on. Disabling the slow comparator allows the device to ignore the higher-than-normal inrush current charging the board capacitors when a card is first plugged into a live backplane.

#### Slow-Comparator Normal Operation

After the startup period is complete, the slow comparator is enabled and the device enters normal operation. The comparator threshold voltage (V<sub>SC,TH</sub>) is adjustable from 25mV to 100mV. The slow-comparator response time is 3ms for a 1mV overdrive. The response time decreases to 100µs with a large overdrive. The variable-speed response time allows the MAX5930A/MAX5931A/ MAX5931B to ignore low-amplitude momentary glitches, thus increasing system noise immunity. After an extended overcurrent condition, a fault is generated, STAT\_ outputs are deasserted and the MOSFET gates are discharged with a 3mA pulldown current.

#### Fast-Comparator Startup Period

During the startup period, the fast comparator regulates the gate voltages to ensure that the voltage across the sense resistor does not exceed the startup fast-comparator threshold voltage (V<sub>SU,TH</sub>), V<sub>SU,TH</sub> is scaled to two times the slow-comparator threshold (V<sub>SC,TH</sub>).

Figure 6. Independent-Mode Startup Waveforms

#### Fast-Comparator Normal Operation

In normal operation, if the load current reaches the fastcomparator threshold, a fault is generated, STAT\_ is deasserted, and the MOSFET gates are discharged with a strong 50mA pulldown current. This happens in the event of a serious current overload or a dead short. The fast-comparator threshold voltage (VFC,TH) is scaled to two times the slow-comparator threshold (VSC,TH). This comparator has a fast response time of 200ns (Figure 7).

#### **Undervoltage Lockout (UVLO)**

The UVLO prevents the MAX5930A/MAX5931A/ MAX5931B from turning on the external MOSFETs until one input voltage exceeds the UVLO threshold (2.45V) for t<sub>D,UVLO</sub>. The MAX5930A/MAX5931A/MAX5931B use power from the highest input voltage rail for the charge pumps. This allows for more efficient charge-pump operation. The highest V<sub>IN</sub> is provided as an output at BIAS. The UVLO protects the external MOSFETs from an insufficient gate-drive voltage. t<sub>D,UVLO</sub> ensures that the board is fully inserted into the backplane and that the input voltages are stable. The MAX5930A/MAX5931A/MAX5931B include a UVLO glitch filter (t<sub>D,GF</sub>) to reject all input voltage noise and transients. Bringing all input supplies

Figure 7. VariableSpeed/BiLevel Response

below the UVLO threshold for longer than  $t_{D,GF}$  reinitiates  $t_{D,UVLO}$  and the startup period,  $t_{START}$ . See Figure 8 for an example of automatic turn-on function.

#### **Latched and Autoretry Fault Management** The MAX5930A can be configured to latch the external MOSFETs off or to autoretry (see Table 2). Toggling

MOSFETS on or to autoretry (see Table 2). Togging ON\_ below 0.875V for at least 100 $\mu$ s clears the MAX5930A/MAX5931A/MAX5931B (LATCH = unconnected) fault and reinitiates the startup period. Similarly, the MAX5930A/MAX5931A/MAX5931B (LATCH = GND) turn the external MOSFETs off when an overcurrent fault is detected, then automatically restart after the autoretry delay that is internally set to 64 times tSTART.

#### Status Outputs (STAT\_)

The status (STAT\_) outputs are open-drain outputs that assert when hot swap is successful and  $t_{START}$  has elapsed. STAT\_ deasserts if ON\_ is low or if the channel is turned off for any fault condition.

The polarity of the STAT\_ outputs is selected using POL for the MAX5930A (see Table 3). Tables 4 and 5 contain the MAX5930A/MAX5931A/MAX5931B truth tables.

Table 2. Selecting Fault-ManagementMode (MAX5930A)

| LATCH       | FAULT MANAGEMENT                    |

|-------------|-------------------------------------|

| Unconnected | Fault condition latches MOSFETs off |

| Low         | Autoretry mode                      |

# Table 3. Selecting STAT\_ Polarity (MAX5930A)

| POL         | STAT_                     |

|-------------|---------------------------|

| Low         | Asserts low               |

| Unconnected | Asserts high (open-drain) |

### \_Applications Information

#### **Component Selection**

#### n-Channel MOSFETs

Select the external MOSFETs according to the application's current levels. Table 6 lists recommended components. The MOSFET's on-resistance (R<sub>DS(ON)</sub>) should be chosen low enough to have a minimum voltage drop at full load to limit the MOSFET power dissipation. High R<sub>DS(ON)</sub> causes output ripple if there is a pulsating load. Determine the device power rating to accommodate a short-circuit condition on the board at startup and when the device is in autoretry mode (see the MOSFET Thermal Considerations section).

Using these devices in latched mode allows the use of MOSFETs with lower power ratings. A MOSFET typically withstands single-shot pulses with higher dissipation than the specified package rating. Table 7 lists some recommended MOSFET manufacturers.

#### Sense Resistor

The slow-comparator threshold voltage is adjustable from 25mV to 100mV. Select a sense resistor that causes a drop equal to the slow-comparator threshold voltage at a current level above the maximum normal operating current. Typically, set the overload current at 1.2 to 1.5 times the full load current. The fast-comparator threshold is two times the slow-comparator threshold in normal operating mode. Choose the senseresistor power rating to be greater than or equal to 2 x (IOVERLOAD) x VSC,TH. Table 7 lists some recommended sense-resistor manufacturers.

Figure 8. Automatic Turn-On When Input Voltages are Above their Respective Undervoltage Lockout Threshold (Provided t<sub>D,UVLO</sub> Requirement is Met)

Slow-Comparator Threshold, RLIM (MAX5930A) The slow-comparator threshold voltage is adjustable from 25mV to 100mV, allowing designers to fine-tune the current-limit threshold for use with standard-value sense resistors. Low slow-comparator thresholds allow for increased efficiency by reducing the power dissipated by the sense resistor. Furthermore, the low 25mV slow-comparator threshold is beneficial when operating with supply rails down to 1V because it allows a small percentage of the overall output voltage to be used for current sensing. The VariableSpeed/BiLevel fault protection feature offers inherent system immunity against load transients and noise. This allows the slow-comparator threshold to be set close to the maximum normal operating level without experiencing nuisance faults. To adjust the slow-comparator threshold, calculate RLIM as follows:

$$R_{LIM} = \frac{V_{TH} - 25mV}{7.5\mu A}$$

where V<sub>TH</sub> is the desired slow-comparator threshold voltage. Shorting LIM\_ to GND sets V<sub>TH</sub> to 25mV. Do not leave LIM\_ unconnected.

| PART                            | CHANNEL 1<br>FAULT | CHANNEL 2<br>FAULT | CHANNEL 3<br>FAULT | STAT1/<br>GATE1* | STAT2/<br>GATE2* | STAT3/<br>GATE3* |

|---------------------------------|--------------------|--------------------|--------------------|------------------|------------------|------------------|

| MAX5930A (POL = 1),<br>MAX5931B | Yes                | Х                  | Х                  | L/OFF            | L/OFF            | L/OFF            |

|                                 | Х                  | Yes                | Х                  | L/OFF            | L/OFF            | L/OFF            |

|                                 | Х                  | Х                  | Yes                | L/OFF            | L/OFF            | L/OFF            |

|                                 | Х                  | Х                  | Х                  | L/OFF            | L/OFF            | L/OFF            |

|                                 | No                 | No                 | No                 | H/ON             | H/ON             | H/ON             |

| MAX5930A (POL = 0),<br>MAX5931A | Yes                | Х                  | Х                  | H/OFF            | H/OFF            | H/OFF            |

|                                 | Х                  | Yes                | Х                  | H/OFF            | H/OFF            | H/OFF            |

|                                 | Х                  | Х                  | Yes                | H/OFF            | H/OFF            | H/OFF            |

|                                 | Х                  | Х                  | Х                  | H/OFF            | H/OFF            | H/OFF            |

|                                 | No                 | No                 | No                 | L/ON             | L/ON             | L/ON             |

### Table 4. Status Output Truth Table: Voltage-Tracking and Power-Sequencing Modes

\*L = Low, H = High.

### Table 5. Status Output Truth Table: Independent Mode

| CHANNEL 1<br>FAULT | CHANNEL 2<br>FAULT | CHANNEL 3<br>FAULT | STAT1/<br>GATE1 | STAT2/<br>GATE2 | STAT3/<br>GATE3 |

|--------------------|--------------------|--------------------|-----------------|-----------------|-----------------|

| Yes                | Yes                | Yes                | Unasserted/OFF  | Unasserted/OFF  | Unasserted/OFF  |

| Yes                | Yes                | No                 | Unasserted/OFF  | Unasserted/OFF  | Asserted/ON     |

| Yes                | No                 | Yes                | Unasserted/OFF  | Asserted/ON     | Unasserted/OFF  |

| Yes                | No                 | No                 | Unasserted/OFF  | Asserted/ON     | Asserted/ON     |

| No                 | Yes                | Yes                | Asserted/ON     | Unasserted/OFF  | Unasserted/OFF  |

| No                 | Yes                | No                 | Asserted/ON     | Unasserted/OFF  | Asserted/ON     |

| No                 | No                 | Yes                | Asserted/ON     | Asserted/ON     | Unasserted/OFF  |

| No                 | No                 | No                 | Asserted/ON     | Asserted/ON     | Asserted/ON     |

*Note:* STAT\_ is asserted when hot swap is successful and t<sub>ON</sub> has elapsed. STAT\_ is unasserted during a fault.

Table 6. Recommended n-Channel MOSFETs

| PART NUMBER  | MANUFACTURER             | DESCRIPTION                                |

|--------------|--------------------------|--------------------------------------------|

| FDB8030L     |                          | 10mΩ, 8-pin SO, 30V                        |

| FDC653N      | Fairchild Semiconductor  | 55mΩ, SuperSOT-6, 30V, 5A                  |

| FDS6670A     |                          | $3.5m\Omega$ , D <sup>2</sup> PAK, 30V     |

| FDS6692A     |                          | 14mΩ, 8-pin SO, 30V                        |

| IRF6635TRPBF |                          | 1.8mΩ, DirectFET MX, 30V                   |

| IRF7413      | International Rectifier  | 11mΩ, 8-pin SO, 30V                        |

| IRF7401      |                          | 22mΩ, 8-pin SO, 20V                        |

| IRF7805ZPBF  |                          | 7mΩ, 8-pin SO, 30V                         |

| NTMS4N01R2G  | ON Semiconductor         | 40mΩ, 8-pin SO, 20V                        |

| NTB75N06L    | ON Semiconductor         | 11m $\Omega$ , D <sup>2</sup> PAK, 60V     |

| НАТ2099Н     | Renesas Technology Corp. | 5m $\Omega$ , 8-pin SO (thermal land), 30V |

#### Table 7. Component Manufacturers

| COMPONENT       | MANUFACTURER            | PHONE        | WEBSITE               |

|-----------------|-------------------------|--------------|-----------------------|

| Sense Resistors | Vishay                  | 402-563-6325 | www.vishay.com        |

| Sense Resistors | IRC, Inc.               | 361-992-7900 | www.irctt.com         |

|                 | Fairchild Semiconductor | 888-522-5372 | www.fairchildsemi.com |

| MOSFETs         | International Rectifier | 310-322-3331 | www.irf.com           |

|                 | ON Semiconductor        | 602-244-6600 | www.onsemi.com        |

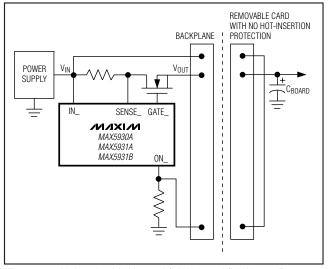

#### Setting the Startup Period, RTIM

The startup period (t<sub>START</sub>) is adjustable from 0.4ms to 50ms. The adjustable startup period feature allows systems to be customized for MOSFET gate capacitance and board capacitance (C<sub>BOARD</sub>). The startup period is adjusted with a resistor connected from TIM to GND (R<sub>TIM</sub>). R<sub>TIM</sub> must be between 4k $\Omega$  and 500k $\Omega$ . The startup period has a default value of 9ms when TIM is left unconnected. Calculate R<sub>TIM</sub> with the following equation:

$$R_{TIM} = \frac{t_{START}}{128 \times 800 pF}$$

where tSTART is the desired startup period.

#### **Startup Sequence**

There are two ways of completing the startup sequence. **Case A** describes a startup sequence that slowly turns on the MOSFETs by limiting the gate charge. **Case B** uses the current-limiting feature and turns on the MOSFETs as fast as possible while still preventing a high inrush current. The output voltage ramp-up time (t<sub>ON</sub>) is determined by the longer of the two timings, case A and case B. Set the startup timer (t<sub>START</sub>) to be longer than t<sub>ON</sub> to guarantee enough time for the output voltage to settle.

#### Case A: Slow Turn-On (Without Current Limit)

There are two ways to turn on the MOSFETs without reaching the fast-comparator current limit:

- If the board capacitance (CBOARD) is small, the inrush current is low.

- If the gate capacitance is high, the MOSFETs turn on slowly.

In both cases, the turn-on time is determined only by the charge required to enhance the MOSFET. The small 100 $\mu$ A gate-charging current effectively limits the output voltage dV/dt. Connecting an external capacitor between GATE and GND extends the turnon time. The time required to charge/discharge a MOSFET is as follows:

# $t = \frac{C_{GATE} \times \Delta V_{GATE} + Q_{GATE}}{I_{GATE}}$

#### where:

$C_{\mbox{GATE}}$  is the external gate to ground capacitance (Figure 9),

$\Delta V_{GATE}$  is the change in gate charge,

QGATE is the MOSFET total gate charge,

IGATE is the gate-charging/discharging current.

In this case, the inrush current depends on the MOSFET gate-to-drain capacitance (C<sub>RSS</sub>) plus any additional capacitance from GATE to GND (C<sub>GATE</sub>), and on any load current ( $I_{LOAD}$ ) present during the startup period.

$$I_{\text{INRUSH}} = \frac{C_{\text{BOARD}}}{C_{\text{RSS}} + C_{\text{GATE}}} \times I_{\text{GATE}} + I_{\text{LOAD}}$$

## Example: Charging and discharging times using the Fairchild FDB7030L MOSFET

If V<sub>IN1</sub> = 5V then GATE1 charges up to 10.4V (V<sub>IN1</sub> + V<sub>DRIVE</sub>), therefore  $\Delta$ V<sub>GATE</sub> = 10.4V. The manufacturer's data sheet specifies that the FDB7030L has approximately 60nC of gate charge and C<sub>RSS</sub> = 600pF. The MAX5930A/MAX5931A/MAX5931B have a 100µA gate charging current and a 3mA/50mA normal/strong discharging current. C<sub>BOARD</sub> = 6µF and the load does not draw any current during the startup period. With no gate capacitor, the inrush current, charge, and discharge times are:

$I_{\text{INRUSH}} = \frac{6\mu\text{F}}{600\text{pF}+0} \times 100\mu\text{A} + 0 = 1\text{A}$  $t_{\text{CHARGE}} = \frac{0 \times 10.4\text{V} + 60\text{nC}}{100\mu\text{A}} = 0.6\text{ms}$  $t_{\text{DISCHARGE(NORMAL)}} = \frac{0 \times 10.4\text{V} + 60\text{nC}}{3\text{mA}} = 0.02\text{ms}$  $t_{\text{DISCHARGE(STRONG)}} = \frac{0 \times 10.4\text{V} + 60\text{nC}}{50\text{mA}} = 1.2\mu\text{s}$

VIN

$R_1 \ge$

IN\_

ON\_

SENSE\_

M IXI M

MAX5930A

MAX5931A

MAX5931B

Figure 10. Adjustable Undervoltage Lockout

GATE\_

Figure 9. Operating with an External Gate Capacitor

With a 22nF gate capacitor, the inrush current, charge, and discharge times are:

6µF  $I_{\text{INRUSH}} = \frac{0\mu\Gamma}{600\rho\text{F} + 22\text{nF}} \times 100\mu\text{A} + 0 = 26.5\text{mA}$  $t_{CHARGE} = \frac{22nF \times 10.4V + 60nC}{100\mu A} = 2.89ms$ 100µA  $\frac{22nF \times 10.4V + 60nC}{0.096ms} = 0.096ms$ tDISCHARGE(NORMAL) = 3mA  $\frac{22nF \times 10.4V + 60nC}{5.8\mu s} = 5.8\mu s$  $t_{DISCHARGE(STRONG)} =$ 50mA

#### Case B: Fast Turn-On (With Current Limit)

In applications where the board capacitance (CBOARD) is high, the inrush current causes a voltage drop across RSENSE that exceeds the startup fast-comparator threshold. The fast comparator regulates the voltage across the sense resistor to VFC.TH. This effectively regulates the inrush current during startup. In this case, the current charging CBOARD can be considered constant and the turn-on time is:

$$t_{ON} = \frac{C_{BOARD} \times V_{IN} \times R_{SENSE}}{V_{FCTH}}$$

The maximum inrush current in this case is:

$$INRUSH = \frac{V_{FC,TH}}{R_{SENSE}}$$

Figure 6 shows the waveforms and timing diagrams for a startup transient with current regulation (see the Typical Operating Characteristics section). When operating under this condition, an external gate capacitor is not required.

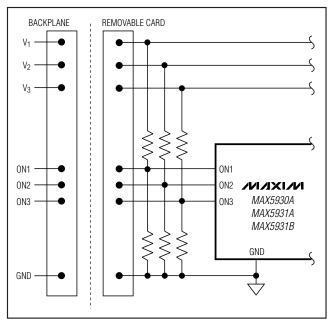

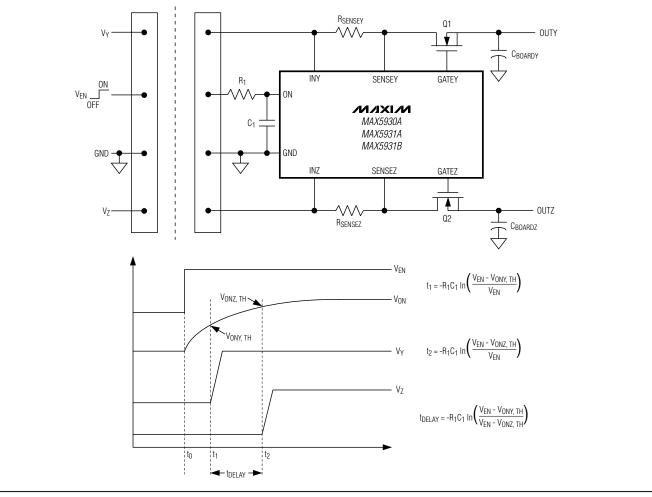

#### Using the MAX5930A/MAX5931A/ MAX5931B on the Backplane

Using the MAX5930A/MAX5931A/MAX5931B on the backplane allows multiple cards with different input capacitance to be inserted into the same slot even if the card does not have on-board hot-swap protection. The startup period can be triggered if IN is connected to ON through a trace on the card (Figure 12).

The ON comparators control the on/off function of the

#### **Input Transients**

V<sub>TURN-ON</sub> - (R<sub>2</sub> x R<sub>1</sub>) V<sub>ON</sub>, <sub>TH</sub>

**ON Comparators**

R<sub>2</sub>

The voltage at IN1, IN2, or IN3 must be above VIIVIO during inrush and fault conditions. When a short-circuit condition occurs on the board, the fast-comparator trips cause the external MOSFET gates to be discharged at 50mA according to the mode of operation (see the Mode section). The main system power supply must be able to sustain a temporary fault current, without dropping below the UVLO threshold of 2.45V, until the external MOSFET is completely off. If the main system power supply collapses below UVLO, the MAX5930A/MAX5931A/MAX5931B force the device to restart once the supply has recovered. The MOSFET is turned off in a very short time resulting in a high di/dt. The backplane delivering the power to the external card must have low inductance to minimize voltage transients caused by this high di/dt.

Figure 11. Power Sequencing: Channel Z Turns On t<sub>DELAY</sub> After Channel Y

#### **MOSFET Thermal Considerations**

During normal operation, the external MOSFETs dissipate little power. The MOSFET  $R_{DS}(ON)$  is low when the MOSFET is fully enhanced. The power dissipated in normal operation is  $P_D = I_{LOAD}^2 \times R_{DS}(ON)$ . The most power dissipation occurs during the turn-on and turn-off transients when the MOSFETs are in their linear regions. By taking into consideration the worst-case scenario of a continuous short-circuit fault, consider these two cases:

The single turn-on with the device latched after a fault: MAX5930A/MAX5931A/MAX5931B (LATCH = high or unconnected).  The continuous autoretry after a fault: MAX5930A/ MAX5931A/MAX5931B (LATCH = low).

MOSFET manufacturers typically include the package thermal resistance from junction to ambient ( $R_{\theta JA}$ ) and thermal resistance from junction to case ( $R_{\theta JC}$ ), which determine the startup time and the retry duty cycle (d = tstart/(tstart + tretry). Calculate the required transient thermal resistance with the following equation:

$$Z_{\theta JA(MAX)} \leq \frac{T_{JMAX} - T_A}{V_{IN} \times I_{START}}$$

where  $I_{START} = V_{SU,TH}/R_{SENSE}$ .

Figure 12. Using the MAX5930A/MAX5931A/MAX5931B on a Backplane

#### Layout Considerations

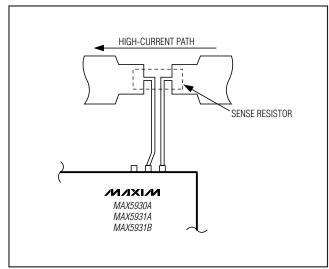

To take full tracking advantage of the switch response time to an output fault condition, it is important to keep all traces as short as possible and to maximize the high-current trace dimensions to reduce the effect of undesirable parasitic inductance. Place the MAX5930A/ MAX5931A/MAX5931B close to the card's connector. Use a ground plane to minimize impedance and inductance. Minimize the current-sense resistor trace length (<10mm), and ensure accurate current sensing with Kelvin connections (Figure 13).

Figure 13. Kelvin Connection for the Current-Sense Resistors

When the output is short circuited, the voltage drop across the external MOSFET becomes large. Hence, the power dissipation across the switch increases, as does the die temperature. An efficient way to achieve good power dissipation on a surface-mount package is to lay out two copper pads directly under the MOSFET package on both sides of the board. Connect the two pads to the ground plane through vias, and use enlarged copper mounting pads on the topside of the board.

### Selector Guide

| PART         | CURRENT LIMIT | FAULT MANAGEMENT | STAT_ POLARITY             |

|--------------|---------------|------------------|----------------------------|

| MAX5930AEEG+ | Programmable  | Selectable       | Selectable                 |

| MAX5931AEEP+ | Fixed         | Selectable       | Asserted Low               |

| MAX5931BEEP+ | Fixed         | Selectable       | Asserted High (Open-Drain) |

### **Pin Configurations (continued)**

Chip Information

PROCESS: BiCMOS

### Package Information

For the latest package outline information and land patterns, go to **www.maxim-ic.com/packages**.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 20 QSOP      | E20-1        | <u>21-0055</u> |

| 24 QSOP      | E24-1        | <u>21-0055</u> |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_

is a registered trademark of Maxim Integrated Products, Inc.

23

## **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated:

MAX5930AEEG+ MAX5930AEEG+T MAX5931AEEP+ MAX5931AEEP+T MAX5931BEEP+ MAX5931BEEP+T