### **MAX32000**

# High-Speed Quad Driver with Integrated DACs, Cable-Droop Compensation, Slew-Rate Control, and VHH Fourth-Level Drive

### **General Description**

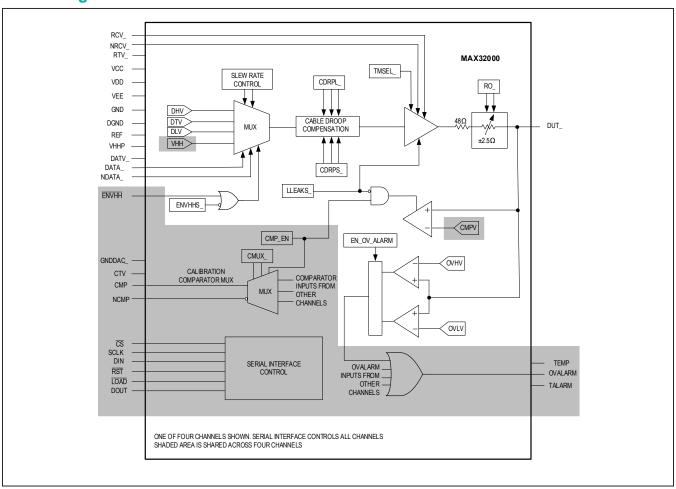

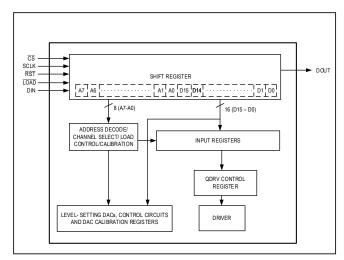

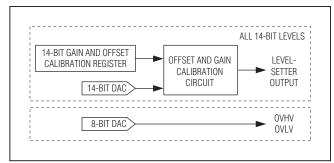

The MAX32000 is a fully integrated, quad-channel, high-performance pin-electronics driver with built-in level-setting DACs, ideal for memory and SOC ATE systems. Each MAX32000 channel includes a four-level pin driver, programmable cable-droop compensation, five 14-bit DACs, and a comparator that is useful for AC calibration.

The driver features a wide -2V to +6V operating range and a data rate of 1200Mbps at +2V operation, and in high-voltage mode (VHH mode) offers an output voltage range of 0 to 13V. The device includes high impedance, active termination (3rd-level drive), and is highly linear even at low voltage swings. The calibration comparators and multiplexer provide a timing calibration path for each channel. A serial interface configures the device, easing PCB signal routing.

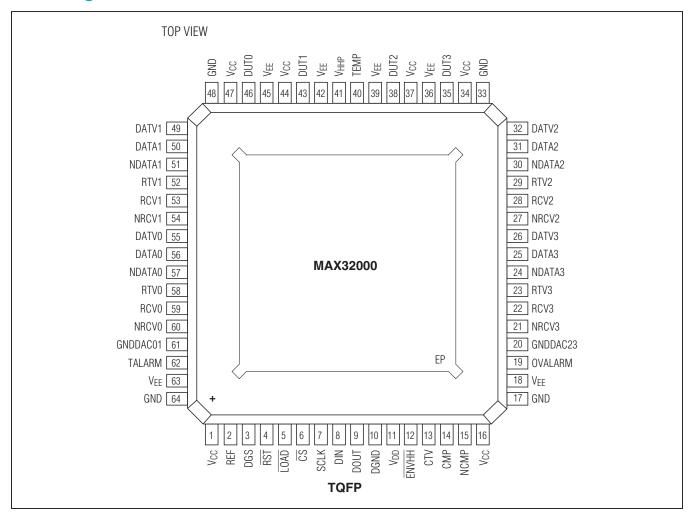

The MAX32000 is available in a 64-pin TQFP-EPR package with top-side exposed pad.

## **Applications**

- Memory Testers

- SOC Testers

- Digital Testers

- Discrete Component ATE

- Burn-In Testers

- Wafer Testers

#### **Benefits and Features**

- Low Power at High-Speed Maximizes Driver Performance

- 700mW per Channel

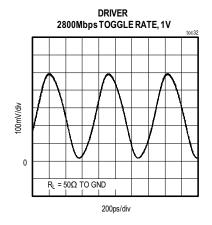

- 2.57Gbps at +1V Programmed

- 280ps Typical Rise/Fall Times at +2V (20% to 80%)

- · Very Low Timing Dispersion at 50ps Typical

- Wide Voltage Range from -2V to +6V

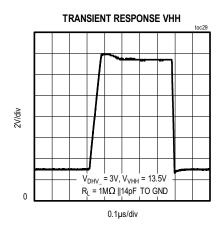

- Integrated VHH Programming Mode (4th-Level Drive) up to 13V

- 100nA Low-Leak Mode

- Integrated Functionality Provides Value-Added Features

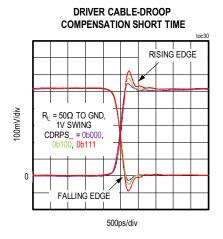

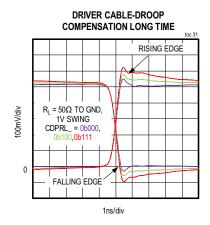

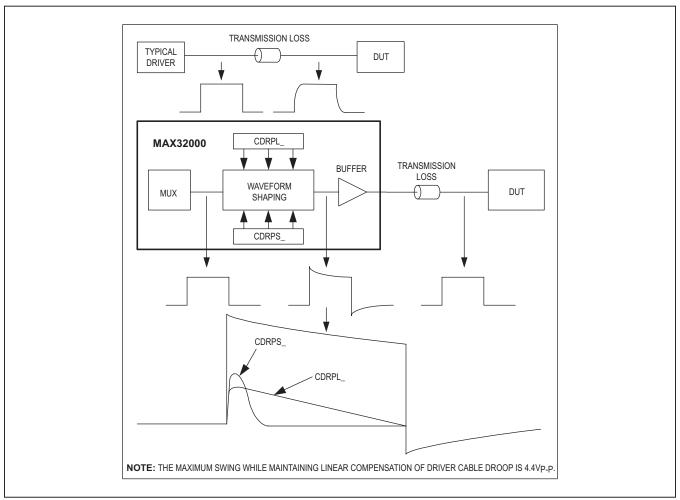

- Programmable Double Time Constant Cable-Droop Compensation

- Digital Slew-Rate Control for EMI-Sensitive Applications

- Adjustable Output Resistance with  $360m\Omega$  Resolution

- 22 DACs to Generate DC Voltage Levels for Control and Monitoring

- 50MHz SPI™ Interface

## **Ordering Information**

| PART         | TEMP RANGE   | PIN-PACKAGE |

|--------------|--------------|-------------|

| MAX32000CCB+ | 0°C to +70°C | 64 TQFP-EP* |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

SPI is a trademark of Motorola, Inc.

<sup>\*</sup>EP = Exposed pad.

## **Absolute Maximum Ratings**

| Vcc to GND                       | 0.3V to +11.0V                    |

|----------------------------------|-----------------------------------|

| VEE to GND                       | 6.0V to +0.3V                     |

| Any VCC to Any VEE               | +16.5V                            |

| V <sub>DD</sub> to DGND          | 0.3V to +5.0V                     |

| V <sub>HHP</sub> to GND          |                                   |

| DGND to GND                      |                                   |

| GNDDAC to GND                    |                                   |

| DGND to GNDDAC                   | ±0.3V                             |

| DGS to GND                       |                                   |

| CTV, DATV_, RTV_ to GND          | 0.3V to +5V                       |

| DATA_, NDATA_ to GND(VEE -       | 0.3V) to (V <sub>CC</sub> + 0.3V) |

| RCV_, NRCV_ to GND(VEE -         | 0.3V) to (Vcc + 0.3V)             |

| CMP, NCMP to GND (VCTV -         |                                   |

| Current into CMP, NCMP           |                                   |

| DATA_ to NDATA_, RCV_ to NRCV    | ±1V                               |

| DUT_ to GND                      |                                   |

| (all modes except VHH)(VEE -     | 0.3V) to (V <sub>CC</sub> + 0.3V) |

| DUT_ to GND (VHH mode)           |                                   |

| DUT to VEE                       |                                   |

| SCLK, DIN, CS, LOAD, RST to DGND |                                   |

| ENVHH to DGND0  OVALARM, TALARM to DGND0  TEMP to GND(VEE - 0 | $0.3V$ to $(V_{DD} + 0.3V)$<br>$0.3V$ ) to $(V_{CC} + 0.3V)$ |

|---------------------------------------------------------------|--------------------------------------------------------------|

| (GNDDAC + 2.6                                                 | V) and (Vcc + 0.3V)                                          |

| REF Current                                                   |                                                              |

| All Digital Inputs                                            | ±30mA                                                        |

| DUT_ Short-Circuit Duration                                   |                                                              |

| Continuous Power Dissipation                                  |                                                              |

| 64-Pin TQFP (derate 125mW/°C above +                          | -70°C)10.0W                                                  |

| Junction Temperature                                          | +150°C                                                       |

| Operating Junction Temperature Range                          | +40°C to +100°C                                              |

| Storage Temperature                                           | 65°C to +150°C                                               |

| Lead Temperature (soldering, 10s)                             | +300°C                                                       |

| Soldering Temperature (reflow)                                | +260°C                                                       |

| ESD, Human Body Model:                                        |                                                              |

| All Pins Excluding Below Pins                                 | 2.000V                                                       |

| ESD, Human Body Model: DATA_, NDATA_                          | 1.500V                                                       |

| ESD, Human Body Model: RCV_, NRCV_, DA                        |                                                              |

| Humidity                                                      | 10% to 90%                                                   |

|                                                               |                                                              |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Thermal Characteristics (Note 1)**

64 TQFP-EP

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ).......40°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ).............1°C/W

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{CC} = +9.25V, V_{EE} = -5.25V, V_{HHP} = +17.5V, V_{DD} = +3.3V, V_{DHV} = +3V, V_{DTV} = +1.5V, V_{DLV} = 0V, V_{DATV} = V_{RTV} = 0V, V_{CTV} = +1.2V, V_{CMPV} = +1V, V_{VHH} = +10V, CDRP_ = 000b, RO_ = 1110b, SC_ = 00b, V_{DGS} = V_{GND} = V_{GNDDAC} = 0V, specifications apply after calibration, level-setter errors included. The device is tested at T<sub>J</sub> = +70°C with an accuracy of <math>\pm 15$ °C; specification compliance with supply and temperature variations are verified by guardbanding mean shifts of characterized data, unless otherwise noted. Temperature coefficients are measured at T<sub>J</sub> = +40°C and +100°C, unless otherwise noted.)

| PARAMETER                      | SYMBOL                  | CONDITIONS                                                                              | MIN      | TYP | MAX  | UNITS |

|--------------------------------|-------------------------|-----------------------------------------------------------------------------------------|----------|-----|------|-------|

| DRIVER                         |                         |                                                                                         |          |     |      |       |

| DRIVER DC CHARACTERISTICS      | (R <sub>L</sub> ≥ 10MΩ, | unless otherwise noted, includes level-sette                                            | r error) |     |      |       |

| Output Voltage Range           | VDHV_                   | V <sub>DLV</sub> _ = -2.0V, V <sub>DTV</sub> _ = +1.5V                                  | -1.8     |     | +6.0 |       |

|                                | V <sub>DLV</sub> _      | V <sub>DHV</sub> _ = +6.0V, V <sub>DTV</sub> _ = +1.5V                                  | -2.0     |     | +5.8 | V     |

|                                | VDTV_                   | V <sub>DHV</sub> = +6.0V, V <sub>DLV</sub> = -2.0V                                      | -2.0     |     | +6.0 |       |

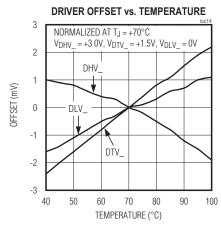

|                                | VDHV_OS                 | V <sub>DHV</sub> = +0.125V, V <sub>DLV</sub> = -2.0V,<br>V <sub>DTV</sub> = +1.5V       |          |     | ±2   |       |

| Output Offset Voltage (Note 2) | VDLV_OS                 | V <sub>DLV</sub> _ = +0.125V, V <sub>DHV</sub> _ = +6.0V,<br>V <sub>DTV</sub> _ = +1.5V |          |     | ±2   | mV    |

|                                | V <sub>DTV</sub> os     | V <sub>DTV</sub> _ = +0.125V, V <sub>DHV</sub> _ = +6.0V,<br>V <sub>DLV</sub> _ = -2.0V |          |     | ±2   |       |

## **Electrical Characteristics (continued)**

$(V_{CC} = +9.25V, V_{EE} = -5.25V, V_{HHP} = +17.5V, V_{DD} = +3.3V, V_{DHV} = +3V, V_{DTV} = +1.5V, V_{DLV} = 0V, V_{DATV} = V_{RTV} = 0V, V_{CTV} = +1.2V, V_{CMPV} = +1V, V_{VHH} = +10V, CDRP_ = 000b, RO_ = 1110b, SC_ = 00b, V_{DGS} = V_{GND} = V_{GNDDAC} = 0V, specifications apply after calibration, level-setter errors included. The device is tested at T<sub>J</sub> = +70°C with an accuracy of <math>\pm 15$ °C; specification compliance with supply and temperature variations are verified by guardbanding mean shifts of characterized data, unless otherwise noted. Temperature coefficients are measured at T<sub>J</sub> = +40°C and +100°C, unless otherwise noted.)

| PARAMETER                                           | SYMBOL               | CONDITIONS                                                                                      | MIN   | TYP   | MAX   | UNITS |

|-----------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

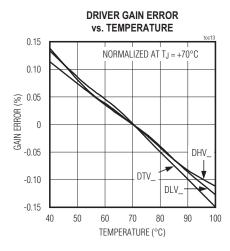

| O 1 - 1 \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \           | V <sub>DHV</sub> _TC |                                                                                                 |       | ±75   | ±500  |       |

| Output Voltage Temperature Coefficient (Notes 3, 4) | VDLV_TC              |                                                                                                 |       | ±75   | ±500  | μV/°C |

| Coefficient (Notes 5, 4)                            | V <sub>DTV</sub> _TC |                                                                                                 |       | ±75   | ±500  | 1     |

| Gain (Note 2)                                       | ADHV_                | V <sub>DLV</sub> = -2.0V, V <sub>DTV</sub> = +1.5V,<br>V <sub>DHV</sub> = +0.125V and +3.875V   | 0.999 | 1     | 1.001 |       |

|                                                     | ADLV_                | V <sub>DHV</sub> = +6.0V, V <sub>DTV</sub> = +1.5V,<br>V <sub>DLV</sub> = +0.125V and +3.875V   | 0.999 | 1     | 1.001 | V/V   |

|                                                     | ADTV_                | V <sub>DHV</sub> = +6.0V, V <sub>DLV</sub> = -2.0V,<br>V <sub>DTV</sub> = +0.125V and +3.875V   | 0.999 | 1     | 1.001 |       |

| Linearity Error, -0.5V to +4.5V (Note 2, 3)         |                      | V <sub>DLV</sub> = -2.0V, V <sub>DTV</sub> = +1.5V,<br>V <sub>DHV</sub> = -0.5V to +4.5V        |       | < ±6  |       | m\/   |

|                                                     |                      | V <sub>DLV</sub> = -2.0V, V <sub>DHV</sub> = +6.0V,<br>V <sub>DTV</sub> = -0.5V to +4.5V        |       | < ±6  |       | - mV  |

| Linearity Error, -1.75V to +5.125V (Note 2, 3)      |                      | V <sub>DLV</sub> = -2.0V, V <sub>DTV</sub> = +1.5V,<br>V <sub>DHV</sub> = -1.75V to +5.125V     |       | < ±12 |       |       |

|                                                     |                      | V <sub>DHV</sub> = +6.0V, V <sub>DTV</sub> = +1.5V,<br>V <sub>DLV</sub> = -1.75V to +5.125V     |       | < ±12 |       | mV    |

|                                                     |                      | V <sub>DLV</sub> = -2.0V, V <sub>DHV</sub> = +6.0V,<br>V <sub>DTV</sub> = -1.75V to +5.125V     |       | < ±12 |       |       |

|                                                     |                      | V <sub>DLV</sub> = -2.0V, V <sub>DTV</sub> = +1.5V,<br>V <sub>DHV</sub> = -1.8V to +6.0V        |       | < ±14 |       |       |

| Linearity Error, Full Range<br>(Note 2, 3)          |                      | V <sub>DHV</sub> = +6.0V, V <sub>DTV</sub> = +1.5V,<br>V <sub>DLV</sub> = -2.0V to +5.8V        |       | < ±14 |       | mV    |

|                                                     |                      | V <sub>DLV</sub> = -2.0V, V <sub>DHV</sub> = +6.0V,<br>V <sub>DTV</sub> = -2.0V to +6.0V        |       | < ±14 |       |       |

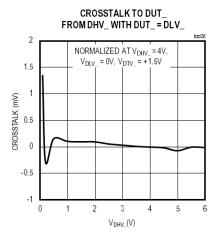

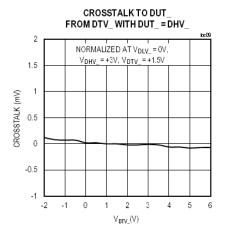

| DHVto-DLV_ Crosstalk                                |                      | V <sub>DLV</sub> = -0.5V, V <sub>DTV</sub> = +1.5V,<br>V <sub>DHV</sub> = -0.3V and +6.0V       |       |       | ±3    | mV    |

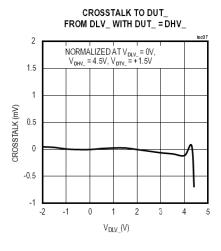

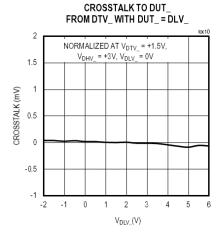

| DLVto-DHV_ Crosstalk                                |                      | V <sub>DHV</sub> _ = +4.5V, V <sub>DTV</sub> _ = +1.5V,<br>V <sub>DLV</sub> _ = -2.0V and +4.3V |       |       | ±3    | mV    |

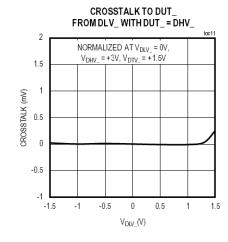

| DTVto-DLV_ and DHV_<br>Crosstalk                    |                      | V <sub>DHV</sub> _ = +3V, V <sub>DLV</sub> _ = 0V, V <sub>DTV</sub> _ = -2.0V<br>and +6.0V      |       |       | ±2    | mV    |

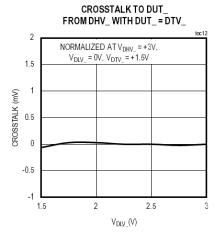

| DHVto-DTV_ Crosstalk                                |                      | $V_{DTV}$ = +1.5V, $V_{DLV}$ = 0V, $V_{DHV}$ = +1.6V and +3.0V                                  |       |       | ±3    | mV    |

| DLVto-DTV_ Crosstalk                                |                      | V <sub>DTV</sub> _ = +1.5V, V <sub>DHV</sub> _ = +3V, V <sub>DLV</sub> _ = 0V<br>and +1.4V      |       |       | ±3    | mV    |

## **Electrical Characteristics (continued)**

$(V_{CC} = +9.25V, V_{EE} = -5.25V, V_{HHP} = +17.5V, V_{DD} = +3.3V, V_{DHV} = +3V, V_{DTV} = +1.5V, V_{DLV} = 0V, V_{DATV} = V_{RTV} = 0V, V_{CTV} = +1.2V, V_{CMPV} = +1V, V_{VHH} = +10V, CDRP_ = 000b, RO_ = 1110b, SC_ = 00b, V_{DGS} = V_{GND} = V_{GNDDAC} = 0V, specifications apply after calibration, level-setter errors included. The device is tested at T<sub>J</sub> = +70°C with an accuracy of <math>\pm 15$ °C; specification compliance with supply and temperature variations are verified by guardbanding mean shifts of characterized data, unless otherwise noted. Temperature coefficients are measured at T<sub>J</sub> = +40°C and +100°C, unless otherwise noted.)

| PARAMETER                                               | SYMBOL                   |                                                           | CONDITIONS                                                                               | MIN  | TYP  | MAX  | UNITS |

|---------------------------------------------------------|--------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------|------|------|------|-------|

| Term Voltage Dependence on DATA_                        |                          | V <sub>DTV</sub> _ = +1.5V<br>DATA_ = high a              | $V_1$ , $V_{DHV}$ = +3 $V_1$ , $V_{DLV}$ = 0 $V_2$ , and low                             |      |      | ±2   | mV    |

|                                                         | PSRR <sub>DHV</sub>      | VDHV_ = +3V, varied full rang                             | VCC and VEE independently<br>e                                                           | 40   |      |      |       |

| DC Power-Supply Rejection                               | PSRR <sub>DLV</sub>      | V <sub>DLV</sub> = 0V, V <sub>0</sub><br>varied full rang | cc and VEE independently e                                                               | 40   |      |      | dB    |

|                                                         | PSRR <sub>DTV</sub>      | V <sub>DTV</sub> _ = +1.5V<br>varied full rang            | , V <sub>CC</sub> and V <sub>EE</sub> independently e                                    | 40   |      |      |       |

| DC Drive Current Limit                                  |                          | When DATA_ = VDUT_ = -2V                                  | = high , $V_{DHV}$ = +6.0V and                                                           | +65  |      | +110 | A     |

|                                                         |                          | When DATA_ = VDUT_ = +6V                                  | low, V <sub>DLV</sub> _ = -2.0V and                                                      | -110 |      | -65  | - mA  |

| DC Output Resistance                                    |                          | RO_ = 0b1000                                              | (Note 5)                                                                                 | 46   | 48   | 50   | Ω     |

| DC Output Resistance Variation (Note 6)                 |                          |                                                           | V <sub>DHV</sub> = +3V, V <sub>DLV</sub> = 0V,<br><sub>DUT</sub> = 1mA, 12mA, 40mA       |      | 1    | 2    |       |

|                                                         |                          |                                                           | / <sub>DHV_</sub> = +3V, V <sub>DLV_</sub> = 0V,<br><sub>DUT_</sub> = -1mA, -12mA, -40mA |      | 1    | 2    | Ω     |

| Adjustable Output Resistance<br>Range                   | DRO                      | RO_ = Fh vs. F<br>RO_ = 8h, reso<br>(see conditions       |                                                                                          |      | ±2.5 |      | Ω     |

| DRIVER AC CHARACTERISTICS                               | (R <sub>L</sub> = 50  to | GND) (Note 7)                                             |                                                                                          |      |      |      |       |

| Dynamic Drive Current                                   |                          | (Note 8)                                                  |                                                                                          |      | ±100 |      | mA    |

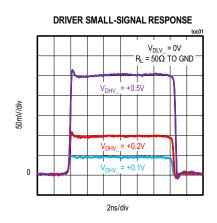

|                                                         |                          | 0.11                                                      | V <sub>DLV</sub> _ = 0V, V <sub>DHV</sub> _ = +0.1V                                      |      | 50   |      |       |

| Drive Mode Overshoot                                    |                          | Cable-droop compensation                                  | V <sub>DLV</sub> _ = 0V, V <sub>DHV</sub> _ = +1V                                        |      | 12   |      | - %   |

| Drive Wode Overshoot                                    |                          | off                                                       | V <sub>DLV</sub> _ = 0V, V <sub>DHV</sub> _ = +3V                                        |      | 3.3  |      | /0    |

|                                                         |                          |                                                           | V <sub>DLV</sub> = 0V, V <sub>DHV</sub> = +5V                                            |      | 2.0  |      |       |

|                                                         |                          | Cabla drass                                               | V <sub>DLV</sub> _ = 0V, V <sub>DHV</sub> _ = +0.1V                                      |      | 20   |      |       |

| Drive Mode Undershoot                                   |                          | Cable-droop compensation                                  | V <sub>DLV</sub> _ = 0V, V <sub>DHV</sub> _ = +1V                                        |      | 5    |      | - %   |

| Drive Wode Oridershoot                                  |                          | off                                                       | V <sub>DLV</sub> _ = 0V, V <sub>DHV</sub> _ = +3V                                        |      | 2.3  |      | /0    |

|                                                         |                          |                                                           | V <sub>DLV</sub> _ = 0V, V <sub>DHV</sub> _ = +5V                                        |      | 2.0  |      |       |

| Cable-Droop Compensation                                |                          | $V_{DLV} = 0V, V_{I}$                                     | DHV_ = +1V, CDRPS_ = 000                                                                 |      | 0    |      | %     |

| Range, Short Time Constant                              |                          | $V_{DLV} = 0V, V_{I}$                                     | DHV_ = +1V, CDRPS_ = 111                                                                 |      | 15   |      | /0    |

| Cable-Droop Compensation                                |                          | $V_{DLV} = 0V, V_{I}$                                     | OHV_ = +1V, CDRPL_ = 000                                                                 |      | 0    |      | - %   |

| Range, Long Time Constant                               |                          | $V_{DLV} = 0V, V_{I}$                                     | DHV_ = +1V, CDRPL_ = 111                                                                 |      | 15   |      | /0    |

| Driver Cable-Droop Compensation,<br>Short Time Constant |                          |                                                           |                                                                                          |      | 60   |      | ps    |

| Driver Cable-Droop Compensation,<br>Long Time Constant  |                          |                                                           |                                                                                          |      | 1.2  |      | ns    |

## **Electrical Characteristics (continued)**

$(V_{CC} = +9.25V, V_{EE} = -5.25V, V_{HHP} = +17.5V, V_{DD} = +3.3V, V_{DHV} = +3V, V_{DTV} = +1.5V, V_{DLV} = 0V, V_{DATV} = V_{RTV} = 0V, V_{CTV} = +1.2V, V_{CMPV} = +1V, V_{VHH} = +10V, CDRP_ = 000b, RO_ = 1110b, SC_ = 00b, V_{DGS} = V_{GND} = V_{GNDDAC} = 0V, specifications apply after calibration, level-setter errors included. The device is tested at T<sub>J</sub> = +70°C with an accuracy of <math>\pm 15$ °C; specification compliance with supply and temperature variations are verified by guardbanding mean shifts of characterized data, unless otherwise noted. Temperature coefficients are measured at T<sub>J</sub> = +40°C and +100°C, unless otherwise noted.)

| PARAMETER                                                                 | SYMBOL    | CONDITIONS                                                                                  | MIN | TYP   | MAX | UNITS |

|---------------------------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------|-----|-------|-----|-------|

|                                                                           |           | To within 100mV, V <sub>DHV</sub> = +5V, V <sub>DLV</sub> = 0V                              |     | 0.25  | 1   |       |

| Settling Time (Notes 4, 9)                                                |           | To within 50mV, VDHV_ = +3V, VDLV_ = 0V                                                     |     | 0.25  | 1   | ns    |

|                                                                           |           | To within 25mV, $V_{DHV} = +0.5V$ , $V_{DLV} = 0V$                                          |     | 0.25  | 1   |       |

| TIMING CHARACTERISTICS (Not                                               | es 7, 10) |                                                                                             |     |       |     |       |

| Propagation Delay, Data to Output                                         |           | V <sub>DHV</sub> _ = +3.0V, V <sub>DLV</sub> _ = 0V (Note 11)                               | 0.6 | 1.0   | 1.4 | ns    |

| Propagation-Delay Match,<br>tLH vs. tHL                                   |           | (Note 4)                                                                                    |     | ±40   | ±80 | ps    |

| Propagation-Delay Match, Drivers<br>Within Package                        |           | Same edge                                                                                   |     | 40    |     | ps    |

| Propagation-Delay Temperature<br>Coefficient                              |           | (Note 4)                                                                                    |     | 3     | 5   | ps/°C |

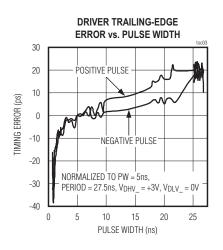

| Propagation-Delay Change vs. Pulse Width                                  |           | V <sub>DHV</sub> _ = +1V, V <sub>DLV</sub> _ = 0V, 0.85ns to 24.150ns pulse width (Note 4)  |     | ±25   | ±50 |       |

|                                                                           |           | V <sub>DHV</sub> = +3V, V <sub>DLV</sub> = 0V, 1.0ns to 24.0ns pulse width (Note 4)         |     | ±35   | ±60 | ps    |

|                                                                           |           | V <sub>DHV</sub> = +5V, V <sub>DLV</sub> = 0V, 1.5ns to 23.5ns pulse width                  |     | ±100  |     |       |

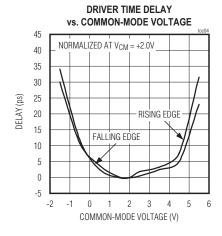

| Propagation-Delay Change vs.                                              |           | V <sub>DHV</sub> - V <sub>DLV</sub> = +1V, V <sub>DHV</sub> = +1V to +4V (using a DC block) |     | 50    | 60  |       |

| Common Mode (Note 4)                                                      |           | VDHV VDLV_ = +1V, VDHV_ = -1V to +6V (using a DC block)                                     |     | 50    | 100 | - ps  |

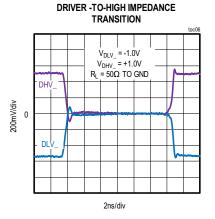

| Propagation Delay, Drive to High<br>Impedance, High Impedance to<br>Drive |           | V <sub>DHV</sub> _ = +1V, V <sub>DLV</sub> _ = -1V (Notes 4, 12)                            | 1.5 | 2.2   | 2.9 | ns    |

| Delay Match, Drive to High<br>Impedance vs. High Impedance<br>to Drive    |           | V <sub>DHV</sub> _ = +1V, V <sub>DLV</sub> _ = -1V (Note 13)                                |     | ±0.35 |     | ns    |

| Delay Match, High Impedance vs.<br>Data                                   |           | (Note 14)                                                                                   |     | 1.1   |     | ns    |

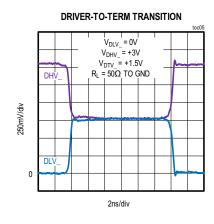

| Propagation Delay, Drive to Term,<br>Term to Drive                        |           | (Notes 4, 14)                                                                               | 1.7 | 2.5   | 3.4 | ns    |

| Delay Match, Drive to Term vs.<br>Term to Drive                           |           | V <sub>DHV</sub> = +3V, V <sub>DLV</sub> = 0V, V <sub>DTV</sub> = +1.5V<br>(Note 15)        |     | ±1    |     | ns    |

| Delay Match, Terminate vs. Data                                           |           | (Note 14)                                                                                   |     | 1.5   |     | ns    |

## **Electrical Characteristics (continued)**

$(V_{CC} = +9.25V, V_{EE} = -5.25V, V_{HHP} = +17.5V, V_{DD} = +3.3V, V_{DHV} = +3V, V_{DTV} = +1.5V, V_{DLV} = 0V, V_{DATV} = V_{RTV} = 0V, V_{CTV} = +1.2V, V_{CMPV} = +1V, V_{VHH} = +10V, CDRP_ = 000b, RO_ = 1110b, SC_ = 00b, V_{DGS} = V_{GND} = V_{GNDDAC} = 0V, specifications apply after calibration, level-setter errors included. The device is tested at T<sub>J</sub> = +70°C with an accuracy of <math>\pm 15$ °C; specification compliance with supply and temperature variations are verified by guardbanding mean shifts of characterized data, unless otherwise noted. Temperature coefficients are measured at T<sub>J</sub> = +40°C and +100°C, unless otherwise noted.)

| PARAMETER                                      | SYMBOL | CONDITIONS                                                                                                           | MIN | TYP | MAX  | UNITS |

|------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------|-----|-----|------|-------|

|                                                |        | 0.2V <sub>P-P</sub> programmed, V <sub>DHV</sub> = +0.2V, V <sub>DLV</sub> = 0V, 20% to 80% (Note 16)                |     | 140 |      |       |

|                                                |        | 0.2V <sub>P-P</sub> programmed, V <sub>DHV</sub> = +0.2V, V <sub>DLV</sub> = 0V, 20% to 80% (Note 17)                |     | 150 |      |       |

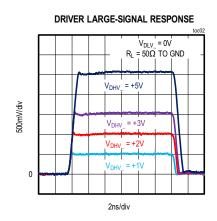

|                                                |        | 1V <sub>P-P</sub> programmed, V <sub>DHV</sub> = +1.0V,<br>V <sub>DLV</sub> = 0V, 10% to 90% (Notes 4, 16)           | 200 | 270 | 400  |       |

|                                                |        | 1V <sub>P-P</sub> programmed, V <sub>DHV</sub> = +1.0V,<br>V <sub>DLV</sub> = 0V, 10% to 90% (Note 17)               |     | 350 |      |       |

|                                                |        | 1V <sub>P-P</sub> programmed, V <sub>DHV</sub> = +1.0V,<br>V <sub>DLV</sub> = 0V, 20% to 80% (Notes 4, 16)           | 140 | 190 | 275  |       |

| Rise and Fall Time                             |        | 2V <sub>P-P</sub> programmed, V <sub>DHV</sub> = +2V,<br>V <sub>DLV</sub> = 0V, 20% to 80% (Notes 4, 16)             | 230 | 280 | 400  | ps    |

|                                                |        | 2V <sub>P-P</sub> programmed, V <sub>DHV</sub> = +2V,<br>V <sub>DLV</sub> = 0V, 20% to 80%, (Note 17)                |     | 300 |      |       |

|                                                |        | 3V <sub>P-P</sub> programmed, V <sub>DHV</sub> = +3V,<br>V <sub>DLV</sub> = 0V, 10% to 90%, trim condition (Note 16) | 425 | 550 | 800  |       |

|                                                |        | 3V <sub>P-P</sub> programmed, V <sub>DHV</sub> = +3V,<br>V <sub>DLV</sub> = 0V, 10% to 90% (Note 17)                 |     | 605 |      |       |

|                                                |        | 5V <sub>P-P</sub> programmed, V <sub>DHV</sub> = +5V,<br>V <sub>DLV</sub> = 0V, 10% to 90% (Notes 4, 16)             | 650 | 850 | 1050 |       |

|                                                |        | 5V <sub>P-P</sub> programmed, V <sub>DHV</sub> = +5V,<br>V <sub>DLV</sub> = 0V, 10% to 90% (Note 17)                 |     | 880 |      |       |

|                                                |        | 0.2V <sub>P-P</sub> programmed, V <sub>DHV</sub> = +0.2V,<br>V <sub>DLV</sub> = 0V, 20% to 80%                       |     | ±20 |      |       |

|                                                |        | 1VP-P programmed, VDHV_ = +1.0V,<br>VDLV_ = 0V, 10% to 90% (Note 4)                                                  |     | ±20 | ±40  |       |

| Rise and Fall Time Matching (Notes 16, 18)     |        | 2VP-P programmed, VDHV_ = +2.0V,<br>VDLV_ = 0V, 20% to 80% (Note 4)                                                  |     | ±20 | ±40  | ps    |

|                                                |        | 3VP-P programmed, VDHV_ = +3V,<br>VDLV_ = 0V, 10% to 90%                                                             |     | ±30 | ±80  |       |

|                                                |        | 5VP-P programmed, VDHV_ = +5V,<br>VDLV_ = 0V, 10% to 90%                                                             |     | ±50 |      |       |

| Slew Rate, Relative to SC1 = SC0 = 0 (Note 19) |        | SC1 = 0, SC0 = 1, V <sub>DHV</sub> = +3V,<br>V <sub>DLV</sub> = 0V, 20% to 80%                                       |     | 75  |      |       |

|                                                | SC0    | SC1 = 1, SC0 = 0, V <sub>DHV</sub> _ = +3V,<br>V <sub>DLV</sub> _ = 0V, 20% to 80%                                   |     | 50  |      | %     |

|                                                |        | SC1 = 1, SC0 = 1, V <sub>DHV</sub> _ = +3V,<br>V <sub>DLV</sub> _ = 0V, 20% to 80%                                   |     | 25  |      |       |

## **Electrical Characteristics (continued)**

$(V_{CC} = +9.25V, V_{EE} = -5.25V, V_{HHP} = +17.5V, V_{DD} = +3.3V, V_{DHV} = +3V, V_{DTV} = +1.5V, V_{DLV} = 0V, V_{DATV} = V_{RTV} = 0V, V_{CTV} = +1.2V, V_{CMPV} = +1V, V_{VHH} = +10V, CDRP_ = 000b, RO_ = 1110b, SC_ = 00b, V_{DGS} = V_{GND} = V_{GNDDAC} = 0V, specifications apply after calibration, level-setter errors included. The device is tested at T<sub>J</sub> = +70°C with an accuracy of <math>\pm 15$ °C; specification compliance with supply and temperature variations are verified by guardbanding mean shifts of characterized data, unless otherwise noted. Temperature coefficients are measured at T<sub>J</sub> = +40°C and +100°C, unless otherwise noted.)

| PARAMETER                                | SYMBOL | CONDITIONS                                                                                                               | MIN  | TYP  | MAX  | UNITS |

|------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

|                                          |        | 0.2V <sub>P-P</sub> programmed, V <sub>DHV</sub> = +0.2V,<br>V <sub>DLV</sub> = 0V (Note 20)                             |      | 400  |      |       |

| Minimum Pulse Width                      |        | 1V <sub>P-P</sub> programmed, V <sub>DHV</sub> = +1V,<br>V <sub>DLV</sub> = 0V (Notes 4, 20)                             |      | 475  | 610  |       |

|                                          |        | 1VP-P programmed, VDHV_ = +1V,<br>VDLV_ = 0V; output reaches at least 90% of<br>its nominal DC output level (Note 4)     |      | 390  | 525  | ps    |

| (Positive or Negative)                   |        | 2V <sub>P-P</sub> programmed, V <sub>DHV</sub> = +2V,<br>V <sub>DLV</sub> = 0V (Notes 4, 20)                             |      | 665  | 833  |       |

|                                          |        | 3V <sub>P-P</sub> programmed, V <sub>DHV</sub> = +3V,<br>V <sub>DLV</sub> = 0V (Notes 4, 20)                             |      | 800  | 1000 |       |

|                                          |        | 5V <sub>P-P</sub> programmed, V <sub>DHV</sub> = +5V,<br>V <sub>DLV</sub> = 0V (Note 20)                                 |      | 1300 |      |       |

|                                          |        | 0.2V <sub>P-P</sub> programmed, V <sub>DHV</sub> = +0.2V,<br>V <sub>DLV</sub> = 0V (Note 21)                             |      | 2500 |      |       |

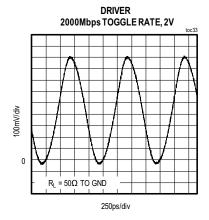

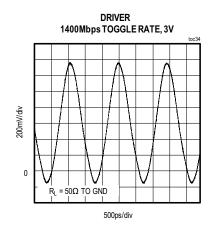

|                                          |        | 1V <sub>P-P</sub> programmed, V <sub>DHV</sub> = +1V,<br>V <sub>DLV</sub> = 0V (Notes 4, 21)                             | 1650 | 2100 |      |       |

| Data Rate                                |        | 1VP-P programmed, VDHV_ = +1V,<br>VDLV_ = 0V; output reaches at least 90% of<br>its nominal DC output level (Note 4)     | 1910 | 2570 |      | Mbps  |

|                                          |        | 2V <sub>P-P</sub> programmed, V <sub>DHV</sub> = +2V,<br>V <sub>DLV</sub> = 0V (Notes 4, 21)                             | 1200 |      |      |       |

|                                          |        | 3V <sub>P-P</sub> programmed, V <sub>DHV</sub> = +3V,<br>V <sub>DLV</sub> = 0V (Notes 4, 21)                             | 1000 |      |      |       |

|                                          |        | 5V <sub>P-P</sub> programmed, V <sub>DHV</sub> = +5V,<br>V <sub>DLV</sub> = 0V (Note 21)                                 |      | 900  |      |       |

| Rise and Fall Time, Drive to Term        |        | V <sub>DHV</sub> _ = +3V, V <sub>DLV</sub> _ = 0V, V <sub>DTV</sub> _ = +1.5V, measured 10% to 90% of waveform (Note 22) | 250  | 700  | 1300 | ps    |

| Rise and Fall Time, Term to Drive        |        | V <sub>DHV</sub> _ = +3V, V <sub>DLV</sub> _ = 0V, V <sub>DTV</sub> _ = +1.5V, measured 10% to 90% of waveform (Note 22) | 400  | 550  | 800  | ps    |

| COMPARATOR                               |        |                                                                                                                          |      |      |      |       |

| COMPARATOR DC CHARACTER                  | ISTICS |                                                                                                                          | ı    |      |      |       |

| Input Voltage Range                      |        | (Note 23)                                                                                                                | -2.2 |      | +6.2 | V     |

| Input Offset Voltage                     |        | V <sub>DUT</sub> _ = +0.125V (Note 24)                                                                                   |      | ±1   | ±5   | mV    |

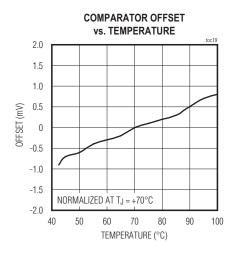

| Input-Voltage Temperature<br>Coefficient |        | (Notes 24, 25)                                                                                                           |      | ±50  |      | μV/°C |

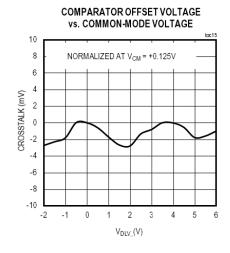

| Common-Mode Rejection                    | CMRR   | V <sub>DUT</sub> _ = -2.0V, +6.0V (Notes 24, 26)                                                                         | 50   | 55   |      | dB    |

## **Electrical Characteristics (continued)**

$(V_{CC} = +9.25V, V_{EE} = -5.25V, V_{HHP} = +17.5V, V_{DD} = +3.3V, V_{DHV} = +3V, V_{DTV} = +1.5V, V_{DLV} = 0V, V_{DATV} = 0V, V_{CTV} = +1.2V, V_{CMPV} = +1V, V_{VHH} = +10V, CDRP_ = 000b, RO_ = 1110b, SC_ = 00b, V_{DGS} = V_{GND} = V_{GNDDAC} = 0V, specifications apply after calibration, level-setter errors included. The device is tested at T<sub>J</sub> = +70°C with an accuracy of ±15°C; specification compliance with supply and temperature variations are verified by guardbanding mean shifts of characterized data, unless otherwise noted. Temperature coefficients are measured at T<sub>J</sub> = +40°C and +100°C, unless otherwise noted.)$

| PARAMETER                                                                 | SYMBOL      | CONDITIONS                                                                             | MIN            | TYP         | MAX            | UNITS |

|---------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------|----------------|-------------|----------------|-------|

|                                                                           |             | -1.75V to +5.125V, V <sub>DUT</sub> = -1.75V to +5.125V                                |                | < ±8        |                |       |

| Linearity Error (Notes 24, 27)                                            |             | Full range, V <sub>DUT</sub> = -2V to +6.0V                                            |                | < ±10       |                | mV    |

|                                                                           |             | Full range, V <sub>DUT</sub> = -2.2V to +6.2V                                          |                | < ±12       |                |       |

| Power-Supply Rejection                                                    | PSRR        | V <sub>DUT</sub> _ = -2.0V and +6.0V (Notes 24, 28)                                    | 50             | 60          |                | dB    |

| COMPARATOR AC CHARACTER                                                   | STICS (Note | es 29–32)                                                                              |                |             |                |       |

| Effective Comparator Bandwidth,<br>Term Mode                              |             | (Notes 4, 33)                                                                          | 2.0            | 4.0         |                | GHz   |

| Effective Comparator Bandwidth,<br>High-Impedance Mode                    |             | (Note 34)                                                                              |                | 800         |                | MHz   |

| Minimum Pulse Width                                                       |             | (Notes 4, 35)                                                                          |                | 0.5         | 0.65           | ns    |

| Propagation Delay                                                         |             |                                                                                        | 0.35           | 0.9         | 1.5            | ns    |

| Propagation-Delay Temperature<br>Coefficient                              |             |                                                                                        |                | 1.7         |                | ps/°C |

| Channel-to-Channel Propagation-<br>Delay Match, High/High vs. Low/<br>Low |             |                                                                                        |                | 15          |                | ps    |

| PROPAGATION-DELAY DISPERS                                                 | IONS        |                                                                                        |                |             |                |       |

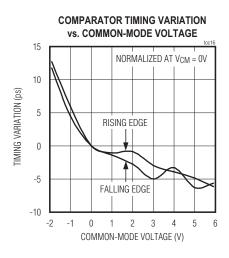

| Propagation-Delay Dispersion vs.<br>Common-Mode Input                     |             | V <sub>CM</sub> = -1.9V to +5.9V (Notes 4, 36)                                         |                | 40          | 55             | ps    |

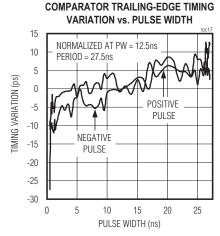

| Propagation-Delay Dispersion vs.<br>Duty Cycle                            |             | 0.6ns to 24.4ns pulse width, relative to 12.5ns pulse width, (Notes 4, 37)             |                | ±25         | ±45            | ps    |

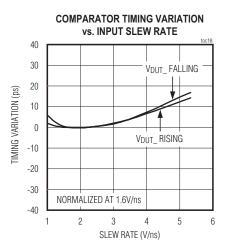

| Propagation-Delay Dispersion vs.<br>Slew Rate                             |             | 1.0V/ns to 6.0V/ns, relative to 2.0V/ns (Note 4)                                       |                | ±30         | ±40            | ps    |

|                                                                           |             | Driver in term mode, peak-to-peak within 100mV < V <sub>CMPV</sub> < 900mV window      |                | 50          | 80             |       |

| Waveform Tracking (Notes 4, 38)                                           |             | Driver in term mode, peak-to-peak within 50mV < VCMPV < 950mV window                   |                | 80          | 130            | ps    |

|                                                                           |             | Driver in high impedance, peak-to-peak within 100mV < V <sub>CMPV</sub> < 900mV window |                | 150         | 200            | ps    |

| LOGIC OUTPUTS CMP, NCMP (CI                                               | MP, NCMP co | ollector output, $R_L = 50\Omega$ internal pullup to C                                 | TV) (Note      | e 39)       |                | ,     |

| Termination Voltage CTV                                                   |             | External termination voltage                                                           | 0              | 1.2         | 3.5            | V     |

| CTV Current                                                               |             | Total current for user-supplied termination voltage                                    |                | 12          | 14             | mA    |

| Output High Voltage                                                       |             |                                                                                        | VCTV -<br>0.1  | VCTV - 0.02 | VCTV + 0.05    | V     |

| Output Low Voltage                                                        |             |                                                                                        | VCTV -<br>0.45 | VCTV - 0.3  | VCTV -<br>0.25 | V     |

## **Electrical Characteristics (continued)**

(VCC =  $\pm 9.25$ V, VEE =  $\pm -5.25$ V, VHHP =  $\pm 17.5$ V, VDD =  $\pm 3.3$ V, VDHV\_ =  $\pm 3$ V, VDTV\_ =  $\pm 1.5$ V, VDLV\_ =  $\pm 0$ V, VDATV\_ =  $\pm 0$ V, VDAT

| PARAMETER                           | SYMBOL       | CONDITIONS                                                                       | MIN                      | TYP  | MAX                      | UNITS |

|-------------------------------------|--------------|----------------------------------------------------------------------------------|--------------------------|------|--------------------------|-------|

| Output-Voltage Swing                |              |                                                                                  | 250                      | 300  | 350                      | mV    |

| Output Termination Resistor         |              |                                                                                  | 47                       |      | 53                       | Ω     |

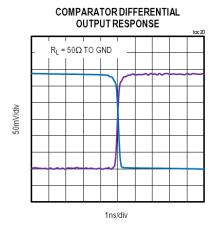

| Differential Rise Time              |              | 10% to 90% (Notes 4, 32)                                                         |                          | 210  | 400                      | ps    |

| Differential Fall Time              |              | 10% to 90% (Notes 4, 32)                                                         |                          | 210  | 400                      | ps    |

| TEMPERATURE MONITOR                 |              |                                                                                  |                          |      |                          |       |

| Nominal Voltage                     |              | T <sub>J</sub> = +70°C, R <sub>L</sub> ≥ 10MΩ                                    |                          | 3.43 |                          | V     |

| Nominal Voltage Variation           |              | T <sub>J</sub> = +125°C, R <sub>L</sub> ≥ 10MΩ, one standard deviation           |                          | ±50  |                          | mV    |

| Temperature Coefficient             |              |                                                                                  |                          | 10   |                          | mV/°C |

| Output Resistance                   |              |                                                                                  |                          | 22   |                          | kΩ    |

| High-Impedance Leakage Current      |              | VTMPSNS = +4V, TSMUX0 = 0                                                        |                          |      | 1                        | μA    |

| TEMPERATURE COMPARATOR/A            | LARM         |                                                                                  |                          |      |                          |       |

| Comparator Hysteresis               |              |                                                                                  |                          | 0    |                          | mV    |

| Alarm Threshold                     |              |                                                                                  |                          | +125 |                          | °C    |

| Temperature Alarm Accuracy          |              |                                                                                  |                          | ±5   |                          | °C    |

| DIGITAL I/O                         |              |                                                                                  |                          |      |                          |       |

| DIFFERENTIAL CONTROL INPUT          | S (DATA_, N  | DATA_, RCV_, NRCV_)                                                              | -                        |      |                          |       |

| Input High Voltage                  | VIH          | Functional test                                                                  | +0.2                     |      | +3.5                     | V     |

| Input Low Voltage                   | VIL          | Functional test                                                                  | -0.2                     |      | +3.1                     | V     |

| Differential Input Voltage          |              | Functional test                                                                  | ±0.15                    |      | ±1.0                     | V     |

| Differential Termination Resistance |              | Differential termination between DATA_/<br>NDATA_ and RCV_/NRCV_, tested at ±4mA | 96                       |      | 104                      | Ω     |

| SINGLE-ENDED INPUTS (CS, SCI        | LK, DIN, RS1 | 1                                                                                |                          |      |                          |       |

| Input High                          |              |                                                                                  | 2/3 x<br>V <sub>DD</sub> |      | V <sub>DD</sub>          | V     |

| Input Low                           |              |                                                                                  | -0.1                     |      | 1/3 x<br>V <sub>DD</sub> | V     |

| Input Bias Current                  |              |                                                                                  |                          |      | ±25                      | μA    |

| SINGLE-ENDED OUTPUT (DOUT)          |              |                                                                                  |                          |      |                          |       |

| High Output                         | Voн          | I <sub>OH</sub> = 25μA                                                           | V <sub>DD</sub> - 0.15   |      |                          | V     |

| Low Output                          | VoL          | I <sub>OL</sub> = -25μA                                                          |                          |      | V <sub>DGND</sub> + 0.15 | V     |

| SINGLE-ENDED OPEN-DRAIN OL          | JTPUTS (OV   | ALARM, TALARM with external 1kΩ to V <sub>DD</sub> )                             |                          |      |                          |       |

| Voltage Range                       | Vvoc         |                                                                                  | V <sub>DD</sub> - 0.3    |      | V <sub>DD</sub> + 0.3    | V     |

| Low Output                          | VoL          |                                                                                  | VDGND                    |      | Vvoc -<br>1.0            | V     |

## **Electrical Characteristics (continued)**

$(V_{CC} = +9.25V, V_{EE} = -5.25V, V_{HHP} = +17.5V, V_{DD} = +3.3V, V_{DHV} = +3V, V_{DTV} = +1.5V, V_{DLV} = 0V, V_{DATV} = V_{RTV} = 0V, V_{CTV} = +1.2V, V_{CMPV} = +1V, V_{VHH} = +10V, CDRP_ = 000b, RO_ = 1110b, SC_ = 00b, V_{DGS} = V_{GND} = V_{GNDDAC} = 0V, specifications apply after calibration, level-setter errors included. The device is tested at T<sub>J</sub> = +70°C with an accuracy of ±15°C; specification compliance with supply and temperature variations are verified by guardbanding mean shifts of characterized data, unless otherwise noted. Temperature coefficients are measured at T<sub>J</sub> = +40°C and +100°C, unless otherwise noted.)$

| PARAMETER                               | SYMBOL                  | CONDITIONS                                                            | MIN      | TYP    | MAX          | UNITS |

|-----------------------------------------|-------------------------|-----------------------------------------------------------------------|----------|--------|--------------|-------|

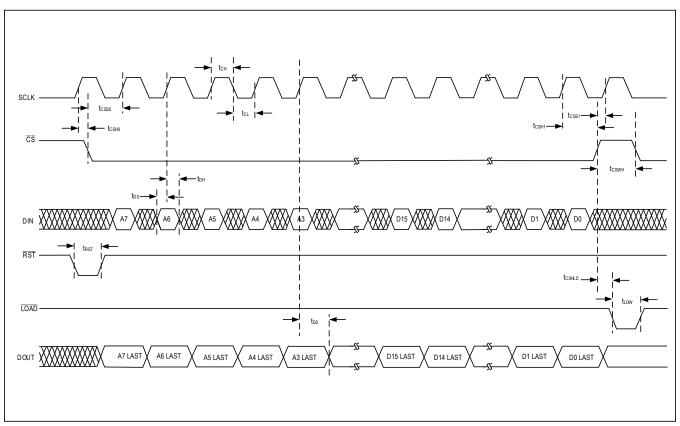

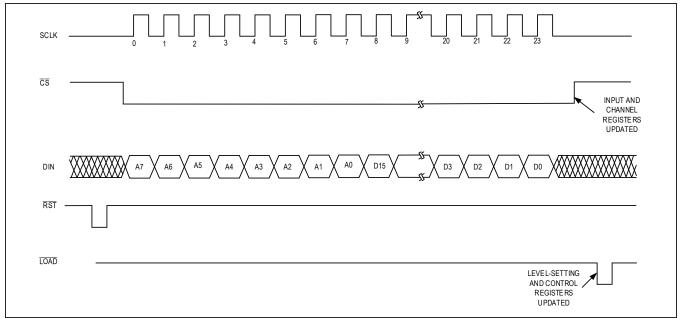

| SERIAL-PORT TIMING (See Figur           | e 3)                    |                                                                       |          |        |              | ,     |

| SCLK Frequency                          |                         |                                                                       |          |        | 50           | MHz   |

| SCLK Pulse-Width High                   | tсн                     |                                                                       | 10       |        |              | ns    |

| SCLK Pulse-Width Low                    | tCL                     |                                                                       | 10       |        |              | ns    |

| CS Low to SCLK High Setup               | tcss0                   |                                                                       | 4.25     |        |              | ns    |

| SCLK High to CS Low Hold                | tCSH0                   |                                                                       | 4.25     |        |              | ns    |

| CS High to SCLK High Setup              | tcss1                   |                                                                       | 4.25     |        |              | ns    |

| SCLK High to CS High Hold               | tCSH1                   |                                                                       | 4.25     |        |              | ns    |

| DIN to SCLK High Setup                  | t <sub>DS</sub>         |                                                                       | 4.25     |        |              | ns    |

| DIN to SCLK High Hold                   | tDH                     |                                                                       | 4.25     |        |              | ns    |

| CS High Pulse Width                     | tcswh                   |                                                                       | 40       |        |              | ns    |

| LOAD Low Pulse Width                    | t <sub>LDW</sub>        |                                                                       | 20       |        |              | ns    |

| RST Low Pulse Width                     | trst                    |                                                                       | 25       |        |              | ns    |

| CS High to LOAD Low Hold                | tCSHLD                  |                                                                       | 50       |        |              | ns    |

| SCLK to DOUT Delay                      | t <sub>DO</sub>         |                                                                       |          |        | 62.4         | ns    |

| COMMON FUNCTIONS (VCC = +9.             | .25V, V <sub>EE</sub> = | -5.25V, V <sub>DD</sub> = +3.3V, V <sub>HHP</sub> = +17.5V, unless of | therwise | noted) |              |       |

| Operating Voltage Range                 |                         |                                                                       | -2.0     |        | +13          | V     |

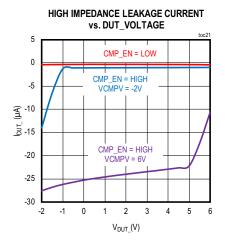

|                                         | 1                       | V <sub>CMPV</sub> = +6.0V, V <sub>DUT</sub> = -2.0V, CMP_EN = high    |          |        | ±50          |       |

| High-Impedance Mode Leakage             | IDUT                    | V <sub>CMPV</sub> = -2.0V, V <sub>DUT</sub> = +6.0V, CMP_EN = high    |          |        | ±50          | - μΑ  |

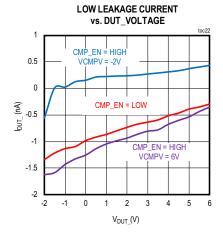

| Low-Leak Mode Leakage                   | IDUT                    | V <sub>DUT</sub> _ = -2.0V and +6.0V (Note 40)                        |          |        | ±100         | nA    |

| O                                       |                         | Driver in terminate mode (Note 4)                                     |          | 0.5    | 1.0          |       |

| Combined Capacitance                    |                         | Driver in high impedance                                              |          | 3      |              | pF    |

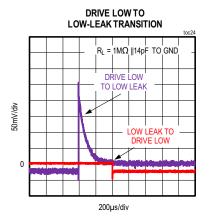

| Low-Leak Enable Time                    |                         | CS high for setting LLEAKS_ high to IDUT_ specification               |          | 20     |              | μs    |

| Low-Leak Disable Time                   |                         | CS high for setting LLEAKS_ low to normal operation                   |          | 20     |              | μs    |

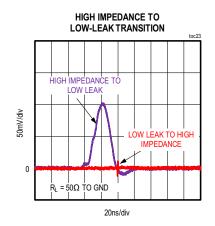

| Low-Leak Spike, V <sub>DLV</sub> _/Leak |                         | V <sub>DLV</sub> _ = 0V, Z <sub>L</sub> = 10MΩ    8pF to GND (Note 4) | -200     |        | +600         | mV    |

| Low-Leak Spike, V <sub>DHV</sub> _/Leak |                         | $V_{DHV}$ = +2V, $Z_L$ = 10M $\Omega$    8pF to GND (Note 4)          | -200     |        | +350         | mV    |

| Low-Leak Spike, High-Impedance/<br>Leak |                         | $R_L = 50\Omega$ to GND (Note 4)                                      | -125     |        | +350         | mV    |

| DUT_ OVERVOLTAGE ALARM                  |                         |                                                                       |          |        |              |       |

| Maximum Programmable OVHV               |                         |                                                                       | 6.7      | 7.0    |              | V     |

| Minimum Programmable OVLV               |                         |                                                                       |          | -3.0   | <b>-</b> 2.7 | V     |

## **Electrical Characteristics (continued)**

$(V_{CC} = +9.25V, V_{EE} = -5.25V, V_{HHP} = +17.5V, V_{DD} = +3.3V, V_{DHV} = +3V, V_{DTV} = +1.5V, V_{DLV} = 0V, V_{DATV} = V_{RTV} = 0V, V_{CTV} = +1.2V, V_{CMPV} = +1V, V_{VHH} = +10V, CDRP_ = 000b, RO_ = 1110b, SC_ = 00b, V_{DGS} = V_{GND} = V_{GNDDAC} = 0V, specifications apply after calibration, level-setter errors included. The device is tested at T<sub>J</sub> = +70°C with an accuracy of ±15°C; specification compliance with supply and temperature variations are verified by guardbanding mean shifts of characterized data, unless otherwise noted. Temperature coefficients are measured at T<sub>J</sub> = +40°C and +100°C, unless otherwise noted.)$

| PARAMETER                     | SYMBOL            | CONDITIONS                                                                                                                                                       | MIN   | TYP   | MAX   | UNITS      |

|-------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------------|

| Voltage Accuracy              |                   | Includes gain, offset, and linearity errors over full alarm range, VOVHV = +6.7V and VOVLV = -2.7V                                                               |       |       | 150   | mV         |

| Comparator Delay              |                   | With 50mV overdrive on DUT_ signal                                                                                                                               |       | 390   |       | ns         |

| Comparator Hysteresis         |                   |                                                                                                                                                                  |       | 7     |       | mV         |

| Minimum Alarm Setting Voltage | Vovhv -<br>Vovlv  |                                                                                                                                                                  |       | 2     |       | V          |

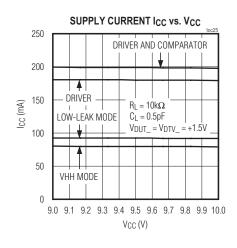

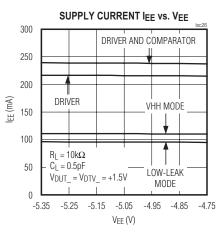

| POWER SUPPLIES                |                   |                                                                                                                                                                  |       |       |       | '          |

| Positive Supply               | Vcc               |                                                                                                                                                                  | 9.0   | 9.25  | 10.0  | V          |

| Negative Supply               | VEE               |                                                                                                                                                                  | -5.35 | -5.25 | -4.75 | V          |

| Logic Supply                  | V <sub>DD</sub>   |                                                                                                                                                                  | 2.3   | 3.3   | 3.6   | V          |

| High Voltage Supply           | VHHP              |                                                                                                                                                                  | 17    | 17.5  | 18    | V          |

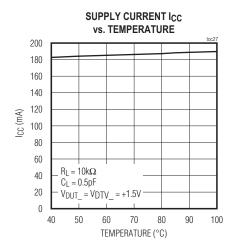

| Positive Supply Current       | Icc               | (Note 41)                                                                                                                                                        |       | 180   | 230   | mA         |

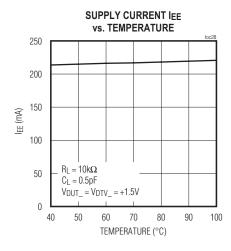

| Negative Supply Current       | IEE               | (Note 41)                                                                                                                                                        |       | 210   | 270   | mA         |

| Logic Supply Current          | I <sub>DD</sub>   | (Note 41)                                                                                                                                                        |       | 11    | 20    | mA         |

| High-Voltage Supply Current   | Інн               | (Note 41)                                                                                                                                                        |       | 2.0   | 4.0   |            |

|                               |                   | VHH mode, all channels enabled (Note 41)                                                                                                                         |       | 60    | 70    | mA         |

| Dawar Discination             |                   | V <sub>CC</sub> = +9.25V, V <sub>EE</sub> = -5.25V, V <sub>DD</sub> = +3.3V,<br>V <sub>HHP</sub> = +17.5V, LLEAKS_ = 0, CMP_EN = 0,<br>ENVHH = high, ENVHHS_ = 0 |       | 0.7   | 0.8   | \\\(C _{2} |

| Power Dissipation             |                   | V <sub>CC</sub> = +9.25V, V <sub>EE</sub> = -5.25V, V <sub>DD</sub> = +3.3V,<br>V <sub>HHP</sub> = +17.5V, LLEAKS_ = 0, CMP_EN = 1,<br>ENVHH = high, ENVHHS_ = 0 |       | 0.74  | 0.90  | - W/Ch     |

| ANALOG INPUTS (DUT_ ground    | sense)            |                                                                                                                                                                  |       |       |       |            |

|                               |                   | Relative to GNDDAC, under the full DAC range (Note 42)                                                                                                           |       | <±250 |       | mV         |

| Input Range                   | V <sub>D</sub> GS | Relative to GNDDAC, under the limited DAC range of -1.5V to +5.5V, for VHH the DAC range is limited to 0.5V to 12.25V (Note 43)                                  |       | <±750 |       | mV         |

| Input Bias Current            |                   | V <sub>DGS</sub> = 0V                                                                                                                                            | -10   |       | +10   | μA         |

| 0-:                           |                   | DGS gain for DHV_, DLV_, DTV_, CMPV                                                                                                                              | 1±2%  |       |       | <u> </u>   |

| Gain                          |                   | DGS gain for VHH                                                                                                                                                 | 1±3%  |       | V/V   |            |

| 2.5V REFERENCE                |                   |                                                                                                                                                                  |       |       |       |            |

| Nominal Voltage               | VREF              |                                                                                                                                                                  |       | 2.5   |       | V          |

| Input Bias Current            |                   |                                                                                                                                                                  | -10   |       | +10   | μA         |

### **Electrical Characteristics (continued)**

$(V_{CC} = +9.25V, V_{EE} = -5.25V, V_{HHP} = +17.5V, V_{DD} = +3.3V, V_{DHV} = +3V, V_{DTV} = +1.5V, V_{DLV} = 0V, V_{DATV} = V_{RTV} = 0V, V_{CTV} = +1.2V, V_{CMPV} = +1V, V_{VHH} = +10V, CDRP_ = 000b, RO_ = 1110b, SC_ = 00b, V_{DGS} = V_{GND} = V_{GNDDAC} = 0V, specifications apply after calibration, level-setter errors included. The device is tested at T<sub>J</sub> = +70°C with an accuracy of ±15°C; specification compliance with supply and temperature variations are verified by guardbanding mean shifts of characterized data, unless otherwise noted. Temperature coefficients are measured at T<sub>J</sub> = +40°C and +100°C, unless otherwise noted.)$

| PARAMETER                                 | SYMBOL       | CONDITIONS                                                            | MIN   | TYP   | MAX   | UNITS |

|-------------------------------------------|--------------|-----------------------------------------------------------------------|-------|-------|-------|-------|

| DRIVER VHH DC CHARACTERIS                 | TICS         |                                                                       | •     |       |       |       |

| Output Voltage Range VVHH                 |              | DGS = AGND; for DGS ≠ AGND, refer to the DGS gain specification       | 0     |       | 13    | V     |

| DC Output Valtage                         |              | V <sub>VHH</sub> = +13V, I <sub>DUT</sub> = 10mA                      |       | 12.45 |       | V     |

| DC Output Voltage                         |              | V <sub>VHH</sub> = 0V, I <sub>DUT</sub> = -10mA                       |       | 0.55  | 0.75  | V     |

| Current Limit                             |              | $V_{VHH}$ = +13V, $V_{DUT}$ = 0V and $V_{VHH}$ = 0V, $V_{DUT}$ = +13V | ±12   |       | ±27   | mA    |

| Offset Voltage                            |              | V <sub>V</sub> HH = +7.75V                                            |       |       | ±30   | mV    |

| Output-Voltage Temperature<br>Coefficient | VVHH_TC      | (Note 3)                                                              |       | ±75   | ±500  | μV/°C |

| Normalized Gain                           |              | V <sub>VHH</sub> = +7.75V, +12.75V                                    | 0.998 | 1.000 | 1.002 | V/V   |

| Linearity Relative to +7.75V, +12.75V     |              | V <sub>VHH</sub> = +7.0 to +13.0V                                     |       |       | ±14   | mV    |

| Linearity Relative to +1.5V, +12.75V      |              | V <sub>VHH</sub> = 0.0V to +13.0V                                     |       |       | ±30   | mV    |

| Output Resistance                         |              | I <sub>DUT</sub> = ±2mA, V <sub>VHH</sub> = +1V                       | 45    | 55    | 75    | Ω     |

| Power-Supply Rejection Ratio              |              | VCC, VEE, VHHP independently varied over their allowed ranges         |       | 20    |       | mV/V  |

| DRIVER VHH AC CHARACTERIS                 | ΓICS (RL ≥ 1 | 0MΩ, C <sub>DUT</sub> = 100pF)                                        |       |       |       |       |

| VHH Rise/Fall Times                       |              | V <sub>DHV</sub> = +3V, V <sub>VHH</sub> = +13V, 10% to 90%           |       |       | 250   | ns    |

| VHH Overshoot                             |              | V <sub>DHV</sub> = +3V, V <sub>VHH</sub> = +13V (Note 3)              |       |       | 180   | mV    |

| LEVEL DACs                                |              |                                                                       |       |       |       |       |

| Settling Time                             |              | Full-scale transition to within 5mV                                   |       | 20    |       | μs    |

|                                           |              | All levels not shown below, 1 LSB = 610μV                             |       | < ±1  |       |       |

| Differential Nonlinearity                 |              | VHH                                                                   |       | < ±2  |       | mV    |

|                                           |              | OVHV, OVLV                                                            |       | < ±39 |       |       |

- Note 2: V<sub>DHV</sub>, V<sub>DLV</sub>, and V<sub>DTV</sub> levels are calibrated for gain at +0.125V and +3.875V and are calibrated for offset at +0.125V; relative to straight line between +0.125V and +3.875V.

- Note 3: Change in level over operating range. Includes both gain and offset temperature effects. Simulated over entire +40°C to +100°C junction operating range. Verified at worst-case points, which are at the endpoints V<sub>DHV</sub> V<sub>DLV</sub> R 200mV.

- Note 4: Guaranteed by design and characterization.

- Note 5: DATA\_ = high, V<sub>DHV</sub> = 3V, V<sub>DLV</sub> = 0V, V<sub>DTV</sub> = 1.5V, I<sub>OUT</sub> = ±30mA. Nominal target value is 48Ω.

- Note 6: Resistance measurements are made using ±2.5mA current changes in the loading instrument about the noted value. Absolute value of the difference in measured resistance over the specified range, tested separately for each current polarity. Test conditions at IDUT are ±1mA, ±12mA, and ±40mA, respectively.

- Note 7: Rise time of the differential inputs DATA\_ and RCV\_ is 150ps (10% to 90%). SC1 = SC0 = 0, 40MHz, unless otherwise specified.

- Note 8: Current supplied for a minimum of 10ns. Verified to be greater than or equal to DC drive current by design and characterization.

- Note 9: Measured from the 90% point of the driver output (relative to its final value) to the waveform settling to within the specified limit.

- Note 10: Propagation delays are measured from the crossing point of the differential input signals to the 50% point of expected output swing.

- Note 11: Average of the two measurements for propagation delay, tLH and tHL.

- Note 12: Average of the four measurements in propagation delay, drive to high impedance, and high impedance to drive (t<sub>LZ</sub>, t<sub>HZ</sub>, t<sub>ZL</sub>, and t<sub>ZH</sub>). Measured from crossing point of RCV\_/NRCV\_ to 50% point of the output waveform.

### **Electrical Characteristics (continued)**

$(V_{CC} = +9.25V, V_{EE} = -5.25V, V_{HHP} = +17.5V, V_{DD} = +3.3V, V_{DHV} = +3V, V_{DTV} = +1.5V, V_{DLV} = 0V, V_{DATV} = V_{RTV} = 0V, V_{CTV} = +1.2V, V_{CMPV} = +1V, V_{VHH} = +10V, CDRP_ = 000b, RO_ = 1110b, SC_ = 00b, V_{DGS} = V_{GND} = V_{GNDDAC} = 0V, specifications apply after calibration, level-setter errors included. The device is tested at T<sub>J</sub> = +70°C with an accuracy of ±15°C; specification compliance with supply and temperature variations are verified by guardbanding mean shifts of characterized data, unless otherwise noted. Temperature coefficients are measured at T<sub>J</sub> = +40°C and +100°C, unless otherwise noted.)$

- Note 13: Four measurements are made: V<sub>DHV</sub> to high impedance, V<sub>DLV</sub> to high impedance, high impedance to V<sub>DHV</sub>, and high impedance to V<sub>DLV</sub> (t<sub>LZ</sub>, t<sub>HZ</sub>, t<sub>ZL</sub>, and t<sub>ZH</sub>). The worst-case difference is calculated.

- Note 14: Average of the four measurements in propagation delay, drive to term, and term to drive (t<sub>LT</sub>, t<sub>HT</sub>, t<sub>TL</sub>, and t<sub>TH</sub>). Measured from the crossing point of RCV\_/NRCV\_ to the 50% point of the output waveform.

- **Note 15:** Four measurements are made: V<sub>DHV</sub> to V<sub>DTV</sub>, V<sub>DLV</sub> to V<sub>DTV</sub>, V<sub>DTV</sub> to V<sub>DHV</sub>, and V<sub>DTV</sub> to V<sub>DLV</sub> (t<sub>LT</sub>, t<sub>HT</sub>, t<sub>TL</sub>, and t<sub>TH</sub>). The worst-case difference is calculated.

- Note 16: Cable-droop compensation disabled. Measured as close as possible to DUT using a high-bandwidth cable.

- Note 17: Cable-droop compensation enabled. Measured at end of 2m RG174 cable.

- Note 18: There should not be a systemic mismatch in rise vs. fall time or tLH vs. tHL.

- Note 19: Functionally tested during production.

- **Note 20:** At this pulse width, the output reaches at least 95% of its nominal (DC) amplitude. The pulse width is measured at the DATA\_ (input) pins.

- Note 21: Maximum data rate in transitions/second. A waveform that reaches at least 95% of its programmed amplitude can be generated at one-half of this frequency.

- Note 22: This specification is indicative of switching speed from V<sub>DHV</sub> or V<sub>DLV</sub> to V<sub>DTV</sub> and V<sub>DTV</sub> to V<sub>DHV</sub> or V<sub>DLV</sub> when V<sub>DLV</sub> < V<sub>DTV</sub> < V<sub>DHV</sub> . If V<sub>DTV</sub> < V<sub>DLV</sub> or V<sub>DTV</sub> > V<sub>DHV</sub> , switching speed is degraded by roughly a factor of 3.

- Note 23: The comparator tolerates the VHH level produced by the driver, but the specifications only apply for the -2.2V to +6.2V input voltage range.

- Note 24: Measured by using a servo to locate comparator thresholds.

- **Note 25:** Change in offset at any voltage over operating range. Includes both gain (CMRR) and offset temperature effects. Simulated over entire operating range. Verified at worst-case points, which are at the endpoints.

- Note 26: Change in offset voltage over input range.

- Note 27: Relative to straight line between +0.125V and +3.875V.

- Note 28: Change in offset voltage with power supplies independently varied over their full range.

- Note 29: All propagation delays measured from VDUT\_ crossing calibrated VCMPV threshold to crossing point of differential outputs.

- Note 30: All AC specifications are measured with the DUT\_ pin (comparator input) as the reference.

- Note 31: 40MHz, 0 to +2V input to comparator, V<sub>CMPV</sub> reference = +1.0V, 50% duty cycle 1ns rise/fall time, Zs = 50Ωs, driver in term mode with V<sub>DTV</sub> = +1.0V, unless otherwise noted.

- **Note 32:** Use calibration comparator per channel and avoid any transition on deselected channel. If transitions cannot be avoided, keep deselected channels in low-leak mode to minimize coupling during calibration.

- Note 33: Input rise/fall time = 45ps. 0 to 1.0V, 50% duty cycle.

- Note 34: Input rise/fall time = 150ps. 0 to 1.0V, 50% duty cycle.

- **Note 35:** At this pulse width, the output reaches at least 90% of its nominal peak-to-peak swing. The pulse width is measured at the crossing points of the differential outputs. 500ps rise/fall time. Timing specifications are not guaranteed.

- Note 36: V<sub>DUT</sub> = 200mV<sub>P-P</sub>, rise/fall time = 250ps, overdrive = 100mV, V<sub>DTV</sub> = V<sub>CM</sub>. Valid for a common-mode range where the signal does not exceed the operating range. This specification is the worst-case (slowest to fastest) over the specified range.

- Note 37: 0 to +1V input to comparator, VCMPV reference = +0.5V, input rise/fall time = 250ps.

- Note 38: Input to comparator is 40MHz at 0 to +1.0V, 50% duty cycle, 1ns rise/fall time.

- Note 39: Unless otherwise specified, comparator outputs are terminated with  $50\Omega$  to +1.2V and  $V_{CTV}$  = +1.2V.

- Note 40: While device is in low-leak mode, care must be taken to never present a voltage greater than V<sub>CC</sub> to the DUT\_ node, as this can damage the part.