## Automotive Low Input Voltage I<sup>2</sup>C 4-Channel 150mA Backlight Driver

## **General Description**

The MAX25014 is a 4-channel backlight driver IC with boost controller for automotive displays. The integrated current outputs can sink up to 150mA LED current each. The device accepts a wide 2.5V to 36V input voltage range and withstands automotive load-dump events.

The internal current-mode switching DC-DC controller supports boost or SEPIC topologies and operates in the 400kHz to 2.2MHz frequency range. Integrated spread spectrum helps reduce EMI. An adaptive output-voltage-control scheme minimizes power dissipation in the LED current-sink paths.

Control is included for an external nMOSFET series switch to reduce quiescent current when the backlight is off and to disconnect the boost converter in the case of a fault.

The device features I<sup>2</sup>C-controlled pulse-width-modulation (PWM) dimming and hybrid dimming. In either case, the minimum pulse width is 500ns. Phase-shifted dimming of the strings is incorporated for lower EMI.

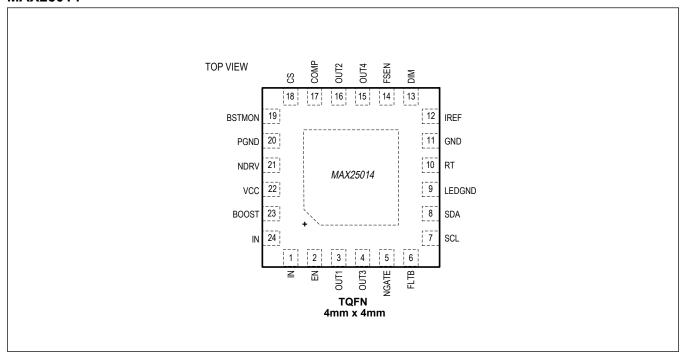

The MAX25014 is available in a 24-pin TQFN or 24-pin side-wettable TQFN (SWTQFN) package and operates over the -40°C to +125°C temperature range.

## **Applications**

- Instrument Clusters

- Central Information Displays

- Infotainment Displays

## **Benefits and Features**

- Wide Voltage-Range Operation

- Operates Down to 2.5V Supply After Startup

- Survives Load Dumps Up to 40V

- High Integration

- Complete 4-Channel Solution Including Boost Controller

- I<sup>2</sup>C Control for Minimum Parts Count

- · Robust and Low EMI

- Spread-Spectrum Oscillator

- · Phase Shifting

- · 400kHz to 2.2MHz Switching-Frequency Range

- nMOS Input Protection Switch

- Multiple Diagnostic Features

- LED-Current Measurement

- · Boost Output Voltage Measurement

- LED Open/Short Detection and Protection

- Boost Output Undervoltage and Overvoltage

- Versatile Dimming Scheme Allows Hybrid or PWM-Only Dimming Using DIM Input or I<sup>2</sup>C

- Dimming Ratio > 10,000:1 Using Hybrid Dimming

- 10,000:1 Dimming Ratio at 200Hz Using PWM Dimming

- Compact (4mm x 4mm) 24-Pin TQFN and SWTQFN Packages

Ordering Information appears at end of data sheet.

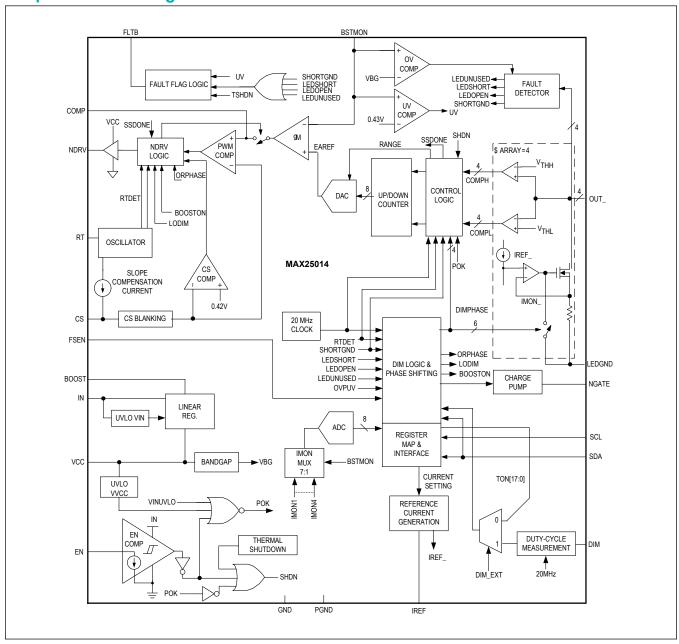

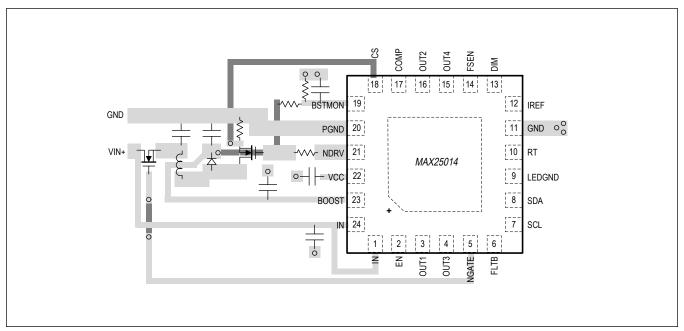

## **Simplified Block Diagram**

## **TABLE OF CONTENTS**

| O                                             |    |

|-----------------------------------------------|----|

| General Description                           |    |

| Benefits and Features                         |    |

| Simplified Block Diagram                      |    |

| •                                             |    |

| Absolute Maximum Ratings                      |    |

| Package Information                           |    |

| TQFN/SWTQFN                                   |    |

| Electrical Characteristics                    |    |

| Typical Operating Characteristics             |    |

| Pin Configuration                             |    |

| MAX25014                                      |    |

| Pin Description                               |    |

| Functional Diagrams                           |    |

| MAX25014 Block Diagram                        |    |

| Detailed Description                          |    |

| Enable                                        |    |

| Low-Voltage Operation                         |    |

| Undervoltage Lockout                          |    |

| Current-Mode DC-DC Controller                 |    |

| Output Undervoltage Protection                |    |

| 8-Bit Digital-to-Analog Converter             |    |

| FSEN Pin Function                             | 19 |

| Dimming                                       | 20 |

| Hybrid Dimming                                | 20 |

| Hybrid Dimming Operation                      | 21 |

| Hybrid Dimming Operation Modes                | 21 |

| Low-Dimming Mode                              | 22 |

| Phase-Shift Dimming                           | 22 |

| Disabling Individual Strings                  | 22 |

| Startup Sequence                              | 22 |

| Stage 1                                       | 22 |

| Stage 2                                       | 22 |

| Stage 3                                       | 23 |

| Boost Startup                                 | 24 |

| Oscillator Frequency/External Synchronization | 24 |

| Spread-Spectrum Modulation                    | 24 |

| 5V LDO Regulator (V <sub>CC</sub> )           | 25 |

| LED Current Control                           | 25 |

## TABLE OF CONTENTS (CONTINUED)

# Automotive Low Input Voltage I<sup>2</sup>C 4-Channel 150mA Backlight Driver

| LIST OF FIGURES                                              |    |

|--------------------------------------------------------------|----|

| Figure 1. Hybrid Dimming Operation with HDIM[1:0] = 10 (25%) | 2  |

| Figure 2. Hybrid Dimming Operation Modes                     | 2  |

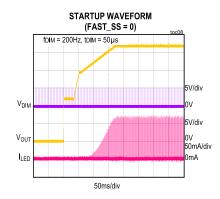

| Figure 3. Boost Startup Waveform with FAST_SS = 0            | 24 |

| Figure 4. Sample Layout                                      | 44 |

# Automotive Low Input Voltage I<sup>2</sup>C 4-Channel 150mA Backlight Driver

| LIST OF TABLES                                                        |    |

|-----------------------------------------------------------------------|----|

| Table 1. FSEN RESISTOR VALUES                                         | 19 |

| Table 2. LED CURRENT WITH 40.2kΩ IREF RESISTOR                        | 25 |

| Table 3. LED CURRENT SETTING (VALUES WITH R <sub>IREF</sub> = 49.9kΩ) | 29 |

## **Absolute Maximum Ratings**

| IN, EN to GND0.3V to +40V                                      | NDRV Continuous Current100mA to +100mA                          |

|----------------------------------------------------------------|-----------------------------------------------------------------|

| OUT_, NGATE, BSTMON, BOOST to GND0.3V to +52V                  | OUT_ Continuous Current150mA to +150mA                          |

| PGND, LEDGND to GND0.3V to +0.3V                               | Continuous Power Dissipation Multilayer Board (T <sub>A</sub> = |

| V <sub>CC</sub> to GND when EN High0.3V to +6V                 | +70°C)2.857W                                                    |

| V <sub>CC</sub> to GND when EN Low0.3V to minimum of +6V and   | Junction-to-Ambient Thermal Resistance (θ <sub>JA</sub> )       |

| $(V_{IN} + 0.3)V$                                              | Package Thermal Resistance (θ <sub>JC</sub> )                   |

| FLTB, SCL, SDA, DIM to GND0.3V to +6V                          | Operating Temperature40°C to +125°C                             |

| FSEN, CS, RT, COMP, NDRV, IREF to GND0.3V to V <sub>CC</sub> + | Junction Temperature40°C to +150°C                              |

| 0.3V                                                           | Storage Temperature Range65°C to +150°C                         |

| NDRV Peak Current (< 100ns)5A to +5A                           | Lead Temperature Range+300°C                                    |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

#### TQFN/SWTQFN

| Package Code                            | T2444+4C       |  |  |  |

|-----------------------------------------|----------------|--|--|--|

| Outline Number                          | <u>21-0139</u> |  |  |  |

| Land Pattern Number                     | 90-0022        |  |  |  |

| Thermal Resistance, Single-Layer Board: |                |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> )  | 48°C/W         |  |  |  |

| Junction to Case $(\theta_{JC})$        | 3°C/W          |  |  |  |

| Thermal Resistance, Four-Layer Board:   |                |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> )  | 36°C/W         |  |  |  |

| Junction to Case $(\theta_{JC})$        | 3°C/W          |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

## **Electrical Characteristics**

$(V_{IN}$  = 12V, R<sub>RT</sub> = 76.8k $\Omega$ , C<sub>VCC</sub> = 2.2 $\mu$ F, T<sub>A</sub> = T<sub>J</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted. (*Note 1*))

| PARAMETER                                | SYMBOL              | CONDITIONS                                                                      | MIN | TYP  | MAX  | UNITS |

|------------------------------------------|---------------------|---------------------------------------------------------------------------------|-----|------|------|-------|

| POWER INPUT                              |                     |                                                                                 |     |      |      |       |

| Operating Voltage<br>Range, High Setting | V <sub>IN</sub>     | Register bit UV_SEL = 0                                                         | 3.2 |      | 36   | V     |

| Operating Voltage<br>Range, Low Setting  | V <sub>IN</sub>     | Register bit UV_SEL = 1                                                         | 2.5 |      | 36   | V     |

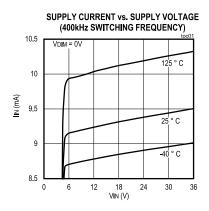

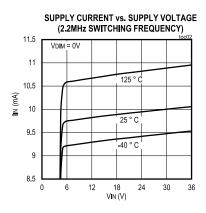

| Quiescent Supply<br>Current              | IQ <sub>IN</sub>    | V <sub>DIM</sub> = 5V; V <sub>BSTMON</sub> = 1.3V,<br>OUT1–OUT4 are unconnected |     | 9.5  | 13   | mA    |

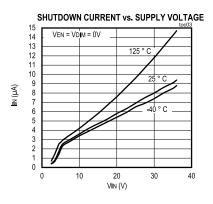

| Standby Supply Current                   | ISHDNIN             | V <sub>IN</sub> = V <sub>BOOST</sub> = 12V, V <sub>EN</sub> = 0V                |     | 4    | 8    | μA    |

| IN Undervoltage<br>Lockout, Rising       | UVLOR <sub>IN</sub> |                                                                                 | 3.8 | 4.15 | 4.45 | V     |

$(V_{IN}$  = 12V, R<sub>RT</sub> = 76.8k $\Omega$ , C<sub>VCC</sub> = 2.2 $\mu$ F, T<sub>A</sub> = T<sub>J</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted. (<u>Note 1</u>))

| PARAMETER                                                      | SYMBOL                                 | CONDITIONS                                                                      | MIN  | TYP  | MAX         | UNITS  |

|----------------------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------|------|------|-------------|--------|

| IN Undervoltage<br>Lockout, Falling                            | UVLOF <sub>IN</sub>                    |                                                                                 | 3.2  | 3.75 | 4           | V      |

| IN Undervoltage<br>Lockout Falling, High<br>Setting            | UVLOF <sub>INCC</sub>                  | After completed boost soft-start. Register bit UV_SEL = 0                       | 2.65 | 2.9  | 3.15        | V      |

| IN Undervoltage<br>Lockout Falling, Low<br>Setting             | UVLOF <sub>INCC</sub>                  | After completed boost soft-start. Register bit UV_SEL = 1                       | 2.15 | 2.3  | 2.45        | V      |

| Startup Delay                                                  | t <sub>STARTUP</sub>                   | From EN high to I <sup>2</sup> C ready                                          |      |      | 2           | ms     |

| IN to BOOST<br>Switchover Voltage                              | V <sub>SO</sub>                        | IN falling, if V <sub>BOOST</sub> > V <sub>IN</sub> + 300mV (typ)               | 5.6  | 5.8  | 6.1         | V      |

| IN to BOOST<br>Switchover Voltage<br>Hysteresis                | V <sub>SO_HYS</sub>                    |                                                                                 |      | 150  |             | mV     |

| BOOST Shutdown Input<br>Current                                | ISHDN <sub>BOOST</sub>                 | V <sub>EN</sub> = 0V, V <sub>BOOST</sub> = 12V                                  |      | 0.1  | 1           | μA     |

| DOOGT last to consider                                         |                                        | V <sub>EN</sub> = 5V, Register bit ENA = 0, V <sub>BOOST</sub> = 24V            |      | 3.5  | 7           |        |

| BOOST Input Current                                            | BOOST Input Current I <sub>BOOST</sub> | V <sub>EN</sub> = 5V, Register bit ENA = 1, V <sub>BOOST</sub> = 24V            |      | 30   | 45          | μA     |

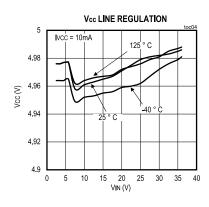

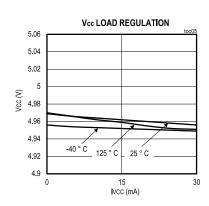

| V <sub>CC</sub> REGULATOR                                      |                                        |                                                                                 |      |      |             | '      |

| V <sub>CC</sub> Output Voltage                                 | Vcc                                    | 6V < V <sub>IN</sub> , V <sub>BOOST</sub> < 36V, I <sub>VCC</sub> = 1mA to 10mA | 4.75 | 5    | 5.25        | V      |

| Dropout Voltage                                                | VCC <sub>DROP</sub>                    | V <sub>IN</sub> = 4.5V, I <sub>VCC</sub> = 5mA                                  |      |      | 0.2         | V      |

| Short-Circuit Current<br>Limit                                 | I <sub>VCC_SC</sub>                    | V <sub>CC</sub> shorted to GND                                                  |      | 60   |             | mA     |

| V <sub>CC</sub> Undervoltage-<br>Lockout Threshold,<br>Rising  | UVLOR <sub>VCC</sub>                   |                                                                                 | 4.05 | 4.2  | 4.35        | V      |

| V <sub>CC</sub> Undervoltage-<br>Lockout Threshold,<br>Falling | UVLOF <sub>VCC</sub>                   |                                                                                 | 3.75 | 3.9  | 4.04        | V      |

| RT OSCILLATOR                                                  | •                                      |                                                                                 |      |      |             |        |

| Switching-Frequency Range                                      | f <sub>SW</sub>                        | Frequency dithering disabled                                                    | 400  |      | 2200        | kHz    |

| Mariana Buta Onda                                              | 5                                      | f <sub>SW</sub> = 400kHz                                                        | 90   | 94.5 | 98.5        | 0.     |

| Maximum Duty Cycle D <sub>MAX</sub>                            | f <sub>SW</sub> = 2200kHz              | 86                                                                              | 90.5 | 95   | %           |        |

| Oscillator-Frequency                                           | f <sub>SW1</sub>                       | R <sub>RT</sub> = 76.8kΩ, dither disabled                                       | 348  | 400  | 444         | 141.1- |

| Accuracy                                                       | f <sub>SW2</sub>                       | $R_{RT}$ = 13.3kΩ, dither disabled                                              | 2013 | 2200 | 00 2387 kHz |        |

| Frequency Dither                                               | SS                                     | Register bit SSL = 1                                                            |      | ±3   |             | %      |

| RT Output Voltage                                              | V <sub>RT</sub>                        | $R_{RT}$ = 76.8kΩ or $R_{RT}$ = 13.3kΩ                                          | 1.22 | 1.25 | 1.28        | V      |

| Sync Rising Threshold                                          | V <sub>SYNCTH</sub>                    |                                                                                 | 2.1  |      |             | V      |

$(V_{IN}$  = 12V, R<sub>RT</sub> = 76.8k $\Omega$ , C<sub>VCC</sub> = 2.2 $\mu$ F, T<sub>A</sub> = T<sub>J</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted. (<u>Note 1</u>))

| PARAMETER                                                                | SYMBOL                 | CONI                                       | DITIONS                            | MIN                      | TYP  | MAX                      | UNITS |

|--------------------------------------------------------------------------|------------------------|--------------------------------------------|------------------------------------|--------------------------|------|--------------------------|-------|

| Sync-Frequency Duty-<br>Cycle Range                                      | D <sub>SYNC</sub>      |                                            |                                    |                          | 50   |                          | %     |

| Sync-Frequency Range                                                     | fsync                  |                                            |                                    | 1.2 x<br>f <sub>SW</sub> |      | 1.5 x<br>f <sub>SW</sub> | kHz   |

| MOSFET DRIVER                                                            |                        | •                                          |                                    |                          |      |                          | •     |

| NDRV On-Resistance,<br>High Side                                         | R <sub>NDRV_H</sub>    | I <sub>SINK</sub> = 30mA                   |                                    |                          | 1.5  | 3                        | Ω     |

| NDRV On-Resistance,<br>Low Side                                          | R <sub>NDRV_L</sub>    | I <sub>SOURCE</sub> = 30mA                 |                                    |                          | 0.8  | 1.6                      | Ω     |

| NDRV Rise Time                                                           | t <sub>NDRV_R</sub>    | C <sub>LOAD</sub> = 1nF, (Note             | <u>= 2</u> )                       |                          | 8    |                          | ns    |

| NDRV Fall Time                                                           | t <sub>NDRV</sub> F    | C <sub>LOAD</sub> = 1nF, (Note             | <u>e 2</u> )                       |                          | 8    |                          | ns    |

| SLOPE COMPENSATION                                                       | N =                    | •                                          |                                    |                          |      |                          | •     |

| Peak Slope-<br>Compensation Current-<br>Ramp Magnitude                   | I <sub>SLOPE</sub>     | Current ramp added                         | I to CS                            | 42                       | 50   | 58                       | μА    |

| CURRENT-SENSE COM                                                        | PARATOR                |                                            |                                    |                          |      |                          | •     |

| Current-Limit Threshold                                                  | V <sub>CL MAX</sub>    | V <sub>CL</sub> = V <sub>CS</sub> + slope- | compensation voltage               | 385                      | 420  | 455                      | mV    |

| Current-Limit Threshold<br>During Low-Voltage<br>Operation, Low Setting  | VCLCC_MAX              | Register bit ILIM = 0 switched to BOOST    | ), V <sub>CC</sub> regulator input | 565                      | 600  | 635                      | mV    |

| Current-Limit Threshold<br>During Low-Voltage<br>Operation, High Setting | VCLCC_MAX              | Register bit ILIM bit input switched to B0 |                                    | 785                      | 825  | 856                      | mV    |

| ERROR AMPLIFIER                                                          |                        |                                            | -                                  |                          |      |                          | 1     |

| OUT_ Regulation, High<br>Threshold                                       | V <sub>OUT_H</sub>     | V <sub>OUT</sub> _ falling                 |                                    | 0.95                     | 1.03 | 1.1                      | V     |

| OUT_ Regulation, Low Threshold                                           | V <sub>OUT_L</sub>     | V <sub>OUT</sub> _ rising                  |                                    | 0.7                      | 0.78 | 0.85                     | V     |

| Transconductance                                                         | GM                     |                                            |                                    | 420                      | 600  | 840                      | μS    |

| COMP Sink Current                                                        | I <sub>COMP_SINK</sub> | V <sub>COMP</sub> = 2V                     |                                    | 200                      | 480  | 800                      | μA    |

| COMP Source Current                                                      | ICOMP_SRC              | V <sub>COMP</sub> = 1V                     |                                    | 200                      | 480  | 800                      | μA    |

| LED CURRENT SINKS                                                        |                        |                                            |                                    |                          |      |                          |       |

| IREF Voltage                                                             | V <sub>IREF</sub>      | R <sub>IREF</sub> = 49.9kΩ                 |                                    | 1.22                     | 1.25 | 1.28                     | V     |

| IREF Resistor<br>IREFOOR Fault<br>Detection Range                        | R <sub>IREFOOR</sub>   | Outside this range a                       | a fault will be detected           | 27.5                     |      | 83.5                     | kΩ    |

|                                                                          |                        | $R_{IREF} = 49.9k\Omega$                   | 120mA setting                      | 115                      | 120  | 125                      |       |

| OUT Output Compat                                                        | la.                    | D = 40.0k0                                 | 100mA setting                      | 96                       | 100  | 104                      | ]^    |

| OUT_ Output Current                                                      | lout_                  | $R_{IREF} = 49.9k\Omega$                   | 50mA setting                       | 48                       | 50   | 52                       | mA    |

|                                                                          |                        | R <sub>IREF</sub> = 40.2kΩ                 | 150mA setting                      | 143                      | 149  | 155                      |       |

$(V_{IN}$  = 12V, R<sub>RT</sub> = 76.8k $\Omega$ , C<sub>VCC</sub> = 2.2 $\mu$ F, T<sub>A</sub> = T<sub>J</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted. (<u>Note 1</u>))

| PARAMETER                                               | SYMBOL                              | CONDITIONS                                                                   | MIN  | TYP  | MAX  | UNITS |

|---------------------------------------------------------|-------------------------------------|------------------------------------------------------------------------------|------|------|------|-------|

| Channel-to-Channel                                      |                                     | I <sub>OUT</sub> _ = 120mA                                                   | -2   |      | +2   | - %   |

| Matching                                                | lout_m                              | I <sub>OUT</sub> _ = 50mA                                                    | -2.5 |      | +2.5 | 70    |

| Total OUT_ Leakage<br>Current to IN                     | IOUTLEAK                            | V <sub>OUT</sub> = 48V, V <sub>DIM</sub> = 0V, all OUT_ are shorted together |      | 8    | 15   | μΑ    |

| OUT_ Current, Rise<br>Time                              | t <sub>IOUT_R</sub>                 | 10% to 90% I <sub>OUT</sub> _, ( <i>Note 2</i> )                             |      | 150  |      | ns    |

| OUT_ Current, Fall Time                                 | t <sub>IOUT_F</sub>                 | 90% to 10% I <sub>OUT</sub> _, ( <i>Note 2</i> )                             |      | 50   |      | ns    |

| DIM Sampling<br>Frequency                               | f <sub>DIM</sub>                    |                                                                              |      | 20   |      | MHz   |

| OVERVOLTAGE AND UN                                      | NDERVOLTAGE                         | PROTECTION                                                                   |      |      |      |       |

| BSTMON Overvoltage-<br>Trip Threshold                   | V <sub>BSTMONTH</sub>               | V <sub>BSTMON</sub> rising                                                   | 1.18 | 1.23 | 1.28 | V     |

| BSTMON Hysteresis                                       | V <sub>BSTMONHY</sub>               |                                                                              |      | 70   |      | mV    |

| BSTMON Input Bias<br>Current                            | I <sub>BSTMON</sub>                 | 0V < V <sub>BSTMON</sub> < 1.3V                                              | -500 |      | +500 | nA    |

| BSTMON Undervoltage-<br>Detection Threshold,<br>Rising  | V <sub>BSTMONUVR</sub>              |                                                                              | 0.47 | 0.5  | 0.53 | V     |

| BSTMON Undervoltage-<br>Detection Threshold,<br>Falling | V <sub>BSTMONUV</sub> F             | NGATE latched off                                                            | 0.4  | 0.43 | 0.46 | V     |

| BSTMON Undervoltage-<br>Blanking Time                   | t <sub>BSTMON_BL</sub>              | After ENA is written to '1', Register bit FAST_SS = 0                        | 47.8 | 52   | 56.2 | ms    |

| BSTMON Undervoltage-<br>Detection Delay                 | t <sub>BSTMON_UV</sub>              | BSTMON falling                                                               | 4    | 10   | 18   | μs    |

| LOGIC INPUT AND OUT                                     | PUTS                                |                                                                              |      |      |      |       |

| EN, SDA, SCL, DIM<br>Input, Logic-High                  | V <sub>IH</sub>                     |                                                                              | 2.1  |      |      | V     |

| EN, SDA, SCL, DIM<br>Input, Logic-Low                   | V <sub>IL</sub>                     |                                                                              |      |      | 0.8  | V     |

| EN Input Current                                        | I <sub>EN</sub>                     | V <sub>EN</sub> = 12V                                                        |      | 7.25 | 12   | μA    |

| SDA, SCL Input Current                                  | I <sub>SDA</sub> , I <sub>SCL</sub> | V <sub>SDA</sub> = V <sub>SCL</sub> = 5V                                     | -1   |      | +1   | μA    |

| DIM Input Frequency                                     | f <sub>DIM</sub> _IN                |                                                                              | 90   |      |      | Hz    |

| DIM Input Pullup<br>Current                             | I <sub>DIM</sub>                    |                                                                              |      | 5    |      | μА    |

| FSEN Input, Logic High                                  | V <sub>FSEN_TH</sub>                | FSEN Rising                                                                  | 2.2  |      |      | V     |

| FSEN Input Current                                      | I <sub>FSEN</sub>                   | V <sub>FSEN</sub> = 1V                                                       | 14.2 | 15   | 15.8 | μA    |

| SDA, FLTB Output Low<br>Voltage                         | V <sub>OL</sub>                     | Sinking 3mA                                                                  |      |      | 0.4  | V     |

| FLTB Output-Leakage<br>Current                          | I <sub>FLTB_LKG</sub>               | V <sub>FLTB</sub> = 5.5V                                                     | -1   |      | +1   | μА    |

$(V_{IN}$  = 12V, R<sub>RT</sub> = 76.8k $\Omega$ , C<sub>VCC</sub> = 2.2 $\mu$ F, T<sub>A</sub> = T<sub>J</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted. (<u>Note 1</u>))

| PARAMETER                             | SYMBOL                 | CONDITIONS                                                                  | MIN  | TYP   | MAX  | UNITS |

|---------------------------------------|------------------------|-----------------------------------------------------------------------------|------|-------|------|-------|

| NGATE OUTPUT                          | I                      |                                                                             |      |       |      | 1     |

| NGATE Source Current                  | I <sub>NGATE_SRC</sub> | V <sub>IN</sub> = 12V, V <sub>NGATE</sub> = V <sub>IN</sub> - 7V            | 37.5 | 50    | 62.5 | μA    |

| NGATE Sink Current                    | INGATE_SINK            | V <sub>IN</sub> = 12V, V <sub>NGATE</sub> = V <sub>IN</sub> + 7V            | 4.5  | 9     |      | mA    |

| NGATE Output Voltage                  | V <sub>NGATE</sub>     | Above V <sub>IN</sub> , 4.5V < V <sub>IN</sub> < 36V                        | 4.5  | 7.5   | 11   | V     |

| NGATE Start Delay                     | t <sub>NGATE</sub>     | Delay between NGATE charge-pump turning on and the boost converter starting |      | 2     | 2.2  | ms    |

| LED FAULT DETECTION                   | İ                      |                                                                             |      |       |      |       |

|                                       |                        | Register bits SLDET[1:0] = 11, Rising                                       | 7.5  | 8     | 8.5  |       |

| LED Short-Detection Threshold         | V <sub>LED_THR</sub>   | Register bits SLDET[1:0] = 10, Rising                                       | 5.6  | 6     | 6.4  | V     |

| THESHOL                               | _                      | Register bits SLDET[1:0] = 01, Rising                                       | 2.8  | 3     | 3.25 | 7     |

| Short-Detection<br>Comparator Delay   | <sup>t</sup> LEDS      |                                                                             |      | 6.5   |      | μs    |

| OUT_ Check LED<br>Source Current      | IOUT_CKLED             |                                                                             | 50   | 60    | 70   | μA    |

| OUT_ Short to GND Detection Threshold | V <sub>OUT_GND</sub>   | Before boost converter startup                                              | 250  | 300   | 365  | mV    |

| OUT_ Unused-Detection<br>Threshold    | V <sub>OUT_UN</sub>    |                                                                             | 1.15 | 1.25  | 1.35 | V     |

| OUT_ Open-LED<br>Detection Threshold  | V <sub>OUT_OPEN</sub>  | During operation                                                            | 250  | 300   | 365  | mV    |

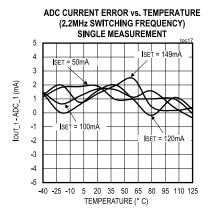

| ANALOG-TO-DIGITAL C                   | ONVERTER               |                                                                             |      |       |      |       |

| ADC Measurement Resolution            | ADC <sub>BIT</sub>     | ( <u>Note 2</u> )                                                           |      | 8     |      | Bits  |

| Total Measurement<br>Error, Current   | E_ADC <sub>OUT</sub>   | 150mA setting                                                               | -8   |       | +8   | mA    |

| Total Measurement<br>Error, BSTMON    | E_ADC <sub>BSTMO</sub> | V <sub>BSTMON</sub> = 1V                                                    | -70  |       | 70   | mV    |

| ADC Gain Error                        | ADC <sub>GAIN</sub>    | 150mA setting                                                               | -4   |       | +6   | %     |

| ADC Offset Error                      | ADC <sub>OFF</sub>     | 150mA setting                                                               | -4   |       | +4   | LSB   |

| Measurement                           | LCD                    | $R_{IREF}$ = 49.9k $\Omega$                                                 |      | 0.505 |      | A     |

| Resolution, Current                   | LSB <sub>OUT</sub>     | R <sub>IREF</sub> = 40.2kΩ                                                  |      | 0.625 |      | mA    |

| Measurement<br>Resolution, BSTMON     | LSB <sub>BSTMON</sub>  |                                                                             |      | 5.1   |      | mV    |

| THERMAL SHUTDOWN                      |                        |                                                                             |      |       |      |       |

| Thermal Warning                       | T <sub>WARN</sub>      |                                                                             |      | 125   |      | °C    |

| Thermal-Shutdown<br>Threshold         | T <sub>SHDN</sub>      |                                                                             |      | 165   |      | °C    |

| Thermal-Shutdown<br>Hysteresis        | T <sub>SHDN_HY</sub>   |                                                                             |      | 15    |      | °C    |

## **Electrical Characteristics (continued)**

$(V_{IN}$  = 12V, R<sub>RT</sub> = 76.8k $\Omega$ , C<sub>VCC</sub> = 2.2 $\mu$ F, T<sub>A</sub> = T<sub>J</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted. (*Note 1*))

| PARAMETER                                            | SYMBOL              | CONDITIONS                                              | MIN | TYP | MAX | UNITS |

|------------------------------------------------------|---------------------|---------------------------------------------------------|-----|-----|-----|-------|

| I <sup>2</sup> C INTERFACE                           |                     |                                                         | •   |     |     | 1     |

| Serial-Clock Frequency                               | f <sub>SCL</sub>    |                                                         |     |     | 400 | kHz   |

| Bus-Free Time Between<br>STOP and START<br>Condition | t <sub>BUF</sub>    |                                                         | 1.3 |     |     | μs    |

| START Condition Setup<br>Time                        | <sup>t</sup> su:sta |                                                         | 0.6 |     |     | μs    |

| START Condition Hold<br>Time                         | t <sub>HD:STA</sub> |                                                         | 0.6 |     |     | μs    |

| STOP Condition Setup<br>Time                         | tsu:sto             |                                                         | 0.6 |     |     | μs    |

| Clock Low Period                                     | t <sub>LOW</sub>    |                                                         | 1.3 |     |     | μs    |

| Clock High Period                                    | tHIGH               |                                                         | 0.6 |     |     | μs    |

| Data Setup Time                                      | t <sub>SU:DAT</sub> |                                                         | 100 |     |     | ns    |

| Data Hold Time                                       | t <sub>HD:DAT</sub> | Measured from 50% point on SCL falling edge to SDA edge | 0   |     |     | μs    |

| Pulse Width of Spike<br>Suppressed                   | t <sub>SP</sub>     |                                                         |     | 50  |     | ns    |

Note 1: Limits are 100% tested at  $T_A$  = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.

Note 2: Guaranteed by design.

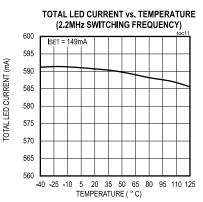

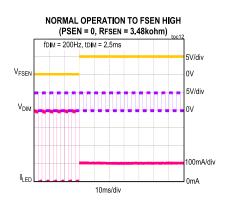

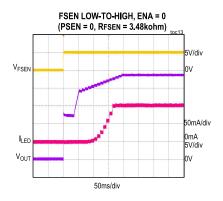

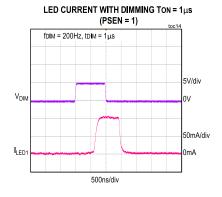

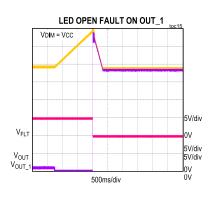

## **Typical Operating Characteristics**

$(V_{IN} = 12V, T_A = 25^{\circ}C \text{ unless otherwise noted.})$

## **Typical Operating Characteristics (continued)**

$(V_{IN} = 12V, T_A = 25^{\circ}C \text{ unless otherwise noted.})$

## **Pin Configuration**

## MAX25014

## **Pin Description**

| PIN | NAME                                                                                                                                                                                 | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | IN                                                                                                                                                                                   | Bias Supply Input. Connect a 2.5V to 36V supply to IN. Bypass IN to GND with a 2.2µF ceramic capacitor.                                                                                                                                                                                                                                                                                  |

| 2   | EN                                                                                                                                                                                   | Enable Input. Connect EN to ground to shut down the device. Connect EN to logic-high or IN for normal operation. EN has an internal clamp at 3V; when EN is above this voltage, an input current of $(V_{EN} - 3V)/1.2M\Omega$ will flow.                                                                                                                                                |

| 3   | 3 OUT1 LED String Cathode Connection 1. OUT1 is the open-drain output of the linear current si controls the current through the LED string connected to OUT1. OUT1 sinks up to 150m/ |                                                                                                                                                                                                                                                                                                                                                                                          |

| 4   | OUT3                                                                                                                                                                                 | LED String Cathode Connection 3. OUT3 is the open-drain output of the linear current sink, which controls the current through the LED string connected to OUT3. OUT3 sinks up to 150mA.                                                                                                                                                                                                  |

| 5   | NGATE                                                                                                                                                                                | Gate Connection for External Series nMOSFET driven by the internal charge pump.                                                                                                                                                                                                                                                                                                          |

| 6   | FLTB                                                                                                                                                                                 | Open-Drain Fault Output. FLTB asserts low when any diagnostic bit that is not masked is asserted. See the <i>Fault Protection</i> section for more details. Connect a pullup resistor from FLTB to V <sub>CC</sub> or to a logic supply of maximum 5V.                                                                                                                                   |

| 7   | SCL                                                                                                                                                                                  | I <sup>2</sup> C Clock Input. Connect a pullup resistor from SCL to the logic supply.                                                                                                                                                                                                                                                                                                    |

| 8   | SDA                                                                                                                                                                                  | I <sup>2</sup> C Data I/O Pin. Connect a pullup resistor from SDA to the logic supply.                                                                                                                                                                                                                                                                                                   |

| 9   | LEDGND                                                                                                                                                                               | LED Ground. LEDGND is the return-path connection for the linear current sinks. Connect GND, LEDGND, and PGND at a single point.                                                                                                                                                                                                                                                          |

| 10  | RT                                                                                                                                                                                   | Oscillator-Timing Resistor Connection. Connect a timing resistor (R <sub>RT</sub> ) from RT to GND to program the switching frequency. Also connect a 100pF capacitor from RT to GND. To synchronize the switching frequency with an external clock, apply an AC-coupled external clock at RT. When the oscillator is synchronized with the external clock, spread spectrum is disabled. |

## **Pin Description (continued)**

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11  | GND             | Signal Ground. GND is the current return-path connection for the low-noise analog signals. Connect GND, LEDGND, and PGND at a single point.                                                                                                                                                                                                                                                                |

| 12  | IREF            | LED Current-Reference Input. Connect a resistor ( $R_{IREF}$ = 40.2k $\Omega$ ) from IREF to GND to set the reference current. Place the resistor as close as possible to the pin using the shortest possible trace.                                                                                                                                                                                       |

| 13  | DIM             | PWM Dimming Input. Apply a PWM signal to DIM for LED dimming control unless $I^2C$ dimming is used. Connect DIM to $V_{CC}$ if dimming control is not used (100% brightness). Connect DIM to GND if dimming will be controlled through $I^2C$ .                                                                                                                                                            |

| 14  | FSEN            | Fail-Safe Enable Pin. When FSEN is taken high the boost converter is enabled and the outputs OUT1–OUT4 are enabled at 100% duty cycle, independently of all register settings. Connect a resistor from FSEN to GND to set the LED current when FSEN is active and the device I <sup>2</sup> C address (see <i>FSEN Pin Function</i> ). If the FSEN function is not needed connect the pin directly to GND. |

| 15  | OUT4            | LED String Cathode Connection 4. OUT4 is the open-drain output of the linear current sink that controls the current through the LED string connected to OUT4. OUT4 sinks up to 150mA.                                                                                                                                                                                                                      |

| 16  | OUT2            | LED String Cathode Connection 2. OUT2 is the open-drain output of the linear current sink that controls the current through the LED string connected to OUT2. OUT2 sinks up to 150mA.                                                                                                                                                                                                                      |

| 17  | COMP            | Switching-Converter Compensation Input. Connect the compensation network from COMP to GND for current-mode control (see the <u>Feedback Compensation</u> section).                                                                                                                                                                                                                                         |

| 18  | cs              | Current-Sense Input for the Switching Regulator. A sense resistor connected from the source of the external power MOSFET to PGND sets the switching current limit. A resistor connected between the source of the power MOSFET and CS sets the slope-compensation ramp rate (see the <u>Slope Compensation and Current-Sense Resistor</u> section).                                                        |

| 19  | BSTMON          | Overvoltage Threshold-Adjust Input. Connect a resistor-divider from the switching converter output to BSTMON and GND. The OVP comparator reference is internally set to 1.23V.                                                                                                                                                                                                                             |

| 20  | PGND            | Power Ground. PGND is the switching current-return-path connection. Connect GND, LEDGND, and PGND at a single point.                                                                                                                                                                                                                                                                                       |

| 21  | NDRV            | Switching nMOSFET Gate-Driver Output. Connect NDRV to the gate of the external switching-power nMOSFET using a $10\Omega$ to $22\Omega$ resistor. This decreases the slew rate of the gate driver and reduces switching noise.                                                                                                                                                                             |

| 22  | V <sub>CC</sub> | 5V Regulator Output. Bypass $V_{CC}$ to GND with a $1\mu F$ (min) ceramic capacitor as close as possible to the device.                                                                                                                                                                                                                                                                                    |

| 23  | BOOST           | Connect to the Output of the Boost Converter. This pin serves as the input to the V <sub>CC</sub> regulator when IN drops below 5.8V.                                                                                                                                                                                                                                                                      |

| 24  | IN              | Bias Supply Input. Connect a 2.5V to 36V supply to IN. Bypass IN to GND with a 2.2µF ceramic capacitor.                                                                                                                                                                                                                                                                                                    |

| _   | EP              | Exposed Pad. Connect EP to a large-area contiguous copper ground plane for effective power dissipation. Do not use as the main IC ground connection. EP must be connected to GND.                                                                                                                                                                                                                          |

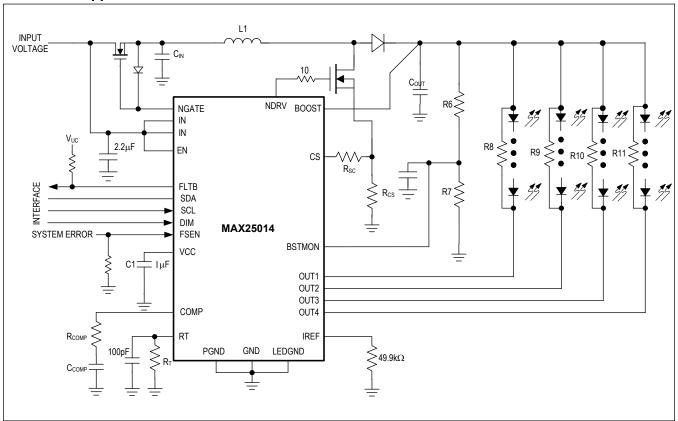

## **Functional Diagrams**

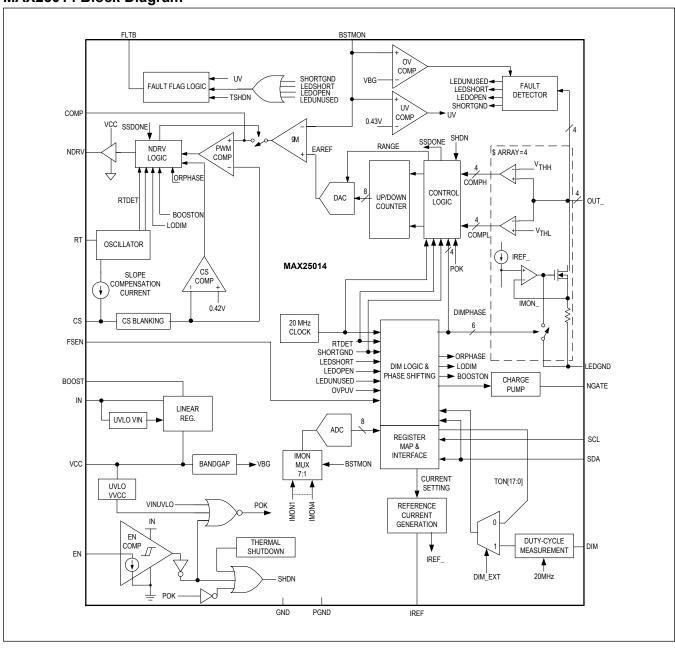

## MAX25014 Block Diagram

## **Detailed Description**

The MAX25014 is a 4-channel backlight driver IC with boost controller for automotive displays. The integrated current outputs can sink up to 150mA LED current each. The device accepts a wide 2.5V to 36V input voltage range. The IC provides load-dump voltage protection up to 40V in automotive applications and incorporates three major blocks: a DC-DC controller with peak current-mode control to implement a boost or SEPIC-type switched-mode power supply, a 4-channel LED driver with 45mA to 150mA constant-current sink capability per channel, and a control block with I<sup>2</sup>C interface.

The internal current-mode switching DC-DC controller supports boost or SEPIC topologies and operates in the 400kHz to 2.2MHz frequency range. Integrated spread spectrum helps reduce EMI. An adaptive output-voltage-control scheme minimizes power dissipation in the LED current-sink paths.

The device features I<sup>2</sup>C-controlled pulse-width-modulation (PWM) dimming and hybrid dimming. In either case, the minimum pulse width is 500ns. Phase-shifted dimming of the strings is incorporated for lower EMI.

#### **Enable**

The internal regulator is enabled when the EN pin is high. To shut down the device drive EN low, and the current consumption is reduced to 8µA (max).

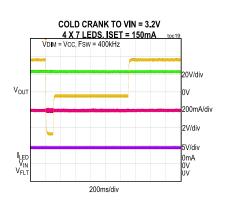

## **Low-Voltage Operation**

After the boost soft-start is completed the MAX25014 continues to operate with IN voltages lower than 5V while maintaining 5V drive for the external MOSFET at NDRV. When the IN voltage drops to  $V_{SWITCHOVER}$  the  $V_{CC}$  regulator switches its input from IN to BOOST, the output of the boost converter. Switchover occurs as long as the voltage on BSTMON is above the undervoltage lockout level of 430mV and BOOST is greater than IN. When IN returns to a voltage above 5.95V the  $V_{CC}$  regulator resumes operation from IN. Bypass IN and BOOST with ceramic capacitors of value 2.2uF placed close to the respective pins.

At very low input voltages the efficiency of the boost converter reduces and the input current can reach very high levels as a consequence. When the input voltage falls below  $V_{SWITCHOVER}$  the boost converter current limit is automatically increased to 600mV or 825mV (typ), the value is set using the ILIM bit in the SETTING register. The external boost converter components must be selected for worst-case operation. Alternatively, it may be necessary to reduce the output power at low input voltages. If the voltage at IN drops below the level programmed by the UV\_SEL bit in register DISABLE the boost converter is disabled.

## **Undervoltage Lockout**

The IC features three undervoltage lockouts (UVLOs) that monitor the input voltage at IN and the output of the internal LDO regulator at  $V_{CC}$ . The device turns on when EN is taken high if both IN and  $V_{CC}$  are higher than their respective UVLO thresholds.

#### **Current-Mode DC-DC Controller**

The IC has a constant-frequency, current-mode controller designed to drive the LEDs in a boost, SEPIC, or coupled-inductor buck-boost configuration. The IC features multi-loop control to regulate the peak current in the inductor, as well as the voltage across the LED current sinks, to minimize power dissipation.

The switching frequency can be programmed over the 400kHz to 2.2MHz range using a resistor connected from RT to GND.

Adjustable slope compensation is provided to compensate for subharmonic oscillations that occur at above 50% duty cycles in continuous-conduction mode.

The external MOSFET is turned on at the beginning of every switching cycle. The inductor current ramps up linearly until it is turned off at the peak current level set by the feedback loop. The peak inductor current is sensed from the voltage across the current-sense resistor ( $R_{CS}$ ) connected from the source of the external MOSFET to ground with the addition of the slope-compensation voltage due to  $R_{SC}$ .

The IC features leading-edge blanking to suppress the MOSFET switching noise. A PWM comparator compares the current-sense voltage plus the slope-compensation signal with the output of the transconductance error amplifier. The controller turns off the MOSFET when the voltage at CS exceeds the error amplifier's output voltage, which is also the voltage on the COMP pin. This process repeats every switching cycle to achieve peak current-mode control.

In addition to the peak current-mode-control loop, the IC has two other feedback loops for control. The converter output voltage is sensed through the BSTMON input, which goes to the inverting input of the error amplifier. The other feedback comes from the OUT\_ current sinks. This loop controls the headroom of the current sinks to minimize total power dissipation while still ensuring accurate LED current matching. Each current sink has a window comparator with a low threshold of 0.78V and a high threshold of 1.03V. The outputs of these comparators control an up/down counter. The up/down counter is updated on every falling edge of the DIM input and drives an 8-bit DAC that sets the reference to the error amplifier. When dimming is set to 100%, the counter is updated at intervals of 10ms.

## **Output Undervoltage Protection**

At the end of the boost converter soft-start, an undervoltage threshold is activated on the output of the DC-DC converter, which is set at 430mV. If the BSTMON pin is below 430mV after the soft-start period of the DC-DC converter, the converter is turned off and the NGATE output discharges the gate of the external nMOSFET. The FLTB pin is asserted low whenever undervoltage protection is activated. The ENA bit in the ISET (0x02) register must be toggled to start up again once the fault condition has been removed. Alternatively, the EN pin or power supply can be toggled.

## 8-Bit Digital-to-Analog Converter

The error amplifier's reference input is controlled with an 8-bit digital-to-analog converter (DAC). The DAC output is ramped up slowly during startup to implement a soft-start function (see the <u>Startup Sequence</u> section). During normal operation, the DAC output range is limited to 0.6V to 1.25V. Because the DAC output is limited to no less than 0.6V during normal operation, the overvoltage threshold for the output should be set to a value less than twice the minimum LED forward voltage. The DAC LSB determines the minimum step-in output voltage according to the equation below.

#### Equation 1:

VSTEP MIN = VDAC LSB × AOVP

where:

V<sub>STEP MIN</sub> = Minimum output-voltage step

V<sub>DAC LSB</sub> = DAC least significant bit size (2.5mV)

$A_{OVP}$  = BSTMON resistor-divider gain (1 + R6/R7)

#### **FSEN Pin Function**

The FSEN pin can be used to enable the device in situations where I<sup>2</sup>C control is temporarily impossible or the interface has stopped functioning (even if the ENA bit is not set). When FSEN is taken high, the boost converter is turned on and the current sinks are enabled at 100% duty cycle. When FSEN returns low, the values programmed in the I<sup>2</sup>C registers are applied at the beginning of the next dimming cycle.

The OUT\_ current, when FSEN is high, is set by a resistor from FSEN to GND according to  $\underline{\text{Table 1}}$ . The resistor value is read at power-up and the set OUT\_ current value and I<sup>2</sup>C address cannot subsequently be changed.

If FSEN is not used connect the pin to GND unless the alternative I<sup>2</sup>C address is to be used.

## **Table 1. FSEN RESISTOR VALUES**

| FSEN RESISTOR VALUE (kΩ) | OUT_ CURRENT (mA)  | 7-BIT I <sup>2</sup> C ADDRESS |

|--------------------------|--------------------|--------------------------------|

| 0                        | Fail-safe disabled | 0x69                           |

| 3.48                     | 25                 | 0x69                           |

| 7.15                     | 25                 | 0x6F                           |

| 12                       | 50                 | 0x69                           |

| 18.7                     | 50                 | 0x6F                           |

**Table 1. FSEN RESISTOR VALUES (continued)**

| FSEN RESISTOR VALUE (kΩ) | OUT_ CURRENT (mA) | 7-BIT I <sup>2</sup> C ADDRESS |

|--------------------------|-------------------|--------------------------------|

| 27.4                     | 75                | 0x69                           |

| 39                       | 75                | 0x6F                           |

| 59                       | 100               | 0x69                           |

| 84.5                     | 100               | 0x6F                           |

## **Dimming**

Dimming can be performed either using an external PWM signal applied to the DIM pin, or by programming the desired dimming level through I<sup>2</sup>C.

When using internal dimming, set the DIM\_EXT bit in the IMODE register (0x03) to 1 (the default value is 0, the DIM pin is the default dimming input) before setting the ENA bit to turn on the backlight. The signal on the DIM pin is sampled with a 20MHz internal clock.

In internal dimming, write up to 18 bits to the TON\_[17:0] bits (see registers 0x04 to 0x0C in the *Register Map* section). The value to be written is calculated using the following formula.

#### Equation 2:

$$TON = \frac{t_{ON}}{50 \text{ns}}$$

where  $t_{ON}$  is the desired on-time. If a value is written that corresponds to an on-time less than 500ns ( $\leq$  0x09), the corresponding OUT\_ will stay on for 500ns. If the value written is longer than the dimming period, the output will be on at 100% duty cycle. To set zero current in any channel, write all the corresponding TON bits to 0.

## **Hybrid Dimming**

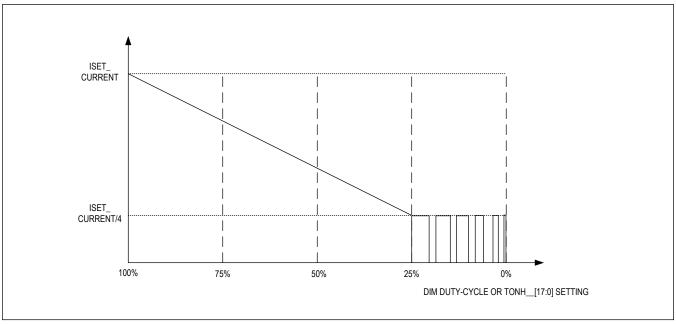

In hybrid dimming mode, the external LEDs are dimmed by first reducing their current as the dimming duty-cycle decreases from 100% (see <u>Figure 1</u>). At the crossover level set by the HDIM\_THR\_1\_0[1:0] bits dimming transitions to PWM dimming where the LED current is chopped. To select hybrid dimming, set the HDIM bit in the IMODE (0x03) register and select the desired crossover level between analog and PWM dimming using the HDIM\_THR\_1\_0[1:0] bits in the same register. Depending on the DIM\_EXT bit, the device functions in one of two ways:

- 1. (DIM\_EXT = 1) measures the duty cycle on the DIM pin and translates it into a combined LED current value and PWM setting.

- 2. (DIM\_EXT = 0) takes the 18-bit value from the TON\_ registers and translates it into a combined LED current value and PWM setting.

**Note:** When hybrid dimming is used with an internal dimming setting (DIM\_EXT = 0), only the value TON1[17:0] is used. It is not possible to have individual dimming settings for each of the channels in this mode but the TON\_ settings for all the channels must be non-zero.

In summary, there are four possible dimming modes:

- 1. External PWM dimming.

- 2. Internal PWM dimming with the pulse-width set through I<sup>2</sup>C and the PWM frequency generated internally.

- 3. External hybrid dimming with a PWM signal applied to the DIM pin; the pulsed current on the OUT\_ pins follows the DIM frequency.

- 4. Internal hybrid dimming with the dimming ratio set through I<sup>2</sup>C and the PWM frequency generated internally. The TON1[17:0] setting is valid for all channels. Any channels with a TON [17:0] setting of 0 will be turned off.

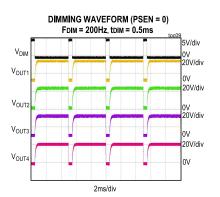

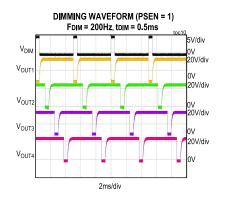

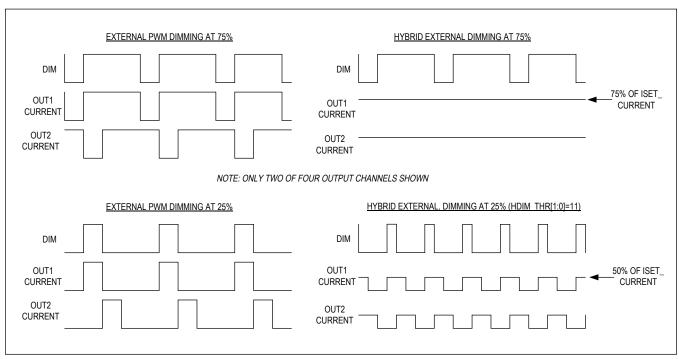

[[Hybrid Dimming Operation]] illustrates the difference between standard and hybrid dimming with phase-shifting enabled.

## **Hybrid Dimming Operation**

Figure 1. Hybrid Dimming Operation with HDIM[1:0] = 10 (25%)

## **Hybrid Dimming Operation Modes**

Figure 2. Hybrid Dimming Operation Modes

## **Low-Dimming Mode**

The IC's operation changes at very narrow dimming pulses to ensure a consistent dimming response of the LEDs. If the dimming on-time (from either the DIM input or the TON\_ value, depending on which is selected) is lower than 50µs (typ), the device enters low-dimming mode. In this state, the converter switches continuously and LED short detection is disabled. When the DIM input is greater than 51µs (typ) the device goes back into normal operation, enabling the short-LED detection and switching the power FET only when the effective dimming signal is high. OUT\_ current monitoring does not operate in low-dim mode although the BSTMON voltage can still be measured.

When internal dimming is used some channels may be in low-dim mode while others are not. If any channel is in low-dim mode, the boost converter runs continuously.

## **Phase-Shift Dimming**

When the PSEN bit in register 0x02 is set phase shifting of the LED strings is enabled. The device automatically sets the phase shift between strings to 90, 120, or 180 degrees, depending on the number of strings enabled.

## **Disabling Individual Strings**

To disable an unused LED string, connect the unused OUT\_ to ground through a  $12k\Omega$  resistor, or set the corresponding DIS\_ bit to 1 in the DISABLE (0x13) register before the ENA bit is set. During startup, the device sources  $60\mu$ A (typ) current through the OUT\_ pins and measures the corresponding voltage. For the string to be properly disabled, the OUT\_ voltage should measure between 365mV and 1.15V during this check. 365mV is the maximum threshold for the OUT\_ short-to-ground check and 1.15V is the minimum unused string-detection threshold.

**Note:** When disabling unused strings, it is necessary to start by disabling the highest-numbered current sinks first (e.g., if two strings need to be disabled, disable OUT4 and OUT3. Do not disable any two strings at random). During normal operation, strings can be selectively turned off by changing the corresponding TON\_ setting to 0. This is only possible when internal dimming is used (not when using the DIM input pin).

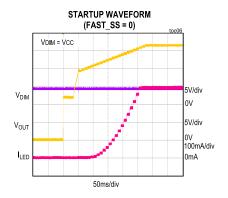

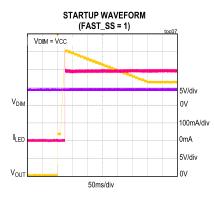

#### **Startup Sequence**

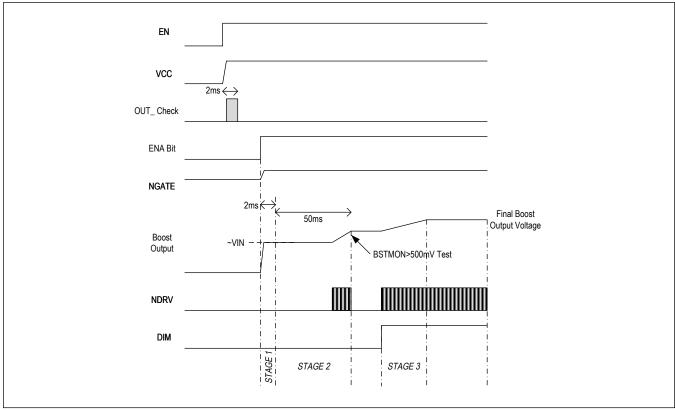

When the EN pin is taken high (assuming the IN voltage is above its undervoltage-lockout value), the internal regulator and the  $I^2C$  interface are turned on and the device checks the OUT\_ channels. If any of the OUT\_ pins are detected as shorted to GND, the boost converter does not start (to avoid possible damage) and the corresponding OUT\_SG bit(s) are set. The device also detects and disconnects any unused current-sink channels connected to GND by means of a  $12k\Omega$  resistor. Alternatively, individual channels can be disabled using the DIS[4:1] bits. The total duration of this phase of the startup is 2ms (max). After this phase, the  $I^2C$  interface can be used and the device registers can be written. The ENA bit should be set to 1 to enable the boost and subsequently the OUT\_ current sinks. Before setting the ENA bit to 1 fast soft-start can be chosen by setting the FAST\_SS bit to 1. When the ENA bit is set high, the startup sequence occurs in three stages:

#### Stage 1

Once the ENA bit is high, the controller begins the soft-start of the boost. First, the driver of the external nMOSFET is turned on. A typical current of 50µA is provided by the internal charge pump at the NGATE pin to turn on the external nMOSFET. Do not connect anything other than the MOSFET gate to the NDRV pin. After a 2ms timeout expires, Stage 2 of the startup begins.

#### Stage 2

After the checks in Stage 1 have been performed, the converter starts switching and the output begins to ramp. The DAC reference to the error amplifier is stepped up 1 bit at a time until the voltage at BSTMON reaches 600mV (or 1.1V when the FAST\_SS bit is set to 1). This stage duration is fixed at approximately 50ms (typ) or 23ms when the FAST\_SS bit is set to 1. The BSTMON pin is then sampled, and if its voltage is less than 500mV (typ), FLTB is asserted low, the power converter is turned off, the external nMOSFET on NGATE is turned off, and they all remain off until the ENA bit, input power, or EN pin is toggled.

## Stage 3

The third stage begins once Stage 2 is complete and the DIM input goes high (with DIM\_EXT = 1), or internal dimming is enabled by setting a PWM value greater than 0 on any of the channels. During Stage 3, the output of the converter is adjusted until the minimum OUT\_ voltage falls within 0.78V (typ) and 1.03V (typ) comparator limits. The output adjustment is again controlled by the DAC, which provides the reference for the error amplifier. The DAC output is updated on each rising edge of the DIM input pin (or internal dimming signal). If the DIM input (or the internal dimming signal when DIM EXT = 1) is at 100% duty cycle (DIM = high), the DAC output is updated once every 10ms.

The total soft-start time can be calculated using Equation 3.

## **Equation 3:**

$$t_{SS} = 52\text{ms} + \frac{(V_{\text{LED}} + 0.91) - (0.6 \times A_{\text{OVP}})}{f_{\text{DIM}} \times 0.01 \times A_{\text{OVP}}}$$

where:

tss = Total soft-start time

52ms = Fixed Stage 1 + Stage 2 duration

V<sub>LED</sub> = Total forward voltage of the LED strings

0.91V = Midpoint of the window comparator

f<sub>DIM</sub> = Dimming frequency (use 100Hz for f<sub>DIM</sub> when input duty cycle is 100%)

0.01V = 4 times the 2.5mV LSB of the DAC

A<sub>OVP</sub> = Gain of the BSTMON resistor-divider or 1 + R6/R7

When the FAST\_SS bit is set to 1 the soft-start is accelerated and the final value of the voltage on the BSTMON pin is 1.1V. The equation for the total soft-start time then becomes:

$$t_{SS} = 25 \text{ms} + \frac{1.1 \times A_{OVP} - (V_{LED} + 0.91)}{f_{DIM} \times 0.01 \times A_{OVP}}$$

After the soft-start period, a fault is detected whenever the BSTMON pin falls below 430mV (typ). When this occurs, the power converter is latched off and the NGATE output discharges the gate of the external nMOSFET, disconnecting the input voltage from the boost converter. The FLTB pin is asserted low whenever the undervoltage protection is activated. Cycling the ENA bit, EN pin, or the supply is required to start up again, once the fault condition has been removed.

## **Boost Startup**

Figure 3. Boost Startup Waveform with FAST\_SS = 0

#### Oscillator Frequency/External Synchronization

The internal oscillator frequency is programmable between 400kHz and 2.2MHz using a timing resistor ( $R_{RT}$ ) connected from the RT pin to GND. Use Equation 4 to calculate the value of  $R_{RT}$  for the desired switching frequency ( $f_{SW}$ ).

#### **Equation 4:**

$$R_{\text{RT}} = \frac{29260 + (2200 - f_{\text{SW}}) \times 0.81}{f_{\text{SW}}}$$

where  $R_{RT}$  is in  $k\Omega$  and  $f_{SW}$  is in kHz.

Synchronize the oscillator with an external clock by AC-coupling the external clock to the RT input. The value of the capacitor used for AC-coupling is  $C_{SYNC}$  = 10pF and the duty cycle of the external clock should be 50%.

At low input voltages and when the switching frequency is above 1MHz, the switching frequency is automatically reduced by a factor of 30% to enabled high-duty-cycle operation and maintain output-voltage regulation.

#### **Spread-Spectrum Modulation**

The IC includes spread-spectrum modulation that reduces peak electromagnetic interference (EMI) at the switching frequency and its harmonics.

The spread spectrum uses a pseudorandom dithering technique where the switching frequency is varied in the 97% range (or 94% when the SSL bit is 1) of the programmed switching frequency, to 103% (or 106% when the SSL bit is 1) of the programmed switching frequency set through the external resistor from RT to GND. When spread spectrum is used, the total energy at the fundamental and each harmonic is spread over a wider bandwidth, reducing the peak energy

at the relevant frequency.

Spread spectrum is disabled if external synchronization is used. Optionally, spread spectrum can also be disabled by setting the SS\_OFF bit in the SETTING (0x12) register to 1. The amount of spread spectrum can also be varied between  $\pm 3\%$  and  $\pm 6\%$  using the SSL bit in the same register.

## 5V LDO Regulator (V<sub>CC</sub>)

The internal LDO regulator converts the input voltage at IN (or the voltage at the BOOST pin when IN is below  $V_{SWITCHOVER}$ ) to a 5V output voltage at  $V_{CC}$ . The LDO regulator supplies current to the internal control circuitry and the gate driver. Bypass  $V_{CC}$  to GND with a 1µF (min) ceramic capacitor as close as possible to the device.

#### **LED Current Control**

The full-scale sink current for the outputs (OUT1–OUT4) is set using the four ISET[3:0] bits in the ISET register (0x02). The OUT\_ current value is also directly related to the reference current in the resistor on the IREF pin ( $R_{IREF}$ ). If the  $R_{IREF}$  value is not in the 27.5k $\Omega$  to 83.5k $\Omega$  range, the device will not operate and an IREFOOR error is indicated (see the *Register Map*).

When PWM dimming is used, the current in the OUT\_ channels switches between zero and the full-scale sink current at the set duty cycle.

When hybrid dimming is used, the sink current in OUT1–OUT4 is reduced linearly from the full-scale value until the level set by HDIM THR 1 0[1:0] is reached; dimming at lower levels is then accomplished using PWM (see Figure 1).

The LED current when using a 40.2kΩ IREF resistor is shown in Table 2.

Table 2. LED CURRENT WITH 40.2kΩ IREF RESISTOR

| ISET[3:0] | LED CURRENT PER OUTPUT (mA) |

|-----------|-----------------------------|

| 0000      | 56                          |

| 0001      | 62                          |

| 0010      | 68                          |

| 0011      | 74                          |

| 0100      | 81                          |

| 0101      | 87                          |

| 0110      | 93                          |

| 0111      | 99                          |

| 1000      | 106                         |

| 1001      | 112                         |

| 1010      | 118                         |

| 1011      | 124                         |

| 1100      | 130                         |

| 1101      | 137                         |

| 1110      | 143                         |

| 1111      | 149                         |

#### **Fault Protection**

Fault protection in the IC includes cycle-by-cycle current limiting in the PWM controller, DC-DC converter output undervoltage protection, output overvoltage protection, open-LED detection, short-LED detection and protection, and overtemperature shutdown. The open-drain fault flag output (FLTB) goes low when an open-LED string is detected, a short-LED string is detected, an output undervoltage, or during thermal shutdown. Certain faults can be inhibited from causing FLTB to go low using the bits in the MASK[7:0] register. FLTB is cleared when the fault condition is removed

during thermal shutdown and shorted LEDs. FLTB is latched low for an open-LED and can be reset by cycling power or toggling the EN pin. The thermal-shutdown threshold is +165°C and has +15°C hysteresis.

## **Open-LED Management and Overvoltage Protection**

After the soft-start of the boost converter, the IC detects open-LED strings and disconnects any such strings from the internal minimum OUT\_ voltage detector. This keeps the DC-DC converter output voltage within safe limits and maintains high efficiency. The current in strings that have been detected open is not measured by the ADC and reads as zero.

During normal operation, the DC-DC converter output-regulation loop uses the minimum OUT\_ voltage as the feedback input. If any LED string is open, the voltage at the opened OUT\_ goes to V<sub>LEDGND</sub>. The DC-DC converter output voltage then increases to the overvoltage-protection threshold set by the voltage-divider network connected between the converter output, the BSTMON input, and GND. The overvoltage-protection threshold at the DC-DC converter output is determined using the equation below.

### Equation 5:

$$V_{\text{OUT\_BSTMON}} = 1.23 \times \left(1 + \frac{R6}{R7}\right)$$

where 1.23V (typ) is the overvoltage threshold on BSTMON (see the Functional Diagram). Select  $V_{OUT\_BSTMON}$  according to the formula below.

#### Equation 6:

$$1.1x(V_{LED\ MAX} + 1.1) < V_{OUT\ BSTMON} < 2x(V_{LED\ MIN} + 0.7)$$

where:

V<sub>LED</sub> MAX = Maximum expected LED string voltage

$V_{LED\ MIN}$  = Minimum expected LED string voltage

Select R6 and R7 such that the voltage at OUT\_ does not exceed the absolute maximum rating. As soon as the DC-DC converter output reaches the overvoltage-protection threshold, the internal MOSFET is switched off.

The overvoltage threshold should be set to less than twice the minimum LED voltage to ensure proper operation and that the BSTMON minimum regulation point of 600mV (typ) is not breached. Connect a  $12k\Omega$  resistor between OUT\_ and LEDGND for each unused channel to avoid overvoltage triggering at startup. When an open-LED overvoltage condition occurs, FLTB is latched low. Any current-sink output with  $V_{OUT}$  < 300mV (typ) is permanently disconnected from the minimum voltage detector. Toggle the EN pin to clear an open-LED condition.

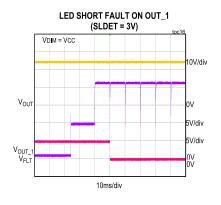

### **Short-LED Detection**

The IC checks for shorted LEDs after the current in any channel is turned on. A shorted-LED is detected at OUT\_ if the condition below is met.

## **Equation 7:**

where:

RSDT = Programmable short-LED-detection threshold set by the SLDET[1:0] bits in the SETTING (0x12) register.