# Click here to ask an associate for production status of specific part numbers.

# Dual-Phase Scalable Integrated Voltage Regulator with PMBus Interface

### **General Description**

The MAX20796 offers a fully integrated, highly efficient, two-phase switching regulator for applications operating from 4.5V to 16V and requiring up to 60A maximum load or 90A with an optional third-phase external power stage. The output voltage range can be configured from 0.5V to 5.5V with some restrictions on duty cycle. The switching regulator uses a fixed-frequency control scheme providing an extremely compact, fast, and accurate power delivery solution for server and telecom applications. Integrated linear regulators allow single-supply operation. To further improve system efficiency and thermal performance, an external 3.3V supply or FET can be used to generate the core supply.

Key system parameters are configured by external resistors, including the selection of soft-start timing, output voltage, switching frequency, PMBus<sup>TM</sup> address, overcurrent trip point, and loop control parameters. The device operates with either coupled or discrete inductors. Coupled inductor technology offers high performance with a minimum number of input and output capacitors for best-inclass solution cost.

The MAX20796 includes fault protection and reporting capabilities. Inherent positive and negative overcurrent and overtemperature protection ensure a rugged design. Input undervoltage lockout shuts down the device when the input voltage is out of specification. Regulation is halted if the output voltage is outside of a programmable range. A PGOOD pin provides an output signal to show that the output voltage is within range and the system is regulating.

The MAX20796 is offered in a 35-pin,  $4\text{mm} \times 10.5\text{mm}$  FC2QFN package, ideal for use in networking and communication end equipment.

The device is also available as MAX20796A, which is preconfigured for a 1V, 800kHz application with LEAD\_LAG enabled.

# **Applications**

- Point-of-Load Voltage Regulators

- Communication, Networking, Servers, and Storage

- Equipment

- Microprocessor Chipsets

- Memory VDDQ

- I/O and Auxiliary Power

PMBus is a trademark of SMIF, Inc.

Ordering Information appears at end of data sheet.

19-100376; Rev 5; 12/21

© 2021 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners.

One Analog Way, Wilmington, MA 01887 U.S.A. | Tel: 781.329.4700 | © 2021 Analog Devices, Inc. All rights reserved.

# **Benefits and Features**

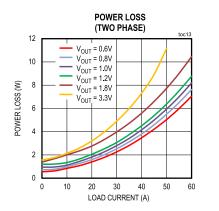

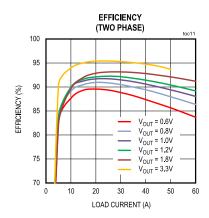

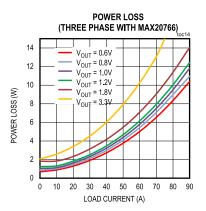

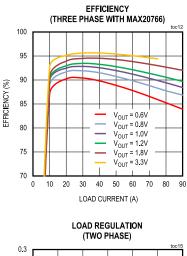

- Peak Efficiency 92%; Full-Load Efficiency 90% at V<sub>IN</sub> = 12V, V<sub>OUT</sub> = 1V

- Operating Input Voltage Range 4.5V to 16V

- Output Voltage Range is 0.5V to 5.5V

- Output Boot Voltage Pin-Strapped Range 0.5V to 5.0V with Direct Feedback

- Integrated Loop Compensation

- Supports Coupled and Discrete Inductors

- PMBus Revision 1.3 Compliant Interface

- Supports External Power Stage to Increase Power Capacity

- Internal Linear Regulators Allow Operation from One Supply Voltage

- Optional External LDO FET for Enhanced Thermal Performance

- Pin-Strapped Configurable Operating Parameters:

- 32 PMBus Addresses

- Output Voltage

- Switching Frequency

- Overcurrent Protection (OCP) Threshold

- Soft-Start Time

- Loop Compensation

- Supports Nonvolatile PMBus Command Storage (Five Writes Available)

- Continuous Conduction Mode Operation Only

- Integrated Accurate Current and Temperature Sensing

- Monotonic Startup and Shutdown, Supports Prebias Startup (Two Phase)

- Fast Peak and Average Overcurrent Protection

- RESTORE Input Pin Resets Output Voltage

- Operating Junction Temperature Range: -40°C to +125°C

- Package: 35-pin, 4mm × 10.5mm, 0.5mm pitch, FC2QFN

# Dual-Phase Scalable Integrated Voltage Regulator with PMBus Interface

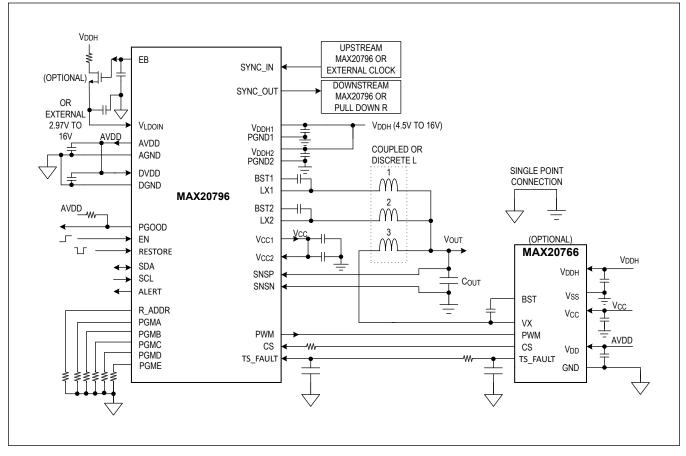

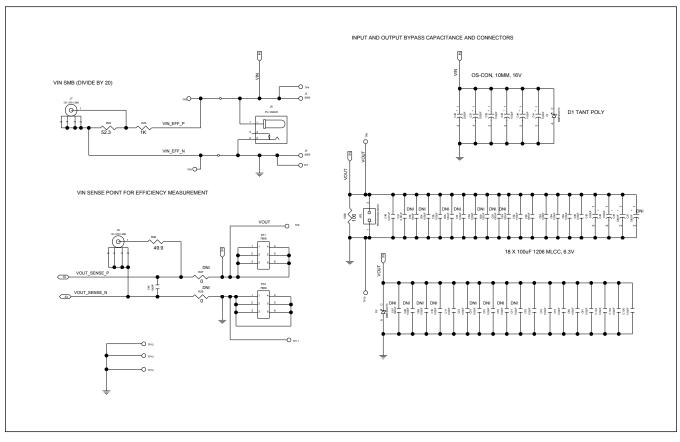

# **Simplified Application Schematic**

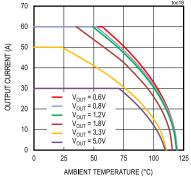

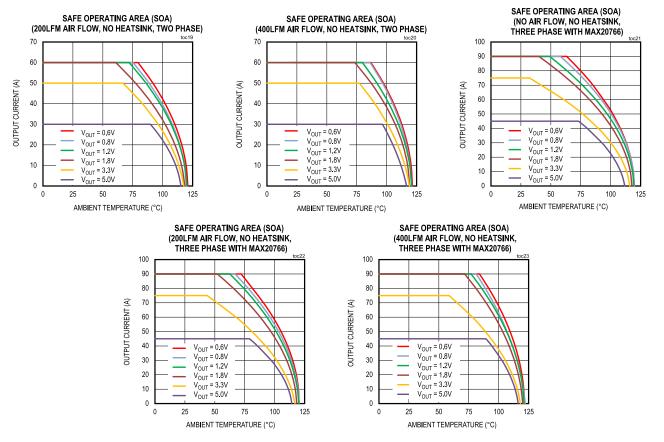

### **Current Ratings**

| DESCRIPTION                                   | CURRENT RATING*<br>(A) | INPUT VOLTAGE<br>(V) | OUTPUT VOLTAGE<br>(V) |

|-----------------------------------------------|------------------------|----------------------|-----------------------|

| Electrical Rating                             | 60                     | 4.5 to 16            | 0.5 to 5.5            |

| Thermal Rating T <sub>A</sub> = +55°C, 200LFM | 60                     | 12                   | 0.8                   |

| Thermal Rating T <sub>A</sub> = +85°C, 0LFM   | 42                     | 12                   | 0.8                   |

Current capability is tested with MAX20796 EV kit two-phase configuration.

\*For specific operating conditions, refer to the SOA curves in the <u>Typical Operating Characteristics</u> section.

# Dual-Phase Scalable Integrated Voltage Regulator with PMBus Interface

### **Absolute Maximum Ratings**

| V <sub>DDH</sub> to PGND (Note1)                  | 0.3V to +18V   | RADDR, PGM_, SYNC_IN,SYNC_OUT to DGND0.3V to                                |

|---------------------------------------------------|----------------|-----------------------------------------------------------------------------|

| V <sub>LDOIN</sub> to PGND_ (Note1)               | 0.3V to +18V   | +2.5V                                                                       |

| LX_to PGND_(DC)                                   | 0.3V to +18V   | TS_FAULT, PWM, CS to AGND0.3V to AVDD + 0.3V                                |

| LX_ to PGND_ (AC) (Note 2)                        | 10V to +23V    | PGOOD, EN, RESTORE to AGND0.3V to +3.7V                                     |

| BST_ to PGND_ (DC)                                | 0.3V to +20.5V | EB0.3V to +7.5V                                                             |

| BST_ to PGND_ (AC) (Note 2)                       | 7V to +25.5V   | SNSP to AGND0.3V to +5.5V                                                   |

| BST_ to LX_ Differential                          | 0.3V to +2.5V  | Peak LX_ Current (Note 3)72A to +72A                                        |

| AVDD, V <sub>CC1</sub> , V <sub>CC2</sub> to AGND | 0.3V to +2.5V  | Junction Temperature (T <sub>J</sub> )+150°C                                |

| DVDD to DGND                                      | 0.3V to +2.5V  | Storage Temperature Range65°C to +150°C                                     |

| PGND_, DGND to AGND                               | 0.3 to +0.3    | Peak Reflow Temperature Lead-Free+260°C                                     |

| SCL, SDA, ALERT to AGND                           | 0.3V to +3.7V  | Maximum Average Input Current (I <sub>VDDH1</sub> + I <sub>VDDH2</sub> )28A |

Note 1: Input high-frequency bypass capacitors placed not more than 60mil away from the V<sub>DDH</sub> pin are required to keep inductive voltage spikes within Absolute Maximum Ratings limits.

Note 2: AC is limited to 25ns.

Note 3: Per phase current capability. IPOCP R limits the application below the peak LX\_ current rating.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **Package Information**

### 35-PIN FC2QFN

| Package Code                                               | F354A10F+2       |

|------------------------------------------------------------|------------------|

| Outline Number                                             | <u>21-100023</u> |

| Land Pattern Number                                        | <u>90-100044</u> |

| Thermal Resistance                                         |                  |

| Junction to Ambient ( $\theta_{JA}$ ) JEDEC                | 32.9°C/W         |

| Junction to Ambient ( $\theta_{JA}$ ) on MAX20796CL2EVKIT# | 9.6°C/W          |

| Junction to Case $(\theta_{JC})$                           | 0.20°C/W         |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/</u> <u>thermal-tutorial</u>.

### **Electrical Characteristics**

(Typical Application Circuit, unless otherwise noted,  $V_{DDH}$  = 12V,  $V_{LDOIN}$  = 3.3V, -40°C ≤  $T_J$  ≤ +125°C; specifications are production tested at  $T_A$  = +32°C; limits within the operating temperature range are guaranteed by design and characterization.)

| PARAMETER                         | SYMBOL                              | CONDITIONS                                                                                   | MIN  | TYP | MAX | UNITS |  |

|-----------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------|------|-----|-----|-------|--|

| INPUT SUPPLY VOLTAG               | INPUT SUPPLY VOLTAGES AND CURRENTS  |                                                                                              |      |     |     |       |  |

| Input Supply Voltage<br>Range     | V <sub>DDH1</sub> V <sub>DDH2</sub> | $V_{\mbox{DDH1}}$ and $V_{\mbox{DDH2}}$ are shorted together                                 | 4.5  |     | 16  | V     |  |

| Input Supply Current              | IVDDH1 +<br>IVDDH2                  | Shutdown (EN low), V <sub>DDH1</sub> = V <sub>DDH2</sub> =<br>12V, V <sub>LDOIN</sub> = 3.3V |      | 1   |     | mA    |  |

| Linear Regulator Input<br>Voltage | V <sub>LDOIN</sub>                  |                                                                                              | 2.97 |     | 16  | V     |  |

# Dual-Phase Scalable Integrated Voltage Regulator with PMBus Interface

# **Electrical Characteristics (continued)**

(Typical Application Circuit, unless otherwise noted,  $V_{DDH}$  = 12V,  $V_{LDOIN}$  = 3.3V, -40°C ≤ T<sub>J</sub> ≤ +125°C; specifications are production tested at T<sub>A</sub> = +32°C; limits within the operating temperature range are guaranteed by design and characterization.)

| PARAMETER                                               | SYMBOL                 | CONDITIONS                                                                                                 | MIN  | TYP           | MAX  | UNITS |  |

|---------------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------|------|---------------|------|-------|--|

| Linear Regulator Input<br>Current                       | ILDOIN                 | System operational, no load, f <sub>SW</sub> =<br>400kHz (two-phase operation). V <sub>OUT</sub> =<br>1.0V |      | 86            | 175  | mA    |  |

|                                                         |                        | Shutdown (EN low)                                                                                          |      | 24            |      |       |  |

| LINEAR REGULATOR (E                                     | B PIN)                 |                                                                                                            |      |               |      | 1     |  |

| External FET Output<br>Set-Point Voltage                |                        | V <sub>DDH</sub> > 5.1V regulating                                                                         | 2.97 | 3.06          | 3.63 | V     |  |

| EB Sink/Source Current                                  | I <sub>EB</sub>        | V <sub>EB</sub> from 0.7V to 6V                                                                            | 25   | 48            |      | μA    |  |

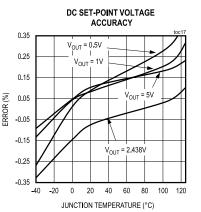

| OUTPUT VOLTAGE RAN                                      | GE AND ACCU            | RACY                                                                                                       |      |               |      |       |  |

| DC Set-Point Voltage<br>Accuracy                        |                        | $T_J$ = +32°C, $V_{OUT}$ = 0.6V to 5.0V,<br>measured between SNSP and SNSN<br>pins                         | -0.8 |               | +0.8 | %     |  |

| Voltage-Sense Input                                     | I <sub>SNSN</sub>      | -0.3V < V <sub>SNSN</sub> < 0.3V                                                                           | -15  |               | +15  |       |  |

| Bias Current                                            | I <sub>SNSP</sub>      | 0V < V <sub>SNSP</sub> < 5.5V                                                                              | -240 |               | +240 | - μΑ  |  |

| SWITCHING FREQUENC                                      | Y ACCURACY             |                                                                                                            |      |               |      |       |  |

| Switching Frequency                                     | fsw                    | PGMx pin-strap or PMBUS programmable                                                                       |      | 200 to<br>799 |      | kHz   |  |

| Switching Frequency<br>Accuracy                         |                        | (Note 4)                                                                                                   |      | ±10           |      | %     |  |

| INPUT VOLTAGE PROTI                                     | ECTION                 |                                                                                                            |      |               |      | •     |  |

| V <sub>DDH</sub> Undervoltage<br>Lockout                | VVDDH_UVLO             | Rising V <sub>DDH</sub>                                                                                    | 4.28 | 4.40          | 4.54 | V     |  |

| V <sub>DDH</sub> Undervoltage-<br>Lockout Hysteresis    |                        |                                                                                                            |      | 500           |      | mV    |  |

| V <sub>CC</sub> Undervoltage<br>Lockout                 | Vvcc_uvlo              | Rising $V_{CC}$                                                                                            | 1.53 | 1.59          | 1.63 | V     |  |

| V <sub>CC</sub> Undervoltage-<br>Lockout Hysteresis     |                        |                                                                                                            |      | 50            |      | mV    |  |

| AV <sub>DD</sub> Undervoltage<br>Lockout                | VAVDD_UVLO             | Rising AV <sub>DD</sub>                                                                                    | 1.53 | 1.61          | 1.66 | V     |  |

| AV <sub>DD</sub> Undervoltage-<br>Lockout Hysteresis    |                        |                                                                                                            |      | 50            |      | mV    |  |

| V <sub>BST</sub> Undervoltage<br>Lockout                | V <sub>VBST_UVLO</sub> | Rising V <sub>BST</sub>                                                                                    | 1.46 | 1.56          | 1.64 | V     |  |

| V <sub>BST</sub> Undervoltage-<br>Lockout Hysteresis    |                        |                                                                                                            |      | 50            |      | mV    |  |

| OUTPUT VOLTAGE PRO                                      | DTECTION               |                                                                                                            |      |               |      |       |  |

| V <sub>OUT</sub> Overvoltage<br>Protection (OVP) Rising |                        | V <sub>OUT</sub> = 0.500 to 2.437V. Relative to DAC voltage. Direct feedback.                              | 190  | 210           | 225  | - mV  |  |

| Threshold (Tracking)                                    |                        | V <sub>OUT</sub> = 2.438 to 5.000V. Relative to DAC voltage. Direct feedback.                              | 415  | 460           | 485  |       |  |

| OVP Blanking Time                                       |                        | End of TON_RISE to protection active (Note 4)                                                              |      |               | 6    | μs    |  |

# Dual-Phase Scalable Integrated Voltage Regulator with PMBus Interface

# **Electrical Characteristics (continued)**

(Typical Application Circuit, unless otherwise noted,  $V_{DDH}$  = 12V,  $V_{LDOIN}$  = 3.3V, -40°C ≤ T<sub>J</sub> ≤ +125°C; specifications are production tested at T<sub>A</sub> = +32°C; limits within the operating temperature range are guaranteed by design and characterization.)

| PARAMETER                                                     | SYMBOL             | CONDITIONS                                                                    | MIN       | TYP           | MAX  | UNITS |

|---------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------|-----------|---------------|------|-------|

| V <sub>OUT</sub> Undervoltage-<br>Protection (UVP) Falling    |                    | V <sub>OUT</sub> = 0.500 to 2.437V. Relative to DAC voltage. Direct feedback. | -310      | -290          | -270 | - mV  |

| Threshold                                                     |                    | V <sub>OUT</sub> = 2.438 to 5.000V. Relative to DAC voltage. Direct feedback. | -670      | -640          | -610 |       |

| V <sub>OUT</sub> UVP and OVP<br>Deglitch Time                 |                    | (Note 4)                                                                      |           | 2             |      | μs    |

| OVERCURRENT PROTE                                             | CTION (OCP)        |                                                                               |           |               |      |       |

| Average OCP Rising<br>Threshold per Phase                     | IOCP_AVG           | Pin-strap programmable                                                        |           | 10 to<br>33.3 |      | A     |

| Average OCP Rising<br>Threshold Accuracy                      |                    | Two phase (Note 4)                                                            |           | ±10           |      | %     |

| POWER-STAGE PEAK C                                            | URRENT PROT        | ECTION                                                                        |           |               |      |       |

| Positive Peak Current<br>Rising Threshold per<br>Power Train  | IPOCP_R            | V <sub>DDH1</sub> = V <sub>DDH2</sub> = 12V (Note 4)                          | 44.0      |               | 62.0 | A     |

| Positive Peak Current<br>Falling Threshold per<br>Power Train | IPOCP_F            | V <sub>DDH1</sub> = V <sub>DDH2</sub> = 12V (Note 4)                          | 30.8      |               | 42.0 | A     |

| Negative Peak Current<br>Limit per Power Train                | INOCP              | V <sub>DDH1</sub> = V <sub>DDH2</sub> = 12V (Note 4)                          |           | -39.2         |      | A     |

| EXTERNAL POWER-STA                                            | GE DRIVE INTI      | ERFACE (PWM, CS, TS_FAULT)                                                    |           |               |      |       |

| PWM Output                                                    |                    | Logic high voltage, sourcing 4mA                                              | 1.32      |               |      | v     |

|                                                               | V <sub>PWM</sub>   | Logic low voltage, sinking 4mA                                                |           |               | 0.4  |       |

| Power-Stage Fault<br>Logic-Low Threshold                      |                    | With respect to AGND                                                          |           | 300           |      | mV    |

| OUTPUT ENABLE (EN)                                            |                    |                                                                               |           |               |      |       |

| EN Thresholds                                                 | V <sub>EN_IH</sub> | Input logic-high                                                              | 0.9       |               |      | - v   |

| EN THESHOLDS                                                  | V <sub>EN_IL</sub> | Input logic-low                                                               |           |               | 0.4  | v     |

| EN Deglitch Delay                                             |                    |                                                                               |           | 1             |      | μs    |

| Turn-on Response Time                                         |                    | From V <sub>EN_IH</sub> to T <sub>ON_DELAY</sub> start (Note 4)               |           | 20            |      | μs    |

| Turn-off Response Time                                        | t4                 | From V <sub>EN_IL</sub> to T <sub>OFF_DELAY</sub> start (Note 4)              |           | 2             |      | μs    |

| STARTUP TIMING                                                |                    |                                                                               |           |               |      |       |

| Time from EN High to<br>Start of Switching                    | t <sub>3</sub>     | $T_{ON\_DELAY} = 0$ , two-phase operation<br>with $\ge 1A$ load (Note 4)      |           | 10            |      | μs    |

| Initialization Time<br>(Includes Pin-Strap<br>Read Time)      | t <sub>2</sub>     | V <sub>DDH</sub> , V <sub>CC</sub> , AVDD UVLO cleared (Note 4)               |           | 10            |      | ms    |

| Soft-Start Time                                               | TON_RISE           | Pin-strap programmable TON_RISE<br>(Note 4)                                   | 0.5,1,4,8 |               |      | ma    |

|                                                               | ION_RISE           | PMBus programmable TON_RISE (Note 4)                                          |           | 0 to 25       |      | - ms  |

# Dual-Phase Scalable Integrated Voltage Regulator with PMBus Interface

# **Electrical Characteristics (continued)**

(Typical Application Circuit, unless otherwise noted,  $V_{DDH}$  = 12V,  $V_{LDOIN}$  = 3.3V, -40°C ≤ T<sub>J</sub> ≤ +125°C; specifications are production tested at T<sub>A</sub> = +32°C; limits within the operating temperature range are guaranteed by design and characterization.)

| PARAMETER                               | SYMBOL                | CONDITIONS                                                                    | MIN  | TYP  | MAX  | UNITS |  |

|-----------------------------------------|-----------------------|-------------------------------------------------------------------------------|------|------|------|-------|--|

| Soft-Start Time<br>Accuracy             |                       | (Note 4)                                                                      |      | ±5   |      | %     |  |

| PGOOD PIN                               |                       | 1                                                                             |      |      |      | 1     |  |

| PGOOD Rising                            |                       | V <sub>OUT</sub> = 0.500 to 2.437V. Relative to DAC voltage. Direct feedback. | -305 | -285 | -265 |       |  |

| Threshold                               |                       | V <sub>OUT</sub> = 2.438 to 5.000V. Relative to DAC voltage. Direct feedback. | -660 | -625 | -590 | - mV  |  |

| PGOOD Threshold<br>Hysteresis           |                       | V <sub>OUT</sub> = 0.5V to 5.0V. Direct feedback.                             |      | 10   |      | mV    |  |

| PGOOD Output High<br>Leakage Current    | IPGOOD                | PGOOD pulled to 3.3V through $20k\Omega$                                      |      |      | 1    | μA    |  |

| PGOOD Output Low                        | V <sub>PGOOD_OL</sub> | I <sub>PGOOD</sub> = 4mA                                                      |      |      | 0.4  | V     |  |

| R_ADDR, PGMA, PGMB,                     | PGMC, PGMD,           | PGME PIN                                                                      |      |      |      |       |  |

| Total Allowable Resistor<br>Accuracy    |                       | (Note 4)                                                                      |      |      | ±1   | %     |  |

| Maximum External Stray<br>Capacitance   |                       | (Note 4)                                                                      |      |      | 5    | pF    |  |

| RESTORE PIN                             |                       |                                                                               |      |      |      |       |  |

| RESTORE Logic-Low<br>Voltage            | V <sub>RSTB_IL</sub>  | Input voltage falling                                                         |      |      | 0.47 | V     |  |

| RESTORE Logic-High<br>Voltage           | V <sub>RSTB_IH</sub>  | Input voltage rising                                                          | 1.3  |      |      | V     |  |

| Input Leakage Current                   |                       |                                                                               | -12  |      | +12  | μΑ    |  |

| Deglitch Time                           |                       | (Note 4)                                                                      | 10   |      |      | μs    |  |

| RESTORE Pullup<br>Resistance            |                       |                                                                               | 150  | 220  | 280  | kΩ    |  |

| SYNCHRONIZATION                         |                       |                                                                               |      |      |      |       |  |

| SYNC_IN Pin Input Low                   | V <sub>SYNC_IL</sub>  |                                                                               |      |      | 0.47 | V     |  |

| SYNC_IN Pin Input High                  | V <sub>SYNC_IH</sub>  |                                                                               | 1.32 |      |      | V     |  |

| SYNC_IN Input Duty<br>Cycle             |                       | f <sub>SW</sub> = 800kHz                                                      | 10   |      | 90   | %     |  |

| Synchronization Lock<br>Frequency Range |                       | With respect to pin-strap fSW                                                 | -15  |      | +30  | %     |  |

| SYNC_OUT Pin Output<br>Low              | V <sub>SYNC_OL</sub>  | Sinking 4mA                                                                   |      |      | 0.4  | V     |  |

| SYNC_OUT Pin Output<br>High             | V <sub>SYNC_OH</sub>  | Sourcing 4mA                                                                  | 1.31 |      |      | V     |  |

| PMBus TELEMETRY                         |                       |                                                                               |      |      |      |       |  |

|                                         |                       | Input voltage (Note 4)                                                        |      | 13   |      |       |  |

| System ADC Update                       |                       | Junction temperature (Note 4)                                                 |      | 13   |      | 1     |  |

| Rate                                    |                       | Output voltage (Note 4)                                                       |      | 6.5  |      | - ms  |  |

|                                         |                       | Output total average current (Note 4)                                         |      | 13   |      | 1     |  |

| System ADC Resolution                   |                       |                                                                               |      | 10   |      | bits  |  |

# Dual-Phase Scalable Integrated Voltage Regulator with PMBus Interface

# **Electrical Characteristics (continued)**

(Typical Application Circuit, unless otherwise noted,  $V_{DDH}$  = 12V,  $V_{LDOIN}$  = 3.3V, -40°C ≤ T<sub>J</sub> ≤ +125°C; specifications are production tested at T<sub>A</sub> = +32°C; limits within the operating temperature range are guaranteed by design and characterization.)

| PARAMETER                                        | SYMBOL              | CONDITIONS                                                                                                                                | MIN  | TYP | MAX  | UNITS |

|--------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|-------|

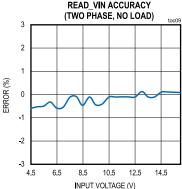

|                                                  |                     | READ_VIN vs. measurement, no load, $V_{DDH}$ = 12V                                                                                        | -3   |     | 3    | %     |

|                                                  |                     | READ_VOUT vs. measurement, V <sub>OUT</sub> = 1.0V, 0A to 50A load                                                                        | -1   |     | 1    | 70    |

| Telemetry Error                                  |                     | READ_IOUT vs. measurement at V <sub>OUT</sub> = 1.0V, no load                                                                             | -2.2 |     | +2.2 | A     |

|                                                  |                     | READ_IOUT vs. measurement at V <sub>OUT</sub> = 1.0V, 50A load                                                                            | -3.6 |     | +3.6 |       |

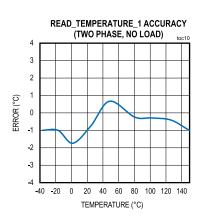

|                                                  |                     | READ_TEMPERATURE1 vs.<br>measurement, V <sub>DDH</sub> = 9V to 12V, f <sub>SW</sub> =<br>400kHz, V <sub>OUT</sub> = 0.6V to 1.0V, no load |      | ±4  |      | °C    |

| PMBus/SMBus                                      |                     |                                                                                                                                           |      |     |      |       |

| SDA, SCL Input Logic-<br>Low Voltage             | V <sub>BUS_IL</sub> |                                                                                                                                           |      |     | 0.8  | V     |

| SDA, SCL Input Logic-<br>High Voltage            | V <sub>BUS_IH</sub> |                                                                                                                                           |      |     |      | V     |

| SDA, SCL, ALERT<br>Logic-High Leakage<br>Current |                     | $V_{SCL}$ , $V_{SDA}$ = 3.3V, and $\overline{ALERT}$ = 3.3V                                                                               |      |     | 1    | μΑ    |

| SDA, ALERT Output<br>Logic-Low                   |                     | Sinking 4mA                                                                                                                               |      |     | 0.4  | V     |

| PMBus Operating<br>Frequency                     | fSCL                |                                                                                                                                           |      |     | 1000 | kHz   |

| SDA Hold Time from SCL                           | <sup>t</sup> HD_DAT | (Note 4)                                                                                                                                  | 300  |     |      | ns    |

| SDA Setup Time from SCL                          | <sup>t</sup> SU_DAT | (Note 4)                                                                                                                                  | 100  |     |      | ns    |

| SCL High Period                                  | thigh               | (Note 4)                                                                                                                                  | 0.5  |     |      | μs    |

| SCL Low Period                                   | t <sub>LOW</sub>    | (Note 4)                                                                                                                                  | 0.5  |     |      | μs    |

Note 4: Guaranteed by design.

# Dual-Phase Scalable Integrated Voltage Regulator with PMBus Interface

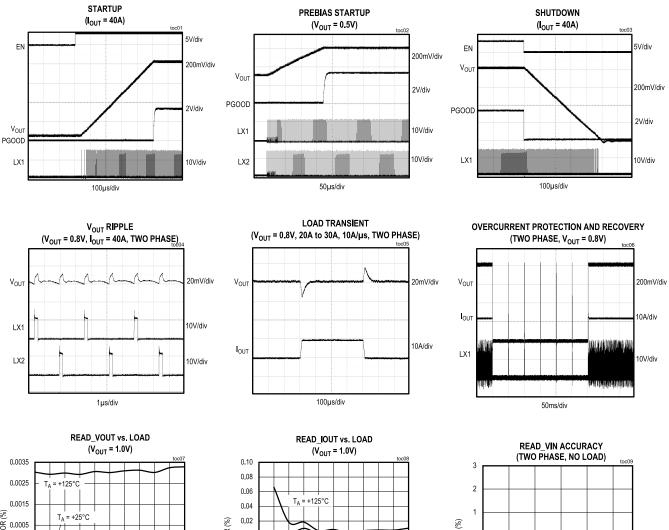

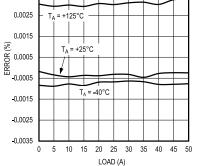

# **Typical Operating Characteristics**

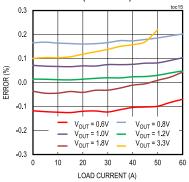

(Typical Application Circuit,  $V_{DDH}$  = 12V,  $V_{LDOIN}$  = 3.3V, FREQUENCY\_SWITCH = 308kHz,  $T_A$  = +25°C,  $V_{OUT}$  = 3.3V and 5.0V are tested under  $f_{SW}$  = 800kHz, unless otherwise noted.)

# Dual-Phase Scalable Integrated Voltage Regulator with PMBus Interface

# **Typical Operating Characteristics (continued)**

(Typical Application Circuit,  $V_{DDH}$  = 12V,  $V_{LDOIN}$  = 3.3V, FREQUENCY\_SWITCH = 308kHz,  $T_A$  = +25°C,  $V_{OUT}$  = 3.3V and 5.0V are tested under  $f_{SW}$  = 800kHz, unless otherwise noted.)

SAFE OPERATING AREA (SOA) (NO AIR FLOW, NO HEATSINK, TWO PHASE)

# Dual-Phase Scalable Integrated Voltage Regulator with PMBus Interface

# **Typical Operating Characteristics (continued)**

(Typical Application Circuit,  $V_{DDH}$  = 12V,  $V_{LDOIN}$  = 3.3V, FREQUENCY\_SWITCH = 308kHz,  $T_A$  = +25°C,  $V_{OUT}$  = 3.3V and 5.0V are tested under  $f_{SW}$  = 800kHz, unless otherwise noted.)

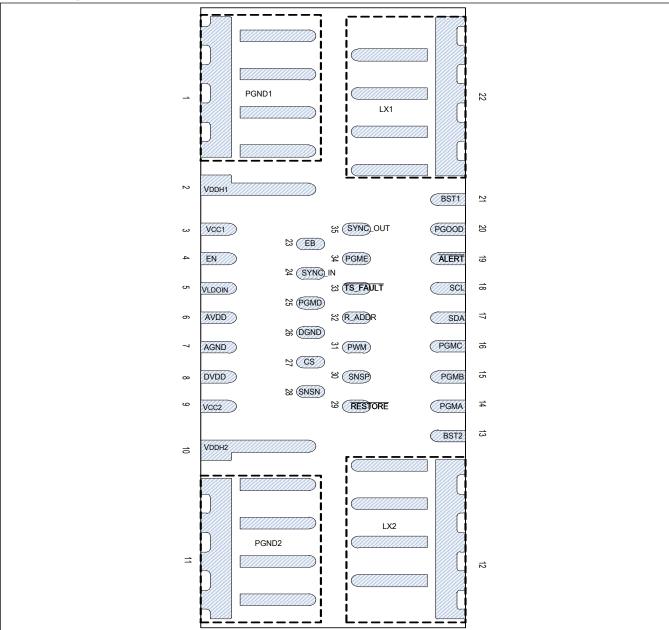

# Dual-Phase Scalable Integrated Voltage Regulator with PMBus Interface

# **Pin Configuration**

# **Pin Description**

| PIN | NAME              | FUNCTION                                                                                                                             |  |  |

|-----|-------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1   | PGND1             | ower Ground 1                                                                                                                        |  |  |

| 2   | V <sub>DDH1</sub> | V <sub>DDH1</sub> Power-Supply Input. The high-side MOSFET switch 1 is connected to this node.                                       |  |  |

| 3   | V <sub>CC1</sub>  | Internal Linear Regulator Output Pin for Gate Bias Supply. Connect a 4.7µF ceramic capacitor to PGND and place it close to this pin. |  |  |

# Dual-Phase Scalable Integrated Voltage Regulator with PMBus Interface

# **Pin Description (continued)**

| PIN           | NAME                                     | FUNCTION                                                                                                                                                    |  |  |

|---------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 4             | EN                                       | Active-High Enable Input                                                                                                                                    |  |  |

| 5             | V <sub>LDOIN</sub>                       | Internal Linear Regulator Input Supply. Connect an external power supply with a 4.7µF capacitor.                                                            |  |  |

| 6             | AVDD                                     | ternal Linear Regulator Output Pin for Core Power Supply. Connect a $4.7\mu F$ ceramic capacito GND and place it close to this pin.                         |  |  |

| 7             | AGND                                     | Analog Ground for AVDD Decoupling                                                                                                                           |  |  |

| 8             | DVDD                                     | Supply Pin for Digital Circuit. Connect a 1µF ceramic capacitor to DGND and place it close to this pin.                                                     |  |  |

| 9             | V <sub>CC2</sub>                         | Internal Linear Regulator Output Pin for Gate Bias Supply. Connect a 4.7µF ceramic capacitor to PGND and place it close to this pin.                        |  |  |

| 10            | V <sub>DDH2</sub>                        | Power-Supply Input. The high-side MOSFET switch 2 is connected to this node.                                                                                |  |  |

| 11            | PGND2                                    | Power Ground 2                                                                                                                                              |  |  |

| 12            | LX2                                      | Switching Node 2. Connect directly to the output inductor.                                                                                                  |  |  |

| 13            | BST2                                     | Bootstrap Pin for High-Side Switch 2. Connect to BST2 with a 0.22µF ceramic capacitor.                                                                      |  |  |

| 14–16, 25, 34 | PGMA,<br>PGMB,<br>PGMC,<br>PGMD,<br>PGME | Program Pin (see Pin Program Table)                                                                                                                         |  |  |

| 17            | SDA                                      | SMBus Data                                                                                                                                                  |  |  |

| 18            | SCL                                      | SMBus Clock                                                                                                                                                 |  |  |

| 19            | ALERT                                    | SMBus Alert. This pin is an open-drain output that pulls low when SMBus interaction is required.                                                            |  |  |

| 20            | PGOOD                                    | Power Good Indication. Open-drain output pin.                                                                                                               |  |  |

| 21            | BST1                                     | Bootstrap Pin for High-Side Switch 1. Connect to BST1 with a 0.22µF ceramic capacitor.                                                                      |  |  |

| 22            | LX1                                      | Switching Node 1. Connect directly to the output inductor.                                                                                                  |  |  |

| 23            | EB                                       | External FET Driver Output. Ground for internal Linear Regulator mode; or connect to external nFET gate for external Linear Regulator mode.                 |  |  |

| 24            | SYNC_IN                                  | Synchronization Clock Input. Ground it to AGND through a 49.9Ω resistor if not used.                                                                        |  |  |

| 26            | DGND                                     | Ground for Digital Circuit. Connect this pin directly to AGND pin.                                                                                          |  |  |

| 27            | CS                                       | External Power Stage IC Current-Sensing Input. Connect to the external power-stage CS output through a $499\Omega$ resistor, or pulled to AGND if not used. |  |  |

| 28            | SNSN                                     | Output Voltage Differential-Sense Negative Input                                                                                                            |  |  |

| 29            | RESTORE                                  | Output Restore Pin. Pull high to AVDD through an external resistor. Falling edge effective, restore to pin-strapped voltage.                                |  |  |

| 30            | SNSP                                     | Output Voltage Differential Sense Positive Input                                                                                                            |  |  |

| 31            | PWM                                      | External Power Stage PWM Output. Connect to the external power-stage PWM input, or pulled to AGND if not used.                                              |  |  |

| 32            | R_ADDR                                   | PMBus Address Program Pin (see Pin Program Table)                                                                                                           |  |  |

| 33            | TS_FAULT                                 | External Power-Stage TS_FAULT Connection. Temperature sense and fault input. Connect a 100pF capacitor to AGND. Float it if not used.                       |  |  |

| 35            | SYNC_OUT                                 | Synchronization Clock Output. Connect this pin to the downstream regulator SYNC_IN pin or a pulldown resistor to ground. See Table 2 for details.           |  |  |

# Dual-Phase Scalable Integrated Voltage Regulator with PMBus Interface

### RESTORE ALERT PGOOD SDA SCL ΕN PMBus CONTROL DIGITAL CORE OTP BANK CLOCK PGMA PGMB PGMC PWM RADC PGMD PGME R\_ADDR £ FAULT BST1,2 BST DETECT SNSP MODULATOR ANALOG FRONT END VDDH1,2 PWM HS HS DRIVER SNSN LOGIC CS LX1,2 OPEN IRECON LS DRIVER ī VERROR-DETECT MM MM Þ PGND1,2 TELEMETRY TS\_FAULT ADCS F h 12V SECTION 12V ł 12V SYNC\_OUT BGAP SECTION SYNC ≱¦ LDO BANGAP LDO TEMP IN/OUT CORE SENSOR 1.8V 1.8V SYNC\_IN I N1 SECTION SECTION L BIAS AGND DGND EB VLDOIN AVDD DVDD VCC1 VCC2

# **Block Diagram**

### **Detailed Description**

The MAX20796 is a highly efficient, monolithic, high-performance 60A integrated dual-phase buck regulator, compliant with PMBus specification Revision 1.3. The MAX20796 solution can be paired with an external power stage, such as the MAX20766 to support up to 90A loads.

This architecture uses lossless current sensing to provide a superior control loop with simple design parameters, highaccuracy current reporting, and fast fault protection. The integrated power switches in MAX20796 and MAX20766 provide low switching losses for a wide range of output currents. The external power stage can be included or omitted, allowing a common PCB layout to be used for multiple applications with different output currents.

Key system parameters are set by the programming resistors at the PGMx pins, which select different application configurations by hardware only. These system parameters and other features can be adjusted by using the PMBus interface as well.

The device includes a PMBus interface that provides extensive reporting features and allows reconfiguring the regulator for development purposes or adapting to different conditions. Refer to <u>Application Note 6453</u>: <u>MAX20796 PMBus User</u> <u>Guide</u> for more details.

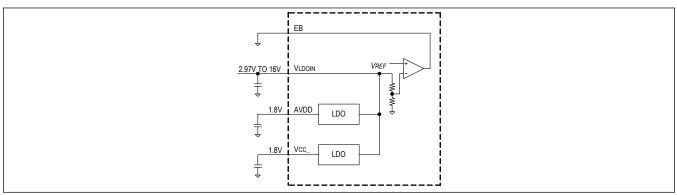

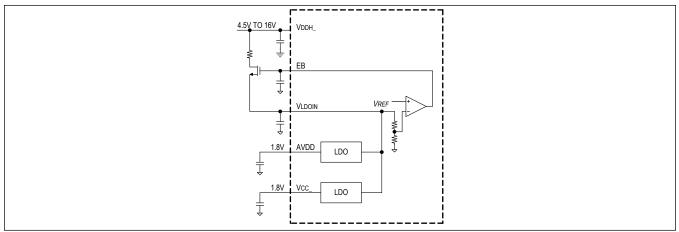

In order to support single-input rail operation, the MAX20796 contains an internal linear regulator to convert the input voltage into the lower voltage that powers the IC internal bias circuitry and gate drive circuitry. Two integrated 1.8V linear regulators, one for AVDD and DVDD and the other for  $V_{CC1}$  and  $V_{CC2}$ , are employed.

The integrated features simplify the overall implementation, making the MAX20796 solution a completely high powerdensity solution.

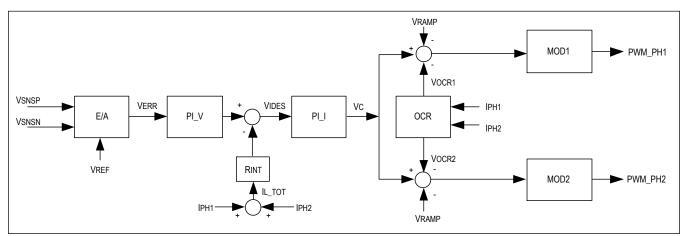

### **Control Architecture**

The MAX20796 control loop is based on the multiphase peak current-mode control architecture. The loop contains multiple amplifier stages and modulator circuits that switch each phase based on its phase current. Figure 1 shows the internal amplifier stages of the controller and how phase-current information is used to generate the phase-control signals by using a two-phase system as an example. The first error amplifier stage is a differential amplifier, which provides an output equal to 2.2 times the error between the reference voltage and the differential remote-sense voltage. Its output voltage ( $V_{ERR}$ ) is used as the input of the first proportional integral (PI) block used for voltage loop. Then the output voltage of the PI\_V block minus the total sensed phase currents ( $I_{L}_{TOT} \times R_{INT}$ ) are generated as the current-loop error amplifier input ( $V_{IDES}$ ). After  $V_{IDES}$  is handled by another PI amplifier, its output ( $V_{C}$ ) along with the slope compensation ramp ( $V_{RAMP}$ ) and the current balancing info (VOCR), are used for the PWM modulation (MOD) for each phase.

Figure 1. Simplified Control Architecture

### **Interleaved Operation**

Interleaved operation reduces the output current and voltage ripple, and mitigates input capacitor AC current stress.

# Dual-Phase Scalable Integrated Voltage Regulator with PMBus Interface

The MAX20796 has its two phases switching with a 180-degree phase shift. If there is an external power stage, the phase shift is 120 degrees. Both coupled and discrete inductors are supported by this interleaved operation. Coupled inductor technology can effectively reduce the current ripple and it requires less output capacitance to meet the transient requirement, which makes it a good candidate for high-power-density design.

### Startup and Shutdown

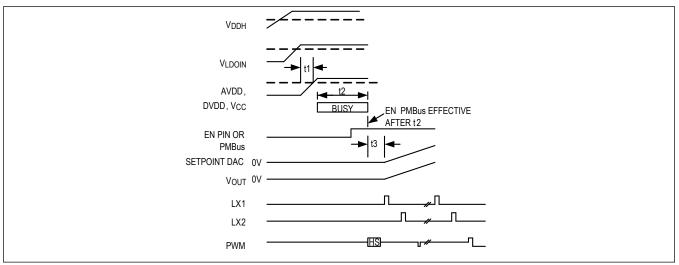

When AVDD,  $V_{CCx}$ , and DVDD are above their rising UVLO thresholds, the device goes through an initialization and phase-detection procedure. Configuration resistors on R\_ADDR and PGMx pins are read and checked for valid values. Any faults during the initialization process prevent switching. If an external power stage is present, additional initialization time is needed for the controller to configure itself before switching. Detailed timing can be found in Figure 2. The PMBus communication and telemetry are then active. The V<sub>DDH</sub> voltage must be above its rising UVLO threshold for the output voltage to turn on.

Depending on how the voltage-regulation enable is configured, an enable signal from the EN pin or the PMBus OPERATION Command might be required for the output voltage to turn on. The default configuration for the enable signal is with the EN pin at the high logic level, with no PMBus command needed.

Figure 2. Startup Timing Diagram

When the V<sub>DDH</sub> voltage is above its rising UVLO threshold and the proper enable signal has occurred, the output voltage turns on after the PMBus programmable TON\_ DELAY time. The output voltage starts to ramp up towards the target voltage VOUT\_COMMAND, which is initially set by the PGMA resistor with the soft-start time TON\_RISE initially set by the PGME resistor. After the output voltage has reached its nominal value, the PGOOD signal is asserted. <u>Table 1</u> shows the typical timing in the startup and shutdown process.

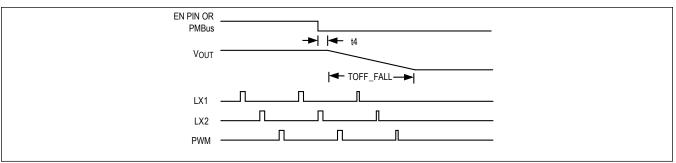

Depending on how the voltage-regulation enable is configured, the output voltage can be turned off using the EN signal or the PMBus OPERATION Command. By default, the output turnoff time (TOFF\_FALL) is the same time as TON\_RISE. A delay time can be set by the PMBus command TOFF\_DELAY. Note that when  $V_{OUT}$  ramps down, energy might be delivered from output to input. The input capacitor should be sized to absorb this energy to prevent a large increase in the  $V_{DDH}$  voltage. Figure 3 shows shut down by EN with TOFF\_FALL.

### Table 1. Startup and Shutdown Timing

|    | TYPICAL | DESCRIPTION                                           |  |

|----|---------|-------------------------------------------------------|--|

| t1 | 5ms     | as-voltage setup time                                 |  |

| t2 | 10ms    | nitialization time (PGMx, R_ADDR read time)           |  |

| t3 | 150µs   | Delay time from EN rise to start of switching         |  |

| t4 | 2µs     | elay time from EN falling edge to start of TOFF_DELAY |  |

# Dual-Phase Scalable Integrated Voltage Regulator with PMBus Interface

Figure 3. Shutdown Timing Diagram

### **Prebias Startup**

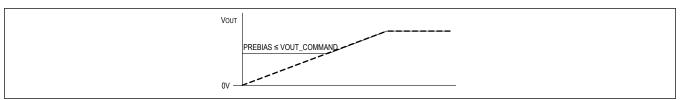

If the output voltage is "prebiased" before regulation is enabled, the MAX20796 generates a monotonic startup ramp with no reverse current, as shown in <u>Figure 4</u>. Two-phase configurations can start monotonically with the output prebias as high as VOUT\_COMMAND, but operational characteristics of the MAX20766 external power-stage limit three-phase configurations to a maximum prebias voltage of 500mV.

### Internal Linear Regulator

The MAX20796 contains internal linear regulators to support single input rail operation. The linear regulators convert the input voltage from the V<sub>LDOIN</sub> pin into lower voltages that provide the internal bias for the controller and the gate drive circuitry. V<sub>LDOIN</sub> can be powered either by V<sub>DDH</sub> voltage (single input rail operation) or any other supply voltage in range of 2.97V to 16V. A lower input voltage, e.g., 3.3V, is preferred to reduce its internal losses and enhance the overall thermal performance. Decoupling capacitors must be used and put close to output pins, i.e., V<sub>CC</sub>, AVDD and DVDD to ensure optimum performance. The V<sub>CC</sub> and AVDD bypass capacitor values must satisfy this equation:

### $C_{\rm VCC} < 1.3 \times C_{\rm AVDD} + 0.9 \mu {\rm F}$

Figure 5 shows the diagram of V<sub>LDOIN</sub> with an external supply voltage.

Figure 4. Prebias Startup

Figure 5. VLDOIN with an External Supply Voltage

To enhance thermal performance when there is no supply voltage other than V<sub>DDH</sub>, an external nFET can be driven by

# Dual-Phase Scalable Integrated Voltage Regulator with PMBus Interface

the EB pin to generate 3V to feed into the V<sub>LDOIN</sub> pin, as shown in Figure 6. The external nFET should be selected with sufficient power dissipation capability under the worst thermal case. SQA410EJ-T1\_GE3 from Vishay is a good candidate to handle most of the application cases. A series resistor, of about  $3\Omega$  to  $5\Omega$  is needed on its drain terminal to limit the peak current when V<sub>DDH</sub> shuts down.

### **Restore Function (RESTORE)**

Upon a high-to-low transition of the RESTORE pin, V<sub>OUT</sub> is restored to the voltage set by PGMA. A 10µs deglitch time is employed to eliminate the possibility of a false RESTORE-low signal caused by noise coupling. The output voltage transition rate between the previous and new output voltage is the same rate as the transition between different VOUT\_COMMAND voltages determined by TON\_RISE/VOUT\_COMMAND.

Note that it is permissible for the system to hold the RESTORE signal low indefinitely. As long as RESTORE is low, the MAX20796 forces the restore function, which is:

- The device does not act on any command that directly changes the output voltage, except for bits 6 and 7 of the OPERATION command that turns the supply on or off (0x00, 0x40, or 0x80);

- The device NACKs any VOUT\_COMMAND data writes (and discards the new VOUT\_COMMAND data), and the corresponding STATUS\_CML error flag (invalid data) is set.

Figure 6. EB Drives a nFET to Generate 3V

### Power Good (PGOOD)

The PGOOD pin is an active-high, open-drain output that is used to show that  $V_{OUT}$  has settled at the target voltage. PGOOD goes high after a fixed delay after the end of the startup transition (see the <u>Electrical Characteristics</u> table). PGOOD is deasserted if the output voltage drops below the PGOOD falling threshold relative to the nominal voltage for any reason.

### **Orthogonal Current Rebalancing (OCR)**

The MAX20796 implements an orthogonal current rebalancing (OCR) feature for enhanced dynamic-current sharing or balancing between different phase currents. This feature maintains current balance during load transients, even at a load-step frequency close to switching frequency or its harmonics. In the MAX20796, the OCR circuit adjusts the individual phase-current control signal from a common average current signal in order to minimize the phase-current imbalance. The individual phase- current control signal is conditioned through the OCR circuit before it reaches individual phase (PWM) modulator. This prevents each phase current from diverging from the average. For example, the new phase current control voltage for phase 1 is given as shown in Equation 1.

### Equation 1:

$V_{\text{CPH1}} = V_{\text{C}} - R_{\text{OCR}} \times (I_{\text{PH1}} - I_{\text{AVG}})$ where,

# Dual-Phase Scalable Integrated Voltage Regulator with PMBus Interface

V<sub>CPH1</sub> = Phase 1 current-control signal,

$V_{C}$  = Common average-current control signal,

R<sub>OCR</sub> = OCR circuit gain resistance,

I<sub>PH1</sub> = Phase 1 current, and

$I_{AVG}$  = Average current.

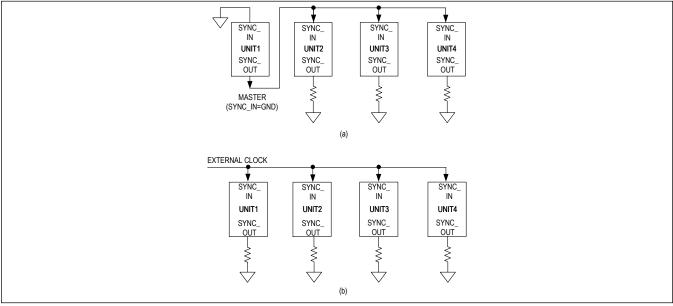

### Synchronization

Synchronizing multiple units can effectively reduce intermodulation noise and its interference to input current and output voltage. Up to four units of MAX20796 can be connected in the star connection format. The external synchronization clock is not necessary. Figure 7 shows the connection diagram without an external clock signal. In this case, Unit 1, by shorting its SYNC\_IN pin to GND, is selected as the master to send out the synchronization clock signal to downstream units. Figure 7 shows how the four units can be connected if there is an external clock signal.

Figure 7. Synchronization Connection Diagram

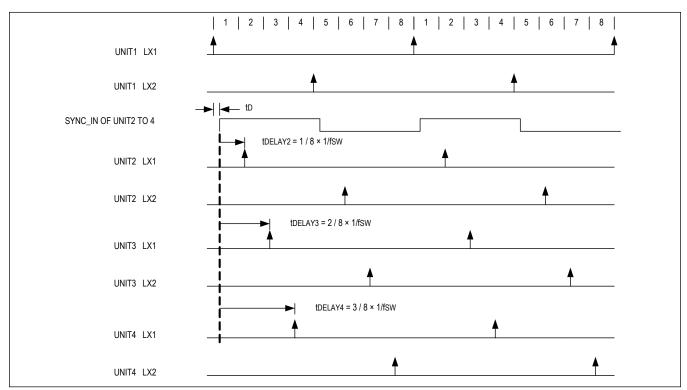

In addition to synchronization, an interleaving feature is included in the MAX20796. Figure 8 shows the phase-shift timing diagram in a four-unit system as in the Figure 7 (a) configuration. Unit 1 serves as the signal master and its SYNC\_OUT is used as the input of Unit 2 to 4. After the SYNC\_OUT pulldown resistor is read in the initialization period, each unit is assigned a fixed phase shift relative to its SYNC\_IN input-signal rising edge. t<sub>D</sub> is the delay time from LX1 to its SYNC\_OUT rising edge in Unit 1. Table 2 shows the SYNC\_OUT pin-strap table.

If the SYNC\_IN signal is disqualified, e.g., the pulse is too narrow, out of lock-in range, or upon sudden loss of signal, the MAX20796 resumes switching smoothly with its pin-strap defined switching frequency.

### Fault Handling

### **SNSP** Open Detection

The MAX20796 supports the SNSP pin open-detection at startup. If the SNSP pad or part of its feedback path is unconnected from the output for any reason, the regulator does not startup switching. This protection is only active at startup and is disabled in regulation.

# Dual-Phase Scalable Integrated Voltage Regulator with PMBus Interface

### **R\_ADDR and PGMx Out of Range Detection**

During a R\_ADDR and PGMx read period in the startup initialization, an error is reported if a pin-strap resistance is out of the defined range and switching is forbidden. STATUS\_MFR\_SPECIFIC [bit 3], a manufacturer-specific PMBus register, is flagged to report this error.

Figure 8. Phase Shift Timing Diagram for Four Synchronized Devices

# **Table 2. Phase Shift in Synchronization**

| SYNC_OUT<br>PIN-<br>STRAP<br>R(Ω)                | PHASE POSITION, SYNC_IN RISING TO LX1, LX2<br>RISING (NO EXTERNAL POWER-STAGE) | PHASE POSITION, SYNC_IN RISING TO LX1, LX2, LX3<br>RISING (WITH EXTERNAL POWER-STAGE) |

|--------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| 453                                              | 130°, 310°                                                                     | 130°, 250°, 370°                                                                      |

| 549                                              | 100°, 280°                                                                     | 100°, 220°, 340°                                                                      |

| 681                                              | 160°, 340°                                                                     | 160°, 280°, 400°                                                                      |

| 976                                              | 85°,265°                                                                       | 85°, 205°, 325°                                                                       |

| 1180                                             | 175°, 355°                                                                     | 175°, 295°, 415°                                                                      |

| 1400 (no<br>clock<br>output)                     | 40°, 220°                                                                      | 40°, 160°, 280°                                                                       |

| ≥ 1690 or<br>open<br>(clock<br>output<br>active) | 40°, 220°                                                                      | 40°, 160°, 280°                                                                       |

# Dual-Phase Scalable Integrated Voltage Regulator with PMBus Interface

### **Overvoltage Protection (Tracking OVP)**

The MAX20796 overvoltage protection compares the output-feedback voltage to the VOUT\_COMMAND value. If the output voltage exceeds VOUT\_COMMAND plus the tracking OVP threshold (see the *Electrical Characteristics* table), an OVP fault is triggered, PGOOD is deasserted, and the device stops switching by turning off both highside and low-side FETs immediately. The OVP default response is "Shutdown and Retry" mode, which can also be changed through PMBus command, VOUT\_OV\_FAULT\_RESPONSE. In "Shutdown and Retry" mode, the system first shuts down switching, deasserts PGOOD, waits for about 50ms and then restarts if the OVP fault disappears. In "Ignore" mode, the system allows switching to continue, but deasserts PGOOD and flags in the corresponding bit in the STATUS\_VOUT register. The OVP fault bit can be cleared by toggling the output enable state off and back on.

### **Undervoltage Protection (UVP)**

The MAX20796 undervoltage protection compares the output-feedback voltage to the VOUT\_COMMAND value. If the output voltage is smaller than the VOUT\_COMMAND minus the UVP threshold (see the <u>Electrical Characteristics</u> table), an UVP fault is triggered, PGOOD is deasserted, and the device stops switching by turning off both high-side and low-side FETs immediately. The UVP default response is "Shutdown and Retry" mode, which can also be changed through the PMBus command, VOUT\_UV\_FAULT\_RESPONSE. In "Shutdown and Retry" mode, the system first shuts down switching, deasserts PGOOD, waits for about 50ms and then restarts. In "Ignore" mode, the system just allows switching to continue, but deasserts PGOOD and flags the corresponding bit in STATUS register. The UVP fault bit can be cleared by toggling the output enable state off and back on.

### **Overvoltage Protection (Umbrella OVP)**

To gain a second level of protection, the absolute output voltage ( $V_{SNSP} - V_{SNSN}$ ) is monitored and compared with fixed thresholds during operation. Two fixed thresholds, 2.5V or 6.0V, are set corresponding to VOUT\_COMMAND in range of 0.5V to 2.437V or 2.438V to 5.0V, respectively. Both tracking and umbrella OVP mechanisms are handled by the same VOUT\_OV\_FAULT\_RESPONSE and reported together as STATUS\_VOUT [bit 7].

### **Overcurrent Protection (Average OCP)**

The total positive average current is compared to the number of phases times the per-phase OCP threshold defined by PGMD. Once an OCP fault is triggered, switching is shut down and PGOOD is deasserted. An OCP fault is not a latching fault and is registered in the fault log. Depending on the IOUT\_OC\_FAULT\_RESPONSE command setting, the regulator begins "Shutdown and Retry" (factory default) after about 50ms or "Shutdown only" without restart. The shutdown and retry continues until the load current falls below the threshold.

### **Overcurrent Protection (Power Stage Peak OCP)**

Besides average OCP, the MAX20796 has the instantaneous cycle-by-cycle peak current protection in each power train. The internal lossless current sense technology is used and intended to operate only in extreme overcurrent conditions to protect the integrated FETs. Its threshold is fixed as shown in the *Electrical Characteristics* table. Once the power-stage peak OCP is triggered, the relevant phase turns off the high-side FET and turns on its low-side FET to keep its peak current at a safe level. Since the protection is based on the instantaneous current, the ripple current must be considered when calculating the maximum average current per phase. The maximum positive DC-phase current before clamping can be calculated as shown in Equation 2.

### Equation 2:

$$I_{PHASE_DC_MAX_POS} = I_{POCP_R} - \frac{I_{PH_P} - P}{2}$$

Where:  $I_{PH_P-P}$  is the peak-to-peak phase-current ripple in the inductor.

The MAX20796 also has a negative cycle-by-cycle overcurrent protection (NOCP) for each power train. Its threshold is also fixed as shown in the <u>Electrical Characteristics</u> table. If the NOCP threshold is reached, the low-side FET turns off and the high-side FET turns on for protection. Equation 3 shows the maximum negative DC current per phase.

### Equation 3:

$I_{\text{PHASE}_\text{DC}_\text{MAX}_\text{NEG}} = I_{\text{NOCP}} + \frac{I_{\text{PH, PP}}}{2}$

# Dual-Phase Scalable Integrated Voltage Regulator with PMBus Interface

### Undervoltage Lockout (UVLO)

The MAX20796 includes UVLO circuits on the AVDD,  $V_{CC}$ , and  $V_{DDH}$  supply input pins. The UVLO thresholds are specified in the <u>Electrical Characteristics</u> table. If a UVLO event is detected, the system stops regulating. Once the faulted input voltage rises above its UVLO rising threshold, the device reinitializes a new startup process.

### **Overtemperature Protection**

Overtemperature protection ensures the power train as well as the controller works within a safe temperature range. There are two temperatures monitored in the MAX20796. READ\_TEMPERATURE\_1 reports the integrated power train junction temperature. If there is an external power stage connected, READ\_ TEMPERATURE\_2 reports its junction temperature by monitoring the TS\_FAULT pin voltage. If any temperature is over the programmed threshold, the fault is triggered. The regulator shuts down switching immediately by turning off both FETs, waiting for about 50ms off time, and then restarting if the junction temperature drops below threshold. STATUS\_TEMPERATURE is flagged to report the fault. The factory default threshold is typically 150°C and it can be programmed using the PMBus commands. OT\_FAULT\_RESPONSE can be programmed to "Shutdown and Retry" (factory default) or "Shutdown only."

### **Fault Handling Table**

The following table summarizes the fault types and system responses. "Configurable" means some of these options, "ignore," "shutdown" and "shutdown and retry," can be selected through PMBus. Refer to <u>Application Note 6453:</u> <u>MAX20796 PMBus User Guide</u> for details.

| FAULT<br>PROTECTION                      | STATUS PIN         | STATUS<br>REGISTER      | RESPONSE                                          | RESPONSE<br>REGISTER       | FAULT LIMIT<br>REGISTER |

|------------------------------------------|--------------------|-------------------------|---------------------------------------------------|----------------------------|-------------------------|

| A/DVDD UVLO                              | N/A                | N/A                     | Reset                                             | N/A                        | N/A                     |

| V <sub>CC</sub> _UVLO                    | ALERT              | STATUS_MFR_<br>SPECIFIC | Stop regulating until<br>UVLO condition<br>clears | N/A                        | N/A                     |

| V <sub>DDH</sub> _UVLO                   | ALERT              | STATUS_INPUT            | Shutdown and retry                                | N/A                        | N/A                     |

| BST_UVLO                                 | ALERT              | STATUS_MFR_<br>SPECIFIC | Stop regulating until<br>UVLO condition<br>clears | N/A                        | N/A                     |

| V <sub>OUT</sub> Tracking OVP            | ALERT/PGOOD        | STATUS_VOUT             | Configurable                                      | VOUT_OV_FAULT_<br>RESPONSE | VOUT_OV_FAULT_<br>LIMIT |

| V <sub>OUT</sub> Umbrella OVP            | ALERT/PGOOD        | STATUS_VOUT             | Configurable                                      | VOUT_OV_FAULT_<br>RESPONSE | Fixed                   |

| V <sub>OUT</sub> UVP                     | ALERT/PGOOD        | STATUS_VOUT             | Configurable                                      | VOUT_UV_FAULT_<br>RESPONSE | VOUT_UV_FAULT_<br>LIMIT |

| Average OCP                              | ALERT              | STATUS_IOUT             | Configurable                                      | IOUT_OC_FAULT_<br>RESPONSE | IOUT_OC_FAULT_<br>LIMIT |

| Power-Stage Peak<br>OCP (cycle-by-cycle) | N/A                | N/A                     | Duty-cycle truncation                             | N/A                        | Fixed                   |

| Overtemperature                          | ALERT              | STATUS_<br>TEMPERATURE  | Configurable                                      | OT_FAULT_<br>RESPONSE      | OT_FAULT_LIMIT          |

| Power-Stage Fault                        | ALERT/<br>TS_FAULT | STATUS_MFR_<br>SPECIFIC | Configurable                                      | SLV_FAULT_<br>RESPONSE     | N/A                     |

| Power-Stage TSENSE<br>Fault              | ALERT/<br>TS_FAULT | STATUS_<br>TEMPERATURE  | Configurable                                      | OT_FAULT_<br>RESPONSE      | OT_FAULT_LIMIT          |

| PT VX Short                              | N/A                | N/A                     | Configurable                                      | SLV_FAULT_<br>RESPONSE     | N/A                     |

| SNSP Open                                | ALERT              | STATUS_MFR_<br>SPECIFIC | No startup                                        | N/A                        | N/A                     |

### Table 3. Fault Handling

# Dual-Phase Scalable Integrated Voltage Regulator with PMBus Interface

### **Table 3. Fault Handling (continued)**

| PGMx Out-of-Range<br>Fault | ALERT | STATUS_MFR_<br>SPECIFIC | No startup | N/A | N/A |

|----------------------------|-------|-------------------------|------------|-----|-----|

|----------------------------|-------|-------------------------|------------|-----|-----|

### Nonvolatile PMBus Memory

The MAX20796 features nonvolatile memory for storage of PMBus command values, which is only guaranteed to retain values correctly when written while  $V_{DDH}$  is 10V to 16V, and while junction temperature is 0°C to 50°C. STORE\_USER\_ALL and STORE\_INVENTORY commands are not sent when these conditions are not met.. The memory capacity is such that there are 5 possible storage "slots." One slot can store most of the PMBus command sets. The contents of the "default" and "user" stores overrides pin-strap command values where appropriate, according to the parameter loading-precedence requirements of the PMBus specification.

At any time, the number of remaining storage slots can be determined by reading the OTP\_REMAINING command. Refer to <u>Application Note 6453</u>: <u>MAX20796 PMBus User Guide</u> for more information.

### Pin-Strap Programmability

### PMBus Address

The PMBus address can be programmed by the R\_ADDR resistor. 32 PMBus addresses can be pre-set by pin-strap.

### Pin-Strap Output Voltage and VOUT\_COMMAND

The PGMA pin-strap resistor is used to set the output voltage, i.e., the initial value of VOUT\_COMMAND. From 0.5V to 1.8V, each step is 50mV. Above 1.8V, only the commonly used rail voltages, e.g., 2.5V, 3.3V, and 5V can be programmed with direct feedback.

To set the output voltage other than by the pin-strap resistor, either use VOUT\_COMMAND through the PMBus interface or add a feedback divider to set the output voltage.

Once VOUT\_COMMAND is initially set by the pin-strap PGMA resistor or from nonvolatile memory, do not change the output voltage with VOUT\_COMMAND, or MARGIN\_HIGH/LOW while regulating by more than ±25%. The slew rate for decreasing the output voltage must not exceed -0.5V/ms, as set by -VOUT\_COMMAND/ TOFF\_FALL. The slew rate for startup and shutdown can be higher than this value if desired.

In the case, when output voltage is not included in the pin-strap table and VOUT\_COMMAND is not available, the MAX20796 also supports the feedback divider method to set the arbitrary output voltage. The new output voltage can be calculated as:

### Equation 4:

$$V_{\rm OUT} = V_{\rm DAC} \times (1 + \frac{R1 + R3}{R2})$$

where  $R_1$  is the resistor between output and the SNSP pin,  $R_3$  is the resistor between ground and the SNSN pin, and  $R_2$  is the resistor between the SNSP and SNSN pins.  $R_1$  is equal to  $R_3$ .

V<sub>DAC</sub> is the setpoint voltage via pin-strap, (e.g., 0.6V or 1.0V, etc).

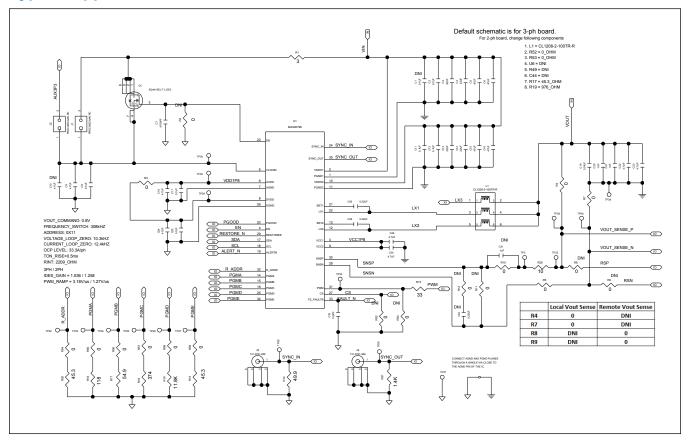

Refer to <u>Typical Application Circuit</u>, where  $R_1 = R_{10}$ ,  $R_2 = R_{11}$ , and  $R_3 = R_5$ .

$R_1$  and  $R_2$  are suggested to select small values (e.g., 100 $\Omega$  or below) in order to avoid output voltage setting error caused by SNSP input bias current;  $(R_1 + R_3)//R_2$ , or any series resistor on SNSP path should be much below 1.6k $\Omega$  to avoid falsely triggering SNSP open detection at startup. The resistors in the divider circuit must be sized appropriately to accommodate the power dissipation. Typically, 1/8W resistors are sufficient.

### Voltage-Loop Gain and Zero

Voltage loop compensation can be set by the PGMB pin-strap resistor. Eight different voltage-loop gains ( $I_{DES\_GAIN}$ ) and four different voltage loop zeros ( $f_{ZV}$ ) can be selected independently by this pin. To set a different voltage loop gain or zero,  $I_{DES\_GAIN}$  and  $F_{ZERO}$  commands can be used through the PMBus interface. Refer to <u>Application Note 6453</u>: <u>MAX20796 PMBus User Guide</u> for details.

# Dual-Phase Scalable Integrated Voltage Regulator with PMBus Interface

### R ADDR PGMA PGMB PGMC PGMD PGME POSITIVE PWM RAMP FREQUENCY IDES AVERAGE OCP TON VOUT R<sub>NOM</sub> RINT SWITCH BIN **PMBus** SLEW fzv fzc THRESHOLD COMMAND GAIN RISE (kHz) # ADDRESS (kHz) (Ω) RATE **(Ω)** fsw (PER PHASE) (V) (V/V)(ms) (V/µs) (kHz) (A) 200 0 37.4 0x10h 0.5 0.98 10.3 4522 5 0.425 10 0.5 1 45.3 0x11h 0.55 1.258 10.3 3668 5 0.425 13.3 0.5 308 2 54.9 0x12h 0.6 1.536 10.3 2964 5 0.425 16.7 0.5 400 3 68.1 0x13h 0.65 10.3 2209 5 0.425 20 0.5 444 1.814 4 82.5 0x14h 0.7 2.092 10.3 1761 5 0.425 23.3 0.5 500 5 97.6 0x15h 0.75 2.37 10.3 1257 5 0.425 26.7 0.5 571 6 118 0x16h 0.8 2.648 10.3 1098 5 0.425 30 0.5 666 7 140 0x17h 0.85 2.926 10.3 878 5 0.425 33.3 0.5 799 8 169 0x18h 0.9 0.98 4522 12.4 1.27 10 1 200 16.5 9 205 0x19h 0.95 1.258 16.5 3668 12.4 1.27 13.3 1 308 10 249 0x1Ah 1 1.536 16.5 2964 12.4 1.27 16.7 1 400 11 374 0x1Bh 1.05 1.814 16.5 2209 12.4 1.27 20 1 444 1761 12 453 0x1Ch 1.1 2.092 16.5 12.4 1.27 23.3 1 500 13 549 0x1Dh 1.15 2.37 16.5 1257 12.4 1.27 26.7 1 571 1.27 30 666 14 681 0x1Eh 1.2 2.648 1098 12.4 1 16.5 1.25 1.27 15 976 0x1Fh 2.926 16.5 878 12.4 33.3 1 799 16 1.18k 0x20h 1.3 0.98 19.6 4522 18 3.18 10 4 200 17 1.4k 0x21h 1.35 1.258 19.6 3668 18 3.18 13.3 4 308 18 1.69k 0x22h 1.4 1.536 19.6 2964 18 3.18 16.7 4 400 19 2.05k 0x23h 1.45 1.814 19.6 2209 18 3.18 20 4 444 2.49k 1.5 19.6 1761 18 3.18 4 500 20 0x24h 2.092 23.3 21 8.25k 0x25h 1.55 2.37 1257 18 3.18 26.7 4 571 19.6 22 18 4 9.76k 0x26h 1.6 2.648 19.6 1098 3.18 30 666 1.65 2.926 878 18 3.18 33.3 4 799 23 11.8k 0x27h 19.6 24 14.0k 0x28h 1.7 0.98 28.8 4522 21.9 4.46 10 8 200 1.75 8 308 25 16.9k 0x29h 1.258 28.8 3668 21.9 4.46 13.3 20.5k 0x2Ah 1.8 1.536 2964 4.46 8 400 26 28.8 21.9 16.7 27 24.9k 0x2Bh 2.5 1.814 28.8 2209 21.9 4.46 20 8 444 28 30.1k 0x2Ch 3.3 2.092 1761 21.9 4.46 23.3 8 500 28.8 29 37.4k 0x2Dh 5 2.37 28.8 1257 21.9 4.46 26.7 8 571 30 45.3k 0x2Eh 0.8 2.648 28.8 1098 21.9 4.46 30 8 666 31 54.9k 0x2Fh 0.7 2.926 28.9 4.46 33.3 8 799 878 21.9

# **Table 4. Pin-Strap Configurations**

### Current-Loop Gain and Zero

Current-loop compensation can be set by the PGMC pinstrap resistor. Eight different current-loop gains ( $R_{INT}$ ) and four different current-loop zeros ( $f_{ZC}$ ) can be selected independently by this pin. Larger  $R_{INT}$  gives higher current loop gain.

# Dual-Phase Scalable Integrated Voltage Regulator with PMBus Interface

### **Compensation Ramp and OCP Thresholds**

An internal PWM ramp compensation is used to improve overall loop stability. Its slew rate can be programmed using the PGMD pin-strap resistor. This pin also sets up system average positive OCP thresholds, which is shown as per phase average current in the table. To get the total output current, the selected value needs to be multiplied by the actual phase count. To use other ramp slew rate values, the PWM\_RAMP command can be used through the PMBus interface. Refer to <u>Application Note 6453</u>: MAX20796 PMBus User Guide for details.

### Soft Time and Switching Frequency

PGME pin-strap resistor can be used to program soft-start time (TON\_RISE) and switching frequency (fSW). Four different soft-start times and eight different switching frequencies can be programmed with PGME. For other soft-start times, the TON\_RISE command can be used through the PMBus interface. Refer to <u>Application Note 6453: MAX20796</u> <u>PMBus User Guide</u> for details.

# Dual-Phase Scalable Integrated Voltage Regulator with PMBus Interface

# **Application Circuit Design Procedure**

### **Output Capacitor Selection**

The primary factors in determining the total required output capacitance ( $C_{OUT}$ ) are the maximum allowable output voltage overshoot and undershoot ("sag" and "soar") during load transients. In step-down converters, the voltage overshoot ( $\Delta V_{OST}$ ) during unloading is the dominant factor in setting the required  $C_{OUT}$  because less forcing voltage is available to reduce the inductor current. For an unloading current-step ( $\Delta I$ ) and maximum allowed output-voltage overshoot ( $\Delta V_{OST}$ ), the minimum required output capacitance can be estimated as in Equation 5.

### **Equation 5:**

$$C_{\text{OUT}} = \frac{\left(\frac{\Delta I}{N} + \frac{I_{\text{PH}} - P - P}{2}\right)^2 \times L \times N}{2 \times \Delta V_{\text{OST}} \times V_{\text{OUT}}}$$

where:

L = Inductance per phase

N = Number of phases

I<sub>PH P-P</sub> = Peak-to-peak phase-current ripple in the inductor

V<sub>OUT</sub> = Nominal output voltage

Selecting a higher total C<sub>OUT</sub> value increases design margin against component variation and effective capacitance loss due to voltage bias.

For example, in a two-phase application,  $V_{DDH} = 12V$ ,  $V_{OUT} = 0.8V$ , L = 100nH (coupled inductor), unloading step  $\Delta I = 10A$ ,  $\Delta V_{OST} = 3\%$  of 0.8V input (= 24mV), the minimum AC capacitance can be calculated at 450µF. If any polymer capacitor is used, their equivalent-series resistance and inductance (ESR, ESL) cause output voltage ripple increase. Thus, sufficient capacitance margin and ceramic capacitors must be considered on the output side to further reduce the overshoot in order to meet the overall transient specs.

### **Output Inductor Selection**

For single-phase discrete inductors, the phase current peak-to-peak ripple (IPH P-P is calculated as in Equation 6.

### Equation 6:

$$I_{\text{PH}_{P}-P} = \frac{(V_{\text{DDH}} - V_{\text{OUT}}) \times V_{\text{OUT}}}{f_{\text{SW}} \times L \times V_{\text{DDH}}}$$

For coupled inductors driven with duty cycle  $\leq$  1/N, the approximate inductor peak-to-peak phase-current ripple can be calculated as in Equation 7.

### Equation 7:

$$I_{\text{PH}\_\text{P}\_P} = \frac{V_{\text{OUT}}}{f_{\text{SW}} \times L} (\frac{1}{N} - \frac{V_{\text{OUT}}}{V_{\text{DDH}}})$$

where:

IPH P-P = Peak-to-peak phase-current ripple in the inductor

f<sub>SW</sub> = Switching frequency

- L = Inductance per phase

- N = Number of phases

V<sub>DDH</sub> = Input voltage

V<sub>OUT</sub> = Nominal output voltage