## Low-Power, High-Performance, Fully Integrated Octal Ultrasound Receiver (Octal LNA, VGA, AAF, ADC, and CWD Beamformer)

#### **General Description**

#### **Benefits and Features**

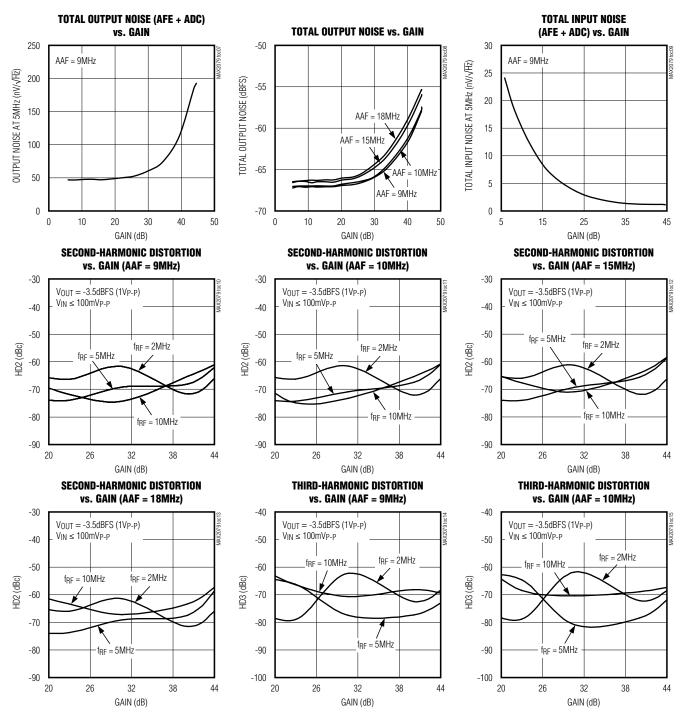

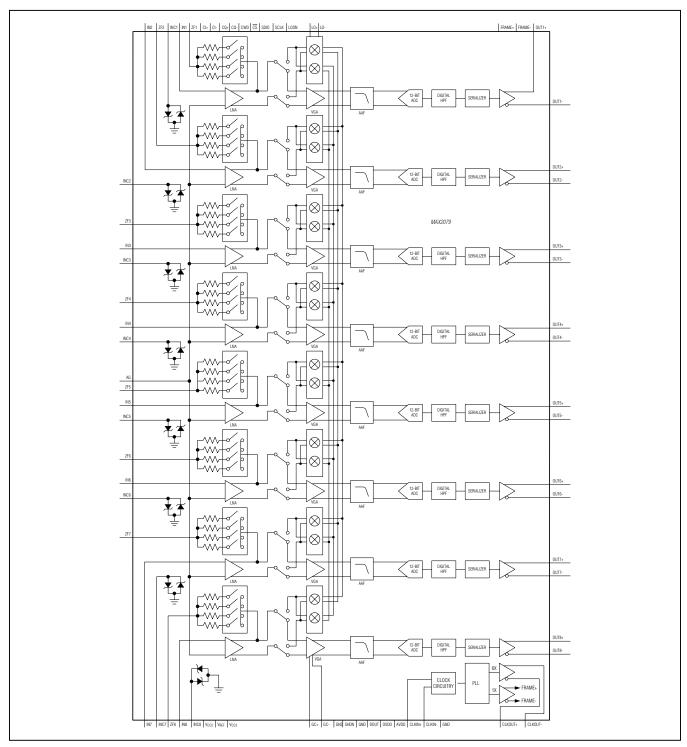

The MAX2079 fully integrated octal ultrasound receiver is optimized for high channel count, high-performance portable and cart-based ultrasound systems. The easyto-use integrated receiver allows the user to achieve high-end 2D and Doppler imaging capability using substantially less space and power. The highly compact low-noise amplifier (LNA), variable-gain amplifier (VGA), anti-alias filter (AAF), analog-to-digital converter (ADC), and digital highpass filter (HPF) achieve an ultra-low 2.8dB noise figure at  $R_S = R_{IN} = 200\Omega$  with a very low 120mW per channel power dissipation at 50Msps. The full receive channel has been optimized for secondharmonic imaging with an exceptional 76dBFS SNR over a 2MHz bandwidth, and -70dBc second-harmonic distortion at  $f_{RF} = 5MHz$  over the full receiver gain range. Near-carrier dynamic range has also been optimized for exceptional pulsed and color-flow Doppler performance under high-clutter conditions. The bipolar front-end and CMOS ADC achieve an exceptional near-carrier SNR of 137dBFS/Hz at 1kHz from a 5MHz tone for excellent lowvelocity Doppler sensitivity.

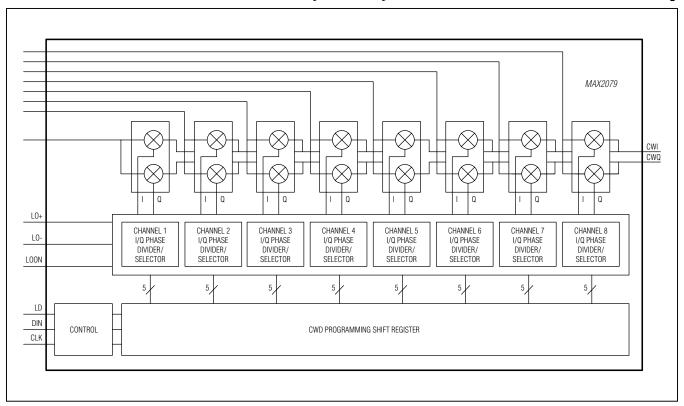

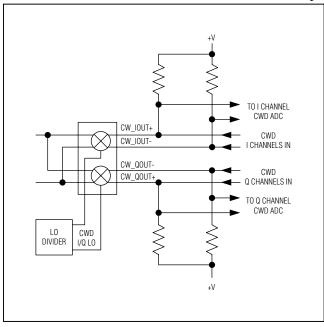

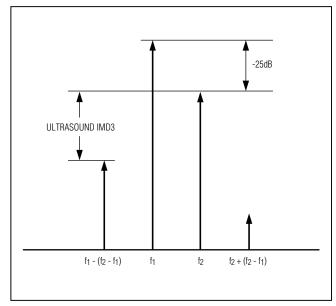

The device also includes an octal CWD beamformer for a full Doppler solution. Separate mixers for each channel are available for optimal CWD sensitivity.

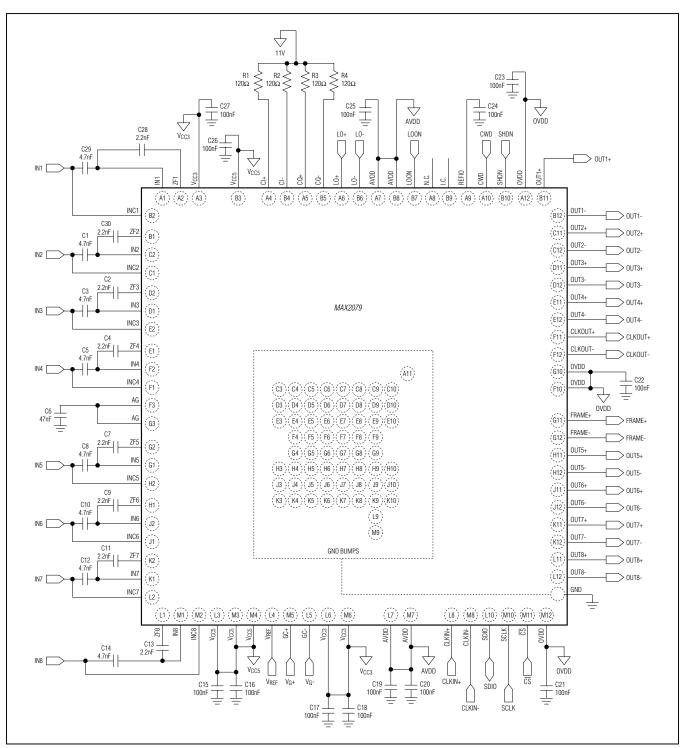

The MAX2079 octal ultrasound front-end is available in a small, 10mm x 10mm, CTBGA package and is specified over the 0°C to +70°C temperature range.

### **Applications**

Medical Ultrasound Imaging Sonar

♦ 8 Full Channels of LNA, VGA, AAF, 12-Bit ADC, Digital HPF and CWD Mixer Beamformer in a Small, 10mm x 10mm CTBGA Package

♦ Improves System Sensitivity

♦ Ultra-Low Full-Channel Noise Figure of 2.8dB at  $R_S = R_{IN} = 200\Omega$

**♦ Improves System Dynamic Range**

- ♦ 76dBFS Image Path SNR Over 2MHz Bandwidth

at f<sub>RF</sub> = 5MHz

- 137dBFS/Hz Image Path SNR at 1kHz Offset from f<sub>RF</sub> = 5MHz

- **♦ Consumes Less Power**

- → Ultra-Low Power of Only 120mW per Full Channel in Imaging Mode at 50Msps

- ♦ Selectable Active Input Impedance Matching of 50Ω, 100Ω, 200Ω, and 1kΩ

- ♦ Programmable VGA Output Clamp

- ♦ Integrated Selectable 3-Pole 9MHz, 10MHz, 15MHz, and 18MHz Butterworth Anti-Alias Filter

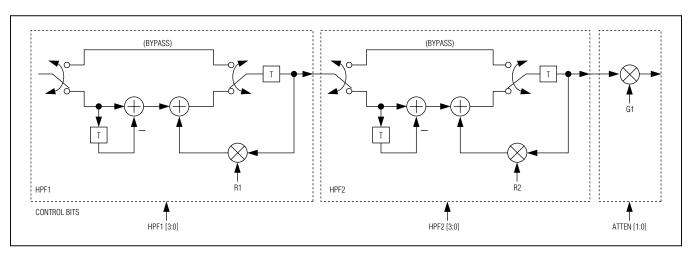

- ♦ Programmable, Digital Highpass, 2-Pole Filter

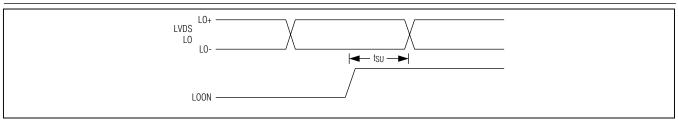

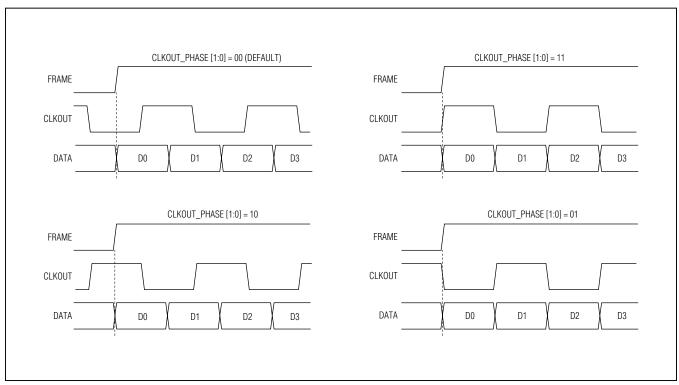

- ♦ Serial LVDS Digital Outputs

- ♦ Fast Recovery Low-Power Modes (< 2µs)

- ♦ Separate Channel I/Q CWD Mixers for Improved Dynamic Range and Sensitivity

Ordering Information appears at end of data sheet.

For related parts and recommended products to use with this part, refer to www.maximintegrated.com/MAX2079.related.

Soldering Temperature (reflow) .....+260°C

## Low-Power, High-Performance, Fully Integrated Octal Ultrasound Receiver (Octal LNA, VGA, AAF, ADC, and CWD Beamformer)

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC3</sub> , V <sub>CC5</sub> to GND0.3V to +5.5V<br>AVDD, OVDD to GND0.3V to +2.1V                  | OUT+/-, SDIO, SCLK, $\overline{\text{CS}}$ , CLKOUT+/-, FRAME+/-, SHDN, CWD to GND0.3V to the lower of (VOVDD + 0.3V)                             |

|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC5</sub> - V <sub>CC3</sub> > -0.3V                                                                | and +2.1V                                                                                                                                         |

| V <sub>REF</sub> , LO+/-, GC+/- to GND0.3V to (V <sub>CC3</sub> + 0.3V)<br>CI+/-, CQ+/- to GND0.3V to +13V | CI+/-, CQ+/-, V <sub>CC5</sub> , V <sub>CC3</sub> , AVDD/OVDD, V <sub>REF</sub> analog and digital control signals must be applied in this order. |

| ZF_, IN_, AG to GND0.3V to (V <sub>CC5</sub> + 0.3V)                                                       | Input Differential Voltage2.0V <sub>P-P</sub> differential                                                                                        |

| INC±20mA DC                                                                                                | Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                                                                                             |

| IN_ to AG0.6V to +0.6V                                                                                     | 144-Bump CTBGA (derate 33.3mW/°C above +70°C)3200mW                                                                                               |

| REFIO, CLKIN+/-, LOON to                                                                                   | Operating Case Temperature Range (Note 1)0°C to +70°C                                                                                             |

| GND0.3V to the lower of $(V_{AVDD} + 0.3V)$ and +2.1V                                                      | Junction Temperature+150°C                                                                                                                        |

|                                                                                                            | Storage Temperature Range40°C to +150°C                                                                                                           |

Note 1:  $T_C$  is the temperature on the bump of the package.  $T_A$  is the ambient temperature of the device and PCB.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **PACKAGE THERMAL CHARACTERISTICS (Note 2)**

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ )......25°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )......7.7°C/W

**Note 2:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

## OCTAL ULTRASOUND FRONT-END SPECIFICATIONS DC ELECTRICAL CHARACTERISTICS—VGA MODE (CWD BEAMFORMER OFF)

$(V_{REF} = 2.5V, V_{CC3} = 3.13V \text{ to } 3.47V, V_{CC5} = 4.5V \text{ to } 5.25V, V_{AVDD} = V_{OVDD} = 1.7V \text{ to } 1.9V, T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}, V_{GND} = 0V, \text{SHDN} = 0, CWD = 0, LOON = 0, f_{RF} = 5MHz, 50mV_{P-P}, ADC f_{CLK} = 50Msps, digital HPF set to 60/64, two poles, 15/16 digital gain, V_{GC+} - V_{GC-} = -3V (minimum gain), high LNA gain. Typical values are at V_{REF} = 2.5V, V_{CC3} = 3.3V, V_{CC5} = 4.75V, V_{AVDD} = V_{OVDD} = 1.8V, V_{GC+} - V_{GC-} = 0V, T_A = +25^{\circ}\text{C}, unless otherwise noted.) (Note 3)$

| PARAMETER                                                                                           | SYMBOL                                                           | CONDITIONS                                                       | MIN   | TYP  | MAX   | UNITS |

|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------|-------|------|-------|-------|

| 3.3V Supply Voltage                                                                                 | V <sub>CC3</sub>                                                 | V <sub>CC3</sub> pins                                            | 3.13  | 3.3  | 3.47  | V     |

| 5V Supply Voltage                                                                                   | V <sub>CC5</sub>                                                 | V <sub>CC5</sub> pins                                            | 4.5   | 4.75 | 5.25  | V     |

| 1.8V Supply Voltage                                                                                 | V <sub>CC1.8</sub>                                               | AVDD and OVDD pins                                               | 1.7   | 1.8  | 1.9   | V     |

| External Reference Voltage<br>Range                                                                 | V <sub>REF</sub>                                                 | (Note 4)                                                         | 2.475 |      | 2.525 | V     |

| External Reference Current                                                                          |                                                                  | Total current into the V <sub>REF</sub> pin                      |       | 5    |       | μΑ    |

| 3V Supply Current per Channel                                                                       | Іссз                                                             | Total I divided by 8, V <sub>GC+</sub> - V <sub>GC-</sub> = 0.4V |       | 9.5  | 16    | mA    |

| 5V Supply Current per Channel                                                                       | I <sub>CC5</sub>                                                 | Total I divided by 8                                             |       | 6.4  | 9     | mA    |

| 4 0 1 0 1                                                                                           |                                                                  | Total I divided by 8, AVDD + OVDD                                |       | 32   | 37.9  | mA    |

| 1.8V Supply Current per Channel ICC1.8 Total I divided by 8, AVDD + OVDD Total I divided by 8, AVDD |                                                                  |                                                                  | 20    | 22.8 | mA    |       |

| per orialities                                                                                      | Supply Current Channel ICC1.8 Total I divided by 8, AVDD 20 22.8 |                                                                  | 15.1  | mA   |       |       |

| DC Power per Channel                                                                                | P_NM                                                             | $V_{GC+} - V_{GC-} = -0.4V$                                      |       | 120  |       | mW    |

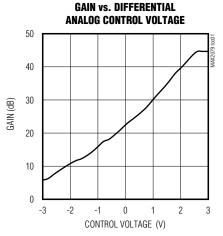

| Differential Analog Control<br>Voltage Range                                                        | VGAIN_RANG                                                       | V <sub>GC+</sub> - V <sub>GC-</sub>                              |       | ±3   |       | V     |

## Low-Power, High-Performance, Fully Integrated Octal Ultrasound Receiver (Octal LNA, VGA, AAF, ADC, and CWD Beamformer)

#### DC ELECTRICAL CHARACTERISTICS—VGA MODE (CWD BEAMFORMER OFF) (continued)

$\begin{array}{l} (V_{REF}=2.5V,V_{CC3}=3.13V\ to\ 3.47V,V_{CC5}=4.5V\ to\ 5.25V,V_{AVDD}=V_{OVDD}=1.7V\ to\ 1.9V,T_{A}=0^{\circ}C\ to\ +70^{\circ}C,V_{GND}=0V,SHDN=0,CWD=0,LOON=0,f_{RF}=5MHz,50mV_{P-P},ADC\ f_{CLK}=50Msps,digital\ HPF\ set\ to\ 60/64,\ two\ poles,\ 15/16\ digital\ gain,V_{GC+}-V_{GC-}=-3V\ (minimum\ gain),\ high\ LNA\ gain.\ Typical\ values\ are\ at\ V_{REF}=2.5V,V_{CC3}=3.3V,V_{CC5}=4.75V,V_{AVDD}=V_{OVDD}=1.8V,V_{CC4}-V_{CC5}=0V,T_{A}=+25^{\circ}C,\ unless\ otherwise\ noted.) \\ \end{array}$

| PARAMETER                                           | SYMBOL      | CONDITIONS                                 | MIN TY    | P MAX | UNITS |

|-----------------------------------------------------|-------------|--------------------------------------------|-----------|-------|-------|

| 5V Supply Nap Current                               | I_NP_5V_TOT | SHDN = 1, nap mode (all 8 channels)        | 3         | )     | mA    |

| 3V Supply Nap Current                               | I_NP_3V_TOT | SHDN = 1, nap mode (all 8 channels)        | 0.0       | 35    | mA    |

| 1.8V Supply Nap Current                             |             | SHDN = 1, nap mode (all 8 channels)        | 4         | )     | mA    |

| 5V Supply Power-Down Current                        | I_PD_5V_TOT | SHDN = 1, power-down mode (all 8 channels) | 1         |       | μА    |

| 3V Supply Power-Down Current                        | I_PD_3V_TOT | SHDN = 1, power-down mode (all 8 channels) | 1         | μА    |       |

| 1.8V Supply Power-Down<br>Current                   |             | SHDN = 1, power-down mode (all 8 channels) | 0.0       | 38    | mA    |

| Common-Mode Voltage for Differential Analog Control | VGAIN_COMM  | (V <sub>GC+</sub> - V <sub>GC-</sub> )/2   | 1.6<br>±5 |       | V     |

| Source/Sink Current for Gain Control Pins           | I_ACONTROL  | Per pin                                    | ±1        | .6    | μА    |

### AC ELECTRICAL CHARACTERISTICS—VGA MODE (CWD BEAMFORMER OFF)

$(V_{REF} = 2.5V, V_{CC3} = 3.13V \ to \ 3.47V, V_{CC5} = 4.5V \ to \ 5.25V, V_{AVDD} = V_{OVDD} = 1.7V \ to \ 1.9V, T_A = 0^{\circ}C \ to \ +70^{\circ}C, V_{GND} = 0V, SHDN = 0, CWD = 0, LOON = 0, f_{RF} = 5MHz, 50mV_{P-P}, ADC \ f_{CLK} = 50Msps, digital HPF set to 60/64, two poles, 15/16 digital gain, V_{GC+} - V_{GC-} = -3V \ (minimum gain), high LNA gain. Typical values are at V_{REF} = 2.5V, V_{CC3} = 3.3V, V_{CC5} = 4.75V, V_{AVDD} = V_{OVDD} = 1.8V, V_{GC+} - V_{GC-} = 0V, T_A = +25^{\circ}C, unless otherwise noted.) (Note 3)$

| PARAMETER                                                                                                                                                                                                                                                                                    | CONDITIONS                                              | MIN  | TYP | MAX | UNITS |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------|-----|-----|-------|--|--|--|

| ADC Bits                                                                                                                                                                                                                                                                                     |                                                         |      | 12  |     | Bits  |  |  |  |

| Minimum ADC Sample Rate                                                                                                                                                                                                                                                                      |                                                         |      | 25  |     | Msps  |  |  |  |

| Maximum ADC Sample Rate                                                                                                                                                                                                                                                                      |                                                         | 50   |     |     | Msps  |  |  |  |

| Mode-Select Response Time                                                                                                                                                                                                                                                                    | CWD stepped from 0 to 1, DC stable within 10%           |      | 1   |     |       |  |  |  |

| Note 5) CWD stepped from 1 to 0, DC stable within 10% $50\Omega \text{ mode, } f_{RF} = 2MHz$                                                                                                                                                                                                |                                                         | 1    |     | μs  |       |  |  |  |

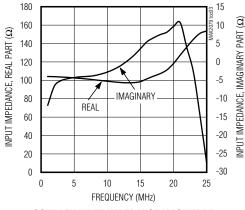

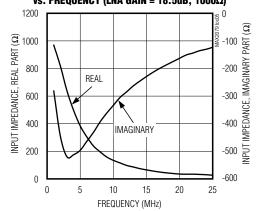

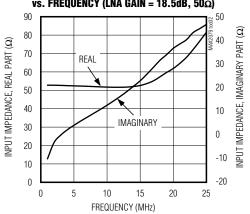

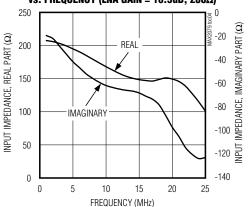

|                                                                                                                                                                                                                                                                                              | $50\Omega$ mode, f <sub>RF</sub> = 2MHz                 |      | 50  |     |       |  |  |  |

| ADC Bits         12           Minimum ADC Sample Rate         25           Maximum ADC Sample Rate         50           Mode-Select Response Time (Note 5)         CWD stepped from 0 to 1, DC stable within 10%         1           CWD stepped from 1 to 0, DC stable within 10%         1 |                                                         | Ω    |     |     |       |  |  |  |

|                                                                                                                                                                                                                                                                                              | \$2                                                     |      |     |     |       |  |  |  |

|                                                                                                                                                                                                                                                                                              |                                                         | 1000 |     |     |       |  |  |  |

|                                                                                                                                                                                                                                                                                              | $R_S = R_{IN} = 50\Omega$ , $V_{GC+} - V_{GC-} = +3V$   |      | 4.8 |     |       |  |  |  |

| Input Impedance                                                                                                                                                                                                                                                                              |                                                         | -10  |     |     |       |  |  |  |

|                                                                                                                                                                                                                                                                                              | $R_S = R_{IN} = 200\Omega$ , $V_{GC+} - V_{GC-} = +3V$  |      | 2.8 |     | dB    |  |  |  |

|                                                                                                                                                                                                                                                                                              | $R_S = R_{IN} = 1000\Omega$ , $V_{GC+} - V_{GC-} = +3V$ |      | 2.5 |     |       |  |  |  |

| Noise Figure (Low LNA Gain)                                                                                                                                                                                                                                                                  | $R_S = R_{IN} = 200\Omega$ , $V_{GC+} - V_{GC-} = +3V$  |      | 3.8 |     | dB    |  |  |  |

## Low-Power, High-Performance, Fully Integrated Octal Ultrasound Receiver (Octal LNA, VGA, AAF, ADC, and CWD Beamformer)

#### AC ELECTRICAL CHARACTERISTICS—VGA MODE (CWD BEAMFORMER OFF) (continued)

$(V_{REF} = 2.5V, V_{CC3} = 3.13V \text{ to } 3.47V, V_{CC5} = 4.5V \text{ to } 5.25V, V_{AVDD} = V_{OVDD} = 1.7V \text{ to } 1.9V, T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}, V_{GND} = 0V, \text{SHDN} = 0, CWD = 0, LOON = 0, f_{RF} = 5MHz, 50mV_{P-P}, ADC f_{CLK} = 50Msps, digital HPF set to 60/64, two poles, 15/16 digital gain, V_{GC+} - V_{GC-} = -3V (minimum gain), high LNA gain. Typical values are at V_{REF} = 2.5V, V_{CC3} = 3.3V, V_{CC5} = 4.75V, V_{AVDD} = V_{OVDD} = 1.8V, V_{GC+} - V_{GC-} = 0V, T_A = +25^{\circ}\text{C}, unless otherwise noted.) (Note 3)$

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CONDITIONS                                                                                                                                                                               | MIN  | TYP   | MAX  | UNITS  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|--------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | No input signal, ratio of 8-channel noise power to single-channel noise power                                                                                                            |      | 9.0   |      |        |

| 8-Channel Correlated Noise<br>Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5MHz signal applied to all 8 channels, $V_{GC+}$ - $V_{GC-}$ = 0V, $f_{RF}$ = 5MHz at -3dBFS, ratio of 8-channel noise power to single-channel noise power                               |      | 8.5   |      | dB     |

| LNA Gain (Low LNA Gain)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                          |      | 12.5  |      | dB     |

| LNA Gain (High LNA Gain)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                          |      | 18.5  |      | dB     |

| Maximum Gain (High LNA Gain)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V <sub>GC+</sub> - V <sub>GC-</sub> = +3V (max gain), LNA input to ADC Input                                                                                                             |      | 44.7  |      | dB     |

| Minimum Gain (High LNA Gain)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V <sub>GC+</sub> - V <sub>GC-</sub> = -3V (min gain), LNA input to ADC Input                                                                                                             |      | 5.9   |      | dB     |

| Maximum Gain (Low LNA Gain)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V <sub>GC+</sub> - V <sub>GC-</sub> = +3V (max gain), LNA input to ADC Input                                                                                                             |      | 40.4  |      | dB     |

| Minimum Gain (Low LNA Gain)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $V_{GC+} - V_{GC-} = -3V$ (min gain), LNA input to ADC input                                                                                                                             |      | 1.4   |      | dB     |

| Gain Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                          |      | 38.8  |      | dB     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9MHz setting                                                                                                                                                                             |      | 9     |      |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10MHz setting                                                                                                                                                                            |      | 10    |      | N 41 1 |

| 8-Channel Correlated Noise Power  8-Channel Correlated Noise Power  8-Channel Correlated Noise Power  8-Channel Correlated Noise Power  SMHz signal applied to a fRF = 5MHz at -3dBFS, r single-channel noise power  LNA Gain (Low LNA Gain)  LNA Gain (High LNA Gain)  Maximum Gain (High LNA Gain)  Maximum Gain (Low LNA Gain)  VGC+ - VGC- = +3V (maximation)  Maximum Gain (Low LNA Gain)  Maximum Gain (Low LNA Gain)  VGC+ - VGC- = -3V (maximation)  Maximum Gain (Low LNA Gain)  VGC+ - VGC- = +3V (maximation)  Maximum Gain (Low LNA Gain)  VGC+ - VGC- = -3V (maximation)  Maximum Gain (Low LNA Gain)  VGC+ - VGC- = -3V (maximation)  Maximum Gain (Low LNA Gain)  VGC+ - VGC- = -3V (maximation)  Maximum Gain (Low LNA Gain)  VGC+ - VGC- = -3V (maximation)  Maximum Gain (Low LNA Gain)  VGC+ - VGC- = -3V (maximation)  Maximum Gain (Low LNA Gain)  VGC+ - VGC- = -3V (maximation)  Maximum Gain (Low LNA Gain)  VGC+ - VGC- = -3V (maximation)  Maximum Gain (Low LNA Gain)  VGC+ - VGC- = -3V (maximation)  Maximum Gain (Low LNA Gain)  VGC+ - VGC- = -3V (maximation)  Maximum Gain (Low LNA Gain)  VGC+ - VGC- = -3V (maximation)  Maximum Gain (Low LNA Gain)  VGC+ - VGC- = -3V (maximation)  Maximum Gain (Low LNA Gain)  VGC+ - VGC- = -3V (maximation)  Maximum Gain (Low LNA Gain)  VGC+ - VGC- = -3V (maximation)  Maximum Gain (Low LNA Gain)  VGC+ - VGC- = -3V (maximation)  Maximum Gain (Low LNA Gain)  VGC+ - VGC- = -3V (maximation)  Maximum Gain (Low LNA Gain)  VGC+ - VGC- = -3V (maximation)  MBL VGC VGC  LNA = high gain, VGC+ - | 15MHz setting                                                                                                                                                                            |      | 15    |      | MHz    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 18MHz setting                                                                                                                                                                            |      | 18    |      |        |

| l. ' '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                          |      | ±10   |      | %      |

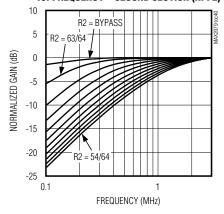

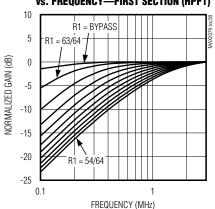

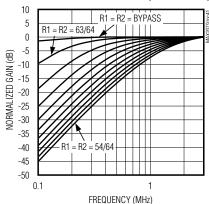

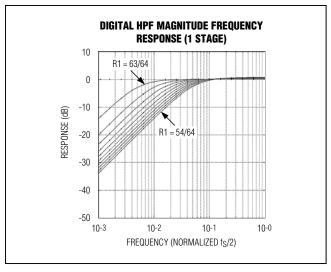

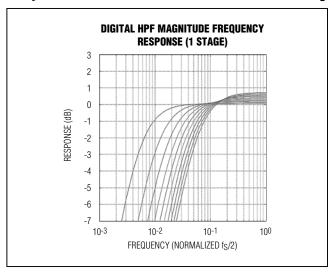

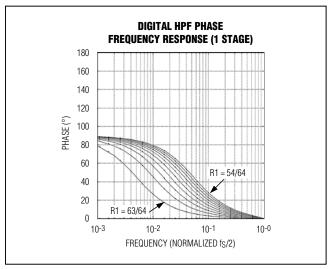

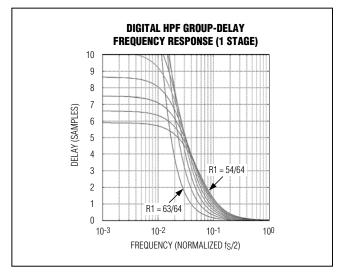

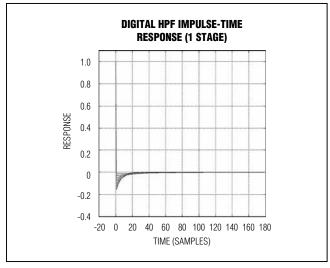

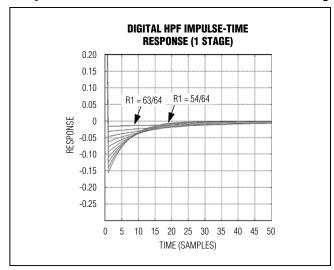

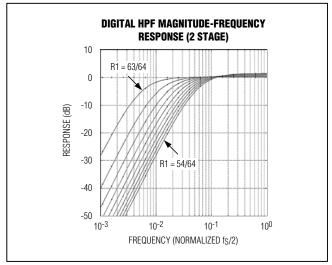

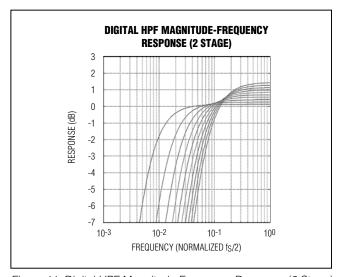

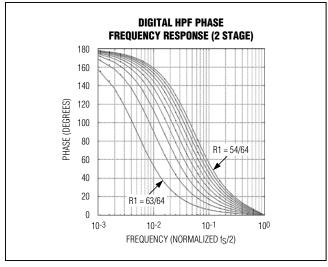

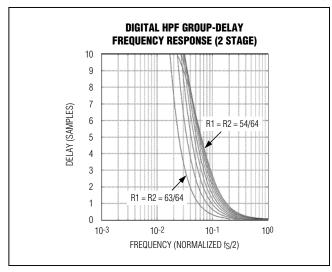

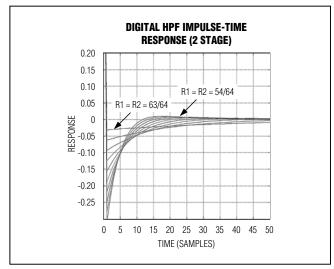

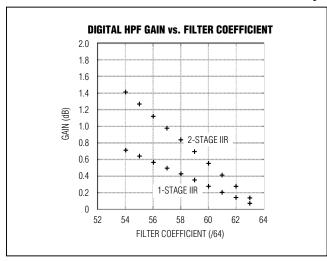

| Digital Highpass Filter 3dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2 poles, coefficients R1 = R2 = 63/64, f <sub>CLK</sub> = 50Msps                                                                                                                         |      | 0.185 |      |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2 poles, coefficients R1 = R2 = 54/64, f <sub>CLK</sub> = 50Msps                                                                                                                         |      | 1.736 |      | MHz    |

| Clamp Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Clamp on (V <sub>P-P</sub> on AAF Output/ADC Input, digital HPF bypassed)                                                                                                                |      | 92    |      | %FS    |

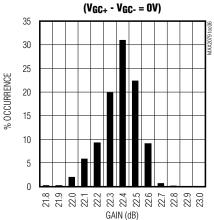

| Device-to-Device Gain Matching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $T_A = +25^{\circ}C$ , $V_{GC+} - V_{GC-} = -3V$ to $+3V$ (Note 6)                                                                                                                       | -1.6 | ±0.5  | +1.6 | dB     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | LNA = high gain, $V_{GC+} - V_{GC-} = -3V$ (VGA = min gain), gain ratio with $330mV_{P-P}/50mV_{P-P}$ input tones                                                                        |      | 0.7   |      |        |

| Input Gain Compression                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | LNA = low gain, $V_{GC+} - V_{GC-} = -3V$ (VGA = min gain), gain ratio with $600mV_{P-P}/50mV_{P-P}$ input tones                                                                         |      | 0.9   |      | dB     |

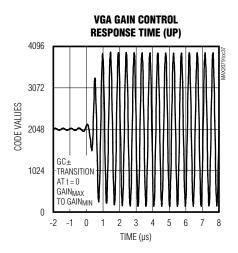

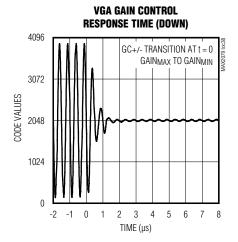

| NOA O : D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Gain step up ( $V_{IN} = 5mV_{P-P}$ , $V_{GC+} - V_{GC-}$ changed from -3V to +3V, settling time is measured within 1dB final value)                                                     |      | 0.8   |      |        |

| VGA Gain Response Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Gain step down ( $V_{IN} = 5mV_{P-P}$ , $V_{GC+} - V_{GC-}$ changed from -3V to +3V, settling time is measured within 1dB final value)                                                   |      | 1.8   |      | μs     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Over drive is $\pm 10$ mA in clamping diodes, $V_{GC+} - V_{GC-} = 1.0V$ (gain = 30dB), 16 pulses at 5MHz, repetition rate 20kHz; offset is measured at output when RF duty cycle is off |      | < 3.3 |      | %FS    |

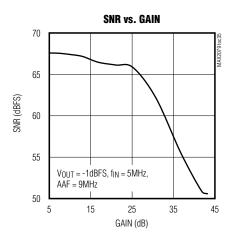

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $V_{OUT\_}$ = -1dBFS, $V_{IN}$ = 200m $V_{P-P}$ , $f_{RF}$ = 5MHz at -1dBFS, anti-alias filter = 9MHz, 50Msps sample rate                                                                |      | 67    |      | dBFS   |

## Low-Power, High-Performance, Fully Integrated Octal Ultrasound Receiver (Octal LNA, VGA, AAF, ADC, and CWD Beamformer)

#### AC ELECTRICAL CHARACTERISTICS—VGA MODE (CWD BEAMFORMER OFF) (continued)