19-0517; Rev 0; 6/06 EVALUATION KIT AVAILABLE 12-Bit, 2.3Gsps, Multi-Nyquist DAC with Selectable Frequency Response

## **General Description**

The MAX19692 12-bit, 2.3Gsps digital-to-analog converter (DAC) enables direct digital synthesis of high-frequency and wideband signals in baseband and higher Nyquist zones. It has been optimized for wideband communications and radar applications. It has excellent spurious and noise performance and can be used for synthesis of wideband signals in the frequency range from DC to more than 2GHz. The 2.3Gsps update rate allows digital generation of signals with more than 1GHz bandwidth. The selectable frequency response enables signal output with high SNR and excellent gain flatness in the first three Nyquist zones, reducing the number of upconversion stages needed in a radio transmitter. With its unique ability to generate broadband signals over a wide frequency range, the MAX19692 enables ultra-high data rate wireless modems and multistandard software radio transmitters.

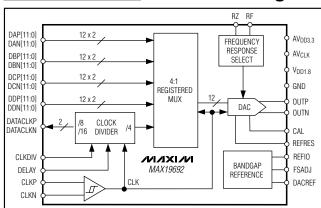

The MAX19692 features an update rate up to 2.3Gsps, and has four 12-bit multiplexed low-voltage differential signaling (LVDS) input ports that each operate up to 575MHz. The device accepts a clock at the DAC update rate that can be either a sine wave or a square wave. The input data rate is 1/4 the DAC update rate. The MAX19692 provides an LVDS data clock output to simplify interfacing to FPGA or ASIC devices.

The MAX19692 has three frequency response output modes:

- Non-Return-to-Zero (NRZ) mode is the most common in the industry and provides highest dynamic range and output power in the 1st Nyquist zone.

- Return-to-Zero (RZ) mode trades off SNR for improved gain flatness in the 1st, 2nd, and 3rd Nyquist zones.

- Radio Frequency (RF) mode provides higher SNR and excellent dynamic performance in the 2nd and 3rd Nyquist zones.

The MAX19692 is a current-steering DAC with an integrated, self-calibrated  $50\Omega$  differential output termination to ensure optimum dynamic performance. The MAX19692 operates from 3.3V and 1.8V power supplies and consumes 760mW at 1.0Gsps.

### Applications

Radar Waveform and LO Signal Synthesis Digital IF Generation in X-Band Transmitters Arbitrary Waveform Generators

**Direct Digital Synthesis** Automatic Test Equipment **Direct Digital Generation** of Wideband RF Signals Up to 2GHz

Pin Configuration appears at end of data sheet.

##

Features

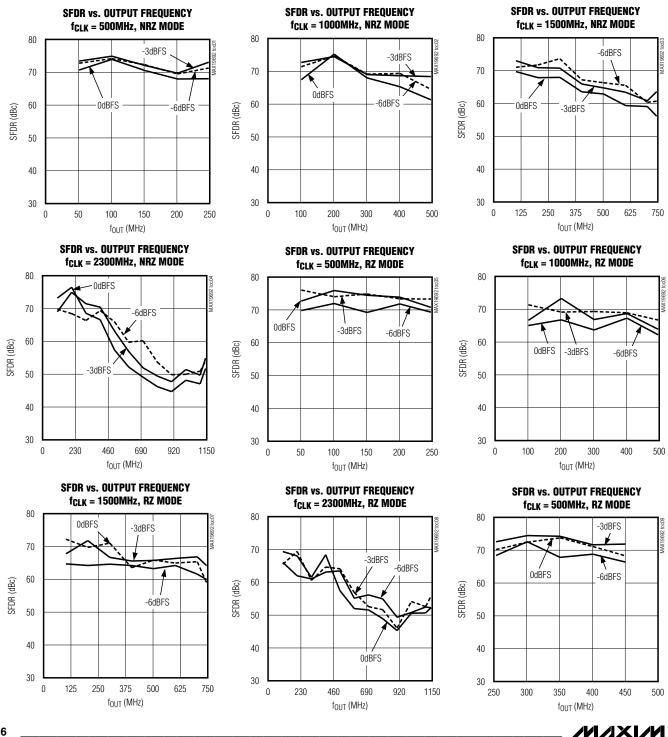

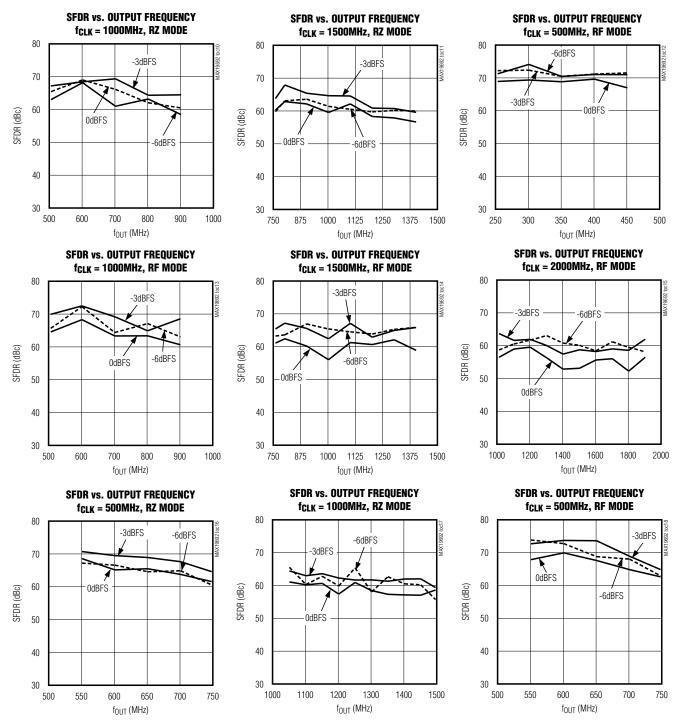

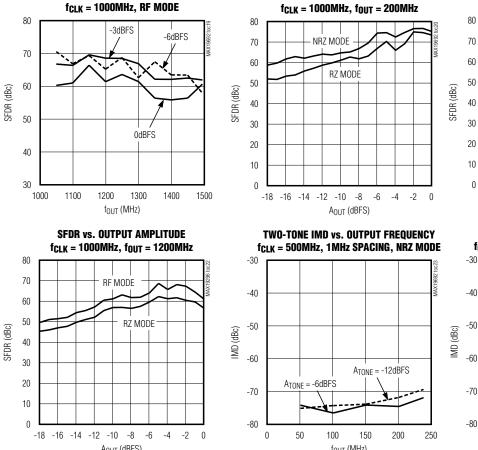

- Industry-Leading Dynamic Performance SFDR = 68dBc at four = 1200MHz Noise Density = -162dBm/Hz at 200MHz

- IGHz Signal Bandwidth

- Frequency Response Modes: NRZ, RZ, RF

- High SNR and Exceptional Gain Flatness in Nyquist Zones 1, 2, 3

- ♦ 4:1 Multiplexed LVDS Inputs (Up to 575MHz Each)

- Internal 50Ω Differential Output Termination

- ♦ Low Power: 760mW (f<sub>CLK</sub> = 1000MHz)

- Compact 11mm x 11mm, 169 CSBGA Package

- Evaluation Kit Available (Order MAX19692EVKIT)

### **Ordering Information**

| PART          | TEMP RANGE     | PACKAGE   | PKGCODE  |

|---------------|----------------|-----------|----------|

| MAX19692EXW-D | -40°C to +85°C | 169 CSBGA | X16911-1 |

#### SELECTABLE FREQUENCY RESPONSE 0 NRZ -5 OUTPUT AMPLITUDE RESPONSE (dB) -10 -15 -20 -25 -30 -35 -40 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8 2.0 four NORMALIZED TO DAC UPDATE RATE (fcl k)

1

Maxim Integrated Products

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642. or visit Maxim's website at www.maxim-ic.com.

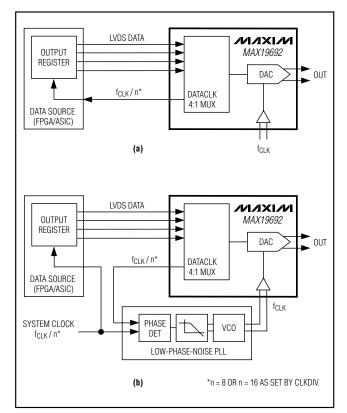

## Functional Diagram

### **ABSOLUTE MAXIMUM RATINGS**

| AV <sub>DD3.3</sub> to GND, DACREF0.3V to +3.9V                    |

|--------------------------------------------------------------------|

| V <sub>DD1.8</sub> , AV <sub>CLK</sub> to GND, DACREF0.3V to +2.1V |

| REFIO, FSADJ to GND, DACREF0.3V to (AV <sub>DD3.3</sub> + 0.3V)    |

| OUTP, OUTN to GND, DACREF0.3V to (AV <sub>DD3.3</sub> + 1.0V)      |

| CREF to GND, DACREF0.3V to (V <sub>DD1.8</sub> + 0.3V)             |

| DELAY, CLKDIV, RZ, RF, REFRES,                                     |

| CAL to GND, DACREF0.3V to (AV <sub>DD3.3</sub> + 0.3V)             |

| CLKP, CLKN to GND, DACREF0.3V to (AV <sub>CLK</sub> + 0.3V)        |

| DAP0–DAP11, DBP0–DBP11,                                            |

| DCP0–DCP11 to GND, DACREF0.3V to (V <sub>DD1.8</sub> + 0.3V)       |

| DDP0–DDP11 to GND, DACREF0.3V to (V <sub>DD1.8</sub> + 0.3V)       |

| DAN0–DAN11, DBN0–DBN11,                                            |

| DCN0–DCN11 to GND, DACREF0.3V to (V <sub>DD1.8</sub> + 0.3V)       |

DDN0–DDN11 to GND, DACREF......0.3V to (V\_DD1.8 + 0.3V) DATACLKP, DATACLKN to GND,

Storage Temperature Range .....-60°C to +150°C

Note 1: Thermal resistance based on a 4.5in x 5.5in multilayer board.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

$(AV_{DD3,3} = 3.3V, V_{DD1,8} = AV_{CLK} = 1.8V, R_{REFRES} = 500\Omega, R_{SET} = 2k\Omega, V_{REFIO} = external 1.25V, CAL on, NRZ mode, transformer$ coupled differential output, I<sub>OUT</sub> = 20mA, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 2)

| PARAMETER                           | SYMBOL    | CONDITIONS                                                     | MIN  | ТҮР     | МАХ  | UNITS  |

|-------------------------------------|-----------|----------------------------------------------------------------|------|---------|------|--------|

| STATIC PERFORMANC                   | E         |                                                                |      |         |      |        |

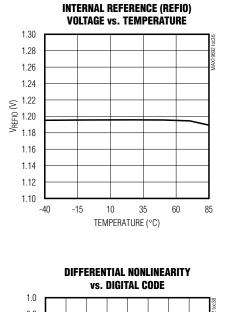

| Resolution                          |           |                                                                |      | 12      |      | Bits   |

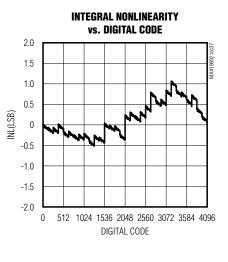

| Integral Nonlinearity               | INL       | Measured differentially                                        |      | ±1.3    |      | LSB    |

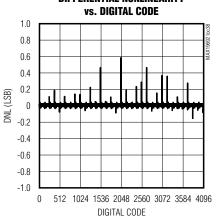

| Differential Nonlinearity           | DNL       | Measured differentially                                        |      | ±0.9    |      | LSB    |

| Offset Voltage Error                | OS        | Measured differentially, no external load resistors            | -0.5 | ±0.1    | +0.5 | %FS    |

| Offset Drift                        |           |                                                                |      | ±10     |      | ppm/°C |

| Full-Scale Output<br>Current        | IOUT      | (Note 3)                                                       | 8    |         | 20   | mA     |

| Output-Current Gain<br>Error        | GE        |                                                                | -4   |         | +4   | %FS    |

| Output-Voltage Gain                 |           | Internal reference                                             |      | -0.003  |      |        |

| Drift                               |           | External reference                                             |      | -0.0025 |      | dB/°C  |

| Maximum Output<br>Power             | Pout      | Differential, into 50 $\Omega$ load                            |      | -2.6    |      | dBm    |

| Output Resistance                   | Rout      | Differential, CAL $\ge$ 0.7 x AV <sub>DD3.3</sub> (Note 4)     | 44   | 48      | 52   | Ω      |

| DYNAMIC PERFORMA                    | NCE (Note | 5)                                                             |      |         |      |        |

| Minimum Output<br>Update Rate       | fclk      |                                                                |      |         | 10   | MHz    |

| Maximum Output<br>Update Rate       | fclk      | $1.8V \le V_{DD1.8} \le 1.9V$                                  | 2300 |         |      | MHz    |

| Wideband Noise-<br>Spectral Density |           | f <sub>CLK</sub> = 1000MHz, f <sub>OUT</sub> = 200MHz, -12dBFS |      | -162    |      | dBm/Hz |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD3.3} = 3.3V, V_{DD1.8} = AV_{CLK} = 1.8V, R_{REFRES} = 500\Omega, R_{SET} = 2k\Omega, V_{REFIO} = external 1.25V, CAL on, NRZ mode, transformer$ coupled differential output, I<sub>OUT</sub> = 20mA, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 2)

| PARAMETER                                                                 | SYMBOL             |                                         | CONDITIONS                                                             | MIN  | ТҮР  | МАХ  | UNITS  |

|---------------------------------------------------------------------------|--------------------|-----------------------------------------|------------------------------------------------------------------------|------|------|------|--------|

|                                                                           |                    |                                         | f <sub>OUT</sub> = 50MHz, -6dBFS, NRZ mode                             |      | 73   |      |        |

|                                                                           |                    |                                         | f <sub>OUT</sub> = 100MHz, -6dBFS, NRZ mode                            |      | 74   |      | dBc    |

|                                                                           |                    | $f_{CLK} = 500 MHz$                     | f <sub>OUT</sub> = 200MHz, -6dBFS, NRZ mode                            |      | 70   |      |        |

|                                                                           |                    |                                         | f <sub>OUT</sub> = 400MHz, -6dBFS, RF mode                             |      | 71   |      |        |

|                                                                           |                    |                                         | f <sub>OUT</sub> = 600MHz, -6dBFS, RF mode                             |      | 73   |      |        |

|                                                                           |                    |                                         | f <sub>OUT</sub> = 200MHz, -6dBFS, NRZ mode                            |      | 75   |      |        |

|                                                                           |                    |                                         | $f_{OUT} = 409MHz$ , -0.1dBFS,<br>NRZ mode, T <sub>A</sub> $\ge$ +25°C | 60   | 68   |      |        |

| Spurious-Free<br>Dynamic Range within<br>Nyquist Zone of f <sub>OUT</sub> | SFDR               | $f_{CLK} = 1000MHz$                     | f <sub>OUT</sub> = 409MHz, -0.1dBFS,<br>NRZ mode                       | 56   | 68   |      | dBc    |

|                                                                           |                    |                                         | f <sub>OUT</sub> = 800MHz, -6dBFS, RF mode                             |      | 67   |      |        |

|                                                                           |                    |                                         | f <sub>OUT</sub> = 1200MHz, -6dBFS, RF mode                            |      | 65   |      |        |

|                                                                           |                    |                                         | f <sub>OUT</sub> = 100MHz, -6dBFS                                      |      | 71   |      |        |

|                                                                           |                    | f <sub>CLK</sub> = 2000MHz,             | f <sub>OUT</sub> = 200MHz, -6dBFS                                      |      | 68   |      |        |

|                                                                           |                    | NRZ mode                                | f <sub>OUT</sub> = 400MHz, -6dBFS                                      |      | 70   |      |        |

|                                                                           |                    |                                         | f <sub>OUT</sub> = 800MHz, -6dBFS                                      |      | 58   |      |        |

|                                                                           |                    | f <sub>CLK</sub> = 2300MHz,<br>NRZ mode | $f_{OUT} = 92MHz$ , 0dBFS                                              | 60   | 71   |      |        |

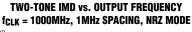

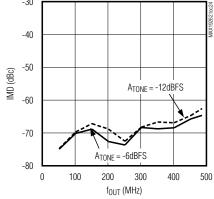

|                                                                           |                    | f <sub>CLK</sub> = 1000MHz,             | f <sub>OUT1</sub> = 200MHz, -7dBFS                                     |      | 70   |      |        |

|                                                                           |                    | NRZ mode                                | f <sub>OUT2</sub> = 201MHz, -7dBFS                                     |      | -72  |      |        |

| 2-Tone IMD                                                                | TTIMD              | f <sub>CLK</sub> = 1000MHz,             | f <sub>OUT1</sub> = 1300MHz, -7dBFS                                    |      |      |      | dBC    |

|                                                                           |                    | RF mode                                 | f <sub>OUT2</sub> = 1301MHz, -7dBFS                                    |      | -66  |      |        |

| Minimum Output<br>Bandwidth                                               | BW-3dB             | (Note 6)                                |                                                                        |      | 1500 |      | MHz    |

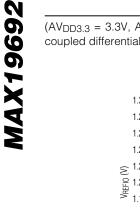

| REFERENCE                                                                 |                    |                                         |                                                                        |      |      |      |        |

| Internal Reference<br>Voltage Range                                       | VREFIO             |                                         |                                                                        | 1.1  | 1.2  | 1.3  | V      |

| Reference Input<br>Compliance Range                                       | VREFIOCR           |                                         |                                                                        | 0.50 |      | 1.25 | V      |

| Reference Input<br>Resistance                                             | R <sub>REFIO</sub> |                                         |                                                                        |      | 10   |      | kΩ     |

| Reference Voltage Drift                                                   | TCOREF             |                                         |                                                                        |      | 50   |      | ppm/°C |

| ANALOG OUTPUT TIM                                                         | ING (Note 7        | )                                       |                                                                        |      |      |      |        |

| Output Fall Time                                                          | tFALL              | 90% to 10%                              |                                                                        |      | 270  |      | ps     |

| Output Rise Time                                                          | <b>t</b> RISE      | 10% to 90%                              |                                                                        |      | 270  |      | ps     |

| Cottling Time                                                             |                    | Settling to 0.1%                        |                                                                        |      | 3.5  |      |        |

| Settling Time                                                             | ts                 | Settling to 0.025%                      |                                                                        | 4.5  |      |      | ns     |

| Output Propagation<br>Delay                                               | tPD                | (Note 8)                                |                                                                        |      | 0.9  |      | ns     |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD3.3} = 3.3V, V_{DD1.8} = AV_{CLK} = 1.8V, R_{REFRES} = 500\Omega, R_{SET} = 2k\Omega, V_{REFIO} = external 1.25V, CAL on, NRZ mode, transformer-coupled differential output, I_{OUT} = 20mA, T_A = -40^{\circ}C to +85^{\circ}C, unless otherwise noted. Typical values are at T_A = +25^{\circ}C.) (Note 2)$

| PARAMETER                                             | SYMBOL            | CONDITIONS                                                                              | MIN                        | ТҮР                  | MAX             | UNITS           |

|-------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------|----------------------------|----------------------|-----------------|-----------------|

| TIMING CHARACTERIS                                    | STICS             | ·                                                                                       |                            |                      |                 |                 |

| Data to Clock Setup<br>Time                           | <b>t</b> SETUP    | Referenced to rising edge of data clock (Note 9)                                        | 1.6                        |                      |                 | ns              |

| Data to Clock Hold<br>Time                            | thold             | Referenced to rising edge of data clock (Note 9)                                        | -0.8                       |                      |                 | ns              |

| Data Latency                                          |                   | (Note 10)                                                                               |                            | 14                   |                 | Clock<br>cycles |

| LVDS LOGIC INPUTS (<br>DDP11-DDP0, DDN11-             |                   | P0, DAN11–DAN0, DBP11–DBP0, DBN11–DBN0, DCP11                                           | –DCP0, D                   | CN11-DC              | CNO,            |                 |

| Differential Input<br>Logic-High                      | VIH               |                                                                                         | 100                        |                      |                 | mV              |

| Differential Input<br>Logic-Low                       | VIL               |                                                                                         |                            |                      | -100            | mV              |

| Common-Mode<br>Voltage Range                          | VCOM              |                                                                                         | 1.125                      |                      | 1.375           | V               |

| Differential Input<br>Resistance                      | R <sub>IN</sub>   |                                                                                         | 85                         |                      | 125             | Ω               |

| Input Capacitance                                     | CIN               |                                                                                         |                            | 1.5                  |                 | pF              |

| CMOS LOGIC INPUTS                                     | (RZ, RF, CL       | KDIV, DELAY)                                                                            | -                          |                      |                 |                 |

| Input Logic-High                                      | VIH               |                                                                                         | 0.7 x<br>AV <sub>DD3</sub> |                      |                 | V               |

| Input Logic-Low                                       | VIL               |                                                                                         |                            | A                    | 0.3 x<br>VDD3.3 | V               |

| Input Leakage Current                                 | l <sub>IN</sub>   |                                                                                         | -15                        |                      | +15             | μA              |

| Input Capacitance                                     | CIN               |                                                                                         |                            | 3                    |                 | pF              |

| CLOCK INPUTS (CLKP                                    | , CLKN)           | r                                                                                       | -                          |                      |                 | n               |

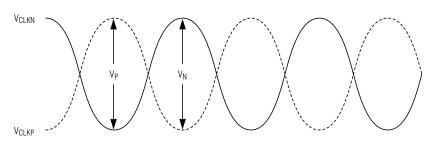

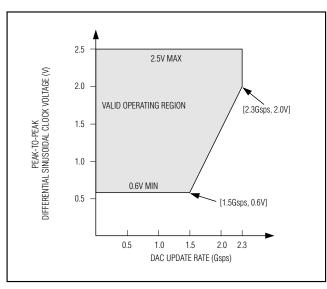

| Minimum Differential Input<br>Voltage Swing (Note 11) | VCLK              | $f_{CLK} \le 1.5 GHz$<br>$f_{CLK} = 2.3 GHz$ , see Figure 6 for dependence on $f_{CLK}$ |                            | 0.6                  |                 | Vp-p            |

| Maximum Differential<br>Voltage Swing                 | VCLK              | (Note 11)                                                                               |                            | 2.5                  |                 | Vp-p            |

| Differential Input<br>Slew Rate                       | SR <sub>CLK</sub> |                                                                                         |                            | 6000                 |                 | V/µs            |

| Common-Mode<br>Voltage Range                          | VCOMCLK           |                                                                                         | 0.55                       | AV <sub>CLK</sub> /3 | 0.65            | V               |

| Input Resistance                                      | R <sub>CLK</sub>  | Differential                                                                            |                            | 100                  |                 | Ω               |

| Input Capacitance                                     | CCLK              |                                                                                         |                            | 2                    |                 | рF              |

**MAX19692**

M/X/W

## **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD3.3} = 3.3V, V_{DD1.8} = AV_{CLK} = 1.8V, R_{REFRES} = 500\Omega, R_{SET} = 2k\Omega, V_{REFIO} = external 1.25V, CAL on, NRZ mode, transformer$  $coupled differential output, I_{OUT} = 20mA, T_A = -40°C to +85°C, unless otherwise noted. Typical values are at T_A = +25°C.) (Note 2)$

| PARAMETER                      | SYMBOL                          | CONDITIONS                                                                     | MIN   | ТҮР   | MAX   | UNITS |

|--------------------------------|---------------------------------|--------------------------------------------------------------------------------|-------|-------|-------|-------|

| DATA CLOCK OUTPUT              | TS (DATAC                       | LKP, DATACLKN)                                                                 |       |       |       |       |

| Differential Output            | VDCLK                           | With 100 $\Omega$ differential termination                                     | ±0.25 | ±0.35 | ±0.45 | V     |

| Output Rise and<br>Fall Time   | t <sub>R</sub> , t <sub>F</sub> | With 100 $\Omega$ differential termination                                     |       | 0.5   |       | ns    |

| Common-Mode<br>Voltage Range   | V <sub>СОМ</sub>                |                                                                                | 1.125 | 1.25  | 1.375 | V     |

| Output Resistance              | RCLK                            | Differential                                                                   |       | 100   |       | Ω     |

| POWER SUPPLIES                 |                                 |                                                                                |       |       |       |       |

| Analog-Supply Voltage<br>Range | AV <sub>DD3.3</sub>             |                                                                                | 3.1   | 3.3   | 3.5   | V     |

| 1.8V Supply Voltage            | Veete                           | 10MHz ≤ f <sub>CLK</sub> < 2.0GHz (Note 9)                                     | 1.7   | 1.8   | 1.9   | V     |

| Range                          | VDD1.8                          | $2.0$ GHz $\leq f_{CLK} \leq 2.3$ GHz                                          | 1.8   |       | 1.9   | v     |

| Clock-Supply Voltage           | AVCLK                           | $10MHz \le f_{CLK} < 2.0GHz$ (Note 9)                                          | 1.7   | 1.8   | 1.9   | V     |

| Range                          | AVCLK                           | $2.0GHz \le f_{CLK} \le 2.3GHz$                                                | 1.8   |       | 1.9   | v     |

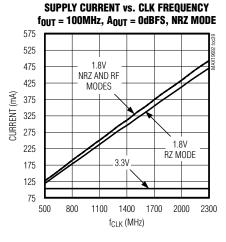

| Analog Supply<br>Current       | IAVDD3.3                        | $f_{CLK} = 1000MHz$ , $f_{OUT} = 10MHz$ , $A_{OUT} = 0dBFS$                    |       | 107   | 117   | mA    |

| Digital Supply Current         | IVDD1.8                         | f <sub>CLK</sub> = 1000MHz, f <sub>OUT</sub> = 10MHz, A <sub>OUT</sub> = 0dBFS |       | 61    | 76    | mA    |

| Clock Supply Current           | IAVCLK                          | $f_{CLK}$ = 1000MHz, $f_{OUT}$ = 10MHz, $A_{OUT}$ = 0dBFS                      |       | 164   | 191   | mA    |

| Total Power Dissipation        | PDISS                           | $f_{CLK}$ = 1000MHz, $f_{OUT}$ = 10MHz, $A_{OUT}$ = 0dBFS                      |       | 760   | 870   | mW    |

Note 2: All specifications are 100% tested at  $T_A \ge +25^{\circ}$ C. Specifications at  $T_A < +25^{\circ}$ C are guaranteed by design and characterization.

**Note 3:** Nominal full-scale current  $I_{OUT} = 32 \times I_{REF}$ .

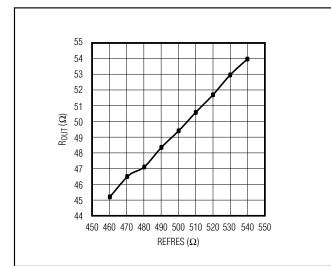

Note 4:  $R_{OUT}$  can be set to  $50\Omega$  as described in the *Output Resistor Calibration* section.

**Note 5:** CLK input = +10dBm, AC-coupled sine wave.

Note 6: Excludes impulse-response dependent rolloff inherent in the DAC. Measured single-ended into  $50\Omega$  termination resistor.

**Note 7:** Measured differentially into a  $50\Omega$  termination resistor.

Note 8: Excludes data latency.

Note 9: Guaranteed by design and characterization.

Note 10: DA\_P/DA\_N to DAC output.

Note 11: Differential voltage swing defined as  $|V_P| + |V_N|$ .

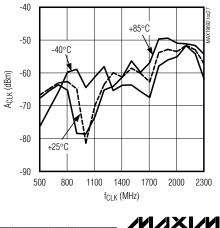

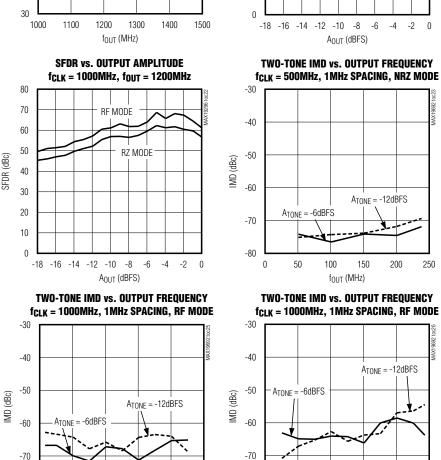

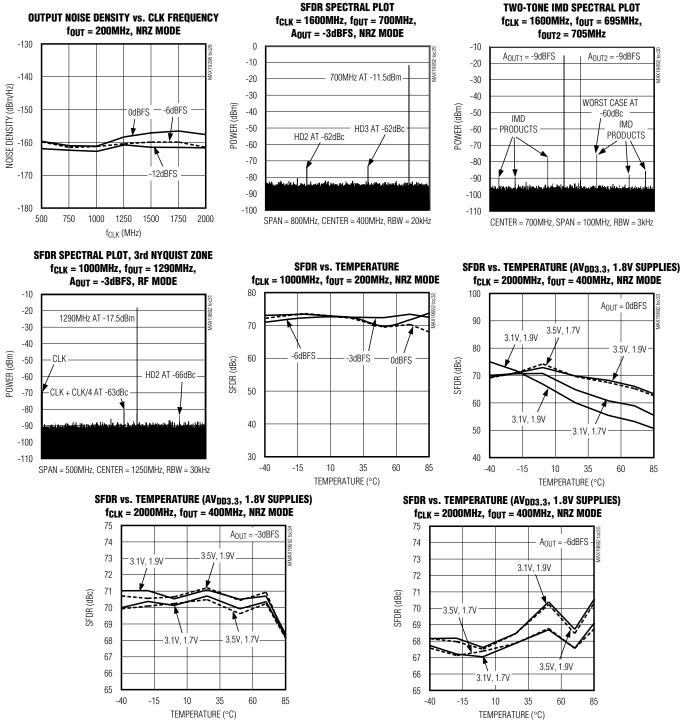

(AVDD3.3 = 3.3V, AVDD1.8 = DVDD = AVCLK = 1.8V, RREFRES = 500Ω, RSET = 2kΩ, VREFIO = external 1.25V, CAL on, transformercoupled differential output,  $I_{OUT} = 20$ mA,  $T_A = +25$ °C, unless otherwise noted.)

**Typical Operating Characteristics**

## **Typical Operating Characteristics (continued)**

(AV<sub>DD3.3</sub> = 3.3V, AV<sub>DD1.8</sub> = DV<sub>DD</sub> = AV<sub>CLK</sub> = 1.8V, R<sub>REFRES</sub> = 500Ω, R<sub>SET</sub> = 2kΩ, V<sub>REFIO</sub> = external 1.25V, CAL on, transformer-

## Typical Operating Characteristics (continued)

(AV<sub>DD3.3</sub> = 3.3V, AV<sub>DD1.8</sub> = DV<sub>DD</sub> = AV<sub>CLK</sub> = 1.8V, R<sub>REFRES</sub> = 500Ω, R<sub>SET</sub> = 2kΩ, V<sub>REFIO</sub> = external 1.25V, CAL on, transformercoupled differential output,  $I_{OUT} = 20$ mA,  $T_A = +25$ °C, unless otherwise noted.)

**SFDR vs. OUTPUT AMPLITUDE**

-80

8

500

600

700

f<sub>OUT</sub> (MHz)

AOUT (dBFS)

-8 -6 -4 -2 0

**SFDR vs. OUTPUT AMPLITUDE**

fclk = 1000MHz, four = 800MHz

**R7 MODF**

RF MODE

-18 -16 -14 -12 -10

**CLK FEEDTHROUGH vs. CLK FREQUENCY** fout = 200MHz, Aout = -1dBFS, NRZ MODE

-80

1000

1100

1200

four (MHz)

1300

1400

1500

900

1000

## \_Typical Operating Characteristics (continued)

$(AV_{DD3.3} = 3.3V, AV_{DD1.8} = DV_{DD} = AV_{CLK} = 1.8V, R_{REFRES} = 500\Omega, R_{SET} = 2k\Omega, V_{REFIO} = external 1.25V, CAL on, transformer$ coupled differential output, I<sub>OUT</sub> = 20mA, T<sub>A</sub> = +25°C, unless otherwise noted.)

9

## **Typical Operating Characteristics (continued)**

$(AV_{DD3.3} = 3.3V, AV_{DD1.8} = DV_{DD} = AV_{CLK} = 1.8V, R_{REFRES} = 500\Omega, R_{SET} = 2k\Omega, V_{REFIO} = external 1.25V, CAL on, transformer$ coupled differential output, I<sub>OUT</sub> = 20mA, T<sub>A</sub> = +25°C, unless otherwise noted.)

## Pin Description

| PIN                                                                  | NAME                | FUNCTION                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

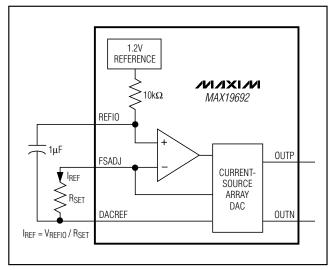

| A1                                                                   | REFIO               | Reference Input/Output. Output pin for the internal 1.2V-bandgap reference. REFIO has a $10k\Omega$ series resistance and can be driven using an external reference. Connect a $1\mu$ F capacitor between REFIO and DACREF.                                                                                                       |

| A2                                                                   | FSADJ               | Full-Scale Adjust Input. Sets the full-scale output current of the DAC. For a 20mA full-scale output current, connect a $2k\Omega$ resistor between FSADJ and DACREF.                                                                                                                                                             |

| АЗ                                                                   | DACREF              | Current-Set Resistor Return Path. For a 20mA full-scale output current, connect a $2k\Omega$ resistor between FSADJ and DACREF. DACREF is internally connected to AGND. <b>DO NOT CONNECT TO EXTERNAL GROUND.</b>                                                                                                                 |

| A4, A5, A7, A9                                                       | AV <sub>DD3.3</sub> | Analog 3.3V Supply Voltage. Accepts a 3.1V to 3.5V supply voltage range. Connect 47nF bypass capacitors between each AV_DD3.3 pin and AGND.                                                                                                                                                                                       |

| A6                                                                   | OUTP                | Positive Terminal of Differential DAC Output. OUTP has a calibrated internal 25 $\Omega$ resistor to AV_DD3.3.                                                                                                                                                                                                                    |

| A8                                                                   | OUTN                | Negative Terminal of Differential DAC Output. OUTN has a calibrated internal 25 $\Omega$ resistor to AV <sub>DD3.3</sub> .                                                                                                                                                                                                        |

| A10, B10, C2, C3, C10,<br>E1–E4, E10–E13, F13                        | V <sub>DD1.8</sub>  | Analog 1.8V Supply Voltage. Accepts a 1.7V to 1.9V supply voltage range. Connect 47nF bypass capacitors between each $V_{DD1.8}$ pin and GND.                                                                                                                                                                                     |

| A11, A13, B5–B9, B11,<br>C4–C9, C11, D1–D11,<br>D13, E5–E9, G13, M13 | GND                 | Ground. Connect to ground plane with minimum inductance.                                                                                                                                                                                                                                                                          |

| A12, B12, C12, D12                                                   | AV <sub>CLK</sub>   | Clock 1.8V Supply Voltage. Accepts a 1.7V to 1.9V supply voltage range. Connect 47nF bypass capacitors between AV <sub>CLK</sub> and GND.                                                                                                                                                                                         |

| B1                                                                   | CREF                | Noise Bypass Pin. A 1 $\mu$ F capacitor between the CREF and DACREF band limits the phase noise of the MAX19692.                                                                                                                                                                                                                  |

| B2                                                                   | REFRES              | Calibration Reference Resistor Input. Connect a 500 $\Omega$ resistor between REFRES and AV <sub>DD3.3</sub> . The internal analog output resistors are calibrated to this external resistor.                                                                                                                                     |

| B3                                                                   | RZ                  | Return-to-Zero (RZ) Mode-Select Input.<br>RZ = 0 (and RF = 0): Normal DAC (NRZ) operation (default).<br>RZ = 1 (and RF = 0): Return-to-zero (RZ) DAC operation.<br>RZ is a 3.3V CMOS logic input with an internal pulldown resistor.                                                                                              |

| B4                                                                   | RF                  | Radio Frequency (RF) Mode-Select Input.<br>RF = 0: NRZ or RZ DAC operation.<br>RF = 1 (and RZ = 0): RF DAC operation.<br>RF is a 3.3V CMOS logic input with internal pulldown resistor.                                                                                                                                           |

| C13                                                                  | CLKP                | LVDS-Compatible Converter Clock Input. There is an internal $100\Omega$ termination resistor between CLKP and CLKN.                                                                                                                                                                                                               |

| B13                                                                  | CLKN                | LVDS-Compatible Converter Clock Input. There is an internal $100\Omega$ termination resistor between CLKP and CLKN.                                                                                                                                                                                                               |

| C1                                                                   | CAL                 | DAC Output Resistance Calibration Input.<br>Calibration of the internal output resistors is initiated by a rising edge on CAL.<br>CAL = 1: Output resistors are calibrated.<br>CAL = 0: Output resistors are uncalibrated.<br>CAL is a 3.3V CMOS input with an internal pulldown resistor. Leakage current is less<br>than ±15µA. |

## **Pin Description (continued)**

| PIN                                          | NAME       | FUNCTION                                                                                                                                                                                                                                           |

|----------------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F6–F3, F1, F2, H6–H1                         | DAP11-DAP0 | Positive Terminals of A-Channel LVDS Data Inputs. DAP11 is MSB.<br>Offset binary format.                                                                                                                                                           |

| G6–G3, G1, G2, J6–J1                         | DAN11-DAN0 | Negative Terminals of A-Channel LVDS Data Inputs                                                                                                                                                                                                   |

| K1–K4, M1–M4, K5, M5,<br>K6, M6              | DBP11-DBP0 | Positive Terminals of B-Channel LVDS Data Inputs. DBP11 is MSB.<br>Offset binary format.                                                                                                                                                           |

| L1–L4, N1–N4, L5, N5, L6, N6                 | DBN11-DBN0 | Negative Terminals of B-Channel LVDS Data Inputs                                                                                                                                                                                                   |

| M7, K7, M8, K8, M9–M12,<br>K9, K10, K11, L12 | DCP11-DCP0 | Positive Terminals of C-Channel LVDS Data Inputs. DCP11 is MSB.<br>Offset binary format.                                                                                                                                                           |

| N7, L7, N8, L8, N9–N12,<br>L9, L10, L11, K12 | DCN11-DCN0 | Negative Terminals of C-Channel LVDS Data Inputs                                                                                                                                                                                                   |

| G7, J7, J12–J8, G12–G8                       | DDP11-DDP0 | Positive Terminals of D-Channel LVDS Data Inputs. DDP11 is MSB.<br>Offset binary format.                                                                                                                                                           |

| F7, H7, H12–H8, F12–F8                       | DDN11-DDN0 | Negative Terminals of D-Channel LVDS Data Inputs                                                                                                                                                                                                   |

| J13                                          | DATACLKP   | Positive Terminal of LVDS Data Output Clock                                                                                                                                                                                                        |

| H13                                          | DATACLKN   | Negative Terminal of LVDS Data Output Clock                                                                                                                                                                                                        |

| K13                                          | DELAY      | Data Clock Delay Mode Input.<br>Adjusts the delay of the output data clock.<br>DELAY = 0: No delay added.<br>DELAY = 1: Add delay of 1/2 input data period (2 DAC clock cycles).<br>DELAY is a 3.3V CMOS input with an internal pulldown resistor. |

| L13                                          | CLKDIV     | Data Clock Divide Mode Input.<br>CLKDIV = 1: Data clock rate = input data rate / 2 ( $f_{CLK}$ / 8).<br>CLKDIV = 0: Data clock rate = input data rate / 4 ( $f_{CLK}$ / 16).<br>CLKDIV is a 3.3V CMOS input with an internal pulldown resistor.    |

| N13                                          | N.C.       | No Connection. This pin should be left unconnected.                                                                                                                                                                                                |

### **Detailed Description**

The MAX19692 is a high-performance, high-speed, 12-bit current-steering DAC with an integrated  $50\Omega$  differential output termination. The DAC is capable of operating with clock speeds up to 2.3GHz. The converter consists of an edge-triggered 4:1 input data multiplexer followed by a current-steering circuit. This circuit is capable of generating differential full-scale currents in the 8mA to 20mA range. Internal  $25\Omega$  resistors on each output, in combination with an external termination, convert the differential current into a voltage. The internal resistors are terminated to the 3.3V analog supply, AVDD3.3. The internal termination resistors can be calibrated to an external  $500\Omega$ precision resistor. A calibration cycle can be run every time the converter is powered up, or at any other time. An integrated 1.2V-bandgap reference, control amplifier, and user-selectable external resistor determine the data converter's full-scale range. The converter features selectable frequency response to allow application-dependent optimization of output power and gain flatness. Three responses can be selected: non-return-to-zero (NRZ), return-to-zero (RZ), or radio frequency (RF).

#### **Reference Input/Output**

The MAX19692 supports operation with the on-chip 1.2Vbandgap reference or an external reference voltage source. REFIO serves as the input for an external, lowimpedance reference source, and as the output if the DAC is operating with the internal reference. For stable operation with the internal reference, REFIO should be decoupled to DACREF with a 1µF capacitor. REFIO must be buffered with an external amplifier if heavier loading is required, due to its 10k $\Omega$  series resistance.

The MAX19692's reference circuit (Figure 1) employs a control amplifier, designed to regulate the full-scale current  $I_{OUT}$  for the differential current outputs of the DAC. The output current can be calculated as follows:

#### IOUT = 32 x IREF x 4095/4096

where IREF is the reference output current (IREF = VREFIO / RSET) and IOUT is the full-scale output current of the DAC. Located between FSADJ and DACREF, RSET is typically set to  $2k\Omega$ , which results in a full-scale current of 20mA if the internal reference is used.

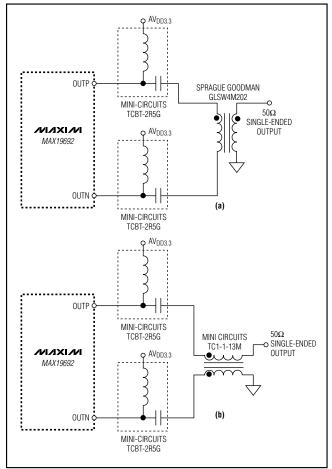

#### **Analog Outputs**

The MAX19692 is a differential current-steering DAC with built-in self-calibrated output termination resistors to optimize performance. The outputs are terminated to AV<sub>DD3.3</sub>, and are calibrated to provide a 50 $\Omega$  differential output resistance. In addition to the signal current, a constant 10mA current sink is connected to each DAC output. Typically, the outputs should be used with a

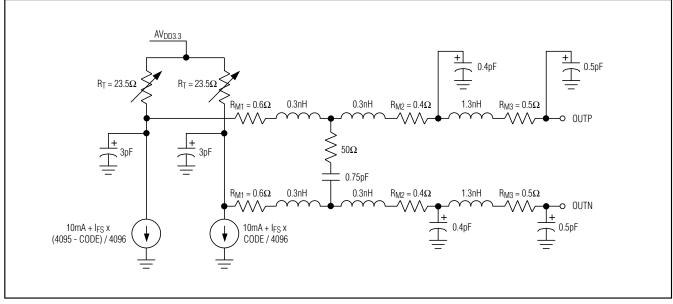

Figure 1. Reference Architecture, Internal Reference Configuration

$50\Omega$  transformer. If the transformer is center tapped, it is recommended that the center tap be connected to AV<sub>DD3.3</sub>. If the transformer is not center tapped, bias tees or RF chokes can be used to pull up the outputs. Figure 2 shows an equivalent circuit of the internal output structure of the MAX19692.

The termination resistors, R<sub>T</sub>, are calibrated to 23.5 $\Omega$ . R<sub>M</sub> = R<sub>M1</sub> + R<sub>M2</sub> + R<sub>M3</sub> is resistance associated with the DAC output traces and bond wires, and is not calibrated. The output resistance is equal to 2R<sub>T</sub> + 2R<sub>M</sub>, and is nominally 50 $\Omega$ . The MAX19692 is normally used with an external differential 50 $\Omega$  load, R<sub>L</sub>. For this case, the peak differential output voltage is calculated as:

$$V_{OUT} = I_{OUT} \times \frac{R_L R_T}{R_L + 2R_M + 2R_T}$$

where I<sub>OUT</sub> is the full-scale current, which is typically set to 20mA. With R<sub>L</sub> = 50 $\Omega$ , R<sub>T</sub> = 23.5 $\Omega$ , and R<sub>M</sub> = 1.5 $\Omega$ , V<sub>OUT</sub> = 0.235V is found. This corresponds to an output power of -2.6dBm. As shown in Figure 2, the output circuit has some resistive, capacitive, and inductive elements. These elements limit the output bandwidth to 2GHz with a resistive differential 50 $\Omega$  load.

#### **Output Resistor Calibration**

The integrated termination resistors, R<sub>T</sub>, must be calibrated to have an accurately known DAC output resistance and an accurately known DAC output voltage.

Figure 2. Equivalent Output Circuit

The termination resistors are calibrated to the external reference resistor, RREFRES, which should be connected between REFRES (pin B2) and AVDD3.3. RREFRES is nominally 500 $\Omega$ . A plot showing the typical relation between the DAC output resistance and RREFRES is shown in Figure 3.

The calibration cycle is initiated with a rising edge on the CAL pin. The CAL pin must be asserted after the supply voltages and the reference voltage have reached steady state. Input data should not be switching while calibration is running. The duration of the calibration cycle is shorter than 65,536 DAC clock cycles—which is less than 65.6µs if the converter is operated with a 1GHz clock rate. The CAL pin must be held high for the output resistors to remain calibrated. If the clock is stopped, or if power is cycled, a new calibration cycle must be run.

Figure 3. Output Resistance vs. REFRES Resistor

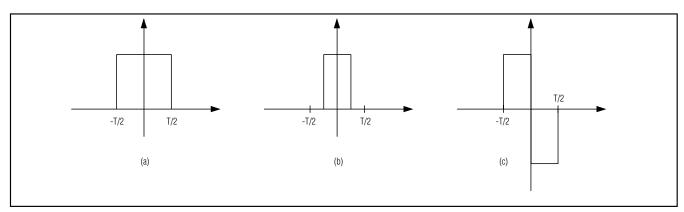

The MAX19692 has three impulse/frequency response modes. These are set with the RZ and RF input pins as described in Table 1.

The impulse responses of the three operating modes are shown in Figure 4. The sample period is equal to T. The default operating mode of the MAX19692 is NRZ mode. The sinc (sine(x)/x) response has zeros at every multiple of the DAC update frequency  $f_{CLK} = 1/T$ . Using this impulse response, the frequency response of the DAC has the familiar sinc shape:

$$A_{NRZ} = A_0 \left[ \frac{\sin(\pi f_{OUT}T)}{\pi f_{OUT}T} \right]$$

where  $f_{OUT}$  is the DAC output frequency, T =  $1/f_{CLK}$  is the period of the DAC clock, and A<sub>0</sub> is the peak low-frequency output amplitude.

In RZ mode, the DAC output has a 50% duty cycle. The DAC output stays at midscale for the remaining 50% of the clock cycle. The resulting frequency response is:

| A   | _ A <sub>0</sub> | $sin(\pi f_{OUT}T / 2)$ |

|-----|------------------|-------------------------|

| ΛRZ | 2                | πf <sub>OUT</sub> T / 2 |

| RZ | RF | FREQUENCY RESPONSE MODE |

|----|----|-------------------------|

| 0  | 0  | NRZ                     |

| 1  | 0  | RZ                      |

| 0  | 1  | RF                      |

| 1  | 1  | Do not use              |

Figure 4. Impulse Responses in (a) NRZ Mode, (b) RZ Mode, and (c) RF Mode

M/IXI/M

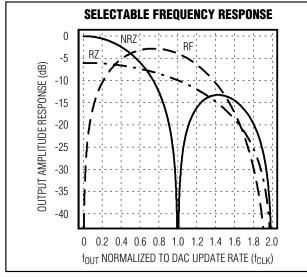

Figure 5. Amplitude Responses for NRZ Mode (Solid Line), RZ Mode (Dash-Dot Line), and RF Mode (Dashed Line). Excludes output bandwidth limitation.

This frequency response is flatter than the NRZ response in the three first Nyquist zones, particularly in the 2nd and 3rd Nyquist zones—making this DAC usable for outputting wideband signals in the 2nd and 3rd Nyquist zones.

The third mode of operation is the RF mode. In this mode, the DAC output response is inverted in the second half of the clock cycle, resulting in a doublet pulse at the output of the DAC in every clock cycle. The resulting DAC frequency response is:

$$A_{RF} = A_0 \left[ \frac{\sin(\pi f_{OUT} T / 2)}{\pi f_{OUT} T / 2} \times \sin(\pi f_{OUT} T / 2) \right]$$

The RF mode increases the DAC output power in the second and third Nyquist zones and attenuates it in the first Nyquist zone.

The frequency responses for the three modes of operation are plotted in Figure 5.

NRZ mode provides the highest power in the first Nyquist zone. RZ mode provides the flattest frequency response in the first and third Nyquist zones, and RF mode provides superior output power in the second and third Nyquist zones, as well as the flattest gain in the second Nyquist zone.

Figure 6. Recommended Clock Amplitude

#### **Clock Inputs**

**MAX19692**

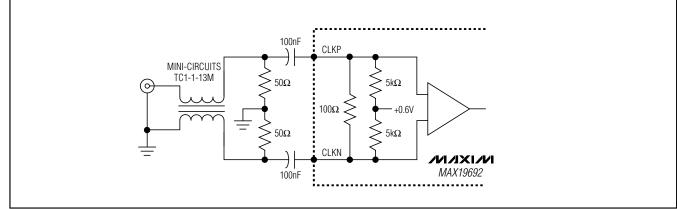

The MAX19692 features a flexible differential clock input (CLKP, CLKN) operating from a separate supply (AV<sub>CLK</sub>) to achieve the best possible jitter performance. The two clock inputs can be driven from a single-ended or a differential clock source. A sine wave or a square wave can be used. For single-ended operation, CLKP should be driven by a logic source, while CLKN should be bypassed to GND with a  $0.1\mu$ F capacitor.

Driving the clocks differentially is recommended for optimum jitter performance. Choose a clock amplitude that is as large as possible (without the clock voltage at the CLKN and CLKP pins going more than 200mV below ground or above the AV<sub>CLK</sub> supply voltage) to minimize jitter. This results in the most accurate duty cycle—and hence the most accurate gain in RZ and RF modes. For an AC-coupled, differential sine-wave clock, the clock amplitude should not be higher than 2.5V peak-to-peak (12dBm if terminated in 50 $\Omega$ ). The typical performance plots in this data sheet have generally been measured using a 10dBm (2VP-P) clock amplitude.

The MAX19692 can be used with a sinusoidal clock amplitude as low as 0.6VP-P below 1.5Gsps. For higher update rates, the clock amplitude should stay within the operating region specified in Figure 6.

The CLKP and CLKN pins are internally biased to 0.6V with resistors. This allows the user to AC-couple clock sources directly to the device without external resistors to define the DC level.

### M/IXI/M

Figure 7. Typical Clock Application Circuit

MAX19692

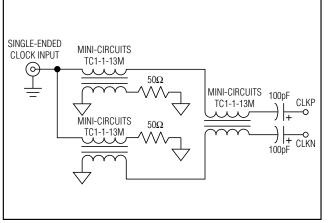

Figure 8. Clock Application Circuit with Improved Symmetry

The MAX19692 has an internal 100 $\Omega$  termination resistor between CLKP and CLKN. An extra 100 $\Omega$  differential termination resistor should be added if using a 50 $\Omega$  clock source. See Figure 7 for a convenient and quick way to apply a differential signal created from a single-ended source and a wideband transformer.

The clock circuit in Figure 7 has some amplitude asymmetry at update rates above 1Gsps, due to transformer loss. This may cause performance degradation for some operating conditions. A clock interface circuit with improved symmetry using three balun transformers is shown in Figure 8. This clock interface circuit provides symmetric and balanced clock signals for frequencies up to the maximum update rate of the MAX19692.

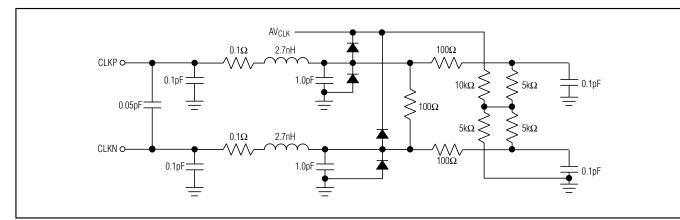

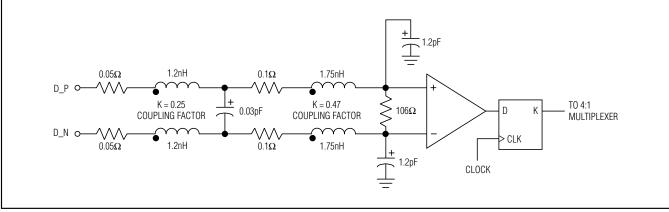

An equivalent circuit model for the clock inputs is shown in Figure 9.

#### **Clock Duty Cycle**

The duty cycle of the converter clock should be close to 50%. If an AC-coupled sine-wave clock is used, the clock duty cycle is automatically close to 50%. If a square-wave clock is used, this is not necessarily the case.

Keeping the clock duty cycle close to 50% is particularly important when operating in RZ and RF modes.

When operating in RZ mode, clock duty-cycle deviation from 50% distorts the converter's frequency response. A clock duty cycle above 50% increases the converter's output power at low frequencies, and lowers the frequency of the zero in the frequency response function—effectively producing a frequency response between that of NRZ and RZ modes.

When operating in RF mode, a clock duty cycle higher or lower than 50% increases the output amplitude at low frequencies in the first Nyquist zone and slightly lowers the output amplitude in the second and third Nyquist zones.

#### **Data Inputs**

Data inputs (DAP[11:0], DAN[11:0], DBP[11:0], DBN[11:0], DCP[11:0], DCN[11:0], DDP[11:0], DDN[11:0]) have LVDS receivers followed by edgetriggered flip flops. Four 12-bit buses accept data in offset binary format. The LVDS inputs feature on-chip termination with differential  $100\Omega$  resistors. A 1.25V common-mode level with a ±400mV differential swing can be applied to these inputs. See Figure 10 for an equivalent circuit of the LVDS inputs.

Figure 9. Clock Input Equivalent Circuit

Figure 10. LVDS Input Equivalent Circuit

#### **Data-Timing Relationships**

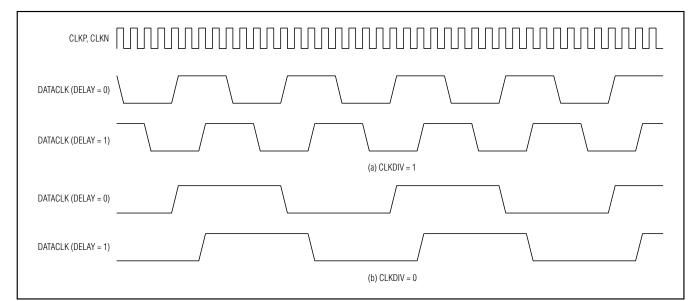

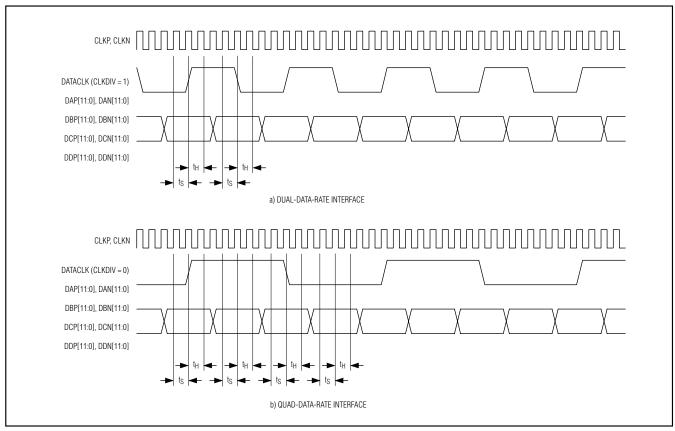

The timing of the LVDS inputs is defined with respect to the LVDS output DATACLK (DATACLKP - DATACLKN). The LVDS data inputs are latched at 1/4 the input clock frequency. The DATACLK output frequency is divided by another factor of 4 (CLKDIV = 0) or by 2 (CLKDIV = 1).

Define the 0° point of DATACLK as the rising edge.

For the case of CLKDIV = 1, data are latched at 0° and 180° of DATACLK, and setup and hold times must be satisfied for both these points in time.

For the case of CLKDIV = 0, data are latched at  $0^{\circ}$ ,  $90^{\circ}$ ,  $180^{\circ}$ , and  $270^{\circ}$  of DATACLK. Setup and hold times must be satisfied for all four of these points in time.

A delay set by the DELAY pin can skew DATACLK by 1/2 period of the input data period, as shown in Figure 11. This eases interfacing to an FPGA where the clock to Q delay of the LVDS outputs is not adjustable. The clock driving the data input register is not delayed with the DELAY pin. The setup and hold times are always referred to the case when DELAY = 0. Data-timing relationships are shown in Figure 12.

Figure 11. Effect of Setting DELAY = 1 on Data Clock Output

Figure 12. Setup (t<sub>S</sub>) and Hold Time (t<sub>H</sub>) for Data Input Interface

M/IXI/M

Figure 13. Possible Output Circuits for MAX19692

### \_Applications Information

#### Differential Coupling Using RF Transformers

The differential voltage existing between OUTP and OUTN can be converted to a single-ended voltage using a transformer or a differential amplifier configuration. Using a differential transformer-coupled output, in which the output power is limited to -2.6dBm, can optimize the dynamic performance. It is recommended that the DAC outputs are pulled up to 3.3V. The use of bias tees, as shown in Figure 13, is recommended for optimal performance. RF chokes can be used rather than bias tees if an isolation transformer is used. Not pulling up the outputs to 3.3V is also possible, but may result in some degradation of dynamic performance in some applications. Two output circuits are shown in Figure 13. The circuit shown in Figure 13(a) has less than 3dB loss (in addition to the sinc attenuation built into the DAC) from approximately

Figure 14. Data Source to DAC Interfacing

4MHz to 700MHz. The circuit shown in Figure 13(b)—that is used on the MAX19692 evaluation kit—has less than 3dB loss at frequencies up to approximately 1150MHz. To achieve the maximum bandwidth, it is important to minimize the inductance in the ground lead on the secondary side of the transformers. It is recommended to use a very short trace and multiple vias for the connection to the ground plane.

#### **Data Synchronization**

The DAC clock is running at four times the data rate of the data interface to the MAX19692. An LVDS level data clock output (DATACLKP, DATACLKN) is provided to help the user synchronize the data source and the DAC. The output data clock frequency can be set to 1/2 the input data rate or 1/4 the input data rate. When the DAC is running at full speed, this allows the data clock to be interfaced directly to FPGAs without using an external clock divider. For example, if the DAC is updating at 2.3Gsps, the input data rate is 575Mwps. If the DAC is interfaced to an FPGA, one could run the data clock at 1/4 the data input rate; hence the data output clock frequency would be 143.75MHz.

**MAX19692**

If the system clock is running at the DAC update rate, the scheme in Figure 14(a) can be used. In this case, the system is clocked using the data clock output from the DAC. The delays of the data and the clock depend upon line lengths and loading. Hence, clock deskewing using a phase-locked loop may be necessary to make this system work properly at speed. When CLKDIV = 0, the data clock output can be phase-shifted by 45° using the DELAY pin. When CLKDIV = 1, the data clock output can be phase-shifted by 90° using the DELAY pin.

An alternative solution is shown in Figure 14(b). In this case, the system clock distribution is running at the data clock rate. A low-jitter, low-phase-noise phase-locked loop is used to generate the high-speed DAC clock. Using the data clock for feedback into the PLL ensures synchronization between data and clock.

If more than one MAX19692 is used in a system, and the relative phases need to be defined, the divided data clock of each DAC should be phase locked to a system clock running at data-rate / 4 or data-rate / 2, which is equal to the input clock rate divided by 8 or 16.

#### Grounding, Bypassing, Power-Supply, and Board Layout Considerations

Grounding and power-supply decoupling can strongly influence the performance of the MAX19692. Unwanted digital crosstalk may couple through the input, reference, power supply, and ground connections, affecting dynamic performance. Proper grounding and powersupply decoupling guidelines for high-speed, high-frequency applications should be closely followed. This reduces EMI and internal crosstalk that can significantly affect the dynamic performance of the MAX19692.

Use of a multilayer PC board with separate ground and power-supply planes is required. It is recommended that the analog output and the clock input are run as controlled-impedance microstrip lines on the top layer of the board, directly above a ground plane, and that no vias are used for the clock input (CLKP, CLKN) and the analog output (OUTP, OUTN) signals. Depending on the length of the traces, and the operating condition, a low-loss dielectric material (such as ROGERS RO4003) as the top layer dielectric may be advisable. The data clock (DATACLKP, DATACLKN) must be routed so its coupling into the clock input and the DAC output is minimized.

Digital input signals should be run as controlled-impedance strip lines between ground planes. Digital signals should be kept as far away from sensitive analog inputs, reference input sense lines, common-mode inputs, and clock inputs as practical. It is particularly important to minimize coupling between digital signals and the clock to optimize dynamic performance for high output frequencies. A symmetric design of the clock input and analog output lines is critical to minimize distortion and optimize the DAC's dynamic performance.

Digital signal paths should be kept short and run lengths matched to avoid propagation delay and dataskew mismatches.

The MAX19692 supports three separate power-supply inputs for analog 3.3V (AV<sub>DD3.3</sub>), switching (V<sub>DD1.8</sub>), and clock (AV<sub>CLK</sub>) circuits. Each AV<sub>DD3.3</sub>, V<sub>DD1.8</sub>, and AV<sub>CLK</sub> input should at least be decoupled with a separate 47nF capacitor as close to the pin as possible and their opposite ends with the shortest possible connection to the corresponding ground plane, to minimize loop inductance. All three power-supply voltages should also be decoupled at the point they enter the PC board with tantalum or electrolytic capacitors. Ferrite beads with additional decoupling capacitors forming a pi-network could also improve performance.

The power-supply inputs V<sub>DD1.8</sub> and AV<sub>CLK</sub> of the MAX19692 allow a 1.8V  $\pm$ 0.1V supply voltage range for update rates < 2.0Gsps. A range of 1.8V to 1.9V should be used for 2.0Gsps to 2.3Gsps. The analog power-supply input AV<sub>DD3.3</sub> allows a 3.3V  $\pm$ 0.2V supply voltage range. To optimize the dynamic performance of the MAX19692 over temperature at the highest update rates, it is important that the difference between V<sub>DD1.8</sub> and AV<sub>DD3.3</sub> is at least 1.4V. If V<sub>DD1.8</sub> is 1.9V and AV<sub>DD3.3</sub> is 3.1V, dynamic performance at these update rates will degrade at higher temperatures, as shown in the *Typical Operating Characteristics*.

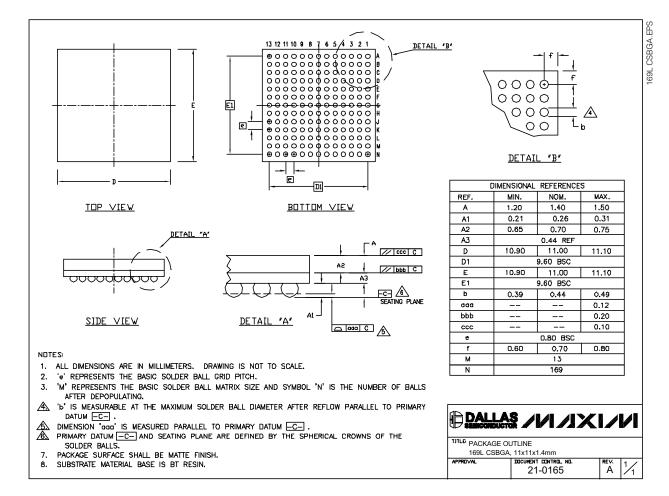

The MAX19692 is packaged in a 169 CSBGA package with 0.8mm ball pitch (package code: X16911-1), providing design flexibility, thermal efficiency, and a small footprint for the DAC.

### Static Performance Parameter Definitions

#### Integral Nonlinearity (INL)

Integral nonlinearity is the deviation of the values on an actual transfer function from either a best straight-line fit (closest approximation to the actual transfer curve) or end-point fit (a line drawn between the end points of the transfer function, once offset and gain errors have been nullified). For a DAC, the deviations are measured at every individual step. The MAX19692 INL is specified using the end-point method.

#### **Differential Nonlinearity (DNL)**

Differential nonlinearity is the difference between an actual step height and the ideal value of 1 LSB. A DNL error specification greater than -1 LSB guarantees a monotonic transfer function.

#### **Offset Error**

The offset error is the difference between the ideal and the actual offset current. For a DAC, the offset point is the average value at the output for the two midscale digital input codes with respect to the full scale of the DAC. This error affects all codes by the same amount.

#### **Gain Error**

A gain error is the difference between the ideal and the actual full-scale output voltage on the transfer curve, after nullifying the offset error. This error alters the slope of the transfer function and corresponds to the same percentage error in each step.

### **Dynamic Performance Parameter Definitions**

#### Settling Time

The settling time is the amount of time required from the start of a transition until the DAC output settles its new output value to within the specified accuracy.

#### **Noise Spectral Density**

The DAC output noise is the sum of the quantization noise and other noise sources. Noise spectral density is the noise power in a 1Hz bandwidth.

#### Spurious-Free Dynamic Range (SFDR)

SFDR is the ratio of the RMS amplitude of the carrier frequency (maximum signal components) to the RMS value of the largest distortion component. SFDR is usually measured in dBc with respect to the carrier frequency amplitude or in dBFS with respect to the DAC's full-scale range. Depending on its test condition, SFDR is observed within a predefined window or to Nyquist.

#### Two-/Four-Tone Intermodulation Distortion (IMD)

The two-/four-tone IMD is the ratio expressed in dBc (or dBFS) of the worst 3rd-order (or higher) IMD products to any output tone.

Pin Configuration

| P VIEW | MAX19692                                         |                    |                    |                     |                     |                |                     |                 |                     |                        |                             |                             |                             |

|--------|--------------------------------------------------|--------------------|--------------------|---------------------|---------------------|----------------|---------------------|-----------------|---------------------|------------------------|-----------------------------|-----------------------------|-----------------------------|

| -      | 1                                                | 2                  | 3                  | 4                   | 5                   | 6              | 7                   | 8               | 9                   | 10                     | 11                          | 12                          | 13                          |

| A      | REFIO                                            | FSADJ              | DACREF             | AV <sub>DD3.3</sub> | AV <sub>DD3.3</sub> | OUTP           | AV <sub>DD3.3</sub> | OUTN            | AV <sub>DD3.3</sub> | V <sub>DD1.8</sub>     | GND<br>(A11)                | AV <sub>CLK</sub>           | GND<br>(A13)                |

| В      | CREF                                             | REFRES             | RZ<br>(B3)         | RF<br>(B4)          | GND<br>(B5)         | GND<br>(B6)    | GND                 | GND<br>(B8)     | GND<br>(B9)         | V <sub>DD1.8</sub>     | GND<br>(B11)                | AV <sub>CLK</sub>           | CLKN<br>(B13)               |

| С      | CAL<br>(01)                                      | V <sub>DD1.8</sub> | V <sub>DD1.8</sub> | GND                 | GND<br>(C5)         | GND<br>(C6)    | GND<br>((C7))       | GND<br>( ( C8 ) | GND<br>(C9)         | V <sub>DD1.8</sub>     | GND<br>(011)                | AV <sub>CLK</sub>           | CLKP<br>(013)               |

| D      | GND<br>(D1)                                      | GND                | GND<br>(D3)        | GND<br>(D4)         | GND<br>(D5)         | GND<br>(D6)    | GND                 | GND<br>(D8)     | GND<br>(D9)         | GND<br>(D10)           | GND<br>(D11)                | AV <sub>CLK</sub>           | GND<br>(D13)                |

| E      | V <sub>DD1.8</sub>                               | V <sub>DD1.8</sub> | V <sub>DD1.8</sub> | V <sub>DD1.8</sub>  | GND<br>(E5)         | GND<br>(E6)    | GND                 | GND<br>(E8)     | GND<br>(E9)         | V <sub>DD1.8</sub>     | V <sub>DD1.8</sub><br>(E11) | V <sub>DD1.8</sub><br>(E12) | V <sub>DD1.8</sub><br>(E13) |

| F      | DAP7                                             | DAP6               | DAP8               | DAP9                | DAP10               | DAP11<br>(F6)  | DDN11<br>(F7)       | DDNO            | DDN1                | DDN2<br>(F10)          | DDN3<br>(F11)               | DDN4<br>(F12)               | V <sub>DD1.8</sub><br>(F13) |

| G      | DAN7<br>(G1)                                     | DAN6               | DAN8<br>( G3 )     | DAN9                | DAN10<br>(G5)       | DAN11<br>()    | DDP11<br>(G7)       | DDP0<br>( 68 )  | DDP1<br>(G9)        | DDP2<br>(G10)          | DDP3<br>(G11)               | DDP4<br>(G12)               | <u>GND</u><br>(G13)         |

| н      | DAPO                                             | DAP1               | DAP2               | DAP3                | DAP4                | DAP5           | DDN10               | DDN5<br>( H8 )  | DDN6                | DDN7<br>(H10)          | DDN8<br>(H11)               | DDN9<br>(H12)               | DATACLKN                    |

| J      | $\left( \begin{array}{c} J1 \end{array} \right)$ | DAN1               | DAN2               | DAN3                | DAN4                | DAN5           | DDP10<br>(J7)       | DDP5<br>()      | DDP6<br>(_J9_)      | DDP7<br>(J10)          | DDP8<br>(J11)               | DDP9<br>(J12)               | DATACLKP                    |

| к      | DBP11<br>(K1)                                    | DBP10<br>(K2)      | DBP9<br>(K3)       | DBP8                | DBP3                | DBP1           | DCP10<br>(K7)       | DCP8<br>( K8 )  | DCP3                | DCP2<br>(K10)          | DCP1<br>(K11)               | DCN0<br>(K12)               | DELAY                       |

| L      | DBN11<br>(L1)                                    | DBN10              | DBN9               | DBN8<br>(_L4_)      | DBN3                | DBN1<br>(_L6_) | DCN10               | DCN8<br>((L8))  | DCN3                | D <u>CN</u> 2<br>(110) | D <u>C</u> N1<br>(L11)      | DCP0<br>(L12)               | CLKQIV                      |

| М      | DBP7                                             | DBP6               | DBP5               | DBP4                | DBP2                | DBP0           | DCP11<br>(M7)       | DCP9<br>(M8)    | DCP7                | DCP6                   | DCP5<br>(M11)               | DCP4<br>(M12)               | GND<br>(M13)                |

| N      | DBN7                                             | DBN6               | DBN5               | DBN4                | DBN2                | DBN0           | DCN11<br>(N7)       | DCN9<br>(N8)    | DCN7                | DCN6<br>(N10)          | DCN5<br>(N11)               | DCN4<br>(N12)               | N.C.<br>(N13)               |

The MAX19692 is packaged in an 11mm x 11mm, 169 CSBGA package (package code X16911-1). Ball pitch is 0.8mm.

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to **www.maxim-ic.com/packages**.)

MAX19692

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

#### Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_

**MAXIM** is a registered trademark of Maxim Integrated Products, Inc.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated: MAX19692EXW+D MAX19692EXW-D