**Features**

## Low-Cost, Multichemistry Battery-**Charger Building Block**

### **General Description**

The MAX1772 is a highly-integrated, multichemistry battery-charger control IC that simplifies the construction of accurate and efficient chargers. The MAX1772 uses analog inputs to control charge current and voltage and can be programmed by the host or hardwired. High efficiency is achieved by a buck topology with synchronous rectification.

Maximum current drawn from the AC adapter is programmable to avoid overloading the AC adapter when supplying the load and the battery charger simultaneously. This enables the user to reduce the cost of the AC adapter. The MAX1772 provides outputs that can be used to monitor the current drawn from the AC adapter, battery-charging current, and the presence of an AC adapter.

The MAX1772 can charge two to four lithium-ion (Li+) series cells, easily providing 4A. When charging, the MAX1772 automatically transitions from regulating current to regulating voltage. It is available in a space-saving 28-pin QSOP package.

### **Applications**

Notebook and Subnotebook Computers Personal Digital Assistants Handheld Terminals

## **♦ Input Current Limiting**

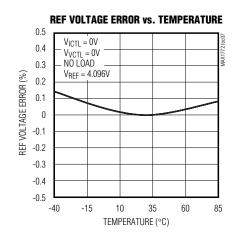

- ♦ ±0.5% Output Voltage Accuracy Using Internal Reference (0°C to +85°C)

- ♦ Programmable Battery Charge Current >4A

- ♦ Analog Inputs Control Charge Current and **Charge Voltage**

- **♦** Monitor Outputs for: **Current Drawn from AC Input Source Charging Current AC Adapter Present**

- ◆ Up to 18.2V (max) Battery Voltage

- ♦ 8V to 28V Input Voltage

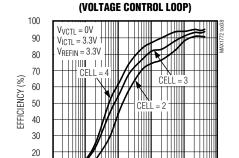

- ♦ > 95% Efficiency

- ♦ 99.99% (max) Duty Cycle for Low-Dropout Operation

- ♦ Charges Any Battery Chemistry: Li+, NiCd, NiMH, Lead Acid, etc.

### Pin Configuration

#### TOP VIEW DCIN IINP 27 CSSP LDO 2 CLS 26 CSSN REF 4 BST NAXIM CCS 5 DHI MAX1772 CCI 6 23 LX CCV 7 DLOV GND 8 21 DL0 PGND GND 9 19 ICHG 10 CSIP ACIN 18 CSIN 17 ACOK 12 BATT REFIN 13 16 CELLS ICTL 14 15 VCTL **QSOP**

### **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE |

|-------------|----------------|-------------|

| MAX1772EEI  | -40°C to +85°C | 28 QSOP     |

| MAX1772EEI+ | -40°C to +85°C | 28 QSOP     |

+Denotes lead(Pb)-free/RoHS-compliant package.

MIXIM

#### **ABSOLUTE MAXIMUM RATINGS**

| DCIN, CSSP, CSSN to GNDBST to GND                                                  | 0.3V to +36V                      |

|------------------------------------------------------------------------------------|-----------------------------------|

| BST to LXDHI to LX                                                                 |                                   |

| LX to GND                                                                          | ,                                 |

| BATT, CSIP, CSIN to GND                                                            | 0.3V to 20V                       |

| CSIP to CSIN or CSSP to CSSN or PGND to GND                                        | 0.3V to +0.3V                     |

| CCI, CCS, CCV, DLO, ICHG, IINP,<br>ACIN, REF to GNDDLOV. VCTL. ICTL. REFIN. CELLS. | 0.3V to (V <sub>LDO</sub> + 0.3V) |

| CLS, LDO, ACOK to GNDDLOV to LDO                                                   |                                   |

|                                | 0.3V to (V <sub>DLOV</sub> + 0.3V) |

|--------------------------------|------------------------------------|

| LDO Short-Circuit Current      | 50mA                               |

| Continuous Power Dissipation ( | $T_A = +70^{\circ}C$               |

| 28-Pin QSOP (derate 12.6mV     | V/°C above +70°C)1008mW            |

| Junction-to-Ambient Thermal Re | esistance (θJA)                    |

| (Note 1)                       | 79.3°C/W                           |

| Junction-to-Case Thermal Resis | stance ( 0JC)                      |

| (Note 1)                       | 27°C/W                             |

|                                | 40°C to +85°C                      |

| Junction Temperature           | 150°C                              |

| Storage Temperature Range      | 60°C to +150°C                     |

|                                | 0s)+300°C                          |

| , , ,                          | ,                                  |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to **www.maxim-ic.com/thermal-tutorial**.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DCIN} = V_{CSSP} = V_{CSSN} = 18V, \ V_{BATT} = V_{CSIP} = V_{CSIN} = 12V, \ V_{REFIN} = 3.0V, \ V_{VCTL} = V_{ICTL} = 0.75 \times V_{REFIN}, \ V_{CELLS} = 2.0V, \ V_{ACIN} = 0V, \ CLS = REF, \ V_{BST} - V_{LX} = 4.5V, \ V_{GND} = V_{PGND} = 0V, \ C_{LDO} = 1\mu F, \ LDO = DLOV, \ C_{REF} = 1\mu F; \ pins \ CCI, \ CCS, \ and \ CCV \ are compensated per Figure 1a; \ \textbf{T_A} = 0^{\circ}\textbf{C} \ \textbf{to} + \textbf{85}^{\circ}\textbf{C}, \ unless \ otherwise \ noted. \ Typical \ values \ are \ at \ T_{A} = +25^{\circ}C.)$

| PARAMETER                              | SYMBOL                   | CONDITIONS                              | MIN   | TYP   | MAX   | UNITS |

|----------------------------------------|--------------------------|-----------------------------------------|-------|-------|-------|-------|

| SUPPLY AND LDO REGULATO                | SUPPLY AND LDO REGULATOR |                                         |       |       |       |       |

| DCIN Input Voltage Range               | V <sub>DCIN</sub>        |                                         | 8     |       | 28    | V     |

| DCIN Undervoltage Lockout              |                          | V <sub>DCIN</sub> falling               | 7.0   | 7.4   |       | V     |

| Trip Point                             |                          | V <sub>DCIN</sub> rising                |       | 7.5   | 7.85  | V     |

| DCIN Quiescent Current                 | IDCIN                    | 8.0V < V <sub>DCIN</sub> < 28V          |       | 2.7   | 6.0   | mA    |

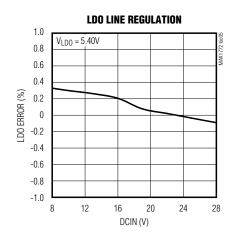

| LDO Output Voltage                     |                          | 8.0V < V <sub>DCIN</sub> < 28V, no load | 5.25  | 5.40  | 5.55  | V     |

| LDO Load Regulation                    |                          | 0 < I <sub>LDO</sub> < 10mA             |       | 34    | 100   | mV    |

| LDO Undervoltage Lockout<br>Trip Point |                          | V <sub>DCIN</sub> = 8.0V                | 3.20  | 4.00  | 5.15  | V     |

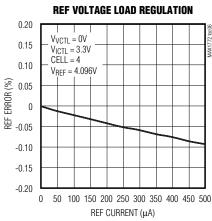

| REF Output Voltage                     |                          | 0 < I <sub>REF</sub> < 500μA            | 4.072 | 4.096 | 4.120 | V     |

| REF Undervoltage Lockout<br>Trip Point |                          | V <sub>REF</sub> falling                |       | 3.1   | 3.9   | V     |

| TRIP POINTS                            |                          |                                         |       |       |       | •     |

| BATT POWER_FAIL Threshold              |                          | V <sub>CSSP</sub> falling               | 50    | 100   | 150   | mV    |

| BATT POWER_FAIL Threshold Hysteresis   |                          |                                         | 100   | 200   | 300   | mV    |

| ACIN Threshold                         |                          | V <sub>ACIN</sub> rising                | 2.007 | 2.048 | 2.089 | V     |

| ACIN Threshold Hysteresis              |                          | 0.5% of V <sub>REF</sub>                | 10    | 20    | 30    | mV    |

| ACIN Input Bias Current                |                          | V <sub>ACIN</sub> = 2.048V              | -1    |       | +1    | μΑ    |

| CLS Input Range                        |                          |                                         | 1.6   |       | REF   | V     |

| CLS Input Bias Current                 |                          | V <sub>CLS</sub> = 2.0V                 | -1    |       | +1    | μΑ    |

| SWITCHING REGULATOR                    |                          |                                         | ·     |       |       |       |

| Minimum Off-Time                       |                          | V <sub>BATT</sub> =16.8V                | 1.00  | 1.25  | 1.50  | μs    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$\begin{array}{l} (V_{DCIN}=V_{CSSP}=V_{CSSN}=18V,\ V_{BATT}=V_{CSIP}=V_{CSIN}=12V,\ V_{REFIN}=3.0V,\ V_{VCTL}=V_{ICTL}=0.75\times V_{REFIN},\ V_{CELLS}=2.0V,\ V_{ACIN}=0V,\ CLS=REF,\ V_{BST}-V_{LX}=4.5V,\ V_{GND}=V_{PGND}=0V,\ C_{LDO}=1\mu F,\ LDO=DLOV,\ C_{REF}=1\mu F;\ pins\ CCI,\ CCS,\ and\ CCV\ are\ compensated\ per\ Figure\ 1a;\ \textbf{T_A}=0^{\circ}\textbf{C}\ to\ +85^{\circ}\textbf{C},\ unless\ otherwise\ noted.\ Typical\ values\ are\ at\ T_{A}=+25^{\circ}\textbf{C}.) \end{array}$

| PARAMETER                                        | SYMBOL            | CONDITIONS                                                                             | MIN           | TYP          | MAX          | UNITS |

|--------------------------------------------------|-------------------|----------------------------------------------------------------------------------------|---------------|--------------|--------------|-------|

| Maximum On-Time                                  |                   |                                                                                        | 5             | 10           | 15           | ms    |

| Oscillator Frequency                             | fosc              | (Note 2)                                                                               |               |              | 400          | kHz   |

| DLOV Supply Current                              | I <sub>DLOV</sub> | DLO low                                                                                |               | 5            | 10           | μΑ    |

| BST Supply Current                               | I <sub>BST</sub>  | DHI high                                                                               |               | 6            | 15           | μΑ    |

| LX Input Bias Current                            | İ                 | V <sub>DCIN</sub> = 28V, V <sub>BATT</sub> = V <sub>LX</sub> = 20V                     |               | 150          | 500          | μΑ    |

| LX Input Quiescent Current                       |                   | V <sub>DCIN</sub> = 0V, V <sub>BATT</sub> = V <sub>LX</sub> = 20V                      |               | 0.3          | 1.0          | μΑ    |

| DHI Maximum Duty Cycle                           |                   |                                                                                        | 99.0          | 99.9         |              | %     |

| DHI On-Resistance High                           |                   | V <sub>BST</sub> - V <sub>LX</sub> = 4.5V, I <sub>DHI</sub> = +100mA                   |               | 4            | 7            | Ω     |

| DHI On-Resistance Low                            |                   | V <sub>BST</sub> - V <sub>LX</sub> = 4.5V, I <sub>DHI</sub> = -100mA                   |               | 1            | 2            | Ω     |

| DLO On-Resistance High                           |                   | $V_{DLOV} = 4.5V$ , $I_{DLO} = +100$ mA                                                |               | 4            | 7            | Ω     |

| DLO On-Resistance Low                            |                   | $V_{DLOV} = 4.5V$ , $I_{DLO} = -100$ mA                                                |               | 1            | 2            | Ω     |

| DATT leavest Occurrent                           | 1                 | VBATT = 19V, VDCIN = 0V                                                                |               |              | 5            | ^     |

| BATT Input Current                               | I <sub>BATT</sub> | V <sub>BATT</sub> = 2V to 19V, V <sub>DCIN</sub> > V <sub>BATT</sub> + 0.3V            |               | 200          | 500          | μΑ    |

| CCID/CCINI Input Current                         |                   | V <sub>DCIN</sub> = 0V                                                                 |               | 1            | 5            |       |

| CSIP/CSIN Input Current                          |                   | V <sub>CSIP</sub> = V <sub>CSIN</sub> = 12V                                            |               |              | 800          | μΑ    |

| CCCD/CCCN Input Current                          |                   | V <sub>DCIN</sub> = 0V                                                                 |               | 0.1          | 0.3          | ^     |

| CSSP/CSSN Input Current                          |                   | VCSSP = VCSSN = VDCIN > 8.0V                                                           |               |              | 800          | μA    |

| BATT/CSIP/CSIN Input Voltage Range               |                   |                                                                                        | 0             |              | 19           | V     |

| CSIP to CSIN Full-Scale<br>Current-Sense Voltage |                   | V <sub>BATT</sub> = 12V                                                                | 189           | 204          | 219          | mV    |

| CSSP to CSSN Full-Scale<br>Current-Sense Voltage |                   |                                                                                        | 189           | 204          | 219          | mV    |

| ERROR AMPLIFIERS                                 | <b>.</b>          |                                                                                        | _ <b>!</b>    |              |              | •     |

| GMV Amplifier<br>Transconductance                |                   | VCTL = REFIN, V <sub>BATT</sub> = 16.8V, CELLS = LDO                                   | 0.0625        | 0.1250       | 0.250        | μS    |

| GMI Amplifier<br>Transconductance                |                   | ICTL = REFIN, V <sub>CSIP</sub> - V <sub>CSIN</sub> = 150.4mV                          | 0.5           | 1            | 2            | μS    |

| GMS Amplifier<br>Transconductance                |                   | V <sub>CLS</sub> = 2.048V, V <sub>CSSP</sub> - V <sub>CSSN</sub> = 102.4mV             | 0.5           | 1            | 2            | μS    |

| CCI/CCS/CCV Clamp Voltage                        |                   | 0.25V < V <sub>CCI</sub> , V <sub>CCS</sub> , V <sub>CCV</sub> < 2.0V                  | 150           | 300          | 600          | mV    |

| CURRENT AND VOLTAGE SET                          | TTING             |                                                                                        | •             |              |              |       |

| Charging Current Assuras:                        |                   | ICTL = REFIN (see Equation 2)                                                          | -8            |              | +8           | 0/    |

| Charging-Current Accuracy                        |                   | ICTL = REFIN/32 (see Equation 2)                                                       | -55           |              | +55          | %     |

| ICTL, VCTL, REFIN Input Bias                     |                   | Vvctl = Victl = Vrefin = 3V                                                            | -1            |              | +1           | μA    |

| Current                                          |                   | V <sub>DCIN</sub> = 0, V <sub>VCTL</sub> = V <sub>ICTL</sub> = V <sub>REFIN</sub> = 5V | -1            |              | +1           |       |

| ICTL Power-Down Mode<br>Threshold Voltage        |                   |                                                                                        | REFIN<br>/100 | REFIN<br>/55 | REFIN<br>/33 | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DCIN} = V_{CSSP} = V_{CSSN} = 18V, V_{BATT} = V_{CSIP} = V_{CSIN} = 12V, V_{REFIN} = 3.0V, V_{VCTL} = V_{ICTL} = 0.75 \times V_{REFIN}, V_{CELLS} = 2.0V, V_{ACIN} = 0V, CLS = REF, V_{BST} - V_{LX} = 4.5V, V_{GND} = V_{PGND} = 0V, C_{LDO} = 1\mu F, LDO = DLOV, C_{REF} = 1\mu F; pins CCI, CCS, and CCV are compensated per Figure 1a; <math>T_A = 0^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                          | SYMBOL | CONDITIONS                                                                                                                                           | MIN                        | TYP  | MAX                       | UNITS |

|------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------|---------------------------|-------|

| Battery-Regulation Voltage         |        | V <sub>VCTL</sub> = V <sub>REFIN</sub> (2, 3, or 4 cells) (see Equation 1)                                                                           | -0.5                       |      | +0.5                      | %     |

| Accuracy                           |        | V <sub>VCTL</sub> = V <sub>REFIN</sub> /20 (2, 3, or 4 cells) (see Equation 1)                                                                       | -0.5                       |      | +0.5                      | /0    |

| REFIN Range                        |        |                                                                                                                                                      | 2.0                        |      | 3.6                       | V     |

| REFIN Undervoltage Lockout         |        |                                                                                                                                                      |                            | 1.20 | 1.92                      | V     |

| ICHG Transconductance              |        | VICHG to (VCSIP - VCSIN); VCSIP -<br>VCSIN = 0.185V; VICHG = 0V, 3.0V                                                                                | 0.95                       | 1.00 | 1.05                      | μS    |

| 10110 4                            |        | V <sub>CSIP</sub> - V <sub>CSIN</sub> = 0.185V                                                                                                       | -5                         |      | +5                        | 0/    |

| ICHG Accuracy                      |        | VCSIP - VCSIN = 0.05V                                                                                                                                | -10                        |      | +10                       | %     |

| IINP Transconductance              |        | V <sub>IINP</sub> to (V <sub>CSSP</sub> - V <sub>CSSN</sub> ); V <sub>CSSP</sub> - V <sub>CSSN</sub> = 0.185V; V <sub>IINP</sub> = 0V, 3.0V (Note 3) | 0.85                       | 1.00 | 1.15                      | μS    |

| III C                              |        | V <sub>CSSP</sub> - V <sub>CSSN</sub> = 0.185V                                                                                                       | -15                        |      | +15                       | 0/    |

| IINP Current Accuracy              |        | V <sub>CSSP</sub> - V <sub>CSSN</sub> = 0.05V (Note 3)                                                                                               | -20                        |      | +20                       | %     |

| CCCD CCCNI A source                |        | V <sub>CSSP</sub> - V <sub>CSSN</sub> = 0.08V, V <sub>CLS</sub> = 1.6V                                                                               | -10                        |      | +10                       | %     |

| CSSP - CSSN Accuracy               |        | V <sub>CSSP</sub> - V <sub>CSSN</sub> = 0.2V, CLS = REF                                                                                              | -10                        |      | +10                       |       |

| CSSP + CSSN Input Voltage<br>Range |        |                                                                                                                                                      | 8.0                        |      | 28                        | V     |

| LOGIC LEVELS                       | I      |                                                                                                                                                      | l .                        |      |                           |       |

| CELLS Input Low Voltage            |        |                                                                                                                                                      |                            |      | 0.2                       | V     |

| CELLS Input Middle Voltage         |        |                                                                                                                                                      | 0.4                        |      | V <sub>LDO</sub><br>- 0.5 | V     |

| CELLS Input High Voltage           |        |                                                                                                                                                      | V <sub>LDO</sub><br>- 0.25 |      | V <sub>LDO</sub>          | V     |

| CELLS Input Bias Current           |        | V <sub>CELLS</sub> = 0V or V <sub>LDO</sub>                                                                                                          | -10                        |      | +10                       | μΑ    |

| ACOK Sink Current                  |        | VACOK = 0.4V                                                                                                                                         | 1                          |      |                           | mA    |

| ACOK Leakage Current               |        | V <sub>ACOK</sub> = 5.5V                                                                                                                             | -1                         |      | +1                        | μΑ    |

#### **ELECTRICAL CHARACTERISTICS**

$\begin{array}{l} (V_{DCIN} = V_{CSSP} = V_{CSSN} = 18V, \ V_{BATT} = V_{CSIP} = V_{CSIN} = 12V, \ V_{REFIN} = 3.0V, \ V_{VCTL} = V_{ICTL} = 0.75 \times V_{REFIN}, \ V_{CELLS} = 2.0V, \ V_{ACIN} = 0V, \ CLS = REF, \ V_{BST} - V_{LX} = 4.5V, \ V_{GND} = V_{PGND} = 0V, \ C_{LDO} = 1\mu\text{F}, \ LDO = DLOV, \ C_{REF} = 1\mu\text{F}; \ pins \ CCI, \ CCS, \ and \ CCV \ are compensated per Figure 1a; \ \textbf{T_A} = -40^{\circ}\textbf{C} \ \ to \ +85^{\circ}\textbf{C}, \ unless \ otherwise \ noted.) \ (Note 1) \end{array}$

| PARAMETER                                        | SYMBOL            | CONDITIONS                                                         | MIN   | TYP | MAX   | UNITS    |

|--------------------------------------------------|-------------------|--------------------------------------------------------------------|-------|-----|-------|----------|

| SUPPLY AND LDO REGULATO                          | R                 |                                                                    |       |     |       |          |

| DCIN Input Voltage Range                         | V <sub>DCIN</sub> |                                                                    | 8.0   |     | 28.0  | V        |

| DCIN Undervoltage Lockout                        |                   | V <sub>DCIN</sub> falling                                          | 7     |     |       | V        |

| Trip Point                                       |                   | V <sub>DCIN</sub> rising                                           |       |     | 7.85  | ľ        |

| DCIN Quiescent Current                           | IDCIN             | 8.0V < V <sub>DCIN</sub> < 28V                                     |       |     | 6     | mA       |

| LDO Output Voltage                               |                   | 8.0V < V <sub>DCIN</sub> < 28V, no load                            | 5.25  |     | 5.65  | V        |

| TRIP POINTS                                      | •                 |                                                                    | •     |     |       | •        |

| BATT POWER_FAIL Threshold                        |                   | V <sub>CSSP</sub> falling                                          | 50    |     | 150   | mV       |

| BATT POWER_FAIL Threshold<br>Hysteresis          |                   |                                                                    | 100   |     | 300   | mV       |

| ACIN Threshold                                   |                   | V <sub>ACIN</sub> rising                                           | 2.007 |     | 2.089 | V        |

| ACIN Threshold Hysteresis                        |                   | 0.5% of REF                                                        | 10    |     | 30    | mV       |

| ACIN Input Bias Current                          |                   | V <sub>ACIN</sub> = 2.048V                                         | -1    |     | +1    | μΑ       |

| CLS Input Range                                  |                   |                                                                    | 1.6   |     | REF   | V        |

| CLS Input Bias Current                           |                   | V <sub>CLS</sub> = 2.0V                                            | -1    |     | +1    | μΑ       |

| SWITCHING REGULATOR                              |                   |                                                                    |       |     |       | 1        |

| Minimum Off-Time                                 |                   | V <sub>BATT</sub> = 16.8V                                          | 1     |     | 1.5   | μs       |

| Maximum On-Time                                  |                   |                                                                    | 5     |     | 15    | ms       |

| Oscillator Frequency                             | fosc              | (Note 1)                                                           |       |     | 400   | kHz      |

| DHI Maximum Duty Cycle                           |                   |                                                                    | 99    |     |       | %        |

|                                                  |                   | VBATT = 19V, VDCIN = 0V                                            |       |     | 5     |          |

| BATT Input Current                               | I <sub>BATT</sub> | VBATT = 2V to 19V, VDCIN > VBATT + 0.3V                            |       |     | 500   | μΑ       |

|                                                  |                   | V <sub>DCIN</sub> = 0V                                             |       |     | 5     |          |

| CSIP/CSIN Input Current                          |                   | V <sub>CSIP</sub> = V <sub>CSIN</sub> = 12V                        |       |     | 800   | μΑ       |

| 0000/00011                                       |                   | V <sub>DCIN</sub> = 0V                                             |       |     | 0.3   |          |

| CSSP/CSSN Input Current                          |                   | VCSSP = VCSSN = VDCIN > 8.0V                                       |       |     | 800   | μA       |

| BATT/CSIP/CSIN Input Voltage<br>Range            |                   |                                                                    | 0     |     | 19    | V        |

| CSIP to CSIN Full-Scale<br>Current-Sense Voltage |                   | V <sub>BATT</sub> = 12V                                            | 189   |     | 219   | mV       |

| CSSP to CSSN Full-Scale<br>Current-Sense Voltage |                   |                                                                    | 189   |     | 219   | mV       |

| CURRENT AND VOLTAGE SET                          | TING              | 1                                                                  | 1     |     |       | <u> </u> |

| 01 1 0 14                                        |                   | ICTL = REFIN (see Equation 2)                                      | -8    |     | +8    | ٥,       |

| Charging Current Accuracy                        |                   | ICTL = REFIN/32 (see Equation 2)                                   | -55   |     | +55   | %        |

| ICTL, VCTL, REFIN Input Bias                     |                   | V <sub>V</sub> CTL = V <sub>I</sub> CTL = V <sub>R</sub> EFIN = 3V | -1    |     | +1    |          |

| Current                                          |                   | VDCIN = 0V, VVCTL = VICTL = VREFIN = 5V                            | -1    |     | +1    | μA       |

### **ELECTRICAL CHARACTERISTICS (continued)**

$\begin{array}{l} (V_{DCIN} = V_{CSSP} = V_{CSSN} = 18V, \ V_{BATT} = V_{CSIP} = V_{CSIN} = 12V, \ V_{REFIN} = 3.0V, \ V_{VCTL} = V_{ICTL} = 0.75 \times V_{REFIN}, \ V_{CELLS} = 2.0V, \ V_{ACIN} = 0V, \ CLS = REF, \ V_{BST} - V_{LX} = 4.5V, \ V_{GND} = V_{PGND} = 0V, \ C_{LDO} = 1\mu F, \ LDO = DLOV, \ C_{REF} = 1\mu F; \ pins \ CCI, \ CCS, \ and \ CCV \ are compensated per Figure 1a; \ \textbf{T_A} = -40^{\circ}\textbf{C} \ to +85^{\circ}\textbf{C}, \ unless \ otherwise \ noted.) \ (Note 1) \end{array}$

| PARAMETER                                 | SYMBOL | CONDITIONS                                             | MIN TY                     | P MAX                     | UNITS |

|-------------------------------------------|--------|--------------------------------------------------------|----------------------------|---------------------------|-------|

| ICTL Power-Down Mode<br>Threshold Voltage |        |                                                        | REFIN<br>/100              | REFIN<br>/33              | V     |

| Battery Regulation Voltage                |        | VvcTL = VREFIN (2, 3, or 4 cells) (see Equation 1)     | -1                         | +1                        | %     |

| Accuracy                                  |        | VvcTL = VREFIN/20 (2, 3, or 4 cells) (see Equation 1)  | -1                         | +1                        | 70    |

| REFIN Range                               |        |                                                        | 2.0                        | 3.6                       | V     |

| REFIN Undervoltage Lockout                |        |                                                        |                            | 1.92                      | V     |

| ICLIC Accuracy                            |        | V <sub>CSIP</sub> - V <sub>CSIN</sub> = 0.185V         | -5                         | +5                        | %     |

| ICHG Accuracy                             | İ      | V <sub>CSIP</sub> - V <sub>CSIN</sub> = 0.05V          | -10                        | +10                       | %     |

| IIND Comment Assume                       |        | V <sub>CSSP</sub> - V <sub>CSSN</sub> = 0.185V         | -15                        | +15                       | 0/    |

| IINP Current Accuracy                     |        | V <sub>CSSP</sub> - V <sub>CSSN</sub> = 0.05V (Note 3) | -20                        | +20                       | %     |

| 0000 000114                               |        | VCSSP - VCSSN = 0.08V, VCLS = 1.6V                     | -10                        | +10                       | 0/    |

| CSSP - CSSN Accuracy                      |        | VCSSP - VCSSN = 0.2V, CLS = REF                        | -10                        | +10                       | - %   |

| CSSP + CSSN Input Voltage<br>Range        |        |                                                        | 8                          | 28                        | V     |

| LOGIC LEVELS                              | -      |                                                        |                            |                           |       |

| CELLS Input Low Voltage                   |        |                                                        |                            | 0.2                       | V     |

| CELLS Input Middle Voltage                |        |                                                        | 0.4                        | V <sub>LDO</sub><br>- 0.5 | V     |

| CELLS Input High Voltage                  |        |                                                        | V <sub>LDO</sub><br>- 0.25 | V <sub>LDO</sub>          | V     |

| CELLS Input Bias Current                  |        | V <sub>CELLS</sub> = 0V or V <sub>LDO</sub>            | -10                        | +10                       | μΑ    |

| ACOK Sink Current                         |        | V <sub>ACOK</sub> = 0.4V                               | 1                          |                           | mA    |

| ACOK Leakage Current                      |        | V <sub>ACOK</sub> = 5.5V                               | -1                         | +1                        | μΑ    |

Note 2: Guaranteed by design. Not production tested.

Note 3: Tested under DC conditions. See text for more detail.

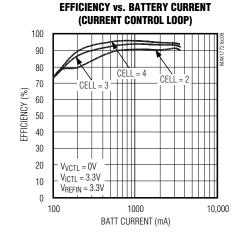

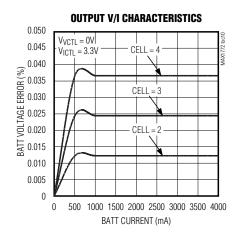

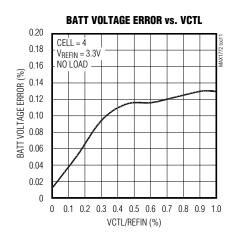

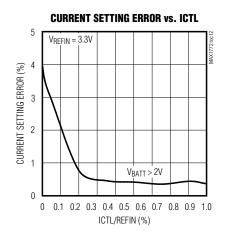

### **Typical Operating Characteristics**

(Circuit of Figure 1a,  $V_{DCIN} = 20V$ ,  $T_A = +25$ °C, unless otherwise noted.)

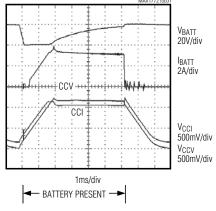

## LOAD-TRANSIENT RESPONSE (BATTERY REMOVAL AND REINSERTION)

$\begin{array}{l} V_{ICTL} = 0.957V \\ V_{CTL} = 3.3V \end{array}$

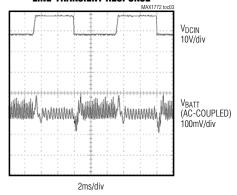

#### LINE-TRANSIENT RESPONSE

$V_{BATT} = 16V$   $V_{DCIN} = 18.5V TO 27.5V$  $I_{LOAD} = 150mA$

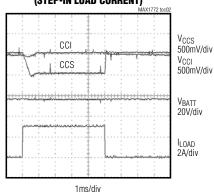

# LOAD-TRANSIENT RESPONSE (STEP-IN LOAD CURRENT)

V<sub>ICTL</sub> = 3.30V CHARGING CURRENT = 2.0A V<sub>BATT</sub> = 16V LOAD STEP = 0 TO 3A I<sub>SOURCE</sub> LIMIT = 5A

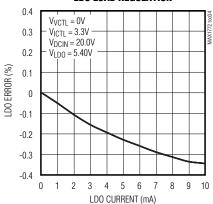

#### LDO LOAD REGULATION

### Typical Operating Characteristics (continued)

(Circuit of Figure 1a, V<sub>DCIN</sub> = 20V, T<sub>A</sub> = +25°C, unless otherwise noted.)

10

0

0.1

10

BATT CURRENT (mA)

100

1000

10 000

**EFFICIENCY vs. BATTERY CURRENT**

## Typical Operating Characteristics (continued)

(Circuit of Figure 1a,  $V_{DCIN} = 20V$ ,  $T_A = +25$ °C, unless otherwise noted.)

### Pin Description

| PIN  | NAME  | FUNCTION                                                                                                                                                                                                                                                                                   |

|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | DCIN  | Charging Voltage Input                                                                                                                                                                                                                                                                     |

| 2    | LDO   | Device Power Supply. Output of the 5.4V linear regulator supplied from DCIN. Bypass LDO with a 1µF capacitor to GND.                                                                                                                                                                       |

| 3    | CLS   | Source Current-Limit Input. Voltage input for setting the current limit of the input source.                                                                                                                                                                                               |

| 4    | REF   | 4.096V Voltage Reference. Bypass REF with a 1µF capacitor to GND.                                                                                                                                                                                                                          |

| 5    | CCS   | Input Current Regulation Loop Compensation Point. Connect a 0.01µF capacitor from CCS to GND.                                                                                                                                                                                              |

| 6    | CCI   | Output Current Regulation Loop Compensation Point. Connect a 0.01µF capacitor from CCI to GND.                                                                                                                                                                                             |

| 7    | CCV   | Voltage Regulation Loop Compensation Point. Connect $1k\Omega$ resistor in series with a $0.1\mu F$ capacitor to GND.                                                                                                                                                                      |

| 8, 9 | GND   | Analog Ground                                                                                                                                                                                                                                                                              |

| 10   | ICHG  | ICHG is a scaled-down replica of the battery output current being sensed. It is used to monitor the charging current and indicates when the chip changes from voltage mode to current mode. The transconductance of (CSIP - CSIN) to ICHG is 1µS. Connect ICHG pin to GND if it is unused. |

| 11   | ACIN  | AC Detect Input. Detects when the AC adapter voltage is available for charging.                                                                                                                                                                                                            |

| 12   | ACOK  | AC Detect Output. Open-drain output is high when ACIN is less than REF/2.                                                                                                                                                                                                                  |

| 13   | REFIN | Reference Input. Allows the ICTL and VCTL pins to have ratiometric ranges for increased DAC accuracy.                                                                                                                                                                                      |

| 14   | ICTL  | Input for Setting Maximum Output Current. Range is REFIN/32 to REFIN. The device shuts down if this pin is forced below REFIN/55 (typ).                                                                                                                                                    |

| 15   | VCTL  | Input for Setting Maximum Output Voltage. Range is 0 to REFIN.                                                                                                                                                                                                                             |

| 16   | CELLS | Trilevel Input for Setting Number of Cells. GND = 2 cells, LDO/2 = 3 cells, LDO = 4 cells.                                                                                                                                                                                                 |

| 17   | BATT  | Battery Voltage Input                                                                                                                                                                                                                                                                      |

| 18   | CSIN  | Output Current-Sense Negative Input                                                                                                                                                                                                                                                        |

| 19   | CSIP  | Output Current-Sense Positive Input. Connect a current-sense resistor from CSIP to CSIN.                                                                                                                                                                                                   |

| 20   | PGND  | Power Ground                                                                                                                                                                                                                                                                               |

| 21   | DLO   | Low-Side Power MOSFET Driver Output. Connect DLO to a low-side nMOS gate.                                                                                                                                                                                                                  |

| 22   | DLOV  | Low-Side Driver Supply                                                                                                                                                                                                                                                                     |

| 23   | LX    | Power Connection for the High-Side Power MOSFET Driver. Connect LX to a source of high-side nMOS.                                                                                                                                                                                          |

| 24   | DHI   | High-Side Power MOSFET Driver Output. Connect DHI to a high-side nMOS gate.                                                                                                                                                                                                                |

| 25   | BST   | Power Connection for the High-Side Power MOSFET Driver. Connect a 0.1µF capacitor from LX to BST.                                                                                                                                                                                          |

| 26   | CSSN  | Input Current-Sense for Charger (negative input)                                                                                                                                                                                                                                           |

| 27   | CSSP  | Input Current-Sense for Charger (positive input). Connect a current-sense resistor from CSSP to CSSN.                                                                                                                                                                                      |

| 28   | IINP  | IINP is a scaled-down replica of the input current being sensed. It is used to monitor the total system current. The transconductance of (CSSP - CSSN) to IINP is 1mS. Connect IINP pin to GND if it is unused.                                                                            |

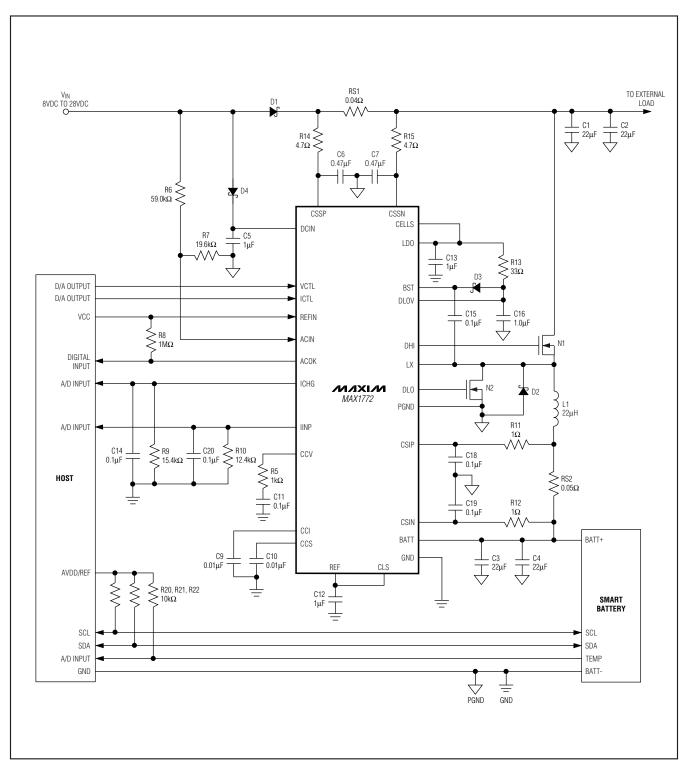

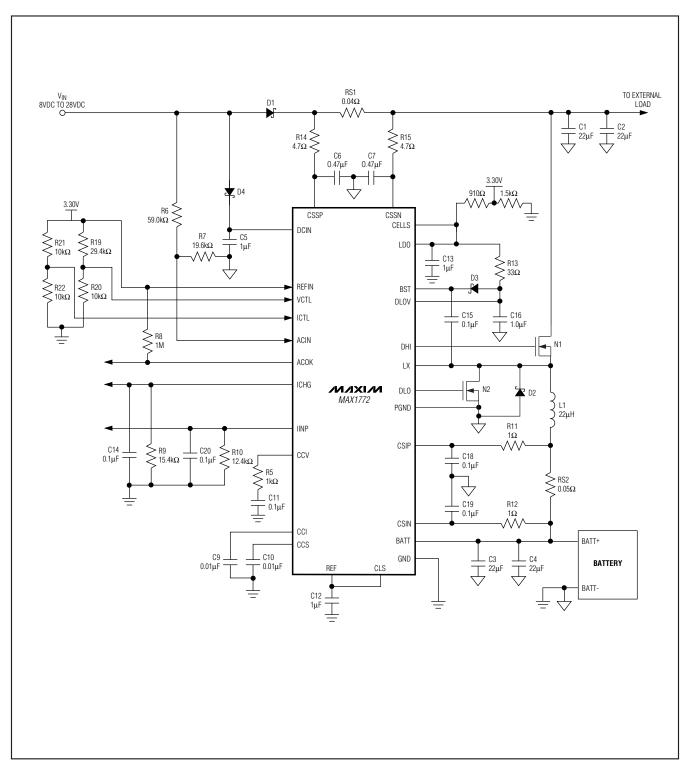

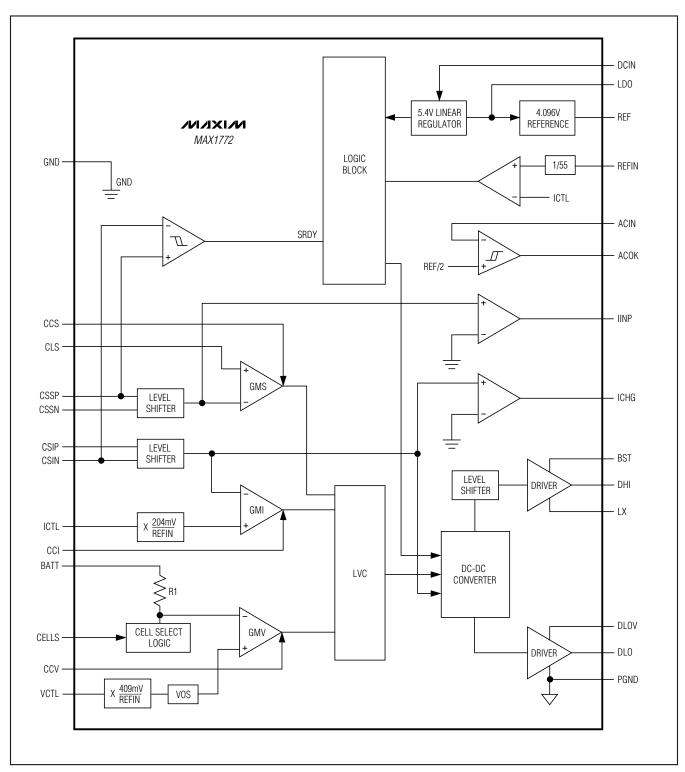

### **Detailed Description**

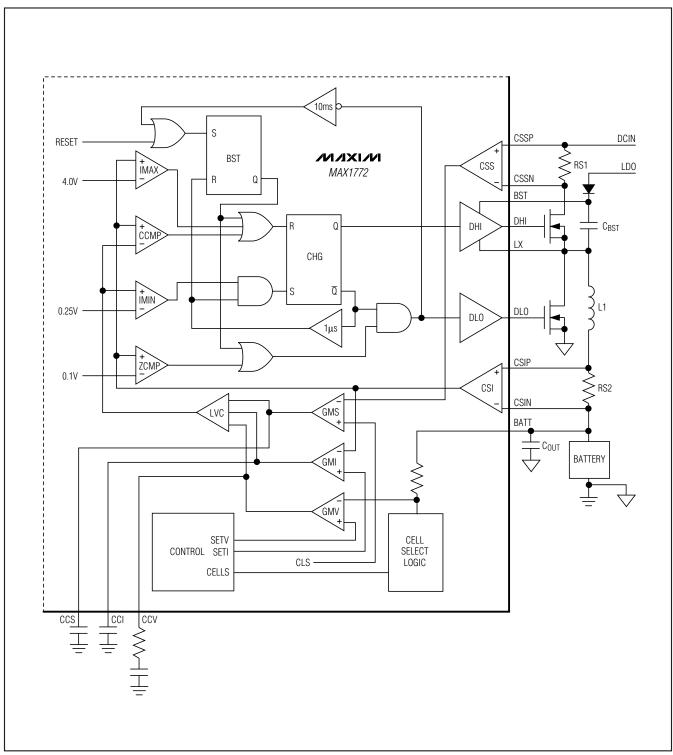

The MAX1772 includes all of the functions necessary to charge Li+, NiMH, and NiCd batteries. A high-efficiency synchronous-rectified step-down DC-DC converter controls charging voltage and current. It also includes input source-current limiting and analog inputs for setting the charge current and charge voltage. The DC-DC converter uses external N-channel MOSFETs as the buck switch and synchronous rectifier to convert the input voltage to the required charging current and voltage. The typical application circuit shown in Figure 1a uses a microcontroller (µC) to allow control of charging current or voltage, while Figure 1b shows a typical application with charging voltage and current fixed to specific values for the application. The voltage at ICTL and the value of RS2 set the charging current. The DC-DC converter generates the control signals for the external MOSFETs to regulate the voltage and the current set by the VCTL, ICTL, and CELLS inputs.

The MAX1772 features a voltage-regulation loop (CCV) and two current-regulation loops (CCI and CCS). The CCV voltage-regulation loop monitors BATT to ensure that its voltage never exceeds the voltage set by VCTL. The CCI battery current-regulation loop monitors current delivered to BATT to ensure that it never exceeds the current limit set by ICTL. A third loop (CCS) takes control and reduces the battery-charging current when the sum of the system load and the battery-charging current exceeds the charging source current limit set by CLS.

#### **Setting the Battery Regulation Voltage**

The MAX1772 uses a high-accuracy voltage regulator for charging voltage. The VCTL input adjusts the battery output voltage. VCTL is allowed to vary from 0 to REFIN (≈3.3V). The per-cell battery termination voltage is a function of the battery chemistry and construction; thus, consult the battery manufacturer to determine this voltage. The battery voltage is calculated by the equation:

$$V_{BATT} = CELLS \times \left(V_{REF} + \left(\frac{V_{REF}}{10} \times \frac{V_{VCTL}}{V_{REFIN}}\right)\right)$$

(1)

CELLS is the programming input for selecting cell count. Table 1 shows how CELLS is connected to charge 2, 3, or 4 cells. Use a voltage-divider from LDO to set the desired voltage at CELLS.

The internal error amplifier (GMV) maintains voltage regulation (Figure 2). The voltage error amplifier is compensated at CCV. The component values shown in Figure 1 provide suitable performance for most appli-

cations. Individual compensation of the voltage regulation and current-regulation loops allow for optimal compensation.

#### **Setting the Charging-Current Limit**

The ICTL input sets the maximum charging current. The current is set by current-sense resistor RS2, connected between CSIP and CSIN. The nominal differential voltage between CSIP and CSIN is 204mV; thus, for a 0.05 $\Omega$  sense resistor, the maximum charging current is 4A. Battery-charging current is programmed with ICTL using the equation:

$$I_{CHG} = \frac{V_{REF}}{RS2} \times \frac{V_{ICTL}}{V_{REFIN}} \times \frac{1}{20}$$

(2)

The input range for ICTL is REFIN/32 to REFIN ( $\approx 3.3$ V). The device shuts down if ICTL is forced below REFIN/55 (typical). The current at ICHG is a scaled-down replica of the battery output current being sensed across CSIP and CSIN.

When choosing the current-sense resistor, note that the voltage drop across this resistor causes further power loss, reducing efficiency. However, adjusting ICTL to reduce the voltage across the current-sense resistor may degrade accuracy due to the input offset of the current-sense amplifier. The charging current-error amplifier (GMI) is compensated at CCI. A 0.01µF capacitor at CCI provides suitable performance for most applications.

#### **Setting the Input Current Limit**

The total input current (from a wall cube or other DC source) is a function of the system supply current and the battery-charging current. The input current regulator limits the source current by reducing the charging current when the input current exceeds the set input current limit. System current will normally fluctuate as portions of the system are powered up or put to sleep. Without input current regulation, the input source must be able to supply the maximum system current and the maximum charger input current. By using the input current limiter, the current capability of the AC wall adapter may be lowered, reducing system cost.

The MAX1772 limits the current drawn by the charger when the load current becomes high. The device limits the charging current, so the AC adapter voltage is not loaded down. An internal amplifier compares the voltage between CSSP and CSSN to the voltage at CLS. VCLS can be set by a resistor-divider between REF and GND. Connect CLS to REF for maximum input current limiting.

Figure 1a. µC-Controlled Typical Application Circuit

Figure 1b. Stand-Alone Typical Application Circuit

Figure 2. Functional Diagram

**Table 1. Cell-Count Programming Table**

| CELL                                                             | CELL COUNT |

|------------------------------------------------------------------|------------|

| V <sub>CELLS</sub> < 0.20V                                       | 2          |

| 0.40V < V <sub>CELLS</sub> < V <sub>LDO</sub> -0.5V              | 3          |

| V <sub>LDO</sub> - 0.25V < V <sub>CELLS</sub> < V <sub>LDO</sub> | 4          |

The input source current is the sum of the device current, the charger input current, and the load current. The device current is minimal (6mA) in comparison to the charge and load currents. The actual source current required is determined as follows:

$$I_{SOURCE} = I_{LOAD} + [(I_{CHARGE} \times V_{BATT}) / (V_{IN} \times \eta)]$$

(3)

where  $\eta$  is the efficiency of the DC-DC converter (85% to 95% typ).

VCLS determines the reference voltage of the GMS error amplifier. Sense resistor RS1 sets the maximum allowable source current. Calculate the maximum current as follows:

$$I_{SOURCE\_MAX} = V_{CLS} / (20 \times RS1)$$

(4)

Once the input current limit is reached, the charging current is tapered back until the input current is below the desired threshold.

When choosing the current-sense resistor, note that the voltage drop across this resistor causes further power loss, reducing efficiency.

#### **AC Adapter Detection**

Connect the AC adapter voltage through a resistive divider to ACIN to detect when AC power is available, as shown in Figure 1. ACOK is an open-drain output and is high when ACIN is less than REF/2.

#### **Current Measurement**

Use ICHG to monitor the battery-charging current being sensed across CSIP and CSIN. The output voltage range is 0 to 3V. The voltage of ICHG is proportional to the output current by the equation:

$$V_{ICHG} = I_{ICHG} \times RS2 \times G_{ICHG} \times R9$$

(5)

where I<sub>ICHG</sub> is the battery-charging current, G<sub>ICHG</sub> is the transconductance of ICHG (1mS typ), and R9 is the resistor connected between ICHG and ground.

Connect ICHG pin to ground if it is not used.

Use IINP to monitor the system input current being sensed across CSSP and CSSN. The output voltage range is 0 to 3V. The voltage of IINP is proportional to the output current by the equation:

$$V_{IINP} = I_{SOURCE} \times RS1 \times G_{IINP} \times R10$$

(6)

where ISOURCE is the DC current being supplied by the AC adapter power,  $G_{\mbox{\footnotesize{IINP}}}$  is the transconductance of IINP (1µS typ), and R10 is the resistor connected between IINP and ground.

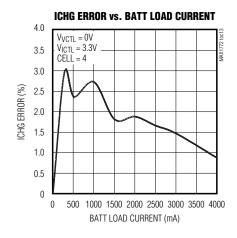

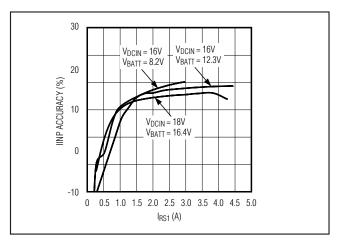

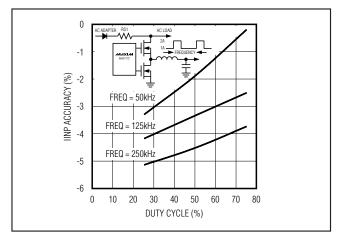

In the typical application circuit, duty cycle affects the accuracy of  $V_{\mbox{\footnotesize{IINP}}}$  (Figure 3). AC load current also affects accuracy (Figure 4).

Connect IINP pin to ground if it is not used.

#### **LDO** Regulator

LDO provides a 5.4V supply derived from DCIN and can deliver up to 15mA of current. The MOSFET drivers are powered by DLOV and BST, which must be connected to LDO as shown in Figure 1. LDO also supplies the 4.096V reference (REF) and most of the control circuitry. Bypass LDO with a 1µF capacitor.

#### **DC-to-DC Converter**

The MAX1772 employs a buck regulator with a bootstrapped NMOS high-side switch and a low-side NMOS synchronous rectifier.

#### **DC-DC Controller**

The control scheme is a constant off-time variable frequency, cycle-by-cycle current mode. The off-time is constant for a given BATT voltage. It varies with VBATT operation; a maximum on-time of 10ms allows the controller to achieve >99% duty cycle with continuous conduction. Figure 5 shows the controller functional diagram.

#### **MOSFET Drivers**

The low-side driver output DLO swings from 0 to DLOV. DLOV is usually connected through a filter to LDO. The high-side driver output DHI is bootstrapped off LX and swings from V<sub>LX</sub> to V<sub>BST</sub>. When the low-side driver turns on, BST rises to one diode voltage below DLOV.

Filter DLOV with a resistor-capacitor (RC) circuit whose cutoff frequency is about 50kHz. The configuration in Figure 1 introduces a cutoff frequency of around 48kHz:

$$f = 1/2\pi RC = 1 / (2\pi \times 33\Omega \times 0.1\mu F) = 48kHz$$

(7)

Figure 3. IINP Accuracy vs. VDCIN/VBATT

#### **Dropout Operation**

The MAX1772 has 99.99% duty-cycle capability with a 10ms maximum on-time and 1µs off-time. This allows the charger to achieve dropout performance limited only by resistive losses in the DC-DC converter components (D1, N1, RS1, RS2) (Figure 1). The actual dropout voltage is limited to 100mV between CSSP and CSIN by the power-fail comparator.

#### Compensation

Each of the three regulation loops—the input current limit, the charging current limit, and charging voltage limit—can be compensated separately using the CCS, CCI, and CCV pins, respectively.

The charge-current-loop error-amp output is brought out at CCI. Likewise, the source current error-amp output is brought out at CCS; 0.01µF capacitors to ground at CCI and CCS compensate the current loops in most charger designs. Raising the value of these capacitors reduces the bandwidth of these loops.

The voltage-regulating-loop error-amp output is brought out at CCV. Compensate this loop by connecting a series RC network from CCV to GND. Recommended values are  $1k\Omega$  and  $0.1\mu F$ . The zero set by the series RC increases midfrequency gain to provide phase compensation. The pole at CCV is set by the capacitor and the voltage error-amp output impedance at low frequencies to integrate the DC error.

### Component Selection

Table 2 lists the recommended components and refers to the circuit of Figure 1. The following sections describe how to select these components.

Figure 4. IINP Accuracy vs. AC Load Duty Cycle

#### **MOSFETs and Schottky Diodes**

Schottky diode D1 provides power to the load when the AC adapter is inserted. This diode must be able to deliver the maximum current as set by RS1.

The n-channel MOSFETs (N1, N2) are the switching devices for the buck controller. High-side switch N1 should have a current rating of at least 8A and have an on-resistance (RDS(ON)) of  $50m\Omega$  or less. The driver for N1 is powered by BST; its current should be less than 10mA. Select a MOSFET with a low total gate charge (QGATE) and determine the required drive current by IGATE = QGATE  $\times$  f (where f is the DC-DC converter's 400kHz maximum switching frequency).

The low-side switch (N2) should also have a current rating of at least 8A, have an  $R_{DS(ON)}$  of  $100m\Omega$  or less, and a total gate charge less than 10nC. N2 is used to provide the starting charge to the BST capacitor (C15). During normal operation, the current is carried by Schottky diode D2. Choose a Schottky diode capable of carrying the maximum charging current.

D3 is a signal-level diode, such as the 1N4148. This diode provides the supply current to the high-side MOSFET driver.

#### **Inductor Selection**

Inductor L1 provides power to the battery while it is being charged. It must have a saturation current of at least 4A plus 1/2 of the current ripple ( $\Delta I_L$ ):

$$I_{SAT} = 4A + (1/2) \Delta I_{L}$$

(8)

\_\_\_ /VI/XI/VI

Figure 5. DC-to-DC Converter Functional Diagram

The controller determines the constant off-time period, which is dependent on BATT voltage. This makes the ripple current independent of input and battery voltage, and it should be kept to less than 1A. Calculate  $\Delta I_L$  with the following equation:

$$\Delta I_{L} = \frac{21V\mu s}{L(\mu H)} \tag{9}$$

Higher inductor values decrease the ripple current. Smaller inductor values require high saturation current capabilities and degrade efficiency. Typically, a 22µH inductor is ideal for all operating conditions.

#### **Current-Sense Input Filtering**

In normal circuit operation with typical components, the current-sense signals can have high-frequency transients that exceed 0.5V due to large current changes and parasitic component inductance. To achieve proper battery and input current compliance, the current-sense input signals should be filtered to remove large common-mode transients. The input current-limit sensing circuitry is the most sensitive case due to large current steps in the input filter capacitors (C6, C7) in Figure 1. Use 0.47µF ceramic capacitors from CSSP and CSSN to ground. Smaller 0.1µF ceramic capacitors (C18, C19) can be used on the CSIP and CSIN inputs to ground since the current into the battery is continuous. Place these capacitors next to the single-point ground directly under the MAX1772.

### Layout and Bypassing

Bypass DCIN with a  $1\mu F$  to ground (Figure 1). D4 protects the MAX1772 when the DC power source input is reversed. A signal diode for D4 is adequate because DCIN only powers the LDO and the internal reference. Bypass LDO, BST, DLOV, and other pins as shown in Figure 1.

Good PCB layout is required to achieve specified noise, efficiency, and stable performance. The PC board layout artist must be given explicit instructions—preferably, a pencil sketch showing the placement of the power switching components and high current routing. Refer to the PCB layout in the MAX1772 evaluation kit for examples. A ground plane is essential for optimum performance. In most applications, the circuit will be located on a multilayer board, and full use of the four or more copper layers is recommended. Use the top layer for high current connections, the bottom layer for quiet connections (REF, CCV, CCI, CCS, DCIN, and GND), and the inner layers for an uninterrupted ground plane.

Use the following step-by-step guide:

- 1) Place the high power connections first, with their grounds adjacent:

- Minimize the current-sense resistor trace lengths, and ensure accurate current sensing with Kelvin connections.

- Minimize ground trace lengths in the high current paths.

- Minimize other trace lengths in the high current paths.

- Use >5mm wide traces.

- Connect C1 and C2 to high-side MOSFET (10mm max length).

- LX node (MOSFETs, rectifier cathode, inductor (15mm max length)).

Ideally, surface-mount power components are flush against one another with their ground terminals almost touching. These high-current grounds are then connected to each other with a wide, filled zone of top-layer copper, so they do not go through vias.

The resulting top-layer subground plane is connected to the normal inner-layer ground plane at the output ground terminals, which ensures that the IC's analog ground is sensing at the supply's output terminals without interference from IR drops and ground noise. Other high current paths should also be minimized, but focusing primarily on short ground and current-sense connections eliminates about 90% of all PCB layout problems.

2) Place the IC and signal components. Keep the main switching node (LX node) away from sensitive analog components (current-sense traces and REF capacitor). Important: the IC must be no further than 10mm from the current-sense resistors.

Keep the gate drive traces (DHI, DLO, and BST) shorter than 20mm, and route them away from the current-sense lines and REF. Place ceramic bypass capacitors close to the IC. The bulk capacitors can be placed further away. Place the current-sense input filter capacitors under the part, connected directly to the GND pin.

3) Use a single-point star ground placed directly below the part. Connect the input ground trace, power ground (subground plane), and normal ground to this node.

**Table 2. Component List**

| DESIGNATION                             | DESCRIPTION                                                                                             |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------|

| C1, C2, C3, C4                          | 22μF, 35V low-ESR tantalum capacitors<br>AVX TPSE226M035R0300 or<br>Sprague 593D226X0035E2W             |

| C5                                      | 1μF, 50V ceramic capacitor (1210)<br>Murata GRM42-2X7R105K050                                           |

| C6, C7                                  | 0.47µF, 25V ceramic capacitors (1210)<br>Murata GRM42-2X7R474K050                                       |

| C9, C10                                 | 0.01µF ceramic capacitors (0805)                                                                        |

| C12, C13                                | 1μF, 10V ceramic capacitors (0805)<br>Taiyo Yuden LMK212BJ105MG                                         |

| C11, C14, C15,<br>C16, C18, C19,<br>C20 | 0.1µF, 50V ceramic capacitors (0805)<br>Taiyo Yuden UMK212BJ104MG or<br>Murata GRM40-034X7R104M050      |

| D1                                      | Schottky diode (DPAK) STM-Microelectronics STPS8L30B or ON Semiconductor MBRD630CT or Toshiba U5FWK2C42 |

| D2                                      | 30V, 3A Schottky diode<br>Nihon EC31QS03L                                                               |

| D3, D4                                  | 100mA Schottky diodes (SOT23)<br>Central Semiconductor CMPSH-3 or<br>Hitachi HRB0103A                   |

| L1                                      | 22µH power inductor<br>Sumida CDRH127-220                                                               |

| DESIGNATION   | DESCRIPTION                                                                 |

|---------------|-----------------------------------------------------------------------------|

| N1            | n-channel MOSFET<br>International Rectifier IRF7805 or<br>Fairchild FDS6680 |

| N2            | n-channel MOSFET<br>Fairchild FDS6612A                                      |

| RS1           | 0.04Ω ±1%, 1W resistor<br>Dale WSL-2512-R040-F or<br>IRC LR2512-01-R040-F   |

| RS2           | 0.05Ω ±1%, 1W resistor<br>Dale WSL-2512-R050-F or<br>IRC LR2512-01-R050-F   |

| R5            | 1kΩ ±5% resistor (0805)                                                     |

| R6            | 59.0kΩ ±1% resistor (0805)                                                  |

| R7            | 19.6kΩ ±1% resistor (0805)                                                  |

| R8            | 1MΩ ±5% resistor (0805)                                                     |

| R9            | 15.4kΩ ±1% resistor (0805)                                                  |

| R10           | 12.4kΩ ±1% resistor (0805)                                                  |

| R11, R12      | $1\Omega \pm 5\%$ resistors (0805)                                          |

| R13           | 33Ω ±5% resistor (1206)                                                     |

| R14, R15      | 4.7Ω ±5% resistors (1206)                                                   |

| R19           | 29.4kΩ ±1% resistor (0805)                                                  |

| R20, R21, R22 | 10k $\Omega$ ±1% resistors (0805)                                           |

### **Chip Information**

PROCESS: BiCMOS

## \_Package Information

For the latest package outline information and land patterns, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |  |

|--------------|--------------|----------------|--|

| 28 QSOP      | E28-1        | <u>21-0055</u> |  |

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION     | PAGES<br>CHANGED |

|--------------------|------------------|-----------------|------------------|

| 0                  | 4/07             | Initial release | _                |

| 4                  | 2/09             | Minor edits.    | 14               |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated:

MAX1772EEI+ MAX1772EEI+T