[Evaluation Kit Available](#)

[Design Resources](#)

[Tools and Models](#)

[Support](#)

Click [here](#) to ask an associate for production status of specific part numbers.

## Automotive High-Current Step-Down Converter with USB Protection/Host Charger Adapter Emulator

**MAX16984**

### General Description

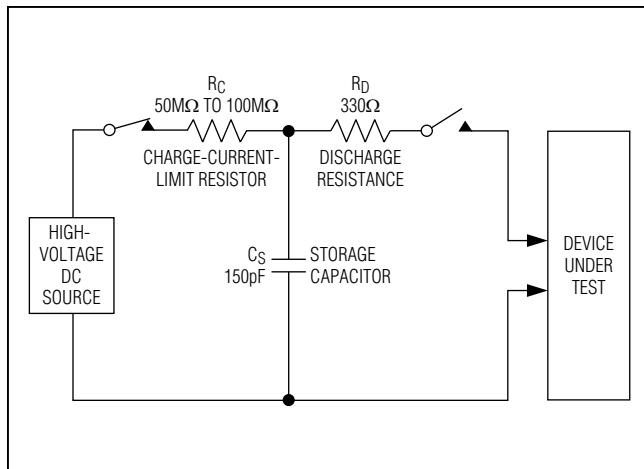

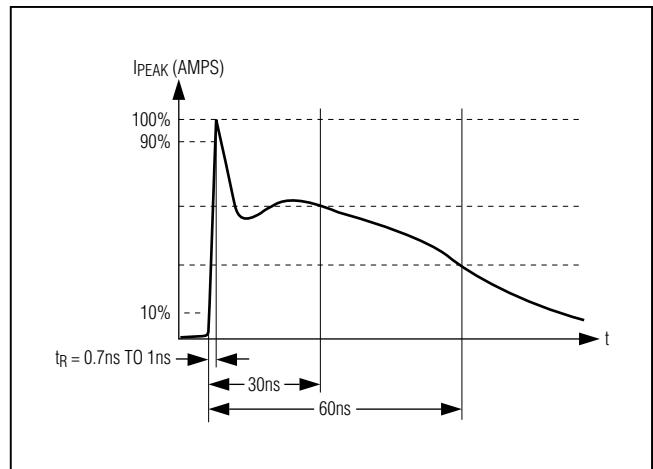

The MAX16984 combines a 5V automotive-grade step-down converter capable of driving up to 2.5A, a USB host charger adapter emulator, and USB protection switches for automotive USB host applications. The USB protection switches provide high-ESD, short-circuit protection and feature integrated host-charger port-detection circuitry adhering to the USB 2.0 Battery Charging Specification BC1.2 battery charging specification and Chinese Telecommunication Industry Standard YD/T 1591-2009. They also include circuitry for iPod®/iPhone® 1.0A and iPad® 2.1A dedicated charging modes. The HVD+ and HVD- ESD protection features include protection to  $\pm 15\text{kV}$  Air/ $\pm 8\text{kV}$  Contact on the HVD+ and HVD- outputs to the IEC 61000-4-2 model and  $330\Omega$ ,  $330\text{pF}$  ESD model.

The high-efficiency step-down DC-DC converter operates from a voltage up to 28V and is protected from load dump transients up to 42V. The device is optimized for high-frequency operation and includes resistor-programmable frequency selection from 220kHz to 2.2MHz to allow optimization of efficiency, noise, and board space based on application requirements. The converter has an internal high-side n-channel switch and uses a low forward-drop freewheeling Schottky diode for rectification. There is a small low-side n-channel switch to maintain fixed frequency under light loads. For lower quiescent current operation requirements, the low side n-channel switch can be disabled to allow skip mode operation under light loads. The converter can deliver up to 2.1A of continuous current at  $105^\circ\text{C}$ . The MAX16984S has an integrated spread-spectrum oscillator to improve EMI performance.

The MAX16984 also includes a USB load current-sense amplifier and configurable feedback adjustment circuit designed to provide automatic USB voltage adjustment to compensate for voltage drops in captive cables associated with automotive applications. The MAX16984 limits the USB load current using both a fixed internal peak current threshold of the DC-DC converter and a user-configurable external USB load current-sense amplifier threshold.

### Applications

- Automotive Radio and Navigation

- USB Port for Host and Hub Applications

- Automotive Connectivity

- Telematics

- Dedicated USB Power Charger

### Benefits and Features

- Integrated DC-DC and USB Host Charge Emulator

Enables 1-Chip Solution Directly from Car Battery to Portable Device

- 4.5V to 28V (42V Load Dump) Operating Voltage

- 5V, 2.5A Output Current Capability

- Low-Q Current Skip and Shutdown Modes

- Soft-Start Reduces Inrush Current

- Low-Noise Features Prevent Interference with AM Band and Portable Devices

- Fixed-Frequency 220kHz to 2.2MHz Operation

- Forced-PWM Option at No Load

- Spread Spectrum for EMI Reduction

- SYNC Input for Frequency Parking

- Optimal USB Power and Communication for Portable Devices

- User-Adjustable Voltage Gain Adjusts Output Between 5V and 6.15V for Cable Compensation

- $\pm 3\%$  Accuracy User-Adjustable USB Current Limit

- $4\Omega$  USB 2.0 480Mbps/12Mbps Data Switches

- Integrated iPod/iPhone/iPad Charge-Detection Termination Resistors

- Supports USB BC1.2 Charging Downstream Port (CDP) and Dedicated Charging Port (DCP) Modes

- Supports Chinese Telecommunication Industry Standard YD/T 1591-2009

- Compatible with USB On-the-Go Specification

- High-Speed Pass-Through Mode

- Robust Design Keeps Vehicle System and Portable Devices Safe in Automotive Environment

- Short-to-Battery Protection on DC-DC Converter

- Short-to-Battery Protection on USB Pins

- $\pm 25\text{kV}$  Air/ $\pm 8\text{kV}$  Contact ISO 10605

- $\pm 15\text{kV}$  Air/ $\pm 8\text{kV}$  Contact IEC 61000-4-2

- $\pm 15\text{kV}$  Air/ $\pm 8\text{kV}$  Contact ( $330\Omega$ ,  $330\text{pF}$ )

- Fault-Indication Active-Low, Open-Drain Output

- Reduced Inrush Current with Soft-Start

- Overtemperature Protection

- $-40^\circ\text{C}$  to  $+125^\circ\text{C}$  Operating Temperature Range

- 28-Pin, 5mm x 5mm, TQFN and Side-Wettable QFN Packages

- 4mm x 4mm, 28-Pin CPQFN and Side-Wettable version available

[Ordering Information](#) and [Typical Operating Circuit](#) appear at end of data sheet.

iPod, iPhone, and iPad are registered trademarks of Apple, Inc.

19-6627; Rev 8; 3/21

**Absolute Maximum Ratings**

|                                                            |                |

|------------------------------------------------------------|----------------|

| IN, D+, D-, CD0, CD1, FBPER,<br>FBMAX, SENSO, FBCAP to GND | -0.3V to +6V   |

| FAULT, FOSC, BIAS, SYNC to GND                             | -0.3V to +6V   |

| D+, D-, to IN                                              | +0.3V          |

| HVD+, HVD- to GND                                          | -0.3V to +18V  |

| SENSN, SENSP to GND                                        | -0.3V to +30V  |

| SENSP to SENSN                                             | -6.0V to +6.0V |

| SUP, SUPSW, ENBUCK to GND                                  | -0.3V to +42V  |

| LX (Note 1)                                                | -0.3V to +42V  |

| SUP to SUPSW                                               | -0.3V to +0.3V |

| BST to GND                                                 | -0.3V to +47V  |

|                                                           |                 |

|-----------------------------------------------------------|-----------------|

| BST to LX (Note 1)                                        | -0.3V to +6V    |

| PGND to GND                                               | -0.3V to +0.3V  |

| Output Short-Circuit Duration                             | Continuous      |

| Continuous Power Dissipation ( $T_A = 70^\circ\text{C}$ ) |                 |

| Side-Wettable QFN (derate 33.3mW/°C above +70°C)          | 2666.7mW        |

| TQFN (derate 34.5mW/°C above +70°C)                       | 2759mW          |

| Operating Temperature Range                               | -40°C to +125°C |

| Junction Temperature                                      | +150°C          |

| Storage Temperature Range                                 | -65°C to +150°C |

| Lead Temperature (soldering, 10s)                         | +300°C          |

| Soldering Temperature (reflow)                            | +260°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Package Thermal Characteristics (Note 2)**

## Side-Wettable QFN

|                                                          |        |

|----------------------------------------------------------|--------|

| Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) | 30°C/W |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )    | 2°C/W  |

## CPQFN

|                                                          |        |

|----------------------------------------------------------|--------|

| Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) | 35°C/W |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )    | 3°C/W  |

**Note 1:** Self-protected against transient voltages exceeding these limits for  $\leq 50\text{ns}$  under normal operation and loads up to the maximum rated output current.

**Note 2:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to [www.maximintegrated.com/thermal-tutorial](http://www.maximintegrated.com/thermal-tutorial).

**Electrical Characteristics**

( $V_{SUP} = V_{SUPSW} = 14\text{V}$ ,  $V_{ENBUCK} = V_{IN} = 3.3\text{V}$ ,  $T_A = T_J = -40^\circ\text{C}$  to  $+125^\circ\text{C}$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ\text{C}$ .) (Note 3)

| PARAMETER                            | SYMBOL         | CONDITIONS                                              | MIN  | TYP  | MAX  | UNITS         |

|--------------------------------------|----------------|---------------------------------------------------------|------|------|------|---------------|

| <b>POWER SUPPLY AND ENABLE</b>       |                |                                                         |      |      |      |               |

| Supply Voltage Range                 | $V_{SUP}$      | Normal operation                                        | 4.5  | 28   |      | V             |

| Load Dump Event Supply Voltage Range | $V_{SUP\_LD}$  | $t < 1\text{s}$ (Note 4)                                |      | 42   |      | V             |

| Supply Current                       | $I_{SUP}$      | $V_{IN} = 0\text{V}$                                    | 6    | 20   |      | $\mu\text{A}$ |

|                                      |                | $V_{SYNC} = 0\text{V}$ , no load, skip mode             | 620  | 950  |      | $\mu\text{A}$ |

|                                      |                | $V_{SYNC} = 3.3\text{V}$ , no load, FPWM mode (Note 4)  | 9    |      |      | mA            |

| BIAS Voltage                         | $V_{BIAS}$     | $5.75\text{V} \leq V_{SUP} = V_{SUPSW} \leq 28\text{V}$ | 4.71 | 5    | 5.31 | V             |

| BIAS Current Limit                   |                |                                                         | 40   | 120  |      | mA            |

| BIAS Undervoltage Lockout            | $V_{UV\_BIAS}$ | $V_{BIAS}$ rising                                       | 3.93 | 4.2  | 4.46 | V             |

| BIAS Undervoltage Lockout Hysteresis |                |                                                         |      | 0.36 |      | V             |

| IN Voltage Range                     | $V_{IN}$       |                                                         | 3.0  | 3.6  |      | V             |

| IN Enable High                       | $V_{IN\_IH}$   |                                                         | 1.6  |      |      | V             |

| IN Enable Low                        | $V_{IN\_IL}$   |                                                         |      | 0.5  |      | V             |

**MAX16984****Automotive High-Current Step-Down Converter with

USB Protection/Host Charger Adapter Emulator****Electrical Characteristics (continued)**

( $V_{SUP} = V_{SUPSW} = 14V$ ,  $V_{ENBUCK} = V_{IN} = 3.3V$ ,  $T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

(Note 3)

| PARAMETER                                             | SYMBOL                       | CONDITIONS                                                                                                       | MIN  | TYP  | MAX  | UNITS     |

|-------------------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------|------|------|------|-----------|

| IN Overvoltage Lockout                                | $V_{IN\_OVLO}$               | $V_{IN}$ rising                                                                                                  | 3.85 | 4.0  | 4.15 | V         |

| IN Input Current                                      | $I_{IN}$                     |                                                                                                                  |      | 5    | 10   | $\mu A$   |

| ENBUCK Enable High                                    | $V_{ENBUCK\_IH}$             |                                                                                                                  | 2.4  |      |      | V         |

| ENBUCK Enable Low                                     | $V_{ENBUCK\_IL}$             |                                                                                                                  |      | 0.6  |      | V         |

| ENBUCK Hysteresis                                     |                              |                                                                                                                  | 0.15 |      |      | V         |

| ENBUCK Input Leakage                                  |                              | $V_{ENBUCK} = 42V$                                                                                               | 0.01 | 1    |      | $\mu A$   |

| <b>D+, D- ANALOG USB SWITCHES</b>                     |                              |                                                                                                                  |      |      |      |           |

| Analog Signal Range                                   |                              | Guaranteed by $R_{ON}$ measurement<br>(Note 4)                                                                   | 0    | 3.6  |      | V         |

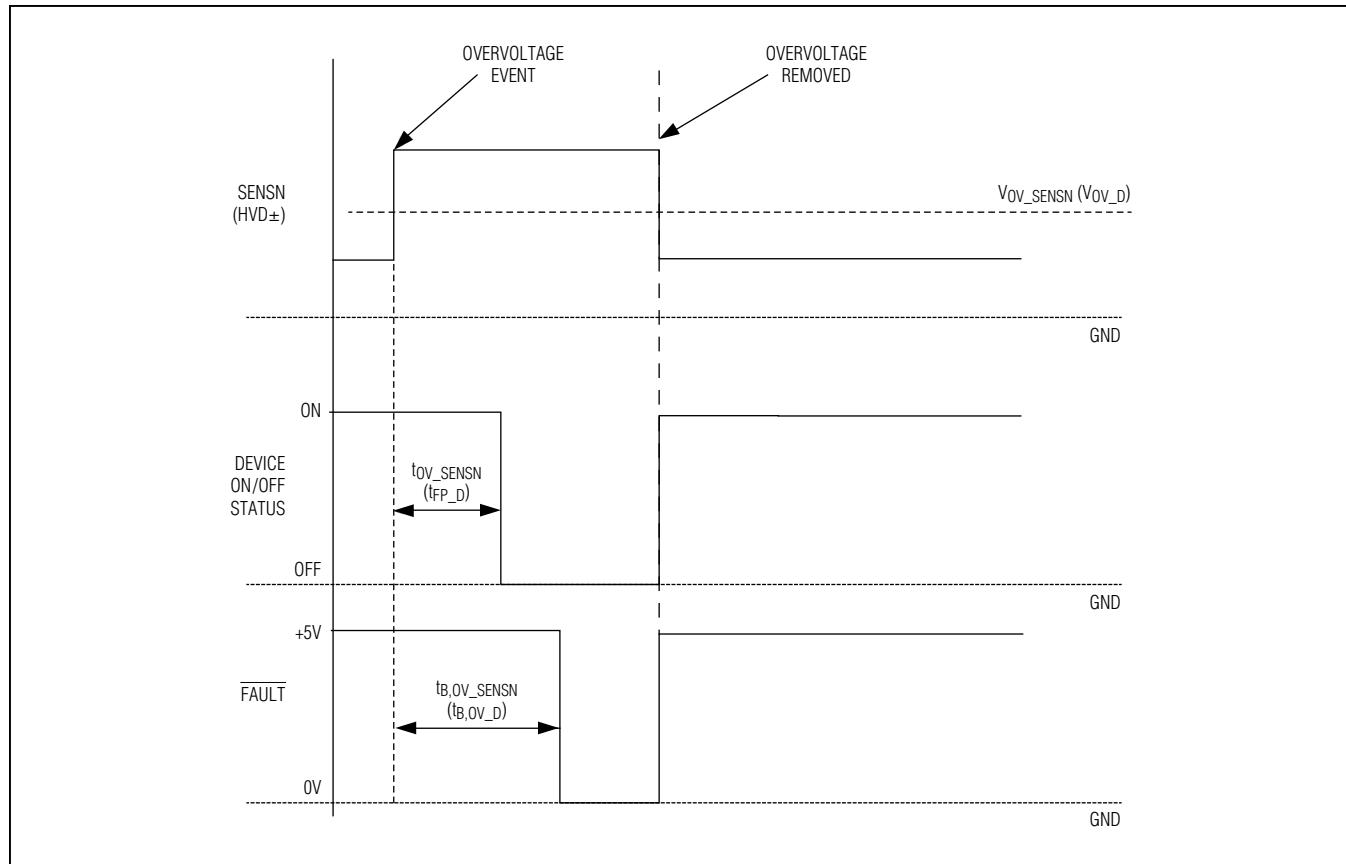

| Protection Trip Threshold                             | $V_{OV\_D}$                  |                                                                                                                  | 3.7  | 3.85 | 4.15 | V         |

| Protection Response Time                              | $t_{FP\_D}$                  | $V_{IN} = 4.0V$ , $V_{HVD\pm} = 3.3V$ to $4.3V$ step,<br>$R_L = 15k\Omega$ on D $\pm$ , delay to $V_{D\pm} < 3V$ | 5    |      |      | $\mu s$   |

| Overvoltage Blanking Timeout Period                   | $t_{B,OV\_D}$                | From overvoltage condition to FAULT asserted                                                                     | 18   | 30   |      | ms        |

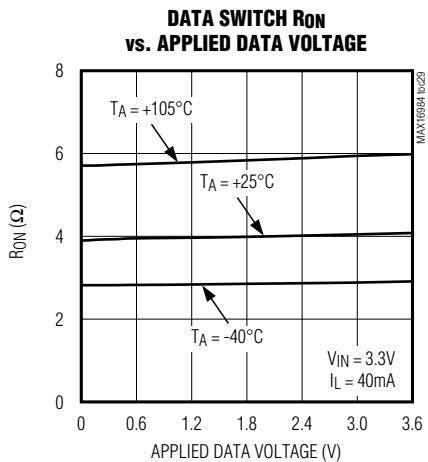

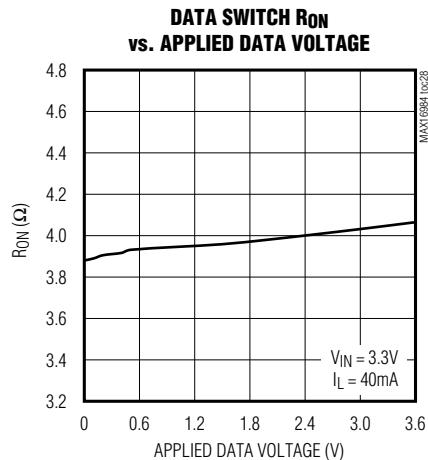

| On-Resistance Switch A                                | $R_{ON\_SA}$                 | $I_L = 5mA$ , $0V \leq V_{D\pm} \leq 3.6V$                                                                       | 4    |      |      | $\Omega$  |

| On-Resistance Match Between Channels Switch A         | $DR_{ON\_SA}$                | $I_L = 5mA$ , $V_{D\_} = 1.5V$ or $3.0V$                                                                         | 10   | 150  |      | $m\Omega$ |

| On-Resistance Flatness Switch A                       | $R_{FLAT(ON)A}$              | $I_L = 5mA$ , $V_{D\_} = 0V$ or $0.4V$                                                                           | 10   |      |      | $m\Omega$ |

| On-Resistance of HVD+/HVD- Short                      | $R_{SHORT}$                  | $V_{DP} = 1V$ , $I_{DM} = 500\mu A$                                                                              | 90   | 180  |      | $\Omega$  |

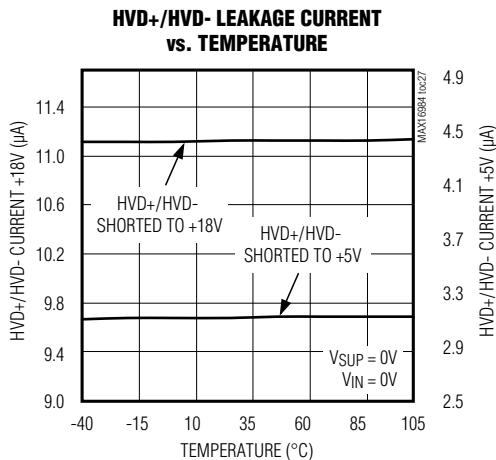

| HVD+/HVD- On-Leakage Current                          | $I_{HVD\_ON}$                | $V_{HVD\pm} = 0V$                                                                                                | -0.1 | 0    | +0.1 | $\mu A$   |

|                                                       |                              | $V_{HVD\pm} = 3.6V$                                                                                              |      | 2.5  |      |           |

| HVD+/HVD- Off-Leakage Current                         | $I_{HVD\_OFF}$               | $V_{HVD\pm} = 18V$ , $V_{D\pm} = 0V$                                                                             | 12   |      |      | $\mu A$   |

| D+/D- Off-Leakage Current                             | $I_{D\_OFF}$                 | $V_{HVD\pm} = 18V$ , $V_{D\pm} = 0V$                                                                             | -1   |      | +1   | $\mu A$   |

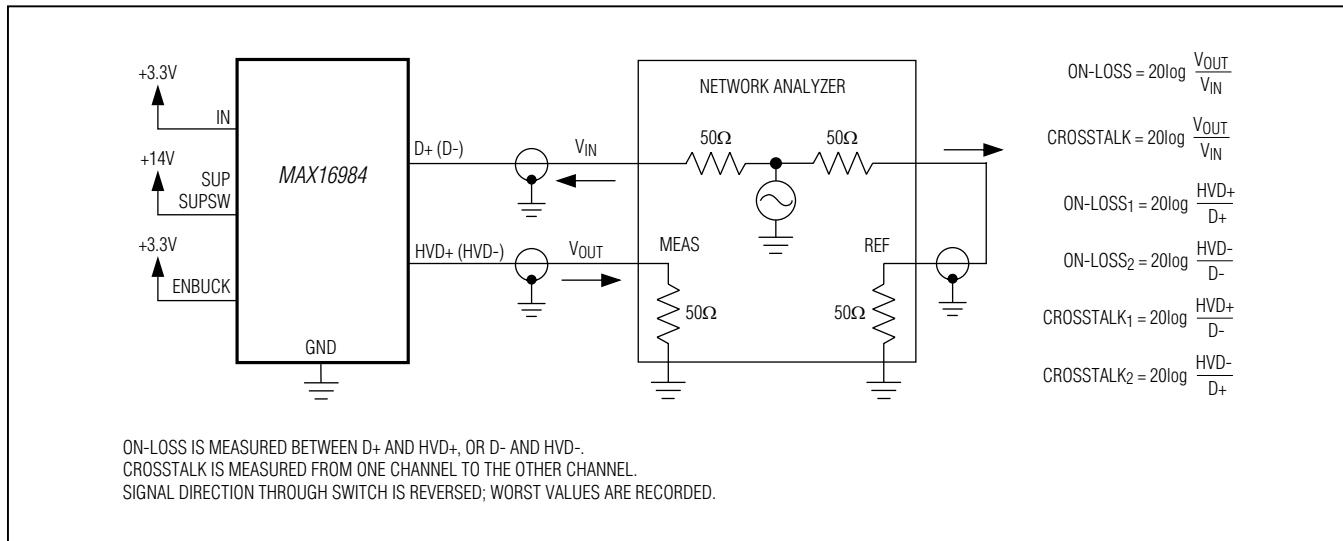

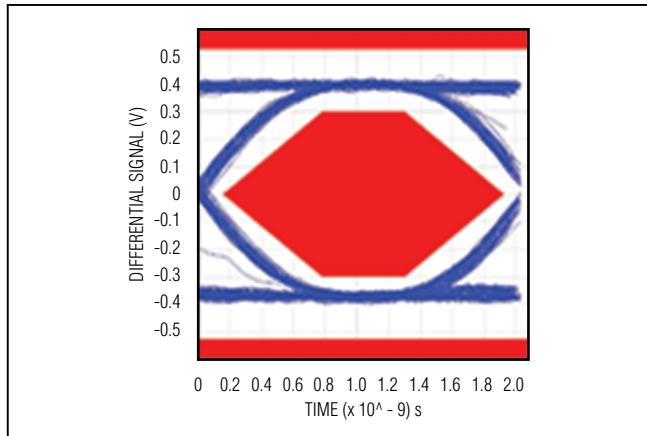

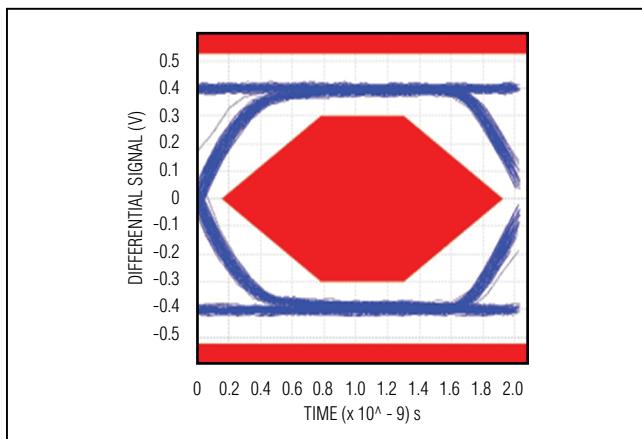

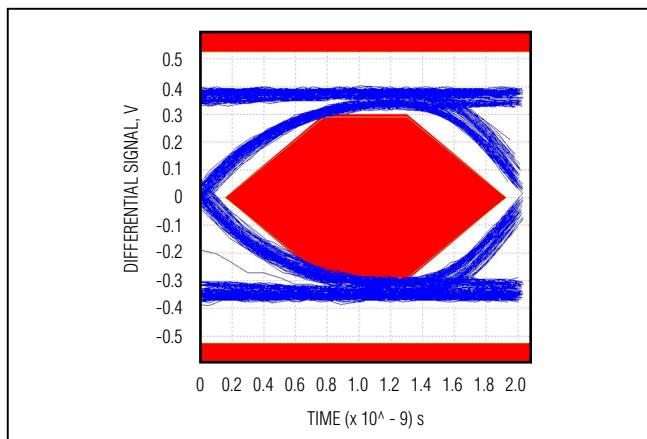

| On-Channel -3dB Bandwidth                             | $BW$                         | $R_L = 50\Omega$ , source impedance $50\Omega$<br>(Figure 3)                                                     | 400  |      |      | MHz       |

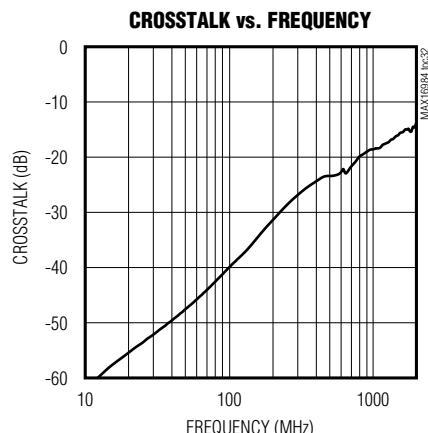

| Crosstalk                                             | $V_{CT}$                     | $R_L = 50\Omega$ , $f = 480MHz$ (Figure 3)                                                                       | -14  |      |      | dB        |

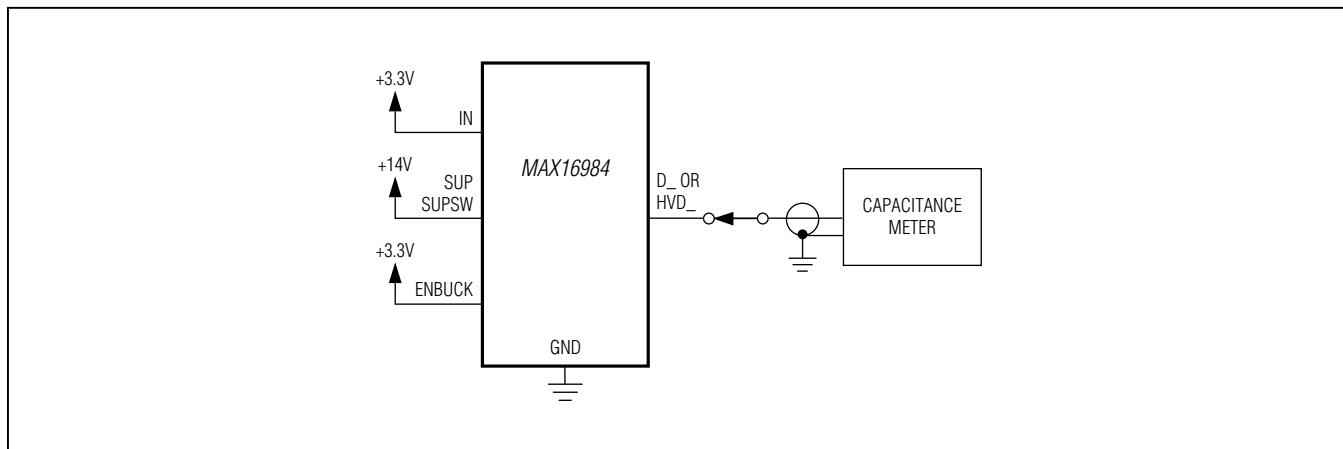

| On-Capacitance Switch A                               | $C_{ON}$                     | $f = 240MHz$ , $V_{BIAS} = 250mV$ ,<br>$V = 500mV_{P-P}$                                                         | 15   |      |      | pF        |

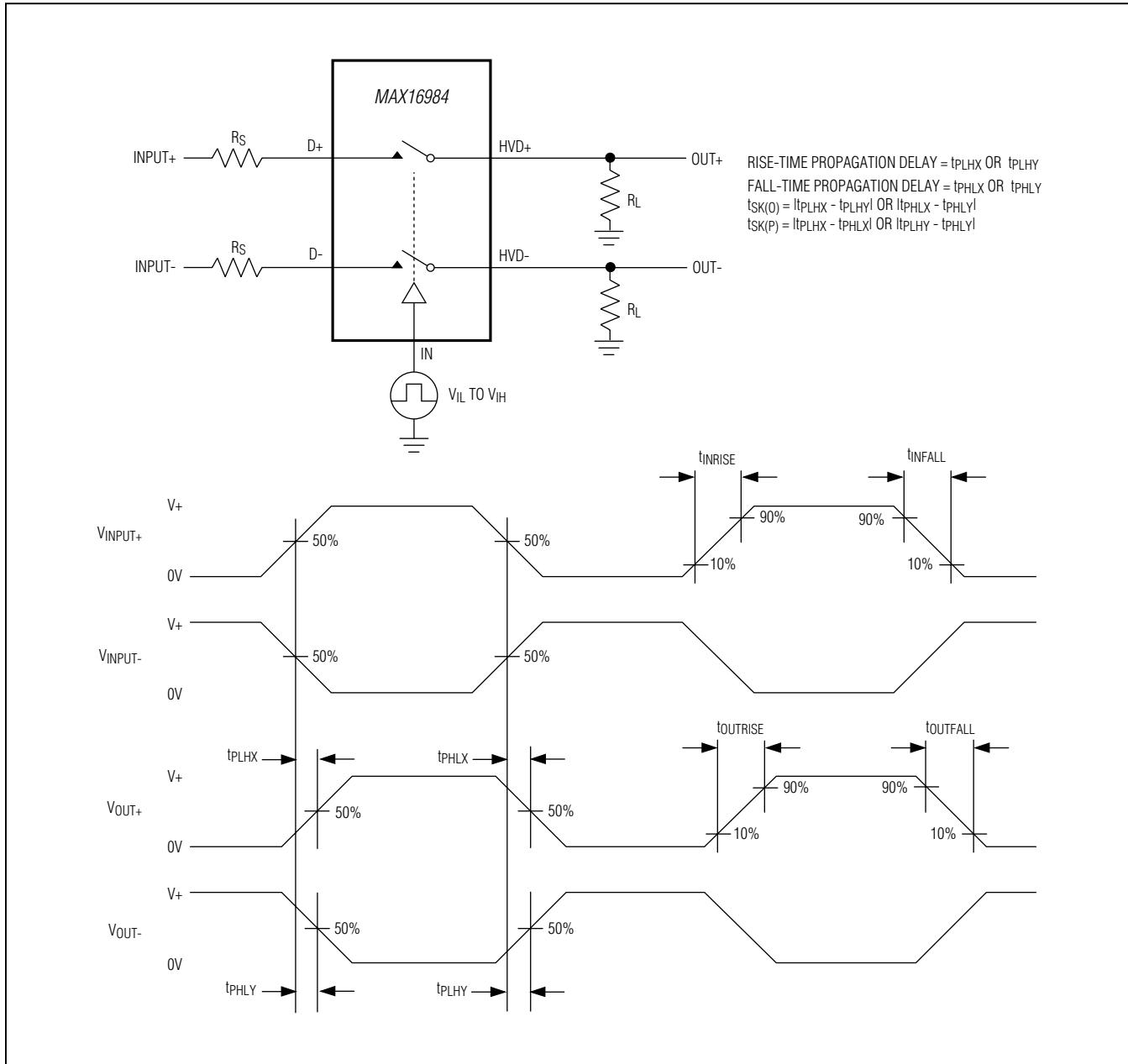

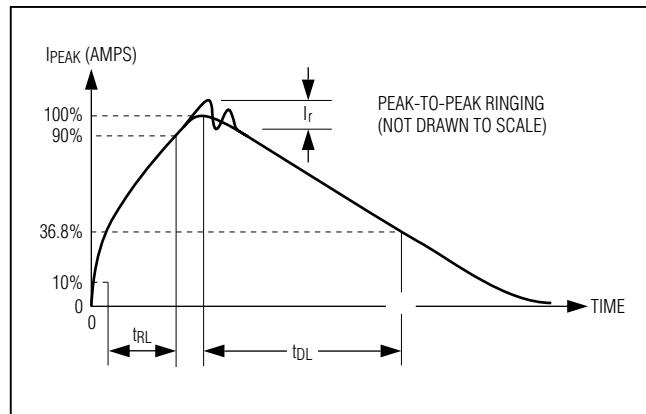

| Rise-Time Propagation Delay                           | $t_{PLH}$                    | $R_S = R_L = 50\Omega$                                                                                           | 200  |      |      | ps        |

| Fall-Time Propagation Delay                           | $t_{PHL}$                    | $R_S = R_L = 50\Omega$                                                                                           | 200  |      |      | ps        |

| Output Skew Between Switches                          | $t_{SK(O)}$                  | Skew between D+ and D- switch,<br>$R_L = 50\Omega$                                                               | 50   |      |      | ps        |

| Output Skew Same Switch                               | $t_{SK(P)}$                  | Skew between opposite transitions in same switch, $R_L = 50\Omega$                                               | 50   |      |      | ps        |

| <b>CURRENT-SENSE AMP (SENSP, SENSN, FBMAX, SENSO)</b> |                              |                                                                                                                  |      |      |      |           |

| FBMAX, SENSO<br>Transconductance                      | $G_{SENSO}$ ,<br>$G_{FBMAX}$ | $I/(V_{SENSP} - V_{SESN})$ ,<br>$V_{SENSP} = 5.25V$                                                              |      | 2.50 |      | $mA/V$    |

MAX16984

Automotive High-Current Step-Down Converter with

USB Protection/Host Charger Adapter Emulator

## Electrical Characteristics (continued)

( $V_{SUP} = V_{SUPSW} = 14V$ ,  $V_{ENBUCK} = V_{IN} = 3.3V$ ,  $T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

(Note 3)

| PARAMETER                                                           | SYMBOL                                     | CONDITIONS                                                                                              | MIN  | TYP   | MAX  | UNITS    |

|---------------------------------------------------------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------|------|-------|------|----------|

| SENSO, FBMAX Voltage Range                                          | $V_{SENSO}$ ,<br>$V_{FBMAX}$               |                                                                                                         | 0    |       | 1.2  | V        |

| Input Differential Voltage Range                                    | $\Delta V_{SENSO}$ ,<br>$\Delta V_{FBMAX}$ | $V_{SENSP} - V_{SENSN}$                                                                                 | 0    |       | 120  | mV       |

| Bandwidth of Transconductance                                       |                                            | Determined by external RC time constant;<br>assumed $R = 10k\Omega$ , and $C = 10pF$                    |      | 1     |      | MHz      |

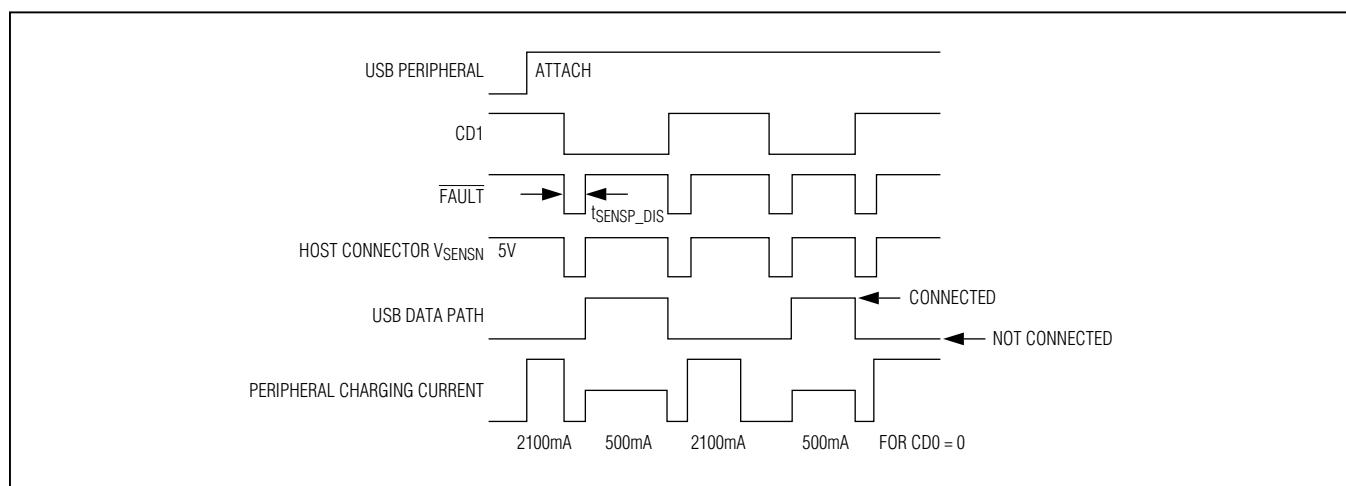

| SENSP Pulldown Resistance                                           | $R_{SENSP\_DIS}$                           | $V_{SENSP} = 5.05V$ , $V_{ENBUCK} = 0V$ or CD1<br>toggle; going into and out of auto-detection<br>modes | 300  | 600   |      | $\Omega$ |

| SENSP Discharge Time Upon<br>CD1 Toggle                             | $t_{SENSP\_DIS}$                           | CD1 toggle; going into and out of auto-<br>detection modes                                              | 0.5  | 1.1   | 2    | s        |

| SENSP Input Bias Current                                            | $t_{SENSP\_LK}$                            | $V_{SENSP} = 5.05V$                                                                                     | 130  | 230   |      | $\mu A$  |

| SENSN Input Bias Current                                            | $t_{SENSN\_LK}$                            | $V_{SENSN} = 5.05V$                                                                                     | 70   | 120   |      | $\mu A$  |

| SENSP Voltage Range                                                 |                                            |                                                                                                         | 3.2  | 28    |      | V        |

| SENSN Overvoltage Threshold                                         | $V_{OV\_SENSN}$                            |                                                                                                         | 6.8  | 7     | 7.1  | V        |

| SENSP Undervoltage Threshold                                        | $V_{UV\_SENSP}$                            |                                                                                                         | 4.64 | 4.75  | 4.81 | V        |

| SENSN Protection Response<br>Time                                   | $t_{OV\_SENSN}$                            |                                                                                                         | 8    |       |      | $\mu s$  |

| SENSN Overvoltage Fault<br>Blanking Timeout Period                  | $t_{B,OV\_SENSN}$                          | From overvoltage condition to FAULT<br>asserted                                                         | 3    | 10    | 20   | ms       |

| <b>SENSO CURRENT LIMIT RELATIONSHIP</b>                             |                                            |                                                                                                         |      |       |      |          |

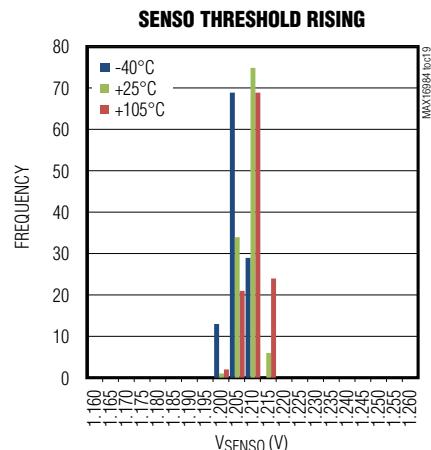

| SENSO ILIMIT Threshold                                              | $V_{TH\_ILIM}$                             | SENSO rising, threshold used to set DC<br>current limit                                                 |      | 1.20  |      | V        |

| Continuous Current-Limit Fault<br>Blanking Timeout                  | $t_{B,ILIM}$                               | From overcurrent condition to FAULT<br>asserted                                                         | 9    | 16.5  | 27   | ms       |

| <b>ANALOG FEEDBACK ADJ</b>                                          |                                            |                                                                                                         |      |       |      |          |

| SENSP Analog Adjustment Gain<br>$\Delta V_{SENSP}/\Delta V_{FBMAX}$ | $A_{SENSP}$                                | $V_{FBPER} = 3.3V$                                                                                      |      | 0.535 |      | V/V      |

|                                                                     |                                            | $V_{FBPER} = 0V$                                                                                        |      | 1.069 |      | V/V      |

| Maximum Feedback Adjustment<br>(compared to SENSP)                  |                                            | $V_{FBPER} = 0V$ , $V_{FBMAX} = 1.2V$                                                                   |      | 25    |      | %        |

| Maximum Feedback Adjustment<br>(compared to SENSP)                  |                                            | $V_{FBPER} = 3.3V$ , $V_{FBMAX} = 1.2V$                                                                 |      | 12.5  |      | %        |

| FBMAX Maximum Adjustment<br>Threshold                               |                                            |                                                                                                         |      | 1.2   |      | V        |

| <b>CD0, CD1, FBPER INPUT</b>                                        |                                            |                                                                                                         |      |       |      |          |

| Input Current                                                       |                                            | $V_{PIN} = 5.5V$ , internal $2M\Omega$ pulldown to GND                                                  | 2.8  | 5.6   |      | $\mu A$  |

| Logic-High                                                          | $V_{IH}$                                   |                                                                                                         | 1.6  |       |      | V        |

| Logic-Low                                                           | $V_{IL}$                                   |                                                                                                         |      | 0.5   |      | V        |

## Electrical Characteristics (continued)

( $V_{SUP} = V_{SUPSW} = 14V$ ,  $V_{ENBUCK} = V_{IN} = 3.3V$ ,  $T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

(Note 3)

| PARAMETER                                    | SYMBOL            | CONDITIONS                                                                                                             | MIN   | TYP   | MAX   | UNITS      |

|----------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------------|

| <b>USB 2.0 HOST CHARGER DETECTION, D+/D-</b> |                   |                                                                                                                        |       |       |       |            |

| Input Logic-High                             | $V_{IH}$          |                                                                                                                        | 2.0   |       |       | V          |

| Input Logic-Low                              | $V_{IL}$          |                                                                                                                        |       | 0.8   |       | V          |

| Data Sink Current                            | $I_{DAT\_SINK}$   | $V_{DAT\_SINK} = 0.25V$ to $0.4V$                                                                                      | 50    | 100   | 160   | $\mu A$    |

| Data Detect Voltage High                     | $V_{DAT\_REFH}$   |                                                                                                                        | 0.4   |       |       | V          |

| Data Detect Voltage Low                      | $V_{DAT\_REFL}$   |                                                                                                                        |       | 0.25  |       | V          |

| Data Detect Voltage Hysteresis               | $V_{DAT\_HYST}$   |                                                                                                                        | 55    |       |       | mV         |

| Data Source Voltage                          | $V_{DAT\_SRC}$    |                                                                                                                        | 0.5   | 0.7   |       | V          |

| Data Source Load Current                     | $I_{DAT\_SRC}$    |                                                                                                                        |       | 200   |       | $\mu A$    |

| <b>iPhone/iPad/DCP CHARGER DETECTION</b>     |                   |                                                                                                                        |       |       |       |            |

| HVD+/HVD- Short Pulldown                     | $R_{PD}$          |                                                                                                                        | 300   | 500   | 750   | k $\Omega$ |

| RP1/RP2 Ratio                                | $R_{T_{RP}}$      |                                                                                                                        | 1.485 | 1.5   | 1.515 | Ratio      |

| RM1/RM2 Ratio                                | $R_{T_{RM}}$      |                                                                                                                        | 0.857 | 0.866 | 0.875 | Ratio      |

| DM1 Comparator Threshold                     | $V_{DM1F}$        | iPhone mode, DM falling (in % of $V_{BIAS}$ )                                                                          | 45    | 46    | 47    | %          |

|                                              |                   | iPad mode, DM falling (in % of $V_{BIAS}$ )                                                                            | 29    | 30    | 31    |            |

| DM2 Comparator Threshold                     | $V_{DM2F}$        | DM falling (in % of $V_{BIAS}$ )                                                                                       | 6     | 7     | 8     | %          |

| DP Comparator Threshold                      | $V_{DPR}$         | iPhone mode, DP rising (in % of $V_{BIAS}$ )                                                                           | 45    | 46    | 47    | %          |

|                                              |                   | iPad mode, DP rising (in % of $V_{BIAS}$ )                                                                             | 55.9  | 57.2  | 58.5  |            |

| DM1 Comparator Debounce Time                 | $t_{DM1}$         | $V_{DM1}$ step from 2.8V to 1.5V                                                                                       | 4     | 9     | 15    | ms         |

| DM2 Comparator Debounce Time                 | $t_{DM2}$         | $V_{DM2}$ step from 2.0V to 0.2V                                                                                       | 1     | 2     | 4     | s          |

| DP Comparator Debounce Time                  | $t_{DP}$          | $V_{DP}$ step from 1.5V to 2.5V                                                                                        | 600   | 1100  | 1800  | $\mu s$    |

| <b>SYNCHRONOUS STEP-DOWN DC-DC CONVERTER</b> |                   |                                                                                                                        |       |       |       |            |

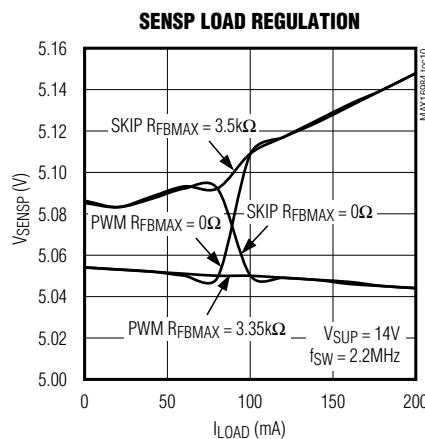

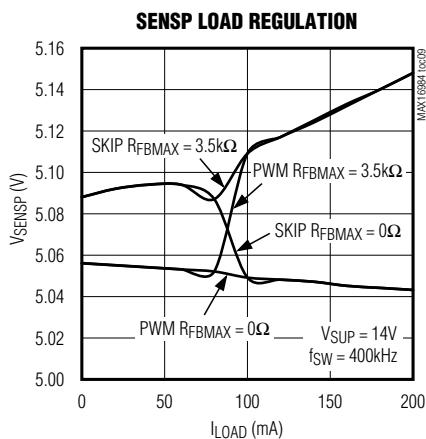

| PWM Output Voltage Accuracy                  | $V_{SENSP}$       | $7V \leq V_{SUPSW} \leq 18V$ , no load, $V_{SYNC} = 3.3V$ or $V_{SYNC} = 0V$ and FPWM mode (see TOC 24)                |       | 5.05  |       | V          |

| Skip Mode Output Voltage Accuracy            | $V_{SENSP\_SKIP}$ | $7V \leq V_{SUPSW} \leq 18V$ , no load, $V_{SYNC} = 0V$ , not in FPWM mode (Note 4)                                    | 4.96  | 5.05  | 5.25  | V          |

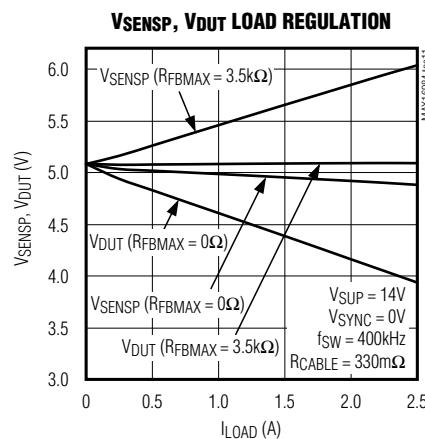

| Load Regulation                              |                   | $7V \leq V_{SUPSW} \leq 18V$ , $0A < I_{LOAD} < 2.1A$ , $V_{FBMAX} = GND$ (Note 4)                                     |       | 1.2   |       | %/A        |

| Output Voltage Accuracy                      | $V_{SENSP}$       | $V_{SUPSW} = 16V$ , $I_{LOAD} = 2.1A$ ; $V_{FBPER} = 0V$ , $V_{FBMAX} = 1.2V$ , $V_{SYNC} = 0V$ and FPWM mode (Note 4) | 6     | 6.15  | 6.3   | V          |

|                                              |                   | $V_{SUPSW} = 8V$ , $I_{LOAD} = 2.1A$ ; $V_{FBPER} = 0V$ , $V_{FBMAX} = 1.2V$ , $V_{SYNC} = 0V$ and FPWM mode (Note 4)  | 6     | 6.15  | 6.3   |            |

| Oscillator Frequency                         | $f_{SW}$          | $R_{FOSC} = 68k\Omega$                                                                                                 | 380   | 440   | 480   | kHz        |

|                                              |                   | $R_{FOSC} = 12k\Omega$                                                                                                 | 2.0   | 2.2   | 2.4   | MHz        |

## Electrical Characteristics (continued)

( $V_{SUP} = V_{SUPSW} = 14V$ ,  $V_{ENBUCK} = V_{IN} = 3.3V$ ,  $T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

(Note 3)

| PARAMETER                          | SYMBOL         | CONDITIONS                             | MIN  | TYP      | MAX | UNITS       |

|------------------------------------|----------------|----------------------------------------|------|----------|-----|-------------|

| Spread-Spectrum Range              |                | MAX16984S only                         |      | 6.5      |     | %           |

| SYNC Switching Threshold Hi        | $V_{SYNC\_HI}$ | Rising                                 |      | 1.4      |     | V           |

| SYNC Switching Threshold Lo        | $V_{SYNC\_LO}$ | Falling                                |      | 0.4      |     | V           |

| SYNC Internal Pulldown             |                |                                        | 200  | 550      |     | k $\Omega$  |

| SYNC Input Clock Acquisition Time  | $t_{SYNC}$     | (Note 4)                               |      | 1        |     | Cycle       |

| High-Side Switch On Resistance     | $R_{ONH}$      | $I_{LX} = 1A$                          | 200  | 450      |     | mA          |

| Low-Side Switch On Resistance      | $R_{ONL}$      | $I_{LX} = 500mA$                       | 1    | 2        |     | $\Omega$    |

| BST Input Current                  | $I_{BST}$      | $V_{BST} - V_{LX} = 5V$ , high side on | 1.2  | 2        |     | mA          |

| LX Current-Limit Threshold         |                | Peak Inductor current                  | 2.7  | 3.6      | 4.7 | A           |

| Skip Mode Peak Current Threshold   | $I_{SKIP\_TH}$ |                                        |      | 300      |     | mA          |

| Negative Current Limit             |                |                                        | 0.65 | 0.85     | 1.1 | A           |

| Soft-Start Ramp Time               | $t_{SS}$       |                                        |      | 9        |     | ms          |

| <b>FAULT OUTPUT</b>                |                |                                        |      |          |     |             |

| Output-High Leakage Current        |                | $V_{FAULT} = 5.5V$                     | -5   |          | +5  | $\mu A$     |

| Output Low Level                   |                | Sinking 1mA                            |      | 0.03     | 0.4 | V           |

| <b>THERMAL OVERLOAD</b>            |                |                                        |      |          |     |             |

| Thermal Shutdown Temperature       |                |                                        |      | 174      |     | $^{\circ}C$ |

| Thermal Shutdown Hysteresis        |                |                                        |      | 30       |     | $^{\circ}C$ |

| <b>ESD PROTECTION (ALL PINS)</b>   |                |                                        |      |          |     |             |

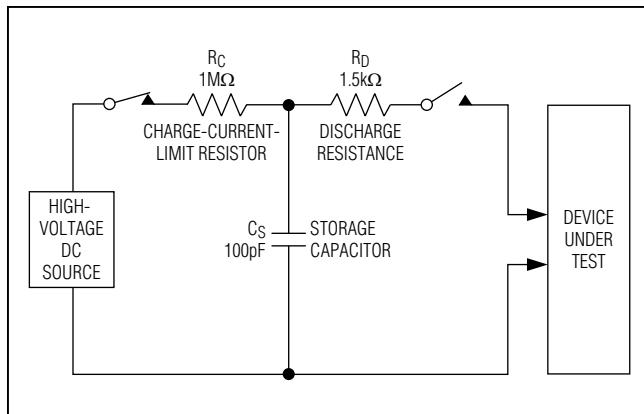

| ESD Protection Level               | $V_{ESD}$      | Human Body Model                       |      | $\pm 2$  |     | kV          |

| <b>ESD PROTECTION (HVD+, HVD-)</b> |                |                                        |      |          |     |             |

| ESD Protection Level               | $V_{ESD}$      | ISO 10605 Air Gap                      |      | $\pm 25$ |     | kV          |

|                                    |                | ISO 10605 Contact                      |      | $\pm 8$  |     | kV          |

|                                    |                | IEC 61000-4-2 Air Gap                  |      | $\pm 15$ |     | kV          |

|                                    |                | IEC 61000-4-2 Contact                  |      | $\pm 8$  |     | kV          |

|                                    |                | 330I, 330pF Air Gap                    |      | $\pm 15$ |     | kV          |

|                                    |                | 330I, 330pF Contact                    |      | $\pm 8$  |     | kV          |

**Note 3:** Specifications with minimum and maximum limits are 100% production tested at  $T_A = +25^{\circ}C$  and are guaranteed over the operating temperature range by design and characterization. Actual typical values may vary and are not guaranteed.

**Note 4:** Guaranteed by design and bench characterization; not production tested.

## Timing Diagrams

Figure 1. Overvoltage Detection on SENSN, HVD+, HVD- Timing Diagram

Figure 2. Peripheral Reset Timing Diagram

## Timing Diagrams (continued)

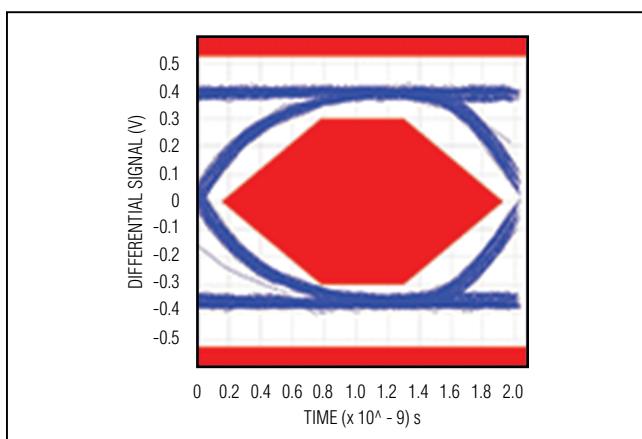

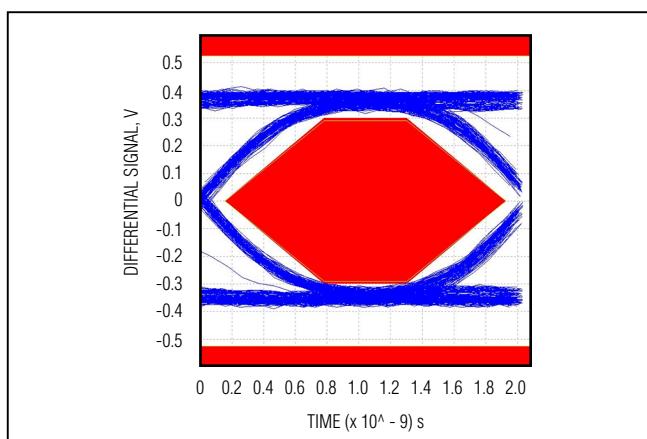

Figure 3. On-Channel -3dB Bandwidth and Crosstalk

Figure 4. On-Capacitance

## Timing Diagrams (continued)

Figure 5. Propagation Delay and Output Skew

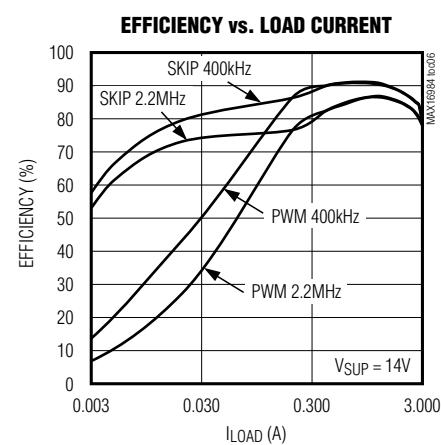

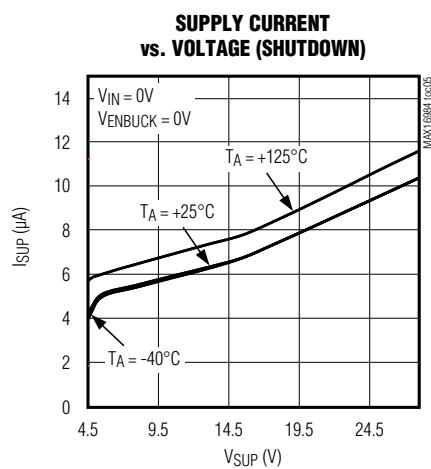

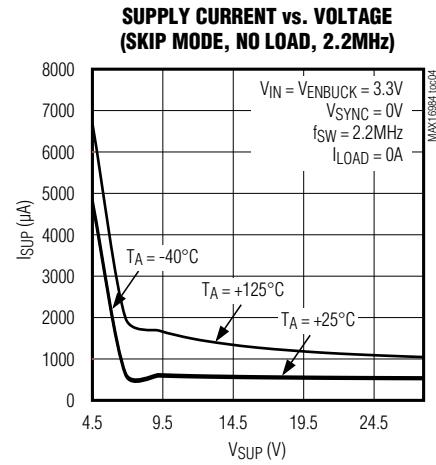

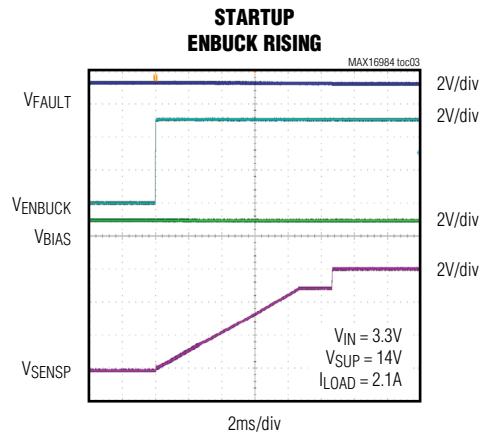

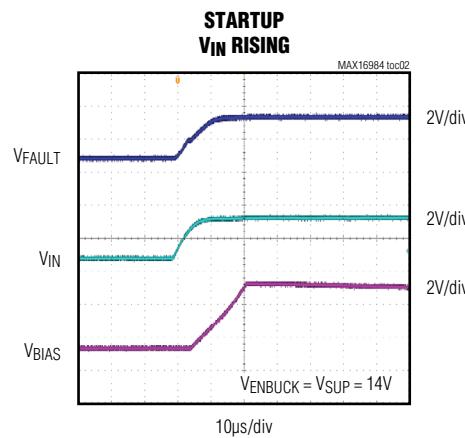

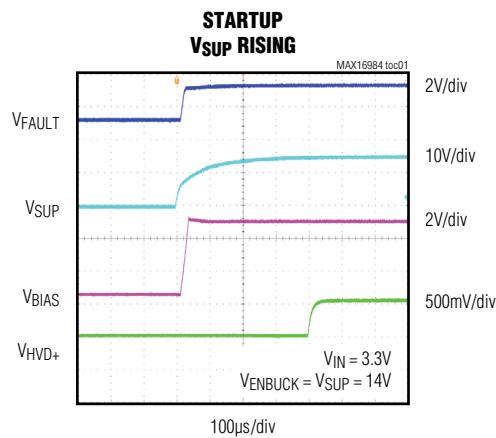

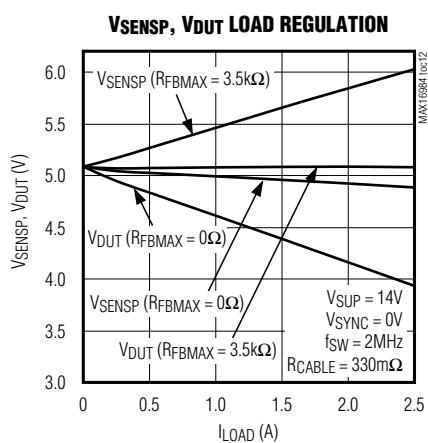

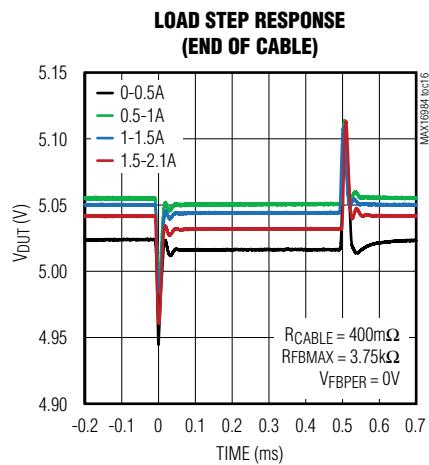

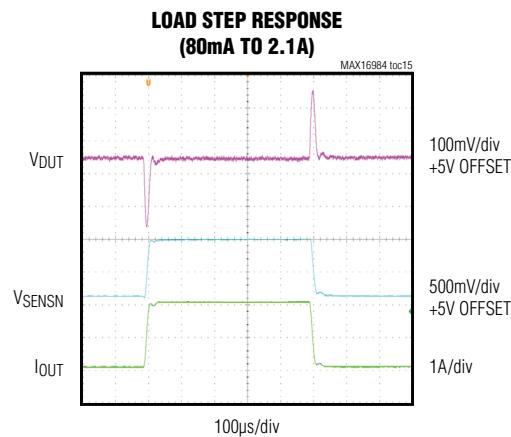

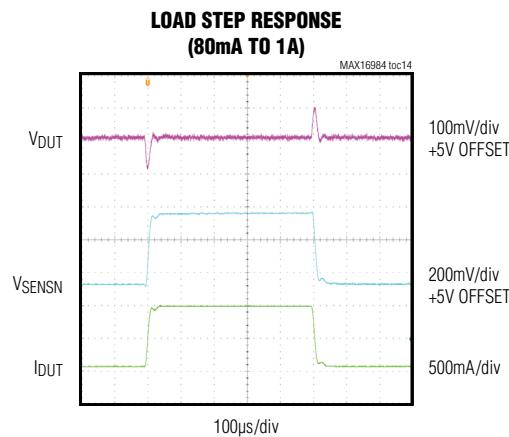

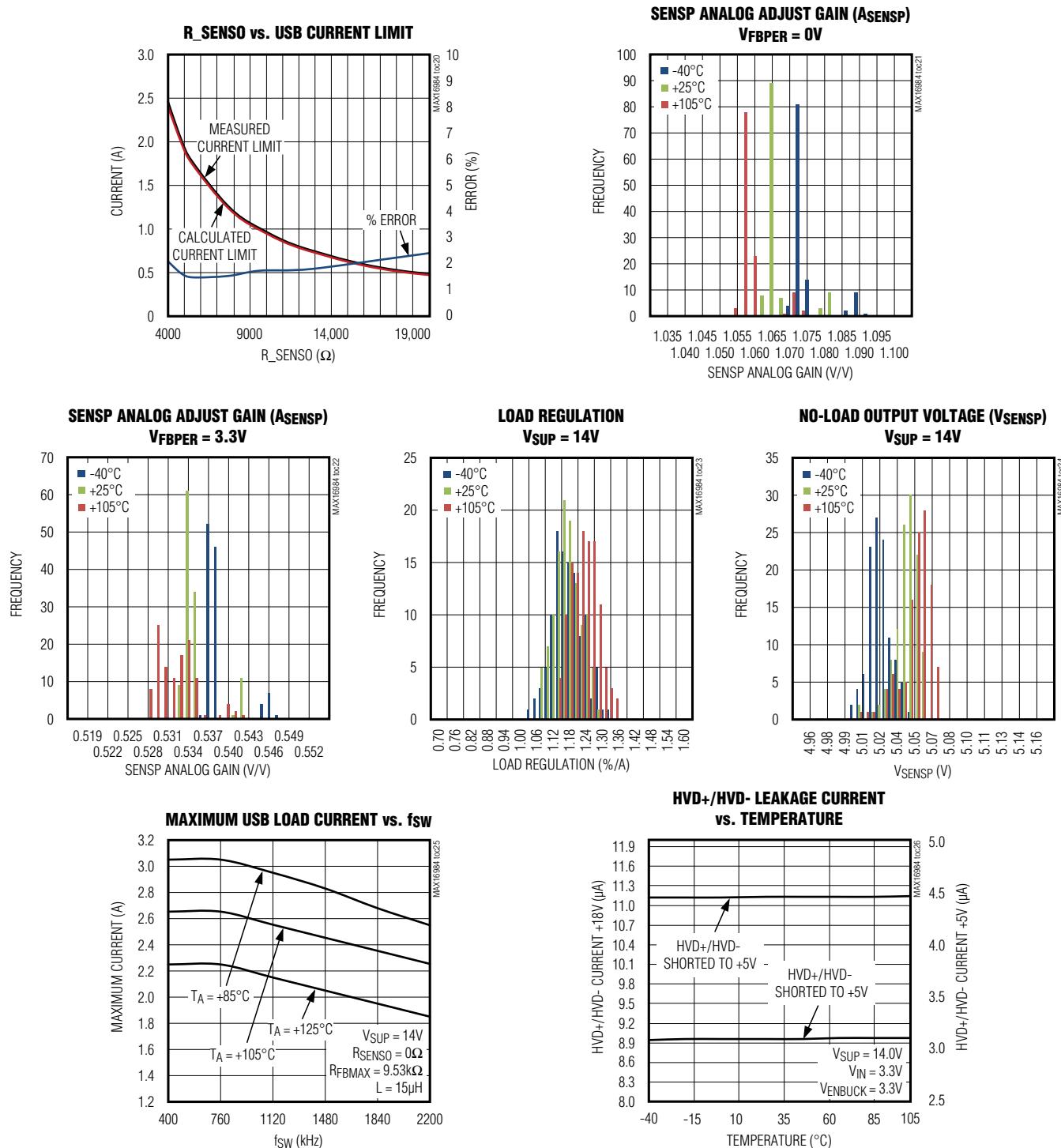

## Typical Operating Characteristics

(TA = +25°C, unless otherwise noted.)

## Typical Operating Characteristics (continued)

(TA = +25°C, unless otherwise noted.)

## Typical Operating Characteristics (continued)

(TA = +25°C, unless otherwise noted.)

## Typical Operating Characteristics (continued)

(TA = +25°C, unless otherwise noted.)

## Typical Operating Characteristics (continued)

(TA = +25°C, unless otherwise noted.)

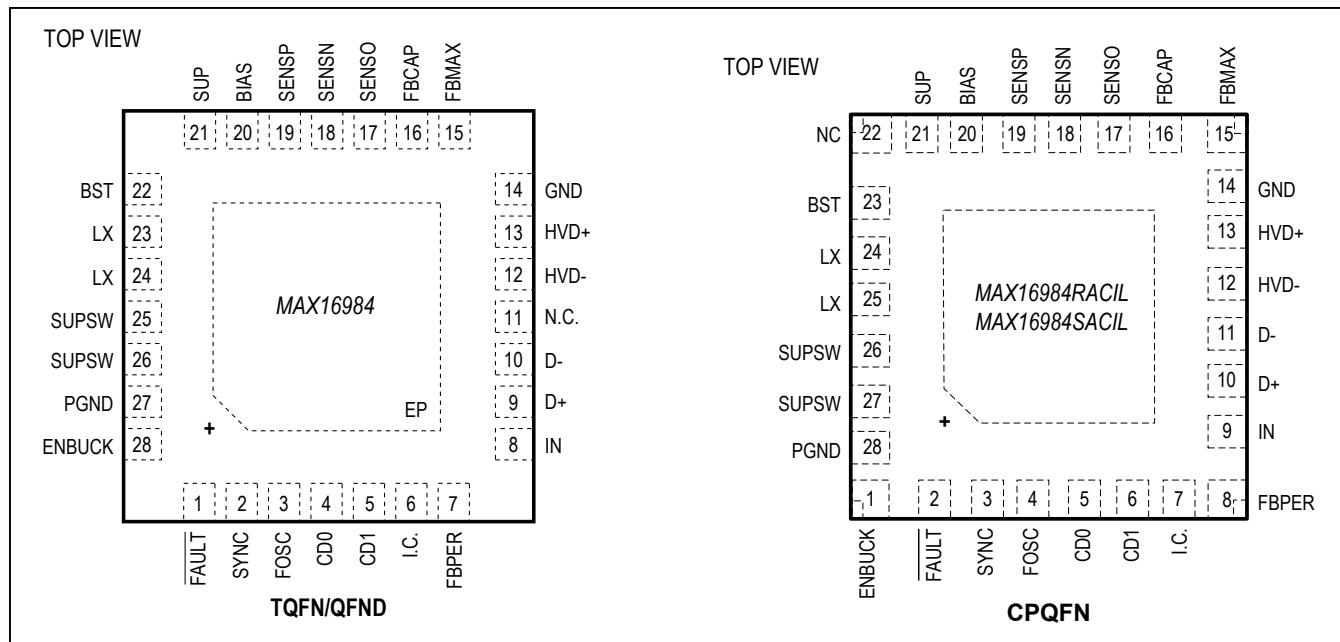

## Pin Configuration

## Pin Description

| PIN          |       | NAME  | FUNCTION                                                                                                                                                                                                                                                    |

|--------------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TQFN/<br>QFN | CPQFN |       |                                                                                                                                                                                                                                                             |

| 1            | 2     | FAULT | Active-Low Open-Drain Fault Indicator Output. Connect a 100kΩ pullup resistor to IN.                                                                                                                                                                        |

| 2            | 3     | SYNC  | Synchronization Input. The device synchronizes to an external signal applied to SYNC. When connected to GND or unconnected, skip mode is allowed under light loads. See Table 1. When connected to a clock source or IN, forced-PWM (FPWM) mode is enabled. |

| 3            | 4     | FOSC  | Resistor-Programmable Switching-Frequency Setting Control Input. Connect a resistor from FOSC to GND to set the switching frequency.                                                                                                                        |

| 4            | 5     | CD0   | Charger Detection Configuration Bit 0                                                                                                                                                                                                                       |

| 5            | 6     | CD1   | Charger Detection Configuration Bit 1                                                                                                                                                                                                                       |

| 6            | 7     | I.C.  | Internal Connection. Must be connected to external GND.                                                                                                                                                                                                     |

| 7            | 8     | FBPER | Digital Input. Used to select voltage feedback adjustment percentage.                                                                                                                                                                                       |

| 8            | 9     | IN    | Logic Enable Input. Connect to I/O voltage of USB transceiver. IN is also used for clamping during overvoltage events on HVD+ or HVD-. Connect a 1μF ceramic capacitor from IN to GND.                                                                      |

| 9            | 10    | D+    | USB Differential Data D+ Input. Connect D+ to low-voltage USB transceiver D+ pin.                                                                                                                                                                           |

| 10           | 11    | D-    | USB Differential Data D- Input. Connect D- to low-voltage USB transceiver D- pin.                                                                                                                                                                           |

| 11           | 22    | N.C.  | No Connection                                                                                                                                                                                                                                               |

## Pin Description (continued)

| PIN          |        | NAME   | FUNCTION                                                                                                                                                                                                                                                  |

|--------------|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TQFN/<br>QFN | CPQFN  |        |                                                                                                                                                                                                                                                           |

| 12           | 12     | HVD-   | High-Voltage-Protected USB Differential Data D- Output. Connect HVD- directly to the USB connector D- pin.                                                                                                                                                |

| 13           | 13     | HVD+   | High-Voltage-Protected USB Differential Data D+ Output. Connect HVD+ directly to the USB connector D+ pin.                                                                                                                                                |

| 14           | 14     | GND    | Analog Ground                                                                                                                                                                                                                                             |

| 15           | 15     | FBMAX  | Current-Sense Amp Output. Connect a resistor and capacitor to GND to set the voltage-adjustment bandwidth and the USB DC current level at which maximum voltage-feedback adjustment is reached.                                                           |

| 16           | 16     | FBCAP  | External Capacitor Connection. Connect a 10pF capacitor to GND.                                                                                                                                                                                           |

| 17           | 17     | SENSO  | Current-Sense Amp Output. Connect a resistor and capacitor to GND to set the maximum USB DC current limit.                                                                                                                                                |

| 18           | 18     | SENSN  | Current-Sense Amp Negative Input. Connect to negative terminal of current-sense resistor.                                                                                                                                                                 |

| 19           | 19     | SENSP  | DC-DC Converter Feedback Input and Current-Sense Amp Positive Input. Connect to positive terminal of current-sense resistor and the main output of the converter. Used for internal voltage regulation loop.                                              |

| 20           | 20     | BIAS   | 5V Linear Regulator Output. Connect a 1 $\mu$ F ceramic capacitor from BIAS to GND. BIAS powers up the internal circuitry.                                                                                                                                |

| 21           | 21     | SUP    | Voltage Supply Input. SUP is the supply pin for the internal linear regulator. Connect a minimum of 4.7 $\mu$ F capacitor from SUP to GND close to the IC.                                                                                                |

| 22           | 23     | BST    | High-Side Driver Supply. Connect a 0.1 $\mu$ F capacitor from BST to LX.                                                                                                                                                                                  |

| 23, 24       | 24, 25 | LX     | Inductor Connection. Connect a rectifying Schottky diode between LX and GND. Connect an inductor from LX to the DC-DC converter output (SENSP).                                                                                                           |

| 25, 26       | 26, 27 | SUPSW  | Internal High-Side Switch-Supply Input. SUPSW provides power to the internal switch. Connect a 4.7 $\mu$ F ceramic capacitor in parallel with a 47 $\mu$ F capacitor from SUPSW to PGND. See the <a href="#">DC-DC Input Capacitor Selection</a> section. |

| 27           | 28     | PGND   | Power Ground                                                                                                                                                                                                                                              |

| 28           | 1      | ENBUCK | Battery-Compatible Enable Input. Drive ENBUCK low/high to disable/enable the switching regulator.                                                                                                                                                         |

| —            | —      | EP     | Exposed Pad. Connect EP to a large-area contiguous copper ground plane for effective power dissipation. Do not use as the only IC ground connection. EP must be connected to GND.                                                                         |

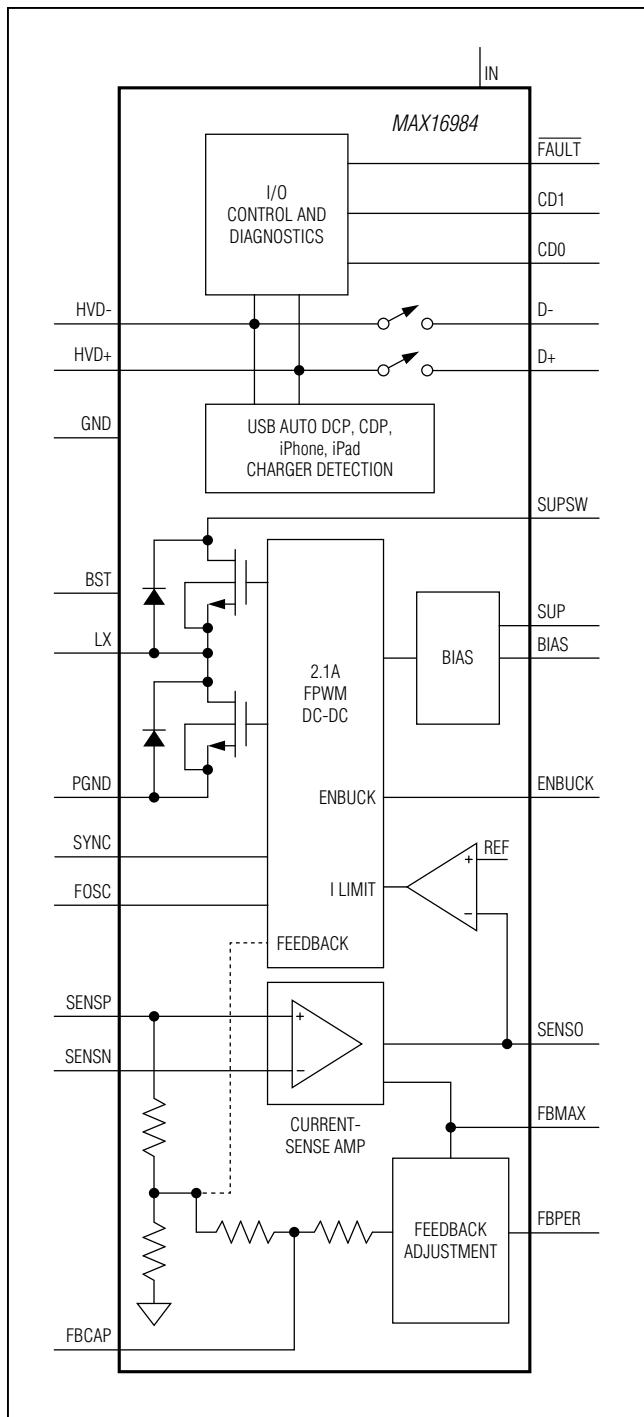

## Functional Diagram

## Detailed Description

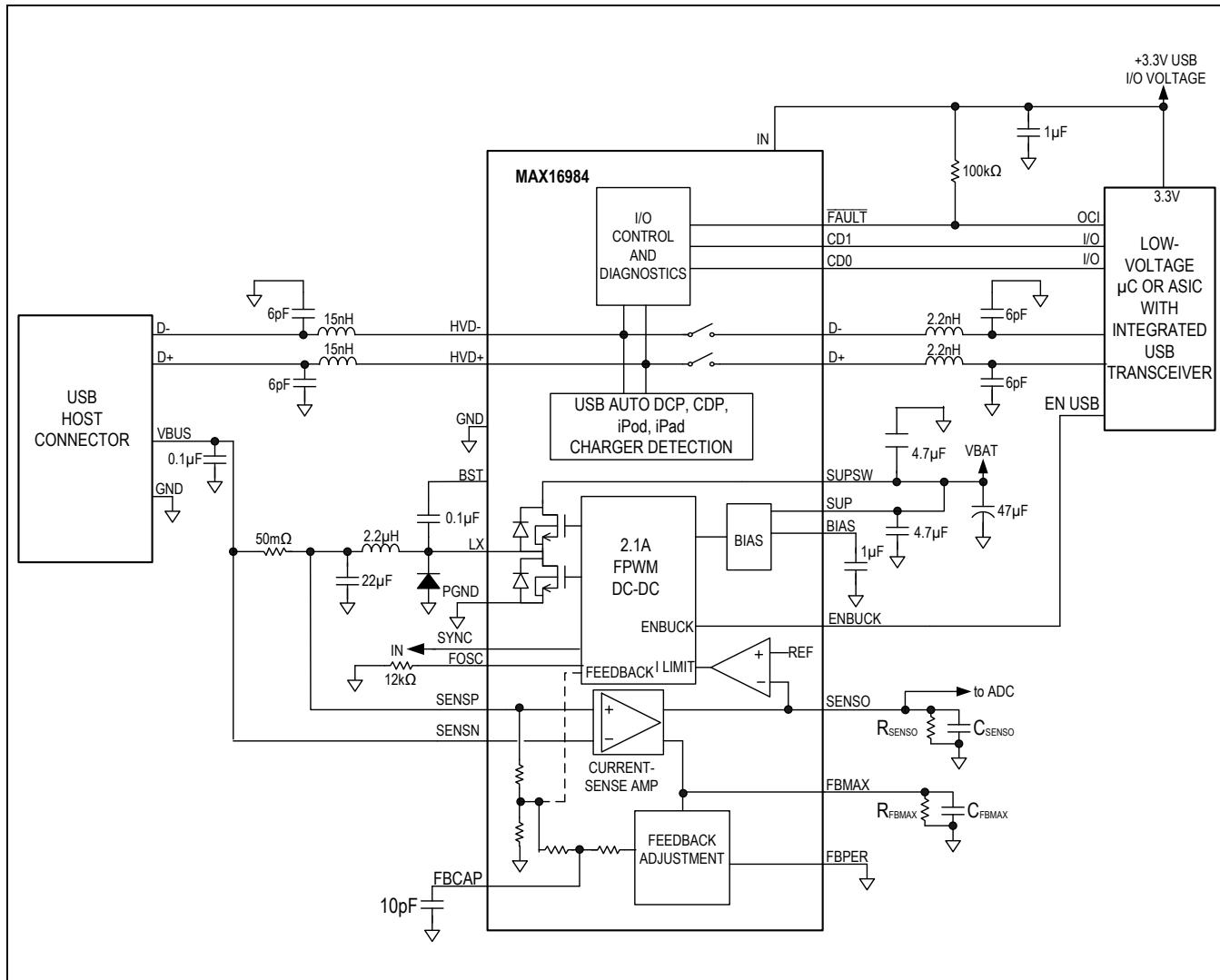

The MAX16984 combines a 5V/2.1A automotive grade step-down converter, a USB host charger adapter emulator, and USB protection switches. It is designed for high-power USB ports in automotive radio, navigation, connectivity, and USB hub applications.

The USB protection switches provide high-ESD and short-circuit protection for the low-voltage internal data lines of the multimedia processor's USB transceiver and support USB Hi-Speed (480Mbps) and USB Full-Speed (12Mbps) pass-through operation. The MAX16984 features integrated host-charger port-detection circuitry adhering to the USB 2.0 Battery Charging Specification BC1.2 and also includes dedicated bias resistors for iPod/iPhone 1.0A and iPad 2.1A dedicated charging modes.

The high-efficiency step-down DC-DC converter operates from a voltage up to 28V and is protected from load-dump transients up to 42V. The device includes resistor-programmable frequency selection from 220kHz to 2.2MHz to allow optimization of efficiency, noise, and board space based on the application requirements. The converter can deliver up to 2.1A of continuous current at 105°C.

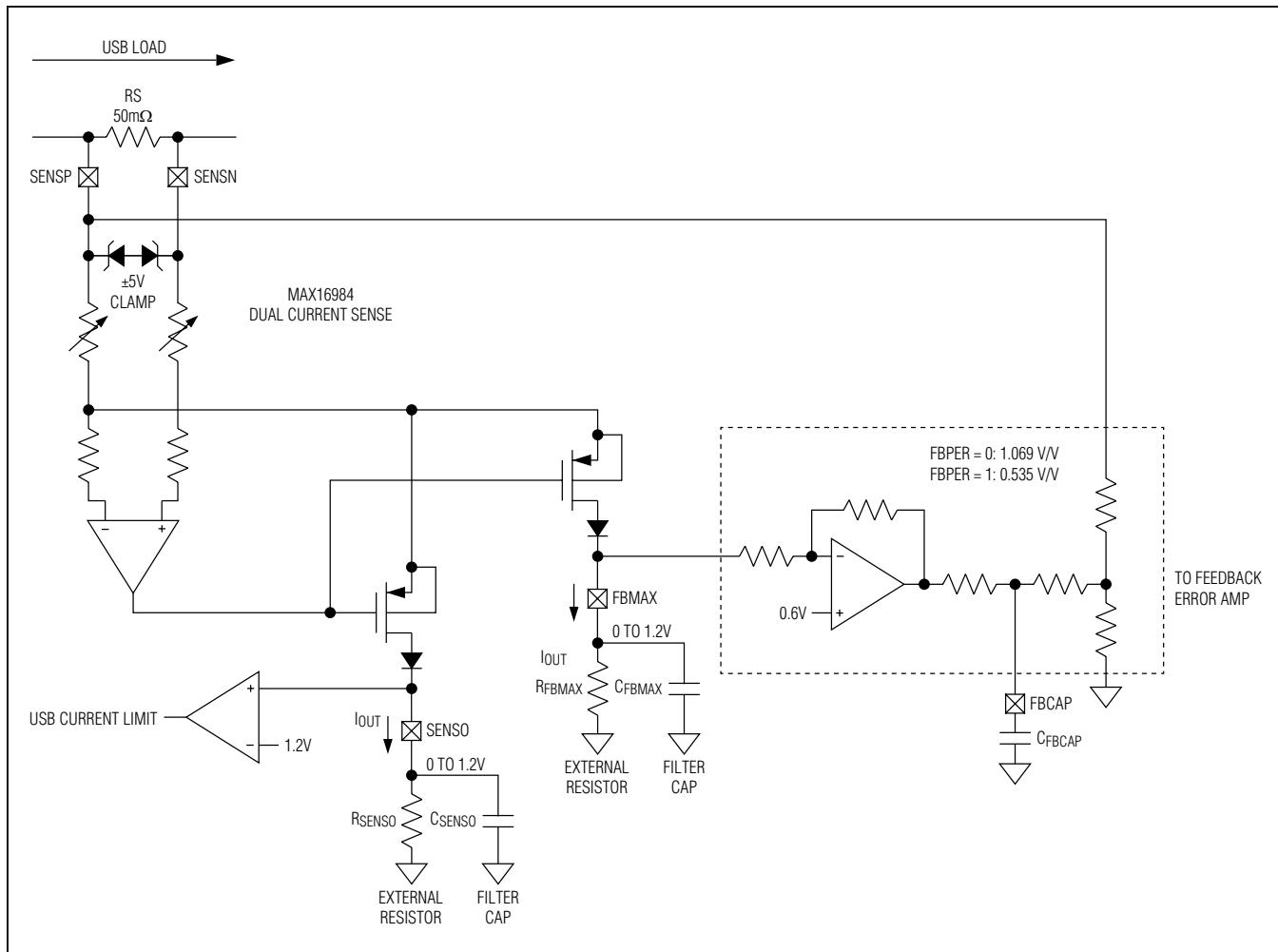

The MAX16984 also includes a high-side current-sense amplifier and configurable feedback-adjustment circuit designed to provide automatic USB voltage adjustment to compensate for voltage drops in captive cables associated with automotive applications.

## Power-Up and Enabling

## System Enable (IN)

IN is used as the main enable to the MAX16984 and is also used to clamp the D+ and D- pins during an ESD and short-to-battery on the HVD+ and HVD- pins. This clamping protects the downstream USB transceiver. The IN pin contains an overvoltage lockout that disables the data switches if IN is above  $V_{IN\_OVLO}$ . Bypass IN with a 1FF capacitor and connect it to the same 3.3V supply as shared with the multimedia processor's USB transceiver. If IN is logic-high, the protection switches are enabled and the USB switches operate in one of four modes per the CD0 and CD1 inputs. If IN is at a logic-low level, SUP power consumption is reduced and the device enters a standby low-quiescent level.

### Linear Regulator Output (BIAS)

BIAS is the output of a 5V linear regulator that powers the internal circuitry for the MAX16984. BIAS is internally powered from SUP and automatically powers up when IN is high and  $V_{SUP}$  exceeds approximately 2.7V. The BIAS output contains an under voltage lockout that keeps the internal circuitry disabled when BIAS is below  $V_{UV\_BIAS}$ . The linear regulator automatically powers down when IN is low and a low 6 $\mu$ A (typ) shutdown current mode is entered. Bypass BIAS to GND with a 1 $\mu$ F ceramic capacitor.

### DC-DC Enable (ENBUCK)

The buck regulator on MAX16984 is activated by driving ENBUCK high and disabled by driving ENBUCK low. ENBUCK is compatible with inputs from automotive battery level down to 3.3V. Connect ENBUCK to the enable output of the USB transceiver controller in a typical application. This allows the USB controller to enable and disable the USB power port via software commands (see the [Functional Diagram](#)). ENBUCK can be directly connected to SUP for dedicated USB power port applications that do not have the USB transceiver controlling ENBUCK.

### Power-On Sequence

For typical radio and navigation applications, the SUP and SUPSW are connected together and connected to the vehicle battery. SUP and IN have no power-up sequence requirements, however, IN is typically enabled after SUP.

### Step-Down DC-DC Regulator

#### Step-Down Regulator

The switching regulator is a high input voltage, constant-frequency, current-mode step-down DC-DC converter delivering output current up to 2.1A. The converter has an internal high-side n-channel switch and uses a low forward-drop freewheeling Schottky diode for rectification. There is a small low-side n-channel switch to maintain fixed frequency under light loads. For lower quiescent current operation requirements, the low-side n-channel switch can be disabled to allow skip mode operation under light loads.

#### Wide Input Voltage Range

The device includes two separate supply inputs, SUP and SUPSW, specified for a wide 4.5V to 28V input voltage range. SUP provides power to the internal BIAS linear regulator, and SUPSW provides power to the internal power switch. Certain conditions such as cold crank can cause the voltage at output to drop below the

programmed output voltage of 5.05V. As the input voltage approaches the output voltage, the device enters dropout and the effective duty cycle of the high-side FET approaches 97%. When the switching regulator is in dropout, the switching frequency is reduced.

#### Output Voltage (SENSP)

The MAX16984 has a precision internal feedback network connected to SENS that is used to set the output voltage of the DC-DC converter. The network nominally sets the average DC-DC converter output voltage to 5.05V when in forced-PWM (FPWM) operation and to 5.09V when operating in skip mode.

#### Soft-Start

When the DC-DC converter is enabled, the regulator soft-starts by gradually ramping up the output voltage from 0 to 5.05V in approximately 9ms. This soft-start feature reduces inrush current during startup. Soft-start is guaranteed into compliant USB loads (see the [USB Loads](#) section).

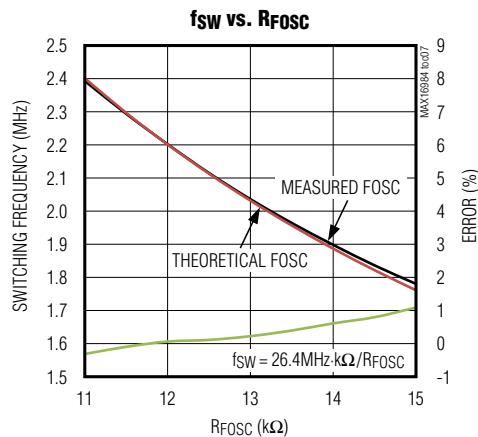

#### Switching Frequency (FOSC, SYNC)

The MAX16984 DC-DC switching frequency can be set by either its internal oscillator or by synchronization to an external clock on the SYNC pin. The internal oscillator frequency ( $f_{SW}$ ) is set by a resistor connected from FOSC to GND (see the [Applications Information](#) section). When operating from its internal oscillator and at no load, the MAX16984 can be operated in FPWM mode or is allowed to enter skip mode operation. See [Table 1](#). When syncing to an external clock, duty cycle must be between 40% and 60%, clock input frequency must be within  $\pm 20\%$  of the resistor-set frequency, and frequency cannot exceed 2.3MHz.

#### Forced-PWM Operation

While operating from a clocked signal on the SYNC pin, the MAX16984 is in FPWM mode operation at all times. While operating from its internal oscillator, FPWM operation can be entered by connecting the SYNC logic-high. The MAX16984 maintains fixed-frequency PWM operation over all load conditions with the SYNC pin logic-high or being clocked by an external clock source. Additionally, the MAX16984 can intelligently enter FPWM mode and exit skip mode ([Table 1](#)) if a portable device is plugged in by determining if the portable device is actively consuming more than 4% of the programmed current limit on SENSO (see the [Current Limit](#) section).

**Table 1. DC-DC Converter Forced-PWM Mode and Skip Mode Operation Truth Table**

| SYNC | CD1 | CD0 | CDP<br>DETECTION              | USB LOAD<br>CURRENT | DCP<br>DETECTION                           | DC-DC CONVERTER<br>OPERATION                      |

|------|-----|-----|-------------------------------|---------------------|--------------------------------------------|---------------------------------------------------|

| 1    | X   | X   | X                             | X                   | X                                          | FPWM Mode: Continuous                             |

| 0    | X   | X   | X                             | $V_{SENDO} < 48mV$  | X                                          | Allow Skip Mode: No USB load detected             |

| 0    | X   | X   | X                             | $V_{SENDO} > 48mV$  | X                                          | FPWM Mode: USB load detected                      |

| 0    | 0   | 1   | (HVD+ or HVD-)<br>$> V_{IH}$  | X                   | X                                          | FPWM Mode: USB device connected to port           |

| 0    | 0   | 1   | (HVD+ and HVD-)<br>$< V_{IL}$ | $V_{SENDO} < 48mV$  | X                                          | Allow Skip Mode: USB device not connected to port |

| 0    | 1   | X   | X                             | $V_{SENDO} < 48mV$  | (HVD- $> V_{DM1F}$ ) & (HVD+ $< V_{DPR}$ ) | Allow Skip Mode: No USB load detected             |

| 0    | 1   | X   | X                             | $V_{SENDO} > 48mV$  | (HVD- $> V_{DM1F}$ ) & (HVD+ $< V_{DPR}$ ) | FPWM Mode: USB load detected                      |

| 0    | 1   | X   | X                             | X                   | (HVD- $> V_{DM1F}$ ) & (HVD+ $> V_{DPR}$ ) | FPWM Mode: USB device detected                    |

| 0    | 1   | X   | X                             | X                   | (HVD- $< V_{DM1F}$ )                       | FPWM Mode: USB device detected                    |

### Intelligent Skip Mode Operation

If the SYNC pin is logic-low, the MAX16984 is allowed to leave FPWM mode and enter skip mode operation (Table 1). While in skip mode, the high-side FET is turned on until the current in the inductor is ramped up to 300mA (typ) peak value and the internal feedback voltage is above the regulation voltage (1.2V typ). At this point, both the high-side and low-side FETs are turned off. Depending on the choice of the output capacitor and the load current, the high-side FET turns on again when SENSP drops below 5.05V (typ).

### Spread-Spectrum Option

Spread spectrum is offered to improve EMI performance of the MAX16984. The MAX16984S has an integrated spread-spectrum oscillator, and the internal operating frequency modulates up to  $\pm 3.25\%$  relative to the internally generated operating frequency, resulting in a total spread-spectrum range of 6.5%. The internal spread spectrum does not interfere with the external clock applied on the SYNC pin. It is active only when the MAX16984 is running with internally generated switching frequency.

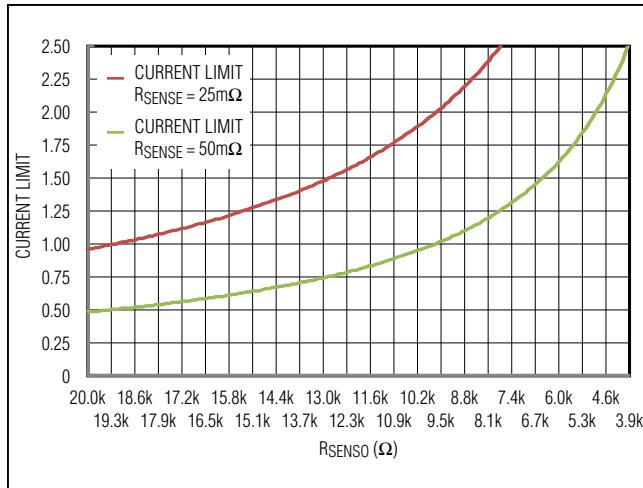

### Current Limit

The MAX16984 limits the USB load current using both a fixed internal peak current threshold of the DC-DC converter and a user-configurable external USB load current-sense amplifier threshold (see the [Current-Sense Output \(SENDO\)](#) section). This allows the current limit to be adjusted between 500mA and 2.1A, depending on the application requirements, and protects the DC-DC converter in the event of a fault. Upon exceeding either the internal or user-programmable current-limit thresholds, the high-side FET is immediately turned off and current-limit algorithms are initiated. When the external current limit lasts for longer than 16.5ms, FAULT asserts. If both the USB current limit is detected and the output voltage exceeds 4.75V for longer than 16.5ms, the DC-DC converter resets. If the internal peak current threshold is exceeded for four consecutive cycles and the output voltage is less than 2.0V, the high-side FET is turned off for 16ms to allow the inductor current to discharge and a soft-start sequence is then initiated.

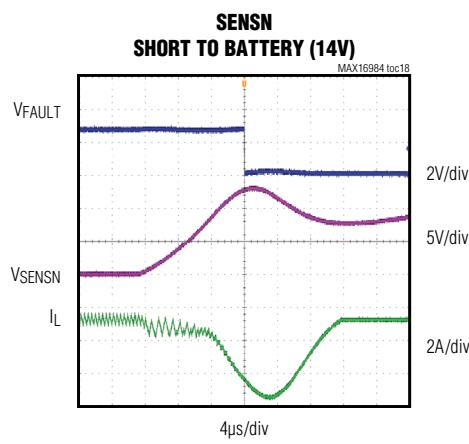

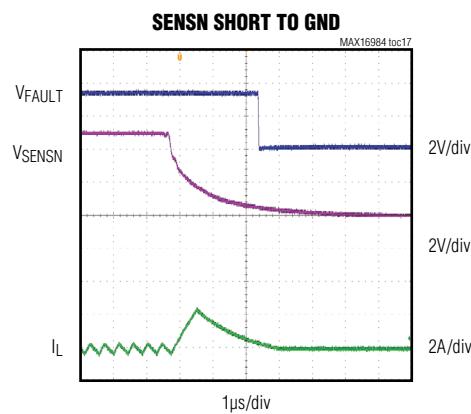

### Output Short-Circuit Protection

The output of the DC-DC converter (SENSP, SENSN) is protected against both short-to-ground and short-to-battery conditions. If a short-to-ground or undervoltage is encountered on SENSP, the device is disabled for 16ms (typ) and then reattempts soft-start. This pattern repeats until the short circuit has been removed.

If a short-to-battery is encountered ( $V_{SENSP} > V_{SEN SN}$ ), the device stops switching and the FAULT pin is asserted after 8μs. The host system should monitor the FAULT output and disable the ENBUCK if multiple FAULT events occur to minimize operating current.

### Thermal-Overload Protection

Thermal-overload protection limits the total power dissipation in the MAX16984. A thermal-protection circuit monitors the die temperature. If the die temperature exceeds +174°C, the device shuts down, allowing it to cool. Once the device has cooled by 30°C, the device is enabled again. This results in a pulsed output during continuous thermal-overload conditions. The thermal-overload protection protects the device in the event of fault conditions. For continuous operation, do not exceed the absolute maximum junction temperature of +150°C.

### USB Current Limit and Captive Cable-Voltage Adjustment

#### Current-Sense Amplifier (SENSP, SENSN)

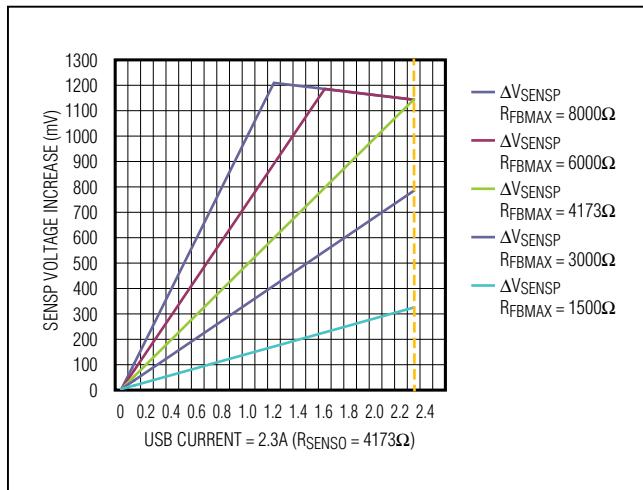

The MAX16984 features an internal USB load current-sense amplifier to monitor the load current being pulled by the USB port. The ( $V_{SENSP} - V_{SEN SN}$ ) voltage sets an output current at both SENSO and FBMAX equal to 2.5mA/V. Choose a sense resistor from SENSP to SENSN to limit the differential voltage across SENSP-SENSN to 120mV.

#### Current-Sense Output (SENSO)

A resistor to ground on the SENSO pin results in a voltage representing the USB load current. Upon crossing the fixed internal threshold of 1.2V, the high-side FET is immediately turned off, the low-side FET is turned on, and the USB load current is reduced until the voltage at SENSO falls below the 1.2V threshold. If the load current exceeds the USB current limit for longer than 16.5ms, a FAULT is asserted. For proper functionality, limit the voltage at SENSO to 2.0V.

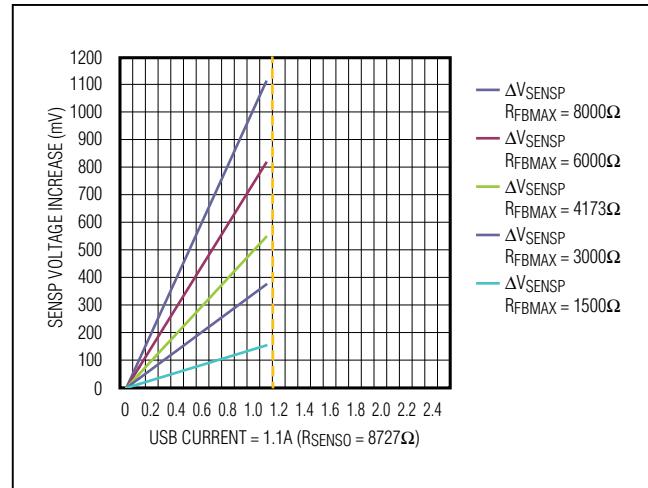

#### Current Feedback Adjustment

The MAX16984 has multiple user-configurable features to adjust the DC-DC converter output voltage higher to help overcome voltage drops associated with captive

cables in automotive applications. The feature set allows for the user to set the maximum amount the voltage can be raised and set the desired operating bandwidth of the adjustment.

#### Feedback Percentage (FBPER)

The FBPER pin allows the user to set the maximum allowable percentage to either +25% ( $V_{FBPER} = 0V$ ) or +12.5% ( $V_{FBPER} = 3.3V$ ). Set the FBPER pin such that the percentage of voltage adjustment needed is minimized for the application in the event of a fault.

#### Maximum Feedback Adjustment (FBMAX)

A resistor to ground on the FBMAX pin results in a voltage representing the USB load current. The output voltage of the DC-DC converter increases linearly as the voltage at FBMAX increases up to 1.2V to maintain voltage at the portable device ( $V_{DUT}$ ) that meets USB specification. Upon crossing the fixed internal threshold of 1.2V, the DC-DC output voltage remains unchanged. For proper functionality, limit the voltage at FBMAX to 2.0V. A capacitor to GND is also needed on the FBMAX pin to limit the bandwidth of the feedback adjustment. See [Figure 6](#).

### USB Protection Switches

#### HVD+ and HVD- Protection

The MAX16984 provides automotive grade ESD and short-circuit protection for the low-voltage internal USB data lines of high-integration multimedia processors. HVD+/HVD- protection consists of ESD and OVP (overvoltage protection) for both 12Mbps and 480Mbps USB transceiver applications. This is accomplished with an extremely low-capacitance, high-voltage FET in series with the D+ and D- data paths.

No external ESD protection diodes are required when using the MAX16984. The HVD+ and HVD- ESD protection features include protection to  $\pm 15kV$  Air/ $\pm 8kV$  Contact on the HVD+ and HVD- outputs to the IEC 61000-4-2 model and  $330\Omega$ ,  $330pF$  ESD model.

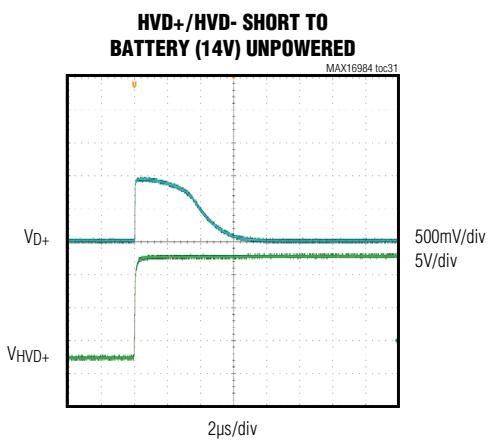

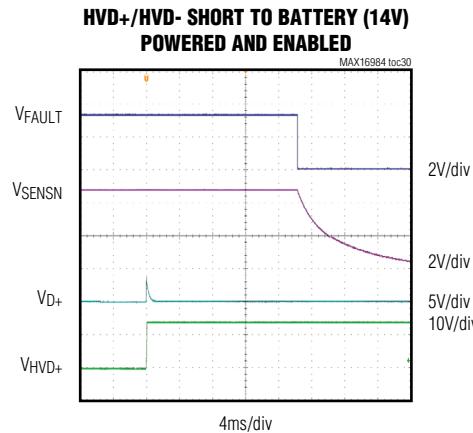

The HVD+ and HVD- short-circuit protection features include short to +18V battery as well as short to +5V on the protected HVD+ and HVD- outputs. This is provided to protect against shorted conditions in the vehicle harness and prevent damage to the low-voltage USB transceiver. Short-to-GND protection is provided by the upstream USB transceiver.

Figure 6. USB Current-Sense Amplifier, USB Current Limit, and USB Voltage Feedback Adjustment

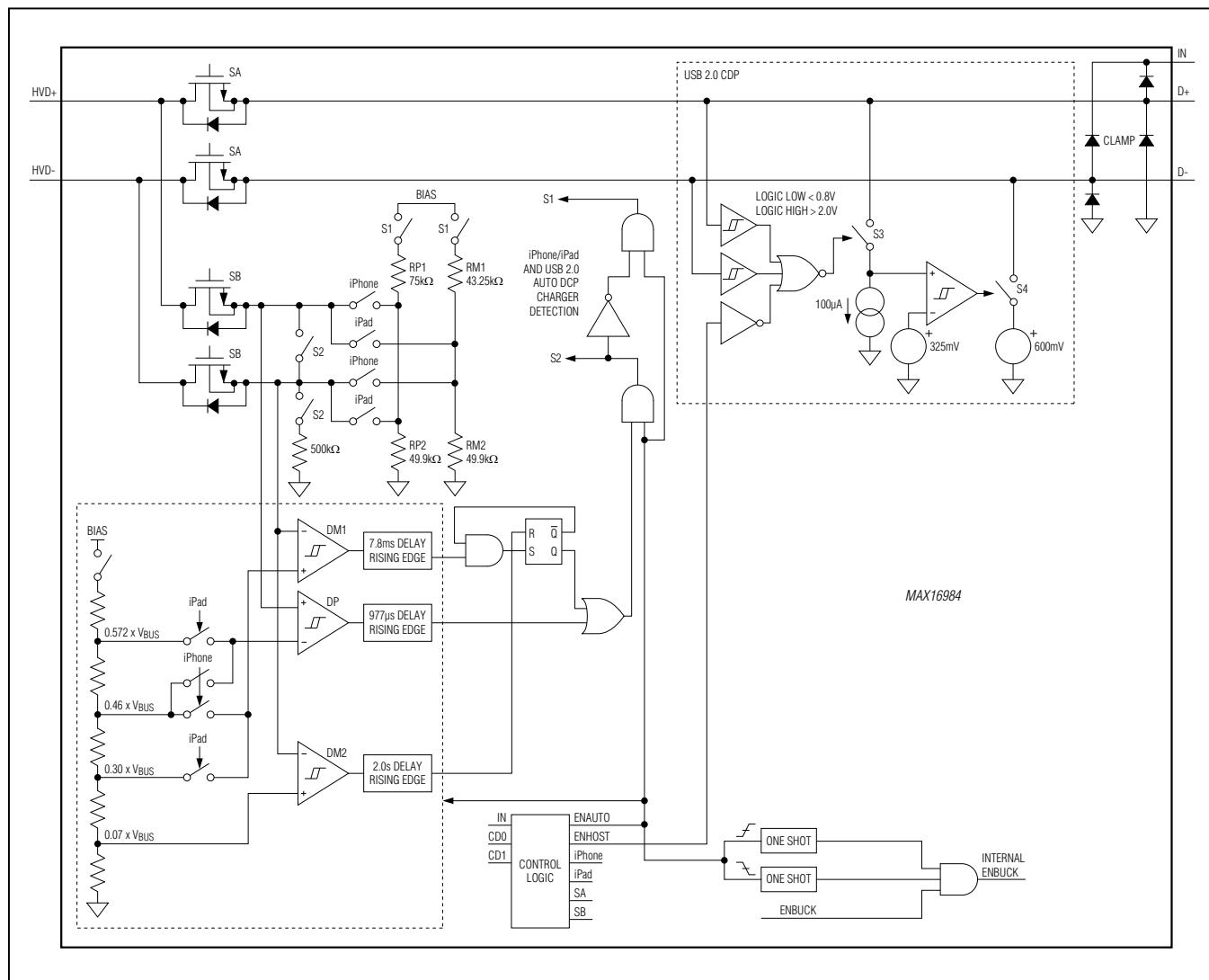

## USB Host Adapter Emulator

The Hi-Speed USB protection switches integrate the latest USB-IF Battery Charging Specification Revision 1.2 CDP and DCP circuitry, both the 1.0A and 2.1A resistor bias options for Apple-compliant devices, and the industry legacy USB D+ short to D- charge detection using data line pullup.

### HVD+ and HVD- Operation (CD1, CD0)

The MAX16984 features dual digital inputs, CD1 and CD0, for mode selection of the HVD+ and HVD- pins (Table 2). Connect CD1/CD0 to a logic-level low for normal USB Hi-Speed (HS) pass-through mode. Connect CD1/CD0 to

a logic-level low/high for USB low-speed (LS) and USB full-speed (FS) data transmission and charging downstream port (CDP) mode. See Table 1 for CDP mode and Figure 7 for a detailed description of all modes.

### Hi-Speed Pass-Through Mode (CD1/CD0 = low/low)

HS pass-through mode provides true pass-through operation for USB HS (480Mbps) data signals and disables the CDP circuitry. Place the device into this mode when the USB transceiver requests to enter HS mode. See Table 2.

Table 2. Data Switch Mode Truth Table

| DEVICE INPUTS |     |     | INTERNAL LOGIC |    |        |        | DATA SWITCH MODE                   |

|---------------|-----|-----|----------------|----|--------|--------|------------------------------------|

| IN            | CD1 | CD0 | SA             | SB | ENAUTO | ENHOST |                                    |

| 0             | X   | X   | X              | X  | X      | X      | Off                                |

| 1             | 0   | 0   | 1              | 0  | 0      | 0      | HS Pass-Through                    |

| 1             | 0   | 1   | 1              | 0  | 0      | 1      | FS/LS with CDP                     |

| 1             | 1   | 0   | 0              | 1  | 1      | 0      | DCP/Apple 2.1A with Auto Detection |

| 1             | 1   | 1   | 0              | 1  | 1      | 0      | DCP/Apple 1.0A with Auto Detection |

Figure 7. Data Switches and Host Adapter Emulator

**Low-Speed/Full-Speed Mode with Charging Downstream Port (CD1/CD0 = low/high)**

After a USB-compliant portable device detects V<sub>BUS</sub>, it is allowed to check if the host device is a CDP by applying a voltage to HVD+ and checking the voltage on HVD-. At this time, it is assumed that HVD+ and HVD- are logic-low, which means that the voltage is less than 0.8V. Then the port-detection circuit is enabled and switch 3 is on ([Figure 7](#)). The portable device then drives HVD+ to 0.6V (typ). The comparator closes switch 4 and the HVD- line is then driven to 0.6V (typ). The portable device can now detect that it is connected to a charging port.

When an FS device connects, it pulls the HVD+ line logic-high to a voltage greater than 2V. Then switch 3 opens, the positive input of the comparator is forced to zero, and switch 4 is also opened. Because HVD- is low, the portable device detects that it is connected to a CDP.

When a LS device connects, it pulls the HVD- line logic-high (after it has stopped driving HVD+ to 0.6V). Because HVD+ stays low, the portable device detects that it is connected to a CDP.

When the portable device has connected in LS or FS mode, either D+ or D- is logic-high upon enumeration, which disables the charger-detect circuit. A delay is implemented that closes switch 3 after HVD+ and HVD- are logic-low longer than 100 $\mu$ s. This ensures that switch 3 stays off when the logic-high states of D+ and D- do not overlap.

If a Hi-Speed-capable device connects to the port and CD1/CD0 = low/high, it can detect that it is connected to a CDP. Upon enumeration, and before entering HS mode, the host system microprocessor must query the USB transceiver to determine if HS mode is needed. If so, it must drive the CD0 input low to disable the port-detection circuit and enter USB HS mode. The host system microprocessor must also query the USB transceiver to detect when the HS portable device is disconnected or no longer in HS mode. Once detected, it must drive the CD0 input high to re-enable the port-detection circuit for the next connection sequence. This is needed as the HS differential logic levels on HVD+ and HVD- are below 500mV.

**USB-IF Dedicated Charging Port and Apple 2.1A with Auto Detection (CD1/CD0 = high/low)**

The MAX16984 features an iPad/DCP auto-detection mode for emulating dedicated iPad 2.1A charging and USB-IF DCPs. CD1/CD0 must be set high/low to activate iPad/DCP auto-detection mode. In this mode, the high-voltage-protected HVD+ and HVD- pins are disconnected from the low-voltage D+ and D- pins and are initially connected to internal resistor-dividers to

provide the proper Apple-compliant iPad bias voltage. Data switches SA are opened and switches SB are closed ([Figure 7](#)). Initially, the iPad termination resistors are presented on the HVD+/- pins, the MAX16984 then monitors the voltages at HVD+ and HVD- to determine the type of device attached.

If the voltage at HVD- is +1.5V (typ) (V<sub>BUS</sub> x 0.3) or higher, and the voltage at HVD+ is +2.86V (typ) (V<sub>BUS</sub> x 0.572) or lower, the state remains unchanged and the iPad termination resistors remain present.

If the voltage at HVD- is forced below the +1.5V (typ) (V<sub>BIAS</sub> x 0.3) threshold or if the voltage at HVD+ is forced higher than the +2.86V (typ) (V<sub>BIAS</sub> x 0.572) threshold, the internal switch disconnects HVD- and HVD+ from the resistor-divider (iPad switch open) and HVD+ and HVD- are shorted together for dedicated charging mode (S2 closed).

Once the charging voltage is removed, the short between HVD+ and HVD- is disconnected and the operation is restarted with the internal resistor-divider bias voltages appearing on HVD+ and HVD-.

**USB-IF Dedicated Charging Port and Apple 1A with Auto Detection (CD1/CD0 = high/high)**

The MAX16984 features an iPhone/DCP auto-detection mode for emulating dedicated iPhone 1.0A charging and USB-IF DCPs. CD1/CD0 must be set high/high to activate iPhone/DCP auto-detection mode. In this mode, the high-voltage-protected HVD+ and HVD- pins are disconnected from the low-voltage D+ and D- pins and are initially connected to internal resistor-dividers to provide the proper Apple-compliant iPhone bias voltage. Data switches SA are opened and switches SB are closed ([Figure 7](#)). Initially, the iPhone termination resistors are presented on the HVD+/- pins. The MAX16984 then monitors the voltages at HVD+ and HVD- to determine the type of the device attached.

If the voltage at HVD- is +2.3V (typ) (V<sub>BIAS</sub> x 0.46) or higher, and the voltage at HVD+ is +2.3V (typ) or lower, the state remains unchanged and the iPhone termination resistors remain present. If the voltage at HVD- is forced below the +2.3V (typ) threshold, or if the voltage at HVD+ is forced higher than the +2.3V (typ) threshold, the internal switch disconnects HVD- and HVD+ from the resistor-divider (iPhone switch open) and HVD+ and HVD- are shorted together for dedicated charging mode (S2 closed). Once the charging voltage is removed, the short between HVD+ and HVD- is disconnected and the operation is restarted with the internal resistor-divider bias voltages appearing on HVD+ and HVD-.

**Fault Output (FAULT)**

The MAX16984 features an open-drain, active low  $\overline{\text{FAULT}}$  output. [Table 3](#) summarizes the conditions that generate a fault and actions taken by the MAX16984. The output remains asserted until the fault condition is removed. The MAX16984 is designed to eliminate false  $\overline{\text{FAULT}}$  reporting by using an internal deglitch, fault blanking, timer. This ensures  $\overline{\text{FAULT}}$  is not accidentally asserted during normal operation such as starting into heavy capacitive loads.

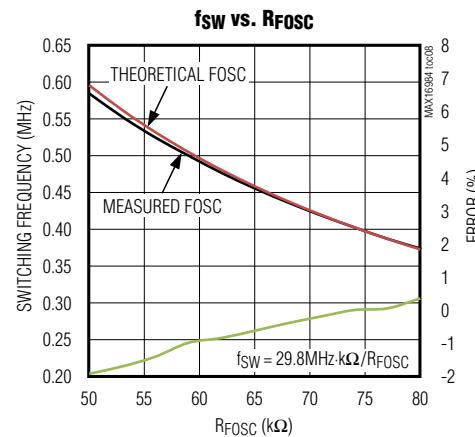

**Applications Information****DC-DC Switching-Frequency Selection**

The switching frequency ( $f_{\text{SW}}$ ) for the MAX16984 is resistor programmable by connecting resistor ( $R_{\text{FOSC}}$ ) from  $\text{FOSC}$  to GND. Select the correct  $R_{\text{FOSC}}$  value for the desired switching frequency. For operation between 1.8MHz and 2.2MHz:  $f_{\text{SW}} \text{ [MHz]} = 26.4/R_{\text{FOSC}}$ , and for operation between 220kHz and 500kHz:  $f_{\text{SW}} \text{ [MHz]} = 29.8/R_{\text{FOSC}}$ , where  $R_{\text{FOSC}}$  is in  $\text{k}\Omega$ . For example, a 2.2MHz switching frequency is set with  $R_{\text{FOSC}} = 12\text{k}\Omega$ . Higher switching frequencies allow for smaller PCB area designs with lower inductor values and less output capacitance. Consequently, peak currents and  $\text{I}^2\text{R}$  losses

are lower at higher switching frequencies, but core losses, gate charge currents, and switching losses increase. Operation between 500kHz and 1.8MHz is not recommended to avoid AM band interference.

**DC-DC Input Capacitor Selection**

The MAX16984 has two main power supply pins to support multiple power architectures. Bypass  $\text{SUP}$  with a 4.7FF ceramic capacitor to GND for proper operation of the internal  $\text{BIAS}$  linear regulator. The selection of the input filter capacitor from  $\text{SUPSW}$  to  $\text{PGND}$  reduces the peak currents drawn from the upstream power source and reduces noise and voltage ripple on the input caused by the circuits switching. The input capacitor RMS current rating requirement ( $\text{I}_{\text{RMS}}$ ) is defined by the following equation:

$$\text{I}_{\text{RMS}} = \text{I}_{\text{LOAD}(\text{MAX})} \frac{\sqrt{V_{\text{SENSP}}(V_{\text{SUPSW}} - V_{\text{SENSP}})}}{V_{\text{SUPSW}}}$$

$\text{I}_{\text{RMS}}$  has a maximum value when the input voltage equals twice the output voltage ( $V_{\text{SUPSW}} = 2V_{\text{SENSP}}$ ), so  $\text{I}_{\text{RMS}(\text{MAX})} = \text{I}_{\text{LOAD}(\text{MAX})}/2$ .

**Table 3. Fault Conditions**

| EVENT                                | ACTION TAKEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Thermal Fault                        | <ul style="list-style-type: none"> <li>If the device is over the thermal limit, the step-down DC-DC regulator is disabled immediately and <math>\overline{\text{FAULT}}</math> goes low.</li> <li>When the thermal fault is removed, the fault is cleared immediately and <math>\overline{\text{FAULT}}</math> goes high.</li> <li>After the fault is removed, the soft starts begins</li> </ul>                                                                                                                                                                                                                                                                                                                                                                             |

| Overvoltage on Pins (HVD+, HVD-, IN) | <ul style="list-style-type: none"> <li>An overvoltage at one of these pins immediately switches off all power and data switches. The step-down DC-DC regulator turns off and the blanking timer turns on.</li> <li>If overvoltage persists for 18ms or longer, <math>\overline{\text{FAULT}}</math> goes low.</li> <li>When the overvoltage is removed, the fault is cleared immediately and <math>\overline{\text{FAULT}}</math> goes high.</li> <li>After the fault is removed, the soft starts begins.</li> </ul>                                                                                                                                                                                                                                                         |

| Undervoltage on BIAS                 | <ul style="list-style-type: none"> <li>A BIAS UVLO immediately switches off all power and data switches and resets the digital logic.</li> <li>During BIAS UVLO, <math>\overline{\text{FAULT}}</math> is high impedance.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Undervoltage on SENSP or Overcurrent | <ul style="list-style-type: none"> <li>If SENSP is less than 4.75V for more than 10ms, <math>\overline{\text{FAULT}}</math> goes low.</li> <li>If USB current limit is high for more than 16.5ms, <math>\overline{\text{FAULT}}</math> goes low.</li> <li>If USB current limit is high and SENSP is less than 4.75V for more than 16.5ms, the step-down DC-DC regulator will reset for 16ms then try to start up again.</li> <li>If the USB current limit is high and if SENSP is less than 2V, <math>\overline{\text{FAULT}}</math> goes low and the part resets.</li> <li>If the step-down DC-DC regulator high-side current limit is high for 4 clock cycles, and if SENSP is less than 2V, <math>\overline{\text{FAULT}}</math> goes low and the part resets.</li> </ul> |