### **MAX15569**

## 2-Phase/1-Phase QuickTune-PWM Controller with Serial I<sup>2</sup>C Interface

### **General Description**

The MAX15569 step-down controller consists of one multiphase regulator. The multiphase CPU regulator uses Maxim's unique 2-phase QuickTune-PWM constant "ontime" architecture. The 2-phase CPU regulator runs 180° out-of-phase for true interleaved operation, minimizing input capacitance.

The device's VR is controlled by writing appropriate data into a function-mapped register file. Output voltages are dynamically changed through a 2-wire, fast I<sup>2</sup>C interface (clock, data), allowing the switching regulator to be programmed to different voltages. A slew-rate controller allows controlled voltage transition and controlled soft-start. The regulator runs in a unique smart, low-power pulse-skipping-state algorithm for best efficiency over the full load range and the best transient response with respect to common pulse-skipping methods.

The device includes multiple fault-protection features: Output overvoltage protection (OVP), undervoltage protection (UVP), and thermal protection. When any of these fault-protection features detect a fault condition, the controller shuts down. A multifunction  $\overline{\text{INT}}$  output monitors output voltage, overcurrent (OC), overrange (VOUTMAX), and thermal faults  $\overline{\text{(VRHOT)}}$ ).

The controller has a programmable switching frequency, allowing 300kHz to 1400kHz per each phase of operation. The controller operates with a wide variety of drivers and MOSFETs, such as the MAX15492 MOSFET driver with standard MOSFETs, or with the power stage that integrates the drivers and MOSFETs together in a single device.

## **Applications**

- ARM Core Power Supply

- Ultrabook<sup>™</sup> and Tablet Core Supplies

- Voltage-Positioned Step-Down Converter

- Multiphase DC-DC Controllers

#### **Benefits and Features**

- Multiphase Controller Maximizes Processor Performance

- 2-Phase QuickTune-PWM CPU Core Regulator

- Output-Voltage Control

- · Active Load-Line Amplifier with Adjustable Gain

- ±5mV FB Accuracy Over Line and Load

- · Programmable Slew Rate and Soft-Start

- Accurate Current Balance and Current Limit

- · True Differential Remote Output Sense

- 8-Bit ADC Digitizes Current Sense to Store in Current Monitor Register

- Transient Phase Overlap Reduces Output Capacitance

- Programmable Functionality Allows Optimized Design Performance

- Programmable 300kHz to 1400kHz Switching Frequency

- Programmable Soft-Shutdown (2kΩ Discharge Switch)

- I<sup>2</sup>C Serial-Interface Control

- Robust Protection for Reliable Operation

- Overcurrent, Output-Voltage Overrange, Overvoltage, Undervoltage, and Thermal-Fault Protection

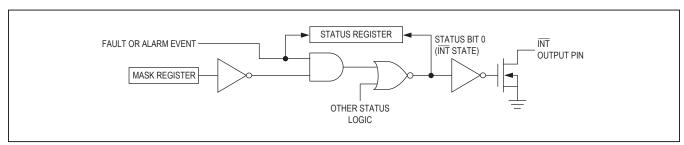

- · System Status Register

- Multifunction INT Output

- 4.5V to 24V Battery Input Range

Ordering Information appears at end of data sheet.

Ultrabook is a trademark of Intel Corporation.

## **Absolute Maximum Ratings**

| V <sub>TT</sub> to AGND0.3V to (V <sub>BIAS</sub> + 0.3V)  | PGND to AGND0.3V to +0.3V                             |

|------------------------------------------------------------|-------------------------------------------------------|

| BIAS to AGND0.3V to +6V                                    | TON to AGND0.3V to +26V                               |

| EN, SCL, SDA to AGND0.3V to +6V                            | Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

| CSP1, CSN1, CSP2, CSN2 to AGND0.3V to +6V                  | TQFN (derate 27.8mW above +70°C)2.2W                  |

| FB, FBAC, IMON to AGND0.3V to (V <sub>BIAS</sub> + 0.3V)   | Operating Temperature Range40°C to +105°C             |

| DRVPWM1, DRVPWM2 to PGND0.3V to (V <sub>BIAS</sub> + 0.3V) | Junction Temperature+150°C                            |

| DRVSKP to PGND0.3V to (V <sub>BIAS</sub> + 0.3V)           | Storage Temperature Range65°C to +165°C               |

| INT, THERM to AGND0.3V to +6V                              | Lead Temperature (soldering, 10s)+300°C               |

| IC to AGND0.3V to +6V                                      | Soldering Temperature (reflow)+260°C                  |

| GNDS to AGND0.3V to +0.3V                                  |                                                       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Thermal Characteristics (Note 1)**

**TQFN**

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ )......36°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )......3°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

## **Electrical Characteristics (0°C to +85°C)**

(Circuit of Figure 1.  $V_{IN}$  = 10V,  $V_{BIAS}$  = 5V,  $V_{TT}$  = 1.8V, EN = BIAS, GNDS = AGND,  $V_{FBAC}$  =  $V_{FB}$  =  $V_{CSP}$  = 1V [SETVOUT register 0x07h set to 0x33h].  $V_{A}$  = 0°C to +85°C, unless otherwise noted. Typical values are at +25°C. All devices 100% tested at +25°C. Limits over temperature are guaranteed by design.)

| PARAMETER                                            | SYMBOL            | CONDITIONS                                                                                                 |                                  | MIN  | TYP | MAX  | UNITS |

|------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------|----------------------------------|------|-----|------|-------|

| BIAS CURRENTS                                        |                   |                                                                                                            |                                  |      |     |      |       |

| BIAS Voltage Range                                   | V <sub>BIAS</sub> |                                                                                                            |                                  | 4.75 |     | 5.25 | V     |

| I <sup>2</sup> C Interface Supply (V <sub>TT</sub> ) | V <sub>TT</sub>   |                                                                                                            |                                  | 1.6  |     | 4.0  | V     |

| Quiescent Supply Current (BIAS)                      | I <sub>BIAS</sub> | Skip mode, measured at BIAS,<br>V <sub>TT</sub> = 1.8V; FB forced above the regulation<br>point, EN = BIAS |                                  |      | 2   | 5    | mA    |

| Shutdown Supply Current (BIAS)                       |                   | Measured at BIAS, EN = GND,<br>V <sub>TT</sub> = 1.8V or GND, T <sub>A</sub> = +25°C                       |                                  |      |     | 6    | μA    |

| V- DIAS Current                                      | L                 | $V_{BIAS}$ = high, EN = low, $T_A$ = +25°C<br>$V_{BIAS}$ = high, EN = high, $T_A$ = +25°C                  |                                  |      |     | 3    |       |

| V <sub>TT</sub> BIAS Current                         | I <sub>VTT</sub>  |                                                                                                            |                                  |      |     | 50   | μA    |

| PWM CONTROLLER                                       |                   |                                                                                                            |                                  |      |     |      |       |

| DC Output Voltage Accuracy (Note 2)                  |                   | T <sub>A</sub> = +25°C; measured at<br>FB, with respect to GNDS;<br>includes load regulation<br>error      | DAC codes from 0.50V to 1.60V    | -5   |     | +5   | mV    |

| DC Output Voltage Accuracy                           |                   | Measured at FB, with                                                                                       | DAC codes from 0.50V to 1.40V    | -8   |     | +8   | mV    |

| (Note 2)                                             |                   | respect to GNDS; includes load regulation error                                                            | DAC codes from<br>1.40V to 1.60V | -0.7 |     | +0.7 | %     |

| Line Regulation Error                                |                   | V <sub>BIAS</sub> = 4.75V to 5.25V, V <sub>I</sub>                                                         | <sub>N</sub> = 5.5V to 20V       |      | 0.1 |      | mV    |

## **Electrical Characteristics (0°C to +85°C) (continued)**

(Circuit of Figure 1.  $V_{IN}$  = 10V,  $V_{BIAS}$  = 5V,  $V_{TT}$  = 1.8V, EN = BIAS, GNDS = AGND,  $V_{FBAC}$  =  $V_{FB}$  =  $V_{CSP}$  = 1V [SETVOUT register 0x07h set to 0x33h].  $V_{A}$  = 0°C to +85°C, unless otherwise noted. Typical values are at +25°C. All devices 100% tested at +25°C. Limits over temperature are guaranteed by design.)

| PARAMETER                                                                                | SYMBOL                | CONDITIONS                                                                                                                         | MIN       | TYP  | MAX  | UNITS |

|------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------|------|------|-------|

| GNDS Input Range                                                                         |                       |                                                                                                                                    | -200      |      | +200 | mV    |

| GNDS Gain                                                                                | A <sub>GNDS</sub>     |                                                                                                                                    | 0.97      | 1.00 | 1.03 | V/V   |

| GNDS Input BIAS Current                                                                  | I <sub>GNDS</sub>     | T <sub>A</sub> = +25°C                                                                                                             | -0.5      |      | +0.5 | μA    |

| TON Shutdown Current                                                                     |                       | EN = AGND, V <sub>IN</sub> = 24V,<br>V <sub>BIAS</sub> = 0V or 5V, T <sub>A</sub> = +25°C                                          |           | 0.01 | 0.1  | μА    |

|                                                                                          |                       | Measured at DRVPWM_,<br>R <sub>TON</sub> = 136.3kΩ (1400kHz)                                                                       | 60        | 71   | 82   |       |

| DRVPWM_ On-Time<br>(Note 3)                                                              | t <sub>ON</sub>       | Measured at DRVPWM_,<br>R <sub>TON</sub> = 200kΩ (1000kHz)                                                                         | 92        | 104  | 114  | ns    |

|                                                                                          |                       | Measured at DRVPWM_,<br>R <sub>TON</sub> = 326.7kΩ (600kHz)                                                                        | 141       | 166  | 192  |       |

| Minimum Off-Time (Note 3)                                                                | t <sub>OFF(MIN)</sub> | Measured at DRVPWM_                                                                                                                |           | 100  | 133  | ns    |

| Slew-Rate Accuracy (see Table<br>8 for Soft-Start and Regular<br>Slew-Rate Combinations) |                       | Slew rate = 3.5mV/µs , 4.5mV/µs, 5.5mV/µs, 7mV/µs, 9mV/µs, 11mV/µs, 14mV/µs, 18mV/µs, 22mV/µs, 28mV/µs, 36mV/µs, 44mV/µs (nominal) | -20       |      |      | %     |

| FAULT PROTECTION                                                                         |                       |                                                                                                                                    |           |      |      |       |

| Upper INT and Output<br>Overvoltage-Protection Trip<br>Threshold                         | V <sub>OVP</sub>      | Soft-start completed, measured at FB                                                                                               | 1.78      | 1.83 | 1.88 | V     |

| Upper INT and Output Overvoltage Propagation Delay                                       | t <sub>OVP</sub>      | FB forced 25mV above trip threshold                                                                                                |           | 5    |      | μs    |

| Lower INT and Output<br>Undervoltage-Protection Trip<br>Threshold                        | V <sub>UVP</sub>      | Measured at FB, with respect to unloaded output voltage                                                                            | -300 -250 |      | -200 | mV    |

| Lower INT Propagation Delay                                                              |                       | FB forced 25mV below trip threshold                                                                                                |           | 5    |      | μs    |

| Output Undervoltage<br>Propagation Delay                                                 | t <sub>UVP</sub>      | FB forced 25mV below trip threshold                                                                                                | 100       | 200  | 350  | μs    |

| INT Output Low Voltage                                                                   |                       | I <sub>SINK</sub> = 4mA                                                                                                            |           |      | 0.3  | V     |

| INT Leakage Current                                                                      |                       | High state, $\overline{\text{INT}}$ forced to 5V, T <sub>A</sub> = +25°C                                                           |           |      | 1    | μA    |

| INT Startup Delay and<br>Transitions Blanking Time                                       | t <sub>INT</sub>      | Measured from the time when FB reaches the target voltage                                                                          |           | 4    |      | μs    |

| V <sub>BIAS</sub> Undervoltage-Lockout<br>Threshold                                      | V <sub>UVLO</sub>     | Rising edge, 50mV typical hysteresis, controller disabled below this level                                                         | 4.3       | 4.5  | 4.7  | V     |

## Electrical Characteristics (0°C to +85°C) (continued)

(Circuit of Figure 1.  $V_{IN}$  = 10V,  $V_{BIAS}$  = 5V,  $V_{TT}$  = 1.8V, EN = BIAS, GNDS = AGND,  $V_{FBAC}$  =  $V_{FB}$  =  $V_{CSP}$  = 1V [SETVOUT register 0x07h set to 0x33h].  $V_{A}$  = 0°C to +85°C, unless otherwise noted. Typical values are at +25°C. All devices 100% tested at +25°C. Limits over temperature are guaranteed by design.)

| PARAMETER                                                             | SYMBOL                | CONDITIONS                                                                                                                                                                                           |                            | TYP                        | MAX                        | UNITS |

|-----------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|----------------------------|-------|

| THERMAL PROTECTION                                                    |                       |                                                                                                                                                                                                      |                            |                            |                            |       |

| THERM Resistor                                                        | R <sub>THERM</sub>    | Internal pullup resistance                                                                                                                                                                           | 5.24                       | 5.35                       | 5.48                       | kΩ    |

| VRHOT Trip Threshold                                                  |                       | Measured at THERM, with respect to $V_{BIAS}$ falling edge; specify as % error for all temp max DAC code settings; typical hysteresis = 100mV, $T_A = +25^{\circ}\text{C}$ to $+100^{\circ}\text{C}$ | 49.5                       |                            | 50.5                       | %     |

| THERM Sampling Period                                                 |                       | 5% duty cycle                                                                                                                                                                                        |                            | 0.75                       | 1.1                        | ms    |

| Internal Thermal-Fault<br>Shutdown Threshold                          | T <sub>TSHDN</sub>    | Typical hysteresis = +15°C                                                                                                                                                                           |                            | 160                        |                            | °C    |

| VALLEY CURRENT LIMIT AND                                              | DROOP                 |                                                                                                                                                                                                      |                            |                            |                            |       |

| Valley Current-Limit Threshold Voltage (Positive)                     | V <sub>ILIM</sub>     | V <sub>CSP</sub> V <sub>CSN</sub> _                                                                                                                                                                  | 35                         | 38                         | 41                         | mV    |

| OC_ALARM Valley Current<br>Threshold Voltage (Positive,<br>CSP1 Only) | V <sub>OC_ALARM</sub> | VCSP1 - VCSN1                                                                                                                                                                                        | 20                         | 23                         | 26                         | mV    |

| Current-Balance Offset Voltage                                        |                       |                                                                                                                                                                                                      | -1.8                       |                            | +1.8                       | mV    |

| Current-Sense Common-Mode Input Range                                 |                       | CSP1, CSN1, CSP2, CSN2                                                                                                                                                                               | 0.5                        |                            | 1.6                        | V     |

| Current-Sense Input Current                                           |                       | CSP1, CSN1, CSP2, CSN2, T <sub>A</sub> = +25°C                                                                                                                                                       | -0.12                      |                            | +0.12                      | μA    |

| Discharge Switch Resistance                                           |                       | CSN1 only                                                                                                                                                                                            |                            | 2                          |                            | kΩ    |

| FB Input Current                                                      |                       | T <sub>A</sub> = +25°C                                                                                                                                                                               | -0.2                       |                            | +0.2                       | μΑ    |

| Phase 2 Disable Threshold                                             |                       | CSP2                                                                                                                                                                                                 | 3                          | V <sub>BIAS</sub><br>- 1.0 | V <sub>BIAS</sub><br>- 0.4 | V     |

| Droop Amplifier (GMD) Offset                                          |                       | Average (V <sub>CSP</sub> - V <sub>CSN</sub> ) at I <sub>FBAC</sub> = 0mA                                                                                                                            | -1.0                       |                            | +1.0                       | mV    |

| Droop Amplifier (GMD)<br>Transconductance                             | G <sub>m(FBAC)</sub>  | $\Delta I_{FBAC}/\Sigma \Delta$ (V <sub>CSP</sub> V <sub>CSN</sub> _), measured at FBAC                                                                                                              | 1.182                      | 1.2                        | 1.218                      | μΑ/mV |

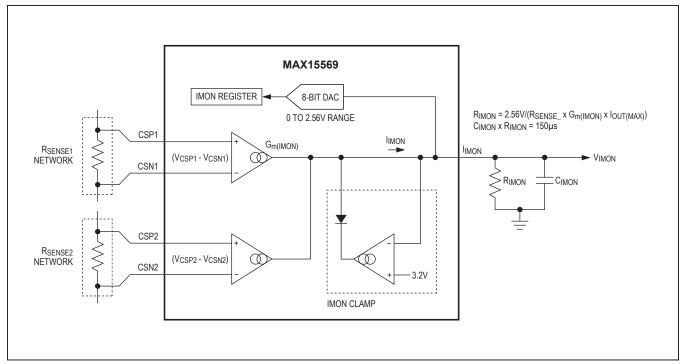

| CURRENT MONITOR (IMON)                                                | •                     |                                                                                                                                                                                                      |                            |                            |                            |       |

| Current Monitor Output Current for Typical Full-Load Conditions       | I <sub>IMON</sub>     | $\Sigma(V_{CSP} - V_{CSN}) = 25mV$                                                                                                                                                                   | 124.2                      | 128                        | 131.8                      | μA    |

| Current Monitor Gain                                                  | G <sub>m(IMON)</sub>  | $\Delta I_{IMON}/\Sigma \Delta$ (V <sub>CSP</sub> V <sub>CSN</sub> _), measured at IMON                                                                                                              | 4.8                        | 5.12                       | 5.44                       | μΑ/mV |

| Current Monitor Clamp Voltage                                         |                       | IMON                                                                                                                                                                                                 |                            | 3.2                        | 3.6                        | V     |

| DRIVER CONTROL                                                        |                       |                                                                                                                                                                                                      |                            |                            |                            |       |

| DRVPWM_, DRVSKP# Output<br>Logic-High Voltage                         | V <sub>OH_DRV</sub>   | I <sub>SOURCE</sub> = 3mA                                                                                                                                                                            | V <sub>BIAS</sub><br>- 0.4 |                            |                            | V     |

| DRVPWM_, DRVSKP# Output<br>Logic-Low Voltage                          | V <sub>OL_DRV</sub>   | I <sub>SINK</sub> = 3mA                                                                                                                                                                              |                            |                            | 0.4                        | V     |

| DRVPWM_ Output Midlevel Voltage                                       |                       |                                                                                                                                                                                                      | 1.6                        |                            | 2.3                        | V     |

## Electrical Characteristics (0°C to +85°C) (continued)

(Circuit of Figure 1.  $V_{IN}$  = 10V,  $V_{BIAS}$  = 5V,  $V_{TT}$  = 1.8V, EN = BIAS, GNDS = AGND,  $V_{FBAC}$  =  $V_{FB}$  =  $V_{CSP}$  = 1V [SETVOUT register 0x07h set to 0x33h].  $V_{A}$  = 0°C to +85°C, unless otherwise noted. Typical values are at +25°C. All devices 100% tested at +25°C. Limits over temperature are guaranteed by design.)

| PARAMETER                                        | SYMBOL              | CONDITIONS                                           | MIN                      | TYP | MAX  | UNITS |

|--------------------------------------------------|---------------------|------------------------------------------------------|--------------------------|-----|------|-------|

| ENABLE LOGIC (EN)                                |                     |                                                      |                          |     |      |       |

| EN Input High Voltage                            | V <sub>IH_EN</sub>  |                                                      | 0.7 x<br>V <sub>TT</sub> |     |      | V     |

| EN Input Low Voltage                             | V <sub>IL_EN</sub>  |                                                      |                          |     | 0.33 | V     |

| EN Input Current                                 | I <sub>EN</sub>     | T <sub>A</sub> = +25°C                               | -1                       |     | +1   | μΑ    |

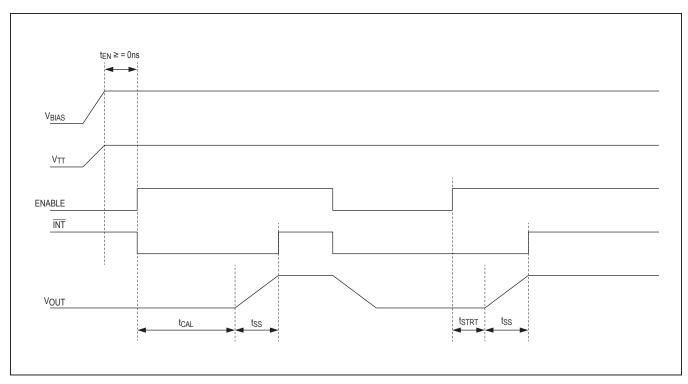

| Power-Up Calibration Delay                       | t <sub>CAL</sub>    |                                                      |                          | 850 |      | μs    |

| Enable to Startup Delay                          | t <sub>STRT</sub>   | EN to first switching edge (fully discharged output) |                          | 150 |      | μs    |

| I <sup>2</sup> C INTERFACE (SDA, SCL)            |                     |                                                      |                          |     |      |       |

| I <sup>2</sup> C Input Low Voltage               | V <sub>IL</sub>     |                                                      |                          |     | 0.4  | V     |

| I <sup>2</sup> C Input High Voltage              | V <sub>IH</sub>     |                                                      | 0.7 x<br>V <sub>TT</sub> |     |      | V     |

| I <sup>2</sup> C Output Low Level<br>(SDA Only)  | V <sub>OL</sub>     | Open-drain output, 3mA pullup to V <sub>TT</sub>     |                          |     | 0.4  | V     |

| I <sup>2</sup> C Logic Inputs Leakage<br>Current |                     | T <sub>A</sub> = +25°C                               | -1                       |     | +1   | μА    |

| I <sup>2</sup> C TIMING REQUIREMENTS             | <u>'</u>            |                                                      | <u>'</u>                 |     |      |       |

| I <sup>2</sup> C Clock Frequency                 |                     |                                                      |                          |     | 3.4  | MHz   |

| Hold Time Repeated START Condition               | t <sub>HD_STA</sub> | (Note 4)                                             | 160                      |     |      | ns    |

| SCL Low Period                                   | t <sub>LOW</sub>    | (Note 4)                                             | 160                      |     |      | ns    |

| SCL High Period                                  | tHIGH               | (Note 4)                                             | 60                       |     |      | ns    |

| Setup Time Repeated START Condition              | t <sub>SU_STA</sub> | (Note 4)                                             | 160                      |     |      | ns    |

| SDA Hold Time                                    | tHD_DAT             | (Note 4)                                             | 0                        |     | 70   | ns    |

| SDA Setup Time                                   | t <sub>SU_DAT</sub> | (Note 4)                                             | 10                       |     |      | ns    |

| Setup Time for STOP Condition                    | t <sub>SU_STO</sub> | (Note 4)                                             | 160                      |     |      | ns    |

## **Electrical Characteristics (-40°C to +105°C)**

(Circuit of Figure 1.  $V_{IN}$  = 10V,  $V_{BIAS}$  = 5V,  $V_{TT}$  = 1.8V, EN = BIAS, GNDS = AGND,  $V_{FBAC}$  =  $V_{FB}$  =  $V_{CSP}$  = 1V [SETVOUT register 0x07h set to 0x33h].  $V_{FBAC}$  = -40°C to +105°C, unless otherwise noted.)

| PARAMETER                                                                                | SYMBOL                | CONDITIONS                                                                                                                         |                                                                | MIN  | TYP | MAX  | UNITS |

|------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------|-----|------|-------|

| BIAS CURRENTS                                                                            |                       |                                                                                                                                    | <u> </u>                                                       |      |     |      |       |

| BIAS Voltage Range                                                                       | V <sub>BIAS</sub>     |                                                                                                                                    |                                                                | 4.75 |     | 5.25 | V     |

| I <sup>2</sup> C Interface Supply (V <sub>TT</sub> )                                     | V <sub>TT</sub>       |                                                                                                                                    |                                                                | 1.6  |     | 4.0  | V     |

| Quiescent Supply Current (BIAS)                                                          | I <sub>BIAS</sub>     |                                                                                                                                    | at BIAS, V <sub>TT</sub> = 1.8V; FB<br>lation point; EN = BIAS |      |     | 5    | mA    |

| PWM CONTROLLER                                                                           |                       |                                                                                                                                    |                                                                |      |     |      |       |

| DC Output Voltage Accuracy                                                               |                       | Measured at FB, with respect to                                                                                                    | DAC codes from 0.50V to 1V                                     | -10  |     | +10  | mV    |

| (Note 2)                                                                                 |                       | GNDS; includes load regulation error                                                                                               | DAC codes from 1V to 1.60V                                     | -1.0 |     | +1.0 | %     |

| GNDS Gain                                                                                | A <sub>GNDS</sub>     |                                                                                                                                    |                                                                | 0.97 |     | 1.03 | V/V   |

|                                                                                          |                       | Measured at DRVPWI<br>R <sub>TON</sub> = 136.3kΩ, (140                                                                             |                                                                | 60   |     | 82   |       |

| DRVPWM_ On-Time (Note 3)                                                                 | t <sub>ON</sub>       | Measured at DRVPWM_,<br>$R_{TON}$ = 200kΩ, (1000kHz)<br>Measured at DRVPWM_,<br>$R_{TON}$ = 326.7kΩ, (600kHz)                      |                                                                | 92   |     | 114  | ns    |

|                                                                                          |                       |                                                                                                                                    |                                                                | 141  |     | 192  |       |

| Minimum Off-Time (Note 3)                                                                | t <sub>OFF(MIN)</sub> | Measured at DRVPWI                                                                                                                 | M_                                                             |      |     | 133  | ns    |

| Slew-Rate Accuracy (see Table<br>8 for Soft-Start and Regular<br>Slew-Rate Combinations) |                       | Slew rate = 3.5mV/μs , 4.5mV/μs, 5.5mV/μs, 7mV/μs, 9mV/μs, 11mV/μs, 14mV/μs, 18mV/μs, 22mV/μs, 28mV/μs, 36mV/μs, 44mV/μs (nominal) |                                                                | -20  |     |      | %     |

| FAULT PROTECTION                                                                         |                       |                                                                                                                                    |                                                                |      |     |      |       |

| Upper INT and Output<br>Overvoltage-Protection Trip<br>Threshold                         | V <sub>OVP</sub>      | Soft-start completed; r                                                                                                            | measured at FB                                                 | 1.78 |     | 1.88 | V     |

| Lower INT and Output<br>Undervoltage-Protection Trip<br>Threshold                        | V <sub>UVP</sub>      | Measured at FB, with respect to unloaded output voltage                                                                            |                                                                | -300 |     | -200 | mV    |

| Output Undervoltage<br>Propagation Delay                                                 | t <sub>UVP</sub>      | FB forced 25mV below trip threshold                                                                                                |                                                                | 100  |     | 350  | μs    |

| INT Output Low Voltage                                                                   |                       | I <sub>SINK</sub> = 4mA                                                                                                            |                                                                |      |     | 0.3  | V     |

| V <sub>BIAS</sub> Undervoltage-Lockout<br>Threshold                                      | V <sub>UVLO</sub>     | Rising edge, 50mV typical hysteresis; controller disabled below this level                                                         |                                                                | 4.3  |     | 4.7  | V     |

## Electrical Characteristics (-40°C to +105°C) (continued)

(Circuit of Figure 1.  $V_{IN}$  = 10V,  $V_{BIAS}$  = 5V,  $V_{TT}$  = 1.8V, EN = BIAS, GNDS = AGND,  $V_{FBAC}$  =  $V_{FB}$  =  $V_{CSP}$  = 1V [SETVOUT register 0x07h set to 0x33h].  $V_{FBAC}$  = -40°C to +105°C, unless otherwise noted.)

| PARAMETER                                                             | SYMBOL               | CONDITIONS                                                                                                                                                                                           | MIN                        | TYP | MAX                        | UNITS |

|-----------------------------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----|----------------------------|-------|

| THERMAL PROTECTION                                                    |                      |                                                                                                                                                                                                      |                            |     |                            |       |

| THERM Resistor                                                        | R <sub>THERM</sub>   | Internal pullup resistance                                                                                                                                                                           | 5.24                       |     | 5.48                       | kΩ    |

| VRHOT Trip Threshold                                                  |                      | Measured at THERM, with respect to $V_{BIAS}$ falling edge; specify as % error for all temp max DAC code settings; typical hysteresis = 100mV; $T_A = +25^{\circ}\text{C}$ to $+105^{\circ}\text{C}$ |                            |     | 50.5                       | %     |

| VALLEY CURRENT LIMIT AND                                              | DROOP                | '                                                                                                                                                                                                    |                            |     |                            |       |

| Valley Current-Limit Threshold<br>Voltage (Positive)                  | V <sub>ILIM</sub>    | V <sub>CSP</sub> V <sub>CSN</sub> _                                                                                                                                                                  | 35                         |     | 41                         | mV    |

| OC_ALARM Valley Current<br>Threshold Voltage (Positive,<br>CSP1 Only) | VOC_ALARM            | V <sub>CSP1</sub> - V <sub>CSN1</sub>                                                                                                                                                                | 20                         |     | 26                         | mV    |

| Current-Balance Offset Voltage                                        |                      |                                                                                                                                                                                                      | -2.5                       |     | +2.5                       | mV    |

| Current-Sense Common-Mode Input Range                                 |                      | CSP1, CSN1, CSP2, CSN2                                                                                                                                                                               | 0.5                        |     | 1.6                        | V     |

| Phase 2 Disable Threshold                                             |                      | CSP2                                                                                                                                                                                                 | 3                          |     | V <sub>BIAS</sub><br>- 0.4 | V     |

| Droop Amplifier (GMD) Offset                                          |                      | Average (V <sub>CSP</sub> - V <sub>CSN</sub> ) at I <sub>FBAC</sub> = 0mA                                                                                                                            | -1.0                       | -   | +1.0                       | mV    |

| Droop Amplifier (GMD)<br>Transconductance                             | G <sub>m(FBAC)</sub> | $\Delta I_{FBAC}/\Sigma \Delta$ (V <sub>CSP</sub> V <sub>CSN</sub> _), measured at FBAC                                                                                                              | 1.176                      |     | 1.224                      | μA/mV |

| CURRENT MONITOR (IMON)                                                |                      |                                                                                                                                                                                                      |                            |     |                            |       |

| Current Monitor Output Current for Typical Full-Load Conditions       | I <sub>IMON</sub>    | $\Sigma(V_{CSP} - V_{CSN}) = 25mV$                                                                                                                                                                   | 122.2                      |     | 133.8                      | μA    |

| Current Monitor Gain                                                  | G <sub>m(IMON)</sub> | $\Delta I_{IMON}/\Sigma \Delta$ (V <sub>CSP</sub> V <sub>CSN</sub> _), measured at IMON                                                                                                              | 4.8                        |     | 5.44                       | μΑ/mV |

| DRIVER CONTROL                                                        |                      |                                                                                                                                                                                                      |                            |     |                            |       |

| DRVPWM_, DRVSKP Output Logic-High Voltage                             | V <sub>OH_DRV</sub>  | I <sub>SOURCE</sub> = 3mA                                                                                                                                                                            | V <sub>BIAS</sub><br>- 0.4 |     |                            | V     |

| DRVPWM_, DRVSKP Output Logic-Low Voltage                              | V <sub>OL_DRV</sub>  | I <sub>SINK</sub> = 3mA                                                                                                                                                                              |                            |     | 0.4                        | V     |

| DRVPWM_ Output Midlevel Voltage                                       |                      |                                                                                                                                                                                                      | 1.6                        |     | 2.3                        | V     |

| ENABLE LOGIC (EN)                                                     |                      |                                                                                                                                                                                                      |                            |     |                            |       |

| EN Input High Voltage                                                 | V <sub>IH_EN</sub>   |                                                                                                                                                                                                      | 0.7 x<br>V <sub>TT</sub>   |     |                            | V     |

| EN Input Low Voltage                                                  | V <sub>IL_EN</sub>   |                                                                                                                                                                                                      |                            |     | 0.33                       | V     |

|                                                                       |                      |                                                                                                                                                                                                      |                            |     |                            |       |

## Electrical Characteristics (-40°C to +105°C) (continued)

(Circuit of Figure 1.  $V_{IN}$  = 10V,  $V_{BIAS}$  = 5V,  $V_{TT}$  = 1.8V, EN = BIAS, GNDS = AGND,  $V_{FBAC}$  =  $V_{FB}$  =  $V_{CSP}$  = 1V [SETVOUT register 0x07h set to 0x33h].  $V_{FBAC}$  = 1V (SETVOUT register 0x07h set to 0x33h).

| PARAMETER                            | SYMBOL              | CONDITIONS | MIN | TYP | MAX | UNITS |

|--------------------------------------|---------------------|------------|-----|-----|-----|-------|

| I <sup>2</sup> C TIMING REQUIREMENTS |                     |            |     |     |     |       |

| I <sup>2</sup> C Clock Frequency     |                     |            |     |     | 3.4 | MHz   |

| Hold Time Repeated START Condition   | t <sub>HD_STA</sub> | (Note 4)   | 160 |     |     | ns    |

| SCL Low Period                       | t <sub>LOW</sub>    | (Note 4)   | 160 |     |     | ns    |

| SCL High Period                      | tHIGH               | (Note 4)   | 60  |     |     | ns    |

| Setup Time Repeated START Condition  | t <sub>SU_STA</sub> | (Note 4)   | 160 |     |     | ns    |

| SDA Hold Time                        | t <sub>HD_DAT</sub> | (Note 4)   | 0   |     | 70  | ns    |

| SDA Setup Time                       | t <sub>SU_DAT</sub> | (Note 4)   | 10  |     |     | ns    |

| Setup Time for STOP Condition        | tsu_sto             | (Note 4)   | 160 |     |     | ns    |

- Note 2: The equation for the target voltage V<sub>TARGET</sub> is: V<sub>TARGET</sub> = the output of slew control DAC, where V<sub>DAC</sub> = 0V for shutdown, V<sub>DAC</sub> = V<sub>BOOT</sub> during startup; otherwise V<sub>DAC</sub> = SETVOUT. The output voltages for all possible codes are given in Table 3.

- Note 3: On-time and minimum off-time specifications are measured from 50% rise to 50% fall at the DRVPWM\_ pin. Actual in-circuit times can be different due to MOSFET driver characteristics.

- Note 4: Guaranteed by design. Not production tested.

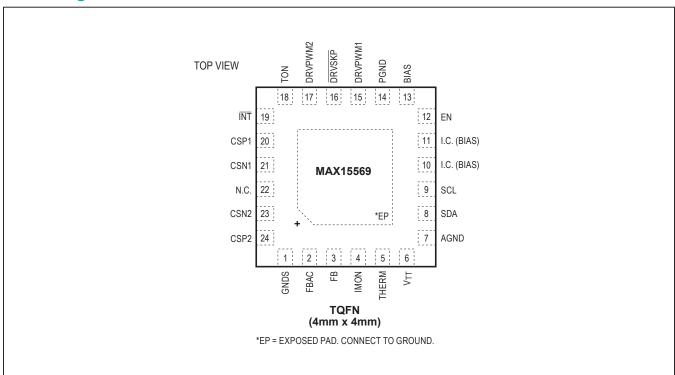

## **Pin Configuration**

## **Pin Description**

| PIN    | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | GNDS            | Ground Remote-Sense Input. Connect GNDS to the ground-sense pin of the CPU located directly at the point of load. GNDS internally connects to an internal transconductance amplifier that adjusts the feedback voltage to compensate for voltage drops between the local controller ground and the remote load ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

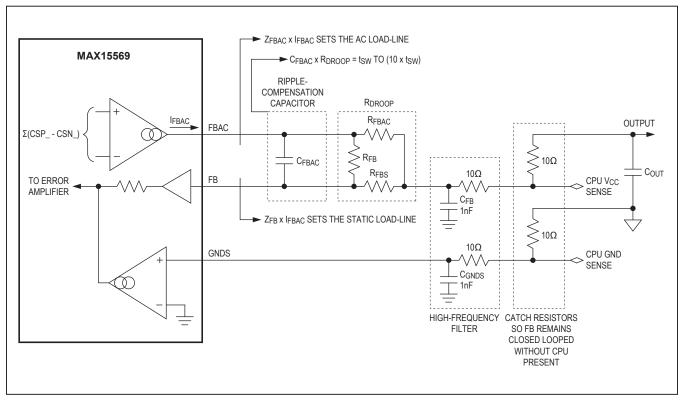

| 2      | FBAC            | Output of the AC Voltage Positioning Transconductance Amplifier. The effective impedance (Z <sub>FBAC</sub> ) between this pin and the positive side of the remote-sensed output voltage sets the transient AC droop. See the <i>Load-Line Amplifier</i> (Steady State and AC Droop) section. FBAC is high impedance in shutdown.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3      | FB              | Feedback-Sense Input. An integrator on FB corrects for output ripple and ground-sense offset. Connect a resistor (R <sub>FB</sub> ) between FB and the positive output of the remote sense (output) to set the DC steady-state droop. The impedance from FBAC to FB sets the current-loop gain over frequency, which dominates stability. See the <i>Load-Line Amplifier</i> (Steady State and AC Droop) section.                                                                                                                                                                                                                                                                                                                                                                |

| 4      | IMON            | Current Monitor Output. The output current at IMON is: $I_{IMON} = G_{M(IMON)} \times \sum (CSP CSN)$ where $G_{M(IMON)} = 5.12\text{mS}$ (typ). An external resistor ( $R_{IMON}$ ) between IMON and GNDS sets the current monitor output voltage: $V_{IMON} = I_{LOAD} \times R_{SENSE} \times G_{M(IMON)} \times R_{IMON}$ where $R_{SENSE}$ is the value of the effective current-sense resistance. Choose $R_{IMON}$ so that $V_{IMON}$ is 2.56V at the desired full current. IMON is high impedance when in shutdown.                                                                                                                                                                                                                                                      |

| 5      | THERM           | Thermal-Sense Input. Connect a $100k\Omega$ NTC with $\beta$ = 4250K from THERM to AGND. The NTC at THERM is used to determine the temperature of the power stages. Place near the hottest region of the regulator (typically the MOSFETs and inductor of phase 1). The VRHOT status bit (D5) activates when the NTC resistance drops to $5.68k\Omega$ (100°C when using a $100k\Omega$ NTC with $\beta$ = 4250K).                                                                                                                                                                                                                                                                                                                                                               |

| 6      | V <sub>TT</sub> | Interface Logic Supply. Power $V_{TT}$ from a 1.8V to 3.3V ±10% source with a compliance of at least 1mA. Decouple $V_{TT}$ with at least 1µF of ceramic capacitance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7      | AGND            | Analog Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 8      | SDA             | I <sup>2</sup> C Serial-Data Input/Output. Open-Drain I/O pin. Connect an external pullup resistor between SDA and the supply used to power the I <sup>2</sup> C interface (V <sub>TT</sub> ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 9      | SCL             | I <sup>2</sup> C Serial-Data Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10, 11 | I.C.            | Internally Connected. Connect to BIAS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 12     | EN              | Controller Enable Input. Drive EN high or connect EN to BIAS for normal operation. Pull to ground to put the controller into its $7\mu A$ (max) standby state (I²C interface active, regulator not switching). During soft-start, the controller slowly ramps the output voltage up to the boot voltage with the selected slew rate (register $0x06$ , default is $4.5mV/\mu s$ for start-up and $9mV/\mu s$ for normal operation). During the transition from normal operation to standby, the output is discharged through a $2k\Omega$ internal discharge MOSFET on CSN1. Toggling EN does <b>NOT</b> reset the fault latches. Cycle power (V <sub>TT</sub> or BIAS) to trigger the power-on reset (POR) to clear the fault conditions. The EN input is rated for up to 5.5V. |

## **Pin Description (continued)**

| PIN | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13  | BIAS    | Analog and Driver Supply Voltage Input. BIAS provides the supply voltage for the driver's PWM and skip control outputs. Connect BIAS to the same supply used by the external drivers (typically the 4.5V to 5.5V system supply voltage). Bypass BIAS to power ground with a local 1µF or greater ceramic capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 14  | PGND    | Power Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 15  | DRVPWM1 | Direct-Drive PWM Output for Controlling the External First-Phase Driver. The DRVPWM1 push-pull output drives the signal between BIAS and PGND. DRVPWM1 is high impedance in shutdown and after fault conditions (output overvoltage/undervoltage or thermal fault).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 16  | DRVSKP  | External Driver Skip-Mode Control Output. The DRVSKP output is low in standby. DRVSKP goes high when the controller detects an output overvoltage fault condition, or during dynamic output-voltage transitions.  For applications operating with forced-PWM operation, disable the driver zero-crossing detection and leave DRVSKP unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 17  | DRVPWM2 | Direct-Drive PWM Output for Controlling the External Second-Phase Driver. The DRVPWM2 push-pull output drives the signal between BIAS and PGND. DRVPWM2 is high impedance in shutdown and after fault conditions (output overvoltage, output undervoltage, or thermal fault).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 18  | TON     | Switching Frequency Adjustment Input. An external resistor between the input power source and TON sets the switching period (per phase) according to the following equation: $f_{SW} = (R_{TON} + 6.5 k\Omega) \times 5 pF$ where $f_{SW} = 1/f_{SW}$ is the nominal switching frequency. A $200 k\Omega$ resistor provides a typical operating frequency of $1 MHz$ . TON is high impedance in shutdown.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 19  | ĪNT     | Open-Drain Interrupt Output. INT is triggered by latched faults (output undervoltage, output overvoltage, thermal shutdown), sticky alarms (internal overcurrent (OC), non-sticky alarms (voltage regulator hot (VRHOT), and VID code violations (VOUTMAX)). The fault conditions and alarms can be masked through register 0x05h. Masking these signals only prevents INT from being asserted; the STATUS register still asserts when any of these conditions occur. INT remains high in standby mode (EN pulled low) to reduce power through the pullup resistor. INT is pulled low during soft-start. After completing the soft-start sequence, INT becomes high impedance as long as FB remains in regulation and there are no active alarms.  To obtain a logic signal, pull up INT with an external resistor connected to a logic supply. |

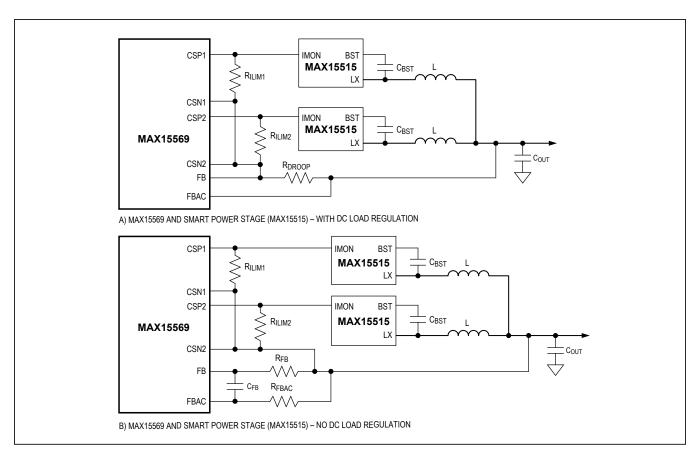

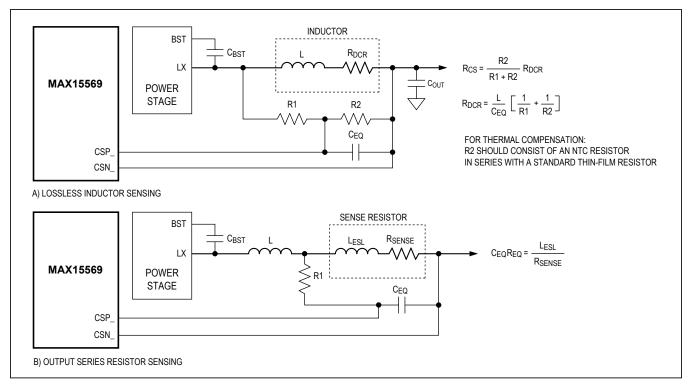

| 20  | CSP1    | Positive Current-Sense Input for the First Phase.  1) Connect CSP1 to the positive side of the current-sense resistor or the DCR sense filter capacitor of phase 1, as shown in Figure 4.  2) Connect CSP1 to the IOUT pin of the smart power stage (MAX15515). A resistor across CSP1 and CSN1 sets the current-sense gain, as shown in Figure 3.  See the <i>Current Sense</i> section.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 21  | CSN1    | Negative Current-Sense Input for the First Phase. Connect CSN1 to the negative side of the current-sense element, as shown in Figure 4. An internal $2k\Omega$ discharge MOSFET between CSN1 and ground is enabled under an input UVLO or shutdown condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 22  | N.C.    | No Connection Internally                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

## **Pin Description (continued)**

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 23  | CSN2 | Negative Current-Sense Input for the Second Phase. Connect CSN2 to the negative side of the current-sense element, as shown in Figure 4.                                                                                                                                                                                                                                                                                    |  |

| 24  | CSP2 | Positive Current-Sense Input for the Second Phase.  1) Connect CSP2 to the positive side of the current-sense resistor or the DCR sense filter capacitor of phase 2, as shown in Figure 4.  2) Connect CSP2 to the IOUT pin of the smart power stage (MAX15515). A resistor across CSP2 and CSN2 sets the current-sense gain, as shown in Figure 3.  See the Current Sense section. To disable phase 2, short CSP2 to BIAS. |  |

| _   | EP   | Exposed Pad. The substrate of the controller is internally connected to the exposed pad. Connected to the ground plane through multiple vias to maintain low thermal impedance.                                                                                                                                                                                                                                             |  |

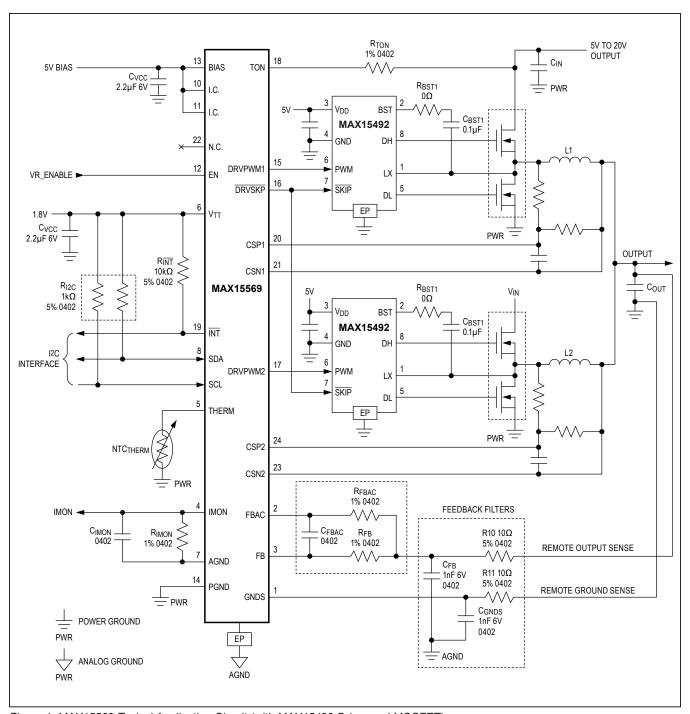

Figure 1. MAX15569 Typical Application Circuit (with MAX15492 Driver and MOSFET)

**Table 1. Components for Typical Application Circuit**

| TYPE                                       | REF                                      | 2-PHASE DESIGN EXAMPLE<br>(1MHz OPERATION)                                                                                          |

|--------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| OPERATING CONDITIONS                       |                                          |                                                                                                                                     |

| Input Voltage                              | V <sub>IN</sub>                          | 5V to 20V                                                                                                                           |

| Output Voltage                             | V <sub>OUT</sub>                         | 1V                                                                                                                                  |

| Output Current                             | I <sub>OUT</sub>                         | 20A (max), 14A RMS                                                                                                                  |

| Load Transient                             | Δl <sub>OUT</sub>                        | 25A                                                                                                                                 |

| Current Limit                              | I <sub>OCP</sub>                         | 40A                                                                                                                                 |

| Switching Frequency                        | f <sub>SW</sub>                          | 1MHz                                                                                                                                |

| Number of Phases                           | N <sub>PH</sub>                          | 2                                                                                                                                   |

| COMPONENTS                                 |                                          |                                                                                                                                     |

| TON                                        | R <sub>TON</sub>                         | 200kΩ 1%                                                                                                                            |

| Inductor                                   | L                                        | 0.2μH/9.5mΩ/9.5A inductor<br>(4.06mm x 4.55mm x 1.2mm)<br>Vishay IHLP-1616AB-1A                                                     |

| MOSFET Driver                              | DRV                                      | MAX15492                                                                                                                            |

| High-Side MOSFET                           | N <sub>H</sub>                           |                                                                                                                                     |

| Low-Side MOSFET                            | N <sub>L</sub>                           | <del>-</del>                                                                                                                        |

| Current Sense                              | R <sub>CS</sub>                          |                                                                                                                                     |

| Bulk Output Capacitors (Mid Frequency)     | C <sub>OUT</sub>                         | _                                                                                                                                   |

| Ceramic Output Capacitors (High Frequency) | C <sub>OUT</sub>                         | 20 x 22μF ceramic capacitors                                                                                                        |

| Input Capacitors                           | C <sub>IN</sub>                          | 2 x 10µF, 16V X5R ceramic capacitors                                                                                                |

| FB Droop Setting                           | _                                        | $R_{FBAC} = R_{FB} = 1k\Omega \ 1\%$ $C_{FBAC} = 4.7nF$ $AC \ droop = -1.5mV/A$ $DC \ droop = 0mV/A$                                |

| IMON                                       | R <sub>IMON</sub> ,<br>C <sub>IMON</sub> | $R_{IMON}$ = 5.62kΩ 1%<br>$C_{IMON}$ = 47nF<br>(260μs time constant)                                                                |

| THERM NTC                                  | R <sub>THERM</sub>                       | $100k\Omega$ , 5% NTC thermistor $\beta$ = 4250K (0603)  Murata NCP18WF104J03RB  TDK NTCG163JF104J (0402) or Panasonic ERT-J1VR104J |

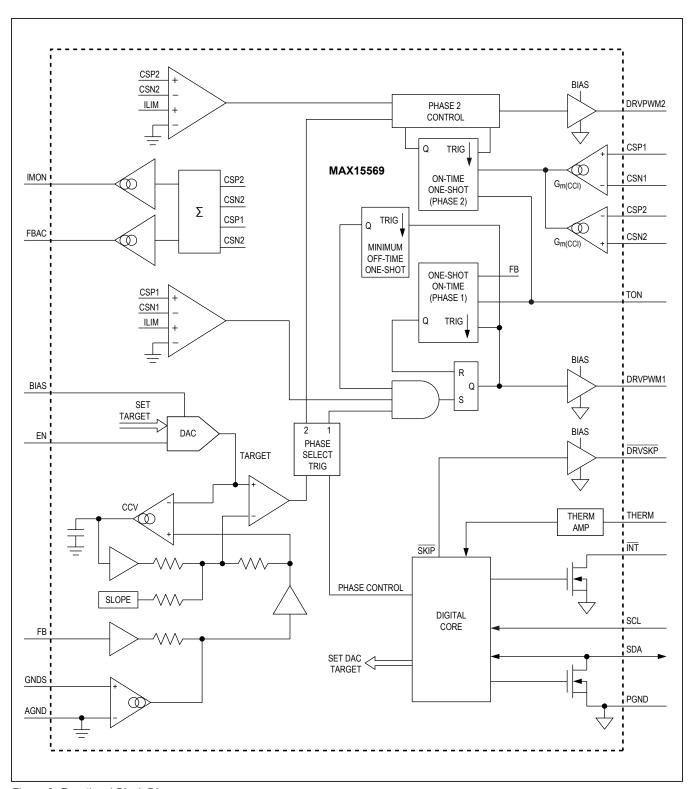

Figure 2. Functional Block Diagram

## **Detailed Description**

For system power management, the MAX15569 controller includes a current gauge and thermal status (VRHOT) that can be monitored over the I<sup>2</sup>C interface. In addition, the device's multiple fault-protection features include: Output overvoltage protection (OVP), undervoltage protection (UVP), and thermal protection. When any of these fault-protection features detect a fault condition, the controller shuts down.

## Free-Running Constant On-Time Controller with Input Feed-Forward

The QuickTune-PWM control architecture consists of a pseudo-fixed frequency, constant on-time, and current-mode regulator with voltage feed-forward (Figure 2). The control algorithm is simple; the high-side switch on-time is determined solely by a one-shot, whose period is inversely proportional to input voltage and directly proportional to the feedback voltage or the difference between the main and secondary inductor currents (see the On-Time One-Shot section). Another one-shot sets a minimum off-time.

The on-time one-shot triggers when the inverting input to the error comparator falls below the target voltage, the inductor current of the selected phase is below the valley current-limit threshold, and the minimum off-time one-shot times out. The regulator maintains 180° out-of-phase operation by alternately triggering the two phases after the error comparator drops below the output-voltage set point.

### **Switching Frequency**

Connect a resistor ( $R_{TON}$ ) between TON and the input supply ( $V_{IN}$ ) to set the switching period ( $t_{SW} = 1/f_{SW}$ ) per phase using the following equation:

$$t_{SW} (R_{TON} + 6.5k\Omega) \times 5pF$$