## **General Description**

The MAX1530/MAX1531 multiple-output power-supply controllers generate all the supply rails for thin-film transistor (TFT) liquid-crystal display (LCD) monitors. Both devices include a high-efficiency, fixed-frequency, step-down regulator. The low-cost, all N-channel, synchronous topology enables operation with efficiency as high as 93%. High-frequency operation allows the use of small inductors and capacitors, resulting in a compact solution. The MAX1530 includes three linear regulator controllers and the MAX1531 includes five linear regulator controllers for supplying logic and LCD bias voltages. A programmable startup sequence enables easy control of the regulators.

The MAX1530/MAX1531 include soft-start functions to limit inrush current during startup. An internal stepdown converter current-limit function and a versatile overcurrent shutdown protect the power supplies against fault conditions. The MAX1530/MAX1531 use a currentmode control architecture, providing fast load transient response and easy compensation. An internal linear regulator provides MOSFET gate drive and can be used to power small external loads.

The MAX1530/MAX1531 can operate from inputs as high as 28V and are well suited for LCD monitor and TV applications running directly from AC/DC wall adapters. Both devices are available in a small (5mm x 5mm), ultrathin (0.8mm), 32-pin QFN package and operate over the -40°C to +85°C temperature range.

## **Applications**

• LCD Monitors and TVs

## **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE |

|--------------|----------------|-------------|

| MAX1530ETJ+  | -40°C to +85°C | 32 TQFN-EP* |

| MAX1530ETJ+T | -40°C to +85°C | 32 TQFN-EP* |

| MAX1531ETJ+  | -40°C to +85°C | 32 TQFN-EP* |

| MAX1531ETJ+T | -40°C to +85°C | 32 TQFN-EP* |

+Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

\*EP = Exposed pad.

Pin Configuration appears at end of data sheet.

# Multiple-Output Power-Supply Controllers for LCD Monitors

## **Features**

- 4.5V to 28V Input Voltage Range

- 250kHz/500kHz Current-Mode Step-Down Converter

Small Inductor/Capacitors

- No Sense Resistor

- Three Positive Linear Regulator Controllers

- One Positive and One Negative Additional Controller (MAX1531)

- Small Input and Output Capacitors

- Timed Reset Output

- Uncommitted Overcurrent Protection (MAX1531)

- Soft-Start for All Regulators

- Programmable Input Undervoltage Comparator

- Programmable Startup Sequencing

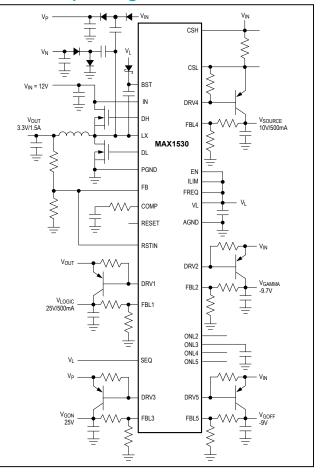

## **Minimal Operating Circuit**

# Multiple-Output Power-Supply Controllers for LCD Monitors

## **Absolute Maximum Ratings**

| IN | DRV/1  | DRV2, | DR\/3   | CSH  |

|----|--------|-------|---------|------|

|    | DIXVI, |       | DI V 0, | 0011 |

| CSL to AGND  | 0.3V to +30V         |

|--------------|----------------------|

| DRV5 to VL   | 28V to +0.3V         |

| CSH to CSL   | 0.3V to +6V          |

| VL to AGND   | 0.3V to +6V          |

| PGND to AGND | ±0.3V                |

| LX to BST    | 6V to +0.3V          |

| BST to AGND  | 0.3V to +36V         |

| DH to LX     | 0.3V to (BST + 0.3V) |

| DL to PGND   | 0.3V to (VL + 0.3V)  |

|              |                      |

| SEQ, ONL2, ONL3, ONL4, ONL5, COMP,<br>ILIM to AGND0.3V to (VL + 0.3V) |

|-----------------------------------------------------------------------|

| RSTIN, RESET, EN, FB, FBL1, FBL2, FBL3, FBL4, FBL5,                   |

| FREQ to AGND0.3V to +6V                                               |

| VL Short Circuit to AGND                                              |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)                 |

| 32-Pin Thin QFN (derate 21.3mW/°C above +70°C)1702mW                  |

| Operating Temperature Range40°C to +85°C                              |

| Storage Temperature Range65°C to +150°C                               |

| Junction Temperature+150°C                                            |

| Lead Temperature (soldering, 10s)+300°C                               |

| Soldering Temperature (reflow)+260°C                                  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Electrical Characteristics**

(Circuit of Figure 1,  $V_{IN}$  = 12V,  $V_{EN}$  =  $V_{SEQ}$  = 5V,  $T_A$  = 0°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                                                   | CONDITIONS                                                                                                                        | MIN   | ТҮР   | MAX   | UNITS |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| GENERAL                                                     |                                                                                                                                   |       |       |       |       |

| Operating Input Voltage Range                               | (Note 1)                                                                                                                          | 4.5   |       | 28.0  | V     |

| Quiescent Supply Current                                    | V <sub>FB</sub> = V <sub>FBL1</sub> = V <sub>FBL2</sub> = V <sub>FBL3</sub> =<br>V <sub>FBL4</sub> = 1.5V, V <sub>FBL5</sub> = 0V |       | 1.7   | 3.0   | mA    |

| IC Disable Supply Current                                   | EN = AGND                                                                                                                         |       | 200   | 400   | μA    |

| VL REGULATOR                                                |                                                                                                                                   |       |       |       |       |

| VL Output Voltage                                           | 5.5V < V <sub>IN</sub> < 28V, 0 < I <sub>VL</sub> < 30mA                                                                          | 4.75  | 5     | 5.25  | V     |

| VL Undervoltage Lockout Threshold                           | VL rising, 3% hysteresis                                                                                                          | 3.2   | 3.5   | 3.8   | V     |

| CONTROL AND SEQUENCE                                        |                                                                                                                                   |       |       |       |       |

| SEQ, FREQ Input Logic High Level                            |                                                                                                                                   | 2.0   |       |       | V     |

| SEQ, FREQ Input Logic Low Level                             |                                                                                                                                   |       |       | 0.6   | V     |

| SEQ, FREQ Input Leakage Current                             |                                                                                                                                   | -1    |       | +1    | μA    |

| ONL_ Input Threshold                                        | ONL_ rising, 25mV hysteresis                                                                                                      | 1.201 | 1.238 | 1.275 | V     |

| ONL_ Source Current                                         | SEQ = EN = VL, $V_{ONL}$ = 0 to 1.24V                                                                                             | 1.8   | 2.0   | 2.2   | μA    |

| ONL_ Input Leakage Current                                  | SEQ = EN = VL, ONL_ = VL                                                                                                          | -500  |       | +500  | nA    |

| ONL_Input Discharge Clamp Resistance                        | V <sub>SEQ</sub> = 0V                                                                                                             | 800   | 1500  | 3000  | Ω     |

| EN Input Threshold                                          | EN rising, 5% hysteresis                                                                                                          | 1.201 | 1.238 | 1.275 | V     |

| EN Input Leakage Current                                    |                                                                                                                                   | -50   |       | +50   | nA    |

| FAULT DETECTION                                             |                                                                                                                                   |       |       |       |       |

| FB, FBL1, FBL2, FBL3, FBL4<br>Undervoltage Fault Trip Level | FB, FBL1, FBL2, FBL3, FBL4 falling, 25mV hysteresis                                                                               | 1.081 | 1.114 | 1.147 | V     |

| FBL5 Undervoltage Fault Trip Level                          | FBL5 rising, 25mV hysteresis                                                                                                      | 300   | 400   | 500   | mV    |

# Multiple-Output Power-Supply Controllers for LCD Monitors

## **Electrical Characteristics (continued)**

(Circuit of Figure 1,  $V_{IN}$  = 12V,  $V_{EN}$  =  $V_{SEQ}$  = 5V,  $T_A$  = 0°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                                    | CONDITIONS                             | MIN   | ТҮР   | MAX   | UNITS |  |

|----------------------------------------------|----------------------------------------|-------|-------|-------|-------|--|

| Comparator Bandwidth                         | For EN, FB, FBL_                       |       | 10    |       | kHz   |  |

| Duration to Trigger Fault Latch              | For FB, FBL_                           | 51    | 64    | 77    | ms    |  |

| Overcurrent Protection Threshold             | (V <sub>CSH</sub> - V <sub>CSL</sub> ) | 270   | 300   | 330   | mV    |  |

| Overcurrent Sense Common-Mode Range          | V <sub>CSH</sub> , V <sub>CSL</sub>    | 2.7   |       | 28.0  | V     |  |

| CSH Input Current                            | V <sub>CSH</sub> = 2.7V to 28V         |       |       | 100   | μA    |  |

| CSL Input Current                            | $V_{CSL} = V_{CSH} = 12V$              | -50   |       | +50   | nA    |  |

| Overcurrent Sense Filter RC Time<br>Constant |                                        |       | 50    |       | μs    |  |

| THERMAL PROTECTION                           |                                        |       |       |       | •     |  |

| Thermal Shutdown                             | Temperature rising, 15°C hysteresis    |       | 160   |       | °C    |  |

| RESET FUNCTION                               |                                        | •     |       |       | •     |  |

| RSTIN Reset Trip Level                       | RSTIN falling, 25mV hysteresis         | 1.081 | 1.114 | 1.147 | V     |  |

| RSTIN Input Leakage Current                  | V <sub>RSTIN</sub> = 1.5V              | -50   |       | +50   | nA    |  |

| Comparator Bandwidth                         |                                        |       | 10    |       | kHz   |  |

| Reset Timeout Period                         |                                        | 102   | 128   | 154   | ms    |  |

| RESET Output Low Level                       | I <sub>RESET</sub> = -1mA              |       |       | 0.4   | V     |  |

| RESET Output High Leakage                    | V <sub>RESET</sub> = 5V                |       |       | 1     | μA    |  |

| STEP-DOWN CONTROLLER                         |                                        |       |       |       |       |  |

| ERROR AMPLIFIER                              |                                        |       |       |       |       |  |

| FB Regulation Voltage                        |                                        | 1.223 | 1.238 | 1.253 | V     |  |

| Transconductance                             | FB to COMP                             | 70    | 100   | 140   | μS    |  |

| Voltage Gain                                 | FB to COMP                             |       | 200   |       | V/V   |  |

| Minimum Duty Cycle                           |                                        |       | 15    |       | %     |  |

| FB Input Leakage Current                     | V <sub>FB</sub> = 1.5V                 | -50   |       | +50   | nA    |  |

| FB Input Common-Mode Range                   | (Note 2)                               | -0.1  |       | +1.5  | V     |  |

| COMP Output Minimum Voltage                  | V <sub>FB</sub> = 1.5V                 |       | 1     |       | V     |  |

| COMP Output Maximum Voltage                  | V <sub>FB</sub> = 1.175V               |       | 3     |       | V     |  |

| Current-Sense Amplifier Voltage Gain         | V <sub>IN</sub> - V <sub>LX</sub>      | 2.75  | 3.5   | 4.0   | V/V   |  |

| Current-Limit Threshold (Default Mode)       | PGND - LX, ILIM = VL                   | 190   | 250   | 310   | mV    |  |

| Current-Limit Threshold (Adjustable Mode)    | PGND - LX, V <sub>ILIM</sub> = 1.25V   | 190   | 250   | 310   | mV    |  |

| ILIM Input Dual Mode™ Threshold              |                                        | 3.0   | 3.5   | 4.00  | V     |  |

| OSCILLATOR                                   |                                        |       |       |       |       |  |

| Switching Froquency                          | FREQ = AGND                            | 200   | 250   | 300   |       |  |

| Switching Frequency                          | FREQ = VL                              | 425   | 500   | 575   | kHz   |  |

| Maximum Duty Cycle                           | FREQ = AGND                            | 75    | 80    | 88    | 0/_   |  |

| waximum Duty Cycle                           | FREQ = VL                              | 75    | 80    | 88    | - %   |  |

# Multiple-Output Power-Supply Controllers for LCD Monitors

## **Electrical Characteristics (continued)**

(Circuit of Figure 1,  $V_{IN}$  = 12V,  $V_{EN}$  =  $V_{SEQ}$  = 5V,  $T_A$  = 0°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                                                  | CONDITIONS                                               | MIN                   | TYP                    | MAX   | UNITS |

|------------------------------------------------------------|----------------------------------------------------------|-----------------------|------------------------|-------|-------|

| SOFT-START                                                 |                                                          |                       |                        |       |       |

| Step Size                                                  | Measured at FB                                           |                       | 1.238/32               |       | V     |

| Desired                                                    | FREQ = GND                                               | 1024/f <sub>OSC</sub> |                        |       | _     |

| Period                                                     | FREQ = VL                                                |                       | 2048/f <sub>OS</sub> ( |       | S     |

| FET DRIVERS                                                | ·                                                        |                       |                        |       |       |

| DH, DL On-Resistance                                       |                                                          |                       | 3                      | 10    | Ω     |

| DH, DL Output Drive Current                                | Sourcing or sinking, $V_{DH}$ or $V_{DL} = V_{VL} / 2$   |                       | 0.5                    |       | A     |

| LX, BST Leakage Current                                    | $V_{BST} = V_{LX} = V_{IN} = 28V$                        |                       |                        | 20    | μA    |

| LINEAR REGULATOR CONTROLLERS                               | 5                                                        | -                     |                        |       |       |

| POSITIVE LINEAR REGULATOR (LR1)                            | )                                                        |                       |                        |       |       |

| FBL1 Regulation Voltage                                    | V <sub>DRV1</sub> = 5V, I <sub>DRV1</sub> = 100µA        | 1.226                 | 1.245                  | 1.264 | V     |

| FBL1 Input Bias Current                                    | V <sub>FBL1</sub> = 1.5V                                 | -50                   |                        | +50   | nA    |

| FBL1 Effective Load Regulation<br>Error (Transconductance) | V <sub>DRV1</sub> = 5V, I <sub>DRV1</sub> = 100μA to 2mA |                       | -15                    | -2    | %     |

| FBL1 Line Regulation Error                                 | I <sub>DRV1</sub> = 100μA, 5.5V < V <sub>IN</sub> < 28V  |                       |                        | 5     | mV    |

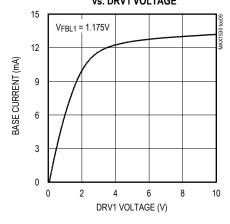

| DRV1 Sink Current                                          | V <sub>FBL1</sub> = 1.175V, V <sub>DRV1</sub> = 5V       | 3                     | 10                     |       | mA    |

| DRV1 Off-Leakage Current                                   | V <sub>FBL</sub> 1 = 1.5V, V <sub>DRV1</sub> = 28V       |                       | 0.1                    | 10    | μA    |

| FBL1 Input Common-Mode Range                               | (Note 2)                                                 | -0.1                  |                        | +1.5  | V     |

| Soft-Start Step Size                                       | Measured at FBL1                                         |                       | 1.238 / 32             | 2     | V     |

|                                                            | FREQ = GND                                               |                       | 1024/f <sub>OS0</sub>  | DSC   |       |

| Soft-Start Period                                          | FREQ = VL                                                |                       | 2048/f <sub>OSC</sub>  |       | S     |

| POSITIVE LINEAR REGULATORS (LF                             | R2 AND LR3)                                              |                       |                        |       |       |

| FBL_Regulation Voltage                                     | V <sub>DRV</sub> = 5V, I <sub>DRV</sub> = 100µA          | 1.226                 | 1.245                  | 1.264 | V     |

| FBL_ Input Bias Current                                    | V <sub>FBL</sub> = 1.5V                                  | -50                   |                        | +50   | nA    |

| FBL_Effective Load Regulation<br>Error (Transconductance)  | $V_{DRV}$ = 5V, $I_{DRV}$ = 50µA to 1mA                  |                       | -1.5                   | -2    | %     |

| FBL_ Line Regulation Error                                 | I <sub>DRV</sub> = 100μA, 5.5V < V <sub>IN</sub> < 28V   |                       |                        | 5     | mV    |

| DRV_ Sink Current                                          | V <sub>FBL</sub> = 1.175V, V <sub>DRV</sub> = 5V         | 2                     | 4                      |       | mA    |

| DRV_Off-Leakage Current                                    | V <sub>FBL</sub> = 1.5V, V <sub>DRV</sub> = 28V          |                       | 0.1                    | 10    | μA    |

| FBL_ Input Common-Mode Range                               | (Note 2)                                                 | -0.1                  |                        | +1.5  | V     |

| Soft-Start Step Size                                       | Measured at FBL_                                         |                       | 1.238 / 32             | 2     | V     |

# Multiple-Output Power-Supply Controllers for LCD Monitors

## **Electrical Characteristics (continued)**

(Circuit of Figure 1,  $V_{IN}$  = 12V,  $V_{EN}$  =  $V_{SEQ}$  = 5V,  $T_A$  = 0°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                                                  | CONDITIONS                                                | MIN   | TYP                                                | MAX   | UNITS |  |

|------------------------------------------------------------|-----------------------------------------------------------|-------|----------------------------------------------------|-------|-------|--|

| Soft-Start Period                                          | FREQ = GND                                                |       | 1024 / f <sub>OS</sub>                             | С     | s     |  |

|                                                            | FREQ = VL                                                 |       | 2048 / f <sub>OS</sub>                             | С     |       |  |

| POSITIVE LINEAR REGULATOR (LR4                             | )                                                         |       |                                                    |       | ,     |  |

| FBL4 Regulation Voltage                                    | V <sub>DRV4</sub> = 5V, I <sub>DRV4</sub> = 500µA         | 1.226 | 1.245                                              | 1.264 | V     |  |

| FBL4 Input Bias Current                                    | V <sub>FBL4</sub> = 1.5V                                  | -50   |                                                    | +50   | nA    |  |

| FBL4 Effective Load Regulation<br>Error (Transconductance) | V <sub>DRV4</sub> = 5V, I <sub>DRV4</sub> = 500µA to 10mA |       | -1.5                                               | -2    | %     |  |

| FBL4 Line Regulation Error                                 | I <sub>DRV4</sub> = 500μA, 5.5V < V <sub>IN</sub> < 28V   |       |                                                    | 5     | mV    |  |

| DRV4 Sink Current                                          | V <sub>FBL4</sub> = 1.175V, V <sub>DRV4</sub> = 5V        | 10    | 28                                                 | 1     | mA    |  |

| DRV4_Off-Leakage Current                                   | V <sub>FBL4</sub> = 1.5V, V <sub>DRV4</sub> = 28V         |       | 0.1                                                | 10    | μA    |  |

| FBL4 Input Common-Mode Range                               | (Note 2)                                                  | -0.1  |                                                    | +1.5  | V     |  |

| Soft-Start Step Size                                       | Measured at FBL4                                          |       | 1.238 / 32                                         | 2     | V     |  |

|                                                            | FREQ = GND                                                |       | 1024 / f <sub>OSC</sub><br>2048 / f <sub>OSC</sub> |       | s     |  |

| Soft-Start Period                                          | FREQ = VL                                                 |       |                                                    |       |       |  |

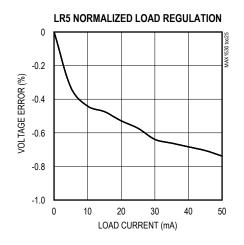

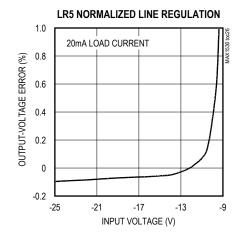

| NEGATIVE LINEAR REGULATOR (LR                              | 5)                                                        | ÷     |                                                    |       |       |  |

| FBL5 Regulation Voltage                                    | V <sub>DRV5</sub> = -10V, I <sub>DRV5</sub> = 100µA       | 100   | 125                                                | 150   | mV    |  |

| FBL5 Input Bias Current                                    | V <sub>FBL5</sub> = 0V                                    | -50   |                                                    | +50   | nA    |  |

| FBL5 Effective Load Regulation<br>Error (Transconductance) | $V_{DRV5}$ = -10V, $I_{DRV5}$ = 50µA to 1mA               |       | -1.5                                               | -2    | %     |  |

| FBL5 Line Regulation Error                                 | I <sub>DRV5</sub> = 100μA, 5.5V < V <sub>IN</sub> < 28V   |       |                                                    | 5     | mV    |  |

| DRV5 Source Current                                        | V <sub>FBL5</sub> = 200mV, V <sub>DRV5</sub> = -10V       | 2     | 9                                                  |       | mA    |  |

| DRV5 Off-Leakage Current                                   | V <sub>FBL5</sub> = 0V, V <sub>DRV5</sub> = -20V          |       | 0.1                                                | 10    | μA    |  |

| FBL5 Input Common-Mode Range                               | (Note 2)                                                  | -0.1  |                                                    | +15   | V     |  |

| Soft-Start Step Size                                       | Measured at FBL5                                          |       | 1.238 / 32                                         | 2     | V     |  |

| Coff Chart Davied                                          | FREQ = AGND                                               |       | 1024 / f <sub>OS</sub>                             | С     |       |  |

| Soft-Start Period                                          | FREQ = VL                                                 |       | 2048 / f <sub>OS</sub>                             | С     | - s   |  |

## **Electrical Characteristics**

(Circuit of Figure 1,  $V_{IN}$  = 12V,  $V_{EN}$  =  $V_{SEQ}$  = 5V,  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 3)

| PARAMETER                            | CONDITIONS                                               | MIN  | TYP | MAX  | UNITS |

|--------------------------------------|----------------------------------------------------------|------|-----|------|-------|

| GENERAL                              |                                                          |      |     |      |       |

| Operating Input Voltage Range        | (Note 1)                                                 | 4.5  |     | 28.0 | V     |

| VL REGULATOR                         |                                                          |      |     |      |       |

| VL Output Voltage                    | 5.5V < V <sub>IN</sub> < 28V, 0 < I <sub>VL</sub> < 30mA | 4.75 |     | 5.25 | V     |

| VL Undervoltage Lockout<br>Threshold | VL rising, 3% hysteresis                                 | 3.2  |     | 3.8  | V     |

# Multiple-Output Power-Supply Controllers for LCD Monitors

## **Electrical Characteristics (continued)**

(Circuit of Figure 1,  $V_{IN}$  = 12V,  $V_{EN}$  =  $V_{SEQ}$  = 5V,  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 3)

| PARAMETER                                      | CONDITIONS                                          | MIN TYP                               | MAX   | UNITS |

|------------------------------------------------|-----------------------------------------------------|---------------------------------------|-------|-------|

| CONTROL AND SEQUENCE                           |                                                     |                                       |       |       |

| ONL_Input Threshold                            | ONL_ rising, 25mV hysteresis                        | 1.201                                 | 1.275 | V     |

| EN Input Threshold                             | EN rising, 5% hysteresis                            | 1.201                                 | 1.275 | V     |

| FAULT DETECTION                                |                                                     | · · ·                                 |       |       |

| FB, FBL1, FBL2, FBL3, FBL4<br>Fault Trip Level | FB, FBL1, FBL2, FBL3, FBL4 falling, 25mV hysteresis | 1.081                                 | 1.147 | V     |

| FBL5 Fault Trip Level                          | FBL5 rising, 25mV hysteresis                        | 300                                   | 500   | mV    |

| Overcurrent Protection Threshold               | (V <sub>CSH</sub> - V <sub>CSL</sub> )              | 270                                   | 330   | mV    |

| RESET FUNCTION                                 |                                                     |                                       |       |       |

| RSTIN Reset Trip Level                         | RSTIN falling, 25mV hysteresis                      | 1.081                                 | 1.147 | V     |

| STEP-DOWN CONTROLLER                           |                                                     |                                       |       |       |

| ERROR AMPLIFIER                                |                                                     |                                       |       |       |

| FB Regulation Voltage                          |                                                     | 1.215                                 | 1.260 | V     |

| Current-Limit Threshold<br>(Default Mode)      | PGND - LX, ILIM = VL                                | 170                                   | 330   | mV    |

| Current-Limit Threshold<br>(Adjustable Mode)   | PGND - LX, V <sub>ILIM</sub> = 1.25V                | 170                                   | 330   | mV    |

| LINEAR REGULATOR CONTROL                       | LERS                                                | · · · · · · · · · · · · · · · · · · · |       |       |

| POSITIVE LINEAR REGULATOR (                    | LR1)                                                |                                       |       |       |

| FBL1 Regulation Voltage                        | V <sub>DRV1</sub> = 5V, I <sub>DRV1</sub> = 100μA   | 1.220                                 | 1.270 | V     |

| FBL1 Input Bias Current                        | V <sub>FBL1</sub> = 1.5V                            | -50                                   | +50   | nA    |

| POSITIVE LINEAR REGULATORS                     | (LR2 AND LR3)                                       | ·                                     |       |       |

| FBL_ Regulation Voltage                        | V <sub>DRV</sub> = 5V, I <sub>DRV</sub> = 100µA     | 1.220                                 | 1.270 | V     |

| FBL_ Input Bias Current                        | V <sub>FBL</sub> = 1.5V                             | -50                                   | +50   | nA    |

| POSITIVE LINEAR REGULATOR (                    | LR4)                                                | ·                                     |       |       |

| FBL4 Regulation Voltage                        | V <sub>DRV4</sub> = 5V, I <sub>DRV4</sub> = 500μA   | 1.220                                 | 1.270 | V     |

| FBL4 Input Bias Current                        | V <sub>FBL4</sub> = 1.5V                            | -50                                   | +50   | nA    |

| NEGATIVE LINEAR REGULATOR                      | (LR5)                                               |                                       |       |       |

| FBL5 Regulation Voltage                        | V <sub>DRV5</sub> = -10V, I <sub>DRV5</sub> = 100µA | 100                                   | 150   | mV    |

| FBL5 Input Bias Current                        | V <sub>FBL5</sub> = 0V                              | -50                                   | +50   | nA    |

| DRV5 Source Current                            | V <sub>FBL5</sub> = 200mV, V <sub>DRV5</sub> = -10V | 2                                     |       | mA    |

|                                                |                                                     |                                       |       |       |

**Note 1:** Operating supply range is guaranteed by VL line regulation test for the range of 5.5V to 28V. Between 4.5V and 5.5V, theV<sub>L</sub> regulator might be in dropout; however, the part continues to operate properly.

Note 2: Guaranteed by design and not production tested.

Note 3: Specifications to -40°C are guaranteed by design and not production tested.

# Multiple-Output Power-Supply Controllers for LCD Monitors

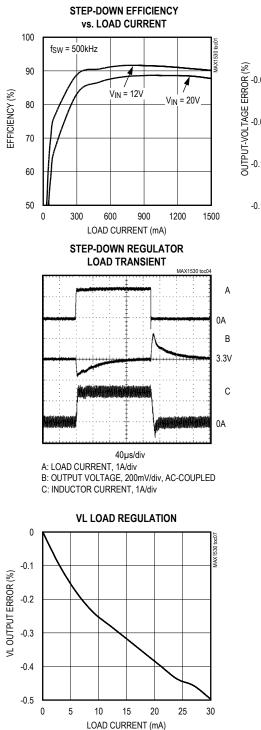

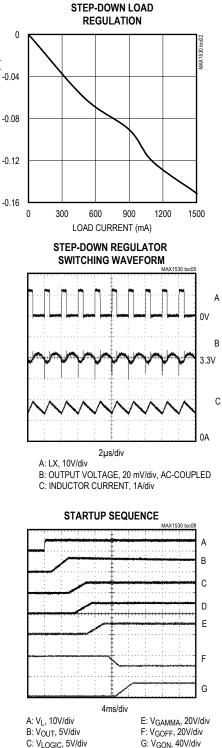

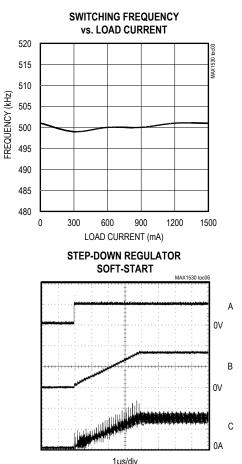

## **Typical Operating Characteristics**

(Circuit of Figure 1; including R5, R6, and D2; T<sub>A</sub> = +25°C, unless otherwise noted.)

D: V<sub>SOURCE</sub>, 20V/div

A: EN, 2V/div B: OUTPUT VOLTAGE, 2V/div C: INDUCTOR CURRENT, 1A/div

LR1 BASE CURRENT vs. DRV1 VOLTAGE

# Multiple-Output Power-Supply Controllers for LCD Monitors

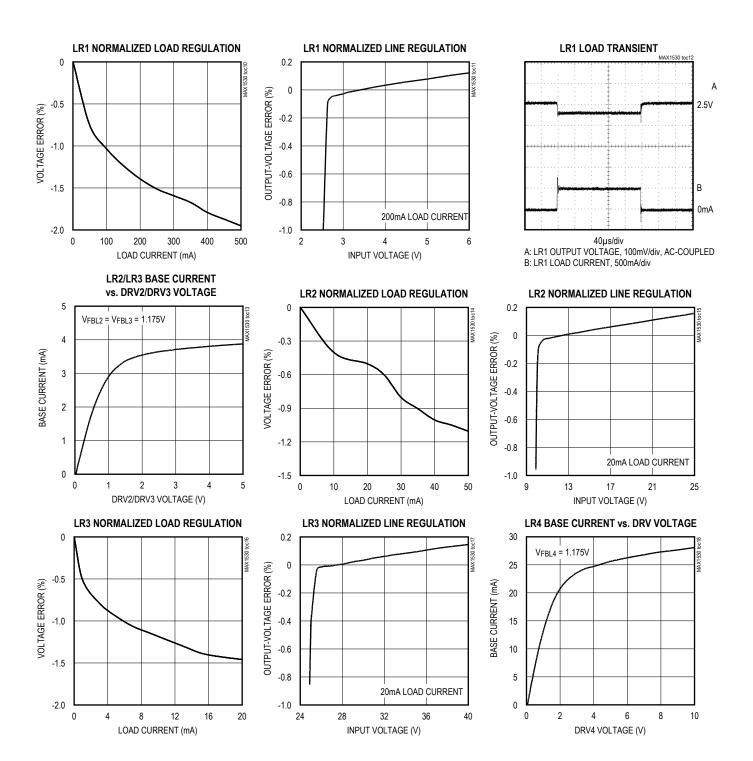

## **Typical Operating Characteristics (continued)**

(Circuit of Figure 1; including R5, R6, and D2;  $T_A = +25^{\circ}C$ , unless otherwise noted.)

# Multiple-Output Power-Supply Controllers for LCD Monitors

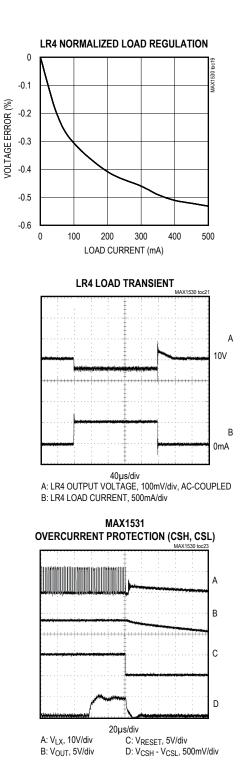

## **Typical Operating Characteristics (continued)**

(Circuit of Figure 1; including R5, R6, and D2; T<sub>A</sub> = +25°C, unless otherwise noted.)

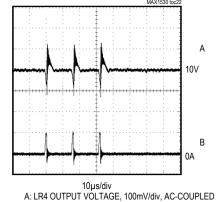

LR4 PULSED LOAD TRANSIENT

A: LR4 OUTPUT VOLTAGE, 100mV/div, AC-COUPLED B: LR4 LOAD CURRENT, 1A/div

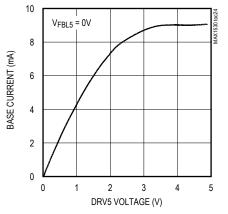

LR5 BASE CURRENT vs. DRV5 VOLTAGE

# Multiple-Output Power-Supply Controllers for LCD Monitors

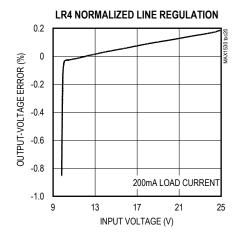

# **Typical Operating Characteristics (continued)**

(Circuit of Figure 1; including R5, R6, and D2;  $T_A = +25^{\circ}C$ , unless otherwise noted.)

# **Pin Description**

| PI              | N  | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|-----------------|----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MAX1530         |    |       | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 1               | 1  | DRV2  | Gamma Linear Regulator (LR2) Base Drive. Open drain of an internal N-channel MOSFET. Connect DRV2 to the base of an external PNP pass transistor to form a positive linear regulator. (See the <i>Pass Transistor Selection</i> section.)                                                                                                                                                                                                                                                                                                                             |  |

| 2               | 2  | FBL2  | Gamma Linear Regulator (LR2) Feedback Input. FBL2 regulates at 1.245V nominal.<br>Connect FBL2 to the center tap of a resistive voltage-divider between the LR2 output<br>and AGND to set the output voltage. Place the divider close to the FBL2 pin.                                                                                                                                                                                                                                                                                                                |  |

| 3               | 3  | FBL3  | Gate-On Linear Regulator (LR3) Feedback Input. FBL3 regulates at 1.245V nominal.<br>Connect FBL3 to the center tap of a resistive voltage-divider between the LR3 output<br>and AGND to set the output voltage. Place the divider close to the FBL3 pin.                                                                                                                                                                                                                                                                                                              |  |

| 4               | 4  | DRV3  | Gate-On Linear Regulator (LR3) Base Drive. Open drain of an internal N-channel MOSFET. Connect DRV3 to the base of an external PNP pass transistor to form a positive linear regulator. (See the <i>Pass Transistor Selection</i> section.)                                                                                                                                                                                                                                                                                                                           |  |

| 5–10,<br>18, 19 | _  | N. C. | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 11              | 11 | RSTIN | Adjustable Reset Input. RESET asserts low when the monitored voltage is less<br>than the reset trip threshold. RESET goes to a high-impedance state only after the<br>monitored voltage remains above the reset trip threshold for the duration of the reset<br>timeout period. Connect RSTIN to the center tap of a resistive voltage-divider between<br>the monitored output voltage and AGND to set the reset trip threshold. The internal<br>RSTIN threshold of 90% of 1.238V allows direct connection of RSTIN to any of the<br>device's positive feedback pins. |  |

# Multiple-Output Power-Supply Controllers for LCD Monitors

# **Pin Description (continued)**

| PI      | PIN     |       | PIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  | FUNCTION |

|---------|---------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|----------|

| MAX1530 | MAX1531 | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |          |

| 12      | 12      | RESET | Open-Drain Reset Output. RESET asserts low when the monitored voltage is less<br>than the reset trip threshold. RESET goes to a high-impedance state only after the<br>monitored voltage remains above the reset trip threshold for the duration of the reset<br>timeout period. RESET also asserts low when VL is less than the VL undervoltage<br>lockout threshold, EN is low, or the thermal, overcurrent or undervoltage fault latches<br>are set.                                                                                                                                                                            |  |          |

| 13      | 13      | COMP  | Step-Down Regulator Compensation Input. A pole-zero pair must be added to compensate the control loop by connecting a series resistor and capacitor from COMP to AGND. (See the <i>Compensation Design</i> section.)                                                                                                                                                                                                                                                                                                                                                                                                               |  |          |

| 14      | 14      | FB    | Step-Down Regulator Feedback Input. FB regulates at 1.238V nominal. Connect FB to the center tap of a resistive voltage-divider between the step-down regulator output and AGND to set the output voltage. Place the divider close to the FB pin.                                                                                                                                                                                                                                                                                                                                                                                  |  |          |

| 15      | 15      | ILIM  | Step-Down Regulator Current-Limit Control Input. Connect this dual-mode input to VL to set the current-limit threshold to its default value of 250mV. The overcurrent comparator compares the voltage across the low-side N-channel MOSFET with the current-limit threshold. Connect ILIM to the center tap of a resistive voltage-divider between VL and AGND to adjust the current-limit threshold to other values. In adjustable mode, the actual current-limit threshold is 1/5th of the voltage at ILIM over a 0.25V to 3.0V range. The dual- mode threshold for switchover to the 250mV default value is approximately 3.5V. |  |          |

| 16      | 16      | ONL2  | Gamma Linear Regulator (LR2) Enable Input. When EN is above its enable threshold, VL is above its UVLO threshold, and ONL2 is greater than the internal reference, LR2 is enabled. Drive ONL2 with a logic signal or, for automatic sequencing, connect a capacitor from ONL2 to AGND. If SEQ is high, EN is above its threshold, and VL is above its UVLO threshold, an internal $2\mu A$ (typ) current source charges the capacitor. Otherwise, an internal switch discharges the capacitor. Connecting various capacitors to each ONL_ pin allows the programming of the startup sequence.                                      |  |          |

| 17      | 17      | ONL3  | Gate-On Linear Regulator (LR3) Enable Input. When EN is above its enable threshold, VL is above its UVLO threshold, and ONL3 is greater than the internal reference, LR3 is enabled. Drive ONL3 with a logic signal or, for automatic sequencing, connect a capacitor from ONL3 to AGND. If SEQ is high, EN is above its threshold, and VL is above its UVLO threshold, an internal $2\mu A$ (typ) current source charges the capacitor. Otherwise, an internal switch discharges the capacitor. Connecting various capacitors to each ONL_ pin allows the programming of the startup sequence.                                    |  |          |

| 20      | 20      | PGND  | Power Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |          |

| 21      | 21      | DL    | Low-Side Gate Driver Output. DL drives the synchronous rectifier of the step-down regulator. DL swings from PGND to VL. DL remains low until VL rises above the UVLO threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |          |

| 22      | 22      | LX    | Step-Down Regulator Current-Sense Input. The IC's current-sense amplifier inputs for current-mode control connect to IN and LX. Connect IN and LX directly to the high-side N- channel MOSFET drain and source, respectively. The low-side current-limit comparator inputs connect to LX and PGND to sense voltage across a low-side N-channel MOSFET.                                                                                                                                                                                                                                                                             |  |          |

# Multiple-Output Power-Supply Controllers for LCD Monitors

#### PIN NAME FUNCTION MAX1530 MAX1531 High-Side Gate Driver Output. DH drives the main switch of the step-down regulator. DH 23 23 DH swings from LX to BST. Step-Down Regulator Boostrap Capacitor Connection for High-Side Gate Driver. 24 24 BST Connect a 0.1µF ceramic capacitor from BST to LX. Sequence Control Input for LR2, LR3, LR4, and LR5. Controls the current sources and 25 SEQ 25 switches that charge and discharge the capacitors connected to the ONL\_ pins. Oscillator Frequency Select Input. Connect FREQ to VL for 500kHz operation. Connect FREQ 26 26 FREQ to AGND for 250kHz operation. Main Input Voltage (+4.5V to 28V). Bypass IN to AGND with a 1µF ceramic capacitor 27 27 IN close to the pins. IN powers the VL linear regulator. Connect IN to the drain of the highside MOSFET (for current sense) through a 1Ω resistor. Internal 5V Linear Regulator Output. Connect a minimum 1µF ceramic capacitor from VL 28 VL to AGND. Place the capacitor close to the pins. VL can supply up to 30mA for gate 28 drive and external loads. VL remains active when EN is low. AGND Analog Ground 29 29 Enable Input. This general-purpose on/off control input has an accurate 1.238V (tvp) rising threshold with 5% hysteresis. This allows EN to monitor an input voltage level or other analog parameter. If EN is less than its threshold, then the main step-down and ΕN 30 30 all linear regulators are turned off. VL and the internal reference remain active when EN is low. The rising edge of EN clears any latched faults except for a thermal fault, which is cleared only by cycling the input power. An internal filter with a 10µs time constant prevents short glitches from accidentally clearing the fault latch. Low-Voltage Logic Linear Regulator (LR1) Feedback Input. FBL1 regulates at 1.245V nominal. Connect FBL1 to the center tap of a resistive voltage-divider between LR1 31 31 FBL1 output AGND to set the output voltage. Place the divider close to the FBL1 pin. LR1 starts automatically after the step-down converter soft-start ends. Low-Voltage Logic Linear Regulator (LR1) Base Drive. Open drain of an internal DRV1 N-channel MOSFET. Connect DRV1 to the base of an external PNP pass transistor. 32 32 (See the Pass Transistor Selection section.) Overcurrent Protection Positive Input. CSH is also the supply input for the overcurrent sense block. CSH and CSL can be used to sense any current in the application circuit and to shut the device down in an overcurrent condition. This feature is typically used to protect the main input or the input to one of the linear regulators since they do not have their own current limits. Insert an appropriate sense resistor in series with the 5 CSH protected input and connect CSH and CSL to its positive and negative terminals. The controller sets the fault latch when $V_{CSH}$ - $V_{CSL}$ exceeds the 300mV (typ) overcurrent threshold. An internal lowpass filter prevents large currents of short duration (less than 50µs) or noise glitches from setting the latch. If the overcurrent protection is not used, connect CSH and CSL to VL. 6 CSL Overcurrent Protection Negative Input. See CSH above.

## **Pin Description (continued)**

# Multiple-Output Power-Supply Controllers for LCD Monitors

# **Pin Description (continued)**

| PIN     |         |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|---------|---------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MAX1530 | MAX1531 | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| _       | 7       | FBL4 | Source Drive Linear Regulator (LR4) Feedback Input. FBL4 regulates at 1.245V nominal. Connect FBL4 to the center tap of a resistive voltage-divider between the LR4 output and AGND to set the output voltage. Place the divider close to the FBL4 pin.                                                                                                                                                                                                                                                                                                                                              |  |  |

| _       | 8       | DRV4 | Source Drive Linear Regulator (LR4) Base Drive. Open drain of an internal N-channel MOSFET. Connect DRV4 to the base of an external PNP pass transistor to form a positive linear regulator. (See the <i>Pass Transistor Selection</i> section.)                                                                                                                                                                                                                                                                                                                                                     |  |  |

| _       | 9       | FBL5 | Gate-Off Linear Regulator (LR5) Feedback Input. FBL5 regulates at 125mV nominal.<br>Connect FBL5 to the center tap of a resistive voltage-divider between the LR5 output<br>and the internal 5V linear regulator output (VL) to set the output voltage. Place the<br>divider close to the FBL5 pin.                                                                                                                                                                                                                                                                                                  |  |  |

| _       | 10      | DRV5 | Gate-Off Linear Regulator (LR5) Base Drive. Open drain of an internal P-channel MOSFET. Connect DRV5 to the base of an external NPN pass transistor to form a negative linear voltage regulator. (See the <i>Pass Transistor Selection</i> section.)                                                                                                                                                                                                                                                                                                                                                 |  |  |

| _       | 18      | ONL4 | Source Drive Linear Regulator (LR4) Enable Input. When EN is above its enable threshold, VL is above its UVLO threshold, and ONL4 is greater than the internal reference, LR4 is enabled. Drive ONL4 with a logic signal or, for automatic sequencing, connect a capacitor from ONL4 to AGND. If SEQ is high, EN is above its threshold, and VL is above its UVLO threshold, an internal $2\mu$ A (typ) current source charges the capacitor. Otherwise, an internal switch discharges the capacitor. Connecting various capacitors to each ONL_ pin allows the programming of the startup sequence. |  |  |

| _       | 19      | ONL5 | Gate-Off Linear Regulator (LR5) Enable Input. When EN is above its enable threshold, VL is above its UVLO threshold, and ONL5 is greater than the internal reference, LR5 is enabled. Drive ONL5 with a logic signal or, for automatic sequencing, connect a capacitor from ONL5 to AGND. If SEQ is high, EN is above its threshold, and VL is above its UVLO threshold, an internal $2\mu A$ (typ) current source charges the capacitor. Otherwise, an internal switch discharges the capacitor. Connecting various capacitors to each ONL_ pin allows the programming of the startup sequence.     |  |  |

| _       | _       | EP   | Exposed Paddle. Internally connected to GND. Connect EP to a large ground plane to improve thermal dissipation. Do not use as the main ground connection of the IC.                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

# Multiple-Output Power-Supply Controllers for LCD Monitors

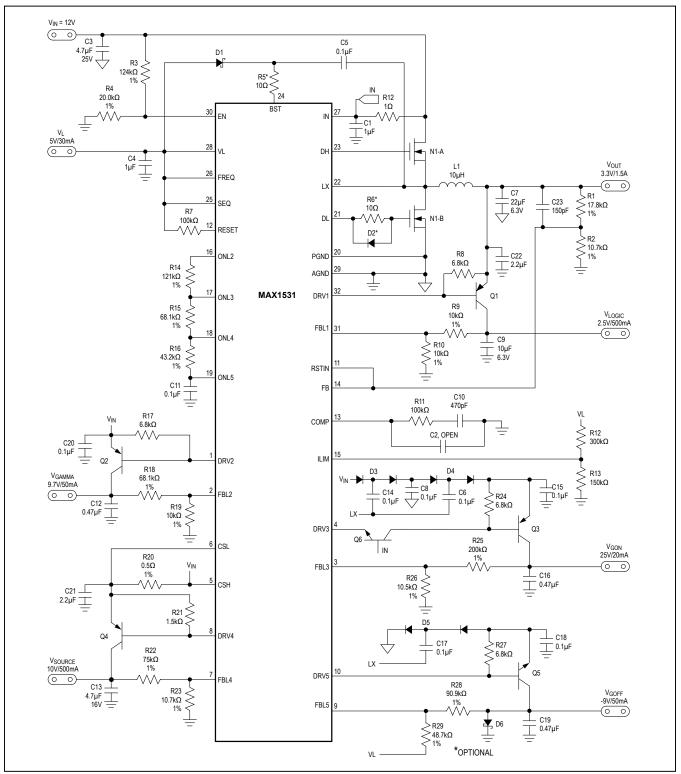

Figure 1. MAX1531 Standard Application Circuit

# Multiple-Output Power-Supply Controllers for LCD Monitors

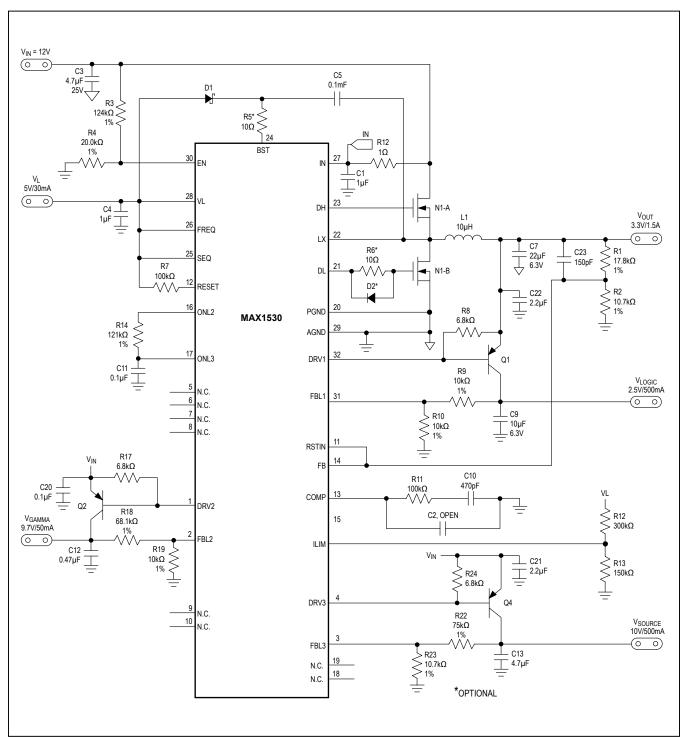

Figure 2. MAX1530 Standard Application Circuit

# Multiple-Output Power-Supply Controllers for LCD Monitors

| DESIGNATION | DESCRIPTION                                                                            |  |

|-------------|----------------------------------------------------------------------------------------|--|

| C3          | 4.7μF, 25V X7R ceramic capacitor<br>(1210) TDK C3225X7R1E475K                          |  |

| C7          | 22µF, 6.3V X7R ceramic capacitor<br>TDK C3216X7R0J226M                                 |  |

| C9          | 10µF, 6.3V X5R ceramic capacitor<br>TDK C2012X5R0J106M                                 |  |

| C12, C19*   | 0.47µF, 16V X7R ceramic capacitors<br>(0805) TDK C2012X7R1C474K                        |  |

| C13         | 4.7μF, 16V X7R ceramic capacitor<br>TDK C3216X7R1C475K                                 |  |

| C21, C22    | 2.2µF, 25V X7R ceramic capacitors<br>(1206) TDK C3216X7R1C475M                         |  |

| D1, D6*     | 100mA, 30V Schottky diodes (SOD523)<br>Central Semiconductor CMOSH-3                   |  |

| D2          | 100mA, 75V, small-signal switching<br>diode, SOT23 Fairchild Semiconductor<br>MMBD4148 |  |

## **Table 1. Selected Component List**

| DESIGNATION   | DESCRIPTION                                                                      |

|---------------|----------------------------------------------------------------------------------|

| D3*, D4*, D5* | 200mA, 25V dual Schottky diodes (SOT23) Fairchild BAT54S                         |

| L1            | 10µH, 2.3A (DC) inductor<br>Sumida CDR7D28MN-100                                 |

| N1            | 2.5A, 30V dual N-channel MOSFET<br>(6-pin Super SOT)<br>Fairchild FDC6561AN      |

| Q1, Q4        | 3A, 60V low-saturation PNP bipolar<br>transistors<br>(SOT-223) Fairchild NZT660A |

| Q2, Q3*       | 200mA, 40V PNP bipolar transistors<br>(SOT23) Fairchild MMBT3906                 |

| Q5*, Q6*      | 200mA, 40V NPN bipolar transistors (SOT23) Fairchild MMBT3904                    |

\*For MAX1531 only.

## **Table 2. Component Suppliers**

| SUPPLIER     | PHONE        | FAX          | WEBSITE                |

|--------------|--------------|--------------|------------------------|

| Central Semi | 516-435-1110 | 516-435-1824 | www.centralsemi.com    |

| Fairchild    | 888-522-5372 | 972-910-8036 | www.fairchildsemi.com  |

| Sumida       | 847-956-0666 | 847-956-0702 | www.sumida.com         |

| ТДК          | 847-803-6100 | 847-390-4405 | www.components.tdk.com |

## **Standard Application Circuit**

The standard application circuit (Figure 1) of the MAX1531 is a complete power-supply system for TFT LCD monitors. The circuit generates a 3.3V/1.5A main output, a 2.5V/500mA output for the timing controller and digital sections of source/gate drive ICs, a 10V/500mA source drive supply voltage, a 9.7V/50mA gamma reference, a 25V/20mA gate-on voltage, and a -10V/50mA gate-off voltage. The input voltage is 12V ±10%. Table 1 lists the selected components and Table 2 lists the component suppliers. The standard application circuit (Figure 2) of the MAX1530 is similar to the MAX1531 application circuit except that gate-on and gate-off voltages are eliminated.

## **Detailed Description**

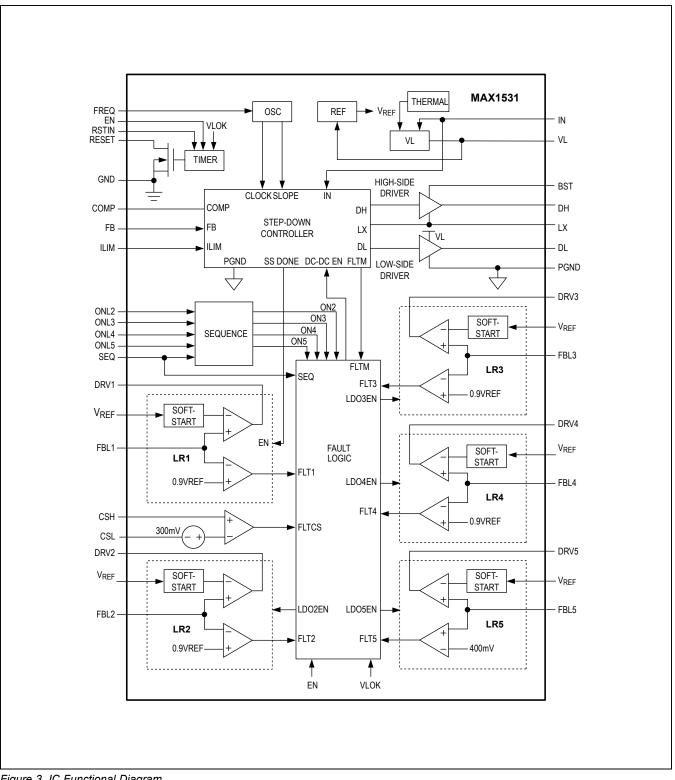

The MAX1530/MAX1531 power-supply controllers provide logic and bias power for LCD monitors. <u>Figure 3</u> shows the IC functional diagram. The main step-down controller employs a current-mode PWM control method to ease compensation requirements and provide excellent load-and line-transient response. The use of synchronous rectification yields excellent efficiency.

The MAX1530 includes three analog gain blocks to control three auxiliary positive linear regulators, and the MAX1531 includes five analog gain blocks to control four positive and one negative linear regulators. Use the positive gain blocks to generate low-voltage rails directly from the input voltage or the main step-down converter output, or higher voltages using charge pumps attached to the switching node or

# Multiple-Output Power-Supply Controllers for LCD Monitors

Figure 3. IC Functional Diagram

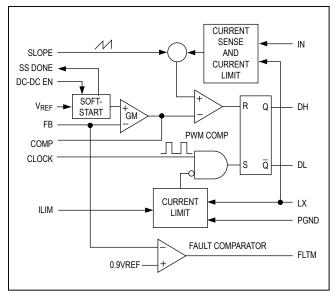

Figure 4. Step-Down Controller Block Diagram

extra windings coupled to the step-down converter inductor. The negative gain block (MAX1531) can be used in conjunction with a charge pump or coupled winding to generate the LCD gate-off voltage or other negative supplies.

## **Step-Down Controller**

The MAX1530/MAX1531 include step-down controllers that use a fixed-frequency current-mode PWM control scheme (Figure 4). An internal transconductance amplifier establishes an integrated error voltage at the COMP pin. The heart of the current-mode PWM controller is an open-loop comparator that compares an integrated voltage-feedback signal with an amplified current-sense signal plus a slope-compensation ramp. At each rising edge of the internal clock, the high-side MOSFET turns on until the PWM comparator trips or the maximum duty cycle is reached. During this on-time, current ramps up through the inductor, sourcing current to the output and storing energy in a magnetic field. The current-mode feedback system regulates the peak inductor current as a function of the output voltage error signal. Since the average inductor current is nearly the same as the peak inductor current (assuming that the inductor value is relatively high to minimize ripple current), the circuit acts as a switch-mode transconductance amplifier. That pushes the output LC filter pole, normally found in a voltage-mode PWM, to a higher frequency. To preserve loop stability, the slopecompensation ramp is summed into the main PWM comparator.

# Multiple-Output Power-Supply Controllers for LCD Monitors

During the second half of the cycle, the high-side MOSFET turns off and the low-side N-channel MOSFET turns on. Now the inductor releases the stored energy as its current ramps down, providing current to the output. The output capacitor stores charge when the inductor current exceeds the load current and discharges when the inductor current exceeds the selected current limit (see *Current Limit Circuit*), the high-side MOSFET is not turned on at the rising edge of the clock and the lowside MOSFET remains on to let the inductor current ramp down.

Under light-load conditions, the MAX1530/MAX1531 maintain a constant switching frequency to minimize cross-regulation errors in applications that use a transformer. The low-side gate-drive waveform is the complement of the high-side gate-drive waveform, which causes the inductor current to reverse under light loads.

## **Current-Sense Amplifier**

The MAX1530/MAX1531s' current-sense circuit amplifies the current-sense voltage generated by the highside MOSFET's on-resistance. This amplified current-sense signal and the internal slope compensation signal are summed together and fed into the PWM comparator's inverting input. Place the high-side MOSFET near the controller, and connect IN and LX to the MOSFET using Kelvin-sense connections to guarantee current-sense accuracy and improve stability.

## **Current-Limit Circuit**

The MAX1530/MAX1531 include two current-limit circuits that use the two MOSFETs' on-resistances as currentsensing elements (Figure 4). The high-side MOSFET's voltage is used with a fixed 400mV (typ) current- limit threshold during the high-side on-times. The low-side MOSFET's voltage is used with an adjustable current-limit threshold during the low-side on-times. Using both circuits together ensures that the current is always measured and controlled.

The high-side MOSFET current limit employs a peak current limit. If the voltage across the high-side MOSFET, measured from IN to LX, exceeds the 400mV threshold during an on-time, the high-side MOSFET turns off and the low-side MOSFET turns on.

The low-side MOSFET current-limit circuit employs a "valley" current limit. If the voltage across the low-side MOSFET, measured from LX to PGND, exceeds the low-side threshold at the end of a low-side on-time, the low-side MOSFET remains on and the high-side MOSFET stays off for the entire next cycle.

# Multiple-Output Power-Supply Controllers for LCD Monitors

The ILIM pin is a dual-mode input. When ILIM is connected to VL, a default low-side current limit of 250mV typ) is used. If ILIM is connected to a voltage between 250mV and 3V, the low-side current limit is typically 1/5th the ILIM voltage.

The MAX1530/MAX1531s' current limits are comparatively inaccurate, since the maximum load current is a function of the MOSFETs' on-resistances and the inductor value, as well as the accuracy of the two thresholds. However, using MOSFET current sensing reduces both cost and circuit size and increases efficiency, since sense resistors are not needed.

## MOSFET Gate Drivers (DH, DL)

The DH and DL drivers are optimized for driving moderate-size high-side and low-side MOSFETs. Adaptive dead-time circuits monitor the DL and DH drivers and prevent either FET from turning on until the other is fully off. This algorithm allows operation without shootthrough with a wide range of MOSFETs, minimizing delays and maintaining efficiency. When the gates are turning off, there must be low-resistance, low-inductance paths from the gate drivers to the MOSFET gates for the adaptive dead-time circuit to work properly. Otherwise, the sense circuitry in the MAX1530/ MAX1531 interpret the MOSFET gate as "off" while gate charge actually remains. Use short, wide traces measuring less than 50 squares (at least 20 mil wide if the MOSFET is 1in from the device). It is advantageous to slow down the turn-on of both gate drivers if there is noise coupling between the switching regulator and the linear regulators. The noise coupling can result in excessive switching ripple on the linear regulator outputs. Slowing down the turn-on of the gate drivers proves to be an effective way of reducing the output ripple. Take care to ensure that the turn- off times are not affected at the same time. As explained above, slowing down the turn-off times may result in shoot-through problems. In Figure 1, a  $10\Omega$  resistor (R5) is inserted in series with the BST pin to slow down the turn-on of the high-side MOSFET (N1-B) without affecting the turn-off. A  $10\Omega$  resistor (R6) is also inserted between DL and the gate of the low-side MOSFET (N1-A) to slow its turn-on. Because the gate resistor would slow down the turn-off time, connect a switching diode (D2) (such as 1N4148) in parallel with the gate resistor as shown in Figure 1 to prevent potential shoot-through.

### High-Side Gate-Drive Supply (BST)

A flying-capacitor bootstrap circuit generates gate-drive voltage for the high-side N-channel switch (Figure 1). The capacitor C5 between BST and LX is alternately charged

from the VL supply and placed parallel to the high-side MOSFET's gate-source terminals.

On startup, the synchronous rectifier (low-side MOS-FET) forces LX to ground and charges the boost capacitor from VL through diode D1. On the second half-cycle, the switch-mode power supply turns on the high-side MOSFET by closing an internal switch between BST and DH. This provides the necessary gate-to-source voltage to turn on the high-side switch, an action that boosts the 5V gate-drive signal above the input voltage.

### **Oscillator Frequency Selection (FREQ)**

The FREQ pin can be used to select the switching frequency of the step-down regulator. Connect FREQ to VL for 500kHz operation. Connect FREQ to AGND for 250kHz operation. The 500kHz operation minimizes the size of the inductor and capacitors. The 250kHz operation improves efficiency by 2% to 3%.

### **Linear Regulator Controllers**

The MAX1530/MAX1531 include three positive linear regulator controllers, LR1, LR2, and LR3. These linear regulator controllers can be used with external pass transistors to regulate supplies for TFT LCDs. The MAX1531 includes an additional positive linear regulator controller (LR4) and a negative linear regulator controller (LR5).

### Low-Voltage Logic Regulator Controller (LR1)

LR1 is an analog gain block with an open-drain N-channel output. It drives an external PNP pass transistor with a  $6.8k\Omega$  base-to-emitter resistor. Its guaranteed base drive sink current is at least 3mA. The regulator including transistor Q1 in Figure 1 uses a 10µF output capacitor and is designed to deliver 500mA at 2.5V.

LR1 is typically used to generate low-voltage logic supplies for the timing controller and the digital sections of the TFT LCD source/gate driver ICs.

LR1 is enabled when the soft-start of the main stepdown regulator is complete. (See the Startup Sequence (ONL\_,SEQ) section.) Each time it is enabled, the controller goes through a soft-start routine that ramps up its internal reference DAC. (See the *Soft-Start* section.)

### Gamma Regulator Controller (LR2)

LR2 is an analog gain block with an open-drain N-channel output. It drives an external PNP pass transistor with a  $6.8k\Omega$  base-to-emitter resistor. Its guaranteed base drive sink current is at least 2mA. The regulator including transistor Q2 in Figure 1 uses a  $0.47\mu$ F output capacitor and is designed to deliver 50mA at 9.7V.

# Multiple-Output Power-Supply Controllers for LCD Monitors

LR2 is typically used to generate the TFT LCD gamma reference voltage, which is usually 0.3V below the source drive supply voltage.

LR2 is enabled when the step-down regulator is enabled and the voltage on ONL2 exceeds ONL2 input threshold (1.238V typ). (See the *Startup Sequence (ONL\_,SEQ)* section.) Each time it is enabled, the controller goes through a soft-start routine that ramps up its internal reference DAC. (See the *Soft-Start* section).

### Linear Regulator Controller (LR3)

LR3 is an analog gain block with an open-drain N channel output. It drives an external PNP pass transistor with a  $6.8k\Omega$  base-to-emitter resistor. Its guaranteed base drive sink current is at least 2mA. The regulator, including Q3 in Figure 1, uses a  $0.47\mu$ F output capacitor and is designed to deliver 20mA at 25V. The regulator including Q3 in Figure 2 uses a  $4.7\mu$ F output capacitor and is designed to deliver 500mA at 10V.

For the MAX1531 (Figure 1), LR3 is typically used to generate the TFT LCD gate driver's gate-on voltage. A sufficient input voltage can be produced using a chargepump circuit as shown in Figure 1. Note that the voltage rating of the DRV3 output is 28V. If higher voltages are present, an external cascode NPN transistor (Q6) should be used with the emitter connected to DRV3, the base to V<sub>IN</sub> (which is the connection point of C1 and R12 in Figure 1), and the collector to the base of the PNP pass transistor (Figure 1). For the MAX1530 (Figure 2), LR3 is typically used to generate the TFT LCD source drive supply voltage. The input for this regulator can come directly from the input supply, be produced from an external step-up regulator, or from an extra winding coupled to the main step-down regulator inductor.

LR3 is enabled when the step-down regulator is enabled and the voltage on ONL3 exceeds the ONL3 input threshold (1.238V typ). (See the *Startup Sequence (ONL\_,SEQ*) section.) Each time it is enabled, the controller goes through a soft-start routine that ramps up its internal reference DAC. (See the *Soft-Start* section.)

# Source Drive Regulator Controller (LR4) (MAX1531 Only)

LR4 is an analog gain block with an open-drain Nchannel output. It drives an external PNP pass transistor with a  $1.5k\Omega$  base-to-emitter resistor. Its guaranteed base drive sink current is at least 10mA. The regulator including Q4 in Figure 1 uses a  $4.7\mu$ F output capacitor and is designed to deliver 500mA at 10V. The regulator's fast transient response allows it to handle brief peak currents up to 2A.

LR4 is typically used to generate the TFT LCD source drive supply voltage. The input for this regulator can come directly from the input supply, be produced from an external step-up regulator, or from an extra winding coupled to the main step-down regulator inductor. LR4 is enabled when the step-down regulator is enabled and the voltage on ONL4 exceeds the ONL4 input threshold (1.238V typ). (See the *Startup Sequence (ONL\_,SEQ*) section.) Each time it is enabled, the regulator goes through a soft-start routine that ramps up its internal reference DAC from 0V to 1.238V (typ). (See the *Soft-Start* section.)

The standard application circuit in <u>Figure 1</u> powers the LR4 regulator directly from the input supply and uses the MAX1531's general-purpose overcurrent protection function to protect the input supply from excessive load currents. (See the *Overcurrent Protection* section.)

# Gate-Off Regulator Controller (LR5) (MAX1531 Only)

LR5 is an analog gain block with an open-drain P-channel output. It drives an external NPN pass transistor with a  $6.8k\Omega$  base-to-emitter resistor. Its guaranteed base drive sink current is at least 2mA. The regulator including Q5 in Figure 1 uses a  $0.47\mu$ F output capacitor and is designed to deliver 10mA at -10V.

LR5 is typically used to generate the TFT LCD gate driver's gate-off voltage. A negative input voltage can be produced using a charge-pump circuit as shown in Figure 1. Use as many stages as necessary to obtain the required output voltage.

LR5 is enabled when the step-down regulator is enabled and the voltage on ONL5 exceeds the ONL5 input threshold (1.238V typ). (See the *Startup Sequence (ONL\_,SEQ)* section.) Each time it is enabled, the regulator goes through a soft-start routine that ramps down its internal reference DAC from VL to 125mV (typ). (See the *Soft-Start* section.)

## Internal 5V Linear Regulator (VL)

All MAX1530/MAX1531 functions, except the thermal sensor, are internally powered from the on-chip, lowdropout 5V regulator. The maximum regulator input voltage (V<sub>IN</sub>) is 28V. Bypass the regulator's output (VL) with at least a 1µF ceramic capacitor to AGND. The V<sub>IN</sub>-to-VL dropout voltage is typically 200mV, so when V<sub>IN</sub> is less than 5.2V, VL is typically V<sub>IN</sub> - 200mV. The internal linear regulator can source up to 30mA to supply the device, power the low-side gate driver, charge the external boost capacitor, and supply small external loads. When driving particularly large MOSFETs, little or no regulator current may be available for external loads. For example, when

# Multiple-Output Power-Supply Controllers for LCD Monitors

switched at 500kHz, large MOSFETs with a total of 40nC total gate charge would require  $40nC \times 500kHz$ , which is approximately 20mA.

## **On/Off Control (EN)**

The EN pin has an accurate 1.238V (typ) rising threshold with 5% hysteresis. The accurate threshold allows it to be used to monitor the input voltage or other analog signals of interest. If  $V_{EN}$  voltage is less than its threshold, then the step-down regulator and all linear regulators are turned off. VL and the internal reference remain active when EN is low to allow an accurate EN threshold. A rising edge on the pin clears any latched faults except for a thermal fault, which is cleared only by cycling the input power.

### **Undervoltage Lockout**

If VL drops below 3.4V (typ), the MAX1530/MAX1531 assume that the supply voltage is too low to make valid decisions. Therefore, the undervoltage lockout (UVLO) circuitry turns off all the internal bias supplies. Switching is inhibited, and the DL and DH gate drivers are forced low. After VL rises above 3.5V (typ), the fault and thermal shutdown latches are cleared and startup begins if EN is above its threshold.

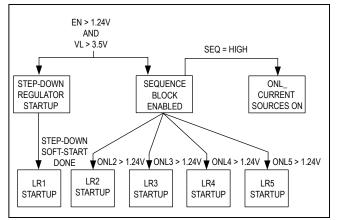

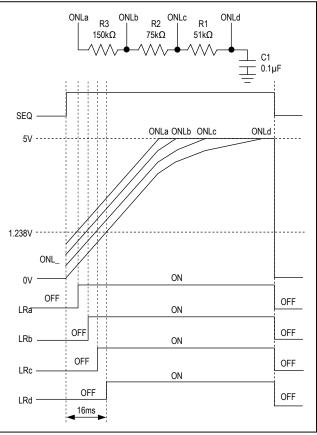

## Startup Sequence (ONL\_, SEQ)

The MAX1530/MAX1531 are not enabled unless all four of the following conditions are met: 1) VL exceeds the UVLO threshold, 2) EN is above 1.238V, 3) the fault latch is not set, and 4) the thermal shutdown latch is not set. After all four conditions are met, the step-down controller starts switching and enables soft-start (Figure 5). After the step-down regulator soft-start is done, the lowvoltage logic linear regulator controller (LR1) soft-starts.

The remaining linear regulator controllers and the sequence block that can be used to control them are enabled at the same time as the step-down regulator. The SEQ logic input is used in combination with the ONL\_ pins to control the startup sequence. When SEQ is high and the sequence block is enabled, each ONL\_ pin sources  $2\mu$ A (typ). When the voltage on an ONL\_ pin reaches 1.238V (typ), its respective linear regulator controller (LR\_) is enabled. When SEQ is low or the sequence block is not enabled, each ONL\_ pin is connected to ground through a 1.5k $\Omega$  internal MOSFET.