# PMIC with Ultra-Low I<sub>Q</sub> Voltage Regulators and Battery Charger for Small Lithium Ion Systems

### **General Description**

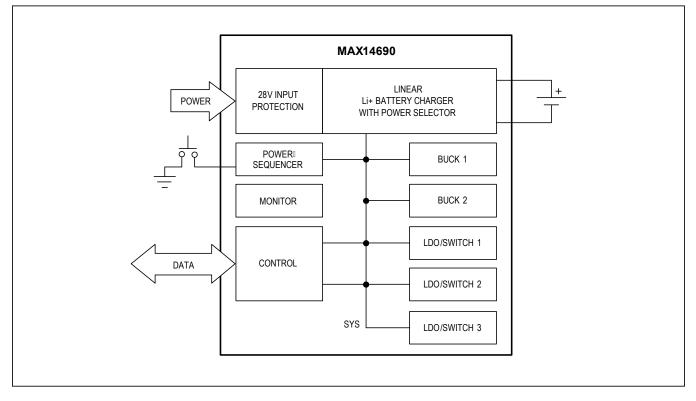

The MAX14690 is a battery-charge-management solution ideal for low-power wearable applications. The device includes a linear battery charger with a smart power selector and several power-optimized peripherals. The MAX14690 features two ultra-low-power buck regulators with a typical quiescent current of 900nA. In addition, three ultra-low power low-dropout (LDO) linear regulators, with a typical quiescent current of 600nA are included. In total, the MAX14690 can provide up to five regulated voltages, each with an ultra-low quiescent current, critical to battery life for the unique power profile in 24/7 operation devices, such as those in the wearable market.

The battery charger features a smart power selector that allows operation on a dead battery when connected to a power source. To avoid overloading a power adapter, the input current to the smart power selector is limited based on an I<sup>2</sup>C register setting. If the charger power source is unable to supply the entire system load, the smart power control circuit supplements the system load with current from the battery.

The two synchronous, high-efficiency step-down buck regulators feature a fixed-frequency PWM mode for tighter regulation and a burst mode for increased efficiency during light-load operation. The output voltage of these regulators can be programmed through I<sup>2</sup>C with the default preconfigured.

The three configurable LDOs each have a dedicated input pin. Each LDO regulator output voltage can be programmed through I<sup>2</sup>C with the default preconfigured. The linear regulators can also be configured to operate as power switches that may be used to disconnect the quiescent load of the system peripherals.

The MAX14690 features a programmable power controller that allows the device to be configured for applications that require the device be in a true-off, or always-on, state. The controller also provides a delayed reset signal and voltage sequencing.

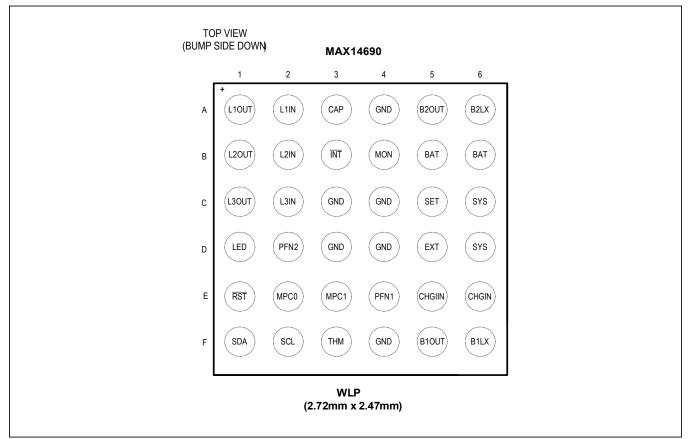

The MAX14690 is available in a 36-bump, 0.4mm pitch, 2.72mm x 2.47mm wafer-level package (WLP).

Ordering Information appears at end of data sheet.

### **Benefits and Features**

- Extend System Use Time Between Battery Charging

- Dual Ultra-Low-I<sub>Q</sub> 200mA Buck Regulators

Output Programmable from 0.8V to 1.8V and 1.5V to 3.3V

- 0.9µA (typ) Quiescent Current

- · Automatic Burst or Forced-PWM Modes

- Three Ultra-Low-IQ 100mA LDOs

- Output Programmable from 0.8V to 3.6V

- 0.6µA (typ) Quiescent Current

- 2.7V to 5.5V Input with Dedicated Pin

- Easy-to-Implement Li+ Battery Charging

- · Smart Power Selector

- 28V/-5.5V Tolerant Input

- Thermistor Monitor

- Minimize Solution Footprint Through High Integration

- Provides Five Regulated Voltage Rails

- Switch Mode Option on Each LDO

- Optimize System Control

- Monitors Pushbutton for Ultra-Low Power Mode

- · Power-On Reset Delay and Voltage Sequencing

- On-Chip Voltage Monitor Multiplexer

### **Applications**

- Wearable Electronics

- Fitness Monitors

- Portable Medical Devices

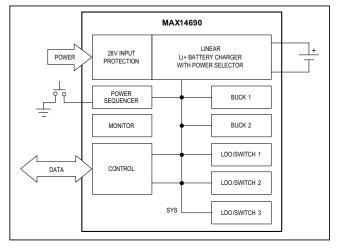

### **Block Diagram**

# PMIC with Ultra-Low I<sub>Q</sub> Voltage Regulators and Battery Charger for Small Lithium Ion Systems

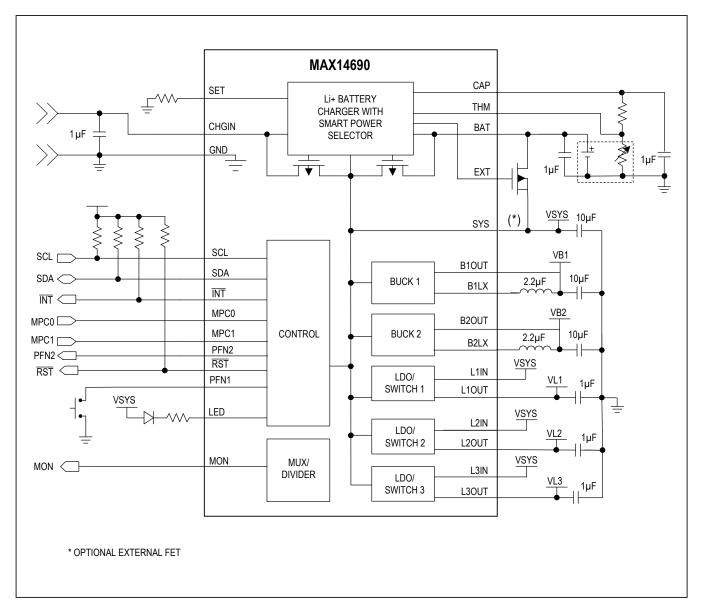

# **Typical Application Circuit**

# PMIC with Ultra-Low $I_Q$ Voltage Regulators and Battery Charger for Small Lithium Ion Systems

### **Absolute Maximum Ratings**

| (Voltages referenced to GND.)                                  | Continuous Current into CHGIN, BAT, SYS±1000mA            |

|----------------------------------------------------------------|-----------------------------------------------------------|

| SDA, SCL, THM, RST, SYS, PFN1, PFN2,                           | Continuous Current into any other terminal±100mA          |

| MPC0, MPC1, INT, MON, BAT LED,                                 | Continuous Power Dissipation (multilayer board at +70°C): |

| L1IN, L2IN, L3IN0.3V to +6.0V                                  | 6 x 6 Array 36-Bump 2.72mm x 2.47mm                       |

| B1LX, B2LX, B1OUT, B2OUT, EXT0.3V to (V <sub>SYS</sub> + 0.3V) | 0.4mm Pitch WLP (derate 21.70mW/°C)1.74W                  |

| L1OUT0.3V to (V <sub>L1IN</sub> + 0.3V)                        | Operating Temperature Range40°C to +85°C                  |

| L2OUT0.3V to (V <sub>L2IN</sub> + 0.3V)                        | Junction Temperature+150°C                                |

| L3OUT0.3V to (V <sub>L3IN</sub> + 0.3V)                        | Storage Temperature Range65°C to +150°C                   |

| CHGIN                                                          | Lead Temperature Soldering (10s)+300°C                    |

| CAP0.3V to min (V <sub>CHGIN</sub> + 0.3V, +6V)                | Soldering Temperature (reflow)+260°C                      |

| SET0.3V to V <sub>BAT</sub> + 0.3V                             |                                                           |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **Package Information**

| PACKAGE TYPE: 36 WLP                  |                                |  |  |  |

|---------------------------------------|--------------------------------|--|--|--|

| Package Code                          | W362D2+1                       |  |  |  |

| Outline Number                        | 21-0897                        |  |  |  |

| Land Pattern Number                   | Refer to Application Note 1891 |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD  |                                |  |  |  |

| Junction to Ambient ( $\theta_{JA}$ ) | 46°C/W                         |  |  |  |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

# PMIC with Ultra-Low I<sub>Q</sub> Voltage Regulators and Battery Charger for Small Lithium Ion Systems

# **Electrical Characteristics**

| PARAMETER                                                   | SYMBOL                                           | CONDITIONS                                                                                                                                                     | MIN  | TYP   | MAX  | UNITS  |

|-------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|--------|

| GLOBAL SUPPLY CURREN                                        | Γ (L_IN Connected to                             | SYS)                                                                                                                                                           |      |       |      |        |

|                                                             |                                                  | All functions disabled                                                                                                                                         |      | 0.26  |      |        |

| Charger Input Current                                       | Iсна                                             | Power on, $V_{CHGIN} = 5V$<br>SYS switch closed, buck regulators in<br>burst mode, LDO1 enabled, $I_{SYS} = 0A$ ,<br>$I_{B_OUT} = 0A$ , $I_{L_OUT} = 0A$       |      |       | 2    | mA     |

|                                                             |                                                  | Power off, V <sub>CHGIN</sub> = 0V,<br>SYS switch open                                                                                                         |      | 0.95  |      |        |

|                                                             |                                                  | Power on, $V_{CHGIN} = 0V$<br>SYS switch closed, 2x buck regulators<br>in Burst mode, LDOs disabled.<br>$I_{SYS} = 0A$ , $I_{BOUT} = 0A$                       |      | 3     |      |        |

| BAT Input Current                                           | IBAT                                             | Power on, $V_{CHGIN} = 0V$<br>SYS switch closed, 2x buck regulators<br>in Burst mode, LDO1 enabled,<br>$I_{SYS} = 0A$ , $I_{BOUT} = 0A$ , $I_{LOUT} = 0A$      |      | 3.5   |      | μA     |

|                                                             |                                                  | Power on, $V_{CHGIN} = 0V$<br>SYS switch closed, 2x buck regulators<br>in burst mode, 3x LDOs enabled,<br>$I_{SYS} = 0A$ , $I_{B_OUT} = 0A$ , $I_{L_OUT} = 0A$ |      | 4.6   |      |        |

| BUCK REGULATOR 1<br>(V <sub>SYS</sub> = +3.7V, Burst mode c | operation, L = 2.2µH,                            | C = 10µF, V <sub>B1OUT</sub> = 1.2V)                                                                                                                           |      |       |      |        |

| Input Voltage                                               | VIN_BUCK1                                        | Input voltage = V <sub>SYS</sub>                                                                                                                               | 2.7  |       | 5.5  | V      |

| Output Voltage                                              | VOUT_BUCK1                                       | 25mV step resolution (Note 2)                                                                                                                                  | 0.8  |       | 1.8  | V      |

|                                                             | IQ_BUCK1                                         | Burst mode, I <sub>OUT</sub> = 0mA (Note 3)                                                                                                                    |      | 0.915 | 2    | μΑ     |

| Quiescent Supply Current                                    | PWM1_BUCK1                                       | FPWM mode, L = $4.7\mu$ H (ESR = $0.6\Omega$ ,<br>2MHz RAC = $2.13\Omega$ ), I <sub>OUT</sub> = 0mA                                                            |      | 2.5   | 3.5  | mA     |

| Output Accuracy                                             | ACC <sub>BUCK1</sub>                             | I <sub>OUT</sub> = 1mA<br>(V <sub>OUT_BUCK1</sub> > 1V, C > 50μF)                                                                                              | -2.6 |       | +2.9 | %      |

| Load Regulation                                             | V <sub>ERR_BUCK1</sub>                           | From I <sub>OUT</sub> = 0 to 200mA<br>(V <sub>B1OUT</sub> = 1.2V average voltage)                                                                              | -3   | -1    |      | %      |

| Peak-to-Peak Ripple in                                      |                                                  | I <sub>OUT</sub> = 10mA, C = 20μF                                                                                                                              |      | 25    |      | m)/    |

| Burst Mode                                                  | VPPRIPPLE1                                       | I <sub>OUT</sub> = 10mA, C = 10μF                                                                                                                              |      | 43    |      | mV     |

| Maximum Operative Output<br>Current                         | IOUT_BUCK1                                       |                                                                                                                                                                | 200  |       |      | mA     |

|                                                             | 1                                                | V <sub>OUT</sub> = V <sub>SYS</sub>                                                                                                                            |      | 200   | 350  | μA     |

| B1OUT Pulldown Current                                      | ILEAK_B1OUT                                      | V <sub>REG</sub> < V <sub>OUT</sub> < V <sub>REG</sub> + 0.1V                                                                                                  |      | 10    | 100  | nA     |

|                                                             |                                                  |                                                                                                                                                                |      |       |      | -      |

| pMOS On-Resistance                                          | R <sub>ONP_BUCK1</sub>                           |                                                                                                                                                                |      | 0.22  | 0.4  | Ω      |

| pMOS On-Resistance<br>nMOS On-Resistance                    | R <sub>ONP_BUCK1</sub><br>R <sub>ONN_BUCK1</sub> |                                                                                                                                                                |      | 0.22  | 0.4  | Ω<br>Ω |

# PMIC with Ultra-Low ${\rm I}_{\rm Q}$ Voltage Regulators and Battery Charger for Small Lithium Ion Systems

# **Electrical Characteristics (continued)**

| PARAMETER                                                 | SYMBOL                  | CONDITIONS                                                                                      | MIN  | TYP  | MAX   | UNITS |

|-----------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------|------|------|-------|-------|

| Maximum Duty Cycle                                        | D <sub>MAX_BUCK1</sub>  |                                                                                                 |      | 100  |       | %     |

| Short-Circuit Current Limit                               | ISHRT_BUCK1             |                                                                                                 | 1.1  | 1.3  | 1.62  | A     |

| BLX Leakage Current                                       | IBLX_BUCK1              |                                                                                                 |      |      | 1     | μA    |

| Active Discharge Current                                  | ID BUCK1                | V <sub>B1OUT</sub> = 1.2V                                                                       | 8    | 18   | 36    | mA    |

| Full Turn-On Time                                         | T <sub>ON_BUCK1</sub>   | Time from enable to full current capability                                                     |      | 58   |       | ms    |

| Thermal-Shutdown<br>Temperature                           | T <sub>SHDN_BUCK1</sub> |                                                                                                 |      | 150  |       | °C    |

| Thermal-Shutdown<br>Temperature Hysteresis                | TSHDN_HYST_BUCK1        |                                                                                                 |      | 20   |       | °C    |

| BUCK REGULATOR 2<br>(V <sub>SYS</sub> = +3.7V, Burst mode | operation, L = 2.2µH, C | = 10µF, V <sub>B2OUT</sub> = 1.8V.)                                                             |      |      |       |       |

| Input Voltage                                             | VIN_BUCK2               | Input voltage = V <sub>SYS</sub>                                                                | 2.7  |      | 5.5   | V     |

| Output Voltage                                            | V <sub>OUT_BUCK2</sub>  | 50mV step resolution                                                                            | 1.5  |      | 3.3   | V     |

| Quiescent Supply Current                                  | IQ_BUCK2                | Burst mode, I <sub>OUT</sub> = 0mA (Note 3)                                                     |      | 1    | 2     | μA    |

| (Note 3)                                                  | IPWM1_BUCK2             | FPWM mode, L = $4.7\mu$ H (ESR = $0.6\Omega$ , 2MHz RAC = $2.13\Omega$ ) I <sub>OUT</sub> = 0mA |      | 2.4  | 3.5   | mA    |

| Output Accuracy                                           | ACC <sub>BUCK2</sub>    | $I_{OUT}$ = 1mA, $V_{OUT\_BUCK2}$ > 1.5V,<br>C > 50µF, $V_{SYS}$ > $V_{B2OUT}$ + 150mV          | -2   |      | +2.93 | %     |

| Load Regulation                                           | VERR_BUCK2              | From $I_{OUT}$ = 0 to 200mA,<br>V <sub>B2OUT</sub> = 1.8V average voltage                       | -3.1 | -1   |       | %     |

| Peak-to-Peak Ripple In                                    |                         | I <sub>OUT</sub> = 10mA, C = 20μF                                                               |      | 38   |       | m)/   |

| Burst Mode                                                | VPPRIPPLE2              | I <sub>OUT</sub> = 10mA, C = 10μF                                                               |      | 54   |       | mV    |

| Maximum Operative Output<br>Current                       | IOUT_BUCK2              |                                                                                                 | 200  |      |       | mA    |

| B2OUT Pulldown Current                                    |                         | V <sub>OUT</sub> = V <sub>SYS</sub>                                                             |      | 5    | 10    | μA    |

|                                                           | ILEAK_B2OUT             | V <sub>REG</sub> < V <sub>OUT</sub> < V <sub>REG</sub> + 0.1V                                   |      | 10   |       | nA    |

| pMOS On-Resistance                                        | R <sub>ONP_BUCK2</sub>  |                                                                                                 |      | 0.22 | 0.4   | Ω     |

| nMOS On-Resistance                                        | R <sub>ONN_BUCK2</sub>  |                                                                                                 |      | 0.18 | 0.3   | Ω     |

| Oscillator Frequency                                      | fBUCK2                  | FPWM mode                                                                                       | 1.78 | 2.00 | 2.24  | MHz   |

| Maximum Duty Cycle                                        | D <sub>MAX_BUCK2</sub>  |                                                                                                 |      | 100  |       | %     |

| Short-Circuit Current Limit                               | ISHRT_BUCK2             |                                                                                                 | 1.4  | 1.8  | 2.2   | A     |

| BLX Leakage Current                                       | IBLX_BUCK2              |                                                                                                 |      |      | 1     | μA    |

| Active Discharge Current                                  | ID_BUCK2                | V <sub>B2OUT</sub> = 1.8V                                                                       | 8    | 18   | 36    | mA    |

| Full Turn-On Time                                         | ton_buck2               | Time from enable to full current capability                                                     |      | 58   |       | ms    |

| Thermal-Shutdown<br>Temperature                           | T <sub>SHDN_BUCK2</sub> |                                                                                                 |      | 150  |       | °C    |

| Thermal-Shutdown<br>Temperature Hysteresis                | TSHDN_HYST_BUCK2        |                                                                                                 |      | 20   |       | °C    |

# PMIC with Ultra-Low I<sub>Q</sub> Voltage Regulators and Battery Charger for Small Lithium Ion Systems

# **Electrical Characteristics (continued)**

| PARAMETER                                  | SYMBOL                     | CONDITIONS                                                                            | MIN       | TYP  | MAX   | UNITS  |  |

|--------------------------------------------|----------------------------|---------------------------------------------------------------------------------------|-----------|------|-------|--------|--|

| LDOs<br>(C = 1µF, unless otherwise         | noted. Typical values a    | ire at V <sub>L_IN</sub> = 3.7V, with I <sub>L_OUT</sub> = 10mA, V                    | L_OUT = 3 | 3V.) | ·     | ·      |  |

| Input Voltage                              | No                         | LDO_Mode = 0                                                                          | 2.7       |      | 5.5   | V      |  |

| input voltage                              | V <sub>IN_LDO</sub>        | LDO_Mode = 1                                                                          | 1.8       |      | 5.5   | V      |  |

|                                            | I <sub>Q_LDO</sub>         | I <sub>L_OUT</sub> = 0mA                                                              |           | 0.56 | 1.2   | μA     |  |

| Quiescent Supply Current                   | IQ_LDO_AD                  | I <sub>L_OUT</sub> = 0mA, VL_IN = 1.8V, LDO_<br>ActDSC = 1, LDO_En = 00               |           | 40   |       | μA     |  |

| Maximum Output Current                     | L_OUT_MAX                  |                                                                                       | 100       |      |       | mA     |  |

| Output Voltage                             | V <sub>L_OUT</sub>         |                                                                                       | 0.8       |      | 3.6   | V      |  |

| Output Accuracy                            | ACC <sub>LDO</sub>         | $V_{L_IN} = (V_{L_OUT} + 0.5V)$ or higher,<br>I <sub>L_OUT</sub> = 100µA              |           |      | 3     | %      |  |

| Dropout Voltage                            | V <sub>DROP_LDO</sub>      | $V_{L_{IN}} = 3.3V, I_{L_{OUT}} = 100$ mA, $V_{L_{OUT}} = 3.3V$                       |           |      | 100   | mV     |  |

| Line Regulation Error                      | V <sub>LINEREG_LDO</sub>   | $V_{L_{IN}} = (V_{L_{OUT}} + 0.5V)$ to 5.5V                                           | -0.09     |      | 0.09  | %/V    |  |

| Load Regulation Error                      | V <sub>LOADREG_LDO</sub>   | I <sub>L_OUT</sub> = 100μA to 100mA                                                   | 0.003     |      | 0.008 | %/mA   |  |

| Line Transient                             |                            | $V_{L_{IN}}$ = 4V to 5V, 200ns rise time                                              |           | ±36  |       | mV     |  |

|                                            | VLINETRAN_LDO              | $V_{L_{IN}}$ = 4V to 5V, 1µs rise time                                                |           | ±28  |       | mV     |  |

| Load Transient                             | VLOADTRAN_LDO              | I <sub>L_OUT</sub> = 0mA to 10mA, 200ns rise time                                     |           | 145  |       | mV     |  |

|                                            |                            | I <sub>L_OUT</sub> = 0mA to 100mA, 200ns rise time                                    |           | 290  |       | mV     |  |

| Active Discharge Current                   | I <sub>PDL</sub>           | V <sub>L_IN</sub> = 3.7V                                                              | 9         | 21   | 37    | mA     |  |

|                                            |                            | $I_{L_{OUT}}$ = 0mA, time to 90% of final value                                       |           | 2.3  |       | ms     |  |

| Turn-On Time                               | <sup>t</sup> ON_LDO        | $V_{L_IN}$ = 3V, switch mode,<br>I <sub>L_OUT</sub> = 0mA, time to 90% of final value |           | 0.45 |       | ms     |  |

| Short-Circuit Current Limit                |                            | V <sub>L_OUT</sub> = GND                                                              |           | 385  |       | mA     |  |

|                                            | ISHRT_LDO                  | V <sub>L_OUT</sub> = GND, switch mode                                                 |           | 375  |       | mA     |  |

| Switch Mode Resistance                     | D                          | V <sub>L_IN</sub> = 2.7V, switch mode                                                 |           | 0.58 | 0.9   | Ω      |  |

| Switch would resistance                    | R <sub>ON_LDO</sub>        | V <sub>L_IN</sub> = 1.8V, switch mode                                                 |           | 0.89 | 1.35  | Ω      |  |

| Thermal-Shutdown<br>Temperature            | T <sub>SHDN_LDO</sub>      |                                                                                       |           | 150  |       | °C     |  |

| Thermal-Shutdown<br>Temperature Hysteresis | T <sub>SHDN_HYST_LDO</sub> |                                                                                       |           | 16   |       | °C     |  |

|                                            |                            | 10Hz to 100kHz, $V_{L_{IN}}$ = 5V,<br>$V_{L_{OUT}}$ = 3.3V                            |           | 110  |       |        |  |

| Output Noice                               |                            | 10Hz to 100kHz, $V_{L_{IN}} = 5V$ ,<br>$V_{L_{OUT}} = 2.5V$                           |           | 95   |       |        |  |

| Output Noise                               | OUT <sub>NOISE</sub>       | $10$ Hz to 100kHz, V <sub>L_IN</sub> = 5V,<br>V <sub>L_OUT</sub> = 1.2V               |           | 60   |       | – µVRM |  |

|                                            |                            | 10Hz to 100kHz, $V_{L_{IN}} = 5V$ ,<br>$V_{L_{OUT}} = 0.8V$                           |           | 60   |       |        |  |

# PMIC with Ultra-Low I<sub>Q</sub> Voltage Regulators and Battery Charger for Small Lithium Ion Systems

# **Electrical Characteristics (continued)**

| PARAMETER                                                                           | SYMBOL                    | CONDITIONS                                          | MIN        | TYP        | MAX        | UNITS |

|-------------------------------------------------------------------------------------|---------------------------|-----------------------------------------------------|------------|------------|------------|-------|

| CHGIN TO SYS PATH<br>(V <sub>CHGIN</sub> = 5.0V, V <sub>SYS</sub> = V <sub>SY</sub> | rs_REG.) (Note 1)         |                                                     |            |            |            |       |

| Allowed CHGIN Input<br>Voltage Range                                                | V <sub>CHGIN_RNG</sub>    |                                                     | -5.5       |            | 28         | V     |

| Allowed BAT Voltage Range                                                           | V <sub>BAT_RNG</sub>      |                                                     | 0          |            | 5.5        | V     |

| V <sub>CHGIN</sub> Detect Threshold                                                 | V <sub>CHGIN_DET</sub>    | Rising<br>Falling                                   | 3.8<br>3.0 | 3.9<br>3.1 | 4.1<br>3.2 | V     |

| V <sub>CHGIN</sub> Overvoltage<br>Threshold                                         | V <sub>CHGIN_OV</sub>     | Rising                                              | 7.2        | 7.5        | 7.8        | V     |

| V <sub>CHGIN</sub> Overvoltage<br>Threshold Hysteresis                              | V <sub>CHGIN_OV_HYS</sub> |                                                     |            | 200        |            | mV    |

| V <sub>CHGIN</sub> Valid Trip Point                                                 | V <sub>CHGIN-SYS_TP</sub> | $V_{CHGIN}$ - $V_{SYS}$ , rising, $V_{BAT}$ = 4V    | 45         | 145        | 280        | mV    |

| V <sub>CHGIN</sub> Valid Trip-Point<br>Hysteresis                                   | VCHGIN-SYS_TP_HYS         |                                                     |            | 200        |            | mV    |

|                                                                                     | ILIM                      | ILimCntl[1:0] = 00                                  |            | 0          |            |       |

| Input Limiter Current                                                               |                           | ILimCntl[1:0] = 01                                  |            | 90         |            | mA    |

|                                                                                     |                           | ILimCntl[1:0] = 10                                  |            | 450        |            |       |

|                                                                                     |                           | ILimCntl[1:0] = 11                                  |            | 1000       |            |       |

| Internal CAP Regulator                                                              | V <sub>CAP</sub>          | V <sub>CHGIN</sub> = 5V                             | 3.9        | 4.2        | 4.7        | V     |

| SYS Regulation Voltage                                                              | V <sub>SYS_REG</sub>      | V <sub>CHGIN</sub> = 5V, I <sub>SYS</sub> = 1mA     | 4.55       | 4.65       | 4.75       | V     |

| SYS Regulation Voltage<br>Dropout                                                   | V <sub>CHGIN-SYS</sub>    | V <sub>CHGIN</sub> = 4V, I <sub>SYS</sub> = 1mA     |            | 40         |            | mV    |

| CHGIN-to-SYS<br>On-Resistance                                                       | R <sub>CHGIN-SYS</sub>    | V <sub>CHGIN</sub> = 4.4V, I <sub>SYS</sub> = 400mA |            | 0.370      | 0.66       | Ω     |

| Thermal-Shutdown<br>Temperature                                                     | TCHGIN_SHDN               | (Note 4)                                            |            | +150       |            | °C    |

| Thermal-Shutdown<br>Temperature Hysteresis                                          | TCHGIN_SHDN_HYS           |                                                     |            | 20         |            | °C    |

| Input Current Soft-Start<br>Time                                                    | <sup>t</sup> SFST_LIM     |                                                     |            | 1          |            | ms    |

| Internal Supply Switchover<br>Threshold                                             | V <sub>CCINT_TH</sub>     | $V_{CHGIN} = V_{CAP}$ rising, $V_{BAT} = 4.2V$      | 2.5        | 2.8        | 3.0        | V     |

# PMIC with Ultra-Low I<sub>Q</sub> Voltage Regulators and Battery Charger for Small Lithium Ion Systems

# **Electrical Characteristics (continued)**

| PARAMETER                                                   | SYMBOL                              | CONDITIONS                                                                                                                                                                | MIN  | TYP   | MAX  | UNITS  |

|-------------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|--------|

| SYS, BATTERY, AND V <sub>CCIN</sub>                         | T UVLOs                             | · · · · · ·                                                                                                                                                               |      |       |      |        |

|                                                             | V <sub>SYSUVLO_R</sub>              | Rising                                                                                                                                                                    |      | 2.644 | 2.69 | V      |

| SYS UVLO Threshold                                          | V <sub>SYSUVLO_F</sub>              | Falling                                                                                                                                                                   | 2.57 | 2.618 | 2.67 | V      |

| SYS UVLO Threshold<br>Hysteresis                            | VSYSUVLO_HYS                        | Hysteresis                                                                                                                                                                |      | 26    |      | mV     |

| SYS UVLO Falling<br>Debounce Time                           | <sup>t</sup> SYSUVLO_FDEB           | SYS falling                                                                                                                                                               |      | 20    |      | μs     |

| V <sub>CCINT</sub> UVLO Threshold<br>(POR)                  | V <sub>UVLO</sub>                   | V <sub>CCINT</sub> rising                                                                                                                                                 | 0.8  | 1.82  | 2.6  | V      |

| V <sub>CCINT</sub> UVLO Threshold<br>Hysteresis             | VUVLO_HYS                           |                                                                                                                                                                           |      | 140   |      | mV     |

| BAT UVLO Threshold                                          | VBAT_UVLO                           | Rising (valid only when CHGIN is<br>present, when V <sub>BAT</sub> < V <sub>BAT_UVLO</sub> ,<br>the BAT-SYS switch opens and BAT is<br>connected to SYS through a diode.) | 1.9  | 2.05  | 2.2  | v      |

| BAT UVLO Threshold<br>Hysteresis                            | V <sub>BAT_UVLO_HYS</sub>           | Hysteresis                                                                                                                                                                |      | 50    |      | mV     |

| BATTERY CHARGER<br>(V <sub>BAT</sub> = 4.2V. Typical values | s are at V <sub>CHRGIN</sub> = 5.0V | , V <sub>SYS</sub> = V <sub>SYS_REG</sub> .)                                                                                                                              |      |       |      |        |

| BAT-to-SYS<br>On-Resistance                                 | R <sub>BAT-SYS</sub>                | V <sub>BAT</sub> = 4.2V, I <sub>BAT</sub> = 300mA                                                                                                                         |      | 80    | 140  | mΩ     |

| Current Reduce Thermal<br>Threshold Temperature             | T <sub>CHG_LIM</sub>                | (Note 5)                                                                                                                                                                  |      | 120   |      | °C     |

| BAT-to-SYS Switch On<br>Threshold                           | VBAT-SYS-ON                         | SYS falling                                                                                                                                                               | 10   | 22    | 35   | mV     |

| BAT-to-SYS Switch Off<br>Threshold                          | VBAT-SYS-OFF                        | SYS rising                                                                                                                                                                | -3   | -1.5  | 0    | mV     |

| SYS Threshold Voltage<br>Charger Limiting Current           | V <sub>SYS_LIM</sub>                | Threshold at which the charger starts to limit the current due to SYS falling                                                                                             |      | 4.36  |      | V      |

| FChg-MtChg Threshold                                        | V <sub>FCHG-MTCHG</sub>             | If V <sub>SYS</sub> drops below this value the charger will not move to maintain charge                                                                                   |      | 4.49  |      | V      |

| FChg-MtChg Threshold<br>Hysteresis                          | V <sub>FCHG-MTCHG_HYS</sub>         |                                                                                                                                                                           |      | 50    |      | mV     |

| Charger Current Soft-Start<br>Time                          | <sup>t</sup> CHG_SOFT               |                                                                                                                                                                           |      | 1     |      | ms     |

| PRECHARGE                                                   |                                     |                                                                                                                                                                           |      |       |      |        |

|                                                             |                                     | IPChg = 00                                                                                                                                                                |      | 5     |      |        |

| Dracharga Current                                           |                                     | IPChg = 01                                                                                                                                                                | 9    | 10    | 11   |        |

| Precharge Current                                           | IPCHG                               | IPChg = 10                                                                                                                                                                |      | 20    |      | %IFChg |

|                                                             |                                     | IPChg = 11                                                                                                                                                                |      | 30    |      | -      |

# PMIC with Ultra-Low I<sub>Q</sub> Voltage Regulators and Battery Charger for Small Lithium Ion Systems

# **Electrical Characteristics (continued)**

| PARAMETER                                       | SYMBOL                    | CON                         | NDITIONS                                        | MIN   | TYP  | MAX   | UNITS    |  |

|-------------------------------------------------|---------------------------|-----------------------------|-------------------------------------------------|-------|------|-------|----------|--|

|                                                 |                           | VPChg = 000, V <sub>E</sub> | AT rising                                       |       | 2.1  |       |          |  |

|                                                 |                           | VPChg = 001, V <sub>E</sub> | AT rising                                       | 2.15  | 2.25 | 2.35  |          |  |

|                                                 |                           | VPChg = 010, V <sub>E</sub> |                                                 |       | 2.40 |       |          |  |

| Due nue life e tiene Thurse he al al            |                           | VPChg = 011, V <sub>B</sub> | AT rising                                       |       | 2.55 |       |          |  |

| Prequalification Threshold                      | V <sub>BAT_PChg</sub>     | VPChg = 100, V <sub>E</sub> | BAT rising                                      |       | 2.7  |       | - V      |  |

|                                                 |                           | VPChg = 101, V <sub>E</sub> | BAT rising                                      |       | 2.85 |       | 1        |  |

|                                                 |                           | VPChg = 110, V <sub>B</sub> | AT rising                                       |       | 3.0  |       | 1        |  |

|                                                 |                           | VPChg = 111, V <sub>B</sub> | AT rising                                       |       | 3.15 |       | ]        |  |

| Prequalification<br>Threshold Hysteresis        | V <sub>BAT_PChg_HYS</sub> |                             |                                                 |       | 90   |       | mV       |  |

| FAST CHARGE                                     |                           |                             |                                                 |       |      |       |          |  |

| SET Current Gain Factor                         | K <sub>SET</sub>          |                             |                                                 |       | 2000 |       | A/A      |  |

| SET Regulation Voltage                          | V <sub>SET</sub>          |                             |                                                 |       | 1    |       | V        |  |

|                                                 |                           | R <sub>SET</sub> = 400kΩ    |                                                 |       | 5    |       |          |  |

| Fast-Charge Current                             | I <sub>FChg</sub>         | R <sub>SET</sub> = 40kΩ     |                                                 | 45    | 50   | 55    | mA       |  |

|                                                 |                           | $R_{SET} = 4k\Omega$        |                                                 |       | 500  |       | -        |  |

| 1/2 Fast-Charge Current<br>Comparator Threshold | I <sub>FC_HALF</sub>      |                             |                                                 |       | 50   |       | %IFChg   |  |

| 1/5 Fast-Charge Current<br>Comparator Threshold | IFC_FIFTH                 |                             |                                                 |       | 20   |       | %IFChg   |  |

| MAINTAIN CHARGE                                 | 1                         |                             |                                                 | 1     |      |       | 1        |  |

|                                                 |                           | ChgDone = 00                |                                                 |       | 5    |       |          |  |

| Charge Done                                     |                           | ChgDone = 01                | gDone = 01 8.5                                  |       | 10   | 11.5  |          |  |

| Qualification                                   | I <sub>Chg_DONE</sub>     | ChgDone = 10                |                                                 |       | 20   |       | - %IFChg |  |

|                                                 |                           | ChgDone = 11                |                                                 |       | 30   |       | 1        |  |

|                                                 |                           | BatReg = 000                |                                                 |       | 4.05 |       |          |  |

|                                                 |                           | BatReg = 001                |                                                 |       | 4.10 |       | 1        |  |

|                                                 |                           | BatReg = 010                |                                                 |       | 4.15 |       | ]        |  |

|                                                 |                           | D (D ) 011                  | T <sub>A</sub> = +25°C                          | 4.179 | 4.2  | 4.221 |          |  |

| BAT Regulation Voltage                          | V <sub>BatReg</sub>       | BatReg = 011                | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$ | 4.158 | 4.2  | 4.242 | V        |  |

|                                                 |                           | BatReg = 100                |                                                 |       | 4.25 |       | 1        |  |

|                                                 |                           | BatReg = 101                | -                                               |       | 4.3  |       | -        |  |

|                                                 |                           | D.(D. 110                   | T <sub>A</sub> = +25°C                          | 4.32  | 4.35 | 4.38  | 1        |  |

|                                                 |                           | BatReg = 110                | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$   | 4.30  | 4.35 | 4.40  |          |  |

|                                                 |                           | BatReChg = 00               | -                                               |       | 70   |       |          |  |

|                                                 |                           | BatReChg = 01               |                                                 |       | 120  |       |          |  |

| BAT Recharge Threshold                          | VBatReChg                 | BatReChg = 10               |                                                 |       | 170  |       | - mV     |  |

|                                                 |                           | BatReChg = 11               |                                                 |       | 220  |       | 1        |  |

# PMIC with Ultra-Low I<sub>Q</sub> Voltage Regulators and Battery Charger for Small Lithium Ion Systems

# **Electrical Characteristics (continued)**

| PARAMETER                | SYMBOL                   | CONDITIONS                                                                                                                                                     | MIN  | TYP  | MAX  | UNITS |  |

|--------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|--|

| CHARGER TIMER            |                          |                                                                                                                                                                |      |      |      |       |  |

|                          |                          | PChgTmr = 00                                                                                                                                                   |      | 30   |      |       |  |

| Maximum Prequalification | 4                        | PChgTmr = 01                                                                                                                                                   |      | 60   |      |       |  |

| Time                     | <sup>t</sup> PChg        | PChgTmr = 10                                                                                                                                                   |      | 120  |      | min   |  |

|                          |                          | PChgTmr = 11                                                                                                                                                   |      | 240  |      | 1     |  |

|                          |                          | FChgTmr = 00                                                                                                                                                   |      | 75   |      |       |  |

| Maximum Fast-Charge      | 4                        | FChgTmr = 01                                                                                                                                                   |      | 150  |      |       |  |

| Time                     | tFChg                    | FChgTmr = 10                                                                                                                                                   |      | 300  |      | min   |  |

|                          |                          | FChgTmr = 11                                                                                                                                                   |      | 600  |      | 1     |  |

|                          |                          | TOChgTmr = 00                                                                                                                                                  |      | 0    |      |       |  |

| Maintain Charge Time     | <sup>t</sup> MTChg       | TOChgTmr = 01                                                                                                                                                  |      | 15   |      |       |  |

| Maintain-Charge Time     |                          | TOChgTmr = 10                                                                                                                                                  |      | 30   |      | min   |  |

|                          |                          | TOChgTmr = 11                                                                                                                                                  |      | 60   |      | ]     |  |

| Timer Accuracy           | tCHG ACC                 |                                                                                                                                                                | -10  |      | +10  | %     |  |

| Timer Extend Threshold   | TIM <sub>EXD_THRES</sub> | If charge current is reduced due to<br>I <sub>LIM</sub> or TDIE, this is the percentage of<br>charge current below which timer clock<br>operates at half speed |      | 50   |      | %     |  |

| Timer Suspend Threshold  | TIM <sub>SUS_THRES</sub> | If charge current is reduced due to I <sub>LIM</sub> or TDIE, this is the percentage of charge current below which timer clock pauses                          |      | 20   |      | %     |  |

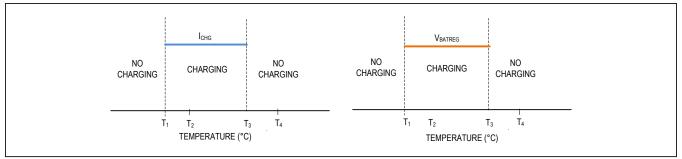

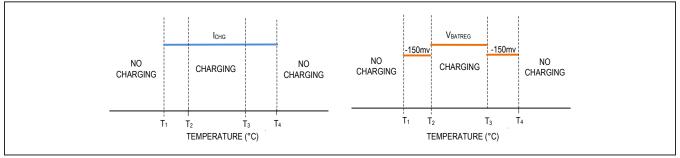

| THERMISTOR MONITOR AN    | ID NTC DETECTION (F      | RPU = 10k, RTHM = 10k, 3380ß)                                                                                                                                  |      |      |      |       |  |

| THM Hot Threshold        | T <sub>4</sub>           | V <sub>THM</sub> falling                                                                                                                                       | 21.3 | 23.3 | 25.3 |       |  |

| THM Warm Threshold       | T <sub>3</sub>           | V <sub>THM</sub> falling                                                                                                                                       | 30.9 | 32.9 | 34.9 | 1     |  |

| THM Cool Threshold       | T <sub>2</sub>           | V <sub>THM</sub> rising                                                                                                                                        | 62.5 | 64.5 | 66.5 | %CAP  |  |

| THM Cold Threshold       | T <sub>1</sub>           | V <sub>THM</sub> rising                                                                                                                                        | 71.9 | 73.9 | 75.9 |       |  |

| THM Disable Threshold    | THM <sub>DIS</sub>       | V <sub>THM</sub> rising                                                                                                                                        | 91   | 93   | 95   | 1     |  |

| THM Threshold Hysteresis | THM <sub>HYS</sub>       | -                                                                                                                                                              |      | 60   |      | mV    |  |

| THM Input Leakage        | ILKG THM                 |                                                                                                                                                                | -1   |      | +1   | μA    |  |

# PMIC with Ultra-Low I<sub>Q</sub> Voltage Regulators and Battery Charger for Small Lithium Ion Systems

# **Electrical Characteristics (continued)**

(V<sub>CHGIN</sub> = 5.0V, V<sub>BAT</sub> = 3.7V, T<sub>A</sub> = -40°C to +85°C, all registers in their default state, unless otherwise noted. Typical values are at  $T_A = +25$ °C.) (Note 1)

| PARAMETER                                                   | SYMBOL              | CONDITIONS            | MIN | TYP | MAX | UNITS |

|-------------------------------------------------------------|---------------------|-----------------------|-----|-----|-----|-------|

| DIGITAL SIGNALS                                             |                     |                       | •   |     |     |       |

| PFN1 PFN2 Button Timer<br>Accuracy                          |                     |                       | -10 |     | +10 | %     |

| Input Logic-High (SDA,<br>SCL, MPC0, MPC1, PFN1,<br>PFN2)   | V <sub>IH</sub>     |                       | 1.4 |     |     | V     |

| Input Logic-Low (SDA,<br>SCL, MPC0, MPC1, PFN1,<br>PFN2)    | V <sub>IL</sub>     |                       |     |     | 0.5 | V     |

| Output Logic-Low (SDA,<br>RST, INT, LED, PFN2)              | V <sub>OL</sub>     | I <sub>OL</sub> = 4mA |     |     | 0.4 | V     |

| High Level Leakage Current<br>(SDA, RST, INT, LED,<br>PFN2) | I <sub>LK</sub>     |                       | -1  |     | +1  | μA    |

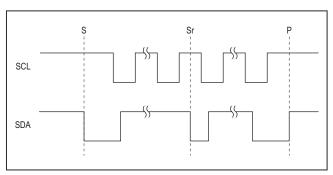

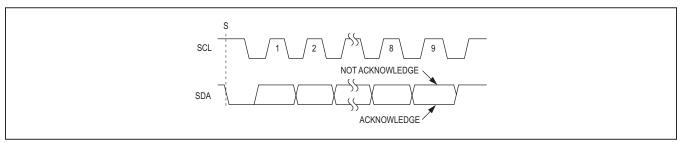

| SCL Clock Frequency                                         | f <sub>SCL</sub>    |                       |     |     | 400 | kHz   |

| Bus Free Time Between<br>a STOP and START<br>Condition      | <sup>t</sup> BUF    |                       | 1.3 |     |     | μs    |

| START Condition<br>(Repeated) Hold-Time                     | <sup>t</sup> HD:STA | (Note 6)              | 0.6 |     |     | μs    |

| Low Period of SCL Clock                                     | <sup>t</sup> LOW    |                       | 1.3 |     |     | μs    |

| High Period of SCL Clock                                    | t <sub>HIGH</sub>   |                       | 0.6 |     |     | μs    |

| Setup Time for a Repeated START Condition                   | <sup>t</sup> SU:STA |                       | 0.6 |     |     | μs    |

| Data Hold Time                                              | <sup>t</sup> HD:DAT | (Notes 7)             | 0   |     | 0.9 | μs    |

| Data Setup Time                                             | <sup>t</sup> SU:DAT | (Note 7)              | 100 |     |     | ns    |

| Setup Time for STOP<br>Condition                            | tsu:sto             |                       | 0.6 |     |     | μs    |

| Spike Pulse Widths<br>Suppressed by Input Filter            | t <sub>SP</sub>     | (Note 8)              |     | 50  |     | ns    |

**Note 1:** All devices are 100% production tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range are guaranteed by design.

Note 2: For input voltages larger than 4.4V, output regulated voltage below 1V are available ONLY in burst mode.

Note 3: This value is included in the I<sub>BAT</sub> quiescent current values for the on states.

Note 4: When the die temperature exceeds T<sub>CHGIN SHDN</sub>, the CHGIN-to-SYS path, and the charger is turned off.

- Note 5: When the die temperature exceeds T<sub>CHG</sub> LIM, the charger current starts to decrease.

- **Note 6:** f<sub>SCL</sub> must meet the minimum clock low time plus the rise/fall times.

Note 7: The maximum t<sub>HD:DAT</sub> has to be met only if the device does not stretch the low period (t<sub>LOW</sub>) of the SCL signal.

Note 8: Filters on SDA and SCL suppress noise spikes at the input buffers and delay the sampling instant.

# PMIC with Ultra-Low ${\rm I}_{\rm Q}$ Voltage Regulators and Battery Charger for Small Lithium Ion Systems

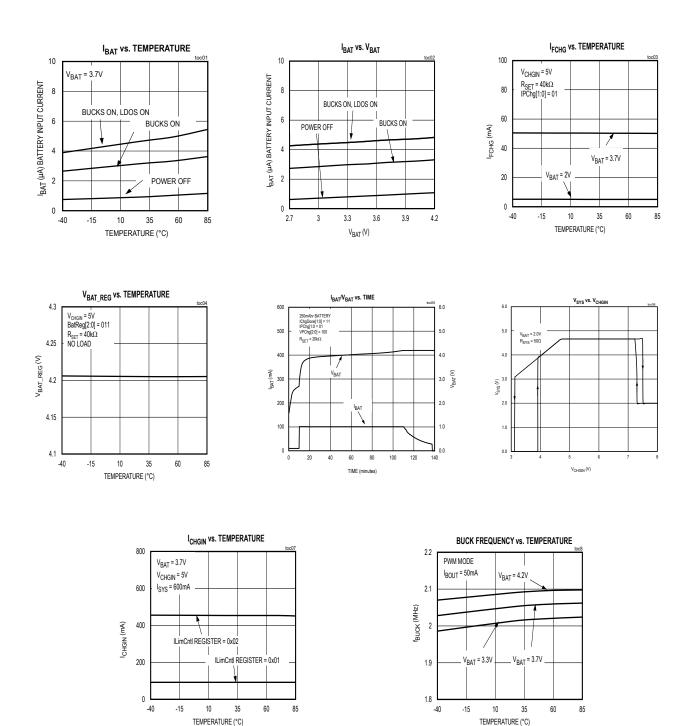

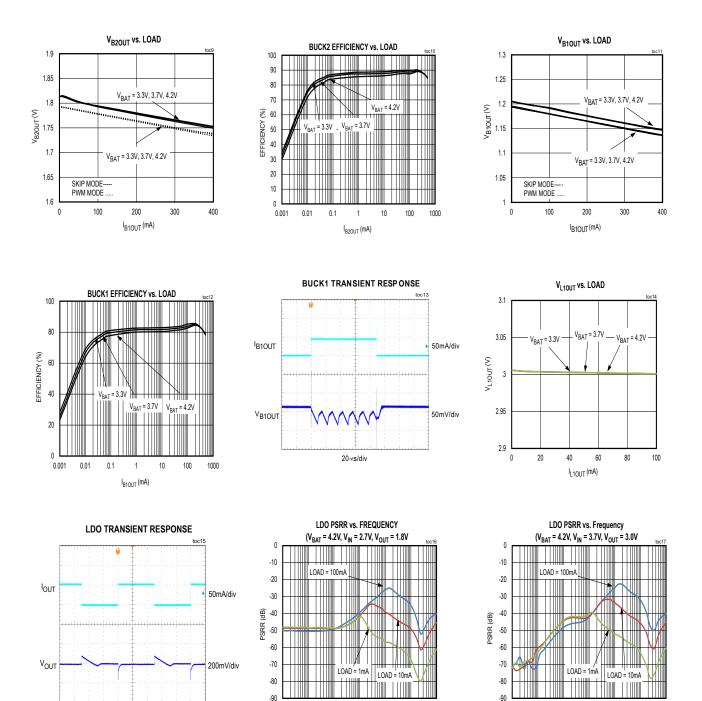

# **Typical Operating Characteristics**

(V<sub>BAT</sub> = 3.7V, V<sub>CHGIN</sub> = 0V, registers in their default state,  $T_A$  = +25°C, unless otherwise noted.)

# PMIC with Ultra-Low ${\rm I}_{\rm Q}$ Voltage Regulators and Battery Charger for Small Lithium Ion Systems

### **Typical Operating Characteristics (continued)**

(V<sub>BAT</sub> = 3.7V, V<sub>CHGIN</sub> = 0V, registers in their default state,  $T_A$  = +25°C, unless otherwise noted.)

0.01 0.10 1.00 10.00 100.00 1000.00

FREQUENCY (kHz)

0.10 1.00 10.00 100.00 1000.00 10000.00 FREQUENCY (kHz)

0.01

2ms/div

# PMIC with Ultra-Low I<sub>Q</sub> Voltage Regulators and Battery Charger for Small Lithium Ion Systems

# **Pin Configuration**

# **Bump Description**

| BUMP                     | NAME  | FUNCTION                                                                                                        |

|--------------------------|-------|-----------------------------------------------------------------------------------------------------------------|

| A1                       | L1OUT | LDO1 Output. Bypass with a minimum 1µF capacitor to GND.                                                        |

| A2                       | L1IN  | LDO1 Input                                                                                                      |

| A3                       | CAP   | Bypass for Internal LDO. Bypass with a 1µF capacitor to GND.                                                    |

| A4, C3, C4<br>D3, D4, F4 | GND   | Ground                                                                                                          |

| A5                       | B2OUT | 1.5V – 3.3V Buck Regulator Output Feedback. Bypass with a minimum 10µF capacitor to GND.                        |

| A6                       | B2LX  | 1.5V – 3.3V Buck Regulator Switch. Connect 2.2µH inductor to B2OUT.                                             |

| B1                       | L2OUT | LDO2 Output. Bypass with a minimum 1µF capacitor to GND.                                                        |

| B2                       | L2IN  | LDO2 Input                                                                                                      |

| B3                       | ĪNT   | Open-Drain, Active-Low Interrupt Output.                                                                        |

| B4                       | MON   | Voltage Monitor Pin                                                                                             |

| B5,B6                    | BAT   | Battery Connection. Connect BAT to a positive battery terminal, bypass BAT with a minimum 1µF capacitor to GND. |

# PMIC with Ultra-Low ${\rm I}_{\rm Q}$ Voltage Regulators and Battery Charger for Small Lithium Ion Systems

# **Pin Description (continued)**

| PIN    | NAME  | FUNCTION                                                                                                                                                                                                                 |

|--------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C1     | L3OUT | LDO3 Output. Bypass with a minimum 1µF capacitor to GND.                                                                                                                                                                 |

| C2     | L3IN  | LDO3 Input                                                                                                                                                                                                               |

| C5     | SET   | External Resistor For Battery Charge Current Level Setting. Do not connect any external capacitance on this pin; maximum allowed capacitance ( $C_{SET} < 5\mu s/R_{SET}$ ) pF.                                          |

| C6, D6 | SYS   | System Load Connection. Connect SYS to the system load. Bypass SYS with a minimum $10\mu F$ low-ESR ceramic capacitor to GND.                                                                                            |

| D1     | LED   | LED Open-Drain Pulldown Current. Add an external current limiting pullup resistor.                                                                                                                                       |

| D2     | PFN2  | Power Function Control Input/Output. Programmable functionality via PwrFnMode. See Table 1.                                                                                                                              |

| D5     | EXT   | Push-Pull Gate Drive for Optional External pFET from BAT-to-SYS. Output is pulled to GND when charger is disconnected and internal BAT-SYS FET is switched on. Otherwise, this output is pulled high to the SYS voltage. |

| E1     | RST   | Power-On Reset Output. Active-low, open-drain.                                                                                                                                                                           |

| E2     | MPC0  | Multipurpose Configuration Input 0                                                                                                                                                                                       |

| E3     | MPC1  | Multipurpose Configuration Input 1                                                                                                                                                                                       |

| E4     | PFN1  | Power Function Control Input. Programmable functionality via PwrFnMode. See Table 1.                                                                                                                                     |

| E5, E6 | CHGIN | +28V Protected Charger Input. Bypass CHGIN with 1µF capacitor to GND.                                                                                                                                                    |

| F1     | SDA   | Open-Drain, I <sup>2</sup> C Serial Data Input/Output.                                                                                                                                                                   |

| F2     | SCL   | I <sup>2</sup> C Serial Clock Input                                                                                                                                                                                      |

| F3     | ТНМ   | Battery Temperature Thermistor Measurement Connection. Connect a $10k\Omega$ resistor from THM to CAP and a $10k\Omega$ , 3380A NTC thermistor from THM to GND.                                                          |

| F5     | B1OUT | 0.8V – 1.8V Buck Regulator Output Feedback. Bypass B1OUT with a minimum 10µF capacitor to GND.                                                                                                                           |

| F6     | B1LX  | 0.8V – 1.8V Buck Regulator Switch Terminal. Connect B1LX to B1OUT with a 2.2µH inductor.                                                                                                                                 |

**Note:** All capacitance values listed in this document refer to effective capacitance. Be sure to specify capacitors that will meet these requirements under typical system operating conditions taking into consideration the effects of voltage and temperature.

# PMIC with Ultra-Low ${\rm I}_{\rm Q}$ Voltage Regulators and Battery Charger for Small Lithium Ion Systems

### **Block Diagram**

### **Detailed Description**

### Power Regulation

The MAX14690 family includes two high-efficiency, low quiescent current buck regulators, and three low quiescent current linear regulators that are also configurable as power switches. Excellent light-load efficiency allows the switching regulators to run continuously without significant energy cost. The standard operating mode for the buck regulators is burst mode, but they can be forced to operate in PWM mode through an I<sup>2</sup>C register.

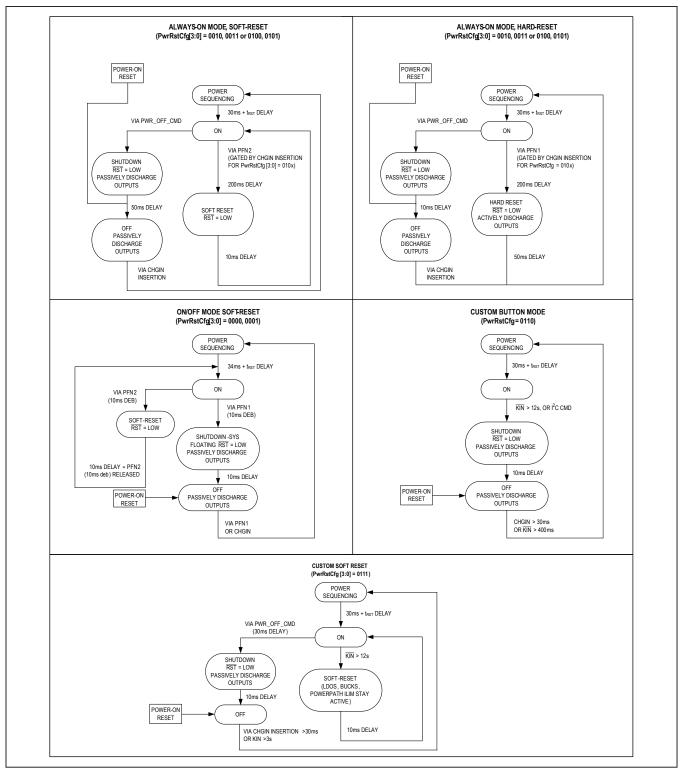

### Power On/Off and Reset Control

The behavior of power function control pins (PFN1 and PFN2) is preconfigured to support one of the multiple types of wearable application cases. <u>Table 1</u> describes the behavior of the PFN1 and PFN2 pins based on the PwrRstCfg[3:0] bits and <u>Figure 1</u> shows basic flow diagrams associated with each mode.

A soft reset will reset all register values and pulls the  $\overline{\text{RST}}$  line low. Hard reset initiates a complete Power-On Reset sequence.

# PMIC with Ultra-Low I<sub>Q</sub> Voltage Regulators and Battery Charger for Small Lithium Ion Systems

# **Table 1. Power Function Input Control Modes**

| PwrRstCfg<br>[3:0] | PFN1                                             | PFN1 PU/PD<br>PFNxResEna = 1<br>(0x1D[7]) | PFN2                                             | PFN2 PU/PD<br>PFNxResEna =<br>1 (0x1D[7]) | NOTES                                                                                                                                                                                                               |

|--------------------|--------------------------------------------------|-------------------------------------------|--------------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000               | Enable                                           | Pulldown                                  | Active-Low<br>Manual Reset                       | Pullup*                                   | On/off Mode with 10ms debounce. Active-high on/off control on PFN1. Logic-low on PFN2 generates 10ms pulse on $\overrightarrow{\text{RST}}$ .<br>Note that, in this mode, the PWR_OFF_CMD in $I^2$ C has no effect. |

| 0001               | Disable                                          | Pullup*                                   | Active-Low<br>Manual Reset                       | Pullup*                                   | On/off Mode with 10ms debounce. Active-low<br>on/off control on PFN1. Logic-low on PFN2<br>generates 10ms pulse on RST. Note that, in<br>this mode, the PWR_OFF_CMD in I <sup>2</sup> C has no<br>effect.           |

| 0010               | Hard-Reset<br>on Rising<br>Edge                  | Pulldown                                  | Soft-Reset on<br>Rising-Edge                     | Pulldown                                  | Always-On Mode (i.e., device can only be put<br>in off state through PWR_OFF_CMD). 50ms<br>hard-reset off time. 10ms soft-reset pulse time.<br>200ms delay prior to both reset behaviors.                           |

| 0011               | Hard-Reset<br>on Falling<br>Edge                 | Pullup*                                   | Soft-Reset<br>Falling-Edge                       | Pullup*                                   | Always-On Mode (i.e., device can only<br>be put in off state via PWR_OFF_CMD).<br>50ms hard-reset off time. 10ms soft-reset<br>pulse time. 200ms delay prior to both reset<br>behaviors.                            |

| 0100               | Hard-Reset<br>After CHGIN<br>Attach When<br>High | Pulldown                                  | Soft-Reset<br>After CHGIN<br>Attach When<br>High | Pulldown                                  | Charger Reset High Mode (i.e., device can only<br>be put in off state through PWR_OFF_CMD).<br>50ms hard-reset off time. 10ms soft-reset<br>pulse time. 200ms delay prior to both reset<br>behaviors.               |

| 0101               | Hard-Reset<br>After CHGIN<br>Attach When<br>Low  | Pullup*                                   | Soft-Reset<br>After CHGIN<br>Attach When<br>Low  | Pullup*                                   | Charger Reset Low Mode (i.e., device can only<br>be put in off state through PWR_OFF_CMD).<br>50ms hard-reset off time. 10ms soft-reset<br>pulse time. 200ms delay prior to both reset<br>behaviors.                |

| 0110               | KIN                                              | Pullup*                                   | KOUT                                             | None                                      | On/Off mode through specific long-press button timing or PWR_OFF_CMD.                                                                                                                                               |

| 0111               | KIN                                              | Pullup*                                   | KOUT                                             | None                                      | Custom Soft-Reset. Off mode through<br>PWR_OFF_CMD (30ms delay). On mode<br>through specific long-press (3s) or CHGIN<br>insertion. Soft-reset through specific long press<br>(12s).                                |

| 1000-1111          |                                                  |                                           |                                                  | _                                         | Reserved                                                                                                                                                                                                            |

\* Pullup is connected to  $V_{CCINT}$ .

# PMIC with Ultra-Low ${\rm I}_{\rm Q}$ Voltage Regulators and Battery Charger for Small Lithium Ion Systems

Figure 1. Power Function Input Control Modes Flow Diagrams

# PMIC with Ultra-Low I<sub>Q</sub> Voltage Regulators and Battery Charger for Small Lithium Ion Systems

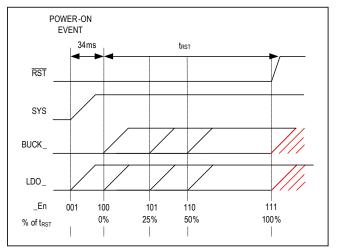

### **Power Sequencing**

The sequencing of the buck regulators and LDOs during power-on is configurable. See <u>Table 1</u> for details. Regulators can be configured to turn on at one of three points during the power-on process: 34ms after the power-on event, after the  $\overline{RST}$  signal is released, or at two points in between. The two points between SYS and  $\overline{RST}$  are fixed proportionally to the duration of the Power-On Reset (POR) process, but the overall time of the reset delay is configurable (80ms, 120ms, 220ms, 420ms). The timing relationship is presented graphically in Figure 2.

Figure 2. Reset Sequence Programming

Additionally, the regulators can be selected to default off and can be turned on with an I<sup>2</sup>C command after  $\overline{\text{RST}}$  is released. Each LDO regulator can be configured to be always-on as long as SYS or BAT is present.

The SYS voltage is monitored during the power-on sequence. If an undervoltage condition is detected on SYS during the sequencing process with a valid voltage at CHGIN, the process repeats from the point where SYS was enabled to allow more time for the voltage to stabilize. If there is not a valid voltage at CHGIN, the device returns to the off state to avoid draining the battery. Power is also turned off if an undervoltage condition is detected on SYS.

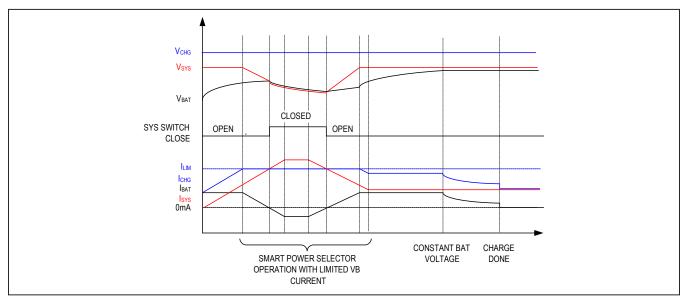

### **Smart Power Selector**

The smart power selector seamlessly distributes power from the external CHGIN input to the battery (BAT) and the system (SYS). With both an external adapter and battery connected, the smart power selector basic functions are:

- When the system load requirements are less than the input current limit, the battery is charged with residual power from the input.

- When the system load requirements exceed the input current limit, the battery supplies supplemental current to the load.

- When the battery is connected and there is no external power input, the system is powered from the battery.

Figure 3. Smart Power Selector Current/Voltage Behavior

# PMIC with Ultra-Low ${\rm I}_{\rm Q}$ Voltage Regulators and Battery Charger for Small Lithium Ion Systems

### Thermal Current Regulation

In case the die temperature exceeds the normal limit, the MAX14690 will attempt to limit the temperature increase by reducing the input current from CHGIN. In this condition, the system load has priority over charger current, so the input current is first reduced by lowering the charge current. If the junction temperature continues to rise and reaches the maximum operating limit, no input current is drawn from CHGIN and the battery powers the entire system load.

### System Load Switch

An internal  $80m\Omega$  (typ) MOSFET connects SYS to BAT when no voltage source is available on CHGIN. When an external source is detected at CHGIN, this switch opens and SYS is powered from the input source through the input current limiter. The SYS-to-BAT switch also prevents V<sub>SYS</sub> from falling below V<sub>BAT</sub> when the system load exceeds the input current limit. If V<sub>SYS</sub> drops to V<sub>BAT</sub> due to the current limit, the load switch turns on so the load is supported by the battery. If the system load continuously exceeds the input current limit the battery is not charged. This is useful for handling loads that are nominally below the input current limit. During these peaks, battery energy is used, but at all other times the battery charges. See Figure 3.

The pin EXT can drive the gate of an external pMOS connected between SYS (source, bulk) and BAT (drain) in parallel to the internal one.

EXT voltage is the buffered version of the internal gate command that controls the internal  $80m\Omega$  (typ) MOSFET.

**Note:** The body diode of an external pMOS connected between BAT and SYS remains present when the device is in off mode.

### **Input Limiter**

The input limiter distributes power from the external adapter to the system load and battery charger. In addition to the input limiter's primary function of passing power to the system load and charger, it performs several additional functions to optimize use of available power:

**Invalid CHGIN Voltage Protection:** If CHGIN is above the overvoltage threshold, the MAX14690 enters overvoltage lockout (OVL). OVL protects the MAX14690 and downstream circuitry from high-voltage stress up to 28V and down to -5.5V. During OVL, the internal circuit remains powered and an interrupt is sent to the host. During OVL, the charger turns off and the system load switch closes, allowing the battery to power SYS. CHGIN is also invalid if it is less than  $V_{BAT}$ , or less than the USB undervoltage threshold. With an invalid input voltage, the SYS-to-BAT load switch closes and allows the battery to power SYS.

**CHGIN Input Current Limit:** The CHGIN input current is limited to prevent input overload. The input current limit is controlled by  $I^2C$ .

**Thermal Limiting:** In case the die temperature exceeds the normal limit ( $T_{CHG\_LIM}$ ), the MAX14690 attempts to limit temperature increase by reducing the input current from CHGIN. In this condition, the system load has priority over the charger current, so the input current is first reduced by lowering the charge current. If the junction temperature continues to rise and reaches the maximum operating limit ( $T_{CHGIN\_SHDN}$ ), no input current is drawn from CHGIN and the battery powers the entire system load.

Adaptive Battery Charging: While the system is powered from CHGIN, the charger draws power from SYS to charge the battery. If the total load exceeds the input current limit, an adaptive charger control loop reduces charge current to prevent  $V_{SYS}$  from collapsing.

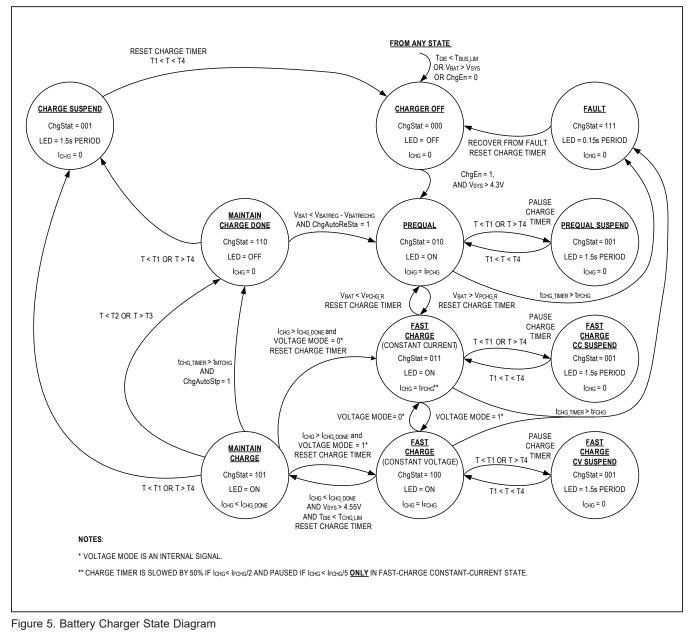

When the charge current is reduced below 50% due to  $I_{LIM}$  or  $T_{DIE}$ , the timer clock operates at half speed. When the charge current is reduced below 20% due to  $I_{LIM}$  or  $T_{DIE}$ , the timer clock is paused.

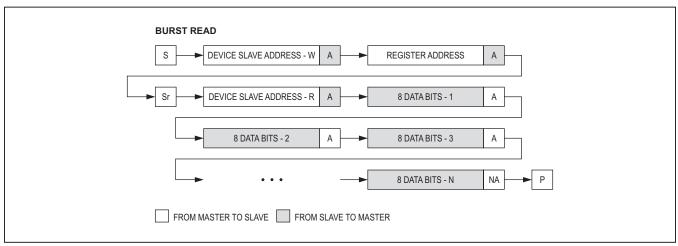

### Fast-Charge Current Setting