**S3 Family of Microcontrollers**

## S3F8S5A Development Kit

#### **User Manual**

UM027202-0816

Copyright ©2016 Zilog<sup>®</sup>, Inc. All rights reserved. <u>www.zilog.com</u>

ii

#### Warning: DO NOT USE THIS PRODUCT IN LIFE SUPPORT SYSTEMS.

#### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2016 Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

S3 and Z8 are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

### **Revision History**

Each instance in this document's revision history reflects a change from its previous edition. To learn more, refer to the corresponding page(s) or appropriate links furnished in the table below.

|             | Revisior | า                                                          |      |

|-------------|----------|------------------------------------------------------------|------|

| Date        | Level    | Description                                                | Page |

| Aug<br>2016 | 02       | Updated for ZDS-S3 version<br>5.3.0. Removed ISP I support | All  |

| Jul<br>2015 | 01       | Original issue.                                            | n/a  |

#### **Overview**

Zilog's S3F8S5A Development Kit, part number S3F8S5A0100ZCOG, allows you to evaluate your S3F8S5A-based designs and applications. The Kit features a Development Board consisting of the following components:

- Four LEDs

- Two pushbuttons

- Buzzer/Speaker

- LCD module

- UART

- 256 byte Serial EEPROM

- Header pins

This user manual provides instructions for setting up and configuring the S3F8S5A Development Board. It includes schematic diagrams and a discussion of the Board features and ZDS II.

The S3F8S5A Development Board features an S3F8S5A MCU in a 44-pin QFP package, plus an S3 PGM connector to connect the Board to a host development PC using the S3 Flash In-System Programmer II (ISP). To learn more about the S3F8S5A MCU, refer to the S3F8S5A Product Specification (<u>PS0323</u>) and/or the S3 Flash In-System Programmer User Manual (<u>UM0266</u>).

This document guides you through the following tasks:

- Downloading and installing ZDSII software and documentation

- Connecting the S3 Flash ISP II and S3F8S5A Development Board to your PC

- Starting the S3F8S5A Ledblink sample program

#### **Kit Contents**

The S3F8S5A Development Kit contains the following items:

- S3F8S5A Development Board

- S3 Flash ISP II

- 10-circuit ribbon cable

- USB A (male) to Mini-B USB cable (2)

- S3F8S5A Development Kit hardcopy insert

2

Figure 1 shows the contents of the S3F8S5A Development Kit.

Figure 1. The S3F8S5A Development Kit

### **Features**

The S3F8S5A Development Kit includes the following key items.

- S3F8S5A Development Board, which contains the following features:

- S3F8S5A 44-pin QFP MCU operating at 12 MHz, with 48KB of internal Flash memory and 1 KB of internal RAM memory

- USB interface to supply power to the board

- LCD module

- Buzzer/Speaker

- UART header at J8

- 256 byte Serial EEPROM

- Test Points headers for all pins of MCU

- MCU current measurement Test Points J4 and J5

- Pin P03/AD3 level adjustable with potentiometer R4

- S3 Flash In-System Programmer II

- ZDSII software, samples, and documentation available free for download

- Sample programs

### **Supported Host Environments**

The S3F8S5A Development Board supports the following operating systems:

- Microsoft Windows 7 (32-bit/64-bit)

- Microsoft Windows 8 (32-bit/64-bit)

### Install the ZDSII Software and Documentation

Observe the following steps to download and install your ZDSII software and documentation.

• Note: If you have already installed ZDSII – S3 <version> and have downloaded the software and documentation by following the procedure on the paper insert in your kit (FL0170), skip ahead to the next section.

- 1. Prior to connecting the S3F8S5A Development Board to your development PC, download ZDS II for S3 v5.3.0 (or later) from the Downloadable Software category in the Zilog Store.

- 2. When the download is complete, unzip the file to your hard drive, then double-click the installation file named ZDS2\_S3\_<Version>.exe and follow the on-screen instructions.

- 3. When the ZDS II installation is complete, double-click the installation file named DOCS\_S3<version>.exe and follow the on-screen instructions.

- 4. When these installations are complete, view the S3F8S5A Development Kit User Manual (UM0272); this document will be located in the following path, by default: C:\Zilog\ZDSII\_ S3 \_<version>\Documentation\Tools\_Documentation

### Establish a Connection with the PC

Observe the following procedure to connect the S3 Flash ISP II and S3F8S5A Development Board to your PC.

**Caution:** Disconnect or turn off the power to the S3F8S5A Development Board before connecting or disconnecting the S3 Flash ISP II.

1. Connect the Mini-B side of the USB A (male)-to-Mini-B cable to the S3 Flash ISP II. Connect the other end of this cable to the PC, as shown in Figure 2.

Figure 2. Connecting the S3 Flash ISP II to the Development PC

2. Connect the 10p 5x2 ribbon cable to the S3 Flash ISP II, as shown in Figure 3.

Figure 3. Connecting the 10-pin Ribbon Cable to the S3 Flash ISP II

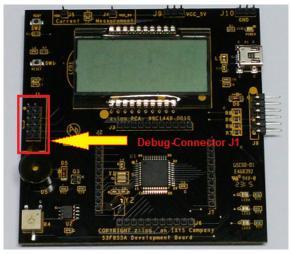

3. Connect the other end of the ribbon cable to Debug Connector J1 on the Development Board, shown in Figure 4.

5

Figure 4. Debug Connector J1

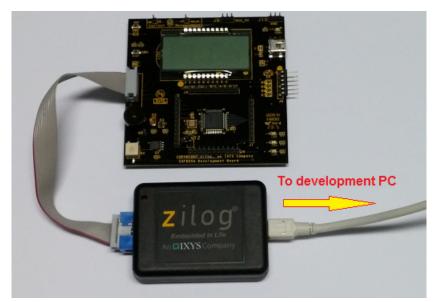

4. After completing the procedure to connect the S3F8S5A Development Board to the PC, the complete setup appears as shown in Figure 5.

Figure 5. The Completed ISP II and Development Board Assembly

### Start the S3F8S5A Ledblink Sample Program

The S3F8S5A Development Kit includes a sample program that demonstrates an LED blinking application. To start the S3F8S5A Ledblink sample program, observe the following procedure.

- 1. Launch ZDSII by navigating from the Windows Start menu to **Programs** → **Zilog ZDSII S3** <**Version**> → **ZDSII S3** <**Version**>.

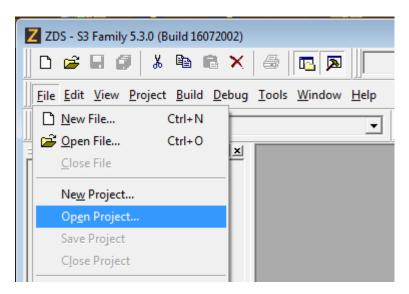

- 2. From the **File** menu in ZDSII, select **Open Project** as indicated in Figure 6, and navigate to the following filepath:

<ZDS Install>\samples\S3F8S5A\ledblink\_asm

Figure 6. The Open Project Selection in the File Menu

3. Select the ledblink.zdsproj project from within the ledblink\_asm folder as indicated in Figure 7 and click **Open**. A list of source files will appear in the Workspace panel.

| Z Open Proj        | ect                              |                    |              | <b>—</b> |

|--------------------|----------------------------------|--------------------|--------------|----------|

| Look in: 🚺         | ledblink_asm 💌                   | ⇔ 🗈 📸 📰 ◄          |              |          |

| Name               | *                                | Date modified      | Size         |          |

| 🛛 ledblink         | zdsproj                          | 7/20/2016 10:54 AM | 24 KB        |          |

|                    |                                  |                    |              |          |

|                    |                                  |                    |              |          |

|                    |                                  |                    |              |          |

|                    |                                  |                    |              |          |

| File <u>n</u> ame: | ledblink.zdsproj                 |                    | <u>O</u> pen |          |

| Files of type:     | ZDS II Project Files (*.zdsproj) |                    | ▼ Cance      |          |

Figure 7. Select the ledblink.zdsproj Project

- 4. From the **Build** menu, select **Set Active Configuration** to open the Select Configuration dialog box.

- 5. Select **Debug**, then click **OK** to close the Select Configuration dialog box.

- 6. From the **Project** menu in ZDSII, select **Settings** to open the Project Settings dialog box. In the Project Settings dialog box, click the **Debugger** tab.

7. On the Debugger page, select **S3F8S5X\_FlashIsplI** from the Target list, then select **S3FlashIsplI** from the **Debug Tool** drop-down menu, as indicated in Figure 8.

| Project Settings                                                                               |                                                                                                                                    |                 |                               | ×    |

|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------|------|

| Configuration: Release                                                                         | •                                                                                                                                  |                 |                               |      |

| General                                                                                        | 😼 Debugger                                                                                                                         |                 |                               |      |

| Assembler<br>Linker<br>Objects and Libraries<br>Address Spaces<br>Warnings                     | <ul> <li>Include ISP debug library (Res<br/>Include Enhanced ISP Debug<br/>Run to Cursor, Reset and Res</li> <li>Target</li> </ul> | g Library (Step | into, Step Over,Step Out, Go. |      |

| - Output                                                                                       | Target Name                                                                                                                        | Loc             | cation                        |      |

|                                                                                                | Setup                                                                                                                              | Add             | Copy Delete                   |      |

|                                                                                                | Debug Tool<br>Current: S3Rashlspll<br>OPENice_i2000<br>S3Rashlspll                                                                 |                 | Setup                         |      |

| ,<br>Note<br>This ZDSII version requires firmware 1.<br>To upgrade the firmware, please select | 5 or later if the selected debug tool is                                                                                           |                 |                               |      |

|                                                                                                |                                                                                                                                    | OK              | Cancel                        | Help |

Figure 8. Select the Target and Debug Tool

8. After selecting **S3FlashIsplI** from the Debug Tool drop-down menu, click **Setup** to select the serial number of the S3 Flash ISP II you are using, as indicated in Figure 9. Click **OK** to close the Setup USB Communication dialog box.

9

| Setup USB Communication             | J          |

|-------------------------------------|------------|

| Serial Number: 1504080006           |            |

| OK Cancel                           | ppy Delete |

| Debug Tool<br>Current: S3FlashIspII | ✓ Setup    |

Figure 9. The Setup USB Communication Dialog

Note: The serial number you see on your screen will be different from the serial number shown > in Figure 9.

- 9. After selecting the serial number of the S3 Flash ISP II that you are using, select Setup from the Target field to select the Target Voltage.

- 10. From the target Configuration dialog, enter "0" on ISP\_DBRG\_IDX and select the **3.3V by ISP** button and Click **OK**. See Figure 10.

| Target Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISP Baudrate Adjustment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ISP_BRG_IDX: 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Note: ISP baud Rate = CPU Clock /(32 + ISP_BRG_IDX)<br>Where CPU Clock = fosc /CPU_Div<br>Where CPU_Div is determined by the CLKCON value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Target Voltage:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| G By External Source     Source |

| C 5.0 V by ISP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| OK Cancel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Figure 10. The Target Configuration Dialog

- 11. Make sure that the **Enhanced ISP Debug Library** is selected on the debugger window..

- 12. Click **OK** to close the Project Settings dialog box.

- 13. If you are prompted to rebuild any affected files, click **Yes**. Otherwise, choose **Build** from the menu bar, then click **Rebuild All**. The following example message is displayed:

| Space | Base   | Тор    | Size    | Used  | Unused |

|-------|--------|--------|---------|-------|--------|

| Page0 | P:00   | P:05   | СОН     | 6H    | BAH    |

|       |        |        | ( 192   | 6     | 186)   |

| ROM   | C:0000 | C:1BB7 | C000H   | 1AB8H | A548H  |

|       |        |        | ( 49152 | 6840  | 42312) |

|       |        |        |         |       |        |

#### OUTPUT CHECKSUM

ledblink.hex F834 ledblink.lod F834 0 warning(s 0 error(s) Build succeeded.

**Note:** This Output Checksum message is an example and may not match the actual checksum of the project for a particular release of the ZDS installation software.

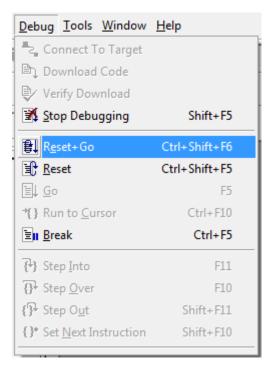

14. To run the application, select **Reset+Go** from the **Debug** menu, as indicated in Figure 11. As a result, LEDs D2, D3, and D4 will blink in sequence.

Figure 11. Select Reset+ Go from the Debug Menu

#### **Troubleshooting Tips**

The following troubleshooting tips are useful when starting the S3F8S5A Ledblink sample program.

- Ensure that the LED1 PWR indicator on the S3 Flash ISP II lights up upon connecting to the USB port of your PC.

- Navigate to **Project** → **Settings** → **Debugger** → **Debug Tool** → **Setup**. Upon clicking **Setup** on the Setup USB Communication dialog box, verify that the S3FlashIspII serial number is displayed.

- Remove and reconnect the ISP II on the USB port of your PC.

- Refer to Figure 14 on page 13 to learn more about the operations and power options of the S3F8S5A Development Board.

### S3F8S5A Development Board

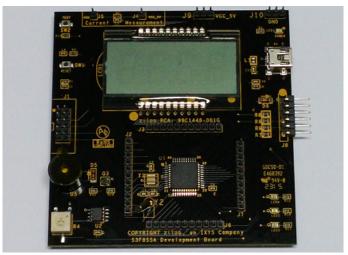

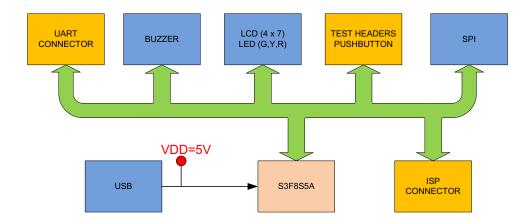

The purpose of the S3F8S5A Development Kit is to provide a set of hardware and software tools for the development of hardware and firmware for applications based on the S3F8S5A microcontroller. An image of the S3F8S5A Development Board is shown in Figure 12; a block diagram is shown in Figure 13.

Figure 12. The S3F8S5A Development Board

Figure 13. S3F8S5A Development Board Block Diagram

### **Operations and Power Options**

The operations and power options of the S3F8S5A Development Board are listed in Figure 14.

| Operat | ions and Pow                | er Opti  | ons            |                    |                    |                                |

|--------|-----------------------------|----------|----------------|--------------------|--------------------|--------------------------------|

| Option | Operations ISP II USB Cable |          | Target Voltage | Power              | Notes              |                                |

|        |                             | cable on | on P1          |                    |                    |                                |

|        |                             | J1       |                |                    |                    |                                |

| 1      | Programming/                | ON       | OFF            | 3.3V by ISP        | VDD = 3.3V         | MCU power from S3 ISP II cable |

|        | Debugging                   |          |                |                    | VCC_5V = 3.3V      |                                |

| 2      | Programming/                | ON       | OFF            | 5.0V by ISP        | VDD = 5.0V         | MCU power from S3 ISP II cable |

|        | Debugging                   |          |                |                    | VCC_5V = 5.0V      |                                |

| 3      | Programming/                | ON       | See Notes      | By External Source | VDD = VCC_5V = Vin | MCU power from External Source |

|        | Debugging                   |          |                |                    |                    | via P1 or J9                   |

| 4      | Standalone                  | OFF      | ON             | Vin at P1          | VDD = VCC_5V = Vin | MCU power from External Source |

|        |                             |          |                |                    |                    | via P1                         |

| 5      | Standalone                  | OFF      | OFF            | Vin at J9          | VDD = VCC_5V = Vin | MCU power from External Source |

|        |                             |          |                |                    |                    | via J9                         |

Figure 14. Operations and Power Options of the S3F8S5A Development Board

### S3F8S5A MCU

Key features of the S3F8S5A MCU include:

- SAM88RC CPU core

- 48K x 8 bits program memory

- $1024 \times 8$  bits data memory

- Endurance: 10,000 Erase/Program cycles

- 78 instructions

- 36 normal I/O pins in the 44-pin QFP package

- Eight bit-programmable pins for external interrupts

- One 8-bit basic timer for oscillation stabilization and watchdog functions (system reset)

- Three 8-bit timer/counters and two 16-bit timer/counters with selectable operating modes

- Watch timer for real time

- LCD controller/driver

- A/D converter with 8 selectable input pins

- Synchronous SIO modules

- Two asynchronous UART modules

- Pattern generation module

To learn more about the S3F8S5A MCU, refer to the S3F8S5A Product Specification (PS0323).

#### **Magnetic Buzzer**

The CEM1206S magnetic buzzer (U5) manufactured by CUI Inc. is rated at a frequency of 2400 Hz and an operating voltage of 3.0-8.0 V zero-to-peak (V<sub>0-P</sub>). An image of the CEM1206S device is shown in Figure 15.

Figure 15. Magnetic Buzzer

To learn more about the CEM1206S device, visit <u>http://www.cui.com/product/resource/cem-1206s.pdf.</u>

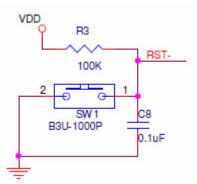

### **Reset Circuit**

The reset circuit features a  $100 \text{K}\Omega$  pull-up resistor R3 and SW1. This circuit resets the S3F8S5A MCU when SW1 is pressed. See Figure 16 for a representation of the reset circuit.

Figure 16. The Reset Circuit

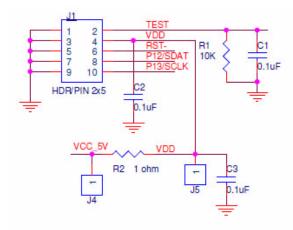

#### **ISP II Connector**

The ISP II connector (J1) provides an interface between the S3 Flash ISP II tool and the S3F8S5A device. See Figure 17 for an illustration of the ISP II connector.

16

Figure 17. The ISP II Connector

### LCD

The VIM-404-DP-RC-S-HV LCD manufactured by Varitronix Ltd. is a 20-pin module. Figure 18 shows an image of this LCD.

Figure 18. LCD

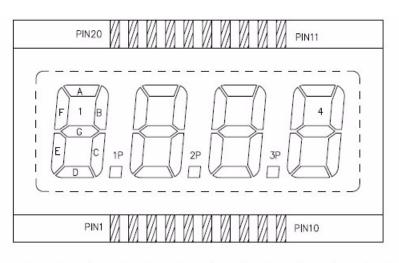

This four-digit LCD is activated by selecting the segment of each digit that must light up. Figure 19 shows the LCD pin configuration and assignments.

17

| PIN  | 1-3  | 4  | 5  | 6  | 7  | 8    | 9-10 | 11   | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20   |

|------|------|----|----|----|----|------|------|------|----|----|----|----|----|----|----|----|------|

| COM1 | N.C. | 1B | 2B | 3B | 4B |      | N.C. | COM1 | 4A | 4F | 3A | 3F | 2A | 2F | 1A | 1F |      |

| COM2 | N.C. | 1C | 2C | 3C | 4C |      | N.C. |      | 4G | 4E | 3G | 3E | 2G | 2E | 1G | 1E | COM2 |

| COM3 | N.C. | 1P | 2P | 3P |    | COM3 | N.C. |      | 4D |    | 3D |    | 2D |    | 1D |    |      |

REMARKS: N.C. = NO CONNECTION

Figure 19. LCD Pin Configuration and Assignments

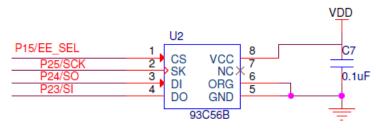

### Serial EEPROM

The 93C56B is enabled through the Chip Select pin (CS) and accessed via a 3-wire serial interface consisting of Data Input (DI), Data Output (DO), and Shift Clock (SK). Upon receiving a Read instruction at DI, the address is decoded, and the data is clocked out serially on the DO pin. Figure 20 shows the Serial EEPROM schematics.

Figure 20. Serial EEPROM

18

### **ZDS Flash Loader Utility**

A Flash Loader utility is included in Zilog Developer Studio II via the Tools menu. Figure 21 shows an image of the Flash Programming screen.

| Hex File | e:                                  |                       |                 |   |                                 | ISP Serial Number    |  |  |  |

|----------|-------------------------------------|-----------------------|-----------------|---|---------------------------------|----------------------|--|--|--|

|          |                                     |                       |                 |   | Pad File With                   |                      |  |  |  |

| log\zd   | sii_s3_5.3.0\samples\s              | 318s5a\ledblink_asm\d | ebug\ledbink.he |   | ← FF ← 00<br>● None ← Other: 98 | 1607140002 • C       |  |  |  |

| lash 0   | ptions                              |                       |                 |   | Serialization                   |                      |  |  |  |

| _        | able Read Protection                |                       |                 | ^ | Method                          | Serial Address (Hex) |  |  |  |

| En       | able HardLock Prote                 | ction                 |                 |   | ( None                          | 0000                 |  |  |  |

| _        | nart Options                        |                       |                 |   |                                 |                      |  |  |  |

|          | From the .hex file                  |                       |                 | Ξ | C Pseudorandom                  |                      |  |  |  |

| 0        | Custom                              |                       |                 |   | C Increment/Decrement(+/-)      | Serial Number Size   |  |  |  |

| -        | <ul> <li>Option Byte 0x0</li> </ul> |                       |                 |   | 0                               | # Bytes 1 💌          |  |  |  |

|          | ISP Reset Ve                        | ctor                  |                 |   |                                 |                      |  |  |  |

|          | O 200H                              |                       |                 |   | - Serial Number (Hex)           |                      |  |  |  |

|          | O 300H                              |                       |                 |   | 00                              | CH-CD-               |  |  |  |

|          | O 900H                              |                       |                 |   | 00 (• Hex C Dec                 |                      |  |  |  |

|          |                                     | efault)               |                 |   |                                 |                      |  |  |  |

| 1        | 1                                   |                       |                 |   |                                 |                      |  |  |  |

| Operal   | tions Options                       |                       |                 |   | Status                          |                      |  |  |  |

| ₽ E      | rase Before Programmi               | ng                    |                 |   |                                 | ~                    |  |  |  |

| ∏ Ir     | nclude Serial Number                |                       |                 |   |                                 |                      |  |  |  |

| In In    | nclude Flash Options                |                       |                 |   |                                 |                      |  |  |  |

| Operal   | tions                               |                       |                 | _ |                                 |                      |  |  |  |

|          | Erase                               | Program + Verify      | Program         |   |                                 |                      |  |  |  |

|          | Verify                              | Program Options       | Read Options    |   |                                 |                      |  |  |  |

|          | Device Checkum                      | File Checksum         | View Memory     |   |                                 | 3                    |  |  |  |

|          |                                     |                       |                 |   |                                 |                      |  |  |  |

Figure 21. The Flash Programming Screen

You can program the S3F8S5A MCU directly using the hex code generated from the ZDS IDE tools.

### S3F8S5A Development Kit Documentation

The documents associated with the S3F8S5A Development Kit are listed in Table 1. Each of these documents can be obtained from the Zilog website by clicking the link associated with its Document Number. Alternatively, navigate to the directory listed in the Location column in your installed application.

| Table 1. S3F8S5A Development Kit Documentation | n |

|------------------------------------------------|---|

|------------------------------------------------|---|

| Document      | Description                                          | Location                          |

|---------------|------------------------------------------------------|-----------------------------------|

| <u>UM0272</u> | S3F8S5A Development Kit User Manual                  | Documentation\Tools_Documentation |

| PS0323        | S3F8S5A Product Specification                        | Documentation\Chip_Documentation  |

| UM0266        | S3 Flash In-System Programmer User Manual            | Documentation\Tools_Documentation |

| FL0170        | S3F8S5A0100ZCOG Development Kit Insert               | Documentation\Tools_Documentation |

| FL0165        | S3 Flash In-System Programmer Insert                 | Documentation\Tools_Documentation |

| Online Help   | ZDS II-S3 IDE, Assembler and C Compiler On-Line Help | ZDS II-S3 >Help >Help Topics      |

### S3F8S5A Sample Projects

Table 2 lists the sample projects developed for this application. Follow the filepath stated in the Location column to access the associated project.

| Project  | Location                     |

|----------|------------------------------|

| timerD   | samples\S3F8S5A\ISP_BL_Demo  |

| lcd      | samples\S3F8S5A\LCD_asm      |

| lcd      | samples\S3F8S5A\LCD_c        |

| ledblink | samples\S3F8S5A\ledblink_asm |

| ledblink | samples\S3F8S5A\ledblink_c   |

| eeprom   | samples\S3F8S5A\EEPROM_c     |

|          |                              |

Table 2. S3F8S5A Sample Projects

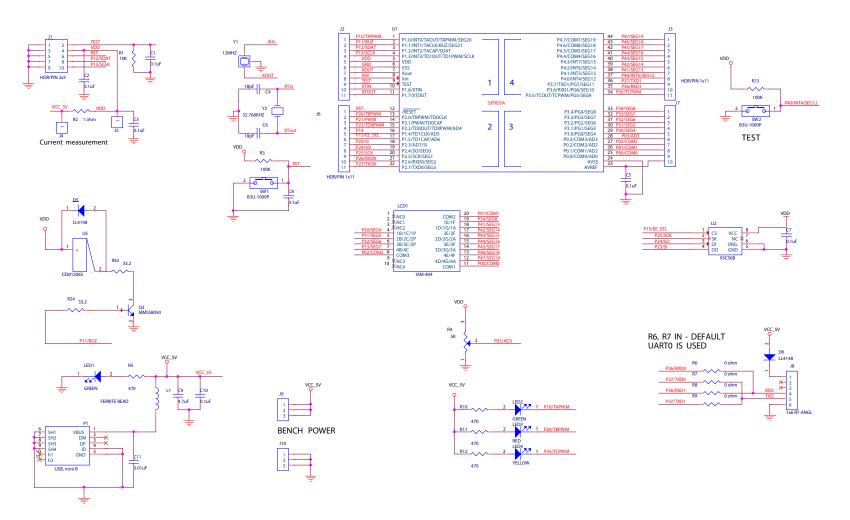

### **Appendix A. Schematic Diagrams**

Figure 22 presents schematic diagrams of the S3F8S5A Development Board.

Figure 22. S3F8S5A Development Board Schematic Diagram

# Customer Support

To share comments, get your technical questions answered, or report issues you may be experiencing with our products, please visit Zilog's Technical Support page at <u>http://support.zilog.com</u>.

To learn more about this product, find additional documentation, or to discover other facets about Zilog product offerings, please visit the <u>Zilog Knowledge Base</u> or consider participating in the <u>Zilog Forum</u>.

This publication is subject to replacement by a later edition. To determine whether a later edition exists, please visit the Zilog website at <u>http://www.zilog.com/</u>

### **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

ZiLOG: S3F8S5A0100ZCOG